STM32中FSMC的总结

STM32接口FSMCFMC难点的理解---写的比较明白,容易理解

STM32接⼝FSMCFMC难点的理解---写的⽐较明⽩,容易理解摘录者说:这篇⽂章说明⽩了以下两件事:(1)ARM CPU的的32位地址怎样对应到FSMC的25:0的26根地址线;(2) 存储器宽度为8位应该怎样对应,存储器宽度为16位应该怎样对应;⼀,FSMC简FSMC,即灵活的静态存储控制器,能够与同步或异步存储器和 16 位 PC 存储器卡连接,STM32 的 FSMC 接⼝⽀持包括 SRAM、NAND FLASH、NOR FLASH 和 PSRAM 等存储器。

⼆,FSMC存储块STM32F767的FMC将外部存储器划分为6个固定⼤⼩的256M的存储区域,如下图如图:FSMC分为4块,每块256M字节⼜被划分为4*64,即四个⽚选NOR / PSRAM使⽤块1,共256MNAND闪存使⽤块2,3,共512MPC卡使⽤块4,共256M三,存储块1(Bank1)寄存器STM32 的 FSMC 存储块 1(Bank1)被分为 4 个区,每个区管理 64M 字节空间,每个区都有独⽴的寄存器对所连接的存储器进⾏配置。

Bank1 的 256M 字节空间由 28 根地址线(HADDR[27:0])寻址。

这⾥ HADDR 是内部 AHB 地址总线,其中 HADDR[25:0]来⾃外部存储器地址FSMC_A[25:0],⽽ HADDR[26:27]对 4 个区进⾏寻址。

我们要特别注意 HADDR[25:0]的对应关系:当 Bank1 接的是 16 位宽度存储器的时候:HADDR[25:1]对应 FSMC-A[24:0]。

当 Bank1 接的是 8 位宽度存储器的时候:HADDR[25:0]对应FSMC_A[25:0]。

⽐如外部存储器接到FMC_NE1上⾯,那么外部存储器的地址为HADDR[26:27] +FMC_A[25:0]=0x60000000+FMC_A[25:0]。

注:不论外部接 8 位/16 位宽设备,FSMC_A[0] 永远接在外部设备地址 A[0] 。

FSMC静态存储器控制器

STM32 FSMC学习笔记FSMC全称“静态存储器控制器”。

使用FSMC控制器后,可以把FSMC提供的FSMC_A[25:0]作为地址线,而把FSMC提供的FSMC_D[15:0]作为数据总线。

(1)当存储数据设为8位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_8b)地址各位对应FSMC_A[25:0],数据位对应FSMC_D[7:0](2)当存储数据设为16位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_ 16b)地址各位对应FSMC_A[24:0],数据位对应FSMC_D[15:0]FSMC 包括4个模块:(1)AHB接口(包括FSMC配置寄存器)(2)NOR闪存和PSRAM控制器(驱动LCD的时候LCD就好像一个PSRAM的里面只有2个16位的存储空间,一个是DA TA RAM 一个是CMD RAM)(3)NAND闪存和PC卡控制器(4)外部设备接口注:FSMC可以请求AHB进行数据宽度的操作。

如果AHB操作的数据宽度大于外部设备(NOR或NAND或LCD)的宽度,此时FSMC将AHB操作分割成几个连续的较小的数据宽度,以适应外部设备的数据宽度。

FSMC对外部设备的地址映像从0x6000 0000开始,到0x9FFF FFFF结束,共分4个地址块,每个地址块256M字节。

可以看出,每个地址块又分为4个分地址块,大小64M。

对NOR的地址映像来说,我们可以通过选择HADDR[27:26]来确定当前使用的是哪个64M的分地址块,如下页表格。

而这四个分存储块的片选,则使用NE[4:1]来选择。

数据线/地址线/控制线是共享的。

NE1 ->Bank1 NE2->Bank2 NE3->Bank3 NE4->Bank4若 NE1 连接,则每小块NOR/PSRAM 64M第一块:6000 0000h--63ff ffffh (DATA长度为8位情况下,由地址线FSMC_A[25:0]决定;DATA长度为16位情况下,由地址线FSMC_A[24:0]决定)第二块:6400 0000h--67ff ffffh第二块:6800 0000h--6bff ffffh第三块:6c00 0000h--6fff ffffh注:这里的HADDR是需要转换到外部设备的内部AHB地址线,每个地址对应一个字节单元。

STM32单片机FSMC的使用解析

STM32单片机FSMC的使用解析

在做项目的过程中遇到了这个问题,感觉文章写得不错,共享给对FSMC的使用怀有疑惑的同伴们!

LCD有如下控制线:

CS:Chip Select片选,低电平有效

RS:Register Select寄存器选择

WR:Write写信号,低电平有效

RD:Read读信号,低电平有效

RESET:重启信号,低电平有效

DB0-DB15:数据线

假如这些线,全部用普通IO口控制。

根据LCD控制芯片手册(大部分控制芯片时序差不多):

如果情况如下:

DB0-DB15的IO全部为1(表示数据0xff),也可以为其他任意值,这里以0xff为例。

CS为0(表示选上芯片,CS拉低时,芯片对传入的数据才会有效)

RS为1(表示DB0-15上传递的是要被写到寄存器的值),如果为0,表示传递的是数据。

WR为0,RD为1(表示是写动作),反过来就是读动作。

RESET一直为高,如果RESET为低,会导致芯片重启。

这种情况,会导致一个值0xff被传入芯片,被LCD控制芯片当作写寄存器值去解析。

LCD 控制芯片收到DB0-15上的值之后,根据其他控制线的情况,它得出结论,这个0xff是用来设置寄存器的。

一般情况下,LCD控制芯片会把传入的寄存器值的高8位当做寄存器地址(因为芯片内部肯定不止一个寄存器),低8位当做真正的要赋给对应寄存器值。

这样,就完成了一个写LCD控制芯片内部寄存器的时序。

如果上述情况不变,只将RS置低,那么得到的情况如下:LCD控制芯片会把DB0-15上的数据当做单纯的数据值来处理。

那么假如LCD处在画图状态,这个传入的值0xff,就。

STM32使用FSMC控制NAND flash 例程概要

本文原创于观海听涛,原作者版权所有,转载请注明出处。

近几天开发项目需要用到STM32驱动NAND FLASH,但由于开发板例程以及固件库是用于小页(512B,我要用到的FLASH为1G bit的大页(2K,多走了两天弯路。

以下笔记将说明如何将默认固件库修改为大页模式以驱动大容量NAND,并作驱动。

本文硬件:控制器:STM32F103ZET6,存储器:HY27UF081G2A首先说一下NOR与NAND存储器的区别,此类区别网上有很多,在此仅大致说明:1、Nor读取速度比NAND稍快2、Nand写入速度比Nor快很多3、NAND擦除速度(4ms远快于Nor(5s4、Nor 带有SRAM接口,有足够的地址引脚来寻址,可以很轻松的挂接到CPU 地址和数据总线上,对CPU要求低5、NAND用八个(或十六个引脚串行读取数据,数据总线地址总线复用,通常需要CPU支持驱动,且较为复杂6、Nor主要占据1-16M容量市场,并且可以片内执行,适合代码存储7、NAND占据8-128M及以上市场,通常用来作数据存储8、NAND便宜一些9、NAND寿命比Nor长10、NAND会产生坏块,需要做坏块处理和ECC更详细区别请继续百度,以上内容部分摘自神舟三号开发板手册下面是NAND的存储结构:由此图可看出NAND存储结构为立体式正如硬盘的盘片被分为磁道,每个磁道又分为若干扇区,一块nand flash也分为若干block,每个block分为如干page。

一般而言,block、page之间的关系随着芯片的不同而不同。

需要注意的是,对于flash的读写都是以一个page开始的,但是在读写之前必须进行flash 的擦写,而擦写则是以一个block为单位的。

我们这次使用的HY27UF081G2A其PDF介绍:Memory Cell Array= (2K+64 Bytes x 64 Pages x 1,024 Blocks由此可见,该NAND每页2K,共64页,1024块。

基于STM32单片机FSMC接口驱动LCD的配置与分析

基于STM32单片机FSMC接口驱动LCD的配置与分析概述:STM32单片机是一款高性能、低功耗的32位ARM Cortex-M系列微控制器。

它具有丰富的外设接口,其中包括FSMC(Flexible Static Memory Controller)接口,用于连接外部存储器,例如LCD显示器。

本文将详细介绍如何配置和驱动LCD显示器,以及分析FSMC接口的工作原理。

一、LCD驱动接口配置1. 在STM32的标准外设库中,FSMC的配置函数位于STM32F10x_stdperiph_driver库的stm32f10x_fsmc.c和stm32f10x_fsmc.h文件中。

通过这些函数,可以配置FSMC接口的参数,以使它能够连接和驱动LCD。

2.首先,需要配置FSMC的时钟预分频值。

根据LCD的要求以及系统时钟频率,选择适当的预分频值。

这可以通过设置FSMC_BCRx寄存器中的MBKEN和PS字段来实现。

3.然后,需要配置FSMC的存储芯片选择使能信号(CSEN)和片选信号(ALE)。

这可以通过设置FSMC_BCRx寄存器中的CSEN和ALEN字段来实现。

4.接下来,需要配置FSMC的读写延迟、数据宽度、存储器类型等参数。

这可以通过设置FSMC_BTRx和FSMC_BWTRx寄存器来实现。

5.最后,需要配置FSMC的地址线、数据线和控制线的映射关系。

这可以通过设置FSMC_BCRx寄存器中的MWID、MTYP、MUXEN、MWID和NWID 字段来实现。

二、FSMC接口工作原理1.FSMC接口是一种高速并行接口,它通过多路复用来连接不同的外部存储器。

它具有独立的读/写数据线和地址线,以及控制线,用于选择读/写操作和片选信号。

2. FSMC接口支持不同类型的存储器,例如SRAM、NOR Flash、NAND Flash和LCD。

每种存储器都有不同的时序和接口要求。

3.FSMC接口的时序参数主要包括时钟预分频值、读/写延迟、数据宽度和地址线宽度等。

STM32FSMC详细理解

STM32FSMC详细理解第二个角度理解:FSMC总线上看,LCD只有2个地址.Bank1_LCD_C是写寄存器,此时RS=1,告诉LCD我在总线上输出数据的是寄存器的地址Bank1_LCD_D是写数据,此时RS=0,告诉LCD我在总线上输出地数据是寄存器的数据或者GRAM的数据.写寄存器数据按2步来:第一步先往Bank1_LCD_C (对应RS=1),送寄存器的地址:*(__IO uint16_t *) (Bank1_LCD_C)= index; 接着在Bank1_LCD_D这个地址(对应RS=0),写入刚指向的寄存器的数据: *(__IO uint16_t *) (Bank1_LCD_D)= val;为什么*(__IO uint16_t *) (Bank1_LCD_C)= index; 就是往 LCD 写寄存器呢?这是一个16位的IO赋值操作,地址是Bank1_LCD_C,这个地址就是指向FSMC的Bank1的NE1对应的地址空间。

而LCD片选正是连接到NE1,具体地址要看RS接到哪一根地址线上。

当CPU执行到这一条的时候,就会通过FSMC总线控制器在数据总线上进行一个地址为Bank1_LCD_C的数据写操作,此操作自动完成CS信号,RD信号,WR信号,以及地址总线数据(RS信号)的输出以及数据总线数据的输出.其他的操作都是这两个操作组合完成。

也就是我上面所说的,'所有的寄存器地址和寄存器数据,以及GRAM数据都是通过IO0-IO15完成传输的,而不是FSMC的地址.这是容易搞混的一个地方.LCD的FSMC地址只有一根 ,就是RS.'----------------------------------------------------------------------------------------------------------------------第三个角度理解: 把TFT看做类似SRAM的存储器,只能接在BANK1上。

STM32-FSMC-NOR FLASH

一、基本概念(详细内容见st网站stm32应用笔记AN2784)1. FSMC配置控制一个NOR闪存存储器,需要FSMC提供下述功能:●选择合适的存储块映射NOR闪存存储器:共有4个独立的存储块可以用于与NOR闪存、SRAM和PSRAM存储器接口,每个存储块都有一个专用的片选管脚。

●使用或禁止地址/数据总线的复用功能。

●选择所用的存储器类型:NOR闪存、SRAM或PSRAM。

●定义外部存储器的数据总线宽度:8或16位。

●使用或关闭同步NOR闪存存储器的突发访问模式。

●配置等待信号的使用:开启或关闭,极性设置,时序配置。

●使用或关闭扩展模式:扩展模式用于访问那些具有不同读写操作时序的存储器。

因为NOR闪存/SRAM控制器可以支持异步和同步存储器,用户只须根据存储器的参数配置使用到的参数。

FSMC提供了一些可编程的参数,可以正确地与外部存储器接口。

依存储器类型的不同,有些参数是不需要的。

当使用一个外部异步存储器时,用户必须按照存储器的数据手册给出的时序数据,计算和设置下列参数:●ADDSET:地址建立时间●ADDHOLD:地址保持时间●DATAST:数据建立时间●ACCMOD:访问模式这个参数允许FSMC可以灵活地访问多种异步的静态存储器。

共有4种扩展模式允许以不同的时序分别读写存储器。

在扩展模式下,FSMC_BTR用于配置读操作,FSMC_BWR用于配置写操作。

(译注:如果读时序与写时序相同,只须使用FSMC_BTR即可。

)如果使用了同步的存储器,用户必须计算和设置下述参数:●CLKDIV:时钟分频系数●DATLAT:数据延时如果存储器支持的话,NOR闪存的读操作可以是同步的,而写操作仍然是异步的。

当对一个同步的NOR闪存编程时,存储器会自动地在同步与异步之间切换;因此,必须正确地设置所有的参数。

2. 时序计算如上所述,对于异步NOR闪存存储器或类似的存储,有不同的访问协议。

首先要确定对特定存储器所需要使用的操作协议,选择的依据是不同的控制信号和存储器在读或写操作中的动作。

STM32与FPGA+之间的FSMC通信

1.引言STM32是ST(意法半导体)公司推出的基于ARM内核Cortex-M3的32位微掌握器系列.Cortex-M3内核是为低功耗和价钱迟钝的运用而专门设计的,具有凸起的能效比和处理速度.经由过程采取Thumb-2高密度指令集,Cortex-M3内核下降了体系存储请求,同时快速的中止处理可以或许知足掌握范畴的高及时性请求,使基于该内核设计的STM32系列微掌握器可以或许以更优胜的性价比,面向更普遍的运用范畴.STM32系列微掌握器为用户供给了丰硕的选择,可实用于工业掌握.智能家电.建筑安防.医疗装备以及花费类电子产品等多方位嵌入式体系设计.STM32系列采取一种新型的存储器扩大技巧——FSMC,在外部存储器扩大方面具有奇特的优势,可依据体系的运用须要,便利地进行不合类型大容量静态存储器的扩大.2.F SMC机制2.1F SMC技巧优势①支撑多种静态存储器类型.STM32经由过程FSMC町以与SRAM.ROM.PSRAM.NOR Flash和NANDFlash存储器的引脚直接相连.②支撑丰硕的存储操纵办法.FSMC不但支撑多种数据宽度的异步读/写操纵,并且支撑对NOR/PSRAM/NAND存储器的同步突发拜访方法.③支撑同时扩大多种存储器.FSMC的映射地址空间中,不合的BANK 是自力的,可用于扩大不合类型的存储器.当体系中扩大和运用多个外部存储器时,FSMC会经由过程总线悬空延迟时光参数的设置,防止各存储器对总线的拜访冲突.④支撑更为普遍的存储器型号.经由过程对FSMC的时光参数设置,扩大了体系中可用存储器的速度规模,为用户供给了灵巧的存储芯片选择空间.⑤支撑代码从FSMC扩大的外部存储器中直接运行,而不须要起首调入内部SRAM.STM32微掌握器之所以可以或许支撑NOR Flash和NAND Flash这两类拜访方法完全不合的存储器扩大,是因为FSMC内部现实包含NOR Flash和NAND/PC Card两个掌握器,分离支撑两种截然不合的存储器拜访方法.在STM32内部,FSMC的一端经由过程内部高速总线AHB衔接到内核Cortex-M3,另一端则是面向扩大存储器的外部总线.内查对外部存储器的拜访旌旗灯号发送到AHB 总线后,经由FSMC转换为相符外部存储器通讯规约的旌旗灯号,送到外部存储器的响应引脚,实现内核与外部存储器之间的数据交互.FSMC起到桥梁感化,既可以或许进行旌旗灯号类型的转换,又可以或许进行旌旗灯号宽度和时序的调剂,屏障失落不合存储类型的差别,使之对内核而言没有差别.FSMC治理 1 GB的映射地址空间.该空间划分为4个大小为256 MB的BANK,每个BANK又划分为4个64 MB的子BANK,如表1所列.FSMC的2个掌握器治理的映射地址空间不合.NOR Flash掌握器治理第1个BANK,NAND/PC Card掌握器治理第2~4个BANK.因为两个掌握器治理的存储器类型不合,扩大时应依据选用的存储装备类型肯定其映射地位.个中,BANK1的4个子BANK失去自力的片选线和掌握存放器,可分离扩大一个自力的存储装备,而BANK2~BANK4只有一组掌握存放器.3.F SMC扩大外部SRAM设置装备摆设在STM32 与 FPGA 进行通讯的时刻,FPGA其实可以看做STM32外部的SRAM,是以响应的设置装备摆设可以参考对外部SRAM的设置装备摆设.SRAM/ROM.NOR Flash和PSRAM类型的外部存储器都是由FSMC的NOR Flash掌握器治理的,扩大办法基底细同,个中NOR Flash最为庞杂.经由过程FSMC扩大外部存储器时,除了传统存储器扩大所须要的硬件电路外,还须要进行FSMC初始化设置装备摆设.FSMC供给大量.过细的可编程参数,以便可以或许灵巧地进行各类不合类型.不合速度的存储器扩大.外部存储器可否正常工作的症结在于:用户可否依据选用的存储器型号,对设置装备摆设存放器进行合理的初始化设置装备摆设3.1地址映射空间经由过程对FSMC特别功效存放器FSMC_BCRi(i为子BANK号,i=1,…,4)中对应掌握位的设置,FSMC依据不合存储器特点可灵巧地进行工作方法和旌旗灯号的调剂.依据选用的存储器芯片肯定须要设置装备摆设的存储器特点,重要包含以下方面:①存储器类型(MTYPE)是SRAM/ROM.PSRAM,照样NOR FlaSh;②存储芯片的地址和数据引脚是否复用(MUXEN),FSMC可以直接与AD0~AD15复用的存储器相连,不须要增长外部器件;③存储芯片的数据线宽度(MWID),FSMC支撑8位/16位两种外部数据总线宽度;④对于NOR Flash(PSRAM),是否采取同步突发拜访方法(BURSTEN);⑤对于NOR Flash(PSRAM),NWAIT旌旗灯号的特点解释(WAITEN.WAITCFG.WAITPOL);⑥对于该存储芯片的读/写操纵,是否采取雷同的时序参数来确准时序关系(EXTMOD).FSMC经由过程运用可编程的存储器时序参数存放器,拓宽了可选用的外部存储器的速度规模.FSMC的SRAM掌握器支撑同步和异步突发两种拜访方法.选用同步突发拜访方法时,FSMC将HCLK(体系时钟)分频后,发送给外部存储器作为同步时钟旌旗灯号FSMC_CLK.此时须要的设置的时光参数有2个:①HCLK与FSMC_CLK的分频系数(CLKDIV),可认为2~16分频;②同步突发拜访中获得第1个数据所须要的等待延迟(DATLAT).对于异步突发拜访方法,FSMC重要设置3个时光参数:地址树立时光(ADDSET).数据树立时光(DATAST)和地址保持时光(ADDHLD).FSMC分解了SRAM/ROM.PSRAM和NOR Flash产品的旌旗灯号特色,界说了4种不合的异步时序模子.选用不合的时序模子时,须要设置不合的时序参数,如表2所列.在现实扩大时,依据选用存储器的特点确准时序模子,从而肯定各时光参数与存储器读/写周期参数指标之间的盘算关系;运用该盘算关系和存储芯片数据手册中给定的参数指标,可盘算出FSMC所须要的各时光参数,从而对时光参数存放器进行合理的设置装备摆设.4.S TM32扩大外部SRAM实例4.1难点解析第一个角度懂得 STM32 有FSMC(其实其他芯片根本都有相似的总线功效),FSMC 的利益就是你一旦设置好之后,WR(写).RD(读).DB0DB15 这些掌握线和数据线,都是FSMC 主动掌握的.打个比方,当你在程序中写到:*(volatile unsigned short int *)(0x60000000)=val;那么FSMC 就会主动履行一个写的操纵,其对应的主控芯片的WE.RD 这些脚,就会呈现出写的时序出来(即WE=0,RD=1),数据val 的值也会经由过程DB015 主动呈现出来(即FSMCD0:FSMCD15=val ).地址0x60000000 会被呈如今数据线上(即A0A25=0,地址线的对应最麻烦,要依据具体情形来.4.1.2 硬件衔接硬件平台:(STM32F103VC + EP3C5E144C8N)将图中的IS61WV512BLL 改为FPGA 对应的接口即,可按照模式ASRAM/PSRAM进行衔接那么在硬件上面,我们须要做的,仅仅是MCU 和LCD 掌握芯片的衔接关系:WEWR,均为低电平有用RDRD,均为低电平有用FSMCD015 接LCD DB015FSMC_NE1CS 接PD7衔接好之后,读写时序都邑被FSMC 主动完成.但是还有一个很症结的问题,就是RS 没有接因为在FSMC 里面,根本就没有对应RS.怎么办呢?这个时刻,有一个好办法,就是用某一根地址线来接RS.比方我们选择了A16 这根地址线来接,那么当我们要写存放器(备注:此处应为数据)的时刻,我们须要RS,也就是A16(RS 为高)置高.软件中怎么做呢?也就是将FSMC 要写的地址改成0x60010000,如下:*(volatile unsigned short int *)(0x60010000)=val;这个时刻,A16 在履行其他FSMC 的同时会被拉高,因为A0A18 要呈现出地0x60010000.0x60010000 里面的Bit17=1,就会导致A16 为1.当要读数据(备注:此处为存放器)时,地址由0x60010000 改为了0x60000000,这个时刻A16 就为0了.RS 问题:RS 为0 暗示;读写存放器;RS 为1,读写数据RAM;ST公司为用户开辟供给了完全.高效的对象和固件库,个中运用C说话编写的固件库供给了笼罩所有尺度外设的函数,运用户无需运用汇编操纵外设特点,从而进步了程序的可读性和易保护性.STM32固件库中供给的FSMC的SRAM掌握器操纵固件,重要包含1个数据构造和3个函数FSMC_NORSRAMInitStructure (挪用库函数)RCC_Configuration(); (时钟选择)NVIC_Configuration(); (中止优先级)FSMC_GPIO_Configuration(); (衔接IO 口初始化)FSMC_SRAM_Init(); (FMSC设置装备摆设)USART_Initial(); (UART1端口设置装备摆设)4.2其他人调试碰到问题点(摘录)项目中须要运用STM32和FPGA通讯,运用的是地址线和数据线,在FPGA中依据STM32的读写模式A的时序完成写入和读取.之前的PCB设计中只运用了8跟数据线和8根地址线,调试进程中没有发明什么问题,在如今的PCB中运用了8根地址线和16根数据线,数据宽度也改成了16位,刚开端是读取数据不准确,后来发明了问题,STM32在16位数据宽度下有个表里地址映射的问题,只须要把FPGA中的设定的地址乘以2在STM32中拜访就可以了,但是在写操纵的时刻会消失写当前地址的时刻把后面的地址写成0的情形,比方说我给FPGA中界说的偏移地址0x01写一个16位数据,按照地址映射,在STM32中我把地址写入0x02,.现实测试发明这个地址上的数据是对的,但是FPGA中0x02地址上的数据也变成了00.块1存储区被划分为4个NOR/PSRAM区,这四个区在内部地址上是持续分列的.但是现实上每个区共用的是统一组地址线与数据线,是以须要有表里的一个地址映射,是以在STM32中现实上有两个地址,一个是在内部拜访的地址,别的一个是现实地址线输出的地址.HADDR[27:0]对应的是须要转换到外部存储器的内部AHB地址线,其HADDR[27:26]位用于选择四个存储块之一.HADDR[25:0]包含外部存储器地址.HADDR是字节地址,而不合的外部存储器数据长度也不一样,是以在数据宽度为8位和16位时映射关系也不一样.在数据宽度为8位时HADDR[25:0]与FSMC_A[25:0]对应相连,这时刻在STM32中拜访的地址和现实地址线产生的地址是一致的.而在16位数据宽度时HADDR[25:1]与FSMC_A[24:0]对应相连,HADDR[0]未接,这时刻现实地址线上给出的地址为须要拜访的偏移地址的一半.经由一晚上的测试,发明写数据时现实上是进行了多次写入,导致把后面的地址也给写上了,最终导致数据凌乱,后来经由学长提示,决议把拜访的地址界说为16位的,本来是32位的,经由测试问题解决.所以这儿也算是长了经验,因为我只用了8根地址线,为了防止可能的问题,地址最好界说成对应的位数.但是照样很纳闷为什么之前八位数据线读写的时刻没有这个问题.5.结语STM32作为新一代ARM CortexM3核处理器,其卓著的机能和功耗掌握可以或许实用于普遍的运用范畴;而其特别的可变静态存储技巧FSMC具有高度的灵巧性,对于存储容量请求较高的嵌入式体系设计,可以或许在不增长外部分立器件的情形下,扩大多种不合类型和容量的存储芯片,下降了体系设计的庞杂性,进步了体系的靠得住性.。

STM32系列FSMC控制器分析和代码

1、FSMC初初了解:FSMC 包括4个模块:(1)AHB接口(包括FSMC配置寄存器)(2)NOR闪存和PSRAM控制器(驱动LCD的时候LCD就好像一个PSRAM的里面只有2个16位的存储空间,一个是DATA RAM 一个是CMD RAM)(3)NAND闪存和PC卡控制器(4)外部设备接口我们驱动TFT很明显用的是第二个模块:NOR闪存。

2、FSMC的外设地址选择FSMC _Bank 用来选择外接存储器的地址,FSMC所控制的外存储器所映射的地址是0x6000 0000 ~ 0x9fff ffff其中属于NOR FLASH 的是0x6000 0000 ~ 0x6fff ffff ,然后这部分的地址空间又被分为四份,每份64MB, 编号是BANK1 ~ BANK 4 ,每个BANK 都有一个片选引脚。

而这四个分存储块的片选,则使用NE[4:1]来选择。

数据线/地址线/控制线是共享的。

NE1 ->Bank1 NE2->Bank2 NE3->Bank3 NE4->Bank4第一块:6000 0000h--63ff ffffh第二块:6400 0000h--67ff ffffh第三块:6800 0000h--6bff ffffh第四块:6c00 0000h--6fff ffffh3、FSMC 驱动LCDFSMC提供了所有的LCD控制器的信号:FSMC_D[16:0]:16bit的数据总线FSMC NEx:分配给NOR的256M,再分为4个区,每个区用来分配一个外设,这四个外设的片选分为是NE1-NE4,对应的引脚为:PD7—NE1,PG9—NE2,PG10-NE3,PG12—NE4FSMC NOE:输出使能,连接LCD的RD脚。

FSMC NWE:写使能,连接LCD的RW脚。

FSMC Ax:用在LCD显示RAM和寄存器之间进行选择的地址线,即该线用于选择LCD的RS脚,该线可用地址线的任意一根线,范围:FSMC_A[25:0]。

STM32使用FSMC控制NAND flash 例程概要

本文原创于观海听涛,原作者版权所有,转载请注明出处。

近几天开发项目需要用到STM32驱动NAND FLASH,但由于开发板例程以及固件库是用于小页(512B,我要用到的FLASH为1G bit的大页(2K,多走了两天弯路。

以下笔记将说明如何将默认固件库修改为大页模式以驱动大容量NAND,并作驱动。

本文硬件:控制器:STM32F103ZET6,存储器:HY27UF081G2A首先说一下NOR与NAND存储器的区别,此类区别网上有很多,在此仅大致说明:1、Nor读取速度比NAND稍快2、Nand写入速度比Nor快很多3、NAND擦除速度(4ms远快于Nor(5s4、Nor 带有SRAM接口,有足够的地址引脚来寻址,可以很轻松的挂接到CPU 地址和数据总线上,对CPU要求低5、NAND用八个(或十六个引脚串行读取数据,数据总线地址总线复用,通常需要CPU支持驱动,且较为复杂6、Nor主要占据1-16M容量市场,并且可以片内执行,适合代码存储7、NAND占据8-128M及以上市场,通常用来作数据存储8、NAND便宜一些9、NAND寿命比Nor长10、NAND会产生坏块,需要做坏块处理和ECC更详细区别请继续百度,以上内容部分摘自神舟三号开发板手册下面是NAND的存储结构:由此图可看出NAND存储结构为立体式正如硬盘的盘片被分为磁道,每个磁道又分为若干扇区,一块nand flash也分为若干block,每个block分为如干page。

一般而言,block、page之间的关系随着芯片的不同而不同。

需要注意的是,对于flash的读写都是以一个page开始的,但是在读写之前必须进行flash 的擦写,而擦写则是以一个block为单位的。

我们这次使用的HY27UF081G2A其PDF介绍:Memory Cell Array= (2K+64 Bytes x 64 Pages x 1,024 Blocks由此可见,该NAND每页2K,共64页,1024块。

FSMC

机制

配置存储器基本特征

通过对FSMC特殊功能寄存器FSMC_BCRi(i为子BANK号,i=1,…,4)中对应控制位的设置,FSMC根据不同存 储器特征可灵活地进行工作方式和信号的调整。

结语

STM32作为新一代ARM Cortex-M3核处理器,其卓越的性能和功耗控制能够适用于广泛的应用领域;而其特 殊的可变静态存储技术FSMC具有高度的灵活性,对于存储容量要求较高的嵌入式系统设计,能够在不增加外部分 立器件的情况下,扩展多种不同类型和容量的存储芯片,降低了系统设计的复杂性,提高了系统的可靠性。

FSMC技术优势

①支持多种静态存储器类型。STM32通过FSMC可以与SRAM、ROM、PSRAM、NOR Flash和NANDFlash存储器的 引脚直接相连。

②支持丰富的存储操作方法。FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存 储器的同步突发访问方式。

内部集成256 KB以上FlaSh,后缀为xC、xD和xE的高存储密度微控制器特有的存储控制机制。之所以称为 “可变”,是由于通过对特殊功能寄存器的设置,FSMC能够根据不同的外部存储器类型,发出相应的数据//控制 信号类型以匹配信号的速度,从而使得STM32系列微控制器不仅能够应用各种不同类型、不同速度的外部静态存 储器,而且能够在不增加外部器件的情况下同时扩展多种不同类型的静态存储器,满足系统设计对存储容量、产 品体积以及成本的综合要求。

STM32 FSMC-LCD的FSMC配置

FSMC全称“静态存储器控制器”。

使用FSMC控制器后,可以把FSMC提供的FSMC_A[25:0]作为地址线,而把FSMC提供的FSMC_D[15:0]作为数据总线。

(1)当存储数据设为8位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_8b)地址各位对应FSMC_A[25:0],数据位对应FSMC_D[7:0](2)当存储数据设为16位时,(FSMC_NANDInitStructure.FSMC_MemoryDataWidth =FSMC_MemoryDataWidth_16b)地址各位对应FSMC_A[24:0],数据位对应FSMC_D[15:0] FSMC 包括4个模块:(1)AHB接口(包括FSMC配置寄存器)(2)NOR闪存和PSRAM控制器(驱动LCD的时候LCD就好像一个PSRAM的里面只有2个16位的存储空间,一个是DATA RAM 一个是CMD RAM)(3)NAND闪存和PC卡控制器(4)外部设备接口注:FSMC可以请求AHB进行数据宽度的操作。

如果AHB操作的数据宽度大于外部设备(NOR或NAND或LCD)的宽度,此时FSMC将AHB操作分割成几个连续的较小的数据宽度,以适应外部设备的数据宽度。

FSMC对外部设备的地址映像从0x6000 0000开始,到0x9FFF FFFF 结束,共分4个地址块,每个地址块256M字节。

可以看出,每个地址块又分为4个分地址块,大小64M。

对NOR的地址映像来说,我们可以通过选择HADDR[27:26]来确定当前使用的是哪个64M的分地址块,如下页表格。

而这四个分存储块的片选,则使用NE[4:1]来选择。

数据线/地址线/控制线是共享的。

NE1 ->Bank1 NE2->Bank2 NE3->Bank3 NE4->Bank4若NE1 连接,则每小块NOR/PSRAM 64M第一块:6000 0000h--63ff ffffh (DATA长度为8位情况下,由地址线FSMC_A[25:0]决定;DATA长度为16位情况下,由地址线FSMC_A[24:0]决定)第二块:6400 0000h--67ff ffffh第二块:6800 0000h--6bff ffffh第三块:6c00 0000h--6fff ffffh注:这里的HADDR是需要转换到外部设备的内部AHB地址线,每个地址对应一个字节单元。

零死角玩转stm32-高级篇4、FSMC详解(3.2寸液晶触摸画板)

0、友情提示《零死角玩转STM32》系列教程由初级篇、中级篇、高级篇、系统篇、四个部分组成,根据野火STM32开发板旧版教程升级而来,且经过重新深入编写,重新排版,更适合初学者,步步为营,从入门到精通,从裸奔到系统,让您零死角玩转STM32。

M3的世界,与野火同行,乐意惬无边。

另外,野火团队历时一年精心打造的《STM32库开发实战指南》将于今年10月份由机械工业出版社出版,该书的排版更适于纸质书本阅读以及更有利于查阅资料。

内容上会给你带来更多的惊喜。

是一本学习STM32必备的工具书。

敬请期待!4、液晶触摸画板4.1实验简介本实验向大家介绍如何使用STM32的FSMC接口驱动LCD屏,及使用触摸屏控制器检测触点坐标。

4.2 LCD控制器简介LCD,即液晶显示器,因为其功耗低、体积小,承载的信息量大,因而被广泛用于信息输出、与用户进行交互,目前仍是各种电子显示设备的主流。

因为STM32内部没有集成专用的液晶屏和触摸屏的控制接口,所以在显示面板中应自带含有这些驱动芯片的驱动电路(液晶屏和触摸屏的驱动电路是独立的),STM32芯片通过驱动芯片来控制液晶屏和触摸屏。

以野火3.2寸液晶屏(240*320)为例,它使用ILI9341芯片控制液晶屏,通过TSC2046芯片控制触摸屏。

4.2.1 ILI9341控制器结构液晶屏的控制芯片内部结构非常复杂,见错误!未找到引用源。

最主要的是位于中间GRAM(Graphics RAM),可以理解为显存。

GRAM中每个存储单元都对应着液晶面板的一个像素点。

它右侧的各种模块共同作用把GRAM存储单元的数据转化成液晶面板的控制信号,使像素点呈现特定的颜色,而像素点组合起来则成为一幅完整的图像。

框图的左上角为ILI9341的主要控制信号线和配置引脚,根据其不同状态设置可以使芯片工作在不同的模式,如每个像素点的位数是6、16还是18位;使用SPI接口还是8080接口与MCU进行通讯;使用8080接口的哪种模式。

STM32 FSMC 配置说明

STM32 FSMC 配置说明typedef struct{uint32_t FSMC_Bank;//nor 被分为四块,其中这个参数是说明对那个块编程uint32_t FSMC_DataAddressMux;//地址\数据是否复用uint32_t FSMC_MemoryType;//存储器类型uint32_t FSMC_MemoryDataWidth;//数据总线宽度8 位/16 位uint32_t FSMC_BurstAccessMode;//是否进行成组模式访问uint32_t FSMC_WaitSignalPolarity;//等待信号有效级性uint32_t FSMC_WrapMode;//该位决定控制器是否支持把非对齐的AHB 成组操作分割成2 次线性操作;该位仅在存储器的成组模式下有效。

uint32_tFSMC_WaitSignalActive;//当闪存存储器处于成组传输模式时,NWAIT 信号指示从闪存存储器出来的数据是否有效或是否需要插入等待周期。

该位决定存储器是在等待状态之前的一个时钟周期产生NWAIT 信号,还是在等待状态期间产生NWAIT 信号。

uint32_t FSMC_WriteOperation;//该位指示FSMC 是否允许/ 禁止对存储器的写操作。

uint32_t FSMC_WaitSignal;//当闪存存储器处于成组传输模式时,这一位允许/禁止通过NWAIT 信号插入等待状态。

uint32_tFSMC_ExtendedMode;//该位允许FSMC 使用FSMC_BWTR 寄存器,即允许读和写使用不同的时序。

uint32_t FSMC_WriteBurst;//对于处于成组传输模式的闪存存储器,这一位允许/禁止通过NWAIT 信号插入等待状态。

读操作的同步成组传输协议使能位是FSMC_BCRx 寄存器的BURSTEN 位。

FSMC_NORSRAMTimingInitTypeDef*FSMC_ReadWriteTimingStruct;//读时序配置指针FSMC_NORSRAMTimingInitTypeDef*FSMC_WriteTimingStruct;//写时序配置指针}FSMC_NORSRAMInitTypeDef;typedef struct{uint32_t FSMC_AddressSetupTime;//这些位定义地址的建立时间,适用于SRAM、ROM 和异步总线复用模式的NOR 闪存操作。

STM32单片机的知识点总结

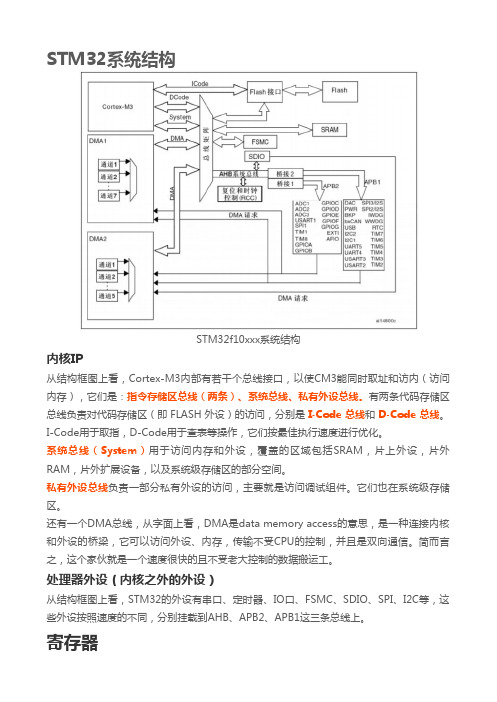

STM32系统结构STM32f10xxx系统结构内核IP从结构框图上看,Cortex-M3内部有若干个总线接口,以使CM3能同时取址和访内(访问内存),它们是:指令存储区总线(两条)、系统总线、私有外设总线。

有两条代码存储区总线负责对代码存储区(即 FLASH 外设)的访问,分别是 I-Code 总线和 D-Code 总线。

I-Code用于取指,D-Code用于查表等操作,它们按最佳执行速度进行优化。

系统总线(System)用于访问内存和外设,覆盖的区域包括SRAM,片上外设,片外RAM,片外扩展设备,以及系统级存储区的部分空间。

私有外设总线负责一部分私有外设的访问,主要就是访问调试组件。

它们也在系统级存储区。

还有一个DMA总线,从字面上看,DMA是data memory access的意思,是一种连接内核和外设的桥梁,它可以访问外设、内存,传输不受CPU的控制,并且是双向通信。

简而言之,这个家伙就是一个速度很快的且不受老大控制的数据搬运工。

处理器外设(内核之外的外设)从结构框图上看,STM32的外设有串口、定时器、IO口、FSMC、SDIO、SPI、I2C等,这些外设按照速度的不同,分别挂载到AHB、APB2、APB1这三条总线上。

寄存器什么是寄存器?寄存器是内置于各个IP外设中,是一种用于配置外设功能的存储器,并且有想对应的地址。

一切库的封装始于映射。

是不是看的眼都花了,如果进行寄存器开发,就需要怼地址以及对寄存器进行字节赋值,不仅效率低而且容易出错。

库的存在就是为了解决这类问题,将代码语义化。

语义化思想不仅仅是嵌入式有的,前端代码也在追求语义特性。

从点灯开始学习STM32内核库文件分析cor_cm3.h这个头文件实现了:1、内核结构体寄存器定义。

2、内核寄存器内存映射。

3、内存寄存器位定义。

跟处理器相关的头文件stm32f10x.h实现的功能一样,一个是针对内核的寄存器,一个是针对内核之外,即处理器的寄存器。

STM32 FSMC操作SRAM的步骤简析

STM32 FSMC操作SRAM的步骤简析本次操作的S(RAM)的型号是IS62WV51216,是高速,8M位静态SRAM。

它采用ISSI(In(te)rgrated Silicon Solu(ti)on, Inc)公司的高性能CMOS技术,按照512K个字(16)位进行组织存储单元。

其具有高性能、低功耗特点。

为方便用户扩展SRAM的存储空间,为用户有提供了两个片选引脚;此外,含有两个字节控制(信号)UB 和LB,可方便用户按字节访问SRAM或按字访问SRAM。

IS62WV51216具有45ns/55ns访问速度,因为是全静态操作,因此无需外部(时钟)和刷新要求。

IS62WV51216功能框图IS62WV51216有地址译码器、数据IO、控制逻辑和存储阵列四部分构成。

地址译码器将19根地址线上的输入进行译码,将译码值与内部存储阵列的单元地址进行建立映射。

数据IO是SRAM是主控制器数据交互的通道,访问数据时,即可字节进行访问也可按字访问,按字节访问功能增强了其与8位机的兼容性。

控制逻辑部分包括读和写的选(通信)号,以及字节访问和片选引脚。

在(硬件)连接上,SRAM与(STM32)F4通过FSMC(接口)进行互连。

SRAM的片选信号CE与FSMC的NE3连接在一起。

由此可知,SRAM被映射到Bank1的第3个存储区当中,显然,其首地址为0x68000000。

由于SRAM的数据口有16根数据线,因此为加快访问速度,提高数据吞吐量,这里仍将数据宽度设置为16位宽。

此时,FSMC接口的一个地址,映射到AHB地址时对应2个地址空间,即u16数据类型所占宽度。

但是,当用户按字节AHB地址空间时,如读取的是两个相邻字节地址空间(地址按2个字节对齐),则显然此时映射到FSMC接口时,地址是一个值,此时用户操作AHB 地址空间中低地址的字节,即相当于操作了FSMC对应地址的低字节,而当用户操作AHB地址窠中高地址字节时,则相当于操作了FSMC同一地址空间中的高字节,即FSMC地址空间可以不变,但通过SRAM 的UB和LB,分别访问了同一地址的不同字节。

STM32的FSMC理解注释

TFT 液晶和STM32的FSMC 理解注释我们下面所说的都是指TFT 液晶16位数据接口而言,而TFT 的8080时序刚刚和FSMC 的时序可以设计成一样,一定要先明白各自时序(看手册),不然会不明白为什么RS 的操作。

一.TFT 不用FSMC 时候的液晶引脚及时序:首先要明白TFT 液晶的连接线有:RD=读选择线,WR=写选择线,CS=片选,RS=写寄存器和写Sram 选择线,其中前面3条引脚线都是低电平有效,所以一般选择写的时候,RD 要拉高,WR 拉低。

选择读的时候,WR 要拉高,RD 拉低。

所以有时候用51驱动TFT 液晶的时候,只要写功能,不要读功能,就把RD 线留空,但是经过测试这样子有时候会成功驱动,有时候会驱动不了,这时候最好还是把RD 上拉就可以。

二.TFT 用STM 的FSMC 时候的液晶引脚:(时序自动不用管)只要操作TFT 的:步1. Reset :直接拉高即可(不复位不用管)步2.RD:读选择线连接FSMC_NOE (固定)=GPIO.PD4 步3.WR:写选择线连接FSMC_NWE (固定)=GPIO.PD5 步4.CS 片选以选择FSMC 的NOR 块;(选择=GPIO.PD7.PG9.PG10.PG12) 步5.RS 以选择写寄存器和写Sram 选择线(选择=如何一根FSMC 的地址线A[25:0]) 步6.DAT 【15:0】接FSMC_D 【15:0】 (固定) 所以只要关心的是步4和步5。

步4:TFT.CS 和STM32的FSMC 连接引脚选择:首先要明白FSMC 功能要看几遍数据手册的FSMC ,不然会不明白(废话!),简单的说,FSMC 操作TFT 就是在NOR 区,NOR 区的基址是0X60 00 00 00,结束地址是0X6F FF FF FF, 大小是256M ,分成4块,每块64M 。

我们可以选择任何一块就可以,怎么选择呢?根据AHB 总线的HADDR(AHB的地址线,可以先理解为一个寄存器)的第26位27位选择决定,如表1。

stm32-FSMC的作用与功能

stm32-FSMC的作⽤与功能FSMC的定义:灵活的静态存储器控制器。

FSMC的主要作⽤:1. 将AHB传输信号转换到适到的外设协议;2. 满⾜访问外部设备对时序的要求;FSMC的主要功能:●具有静态存储器接⼝的器件包括:─静态随机存储器(SRAM)─只读存储器(ROM)─ NOR闪存─ PSRAM(4个存储器块)●两个NAND闪存块,⽀持硬件ECC并可检测多达8K字节数据● 16位的PC卡兼容设备●⽀持对同步器件的成组(Burst)访问模式,如NOR闪存和PSRAM● 8或16位数据总线●每⼀个存储器块都有独⽴的⽚选控制●每⼀个存储器块都可以独⽴配置●时序可编程以⽀持各种不同的器件:─等待周期可编程(多达15个周期)─总线恢复周期可编程(多达15个周期)─输出使能和写使能延迟可编程(多达15周期)─独⽴的读写时序和协议,可⽀持宽范围的存储器和时序● PSRAM和SRAM器件使⽤的写使能和字节选择输出●将32位的AHB访问请求,转换到连续的16位或8位的,对外部16位或8位器件的访问●具有16个字,每个字32位宽的写⼊FIFO,允许在写⼊较慢存储器时释放AHB进⾏其它操作。

在开始⼀次新的FSMC操作前,FIFO要先被清空。

通常在系统复位或上电时,应该设置好所有定义外部存储器类型和特性的FSMC寄存器,并保持它们的内容不变;当然,也可以在任何时候改变这些设置FSMC结构框图:AHB接⼝:AHB接⼝为内部CPU和其它总线控制设备访问外部静态存储器提供了通道。

AHB操作被转换到外部设备的操作。

当选择的外部存储器的数据通道是16或8位时,在AHB上的32位数据会被分割成连续的16或8位的操作(具体操作规则见参考⼿册)。

AHB时钟(HCLK)是FSMC的参考时钟。

FSMC的地址映像:●存储块1⽤于访问最多4个NOR闪存或PSRAM存储设备。

这个存储区被划分为4个NOR/PSRAM区并有4个专⽤的⽚选。

●存储块2和3⽤于访问NAND闪存设备,每个存储块连接⼀个NAND闪存。

基于STM32的FSMC接口驱动TFT彩屏的设计方案

基于STM32的FSMC接口驱动TFT彩屏的设计方案一、背景介绍TFT(Thin Film Transistor)彩屏是一种薄膜晶体管彩色液晶显示屏,具有高分辨率、广视角和真实色彩等特点,广泛应用于消费电子产品和工业设备等领域。

STM32是意法半导体(STMicroelectronics)推出的一系列基于ARM Cortex-M内核的32位微控制器,具有丰富的外设和强大的计算性能。

二、设计方案1.硬件选型选择适配的TFT彩屏模块和STM32系列微控制器,确保彩屏和微控制器之间的电气和通信接口兼容。

在硬件设计中,需要注意考虑TFT彩屏的分辨率、尺寸、显示接口、电源供应和触摸屏等特性。

2.接口连接将TFT彩屏的数据总线连接到STM32微控制器的FSMC(Flexible Static Memory Controller)接口,FSMC接口支持多种外部存储器和显示器设备的数据交互,包括SRAM、NOR Flash和LCD等。

在硬件设计中,需要根据TFT彩屏的接口类型(如RGB接口、SPI接口等)选择合适的引脚进行连接,并参考STM32的技术手册或数据手册配置FSMC接口的参数。

3.驱动程序编写根据TFT彩屏的型号和厂家提供的数据手册,编写合适的驱动程序来实现对TFT彩屏的初始化、配置和数据传输等操作。

驱动程序需要调用STM32的FSMC接口相关的函数来进行数据收发,并通过设置FSMC寄存器来配置时序和控制信号。

在编写驱动程序时,可以参考STM32提供的示例代码和库函数,或者使用第三方开源的驱动程序库。

4.显示数据处理通过使用TFT彩屏的驱动程序,可以实现对图像和文本等数据的显示。

在STM32微控制器中,可以通过使用内部存储器或外部存储器来存储需要显示的数据。

在显示数据处理时,需要根据TFT彩屏的分辨率和颜色配置,将数据转化为对应的像素点或颜色值,并通过驱动程序进行传输和显示。

5.功能扩展在基于STM32的FSMC接口驱动TFT彩屏的设计中,可以进一步扩展功能,如添加触摸屏控制、图形界面设计、动画效果和多任务处理等。

FSMC讲解

#define rFSMC_BWTR4 (*(volatile unsigned *)0xA000011C) // SRAM/NOR写时序寄存器4

#define rFSMC_BTR1 (*(volatile unsigned *)0xA0000004) // SRAM/NOR片选时序寄存器1

#define rFSMC_BTR2 (*(volatile unsigned *)0xA000000C) // SRAM/NOR片选时序寄存器2

#define rFSMC_PIO4 (*(volatile unsigned *)0xA00000B0) // I/O存储空间时序寄存器4

// BANK1

#define RFSMC_BCR1 (*(volatile unsigned *)0xA0000000) // SRAM/NOR片选控制寄存器1

#define rFSMC_BCR2 (*(volatile unsigned *)0xA0000008) // SRAM/NOR片选控制寄存器2

#define rFSMC_PMEM2 (*(volatile unsigned *)0xA0000068) // 通用存储空间时序寄存器2

#define rFSMC_PATT2 (*(volatile unsigned *)0xA000006C) // 属性存储空间时序寄存器2

// BANK3

不知道ST为什么把FSMC搞的如此复杂,说白了就和ARM7或是9的几个BANK的配置一样,但是好像STM32的配置更加详细一点(不知道具体有无用处)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用STM32的FSMC控制LCD例程

void LCD_FSMCConfig(void)

{

FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;

FSMC_NORSRAMTimingInitTypeDef p;

/*-- FSMC Configuration ------------------------------------------------------*/

/*----------------------- SRAM Bank 4 ----------------------------------------*/

/* FSMC_Bank1_NORSRAM4 configuration */

p.FSMC_AddressSetupTime = 0;

p.FSMC_AddressHoldTime = 0;

p.FSMC_DataSetupTime = 2;

p.FSMC_BusTurnAroundDuration = 0;

p.FSMC_CLKDivision = 0;

p.FSMC_DataLatency = 0;

p.FSMC_AccessMode = FSMC_AccessMode_A;

/* Color LCD configuration ------------------------------------

LCD configured as follow:

- Data/Address MUX = Disable

- Memory Type = SRAM

- Data Width = 16bit

- Write Operation = Enable

- Extended Mode = Enable

- Asynchronous Wait = Disable */

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM4;

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_Mem oryDataWidth_16b;

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low; FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable; FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &p;

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &p;

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);

/* BANK 4 (of NOR/SRAM Bank 1~4) is enabled */

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM4, ENABLE);

}

* Description : This file includes the LCD driver for AM-240320L8TNQW00H

* (LCD_ILI9320) Liquid Crystal Display Module of STM3210E-EVAL

* board.

//////////////////////////////////////////////////////////////////////////////////////

/* Private typedef -----------------------------------------------------------*/

typedef struct

{

vu16 LCD_REG;

vu16 LCD_RAM;

} LCD_TypeDef;

/* LCD is connected to the FSMC_Bank1_NOR/SRAM4 and NE4 is used as ship select signal */

#define LCD_BASE ((u32)(0x60000000 | 0x0C000000))

#define LCD ((LCD_TypeDef *) LCD_BASE)

////////////////////////////////////////////////////////////////////////////////////////

void LCD_WriteReg(u8 LCD_Reg, u16 LCD_RegValue)

{

/* Write 16-bit Index, then Write Reg */

LCD->LCD_REG = LCD_Reg;

/* Write 16-bit Reg */

LCD->LCD_RAM = LCD_RegValue;

}

/////////////////////////////////////////////////////////////////////////////////////////

u16 LCD_ReadReg(u8 LCD_Reg)

{

/* Write 16-bit Index (then Read Reg) */

LCD->LCD_REG = LCD_Reg;

/* Read 16-bit Reg */

return (LCD->LCD_RAM);

}

/////////////////////////////////////////////////////////////////////////////////////////

void LCD_WriteRAM_Prepare(void)

{

LCD->LCD_REG = R34;

}

/////////////////////////////////////////////////////////////////////////////////////////

void LCD_WriteRAM(u16 RGB_Code)

{

/* Write 16-bit GRAM Reg */

LCD->LCD_RAM = RGB_Code;

}

在结构体里的定义:LCD_REG变量地址:0x6c000000;LCD_RAM变量地址:0x6c000001,STM32的FSMC的地址引脚A0接LCD_ILI9320的RS(L:访问reg;H:访问ram),通过STM32地址线A0的0,1变换,来实现访问LCD_ILI9320里的reg 和RAM. A0为0时传输的是地址,为1时,传输的数据,故这句话LCD->LCD_RAM = LCD_RegValue表示向上面传的地址里写数据。

这里的RAM不是显示用的RAM,它仅表示传输的数据。