LM3S3739-IQC50-A0T,LM3S3739-IQC50-A0,LM3S3739-IQC50, 规格书,Datasheet 资料

TI模拟器件, TI半导体, TI数字信号处理 - 德州仪器 处理器 宽带 RF IF 和数字音频广播

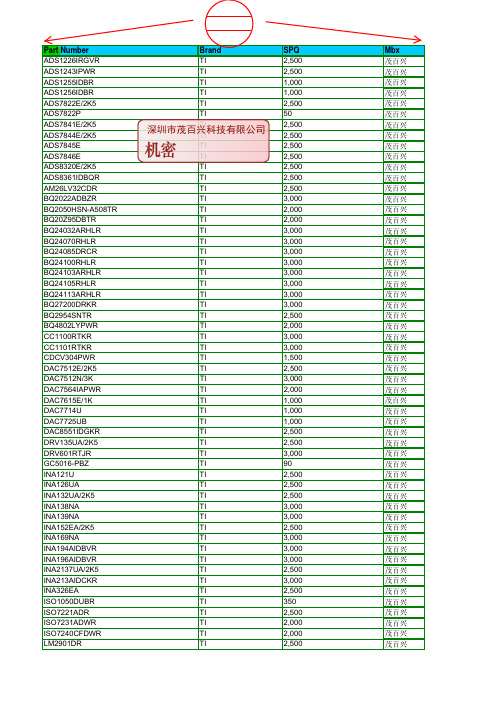

LM2903DR TI2,500茂百兴LM2903PWR TI2,000茂百兴LM3S1601-IQC50-A2T TI1,000茂百兴LM3S1607-IQR50-A0T TI1,500茂百兴LM3S1911-IQC50-A2T TI1,000茂百兴LM3S1968-IQC50-A2T TI1,000茂百兴LM3S2793-IQC80-C3T TI1,000茂百兴LM3S2965-IQC50-A2T TI1,000茂百兴LM3S3749-IQC50-A0T TI1,000茂百兴LM3S6911-IQC50-A2T TI1,000茂百兴LM3S9B90-IQC80-C3T TI1,000茂百兴LM3S9B92-IQC80-C1TI90茂百兴LM3S9B92-IQC80-C3TI90茂百兴LM4040C50IDBZR TI3,000茂百兴LM4041C12IDCKR TI3,000茂百兴LMV321IDBVR TI3,000茂百兴LMV324IPWR TI2,000茂百兴LMV331IDCKR TI3,000茂百兴LT1013DDR TI2,500茂百兴MAX3221CDBR TI2,000茂百兴MAX3221CPWR TI2,000茂百兴MAX3221IPWR TI2,000茂百兴MAX3223ECDBR TI2,000茂百兴MAX3232CDBR TI2,000茂百兴MAX3232CPWR TI2,000茂百兴MAX3232ECDBR TI2,000茂百兴MAX3232IPWR TI2,000茂百兴MAX3238EIPWR TI2,000茂百兴MAX3243CDBR TI2,000茂百兴MAX3243CPWR TI2,000茂百兴MAX3243ECDBR TI2,000茂百兴MAX3243ECPWR TI2,000茂百兴MSC1211Y5PAGR TI1,500茂百兴MSP430F1232IPWR TI2,000茂百兴MSP430F135IPMR TI1,000茂百兴MSP430F149IPMR TI1,000茂百兴MSP430F1611IPMR TI1,000茂百兴MSP430F1612IPMR TI1,000茂百兴MSP430F169IPMR TI1,000茂百兴MSP430F2001IPWR TI2,000茂百兴MSP430F2011TPWR TI2,000茂百兴MSP430F2132IPMR TI2,000茂百兴MSP430F2232IDAR TI2,000茂百兴MSP430F2252IRHAR TI2,500茂百兴MSP430F413IPMR TI1,000茂百兴MSP430F4250IRGZR TI2,500茂百兴MSP430F5418IPNR TI1,000茂百兴ONET1101LRGER TI3,000茂百兴ONET8501PRGTR TI3,000茂百兴ONET8501VRGPR TI3,000茂百兴OPA2131UA TI2,500茂百兴OPA2132UA TI2,500茂百兴OPA2134UA TI2,500茂百兴OPA2227UA TI2,500茂百兴OPA2244EA TI2,500茂百兴OPA2277UA TI2,500茂百兴OPA2335AIDR TI2,500茂百兴OPA2343EA/2K5TI2,500茂百兴OPA2348AIDCNR TI3,000茂百兴OPA2348AIDR TI3,000茂百兴OPA2349EA/3K TI3,000茂百兴OPA2350UA TI2,500茂百兴OPA2354AIDGKR TI2,500茂百兴OPA2357AIDGSR TI2,500茂百兴OPA2364AIDGKR TI2,500茂百兴OPA2364IDGKR TI2,500茂百兴OPA277AIDRMR TI3,000茂百兴OPA277U TI2,500茂百兴OPA277UA TI2,500茂百兴OPA334AIDBVR TI3,000茂百兴OPA335AIDBVR TI3,000茂百兴OPA336N TI3,000茂百兴OPA340UA/2K5TI2,500茂百兴OPA348AIDBVR TI3,000茂百兴OPA361AIDCKR TI3,000茂百兴OPA374AIDBVR TI3,000茂百兴OPA376AIDBVR TI3,000茂百兴OPA4227UA/2K5TI2,500茂百兴OPA4340UA/2k5TI2,500茂百兴OPA846IDBVR TI3,000茂百兴PCI1510PGE TI60茂百兴PCI1520ZHK TI90茂百兴PCI2040PGE TI60茂百兴PCI2050BIPDV TI36茂百兴PCI2050BIZHK TI450茂百兴PCI2050BPDV TI360茂百兴PCI2050BZHK TI450茂百兴PCI2050IBPDV TI360茂百兴PCI2250PCM TI24茂百兴PCI8402ZHK TI90茂百兴PCI8412ZHK TI90茂百兴PCM1742KE/2K TI2,000茂百兴PCM1753DBQR TI2,000茂百兴PCM1754DBQR TI2,000茂百兴PCM1755DBQR TI2,000茂百兴PCM1808PWR TI2,000茂百兴PCM4104PFBR TI2,000茂百兴PCM4204PAPR TI1,500茂百兴PTH08T220WAZT TI250茂百兴PTH08T260WAZT TI250茂百兴REF3025AIDBZR TI3,000茂百兴REF3030AIDBZR TI3,000茂百兴REF3033AIDBZR TI3,000茂百兴SN65176BDR TI2,500茂百兴SN65220DBVR TI3,000茂百兴SN65240PWR TI2,000茂百兴SN65HVD10DR TI2,500茂百兴SN65HVD11DR TI2,500茂百兴SN65HVD230DR TI2,500茂百兴SN65HVD23DR TI2,500茂百兴SN65HVD251DR TI2,500茂百兴SN65HVD3082EDR TI2,500茂百兴SN65HVD3088EDGKR TI2,500茂百兴SN65HVD33DR TI2,500茂百兴SN65LVDS2DBVR TI3,000茂百兴SN65MLVD200ADR TI2,500茂百兴SN7406DR TI2,500茂百兴SN7407DR TI2,500茂百兴SN74ABTE16246DGGR TI2,000茂百兴SN74AC14PWR TI2,000茂百兴SN74AHC14PWR TI2,000茂百兴SN74AHC1G14DBVR TI3,000茂百兴SN74AHCT08DGVR TI2,000茂百兴SN74AHCT132DR TI2,500茂百兴SN74ALVC164245DLR TI1,000茂百兴SN74ALVCH162244GR TI2,000茂百兴SN74ALVCH162373GR TI2,000茂百兴SN74AUP1G125DCKR TI3,000茂百兴SN74AVC2T45DCUR TI3,000茂百兴SN74CB3Q3257PWR TI2,000茂百兴SN74CBTLV3125PWR TI2,000茂百兴SN74HC14DR TI2,500茂百兴SN74HC164PWR TI2,000茂百兴SN74HC165DR TI2,500茂百兴SN74HC590ADR TI2,500茂百兴SN74HCT541PWR TI2,000茂百兴SN74LV07APWR TI2,000茂百兴SN74LV08APWR TI2,000茂百兴SN74LV14APWR TI2,000茂百兴SN74LV164APWR TI2,000茂百兴SN74LV244ADWR TI2,000茂百兴SN74LV244APWR TI2,000茂百兴SN74LV32APWR TI2,000茂百兴SN74LV595APWR TI2,000茂百兴SN74LV595ARGYR TI1,000茂百兴SN74LVC04ADR TI2,500茂百兴SN74LVC04APWR TI2,000茂百兴SN74LVC08APWR TI2,000茂百兴SN74LVC125APWR TI2,000茂百兴SN74LVC138APWR TI2,000茂百兴SN74LVC14ADR TI2,500茂百兴SN74LVC14APWR TI2,000茂百兴SN74LVC16244ADLR TI1,000茂百兴SN74LVC16245ADGGR TI2,000茂百兴SN74LVC16373ADGGR TI2,000茂百兴SN74LVC1G07DCKR TI3,000茂百兴SN74LVC1G125DCKR TI3,000茂百兴SN74LVC244APWR TI2,000茂百兴SN74LVC245ADGVR TI2,000茂百兴SN74LVC245APWR TI2,000茂百兴SN74LVC2G17DBVR TI3,000茂百兴SN74LVC32APWR TI2,000茂百兴SN74LVC4245APWR TI2,000茂百兴SN74LVC8T245PWR TI2,000茂百兴SN74LVCH162244AGR TI2,000茂百兴SN74LVCH16244ADGGR TI2,000茂百兴SN74LVCH16245ADLR TI1,000茂百兴SN74LVCHR16245AGR TI2,000茂百兴SN74LVTH125PWR TI2,000茂百兴SN74LVTH162244DGGR TI2,000茂百兴SN74LVTH16244ADGGR TI2,000茂百兴SN74LVTH16244ADLR TI1,000茂百兴SN74LVTH16245ADLR TI1,000茂百兴SN74LVTH244APWR TI2,000茂百兴SN75240PWR TI2,000茂百兴SN75ALS1178NSR TI2,000茂百兴SN75LBC176ADR TI2,500茂百兴TAS1020BPFBR TI1,000茂百兴TAS5707PHPR TI1,000茂百兴TFP410PAP TI160茂百兴THS7314DR TI2,500茂百兴THS7316DR TI2,500茂百兴THS7374IPWR TI2,000茂百兴THS8134BCPHP TI250茂百兴THS8200PFP TI96茂百兴TL16C2550PFBR TI1,000茂百兴TL16C550CIPTR TI1,000茂百兴TL16C550CPTR TI1,000茂百兴TL16C550CPTR TI1,000茂百兴TL16C554AFNR TI250茂百兴TL16C554AIPNR TI1,000茂百兴TL16C554APNR TI1,000茂百兴TL16C752BPTR TI1,000茂百兴TL431AIDBVR TI3,000茂百兴TL431IDBVR TI3,000茂百兴TL7705ACDR TI2,500茂百兴TL7712ACDR TI2,500茂百兴TLC1543CDWR TI2,000茂百兴TLC2252AIDR TI2,500茂百兴TLC2252CDR TI2,500茂百兴TLC2254IDR TI2,500茂百兴TLC2262CDR TI2,500茂百兴TLC2272CDR TI2,500茂百兴TLC2274ACDR TI2,500茂百兴TLC2543CDBR TI2,000茂百兴TLC2543CDWR TI2,000茂百兴TLC25M2CDR TI2,500茂百兴TLC3548IDWR TI2,000茂百兴TLC3548IPWR TI2,000茂百兴TLC3702IDR TI2,500茂百兴TLC5510INSR TI2,000茂百兴TLC555CDR TI2,500茂百兴TLC555IDR TI2,500茂百兴TLC5602CDWR TI2,000茂百兴TLC5946RHBR TI3,000茂百兴TLC7701IDR TI2,500茂百兴TLE2062ACDR TI2,500茂百兴TLE2072CDR TI2,500茂百兴TLK1501IRCPR TI1,000茂百兴TLV1543CDWR TI2,000茂百兴TLV2211IDBVR TI3,000茂百兴TLV2231IDBVR TI3,000茂百兴TLV2371IDBVR TI3,000茂百兴TLV2372IDGKR TI2,500茂百兴TLV2432AIDR TI2,500茂百兴TLV2442CDR TI2,500茂百兴TLV2462IDGKR TI2,500茂百兴TLV2556IPWR TI2,000茂百兴TLV272CDR TI2,500茂百兴TLV274CPWR TI2,000茂百兴TLV320AIC1106PWR TI2,000茂百兴TLV320AIC12IDBTR TI2,000茂百兴TLV320AIC3104IRHBR TI3,000茂百兴TLV320AIC31IRHBR TI3,000茂百兴TLV320AIC32IRHBR TI3,000茂百兴TLV320AIC33IZQER TI2,500茂百兴TLV431ACDBVR TI3,000茂百兴TMDS442PNPR TI1,000茂百兴TMP100NA TI3,000茂百兴TMP101NA TI3,000茂百兴TMP20AIDCKR TI3,000茂百兴TMP275AIDR TI2,500茂百兴TMP411ADR TI2,500茂百兴TMP75AIDGKR TI2,500茂百兴TMP75AIDR TI2,500茂百兴TMS320C32PCM50TI24茂百兴TMS320C6205ZHK200TI90茂百兴TMS320C6211BZFN167TI40茂百兴TMS320C6713BGDP225TI40茂百兴TMS320C6713BZDP225TI40茂百兴TMS320C6713BZDP300TI40茂百兴TMS320C6727BZDH300TI90茂百兴TMS320DM355ZCE216TI160茂百兴TMS320DM355ZCE270TI160茂百兴TMS320DM365ZCE27TI160茂百兴TMS320DM365ZCE30TI160茂百兴TMS320DM642AZDK6TI60茂百兴TMS320DM642AZDK7TI60茂百兴TMS320DM642AZNZ7TI40茂百兴TMS320DM6441AZWT TI90茂百兴TMS320DM6446AZWT TI90茂百兴TMS320DM6467TZUT1TI84茂百兴TMS320DM648ZUT9TI84茂百兴TMS320F28015PZA TI90茂百兴TMS320F2802PZA TI90茂百兴TMS320F2806PZA TI90茂百兴TMS320F2808PZA TI90茂百兴TMS320F2810PBKA TI90茂百兴TMS320F2811PBKA TI90茂百兴TMS320F2812GHHA TI160茂百兴TMS320F2812PGFA TI40茂百兴TMS320F28335PGFA TI40茂百兴TMS320LC549PGE-80TI60茂百兴TMS320LF2401AVFA TI250茂百兴TMS320LF2406APZA TI90茂百兴TMS320LF2407APGEA TI60茂百兴TMS320VC33PGE120TI60茂百兴TMS320VC33PGE150TI60茂百兴TMS320VC33PGEA120TI60茂百兴TMS320VC5402PGE100TI60茂百兴TMS320VC5409APGE16TI60茂百兴TMS320VC5409PGE80TI60茂百兴TMS320VC5410APGE16TI60茂百兴TMS32C6713BGDPA200TI40茂百兴TPA2005D1DRBR TI3,000茂百兴TPA2008D2PWPR TI2,000茂百兴TPA2010D1YZFR TI2,500茂百兴TPA2012D2RTJR TI3,000茂百兴TPA2013D1RGPR TI3,000茂百兴TPA3001D1PWPR TI2,000茂百兴TPA3007D1PWR TI2,000茂百兴TPA3100D2PHPR TI1,000茂百兴TPA3101D2PHPR TI1,000茂百兴TPA3110D2PWPR TI2,000茂百兴TPA3113D2PWPR TI2,000茂百兴TPA3120D2PWPR TI2,000茂百兴TPA3121D2PWPR TI2,000茂百兴TPA3123D2PWPR TI2,000茂百兴TPA3123D2PWPR TI2,000茂百兴TPA3124D2PWPR TI2,000茂百兴TPA6011A4PWPR TI2,000茂百兴TPA6110A2DGNR TI2,500茂百兴TPA6111A2DGNR TI2,500茂百兴TPA6111A2DR TI2,500茂百兴TPA6112A2DGQR TI2,500茂百兴TPA6132A2RTER TI3,000茂百兴TPA6204A1DRBR TI3,000茂百兴TPA6211A1DGNR TI2,500茂百兴TPA6211A1DRBR TI3,000茂百兴TPD12S520DBTR TI2,000茂百兴TPIC6595DWR TI2,000茂百兴TPIC6B595DWR TI2,000茂百兴TPS2034DR TI2,500茂百兴TPS2041BDBVR TI3,000茂百兴TPS2041BDR TI2,500茂百兴TPS2042BDGNR TI2,500茂百兴TPS2042BDR TI2,500茂百兴TPS2044BDR TI2,500茂百兴TPS2051BDBVR TI3,000茂百兴TPS2051BDGNR TI2,500茂百兴TPS2051BDR TI2,500茂百兴TPS2052BDR TI2,500茂百兴TPS2061DGN TI80茂百兴TPS2105DBVR TI3,000茂百兴TPS2113APWR TI2,000茂百兴TPS2115PWR TI2,000茂百兴TPS2320IPWR TI2,000茂百兴TPS2331IPWR TI2,000茂百兴TPS2350PW TI2,000茂百兴TPS23750PWPR TI2,000茂百兴TPS23753PWR TI2,000茂百兴TPS23754PWPR TI2,000茂百兴TPS2375DR TI2,500茂百兴TPS23770PWPR TI2,000茂百兴TPS2390DGKR TI2,500茂百兴TPS2391DGKR TI2,500茂百兴TPS2551DRVR TI3,000茂百兴TPS2553DBVR TI3,000茂百兴TPS2553DRVR TI3,000茂百兴TPS2812DR TI2,500茂百兴TPS2814DR TI2,500茂百兴TPS2814PWR TI2,000茂百兴TPS2829DBVR TI3,000茂百兴TPS3106E09DBVR TI3,000茂百兴TPS3106K33DBVR TI3,000茂百兴TPS3305-18DR TI2,500茂百兴TPS3307-18DR TI2,500茂百兴TPS3619-33DGKR TI2,500茂百兴TPS3620-33DGKR TI2,500茂百兴TPS3707-33DR TI2,500茂百兴TPS3801E18DCKR TI3,000茂百兴TPS3801J25DCKR TI3,000茂百兴TPS3801K33DCKR TI3,000茂百兴TPS3803-01DCKR TI3,000茂百兴TPS3808G01DBVR TI3,000茂百兴TPS3808G18DBVR TI3,000茂百兴TPS3808G33DBVR TI3,000茂百兴TPS3809K33DBVR TI3,000茂百兴TPS3820-33DBVR TI3,000茂百兴TPS3823-33DBVR TI3,000茂百兴TPS3824-33DBVR TI3,000茂百兴TPS3825-33DBVR TI3,000茂百兴TPS3828-33DBVR TI3,000茂百兴TPS3828-50DBVR TI3,000茂百兴TPS40001DGQR TI2,500茂百兴TPS40009DGQR TI2,500茂百兴TPS40021PWPR TI2,000茂百兴TPS40041DRBR TI3,000茂百兴TPS40055PWPR TI2,000茂百兴TPS40056PWPR TI2,000茂百兴TPS40057PWPR TI2,000茂百兴TPS40060PWPR TI2,000茂百兴TPS40061PWPR TI2,000茂百兴TPS40071PWPR TI2,000茂百兴TPS40077PWPR TI2,000茂百兴TPS40100RGER TI3,000茂百兴TPS40101RGER TI3,000茂百兴TPS40130DBTR TI2,000茂百兴TPS40190DRCR TI2,500茂百兴TPS40192DRCR TI3,000茂百兴TPS40200DR TI2,500茂百兴TPS40210DGQR TI2,500茂百兴TPS40222DRPR TI3,000茂百兴TPS51100DGQR TI2,500茂百兴TPS51116PWPR TI2,000茂百兴TPS51116RGER TI3,000茂百兴TPS51117RGYR TI3,000茂百兴TPS51120RHBR TI3,000茂百兴TPS51200DRCR TI3,000茂百兴TPS51218DSCR TI3,000茂百兴TPS54010PWPR TI2,000茂百兴TPS5410DR TI2,500茂百兴TPS54110PWPR TI2,000茂百兴TPS54140DGQR TI2,500茂百兴TPS54160DGQR TI2,500茂百兴TPS5420DR TI2,500茂百兴TPS54226PWPR TI2,000茂百兴TPS54231DR TI2,500茂百兴TPS54283PWPR TI2,000茂百兴TPS54286PWPR TI2,000茂百兴TPS54292PWPR TI2,000茂百兴TPS5430DDAR TI2,500茂百兴TPS54310PWPR TI2,000茂百兴TPS54314PWPR TI2,000茂百兴TPS54319RTER TI3,000茂百兴TPS54325PWPR TI2,000茂百兴TPS54331DR TI2,500茂百兴TPS54350PWPR TI2,000茂百兴TPS54357PWPR TI2,000茂百兴TPS54372PWPR TI2,000茂百兴TPS54380PWPR TI2,000茂百兴TPS54383PWPR TI2,000茂百兴TPS54386PWPR TI2,000茂百兴TPS54418RTER TI3,000茂百兴TPS5450DDAR TI2,500茂百兴TPS54550PWPR TI2,000茂百兴TPS54610PWPR TI2,000茂百兴TPS54612PWPR TI2,000茂百兴TPS54614PWPR TI2,000茂百兴TPS54616PWPR TI2,000茂百兴TPS54620RGYR TI3,000茂百兴TPS54672PWPR TI2,000茂百兴TPS54680PWPR TI2,000茂百兴TPS54910PWPR TI2,000茂百兴TPS54972PWPR TI2,000茂百兴TPS60150DRVR TI3,000茂百兴TPS60230RGTR TI3,000茂百兴TPS60231RGTR TI3,000茂百兴TPS60400DBVR TI3,000茂百兴TPS60403DBVR TI3,000茂百兴TPS60500DGSR TI2,500茂百兴TPS61020DRCR TI3,000茂百兴TPS61026DRCR TI3,000茂百兴TPS61030PWPR TI2,000茂百兴TPS61030RSAR TI2,000茂百兴TPS61032PWPR TI2,000茂百兴TPS61040DBVR TI3,000茂百兴TPS61041DBVR TI3,000茂百兴TPS61042DRBR TI3,000茂百兴TPS61045DRBR TI3,000茂百兴TPS61050YZGR TI3,000茂百兴TPS61070DDCR TI3,000茂百兴TPS61080DRCR TI3,000茂百兴TPS61081DRCR TI3,000茂百兴TPS61087DRCR TI3,000茂百兴TPS61090RSAR TI3,000茂百兴TPS61097-33DBVR TI3,000茂百兴TPS61160DRVR TI3,000茂百兴TPS61161DRVR TI3,000茂百兴TPS61165DRVR TI3,000茂百兴TPS62000DGSR TI2,500茂百兴TPS62040DGQR TI2,500茂百兴TPS62040DRCR TI3,000茂百兴TPS62046DGQR TI2,500茂百兴TPS62050DGSR TI2,500茂百兴TPS62060DSGR TI3,000茂百兴TPS62110RSAR TI3,000茂百兴TPS62111RSAR TI3,000茂百兴TPS62200DBVR TI3,000茂百兴TPS62201DBVR TI3,000茂百兴TPS62202DBVR TI3,000茂百兴TPS62203DBVR TI3,000茂百兴TPS62204DBVR TI3,000茂百兴TPS62260DDCR TI3,000茂百兴TPS62260DRVR TI3,000茂百兴TPS62290DRVR TI3,000茂百兴TPS62410DRCR TI3,000茂百兴TPS62510DRCR TI3,000茂百兴TPS62590DRVR TI3,000茂百兴TPS63000DRCR TI3,000茂百兴TPS63001DRCR TI3,000茂百兴TPS63020DSJR TI3,000茂百兴TPS63021DSJR TI3,000茂百兴TPS63030DSKR TI3,000茂百兴TPS63031DSKR TI3,000茂百兴TPS63700DRCR TI3,000茂百兴TPS64200DBVR TI3,000茂百兴TPS64202DBVR TI3,000茂百兴TPS65020RHAR TI2,500茂百兴TPS65021RHAR TI2,500茂百兴TPS65023RSBR TI3,000茂百兴TPS650243RHBR TI3,000茂百兴TPS65053RGER TI3,000茂百兴TPS65120RGTR TI3,000茂百兴TPS65150PWPR TI2,000茂百兴TPS65251RHAR TI2,500茂百兴TPS65920BZCHR TI2,000茂百兴TPS65930BZCHR TI1,000茂百兴TPS6755IDR TI2,500茂百兴TPS70102PWPR TI2,000茂百兴TPS70302PWPR TI2,000茂百兴TPS7101QDR TI2,500茂百兴TPS71501DCKR TI3,000茂百兴TPS71530DCKR TI3,000茂百兴TPS71533DCKR TI3,000茂百兴TPS71550DCKR TI3,000茂百兴TPS71701DCKR TI3,000茂百兴TPS72301DBVR TI3,000茂百兴TPS72501DCQR TI2,500茂百兴TPS72515DCQR TI2,500茂百兴TPS73018DBVR TI3,000茂百兴TPS73033DBVR TI3,000茂百兴TPS73101DBVR TI3,000茂百兴TPS73115DBVR TI3,000茂百兴TPS73130DBVR TI3,000茂百兴TPS73133DBVR TI3,000茂百兴TPS73201DBVR TI3,000茂百兴TPS73601DBVR TI3,000茂百兴TPS73601DCQR TI3,000茂百兴TPS73633DRBR TI3,000茂百兴TPS73701DCQR TI2,500茂百兴TPS73701DRBR TI3,000茂百兴TPS74401RGWR TI3,000茂百兴TPS74701DRCR TI3,000茂百兴TPS74801DRCR TI3,000茂百兴TPS75201QPWPR TI2,000茂百兴TPS76050DBVR TI3,000茂百兴TPS76301DBVR TI3,000茂百兴TPS76318DBVR TI3,000茂百兴TPS76333DBVR TI3,000茂百兴TPS76350DBVR TI3,000茂百兴TPS76633DR TI2,500茂百兴TPS76650DR TI2,500茂百兴TPS76701QPWPR TI2,000茂百兴TPS767D318PWPR TI2,000茂百兴TPS76801QDR TI2,500茂百兴TPS76933DBVR TI3,000茂百兴TPS77601PWPR TI2,000茂百兴TPS77633DR TI2,500茂百兴TPS77701PWPR TI2,000茂百兴TPS77801PWPR TI2,000茂百兴TPS78833DBVR TI3,000茂百兴TPS79101DBVR TI3,000茂百兴TPS79301DBVR TI2,500茂百兴TPS79318DBVR TI3,000茂百兴TPS793285DBVR TI3,000茂百兴TPS79328DBVR TI3,000茂百兴TPS79330DBVR TI3,000茂百兴TPS79333DBVR TI3,000茂百兴TPS79501DCQR TI2,500茂百兴TPS79533DCQR TI2,500茂百兴TPS79633DCQR TI2,500茂百兴TPS79730DCKR TI3,000茂百兴TPS79901DDCR TI3,000茂百兴TS3USB221DRCR TI3,000茂百兴TS5A3167DBVR TI3,000茂百兴TSB12LV26PZT TI90茂百兴TSB43AB22APDT TI90茂百兴TSC2003IPWR TI2,500茂百兴TSC2007IPWR TI2,000茂百兴TSC2007IYZGR TI3,000茂百兴TSC2017IYZGR TI3,000茂百兴TSC2046IPWR TI2,500茂百兴TUSB2046BIVFR TI1,000茂百兴TUSB2046BVFR TI1,000茂百兴TUSB3200ACPAHR TI1,500茂百兴TUSB3410VF TI250茂百兴TVP5150AM1PBSR TI1,000茂百兴TVP5154APNPR TI1,000茂百兴TVP5158IPNPR TI1,000茂百兴TVP5158PNPR TI1,000茂百兴UC2637DWTR TI2,000茂百兴UC2825ADWTR TI2,000茂百兴UC2842AD8TR TI2,500茂百兴UC2843AD8TR TI2,500茂百兴UC2844AD8TR TI2,500茂百兴UC3637DWTR TI2,000茂百兴UC3825ADWTR TI2,000茂百兴UC3843AD8TR TI2,500茂百兴UC3845AD8TR TI2,500茂百兴UC3845AN TI50茂百兴UC3846DWTR TI2,000茂百兴UC3846N TI25茂百兴UC3854AN TI25茂百兴UC3854BDWTR TI2,000茂百兴UC3854N TI25茂百兴UC3902DTR TI2,500茂百兴UCC27223PWPR TI2,000茂百兴UCC27324DGNR TI2,500茂百兴UCC27324DR TI2,500茂百兴UCC27423DR TI2,500茂百兴UCC27424DR TI2,500茂百兴UCC2800DTR TI2,500茂百兴UCC28060DR TI2,500茂百兴UCC28061DR TI2,500茂百兴UCC28070PWR TI2,000茂百兴UCC2808APWTR-2TI2,000茂百兴UCC2809DTR-1TI2,500茂百兴UCC2809PTR-1TI2,500茂百兴UCC2818DTR TI2,500茂百兴UCC28600DR TI2,500茂百兴UCC2891PWR TI2,000茂百兴UCC2894DR TI2,500茂百兴UCC2895DWTR TI2,000茂百兴UCC2897APWR TI2,000茂百兴UCC28C43DR TI2,500茂百兴UCC28C44DR TI2,500茂百兴UCC28C45DR TI2,500茂百兴UCC37324DGNR TI2,500茂百兴UCC3801DTR TI2,500茂百兴UCC3807DTR-3TI2,500茂百兴UCC3808DTR-2TI2,500茂百兴UCC3818PWTR TI2,000茂百兴UCC3895DWTR TI2,000茂百兴UCC3895PWTR TI2,000茂百兴UCC3919DTR TI2,500茂百兴UCC3946DTR TI2,500茂百兴ULN2003ADR TI2,500茂百兴ULN2003AIDR TI2,500茂百兴ULN2003AN TI25茂百兴XIO1100GGB TI160茂百兴XTR116UA/2K5TI2,500茂百兴。

LM3S8962产品说明

■ 带有SPI、MICROWIRE或是 TI 同步串行主从 模式的同步串行接口(SSI) ■ I2C 接口(主从) ■ 两个完全可编程的带IrDA 支持的16C550型 UARTs

模数转换器 (ADC)

■ 单分和差分输入配置 ■ 用作单端输入时,有4个10位通道(输入) ■ 每秒500000样本的采样率

GPIOs

■ 5-42 GPIOs,根据配置而定 ■ 输入/输出端口可承受5V电压 ■ 可编程的中断产生 ■ 每两个时钟周期改变一次的快速触发能力 ■ 可启动一个ADC采样序列 ■ 可编程驱动能力和转换速率控制

电源

■ 片上的低压差稳压器(LDO) ■ 带RTC和256字节的非易失性存储器的备用电 池睡眠模块 ■ 提供3.3V电源掉电检测

模拟比较器

■ 一个独立集成的模拟比较器 ■ 输出配置目的: 驱动输出引脚,产生中断或启动 一个ADC采样序列 ■ 外部引脚输入与外部引脚输入相比较或外部引 脚输入与内部可编程基准电压相比较

I2C 接口

■ 主从收发操作,标准模式下传输速率达100Kbps, 快速模式下传输速率达400 Kbps ■ 产生中断 ■ 带仲裁和时钟同步的主设备,支持多主和7位寻 址模式

订购须知

可订购的部件号

描述

LM3S8962-IQC50 LM3S8962-IQC50(T)a

Stellaris LM3S8962 微控制器 Stellarisٛ LM3S8962 微控制器

Luminary Micro 公司的 Stellaris® LM3S8962 以太 网和 CAN 评估套件提供了硬件和软件工具来提高 开发速度,这些开发使用 LM3S8962 微控制器的完 整的 CAN 和 10/100 以太网控制器。咨询 Luminary Micro 公司发行人获取部件号 EKK-LM3S8962 (ARM RealView®MDK 开发工具),

BF6910(BF6911)ASXX规格书

3.1 引脚图 ....................................................................................................................................................... 6 3.2 引脚描述 ................................................................................................................................................... 6

部分电视机CPU型号及简单代换

部分电视机CPU型号及简单代换部分电视机CPU型号及简单代换8879CPBNG6V38 海信CPU8873CPBNG6U73 创维CPUTOSHIBA-HAY-22、8873CSCNG6PR6 通用CPUTDA9373PS/N2/AI1115 SVA CPU13-TB73-TM1V001、LC863332A-5T25、LC863332A-5S97 夏华CPU88CS38N-3P48、TMP88PS38 夏华K2918、K2926,解码TB1251TDA9381PS/N3/2/1741 索尼CPUTDA9381PS/N2/3I0837 LG CPUTDA9381PS/N2/3I0975 三星CPUTDA9373PS/N2/AI0939(Haier9373-V2.0)Haier9373-V1.0 海尔CPU V1.0的可以换空白存储器,按遥控器数字8、V+ 进总线LC863324B-54M2、LC863324A-5W21、LC863324C-55M5 海信CPUOM8370-A-3NC、NOM8370-A-1NC 海信、西湖、夏华、彩星CP-2156TCL-M18V3PNICAN、TCL-M11V1P 王牌CPUH13V02-T0、8829CSNG5CJ2、H13V01-T0 TCL CPUTDA9370PS/N2/AI1429(4706-D93705-64)3P36、4P36 创维CPU 4706-D83702-64CH05T1501 长虹CHD2590M37210M3-551SP日立25M8C CPUTDA9373PS/N2/AI0911(A01V01-PH)TDA9373PS/N2/AI0996 TCL 2990UHD0401、S3F880AXZZ 创维(3S30/5S30/5S31)MN152811TJS 松下CPU 85元LC863524C-55L7、53P4、52Y7、TH-50J2 杂牌CPULC863524C-55L6、55Y5、55K8 杂牌CPU87CK38N-3647(TMP87CK38N-3675、1C48)澳柯玛、松王M37221M6-309S 厦华R2920 CPUTDA9380PS/N1/IS0380(TCL-UOC-V01)王牌CPU,用TDA9383PS代替要把60脚接地13-T00S23-03M01、8879CSBNG6K02 乐华25G6BCH08T2602(8873CSANG6JH8)长虹CPUOM8373PS/N3/2/1870(4706-D83732-64)创维短管机专用CPULC863328A-51J8 嘉华CPU8803CPAN-3PE8(8823CPNG4JR6)换存储器、39脚,C205换1UF,ST6378B1/FKF 4S02-3008 创维数码3008TMP47C434N-3526 通用王牌TCL M14VBC 王牌CPUST6367BB1/BFX 不详LC863324A-5N09 海信CPULC864512V-5C77 海信CPUM34300N4-565SPKY88C94 夏华CPUM34300N4-555SP 日立CPULC863328A-5S15 高路华、海信CPUMC8902A-5Y83 熊猫、高路华CPUMC8904A-5Z25 熊猫、高路华、海信、西湖CPUM37210M3-807SP 康力CPUT-P-16 8823CPNG5RH6 熊猫CPU SAA5647HL/M1 飞利蒲CPUOM8373PS/N3/A/1914(OM8373PS/N3/A/1854)康佳短管CPUTMP47C634AN RC18 厦华CPUHAIER1132S、HAIER1532S 海尔21T8D-S、21F9G-Shisense 8803-1(8803CPBNG3VG6)8823CPNG3PE8 海信TC2111A 换存储器、39脚,C205换1UF,OM8370PS/N3/1(HZ10V01)(TOUL 12-02M00)TCL CPUHAIER8829-V2.0(8829CPNG4PG3)海尔CPUCH0504、CH0503 长虹CPUM34302M8-612SP SONY CPUCH04T1306 长虹CPUNOM8370-A-11B 西湖CPUTCL-T00Y12-02M01(LA76931)、TOOY12-01M01 TCL CPUCKP1302S1(8829CPNG6FP6)CKP1302S 康佳CPUP88P8432N、S3C8849X13-AQB7 嘉华CPU OM8373-B-3NC 海信TF2507FLC863328C-55N6、5T45 康佳CPUTDA9373PS/N2/AI0889、4706-D93731-64 5P30 创维CPULC863328B-53P5、LC863328C-56M9、LC863328B-52E4、50J1 SVA CPUR2J10160G8-A12FP、R2J1016008-A06FP 数源S21A07 等13-TOOS13-08M01、8873CSBNG6N15 TCL CPU8873CPANG6HV9 数源TJ21A23 CPU87CM38N-1K45、87CM38N-1U87 夏华XT-259ATAVC139 三洋CPULC863320A-5N94、LC863320A-5N17(3Y01)创维CPUCH05T1604(TDA9370PS/N2/AI0848)长虹超级芯片CH05T1607(TDA9370PS/N2/AI1092)TDA9370PS 长虹超级芯片CH05T1606(TDA9373PS/N2/AI1087)TDA9373PS 长虹超级芯片CH05T1630、OM8373PS/N3/A/1842(CH05T1621)长虹,按键功能错乱,伴音失控。

低成本、高准确度和高磁性噪声抵抗位置传感器IC LX3302AQPW和LX3301AQPW说明书

Inductive Position Sensor Pro Sensor KitIntroductionThe LX3302AQPW and LX3301AQPW ICs are a low cost, high-accuracy and superior magnetic noise immune position sensor IC. The sensor system consists of the inductive position sensor ICs, its printed circuit board sensor, and the target. A target Metal is attached to the moving mechanical housing, which provides position relative to the fixed position of sensor PCB.The inductive PCBs are constructed using printed circuit board materialThe sensor assembly is connected to the USB IPCE Programmer Interface through a 4-wires cable carrying +5V, GND, IO2 (DOUT) and IO3 (AOUT). The IPCE Programmer allows programming of LX3302AQPW and LX3301AQPW internal configuration EEPROM.1. Features1.1. Pro Kit ContentsThe Evaluation Kit contains the following items:•Inductive position sensor PCB with target assembly•IPCE interface programmer•4pin to 10pin Cable between LXM9518 and Sensor PCB•USB power Cable•The IPCE Software downloaded from Microchip Technology Inductive Position Sensor Landing PageFigure 1 - LX3302A Pro Sensor Kit Example (LXK3302AL002)2. System OperationThe evaluation kit has been factory calibrated and is ready to use. The default operation requires a +5VDC power source which can be supplied either by an external DC power supply or the ICPE programmer connected to PC via USB.The Inductive Sensor kit constitutes a main sensor board and a movable target PCB. The main sensor board contains two oscillator coils (OSC1 and OSC2) and two pickup coils (CL1 and CL2). The IC energizes the two oscillator coils. The position of the target varies the reception of the two pickup coils relative to each other. The IC demodulates the two received signals and generates an output signal representative of the relative difference between the CL1 and CL2 signals as shown Fig 2.The values of the two OSC1 and OSC2 capacitors vary depending on the characteristics of the OSC1 and OSC2 printed circuit board layout pattern. The combination L/C impedance of the printed circuit board layout is matched to the LX3302AQPW’s and LX3301AWPW oscillation requirement. Refer to the LX3302AQPW and LX3301AQPW3.Figure 3 - 4pin to 10pin connectorThe following figure shows the required external system equipment and their respective connections to the LX3302A evaluation board. The sensor assembly comes with a 4pin (CN1) to 10pin (CN2) connector to connect the sensor to the IPCE Programmer. The pin4. Inductive Sensor Board Typical CharacteristicsThe following plot displays an example of linearity achievable with the sensor with a SENT output. Other output formats will have the same accuracy.Figure 4 – An Example of typical Inductive Sensor Board Linearity (Calibrated)5. Configuration EEPROMThe measurement IC contains an internal EEPROM for storing calibration and configuration parameters. The calibration parameters enable the production sensor assembly to be factory calibrated guaranteeing consistent unit-to-unit performance.6.Kit EEPROM Programming IPCEThe sensor kit includes an Integrated Programming and Calibration Environment (IPCE) to facilitate system calibration and configuration. The Integrated Programming Environment contains an EEPROM Programming tool and data measuring system.256512768102412801536179220482304256028163072332835843840409601282563845126407688961024115212801408153616641792192020482176230424322560268828162944307232003328345635843712384039684096I O 3 A m p l i t u d e A x i s M a t r i xSensor Board X Axis Displacement MatrixRotary Inductive Sensor Board LX3302 Matrix Chart6.1 IPCE Installation and startup1) After downloading software from web landing page, run the install program.2) When you are connected, dongle status will report that the port is open and itdetects the EVB3) The voltages or digital signals from each output will be displayed in the liveupdate section of the IPCE tool。

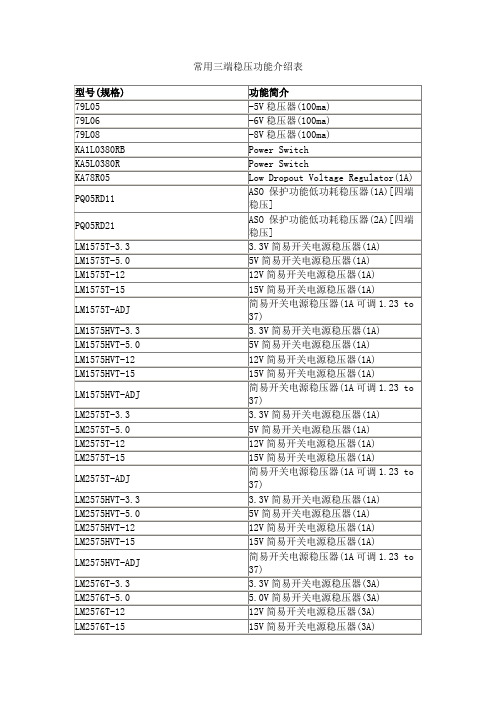

稳压管大全)

3.3V简易开关电源稳压器(1A)

LM1575T-5.0

5V简易开关电源稳压器(1A)

LM1575T-12

12V简易开关电源稳压器(1A)

LM1575T-15

15V简易开关电源稳压器(1A)

LM1575T-ADJ

简易开关电源稳压器(1A可调1.23 to 37)

LM1575HVT-3.3

LM2575HVT-ADJ

简易开关电源稳压器(1A可调1.23 to 37)

LM2576T-3.3

3.3V简易开关电源稳压器(3A)

LM2576T-5.0

5.0V简易开关电源稳压器(3A)

LM2576T-12

12V简易开关电源稳压器(3A)

LM2576T-15

15V简易开关电源稳压器(3A)

LM2576T-ADJ

79L08

-8V稳压器(100ma)

KA1L0380RB

Power Switch

KA5L0380R

Power Switch

KA78R05

Low Dropout Voltage Regulator(1A)

PQ05RD11

ASO保护功能低功耗稳压器(1A)[四端稳压]

PQ05RD21

ASO保护功能低功耗稳压器(2A)[四端稳压]

型号(规格)

功能简介

兼容型号

CA3130

高输入阻抗运算放大器

Intersil[DATA]

CA3140

高输入阻抗运算放大器

CD4573

四可编程运算放大器

MC14573

ICL7650

斩波稳零放大器

LF347(NS[DATA])

带宽四运算放大器

LM337芯片资料

LM337芯片资料一、概述LM337是一种三端稳压器,由美国国家半导体公司生产。

它是针对负电压应用而设计的,能够在输入电压在−1.5V ~−37V 的范围内提供可调的负压输出。

由于它是可调的,因此可以使用多种电压应用。

LM337是LM317的负极版本,它们具有类似的特性和应用。

与LM317一样,LM337具有低压差、可调节电压范围和过流和过热保护等特性。

二、引脚描述LM337有三个引脚,其中包括输入电源引脚(VIN)、输出电源引脚(VOUT)和调节电压引脚(ADJ)。

1. 输入电源引脚(VIN)VIN引脚是LM337的输入端。

此引脚接收负电源,其输入电压在-1.5V至-37V之间。

2. 输出电源引脚(VOUT)VOUT引脚是LM337的输出端。

此引脚输出负电源电压,其电压大小范围由整定电阻和调节电压引脚的电压设置确定。

3. 调节电压引脚(ADJ)ADJ引脚是LM337的调节电压输入端。

此引脚允许通过连接一个电阻器来设置输出的电压大小。

ADJ引脚的电压范围为-40V至0V。

三、参数规格以下是LM337的参数规格:1.输出电流: -1.5A2.输入端电压: -1.5V至 -37V3.输出电压范围: -1.3V 至 -37V4.电源抑制: 75db(最小)在10Hz5.最大工作温度: 125℃四、应用LM337可用于各种负电压应用,包括负电源电源、可调电源和稳压器。

例如,它可用于以下应用:1.-5V电源2.动态电阻器电源3.VCO电压控制器电路五、LM337的优点1.LM337与LM317具有相同的特性和应用。

2.它具有可调节的输出电压范围。

3.具有过电流和过热保护功能。

4.它适用于各种负电压应用。

六、LM337是一种高性能的三端稳压器。

它是LM317的负极版本,具有可调节的输出电压范围、过电流和过热保护功能以及用于各种负电压应用的能力。

德州仪器,LM3S9B90-I系列, 规格书,Datasheet 资料

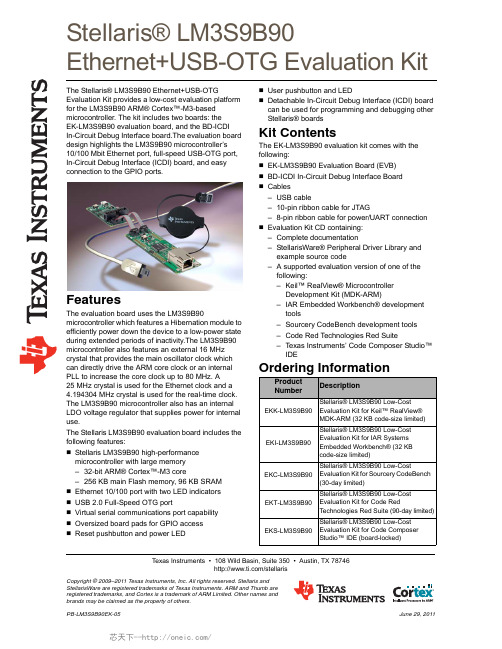

Texas Instruments •108 Wild Basin, Suite 350•Austin, TX 78746/stellarisCopyright © 2009–2011 Texas Instruments, Inc. All rights reserved. Stellaris andStellarisWare are registered trademarks of Texas Instruments. ARM and Thumb areregistered trademarks, and Cortex is a trademark of ARM Limited. Other names andbrands may be claimed as the property of others.PB-LM3S9B90EK-05June 29, 2011The Stellaris® LM3S9B90 Ethernet+USB-OTG Evaluation Kit provides a low-cost evaluation platform for the LM3S9B90 ARM® Cortex™-M3-based microcontroller. The kit includes two boards: the EK-LM3S9B90 evaluation board, and the BD-ICDI In-Circuit Debug Interface board.The evaluation board design highlights the LM3S9B90 microcontroller’s10/100 Mbit Ethernet port, full-speed USB-OTG port, In-Circuit Debug Interface (ICDI) board, and easy connection to the GPIO ports.Features The evaluation board uses the LM3S9B90 microcontroller which features a Hibernation module toefficiently power down the device to a low-power state during extended periods of inactivity.The LM3S9B90 microcontroller also features an external 16MHz crystal that provides the main oscillator clock which can directly drive the ARM core clock or an internalPLL to increase the core clock up to 80MHz. A 25MHz crystal is used for the Ethernet clock and a 4.194304MHz crystal is used for the real-time clock. The LM3S9B90 microcontroller also has an internal LDO voltage regulator that supplies power for internal use.The Stellaris LM3S9B90 evaluation board includes the following features: Stellaris LM3S9B90 high-performance microcontroller with large memory –32-bit ARM® Cortex™-M3 core –256KB main Flash memory, 96KB SRAM Ethernet 10/100 port with two LED indicators USB 2.0 Full-Speed OTG port Virtual serial communications port capability Oversized board pads for GPIO access Reset pushbutton and power LED User pushbutton and LEDDetachable In-Circuit Debug Interface (ICDI) board can be used for programming and debugging other Stellaris® boardsKit ContentsThe EK-LM3S9B90 evaluation kit comes with the following:EK-LM3S9B90 Evaluation Board (EVB)BD-ICDI In-Circuit Debug Interface BoardCables–USB cable–10-pin ribbon cable for JTAG–8-pin ribbon cable for power/UART connectionEvaluation Kit CD containing:–Complete documentation–StellarisWare® Peripheral Driver Library andexample source code– A supported evaluation version of one of thefollowing:–Keil™ RealView® MicrocontrollerDevelopment Kit (MDK-ARM)–IAR Embedded Workbench® developmenttools–Sourcery CodeBench development tools –Code Red Technologies Red Suite –Texas Instruments’ Code Composer Studio™ IDEOrdering InformationProductNumber Description EKK-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Keil™ RealView® MDK-ARM (32 KB code-size limited)EKI-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for IAR Systems Embedded Workbench® (32 KB code-size limited)EKC-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Sourcery CodeBench(30-day limited)EKT-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Code Red Technologies Red Suite (90-day limited)EKS-LM3S9B90Stellaris® LM3S9B90 Low-Cost Evaluation Kit for Code ComposerStudio™ IDE (board-locked)Stellaris®LM3S9B90Ethernet+USB-OTG Evaluation Kit 芯天下--/IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and /automotiveAutomotiveMicrocontrollers Video and Imaging /videoRFID Wireless /wireless-appsRF/IF and ZigBee®Solutions /lprfTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated芯天下--/。

集电极带电阻的三极管型号

【字数统计:2952字】一、引言三极管作为一种重要的电子器件,广泛应用于各个领域。

在三极管的分类中,集电极带电阻的三极管具有一定的特殊性。

本文将会对集电极带电阻的三极管进行深入的探讨和评估,以帮助读者全面了解其特点、应用以及未来的发展方向。

二、背景知识在我们深入讨论集电极带电阻的三极管之前,首先我们需要了解一些基础的背景知识。

1. 三极管三极管,也称为双极型晶体管,是一种半导体器件,由发射极、基极和集电极组成。

它具有放大、开关和稳压等多种功能,因此被广泛应用于放大电路、开关电路、稳压电源等各种电子设备中。

2. 集电极带电阻在传统的三极管中,集电极通常是一个无源电极。

然而,为了提高电路的性能和稳定性,人们开始尝试在集电极引入一个带电阻的电极。

这样一来,集电极不仅能够接收电流信号,还能提供一个电阻来控制电路的放大倍数。

三、集电极带电阻的三极管型号在这一部分,我们将对一些常见的集电极带电阻的三极管型号进行介绍,以便读者对其有一个初步的了解。

1. BC546BC546是一种常见的集电极带电阻的三极管型号。

它具有高电压、中电流的特点,适用于低噪声放大、混频器和开关电路等应用中。

该型号具有良好的高频特性和低噪声系数,适合用于广播接收机和电视机等高品质音频和视频信号处理电路。

2. BC547BC547是一款常用的低功耗NPN型三极管,也是集电极带电阻的三极管型号之一。

它具有高电压、低噪声、中电流的特点,广泛应用于各种放大电路、开关电路以及工业控制设备。

3. BC548BC548是另一种常用的集电极带电阻的三极管型号。

它与BC547类似,同样是一种低功耗NPN型三极管,也适用于各种电子设备的放大和开关应用中。

四、集电极带电阻三极管的特点现在我们已经对一些常见的集电极带电阻的三极管型号有了初步的了解,接下来我们将探讨集电极带电阻三极管的一些特点。

1. 高放大倍数集电极带电阻的三极管由于在集电极引入了电阻,使得其在电路中具有更高的放大倍数。

模拟器件TI半导体TI数字信号处理德州仪器处理器宽带RFIF和数字音频广播

LM2903DR TI2,500茂百兴LM2903PWR TI2,000茂百兴LM3S1601-IQC50-A2T TI1,000茂百兴LM3S1607-IQR50-A0T TI1,500茂百兴LM3S1911-IQC50-A2T TI1,000茂百兴LM3S1968-IQC50-A2T TI1,000茂百兴LM3S2793-IQC80-C3T TI1,000茂百兴LM3S2965-IQC50-A2T TI1,000茂百兴LM3S3749-IQC50-A0T TI1,000茂百兴LM3S6911-IQC50-A2T TI1,000茂百兴LM3S9B90-IQC80-C3T TI1,000茂百兴LM3S9B92-IQC80-C1TI90茂百兴LM3S9B92-IQC80-C3TI90茂百兴LM4040C50IDBZR TI3,000茂百兴LM4041C12IDCKR TI3,000茂百兴LMV321IDBVR TI3,000茂百兴LMV324IPWR TI2,000茂百兴LMV331IDCKR TI3,000茂百兴LT1013DDR TI2,500茂百兴MAX3221CDBR TI2,000茂百兴MAX3221CPWR TI2,000茂百兴MAX3221IPWR TI2,000茂百兴MAX3223ECDBR TI2,000茂百兴MAX3232CDBR TI2,000茂百兴MAX3232CPWR TI2,000茂百兴MAX3232ECDBR TI2,000茂百兴MAX3232IPWR TI2,000茂百兴MAX3238EIPWR TI2,000茂百兴MAX3243CDBR TI2,000茂百兴MAX3243CPWR TI2,000茂百兴MAX3243ECDBR TI2,000茂百兴MAX3243ECPWR TI2,000茂百兴MSC1211Y5PAGR TI1,500茂百兴MSP430F1232IPWR TI2,000茂百兴MSP430F135IPMR TI1,000茂百兴MSP430F149IPMR TI1,000茂百兴MSP430F1611IPMR TI1,000茂百兴MSP430F1612IPMR TI1,000茂百兴MSP430F169IPMR TI1,000茂百兴MSP430F2001IPWR TI2,000茂百兴MSP430F2011TPWR TI2,000茂百兴MSP430F2132IPMR TI2,000茂百兴MSP430F2232IDAR TI2,000茂百兴MSP430F2252IRHAR TI2,500茂百兴MSP430F413IPMR TI1,000茂百兴MSP430F4250IRGZR TI2,500茂百兴MSP430F5418IPNR TI1,000茂百兴ONET1101LRGER TI3,000茂百兴ONET8501PRGTR TI3,000茂百兴ONET8501VRGPR TI3,000茂百兴OPA2131UA TI2,500茂百兴OPA2132UA TI2,500茂百兴OPA2134UA TI2,500茂百兴OPA2227UA TI2,500茂百兴OPA2244EA TI2,500茂百兴OPA2277UA TI2,500茂百兴OPA2335AIDR TI2,500茂百兴OPA2343EA/2K5TI2,500茂百兴OPA2348AIDCNR TI3,000茂百兴OPA2348AIDR TI3,000茂百兴OPA2349EA/3K TI3,000茂百兴OPA2350UA TI2,500茂百兴OPA2354AIDGKR TI2,500茂百兴OPA2357AIDGSR TI2,500茂百兴OPA2364AIDGKR TI2,500茂百兴OPA2364IDGKR TI2,500茂百兴OPA277AIDRMR TI3,000茂百兴OPA277U TI2,500茂百兴OPA277UA TI2,500茂百兴OPA334AIDBVR TI3,000茂百兴OPA335AIDBVR TI3,000茂百兴OPA336N TI3,000茂百兴OPA340UA/2K5TI2,500茂百兴OPA348AIDBVR TI3,000茂百兴OPA361AIDCKR TI3,000茂百兴OPA374AIDBVR TI3,000茂百兴OPA376AIDBVR TI3,000茂百兴OPA4227UA/2K5TI2,500茂百兴OPA4340UA/2k5TI2,500茂百兴OPA846IDBVR TI3,000茂百兴PCI1510PGE TI60茂百兴PCI1520ZHK TI90茂百兴PCI2040PGE TI60茂百兴PCI2050BIPDV TI36茂百兴PCI2050BIZHK TI450茂百兴PCI2050BPDV TI360茂百兴PCI2050BZHK TI450茂百兴PCI2050IBPDV TI360茂百兴PCI2250PCM TI24茂百兴PCI8402ZHK TI90茂百兴PCI8412ZHK TI90茂百兴PCM1742KE/2K TI2,000茂百兴PCM1753DBQR TI2,000茂百兴PCM1754DBQR TI2,000茂百兴PCM1755DBQR TI2,000茂百兴PCM1808PWR TI2,000茂百兴PCM4104PFBR TI2,000茂百兴PCM4204PAPR TI1,500茂百兴PTH08T220WAZT TI250茂百兴PTH08T260WAZT TI250茂百兴REF3025AIDBZR TI3,000茂百兴REF3030AIDBZR TI3,000茂百兴REF3033AIDBZR TI3,000茂百兴SN65176BDR TI2,500茂百兴SN65220DBVR TI3,000茂百兴SN65240PWR TI2,000茂百兴SN65HVD10DR TI2,500茂百兴SN65HVD11DR TI2,500茂百兴SN65HVD230DR TI2,500茂百兴SN65HVD23DR TI2,500茂百兴SN65HVD251DR TI2,500茂百兴SN65HVD3082EDR TI2,500茂百兴SN65HVD3088EDGKR TI2,500茂百兴SN65HVD33DR TI2,500茂百兴SN65LVDS2DBVR TI3,000茂百兴SN65MLVD200ADR TI2,500茂百兴SN7406DR TI2,500茂百兴SN7407DR TI2,500茂百兴SN74ABTE16246DGGR TI2,000茂百兴SN74AC14PWR TI2,000茂百兴SN74AHC14PWR TI2,000茂百兴SN74AHC1G14DBVR TI3,000茂百兴SN74AHCT08DGVR TI2,000茂百兴SN74AHCT132DR TI2,500茂百兴SN74ALVC164245DLR TI1,000茂百兴SN74ALVCH162244GR TI2,000茂百兴SN74ALVCH162373GR TI2,000茂百兴SN74AUP1G125DCKR TI3,000茂百兴SN74AVC2T45DCUR TI3,000茂百兴SN74CB3Q3257PWR TI2,000茂百兴SN74CBTLV3125PWR TI2,000茂百兴SN74HC14DR TI2,500茂百兴SN74HC164PWR TI2,000茂百兴SN74HC165DR TI2,500茂百兴SN74HC590ADR TI2,500茂百兴SN74HCT541PWR TI2,000茂百兴SN74LV07APWR TI2,000茂百兴SN74LV08APWR TI2,000茂百兴SN74LV14APWR TI2,000茂百兴SN74LV164APWR TI2,000茂百兴SN74LV244ADWR TI2,000茂百兴SN74LV244APWR TI2,000茂百兴SN74LV32APWR TI2,000茂百兴SN74LV595APWR TI2,000茂百兴SN74LV595ARGYR TI1,000茂百兴SN74LVC04ADR TI2,500茂百兴SN74LVC04APWR TI2,000茂百兴SN74LVC08APWR TI2,000茂百兴SN74LVC125APWR TI2,000茂百兴SN74LVC138APWR TI2,000茂百兴SN74LVC14ADR TI2,500茂百兴SN74LVC14APWR TI2,000茂百兴SN74LVC16244ADLR TI1,000茂百兴SN74LVC16245ADGGR TI2,000茂百兴SN74LVC16373ADGGR TI2,000茂百兴SN74LVC1G07DCKR TI3,000茂百兴SN74LVC1G125DCKR TI3,000茂百兴SN74LVC244APWR TI2,000茂百兴SN74LVC245ADGVR TI2,000茂百兴SN74LVC245APWR TI2,000茂百兴SN74LVC2G17DBVR TI3,000茂百兴SN74LVC32APWR TI2,000茂百兴SN74LVC4245APWR TI2,000茂百兴SN74LVC8T245PWR TI2,000茂百兴SN74LVCH162244AGR TI2,000茂百兴SN74LVCH16244ADGGR TI2,000茂百兴SN74LVCH16245ADLR TI1,000茂百兴SN74LVCHR16245AGR TI2,000茂百兴SN74LVTH125PWR TI2,000茂百兴SN74LVTH162244DGGR TI2,000茂百兴SN74LVTH16244ADGGR TI2,000茂百兴SN74LVTH16244ADLR TI1,000茂百兴SN74LVTH16245ADLR TI1,000茂百兴SN74LVTH244APWR TI2,000茂百兴SN75240PWR TI2,000茂百兴SN75ALS1178NSR TI2,000茂百兴SN75LBC176ADR TI2,500茂百兴TAS1020BPFBR TI1,000茂百兴TAS5707PHPR TI1,000茂百兴TFP410PAP TI160茂百兴THS7314DR TI2,500茂百兴THS7316DR TI2,500茂百兴THS7374IPWR TI2,000茂百兴THS8134BCPHP TI250茂百兴THS8200PFP TI96茂百兴TL16C2550PFBR TI1,000茂百兴TL16C550CIPTR TI1,000茂百兴TL16C550CPTR TI1,000茂百兴TL16C550CPTR TI1,000茂百兴TL16C554AFNR TI250茂百兴TL16C554AIPNR TI1,000茂百兴TL16C554APNR TI1,000茂百兴TL16C752BPTR TI1,000茂百兴TL431AIDBVR TI3,000茂百兴TL431IDBVR TI3,000茂百兴TL7705ACDR TI2,500茂百兴TL7712ACDR TI2,500茂百兴TLC1543CDWR TI2,000茂百兴TLC2252AIDR TI2,500茂百兴TLC2252CDR TI2,500茂百兴TLC2254IDR TI2,500茂百兴TLC2262CDR TI2,500茂百兴TLC2272CDR TI2,500茂百兴TLC2274ACDR TI2,500茂百兴TLC2543CDBR TI2,000茂百兴TLC2543CDWR TI2,000茂百兴TLC25M2CDR TI2,500茂百兴TLC3548IDWR TI2,000茂百兴TLC3548IPWR TI2,000茂百兴TLC3702IDR TI2,500茂百兴TLC5510INSR TI2,000茂百兴TLC555CDR TI2,500茂百兴TLC555IDR TI2,500茂百兴TLC5602CDWR TI2,000茂百兴TLC5946RHBR TI3,000茂百兴TLC7701IDR TI2,500茂百兴TLE2062ACDR TI2,500茂百兴TLE2072CDR TI2,500茂百兴TLK1501IRCPR TI1,000茂百兴TLV1543CDWR TI2,000茂百兴TLV2211IDBVR TI3,000茂百兴TLV2231IDBVR TI3,000茂百兴TLV2371IDBVR TI3,000茂百兴TLV2372IDGKR TI2,500茂百兴TLV2432AIDR TI2,500茂百兴TLV2442CDR TI2,500茂百兴TLV2462IDGKR TI2,500茂百兴TLV2556IPWR TI2,000茂百兴TLV272CDR TI2,500茂百兴TLV274CPWR TI2,000茂百兴TLV320AIC1106PWR TI2,000茂百兴TLV320AIC12IDBTR TI2,000茂百兴TLV320AIC3104IRHBR TI3,000茂百兴TLV320AIC31IRHBR TI3,000茂百兴TLV320AIC32IRHBR TI3,000茂百兴TLV320AIC33IZQER TI2,500茂百兴TLV431ACDBVR TI3,000茂百兴TMDS442PNPR TI1,000茂百兴TMP100NA TI3,000茂百兴TMP101NA TI3,000茂百兴TMP20AIDCKR TI3,000茂百兴TMP275AIDR TI2,500茂百兴TMP411ADR TI2,500茂百兴TMP75AIDGKR TI2,500茂百兴TMP75AIDR TI2,500茂百兴TMS320C32PCM50TI24茂百兴TMS320C6205ZHK200TI90茂百兴TMS320C6211BZFN167TI40茂百兴TMS320C6713BGDP225TI40茂百兴TMS320C6713BZDP225TI40茂百兴TMS320C6713BZDP300TI40茂百兴TMS320C6727BZDH300TI90茂百兴TMS320DM355ZCE216TI160茂百兴TMS320DM355ZCE270TI160茂百兴TMS320DM365ZCE27TI160茂百兴TMS320DM365ZCE30TI160茂百兴TMS320DM642AZDK6TI60茂百兴TMS320DM642AZDK7TI60茂百兴TMS320DM642AZNZ7TI40茂百兴TMS320DM6441AZWT TI90茂百兴TMS320DM6446AZWT TI90茂百兴TMS320DM6467TZUT1TI84茂百兴TMS320DM648ZUT9TI84茂百兴TMS320F28015PZA TI90茂百兴TMS320F2802PZA TI90茂百兴TMS320F2806PZA TI90茂百兴TMS320F2808PZA TI90茂百兴TMS320F2810PBKA TI90茂百兴TMS320F2811PBKA TI90茂百兴TMS320F2812GHHA TI160茂百兴TMS320F2812PGFA TI40茂百兴TMS320F28335PGFA TI40茂百兴TMS320LC549PGE-80TI60茂百兴TMS320LF2401AVFA TI250茂百兴TMS320LF2406APZA TI90茂百兴TMS320LF2407APGEA TI60茂百兴TMS320VC33PGE120TI60茂百兴TMS320VC33PGE150TI60茂百兴TMS320VC33PGEA120TI60茂百兴TMS320VC5402PGE100TI60茂百兴TMS320VC5409APGE16TI60茂百兴TMS320VC5409PGE80TI60茂百兴TMS320VC5410APGE16TI60茂百兴TMS32C6713BGDPA200TI40茂百兴TPA2005D1DRBR TI3,000茂百兴TPA2008D2PWPR TI2,000茂百兴TPA2010D1YZFR TI2,500茂百兴TPA2012D2RTJR TI3,000茂百兴TPA2013D1RGPR TI3,000茂百兴TPA3001D1PWPR TI2,000茂百兴TPA3007D1PWR TI2,000茂百兴TPA3100D2PHPR TI1,000茂百兴TPA3101D2PHPR TI1,000茂百兴TPA3110D2PWPR TI2,000茂百兴TPA3113D2PWPR TI2,000茂百兴TPA3120D2PWPR TI2,000茂百兴TPA3121D2PWPR TI2,000茂百兴TPA3123D2PWPR TI2,000茂百兴TPA3123D2PWPR TI2,000茂百兴TPA3124D2PWPR TI2,000茂百兴TPA6011A4PWPR TI2,000茂百兴TPA6110A2DGNR TI2,500茂百兴TPA6111A2DGNR TI2,500茂百兴TPA6111A2DR TI2,500茂百兴TPA6112A2DGQR TI2,500茂百兴TPA6132A2RTER TI3,000茂百兴TPA6204A1DRBR TI3,000茂百兴TPA6211A1DGNR TI2,500茂百兴TPA6211A1DRBR TI3,000茂百兴TPD12S520DBTR TI2,000茂百兴TPIC6595DWR TI2,000茂百兴TPIC6B595DWR TI2,000茂百兴TPS2034DR TI2,500茂百兴TPS2041BDBVR TI3,000茂百兴TPS2041BDR TI2,500茂百兴TPS2042BDGNR TI2,500茂百兴TPS2042BDR TI2,500茂百兴TPS2044BDR TI2,500茂百兴TPS2051BDBVR TI3,000茂百兴TPS2051BDGNR TI2,500茂百兴TPS2051BDR TI2,500茂百兴TPS2052BDR TI2,500茂百兴TPS2061DGN TI80茂百兴TPS2105DBVR TI3,000茂百兴TPS2113APWR TI2,000茂百兴TPS2115PWR TI2,000茂百兴TPS2320IPWR TI2,000茂百兴TPS2331IPWR TI2,000茂百兴TPS2350PW TI2,000茂百兴TPS23750PWPR TI2,000茂百兴TPS23753PWR TI2,000茂百兴TPS23754PWPR TI2,000茂百兴TPS2375DR TI2,500茂百兴TPS23770PWPR TI2,000茂百兴TPS2390DGKR TI2,500茂百兴TPS2391DGKR TI2,500茂百兴TPS2551DRVR TI3,000茂百兴TPS2553DBVR TI3,000茂百兴TPS2553DRVR TI3,000茂百兴TPS2812DR TI2,500茂百兴TPS2814DR TI2,500茂百兴TPS2814PWR TI2,000茂百兴TPS2829DBVR TI3,000茂百兴TPS3106E09DBVR TI3,000茂百兴TPS3106K33DBVR TI3,000茂百兴TPS3305-18DR TI2,500茂百兴TPS3307-18DR TI2,500茂百兴TPS3619-33DGKR TI2,500茂百兴TPS3620-33DGKR TI2,500茂百兴TPS3707-33DR TI2,500茂百兴TPS3801E18DCKR TI3,000茂百兴TPS3801J25DCKR TI3,000茂百兴TPS3801K33DCKR TI3,000茂百兴TPS3803-01DCKR TI3,000茂百兴TPS3808G01DBVR TI3,000茂百兴TPS3808G18DBVR TI3,000茂百兴TPS3808G33DBVR TI3,000茂百兴TPS3809K33DBVR TI3,000茂百兴TPS3820-33DBVR TI3,000茂百兴TPS3823-33DBVR TI3,000茂百兴TPS3824-33DBVR TI3,000茂百兴TPS3825-33DBVR TI3,000茂百兴TPS3828-33DBVR TI3,000茂百兴TPS3828-50DBVR TI3,000茂百兴TPS40001DGQR TI2,500茂百兴TPS40009DGQR TI2,500茂百兴TPS40021PWPR TI2,000茂百兴TPS40041DRBR TI3,000茂百兴TPS40055PWPR TI2,000茂百兴TPS40056PWPR TI2,000茂百兴TPS40057PWPR TI2,000茂百兴TPS40060PWPR TI2,000茂百兴TPS40061PWPR TI2,000茂百兴TPS40071PWPR TI2,000茂百兴TPS40077PWPR TI2,000茂百兴TPS40100RGER TI3,000茂百兴TPS40101RGER TI3,000茂百兴TPS40130DBTR TI2,000茂百兴TPS40190DRCR TI2,500茂百兴TPS40192DRCR TI3,000茂百兴TPS40200DR TI2,500茂百兴TPS40210DGQR TI2,500茂百兴TPS40222DRPR TI3,000茂百兴TPS51100DGQR TI2,500茂百兴TPS51116PWPR TI2,000茂百兴TPS51116RGER TI3,000茂百兴TPS51117RGYR TI3,000茂百兴TPS51120RHBR TI3,000茂百兴TPS51200DRCR TI3,000茂百兴TPS51218DSCR TI3,000茂百兴TPS54010PWPR TI2,000茂百兴TPS5410DR TI2,500茂百兴TPS54110PWPR TI2,000茂百兴TPS54140DGQR TI2,500茂百兴TPS54160DGQR TI2,500茂百兴TPS5420DR TI2,500茂百兴TPS54226PWPR TI2,000茂百兴TPS54231DR TI2,500茂百兴TPS54283PWPR TI2,000茂百兴TPS54286PWPR TI2,000茂百兴TPS54292PWPR TI2,000茂百兴TPS5430DDAR TI2,500茂百兴TPS54310PWPR TI2,000茂百兴TPS54314PWPR TI2,000茂百兴TPS54319RTER TI3,000茂百兴TPS54325PWPR TI2,000茂百兴TPS54331DR TI2,500茂百兴TPS54350PWPR TI2,000茂百兴TPS54357PWPR TI2,000茂百兴TPS54372PWPR TI2,000茂百兴TPS54380PWPR TI2,000茂百兴TPS54383PWPR TI2,000茂百兴TPS54386PWPR TI2,000茂百兴TPS54418RTER TI3,000茂百兴TPS5450DDAR TI2,500茂百兴TPS54550PWPR TI2,000茂百兴TPS54610PWPR TI2,000茂百兴TPS54612PWPR TI2,000茂百兴TPS54614PWPR TI2,000茂百兴TPS54616PWPR TI2,000茂百兴TPS54620RGYR TI3,000茂百兴TPS54672PWPR TI2,000茂百兴TPS54680PWPR TI2,000茂百兴TPS54910PWPR TI2,000茂百兴TPS54972PWPR TI2,000茂百兴TPS60150DRVR TI3,000茂百兴TPS60230RGTR TI3,000茂百兴TPS60231RGTR TI3,000茂百兴TPS60400DBVR TI3,000茂百兴TPS60403DBVR TI3,000茂百兴TPS60500DGSR TI2,500茂百兴TPS61020DRCR TI3,000茂百兴TPS61026DRCR TI3,000茂百兴TPS61030PWPR TI2,000茂百兴TPS61030RSAR TI2,000茂百兴TPS61032PWPR TI2,000茂百兴TPS61040DBVR TI3,000茂百兴TPS61041DBVR TI3,000茂百兴TPS61042DRBR TI3,000茂百兴TPS61045DRBR TI3,000茂百兴TPS61050YZGR TI3,000茂百兴TPS61070DDCR TI3,000茂百兴TPS61080DRCR TI3,000茂百兴TPS61081DRCR TI3,000茂百兴TPS61087DRCR TI3,000茂百兴TPS61090RSAR TI3,000茂百兴TPS61097-33DBVR TI3,000茂百兴TPS61160DRVR TI3,000茂百兴TPS61161DRVR TI3,000茂百兴TPS61165DRVR TI3,000茂百兴TPS62000DGSR TI2,500茂百兴TPS62040DGQR TI2,500茂百兴TPS62040DRCR TI3,000茂百兴TPS62046DGQR TI2,500茂百兴TPS62050DGSR TI2,500茂百兴TPS62060DSGR TI3,000茂百兴TPS62110RSAR TI3,000茂百兴TPS62111RSAR TI3,000茂百兴TPS62200DBVR TI3,000茂百兴TPS62201DBVR TI3,000茂百兴TPS62202DBVR TI3,000茂百兴TPS62203DBVR TI3,000茂百兴TPS62204DBVR TI3,000茂百兴TPS62260DDCR TI3,000茂百兴TPS62260DRVR TI3,000茂百兴TPS62290DRVR TI3,000茂百兴TPS62410DRCR TI3,000茂百兴TPS62510DRCR TI3,000茂百兴TPS62590DRVR TI3,000茂百兴TPS63000DRCR TI3,000茂百兴TPS63001DRCR TI3,000茂百兴TPS63020DSJR TI3,000茂百兴TPS63021DSJR TI3,000茂百兴TPS63030DSKR TI3,000茂百兴TPS63031DSKR TI3,000茂百兴TPS63700DRCR TI3,000茂百兴TPS64200DBVR TI3,000茂百兴TPS64202DBVR TI3,000茂百兴TPS65020RHAR TI2,500茂百兴TPS65021RHAR TI2,500茂百兴TPS65023RSBR TI3,000茂百兴TPS650243RHBR TI3,000茂百兴TPS65053RGER TI3,000茂百兴TPS65120RGTR TI3,000茂百兴TPS65150PWPR TI2,000茂百兴TPS65251RHAR TI2,500茂百兴TPS65920BZCHR TI2,000茂百兴TPS65930BZCHR TI1,000茂百兴TPS6755IDR TI2,500茂百兴TPS70102PWPR TI2,000茂百兴TPS70302PWPR TI2,000茂百兴TPS7101QDR TI2,500茂百兴TPS71501DCKR TI3,000茂百兴TPS71530DCKR TI3,000茂百兴TPS71533DCKR TI3,000茂百兴TPS71550DCKR TI3,000茂百兴TPS71701DCKR TI3,000茂百兴TPS72301DBVR TI3,000茂百兴TPS72501DCQR TI2,500茂百兴TPS72515DCQR TI2,500茂百兴TPS73018DBVR TI3,000茂百兴TPS73033DBVR TI3,000茂百兴TPS73101DBVR TI3,000茂百兴TPS73115DBVR TI3,000茂百兴TPS73130DBVR TI3,000茂百兴TPS73133DBVR TI3,000茂百兴TPS73201DBVR TI3,000茂百兴TPS73601DBVR TI3,000茂百兴TPS73601DCQR TI3,000茂百兴TPS73633DRBR TI3,000茂百兴TPS73701DCQR TI2,500茂百兴TPS73701DRBR TI3,000茂百兴TPS74401RGWR TI3,000茂百兴TPS74701DRCR TI3,000茂百兴TPS74801DRCR TI3,000茂百兴TPS75201QPWPR TI2,000茂百兴TPS76050DBVR TI3,000茂百兴TPS76301DBVR TI3,000茂百兴TPS76318DBVR TI3,000茂百兴TPS76333DBVR TI3,000茂百兴TPS76350DBVR TI3,000茂百兴TPS76633DR TI2,500茂百兴TPS76650DR TI2,500茂百兴TPS76701QPWPR TI2,000茂百兴TPS767D318PWPR TI2,000茂百兴TPS76801QDR TI2,500茂百兴TPS76933DBVR TI3,000茂百兴TPS77601PWPR TI2,000茂百兴TPS77633DR TI2,500茂百兴TPS77701PWPR TI2,000茂百兴TPS77801PWPR TI2,000茂百兴TPS78833DBVR TI3,000茂百兴TPS79101DBVR TI3,000茂百兴TPS79301DBVR TI2,500茂百兴TPS79318DBVR TI3,000茂百兴TPS793285DBVR TI3,000茂百兴TPS79328DBVR TI3,000茂百兴TPS79330DBVR TI3,000茂百兴TPS79333DBVR TI3,000茂百兴TPS79501DCQR TI2,500茂百兴TPS79533DCQR TI2,500茂百兴TPS79633DCQR TI2,500茂百兴TPS79730DCKR TI3,000茂百兴TPS79901DDCR TI3,000茂百兴TS3USB221DRCR TI3,000茂百兴TS5A3167DBVR TI3,000茂百兴TSB12LV26PZT TI90茂百兴TSB43AB22APDT TI90茂百兴TSC2003IPWR TI2,500茂百兴TSC2007IPWR TI2,000茂百兴TSC2007IYZGR TI3,000茂百兴TSC2017IYZGR TI3,000茂百兴TSC2046IPWR TI2,500茂百兴TUSB2046BIVFR TI1,000茂百兴TUSB2046BVFR TI1,000茂百兴TUSB3200ACPAHR TI1,500茂百兴TUSB3410VF TI250茂百兴TVP5150AM1PBSR TI1,000茂百兴TVP5154APNPR TI1,000茂百兴TVP5158IPNPR TI1,000茂百兴TVP5158PNPR TI1,000茂百兴UC2637DWTR TI2,000茂百兴UC2825ADWTR TI2,000茂百兴UC2842AD8TR TI2,500茂百兴UC2843AD8TR TI2,500茂百兴UC2844AD8TR TI2,500茂百兴UC3637DWTR TI2,000茂百兴UC3825ADWTR TI2,000茂百兴UC3843AD8TR TI2,500茂百兴UC3845AD8TR TI2,500茂百兴UC3845AN TI50茂百兴UC3846DWTR TI2,000茂百兴UC3846N TI25茂百兴UC3854AN TI25茂百兴UC3854BDWTR TI2,000茂百兴UC3854N TI25茂百兴UC3902DTR TI2,500茂百兴UCC27223PWPR TI2,000茂百兴UCC27324DGNR TI2,500茂百兴UCC27324DR TI2,500茂百兴UCC27423DR TI2,500茂百兴UCC27424DR TI2,500茂百兴UCC2800DTR TI2,500茂百兴UCC28060DR TI2,500茂百兴UCC28061DR TI2,500茂百兴UCC28070PWR TI2,000茂百兴UCC2808APWTR-2TI2,000茂百兴UCC2809DTR-1TI2,500茂百兴UCC2809PTR-1TI2,500茂百兴UCC2818DTR TI2,500茂百兴UCC28600DR TI2,500茂百兴UCC2891PWR TI2,000茂百兴UCC2894DR TI2,500茂百兴UCC2895DWTR TI2,000茂百兴UCC2897APWR TI2,000茂百兴UCC28C43DR TI2,500茂百兴UCC28C44DR TI2,500茂百兴UCC28C45DR TI2,500茂百兴UCC37324DGNR TI2,500茂百兴UCC3801DTR TI2,500茂百兴UCC3807DTR-3TI2,500茂百兴UCC3808DTR-2TI2,500茂百兴UCC3818PWTR TI2,000茂百兴UCC3895DWTR TI2,000茂百兴UCC3895PWTR TI2,000茂百兴UCC3919DTR TI2,500茂百兴UCC3946DTR TI2,500茂百兴ULN2003ADR TI2,500茂百兴ULN2003AIDR TI2,500茂百兴ULN2003AN TI25茂百兴XIO1100GGB TI160茂百兴XTR116UA/2K5TI2,500茂百兴。

校验SAMSON3730-3型定位器

校验SAMSON3730-3型定位器丁玲【摘要】指导仪表工程师如何正确校验SAMSON3730-3型定位器,定位器是调节阀的主要附件,通常与气动调节阀配套使用,它接受调节器(DCS、PLC)的输出信号(4-20mA),按照预先设置关系辅助气动执行机构调整阀位并实现准确定位.阀门定位器将输入控制信号和控制阀位行程或旋转角度反馈量进行比较、处理,进而输出相应的气动控制信号给气动执行机构.【期刊名称】《数字技术与应用》【年(卷),期】2015(000)002【总页数】1页(P18)【关键词】定位器;调节阀;校验;气动控制信号【作者】丁玲【作者单位】黑龙江黑化集团有限公司黑龙江齐齐哈尔 161041【正文语种】中文【中图分类】TP207微处理确定执行机构的零位,最大行程,作用方向和执行机构的定位速度,用这些来确定最小脉冲时间和死区,从而优化控制效果。

2.1 工作准备2.1.1 工具材料准备对讲机、螺丝刀、万用表2.1.2 风险分析(1)填写安全工作许可,在工艺相关人员确认后由主控室操作人员将欲校验调节阀打到手动;风险:系统停机、管道超压、冷脆;预防措施:停机时校验、泄压操作、确认无低温液体流入碳钢管道。

(2)到现场确认要调校的调节阀;风险:误调控制阀;预防措施:和主控联系确认动作的阀与要调校的阀一致。

(3)用万用表连接至定位器读出调节阀的输入电流信号;风险:电信号短接,引起相应模块短路,烧毁该通道,使之失效;预防措施:在用万用表连接的时候,小心不要两极接触。

(4)定位器初始化;风险:系统停机、管道超压、阀门受损、冷脆;预防措施:停机时校验、泄压操作、确认阀门所需气源压力通过过滤减压阀调节、确认无低温液体流入碳钢管道。

(5)调校完毕通知主控室操作人员,将调节阀恢复至正常状态;风险:如果没有切到自动,调节阀在工况有变化时,将不会自动调节,导致工况紊乱;预防措施:通知主控室操作人员可以根据工况的变化切至自动。

德州仪器(TI)LM3S1960系列 规格书,Datasheet 资料

S T E L L A R I S E R R A T AStellaris ®LM3S1960RevA2ErrataThis document contains known errata at the time of publication for the Stellaris LM3S1960microcontroller.The table below summarizes the errata and lists the affected revisions.See the data sheet for more details.See also the ARM®Cortex™-M3errata,ARM publication number PR326-PRDC-009450v2.0.Table 1.Revision HistoryDescription Revision Date ■Added issue “Standard R-C network cannot be used on RST to extend POR timing”on page 5.■Clarified issue “General-purpose timer 16-bit Edge Count or Edge Time mode does not load reload value”on page 8to include Edge-Time mode.3.0August 2011■Added issue “Hibernation module does not operate correctly”on page 6,replacing previous Hibernation module errata items.■Minor edits and clarifications.2.10September 2010■Added issue “The RTRIS bit in the UARTRIS register is only set when the interrupt is enabled”on page 9.2.9July 2010■Added issue “External reset does not reset the XTAL to PLL Translation (PLLCFG)register”on page 5.2.8June 2010■Removed issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values"as it does not apply to this part.■Minor edits and clarifications.2.7May 2010■Removed issue "Writes to Hibernation module registers sometimes fail"as it does not apply to this part.■Added issue "Hibernation Module 4.194304-MHz oscillator supports a limited range of crystal load capacitance values."■Minor edits and clarifications.2.6April 2010■Removed issue "Setting Bit 7in I2C Master Timer Period (I2CMTPR)register may have unexpected results".The data sheet description has changed such that this is no longer necessary.■Minor edits and clarifications.2.5April 2010■Added issue “The General-Purpose Timer match register does not function correctly in 32-bit mode”on page 8.■Added issue "Setting Bit 7in I2C Master Timer Period (I2CMTPR)register may have unexpected results".2.4February 2010■"Hard Fault possible when waking from Sleep or Deep-Sleep modes and Cortex-M3Debug Access Port (DAP)is enabled"has been removed and the content added to the LM3S1960data sheet.2.3Jan 2010Started tracking revision history.2.2Dec 2009Stellaris LM3S1960A2Errata Table2.List of ErrataStellaris LM3S1960A2Errata1JTAG and Serial Wire Debug1.1JTAG pins do not have internal pull-ups enabled at power-on resetDescription:Following a power-on reset,the JTAG pins TRST,TCK,TMS,TDI,and TDO(PB7and PC[3:0])donot have internal pull-ups enabled.Consequently,if these pins are not driven from the board,twothings may happen:■The JTAG port may be held in reset and communication with a four-pin JTAG-based debugger may be intermittent or impossible.■The receivers may draw excess current.Workaround:There are a number of workarounds for this problem,varying in complexity and impact:1.Add external pull-up resistors to all of the affected pins.This workaround solves both issues ofJTAG connectivity and current consumption.2.Add an external pull-up resistor to TRST.Firmware should enable the internal pull-ups on theaffected pins by setting the appropriate PUE bits of the appropriate GPIO Pull-Up Select(GPIOPUR)registers as early in the reset handler as possible.This workaround addresses theissue of JTAG connectivity,but does not address the current consumption other than to limitthe affected period(from power-on reset to code execution).3.Pull-ups on the JTAG pins are unnecessary for code loaded via the SWD interface or via theserial boot loader.Loaded firmware should enable the internal pull-ups on the affected pins bysetting the appropriate PUE bits of the appropriate GPIOPUR registers as early in the resethandler as possible.This method does not address the current consumption other than to limitthe affected period(from power-on reset to code execution).Silicon Revision Affected:A21.2JTAG INTEST instruction does not workDescription:The JTAG INTEST(Boundary Scan)instruction does not properly capture data.Workaround:None.Silicon Revision Affected:A2Stellaris LM3S1960A2Errata2System Control2.1Clock source incorrect when waking up from Deep-Sleep mode insome configurationsDescription:In some clocking configurations,the core prematurely starts executing code before the main oscillator(MOSC)has stabilized after waking up from Deep-Sleep mode.This situation can cause undesirablebehavior for operations that are frequency dependent,such as UART communication.This issue occurs if the system is configured to run off the main oscillator,with the PLL bypassedand the DSOSCSRC field of the Deep-Sleep Clock Configuration(DSLPCLKCFG)register set touse the internal12-MHz oscillator,30-KHz internal oscillator,or32-KHz external oscillator.Whenthe system is triggered to wake up,the core should wait for the main oscillator to stabilize beforestarting to execute code.Instead,the core starts executing code while being clocked from thedeep-sleep clock source set in the DSLPCLKCFG register.When the main oscillator stabilizes,theclock to the core is properly switched to run from the main oscillator.Workaround:Run the system off of the main oscillator(MOSC)with the PLL enabled.In this mode,the clocksare switched at the proper time.If the main oscillator must be used to clock the system without the PLL,a simple wait loop at thebeginning of the interrupt handler for the wake-up event should be used to stall thefrequency-dependent operation until the main oscillator has stabilized.Silicon Revision Affected:A22.2PLL may not function properly at default LDO settingDescription:In designs that enable and use the PLL module,unstable device behavior may occur with the LDOset at its default of2.5volts or below(minimum of2.25volts).Designs that do not use the PLLmodule are not affected.Workaround:Prior to enabling the PLL module,it is recommended that the default LDO voltage setting of2.5Vbe adjusted to2.75V using the LDO Power Control(LDOPCTL)register.Silicon Revision Affected:A22.3I/O buffer5-V tolerance issueDescription:GPIO buffers are not5-V tolerant when used in open-drain mode.Pulling up the open-drain pinabove4V results in high current draw.Stellaris LM3S1960A2ErrataWorkaround:When configuring a pin as open drain,limit any pull-up resistor connections to the3.3-V power rail.Silicon Revision Affected:A22.4PLL Runs Fast When Using a3.6864-MHz CrystalDescription:If the PLL is enabled,and a3.6864-MHz crystal is used,the PLL runs4%fast.Workaround:Use a different crystal whose frequency is one of the other allowed crystal frequencies(see thevalues shown for the XTAL bit in the RCC register).Silicon Revision Affected:A22.5External reset does not reset the XTAL to PLL Translation(PLLCFG)registerDescription:Performing an external reset(anything but power-on reset)reconfigures the XTAL field in theRun-Mode Clock Configuration(RCC)register to the6MHz setting,but does not reset the XTALto PLL Translation(PLLCFG)register to the6MHz setting.Consider the following sequence:1.Performing a power-on reset results in XTAL=6MHz and PLLCFG=6MHz2.Write an8MHz value to the XTAL field results in XTAL=8MHz and PLLCFG=8MHz3.RST asserted results in XTAL=6MHz and PLLCFG=8MHzIn the last step,PLLCFG was not reset to its6MHz setting.If this step is followed by enabling thePLL to run from an attached6-MHz crystal,the PLL then operates at300MHz instead of400MHz.Subsequently configuring the XTAL field with the8MHz setting does not change the setting ofPLLCFG.Workaround:Set XTAL in PLLCFG to an incorrect value,and then to the desired value.The second changeupdates the register correctly.Do not enable the PLL until after the second change.Silicon Revision Affected:A22.6Standard R-C network cannot be used on RST to extend POR timingDescription:The standard R-C network on RST does not work to extend POR timing beyond the10ms on-chipPOR.Instead of following the standard capacitor charging curve,RST jumps straight to3V at powerStellaris LM3S1960A2Errataon.The capacitor is fully charged by current out of the RST pin and does not extend or filter thepower-on condition.As a result,the reset input is not extended beyond the POR.Workaround:Add a diode to block the output current from RST.This helps to extend the RST pulse,but alsomeans that the R-C is not as effective as a noise filter.Silicon Revision Affected:A23Hibernation Module3.1Hibernation module does not operate correctlyDescription:The Hibernation module on this microcontroller does not operate correctly.Workaround:This errata item does not apply to many Stellaris devices,including the LM3S1166,LM3S1636,LM3S1969,and LM3S2919.Refer to the Stellaris Product Selector Guide(/stellaris_search)and Errata documents to find an alternative microcontroller that meetsthe design requirements for your application.Silicon Revision Affected:A24Flash Controller4.1MERASE bit of the FMC register does not erase the entire FlasharrayDescription:The MERASE bit of the Flash Memory Control(FMC)register does not erase the entire Flash array.If the contents of the Flash Memory Address(FMA)register contain a value less than0x20000,only the first128KB of the Flash array are erased.If bit17(value of0x20000)is set,then only theupper address range of Flash(greater than128KB)is erased.Workaround:If the entire array must be erased,the following sequence is recommended:1.Write a value of0x00000000to the FMA register.2.Write a value of0xA4420004to the FMC register,and poll bit2until it is cleared.3.Write a value of0x00020000to the FMA register.4.Write a value of0xA4420004to the FMC register,and poll bit2until it is cleared.The entire array can also be erased by individually erasing all of the pages in the array.Stellaris LM3S1960A2ErrataSilicon Revision Affected:A25GPIO5.1GPIO input pin latches in the Low state if pad type is open drainDescription:GPIO pins function normally if configured as inputs and the open-drain configuration is disabled.Ifopen drain is enabled while the pin is configured as an input using the GPIO Alternate FunctionSelect(GPIOAFSEL),GPIO Open Drain Select(GPIOODR),and GPIO Direction(GPIODIR)registers,then the pin latches Low and excessive current(into pin)results if an attempt is made todrive the pin High.The open-drain device is not controllable.A GPIO pin is not normally configured as open drain and as an input at the same time.A user maywant to do this when driving a signal out of a GPIO open-drain pad while configuring the pad as aninput to read data on the same pin being driven by an external device.Bit-banging a bidirectional,open-drain bus(for example,I2C)is an example.Workaround:If a user wants to read the state of a GPIO pin on a bidirectional bus that is configured as anopen-drain output,the user must first disable the open-drain configuration and then change thedirection of the pin to an input.This precaution ensures that the pin is never configured as an inputand open drain at the same time.A second workaround is to use two GPIO pins connected to the same bus signal.The first GPIOpin is configured as an open-drain output,and the second is configured as a standard input.Thisway the open-drain output can control the state of the signal and the input pin allows the user toread the state of the signal without causing the latch-up condition.Silicon Revision Affected:A25.2GPIO pins may glitch during power supply ramp upDescription:Upon completing a POR(power on reset)sequence,the GPIO pins default to a tri-stated inputcondition.However,during the initial ramp up of the external V DD supply from0.0V to3.3V,theGPIO pins are momentarily configured as output drivers during the time the internal LDO circuit isalso ramping up.As a result,a signal glitch may occur on GPIO pins before both the external V DDsupply and internal LDO voltages reach their normal operating conditions.This situation can occurwhen the V DD and LDO voltages ramp up at significantly different rates.The LDO voltage ramp-uptime is affected by the load capacitance on the LDO pin,therefore,it is important to keep this loadat a nominal1µF value as recommended in the data sheet.Adding significant more capacitanceloading beyond the specification causes the time delay between the two supply ramp-up times togrow,which possibly increases the severity of the glitching behavior.Workaround:Ensuring that the V DD power supply ramp up is a fast as possible helps minimize the potential forGPIO glitches.Follow guidelines for LDO pin capacitive loading documented in the electrical sectionStellaris LM3S1960A2Errataof the data sheet.System designers must ensure that,during the V DD supply ramp-up time,possibleGPIO pin glitches can cause no adverse effects to their systems.Silicon Revision Affected:A26General-Purpose Timers6.1General-purpose timer Edge Count mode count error when timeris disabledDescription:When a general-purpose timer is configured for16-Bit Input Edge Count Mode,the timer(A or B)erroneously decrements by one when the Timer Enable(TnEN)bit in the GPTM Control(GPTMCTL)register is cleared(the timer is disabled).Workaround:When the general-purpose timer is configured for Edge Count mode and software needs to“stop”the timer,the timer should be reloaded with the current count+1and restarted.Silicon Revision Affected:A26.2General-purpose timer16-bit Edge Count or Edge Time mode doesnot load reload valueDescription:In Edge Count or Edge Time mode,the input events on the CCP pin decrement the counter until thecount matches what is in the GPTM Timern Match(GPTMTnMATCHR)register.At that point,aninterrupt is asserted and then the counter should be reloaded with the original value and countingbegins again.However,the reload value is not reloaded into the timer.Workaround:Rewrite the GPTM Timern Interval Load(GPTMTnILR)register before restarting.Silicon Revision Affected:A26.3The General-Purpose Timer match register does not functioncorrectly in32-bit modeDescription:The GPTM Timer A Match(GPTMTAMATCHR)register triggers a match interrupt when the lower16bits match,regardless of the value of the upper16bits.Workaround:None.Stellaris LM3S1960A2ErrataSilicon Revision Affected:A27UART7.1The RTRIS bit in the UARTRIS register is only set when the interruptis enabledDescription:The RTRIS(UART Receive Time-Out Raw Interrupt Status)bit in the UART Raw Interrupt Status(UARTRIS)register should be set when a receive time-out occurs,regardless of the state of theenable RTIM bit in the UART Interrupt Mask(UARTIM)register.However,currently the RTIM bitmust be set in order for the RTRIS bit to be set when a receive time-out occurs.Workaround:For applications that require polled operation,the RTIM bit can be set while the UART interrupt isdisabled in the NVIC using the IntDisable(n)function in the StellarisWare Peripheral Driver Library,where n is21,22,or49depending whether UART0,UART1or UART2is used.With thisconfiguration,software can poll the RTRIS bit,but the interrupt is not reported to the NVIC.Silicon Revision Affected:A28PWM8.1PWM pulses cannot be smaller than dead-band timeDescription:The dead-band generator in the PWM module has undesirable effects when receiving input pulsesfrom the PWM generator that are shorter than the dead-band time.For example,providing a4-clock-wide pulse into the dead-band generator with dead-band times of20clocks(for both risingand falling edges)produces a signal on the primary(non-inverted)output that is High except for40clocks(the combined rising and falling dead-band times),and the secondary(inverted)output isalways Low.Workaround:User software must ensure that the input pulse width to the dead-band generator is greater thanthe dead-band delays.Silicon Revision Affected:A28.2PWM interrupt clear misses in some instancesDescription:It is not possible to clear a PWM generator interrupt in the same cycle when another interrupt fromthe same PWM generator is being asserted.PWM generator interrupts are cleared by writing a1to the corresponding bit in the PWM Interrupt Status and Clear(PWMnISC)register.If a write toclear the interrupt is missed because another interrupt in that PWM generator is being asserted,Stellaris LM3S1960A2Erratathe interrupt condition still exists,and the PWM interrupt routine is called again.System problemscould result if an interrupt condition was already properly handled the first time,and the softwaretries to handle it again.Note that even if an interrupt event has not been enabled in the PWMInterrupt and Trigger Enable(PWMnINTEN)register,the interrupt is still asserted in the PWMRaw Interrupt Status(PWMnRIS)register.Workaround:In most instances,performing a double-write to clear the interrupt greatly decreases the chancethat the write to clear the interrupt occurs on the same cycle as another interrupt.Because eachgenerator has six possible interrupt events,writing the PWMnISC register six times in a rowguarantees that the interrupt is cleared.If the period of the PWM is small enough,however,thismethod may not be practical for the application.Silicon Revision Affected:A28.3PWM generation is incorrect with extreme duty cyclesDescription:If a PWM generator is configured for Count-Up/Down mode,and the PWM Load(PWMnLOAD)register is set to a value N,setting the compare to a value of1or N-1results in steady state signalsinstead of a PWM signal.For example,if the user configures PWM0as follows:■PWMENABLE=0x00000001–PWM0Enabled■PWM0CTL=0x00000007–Debug mode enabled–Count-Up/Down mode–Generator enabled■PWM0LOAD=0x00000063–Load is99(decimal),so in Count-Up/Down mode the counter counts from zero to99and back down to zero(200clocks per period)■PWM0GENA=0x000000b0–Output High when the counter matches comparator A while counting up–Output Low when the counter matches comparator A while counting down■PWM0DBCTL=0x00000000–Dead-band generator is disabledIf the PWM0Compare A(PWM0CMPA)value is set to0x00000062(N-1),PWM0should output a2-clock-cycle long High pulse.Instead,the PWM0output is a constant High value.If the PWM0CMPA value is set to0x00000001,PWM0should output a2-clock-cycle long negative(Low)pulse.Instead,the PWM0output is a constant Low value.Stellaris LM3S1960A2ErrataWorkaround:User software must ensure that when using the PWM Count-Up/Down mode,the compare valuesmust never be1or the PWMnLOAD value minus one(N-1).Silicon Revision Affected:A28.4PWMINTEN register bit does not function correctlyDescription:In the PWM Interrupt Enable(PWMINTEN)register,the IntPWM0(bit0)bit does not functioncorrectly and has no effect on the interrupt status to the ARM Cortex-M3processor.This bit shouldnot be used.Workaround:PWM interrupts to the processor should be controlled with the use of the PWM0-PWM2Interruptand Trigger Enable(PWMnINTEN)registers.Silicon Revision Affected:A28.5Sync of PWM does not trigger"zero"actionDescription:If the PWM Generator Control(PWM0GENA)register has the ActZero field set to0x2,then theoutput is set to0when the counter reaches0,as expected.However,if the counter is cleared bysetting the appropriate bit in the PWM Time Base Sync(PWMSYNC)register,then the"zero"actionis not triggered,and the output is not set to0.Workaround:None.Silicon Revision Affected:A28.6PWM"zero"action occurs when the PWM module is disabledDescription:The zero pulse may be asserted when the PWM module is disabled.Workaround:None.Silicon Revision Affected:A2August04,2011/Rev.3.011Texas Instruments9QEI 9.1QEI index resets position when index is disabledDescription:When the QEI module is configured to not reset the position on detection of the index signal (thatis,the ResMode bit in the QEI Control (QEICTL)register is 0),the module resets the position whenthe index pulse occurs.The position counter should only be reset when it reaches the maximumvalue set in the QEI Maximum Position (QEIMAXPOS)register.Workaround:Do not rely on software to disable the index pulse.Do not connect the index pulse if it is not needed.Silicon Revision Affected:A29.2QEI hardware position can be wrong under certain conditionsDescription:The QEI Position (QEIPOS)register can be incorrect if the QEI is configured for quadrature phasemode (SigMode bit in QEICTL register =0)and to update the position counter of every edge ofboth PhA and PhB (CapMode bit in QEICTL register =1).This error can occur if the encoder isstepped in the reverse direction,stepped forward once,and then continues in the reverse direction.The following sequence of transitions on the PhA and PhB pins causes the error:PhBAssuming the starting position prior to the above PhA and PhB sequence is 0,the position after thefalling edge on PhB should be -3,however the QEIPOS register will show the position to be -1.Workaround:Configure the QEI to update the position counter on every edge on PhA only (CapMode bit in QEICTLregister =0).The effective resolution is reduced by 50%.If full resolution position detection is requiredby updating the position counter on every edge of both PhA and PhB ,no workaround is available.Hardware and software must take this into account.Silicon Revision Affected:A2August 04,2011/Rev.3.0Texas Instruments12Stellaris LM3S1960A2ErrataCopyright©2007-2011Texas Instruments Incorporated All rights reserved.Stellaris and StellarisWare are registered trademarks of Texas Instruments Incorporated.ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited.Other names and brands may be claimed as the property of others.Texas Instruments Incorporated108Wild Basin,Suite350Austin,TX78746/stellaris/sc/technical-support/product-information-centers.htmAugust04,2011/Rev.3.0Texas Instruments13IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connctivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

lmv7239 高速单电源电压比较器

LMV7235/LMV7239/ LMV7239Q

5-Pin SC70/SOT23

Top View

10135903

Ordering Information

Package 5-pin SC70 5-pin SOT23

Part Number LMV7235M7 LMV7235M7X LMV7239M7 LMV7239M7X LMV7239QM7 LMV7239QM7X LMV7235M5 LMV7235M5X LMV7239M5 LMV7239M5X

The LMV7235/LMV7239/LMV7239Q have a greater than railto-rail common mode voltage range. The input common mode voltage range extends 200mV below ground and 200mV above supply, allowing both ground and supply sensing.

Symbol

Parameter

Conditions

Min (Note 6)

Typ (Note 5)

Max (Note 6)

Units

VOS

Input Offset Voltage

0.8

6

mV

8

IB

Input Bias Current

30

AD9273BSVZ-50;AD9273BSVZ-25;AD9273BBCZ-25;AD9273BSVZ-40;AD9273BBCZ-40;中文规格书,Datasheet资料

/

CLK+ CLK–

AD9273 TABLE OF CONTENTS

Features .............................................................................................. 1 Applications ....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 Product Highlights ........................................................................... 3 Specifications..................................................................................... 4 AC Specifications.......................................................................... 4 Digital Specifications ................................................................... 8 Switching Specifications .............................................................. 9 ADC Timing Diagrams ................................................................. 10 Absolute Maximum Ratings.......................................................... 11 Thermal Impedance ................................................................... 11 ESD Caution ................................................................................ 11 Pin Configuration and Function Descriptions ........................... 12 Typical Performance Characteristics ........................................... 15 Equivalent Circuits ......................................................................... 19 Theory of Operation ...................................................................... 21 Ultrasound .................................................................................. 21 Channel Overview ..................................................................... 22 Input Overdrive .......................................................................... 25 CW Doppler Operation............................................................. 25 TGC Operation ........................................................................... 27 ADC ............................................................................................. 31 Clock Input Considerations ...................................................... 31 Serial Port Interface (SPI) .............................................................. 38 Hardware Interface..................................................................... 38 Memory Map .................................................................................. 40 Reading the Memory Map Table .............................................. 40 Reserved Locations .................................................................... 40 Default Values ............................................................................. 40 Logic Levels ................................................................................. 40 Outline Dimensions ....................................................................... 44 Ordering Guide .......................................................................... 45

LM3S2919-IQC50-A2T,LM3S2919-IQC50-A2, 规格书,Datasheet 资料