如何使用debussy与modelsim做co-simulation(soc)(verilog)(vhdl)(debussy)(modelsim)

基于modelsim和debussy的批处理仿真

基于modelsim和debussy的批处理仿真本文将会叙述采用批处理的方法进行modelsim结合debussy仿真调试。

目的在于提高仿真效率。

该流程只适用于FPGA的前仿真,使用verilog文件以及测试文件。

如此操作有以下几个优点:1、虽然开始的时候需要稍作准备,但等你完成了一次仿真后,以后只需要略微修改一下就可以直接应用到其他工程里边去。

相对于采用用modelsim的界面操作,省去了很多例如创建工程、添加仿真文件、进行编译、进行仿真等等节省了宝贵的工作时间。

当然可以提高工作效率。

2、文件管理非常清楚。

所有的verilog文件都放在一个文件夹,所有仿真需要的文件以及仿真结果都放在另外一个文件里边,而且仿真后的文件也相对于使用modelsim界面操作仿真结果要少。

3、还有就是,因为没有界面操作,仿真速度会快很多,特别是采用modelsim进行稍微大的仿真的时候,这时候采用这种方法的优势就更加明显了。

以下是进行仿真前的准备工作第一步:安装modelsim、debussy软件以及编译相应的仿真库,如何安装以及破解,网络上有很多的资料说明,在这里就不详细说了。

对于仿真库的编译,也有很多的方法,可以参考文章《modelsim添加仿真库方法》by Craftor。

许多工程师也在自己的博客写过或转载过相似的库编译的方法。

这些都是我进行批处理仿真前已经做好了。

我的软件都是装在D盘分别是:D:\modeltech_6.5e和D:\Novas\Debussy第二步:创建do文件。

如下(行号不需要):1、vlib work2、vlog-f vfile.f-incr3、vsim-L xilinxcorelib_ver-L unisims_ver-L simprims_ver-L uni9000_ver-L unisims_ver-pli novas_fli.dll-lib work tuner_iic_tb4、run40ms5、exit然后保存为sim.do解析:1表示创建仿真工作库,也就是将你编译文件之后的文件存在这个work文件夹下。

Modelsim的仿真教程

ModelSim的仿真1.仿真的分类仿真过程是正确实现设计的关键环节,用来验证设计者的设计思想是否正确,及在设计实现过程中各种分布参数引入后,其设计的功能是否依然正确无误。

仿真主要分为功能仿真和时序仿真。

功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。

1). 功能仿真( 前仿真)功能仿真是指在一个设计中,在设计实现前对所创建的逻辑进行的验证其功能是否正确的过程。

布局布线以前的仿真都称作功能仿真,它包括综合前仿真(Pre-Synthesis Simulation )和综合后仿真(Post-Synthesis Simulation )。

综合前仿真主要针对基于原理框图的设计; 综合后仿真既适合原理图设计, 也适合基于HDL 语言的设计。

2). 时序仿真(后仿真)时序仿真使用布局布线后器件给出的模块和连线的延时信息,在最坏的情况下对电路的行为作出实际地估价。

时序仿真使用的仿真器和功能仿真使用的仿真器是相同的,所需的流程和激励也是相同的;惟一的差别是为时序仿真加载到仿真器的设计包括基于实际布局布线设计的最坏情况的布局布线延时,并且在仿真结果波形图中,时序仿真后的信号加载了时延,而功能仿真没有。

后仿真也称为时序仿真或者布局布线后仿真,是指电路已经映射到特定的工艺环境以后,综合考虑电路的路径延迟与门延迟的影响,验证电路能否在一定时序条件下满足设计构想的过程,是否存在时序违规。

其输入文件为从布局布线结果中抽象出来的门级网表、Testbench 和扩展名为SDO 或SDF 的标准时延文件。

SDO 或SDF 的标准时延文件不仅包含门延迟,还包括实际布线延迟,能较好地反映芯片的实际工作情况。

一般来说后仿真是必选的,检查设计时序与实际的FPGA运行情况是否一致,确保设计的可靠性和稳定性。

2.仿真的作用1).设计出能工作的电路:因此功能仿真不是一个孤立的过程,其和综合、时序分析等形成一个反馈工作过程,只有这个过程收敛,各个环节才有意义。

Modelsim Simulation操作技巧

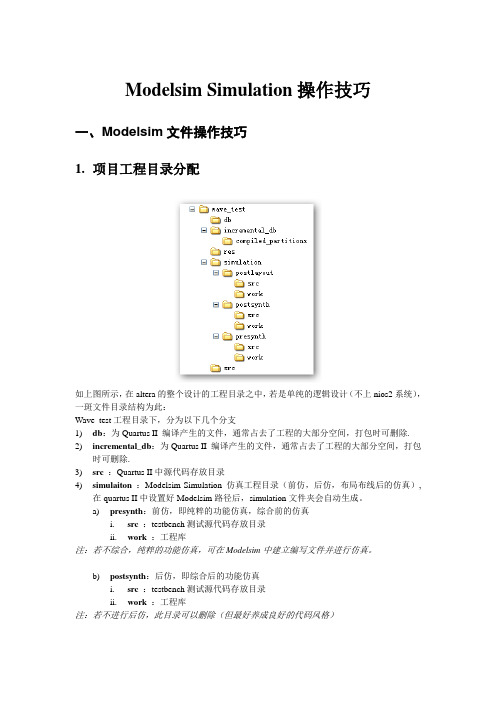

Modelsim Simulation操作技巧一、Modelsim文件操作技巧1.项目工程目录分配如上图所示,在altera的整个设计的工程目录之中,若是单纯的逻辑设计(不上nios2系统),一斑文件目录结构为此:Wave_test工程目录下,分为以下几个分支1)db:为Quartus II 编译产生的文件,通常占去了工程的大部分空间,打包时可删除.2)incremental_db:为Quartus II 编译产生的文件,通常占去了工程的大部分空间,打包时可删除.3)src :Quartus II中源代码存放目录4)simulaiton :Modelsim Simulation 仿真工程目录(前仿,后仿,布局布线后的仿真),在quartus II中设置好Modelsim路径后,simulation文件夹会自动生成。

a)presynth:前仿,即纯粹的功能仿真,综合前的仿真i.src :testbench测试源代码存放目录ii.work :工程库注:若不综合,纯粹的功能仿真,可在Modelsim中建立编写文件并进行仿真。

b)postsynth:后仿,即综合后的功能仿真i.src :testbench测试源代码存放目录ii.work :工程库注:若不进行后仿,此目录可以删除(但最好养成良好的代码风格)c)postlayout :后仿,布局布线后的时序仿真(只进行功能仿真没必要此)i.src :testbench测试源代码存放目录ii.work :工程库注:若不进行后仿,此目录可以删除(但最好养成良好的代码风格)5)res :其他文件存放目录二、Modelsim仿真操作技巧1.多个testbench文件若有多个testbench文件,要对波形进行仿真,可在Libyryr-work中选中要进行仿真的testbench文件,右键单击选择simulation即可(此步骤也可以省去选择design units的麻烦),之后同样打开wave,添加message,run……2.Transcript command以下是最常用的命令,出了用脚本,也可以在gui中用按钮来操作。

debussy使用指南

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

Debussy功能及包含软件模块

Debussy功能

Debussy直接编译Verilog\VHDL源代码,并且采用了预综合技术 识别电路的单元,可以生成原理图。在导入仿真结果后,可以用 Active Annotation在源代码、原理图、状态图上动态显示变量的 仿真值

nWave 的使用 (Cont.)

4. 選擇欲觀察的signal,以中鍵按住拖曳到右邊的視窗, 如圖所示。

い龄╈Σ:

娩跌怠

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

nWave 的使用 (Cont.)

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

nTrace 的使用 (Cont.)

¤ Â_

ÂI ªº

²Å

¸¹

¼Ð°O

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

Liyong xjtu’soc center

Institute of Artificial Intelligence and Robotics

nSchematic 的使用

1. 在 Import Design 完成之後,進入 Interactive Mode。 2. 按 New Schematic icon ,會出現程式相對應的電路 圖。

使用Modelsim如何产生debussy用的fsdb档

使用Modelsim如何產生debussy用的fsdb檔如題, 盼先進告知!! 謝謝lunkun 2006-8-25 09:42 AM要先装了Debussy,然后在运行modelsim是加上lpi的选项就可以了haha 2006-9-13 04:48 PM[quote]原帖由 [i]chip789[/i] 於 2006-4-27 11:22 PM 發表如題,<br> 盼先進告知!!<br><br>謝謝 [/quote]請參考Verdi/Debussy 內附的linking.pdf 或詢問Novas的AE.thjan65 2006-9-22 01:49 PMHow to use FSDB under Modelsim1. Edit X:\modelsim\modelsim.iniVeriuser = Full_path_of_novas.dllFull_path_of_novas.dll may look like c:\novas\debussy\share\pli\modelsim_pli54\winnt\novas.dll If the abo ve setting doesn’t work, you must set PLIOBJS.2. Set the " PLIOBJS" system environment variable before running vsim.PLIOBJS= C:\Novas\Debussy\share\PLI\modelsim_pli54\WINNT\novas.dll3. In your testbench, add the following text:initialbegin$fsdbDumpfile("filename_you_want.fsdb");$fsdbDumpvars;endhgby2209 2007-1-12 07:37 AM如同 thjan65 所述 step 1 就是掛 PLI 也就是將 modelsim.ini 這個檔案中, 找到如下的敘述; List of dynamically loaded objects for Verilog PLI applications; Veriuser = veriuser.sl並將; Veriuser = veriuser.sl 改為 Veriuser =c:\novas\debussy\share\pli\modelsim_pli54\winnt\novas.dll 記得前面那個 ";" 要拿掉喔 ~~然後在 TestBench 中加入initialbegin$fsdbDumpfile("filename_you_want.fsdb");$fsdbDumpvars;end即可 Dump FSDB 了yhchang 2008-2-17 04:41 PMRe : 使用Modelsim如何產生debussy用的fsdb檔這幾天try了一下,原來以debussy開啟dumpfile時,debussy會自動將dumpfile轉成.fsdb -- debussy 的 vfast 功能.但我覺得還是麻煩, 我會再try看看, 是否可以在run 完modelsim後自動call debussy-fast 將dumpfile轉成fsdb file.如果未試出來前有先進看到這篇post, 請不吝告知!!謝謝!!yhchang 2008-2-17 04:41 PMRe : 使用Modelsim如何產生debussy用的fsdb檔You can use the command "fsdbdumpxxx" to generate dump *.fsdb.But you must use the PLI library to modelsim simulation.lease to refer the readme.txt that tell you how to use the PLImode library.yhchang 2008-2-17 04:42 PM我按著debussy install guide 跟 modelsim 的 user manual試著安裝modelsim PLI library, 但是都不行(無法在modelsim run vsim時使用fsdbdump指令):我的做法如下:1. 使用debussy 提供的veriuser.c file作compile跟link,cl -c -IC:\modeltech_5.5f\include veriuser.clink -dll -outovas.dll -nodefaultlib:libcmt.lib -exportnit_usertfs veriuser.obj pli.lib shell32.lib C:\modeltech_5.5f\win32\mtipli.lib2. 根據 debussy install guide 新增環境變數環境變數D_LIBRARY_PATH變數值: C:\novas\debussy\share\pli\modelsim_pli\winnt\novas.dll3. 根據 debussy install guide在modelsim.ini 新增:[vsim]..veriuser=novas.dll4. 根據modelsim 的 user manual 新增環境變數環境變數LIOBJS變數值: C:\novas\debussy\share\pli\modelsim_pli\winnt\novas.dll然後直接vsim testrun -all後看路徑下未發現 fsdb file只有dump file(我同時用了$fsdbdump及$dump兩個指令來check $fsdbdump是否可用), 所以我想是 PLI 安裝的問題可以請大大門再指點一下好嗎!!感謝啦 ~_~yhchang 2008-2-17 04:43 PM哎呀呀~~~~凌晨2:15 了試了一整晚, 答案揭曉....殘酷的竟然是: $fsdbDump指令的大小寫沒注意到!是$fsdbDump非$fsdbdump啦....我的天阿!!嗚~~~ 我明天一大早還要去台北上課ㄋㄟ.....不過以上在win2000 上如何設定modelsim 的PLI程序倒可提供需要者參考!!感謝各位大大囉....頁: [1]。

simulink和modelsim联合仿真的简单例子

使用Link for ModelSim ,你可以建立一个有效的环境来进行联合仿真、器件建模、以及分析和可视化。

进行如下的实例的开发。

1 :可以在MA TLAB或Simulink 中针对HDL实体开发软件测试基准(test bench) 。

2 :可以在Simulink 中对包含在大规模系统模型的HDL 模型进行开发和仿真。

3 :可以生成测试向量进行测试、调试,以及同MA TLAB/Simulink下的规范原形进行HDL 代码的验证。

4 :提供在MA TLAB/Simulink下的对HDL行为级的建模能力。

5 :可以在MA TLAB/Simulink下对HDL的实现进行验证、分析、可视化。

Link for ModelSim中MA TLAB与ModelSim 接口和Simulink与ModelSim 接口是独立的。

这使得你可以单独使用一个接口或同时使用两个。

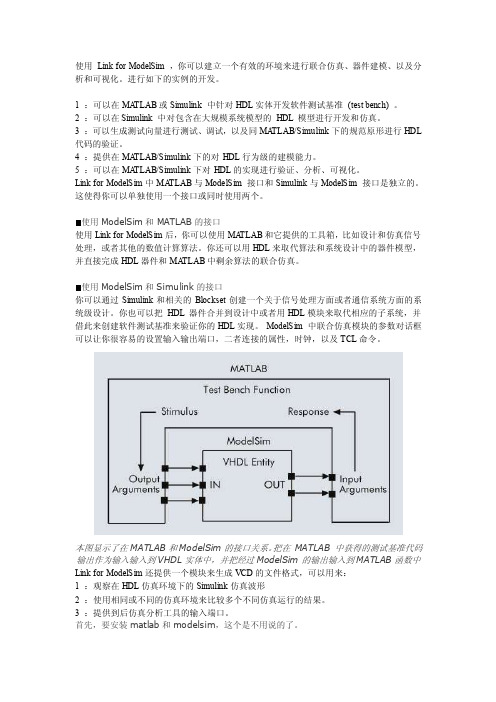

使用ModelSim和MATLAB的接口使用Link for ModelSim后,你可以使用MA TLAB和它提供的工具箱,比如设计和仿真信号处理,或者其他的数值计算算法。

你还可以用HDL来取代算法和系统设计中的器件模型,并直接完成HDL器件和MA TLAB中剩余算法的联合仿真。

使用ModelSim和Simulink的接口你可以通过Simulink和相关的Blockset创建一个关于信号处理方面或者通信系统方面的系统级设计。

你也可以把HDL 器件合并到设计中或者用HDL模块来取代相应的子系统,并借此来创建软件测试基准来验证你的HDL实现。

ModelSim 中联合仿真模块的参数对话框可以让你很容易的设置输入输出端口,二者连接的属性,时钟,以及TCL命令。

本图显示了在MATLAB和ModelSim的接口关系。

把在MATLAB 中获得的测试基准代码输出作为输入输入到VHDL实体中,并把经过ModelSim的输出输入到MATLAB函数中Link for ModelSim还提供一个模块来生成VCD的文件格式,可以用来:1 :观察在HDL仿真环境下的Simulink仿真波形2 :使用相同或不同的仿真环境来比较多个不同仿真运行的结果。

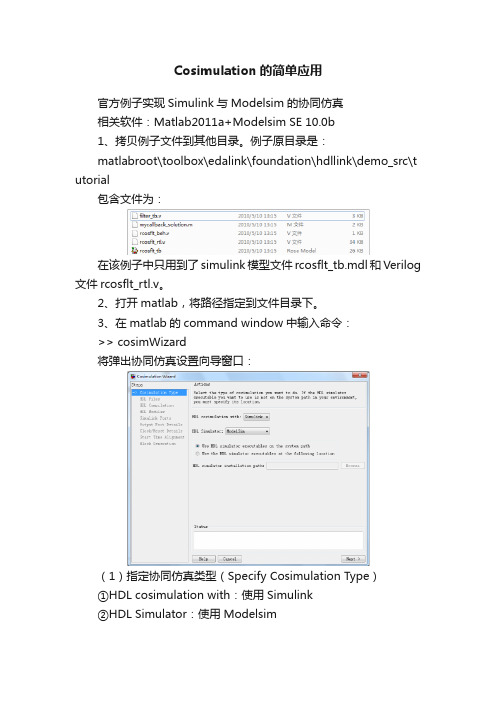

Cosimulation的简单应用

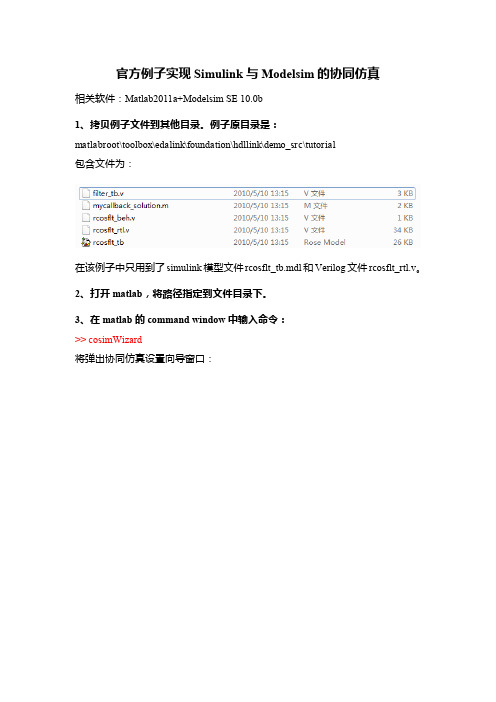

官方例子实现Simulink与Modelsim的协同仿真相关软件:Matlab2011a+Modelsim SE 10.0b1、拷贝例子文件到其他目录。

例子原目录是:matlabroot\toolbox\edalink\foundation\hdllink\demo_src\tutorial包含文件为:在该例子中只用到了simulink模型文件rcosflt_tb.mdl和Verilog文件rcosflt_rtl.v。

2、打开matlab,将路径指定到文件目录下。

3、在matlab的command window中输入命令:>> cosimWizard将弹出协同仿真设置向导窗口:(1)指定协同仿真类型(Specify Cosimulation Type)①HDL cosimulation with:使用Simulink②HDL Simulator:使用Modelsim③HDL仿真执行软件,默认即可(由于自己的有Modelsim Altera6.5b不支持协同仿真,所以需要人为指定Modelsim SE10.0b的版本)上述三步完成后,如下图所示:(2)选择HDL文件(Select HDL Files)这里只需要添加rcosflt_rtl.v文件。

(3)指定HDL编译命令(Specify HDL Compilation Commands)由于使用Modelsim,在“-incr”后紧接着添加:-vlog01compat选择Next后会看到编译信息。

(4)选择协同仿真的HDL模块(Select HDL Modules for Cosimulation)①选择协同仿真文件:rcosflt_rtl。

如果下拉中没有,可直接输入文件名②去掉Simulation Options中的“-novopt”(5)指定端口类型(Specify Port Types)默认即可。

需要注意,input port提供的四种类型中,只有input类型的会连接到simulink,output port提供的两种类型中,只有output类型的会连接到simulink。

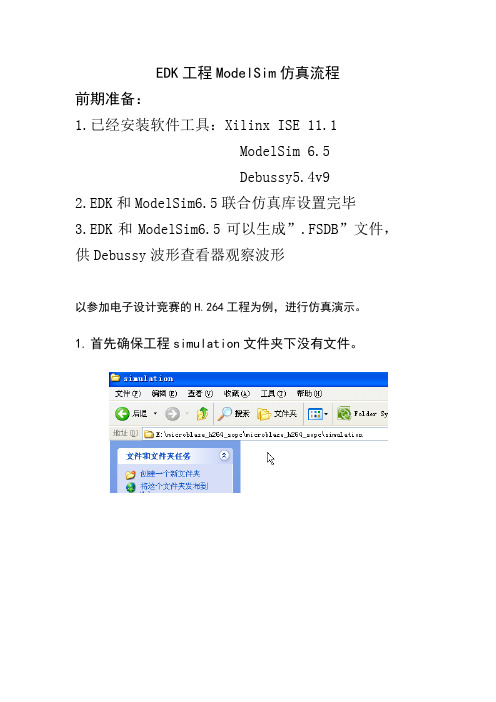

EDK工程ModelSim仿真流程

EDK工程ModelSim仿真流程前期准备:1.已经安装软件工具:Xilinx ISE 11.1ModelSim 6.5Debussy5.4v92.EDK和ModelSim6.5联合仿真库设置完毕3.EDK和ModelSim6.5可以生成”.FSDB”文件,供Debussy波形查看器观察波形以参加电子设计竞赛的H.264工程为例,进行仿真演示。

1.首先确保工程simulation文件夹下没有文件。

2.如果有文件,要通过如下方式清除,不能直接删除。

3.清除后,点击Simulation Generate Simulation HDLFiles,重新生成工程仿真的库文件。

Console控制台显示生成了Simulation ModelSimulation文件夹下生成了一堆文件。

4.在Simulation文件夹下,找到“system_tb.v”文件,打开,添加如下语句initial begin$dumpfile("aa.fsdb");$dumpvars;end以便仿真时,生成fsdb文件。

5.返回XPS界面,选择Simulation->Launch HDL Simulator,通过这种方式,打开了ModelSim6.5软件6.打开了ModelSim6.5软件,如下图所示7.打开Simulation文件夹中的system_setup.do文件,该文件中存放了系统生成的仿真脚本语句。

8.返回ModelSim6.5,在命令行下先输入“do system.do”命令。

9.输入如下命令“vsim -novopt -t ps D:/modeltech_6.5/win32/novas.dll -Lxilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”理由(复制system_setup.do文件中第二条脚本语句”vsim -novopt -t ps -L xilinxcorelib_ver -L secureip -L unisims_ver +notimingchecks system_tb glbl”,注意到要仿真生成fsdb波形文件,所以在ps和-L前添加一条新的语句”D:/modeltech_6.5/win32/novas.dll”,要链接这个“novas.dll”动态链接文件。

FPGA开发-使用modelsim和debussy做rtl仿真

1 引言

做 ASIC 或者 FPGA 设计中,选择合适的软件工具,对工作的开展有很大的帮助,一杆 利器,绝对可以使工作事半功倍。在 Windows 环境下做 rtl 开发(Verilog/VHDL),modelsim 是主流的仿真工具。Modelsim 虽然仿真速度快,功能强大。但是在调试查看波形时,便利 性远比不上 debussy。 或许大家对 debussy 有些陌生, 但是说到 linux 下被广泛使用的 verdi, 应该熟悉。Debussy 就是 verdi 的 Windows 版本,都是思源科技 NOVAS 开发的波形调试工 具,具有相同的源码。Debussy 和 verdi 具有相同的操作界面,熟悉 verdi 的工程师,使用 debussy 很容易上手。

图 6 Debussy 导入设计

4.

选中”From File”选项卡,然后在左下方的窗口中,按路径依次双击文件夹并打开, 找到 nv_lab1.f 的位置, 这时右下侧窗口显示出 nv_lab.f 文件, 双击该文件, 把 nv_lab.f 添加到了 Design Files 列表中,如图 7。然后点击 OK 按钮,则在 Debussy 中打开 了 lab1 的设计。

图 8 Debussy 中打开波形窗口

图 9 打开的波形窗口

6.

在波形窗口菜单栏,点击 File Open,在弹出的对话框中按路径找到 sim_top.fsdb 文件,双击,打开波性文件,如图 10 所示。

图 10 找到并打开波性文件

7.

查看信号波形。如图 11 所示,切换到 debussy 主界面,通过左边的导航栏,找到 想查看的文件并双击打开, 在文件中选中需要观察的信号, 可以按住鼠标左键拖动, 选中多个新号,选中后按 ctrl+w 键,把信号添加到波形窗口中。

Debussy 仿真快速上手教程

Debussy 仿真快速上手教程Debussy 介绍Debussy 是NOVAS Software, Inc(思源科技)发展的HDL Debug & Analysis tool,这套软体主要不是用来跑模拟或看波形,它最强大的功能是:能够在HDL source code、schematic diagram、waveform、state bubble diagram之间,即时做trace,协助工程师debug。

可能您会觉的:只要有simulator如ModelSim就可以做debug了,我何必再学这套软体呢? 其实Debussy v5.0以后的新版本,还提供了nLint -- check coding style & synthesizable,这蛮有用的,可以协助工程师了解如何写好coding style,并养成习惯。

下图所示为整个Debussy 的原理架构,可归纳几个结论:Debussy有四个主要单元(component),nTrace、nWave、nSchema、nStatenTrace -- Hypertext source code analysis and browse tool (为%Debussy &所开启的主画面)nWave -- Waveform analysis tool (可由nTrace内开启,或直接%nWave &开启)nSchema -- Hierarchy schematic generatornState -- Finite State Machine Extraction and analysis toolDebussy本身不含模拟器(simulator),必须呼叫外部模拟器(如Verilog-XL or ModelSim)产生FSDB file,其显示波形的单元"nWave"透过读取FSDB file,才能显示波形或讯号值的变化快速上手五部曲:(Debussy v.5.2)1. Import Files and generate FSDB file2. Trace between hierarchy browser and source code3. Trace between hierarchy browser、source code and schematic4. Trace between hierarchy browser、source code、schematic and waveform5. nLint(nState本文没介绍,有兴趣的读者,请依文后的连结,自行下载CIC所提供的NOVAS原厂编写教材参考)1. Import Files and generate FSDB file1-1 启动Debussy:% Debussy & (此处的D大小写都可以,但其它指令的大小写可能就有差别)开启nTrace window如下,此时工作目录下会新建一个"DebussyLog"目录1-2 Import Files:File \ Import Design...结果如下图所示:nTrace视窗中,含有三个区域,Hierarchical Brower、Source code window、Message window。

Debussy仿真快速上手教程

目录Debussy 仿真快速上手教程错误!未定义书签。

Debussy 介绍......................................................................................... 错误!未定义书签。

1. Import Files and generate FSDB file ............................................. 错误!未定义书签。

1-1 启动Debussy ........................................................................... 错误!未定义书签。

1-2 Import Files ............................................................................... 错误!未定义书签。

1-3 设定外部模拟器 ..................................................................... 错误!未定义书签。

1-4 切换到Interactive Mode ......................................................... 错误!未定义书签。

1-5 结束程式 ................................................................................. 错误!未定义书签。

1-6 快速启动执行序 ..................................................................... 错误!未定义书签。

1-7 其他启动Debussy的方法...................................................... 错误!未定义书签。

Cosimulation的简单应用

Cosimulation的简单应用官方例子实现Simulink与Modelsim的协同仿真相关软件:Matlab2011a+Modelsim SE 10.0b1、拷贝例子文件到其他目录。

例子原目录是:matlabroot\toolbox\edalink\foundation\hdllink\demo_src\t utorial包含文件为:在该例子中只用到了simulink模型文件rcosflt_tb.mdl和Verilog 文件rcosflt_rtl.v。

2、打开matlab,将路径指定到文件目录下。

3、在matlab的command window中输入命令:>> cosimWizard将弹出协同仿真设置向导窗口:(1)指定协同仿真类型(Specify Cosimulation Type)①HDL cosimulation with:使用Simulink②HDL Simulator:使用Modelsim③HDL仿真执行软件,默认即可(由于自己的有Modelsim Altera6.5b不支持协同仿真,所以需要人为指定Modelsim SE10.0b的版本)上述三步完成后,如下图所示:(2)选择HDL文件(Select HDL Files)这里只需要添加rcosflt_rtl.v文件。

(3)指定HDL编译命令(Specify HDL Compilation Commands)由于使用Modelsim,在“-incr”后紧接着添加: -vlog01compat选择Next后会看到编译信息。

(4)选择协同仿真的HDL模块(Select HDL Modules for Cosimulation)①选择协同仿真文件:rcosflt_rtl。

如果下拉中没有,可直接输入文件名②去掉Simulation Options中的“-novopt”(5)指定端口类型(Specify Port Types)默认即可。

Modelsim与debussy在FPGA仿真和debug中的应用

Modelsim与debussy在FPGA仿真和debug中的应⽤仿真是FPGA设计中的⼀个⾮常重要的环节,但很多朋友在做FPGA设计的过程中,却并没有意识到仿真的作⽤,也没有⼀个好的仿真流程来保证仿真验证的效果。

我们做仿真的⽬的是要通过仿真找到设计中潜在的问题并解决之,这就需要⼀个debug 的过程。

在这篇⽂章中,会讨论⼀下我对FPGA设计中仿真验证和debug的看法,也介绍⼀下modelsim+Debussy在仿真和debug中的应⽤流程。

记得在学校的时候,搭硬件系统要⽤到FPGA。

那时候没有任何FPGA设计的经验,也没有好的设计流程可以参考。

在做设计的时候,基本上是很随意的去写代码,很少顾及到甚⾄很基本的设计原则。

代码写好后,尽管有验证代码正确性的意识,但并没有成熟可靠的⽅法可以使⽤,基本上就是画⼀些简单的波形作为激励信号,通过开发软件⾃带的仿真⼯具,⼤概看⼀下输出的波形是不是正确。

这样做存在很多问题。

⾸先测试覆盖率⾮常的低,激励信号不可能做的很复杂,不可能涵盖所有需要验证的设计环节;再者就是要看被测设计的输出波形来检验设计是否正确,这样就需要⼤量的时间,效率很低。

在发现设计有问题的时候,检查设计代码,也⽤很原始的⼿段,⼀⾏⼀⾏的去查看,没有意识到或者说根本就不知道有⼯具软件可以来做trace。

更通常的验证⽅法就是在FPGA程序写好以后,综合出来,烧录到实际的系统中,在系统上直接验证。

但这种做法,效率低下且有问题的话,很难debug。

另外⽐较糟糕的是很难发现⼀些⽐较特殊的问题。

后来在公司的时候,做IC设计,公司有⽐较成熟和完善的设计流程。

主要⽤NC来做仿真,⽤debussy来做debug。

成熟和完善的设计流程带来的就是⽐较⾼的仿真的效率和⽐较⾼的覆盖率,我们在debug的时候,基于⽐较好的流程和⽅法,效率也⽐较⾼。

数年⼯作下来,让我建⽴起了⼀个基本的仿真验证的概念,这个时候,再回头看当初做FPGA设计的时候所遇到的问题,感触颇深。

debussy使用

前期问题解决方案1.altera后仿真问题系统内有宏模块库的仿真:需要添加库文件,路径\altera\80\quartus\eda\sim_lib220model.v :带有用户原语类型的Quartus自带的IP核的库文件altera_mf.v:Quartus自带的IP核的库文件cycloneii_atoms.v:相应系列的器件库,这个和你选择的器件有关,这一点一定要注意,如果你选择CycloneIII,那就选择III代的,不然会编译不通过,因为你在新建项目的时候已经确立了选用芯片的型号。

布局布线后仿真:首先在新建工程时要选择Modelsim作为仿真工具,在quartus II中编译后,在工程文件夹中生成一个:\simulation\modelsim文件夹,其中包括*.vo是仿真网表文件,可以用来代替设计文件*_modelsim.xrf是Quartus编译生成的信息文件;*_v.sdo是工程延时的文件将*.vo和*_v.sdo添加在工程中。

注意:后仿真可以不加载altera_mf.v,因为*.vo中包含了构造信息和参数。

总结:RTL级前仿真,如果有宏模块库必须加载altera_mf.v,不需要cycloneii_atoms.v 综合布局布线后仿真,必须对cycloneii_atoms.v进行编译,altera_mf.v和*.vo 任选一个即可。

2.debuss波形输入问题Debussy 介绍Debussy 是NOVAS Software, Inc(思源科技)发展的HDL Debug & Analy sis tool,这套软体主要不是用来跑模拟或看波形,它最强大的功能是:能够在HDL source code、schematic diagram、waveform、state bubble diagram 之间,即时做trace,协助工程师debug。

可能您会觉的:只要有simulator如ModelSim就可以做debug了,我何必再学这套软体呢? 其实Debussy v5.0以后的新版本,还提供了nLint -- check coding style & synthesizable,这蛮有用的,可以协助工程师了解如何写好co ding style,并养成习惯。

怎样使用Debussy+ModelSim快速查看前仿真波形

怎样使用Debussy+ModelSim快速查看前仿真波形作者:未知 时间:2010-06-18 08:22:23 来自:网络转载引子:ModelSim是HDL仿真软件,Debussy是波形查看软件;搭配使用,相当爽。

此处所谓快速查看前仿真波形仅为抛砖引玉,大家不要拘泥于此。

两款软件的功能都很强大,请自行研究。

注:本篇博文的软件环境为:Debussy 5.3v9 + Modelsim SE 6.5配置篇1 安装、和谐软件。

略。

2 拷贝文件..\Novas\Debussy\share\PLI\modelsim_pli\WINNT\novas.dll至文件夹..\modeltech_6.5\win32。

3 取消文件..\modeltech_6.5\modelsim.ini的只读属性后,打开。

找到view sourceprint?1; Veriuser = veriuser.sl替换为view sourceprint?1Veriuser = novas.dll保存;关闭;设为只读。

配置完,以后就一劳永逸了。

实战篇此处以一简单分频器为例。

文件地图如下:view sourceprint?1│ rtl.f2│ run.bat3│ sim.do4│5└─rtl6 clk_rst.v7 divider.v8 divider_tb.v1 编写欲仿真的HDL文件:RTL级代码+Testbench代码。

保存在文件夹rtl中。

(1)divider.v // RTL级代码模块view sourceprint?01`timescale1ns/10ps0203module divider(05 input i_rst_n,0607 output o_clk08);0910parameter U_DLY = 1;1112// log2(5) = 2.3219 <= 313reg[2:0] cnt_p; // 上升沿计数子1415// 5位上升沿计数器: 0 ~ 416// 4 = 5 - 117always@ (posedge i_clk, negedge i_rst_n)18begin19 if(!i_rst_n)20 cnt_p <= 0;21 else22 begin23 if(cnt_p == 4)24 cnt_p <= 0;25 else26 cnt_p <= #U_DLY cnt_p + 1'b1;27 end28end2930// log2(5) = 2.3219 <= 331reg[2:0] cnt_n; // 下降沿计数子3233// 5位下降沿计数器: 0 ~ 434// 4 = 5 - 135always@ (negedge i_clk, negedge i_rst_n)36begin37 if(!i_rst_n)39 else40 begin41 if(cnt_n == 4)42 cnt_n <= 0;43 else44 cnt_n <= #U_DLY cnt_n + 1'b1;45 end46end474849reg o_clk_p; // 上升沿时钟输出寄存器 5051// 输出上升沿时钟52// 0 ~ 2 ↑-> 153// (2+1) ~ 4 ↑-> 054// 2 = 5>>155// 4 = 5 - 156always@ (posedge i_clk, negedge i_rst_n)57begin58 if(!i_rst_n)59 o_clk_p <= 0;60 else61 begin62 if(cnt_p <= 2) // 2 = 5>>163 o_clk_p <= 1;64 else65 o_clk_p <= 0;66 end67end6869reg o_clk_n; // 下降沿时钟输出寄存器 7071// 输出下降沿时钟73// (2+1) ~ 4 ↓-> 074// 2 = 5>>175// 4 = 5 - 176always@ (negedge i_clk, negedge i_rst_n)77begin78 if(!i_rst_n)79 o_clk_n <= 0;80 else81 begin82 if(cnt_n <= 2) // 2 = 5>>183 o_clk_n <= 1;84 else85 o_clk_n <= 0;86 end87end8889assign o_clk = o_clk_n & o_clk_p; // 按位与(作用:掩码) 9091endmodule(2)clk_rst.v // Testbench的时钟及复位模块view sourceprint?01`timescale1ns/10ps0203module clk_rst(04 output reg i_clk,05 output reg i_rst_n06);0708parameter CLK_PERIOD = 20;09parameter MULT_RATIO = 10;10parameter RESET_TIME = MULT_RATIO * CLK_PERIOD + 1;1112initial13begin14 i_rst_n <= 1'b0;15 #RESET_TIME i_rst_n <= 1'b1;16end1718initial19begin20 i_clk <= 1'b0;21 forever22 #(CLK_PERIOD / 2) i_clk <= ~i_clk;23end2425endmodule把时钟及复位单独剥出来,便于移植到其他平台。

(笔记)如何使用ModelSim作前仿真与后仿真(SOC)(QuartusII)(ModelSim)

(笔记) 如何使用ModelSim作前仿真与后仿真? (SOC) (Quartus II) (ModelSim)Abstract本文介绍使用ModelSim做前仿真,并搭配Quartus II与ModelSim作后仿真。

Introduction使用环境:Quartus II 8.1 + ModelSim-Altera 6.3g由于FPGA可重复编程,所以不少开发人员就不写testbench,直接使用Quartus II的programmer烧进开发板看结果,或者使用Quartus II自带的Waveform Editor进行仿真,这种方式虽然可行,但仅适用于小project,若project越写越大,Quartus II光做fitter就很耗时间,一整天下来都在作Quartus II编译。

比较建议的方式,还是学ASIC那招:『写testbench先对每个module作前仿真,再对每个module作后仿真,最后再烧入FPGA测试。

』这种方式的优点是:1.testbench比waveform editor可更灵活的描述电路规格。

2.testbench可使用Verilog的系统函数,如$display()、$fwrite()...等。

但要使用testbench作仿真,单独Qaurtus II并无法做到,就得使用ModelSim了,这又牵涉到『前仿真』与『后仿真』。

所谓的『前仿真』,就是Quartus II的Functional Simulation,不考虑电路的门延迟与线延迟,重点在观察电路在理想环境下的行为与设计构想是否一致[1]。

由于没经过fitter阶段,所以仿真速度很快。

前仿真结果正确,并不表示将来结果结果正确,但若前仿真结果不正确,则将来结果一定不正确。

所谓的『后仿真』,就是Quartus II的Timing Simulation,考虑了电路的门延迟与线延迟,由于经过fitter阶段,所以模拟结果最为精准。

verilog仿真环境的搭建3:Debussy的设置

verilog仿真环境的搭建3:Debussy的设置Posted on 2009/07/05, 21:10, by Feng Jun, under 技术.Debussy是Novas公司出品的调试工具,在5.4V9版之后就只发行Linux了,在这里使用的是Win32上的最后一个版本。

在前面文章中,已经可以调用modelsim进行仿真了,要配合Debussy使用的话,就需要在仿真中生成波形文件供调试。

Debussy 可以使用.fsdb文件,大小要比.vcd文件要小不少。

波形文件的生成首先,将Debussy安装目录下share\PLI\modelsim_pli54\WINNT目录中的Novas.dll文件复制到modelsim安装目录下。

然后,在modelsim.ini的[vsim]标签下增加一行,用来在仿真时以供调用。

1: Veriuser = novas.dll接着,在仿真的顶层模块中添加如下语句:1: initial2:begin3: $fsdbDumpfile("wave_out.fsdb");4: $fsdbDumpvars;5:end这样,在仿真时就会在script目录生成wave_out.fsdb波形文件。

如果波形文件比较大的话,打开时会占用很多内存,这时可以把波形文件分段输出,调试时只要载入指定时间段的波形文件就可以了,将第三行语句替换为如下语句:1: $fsdbAutoSwitchDumpfile(25, "test.fsdb", 150);这条语句表示将fsdb文件分成每个大小为25MB的文件,最多输出150个文件。

每个文件的仿真时间范围记录在test.log文件中。

调用Debussy启动Debussy时,可以使用命令行方式,同时载入项目文件。

结合命令行调用Modelsim,可以写出如下的两个批处理文件。

sim.bat1: d:/program/Modeltech_6.3c/win32/vsim.exe -c -do sim.do 2: d:/program/Novas/Debussy/bin/debussy.exe -f run.fvsim中的-c参数是指定采用命令行模式,-do则是制定采用.do 脚本模式。

debussy使用教程

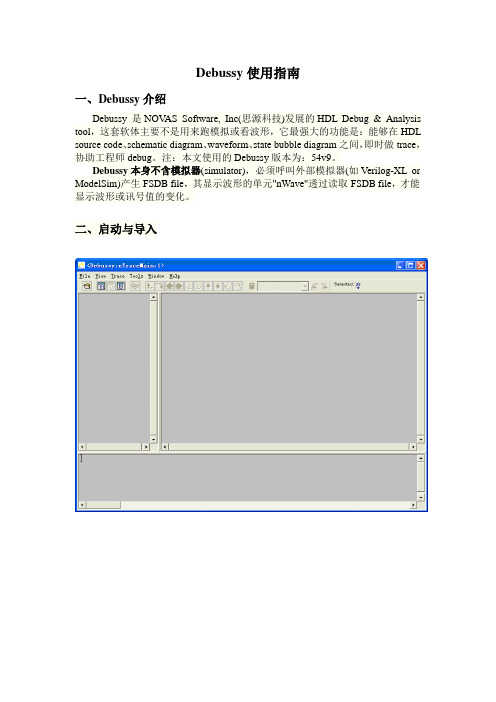

Debussy使用指南一、Debussy介绍Debussy 是NOV AS Software, Inc(思源科技)发展的HDL Debug & Analysis tool,这套软体主要不是用来跑模拟或看波形,它最强大的功能是:能够在HDL source code、schematic diagram、waveform、state bubble diagram之间,即时做trace,协助工程师debug。

注:本文使用的Debussy版本为:54v9。

Debussy本身不含模拟器(simulator),必须呼叫外部模拟器(如Verilog-XL or ModelSim)产生FSDB file,其显示波形的单元"nWave"透过读取FSDB file,才能显示波形或讯号值的变化。

二、启动与导入启动Debussy后,需要导入已编译成功的v文件以及相应的testbench导入文件:File\Import Design三、nTrace介绍3-1在Hierarchy browser点击“+”可以展开这个testbench所引用的所有模块3-2点击左侧的模块名称,右边的source code window就会立即切换到相应的module3-3 点击代码内的模块名称也会转到左侧的模块列表中你可以利用此方法轻易的追踪出project中所有design之间彼此的联系3-4除了追踪design之间的关联性,也可以用同样的方法追踪出信号的drivers与loads。

点选代码中的任意信号,使用工具栏中“D”与“L”可以查看此信号的drivers与loads,右侧的箭头用于选择上一个与下一个。

四、nSchema介绍点击工具栏中的New Schematic即可进入nSchema,中的上一层与下一层,当到达最底层时,可以通过双击某一图形单元查看其代码五、nWave介绍5-1 fsdb文件生成Debussy中,nWave只能导入fsdb文件来观察波形,fsdb文件通常是有ModelSim软件生成的,但要让ModelSim能成生成fsdb文件,必需要有如下步骤:第一步:挂PLI找到Debussy安装目录下\share\pli\modelsim_pli\winnt\下的novas.dll文件,复制到ModelSim安装目录下\win32中,找到modelsim.ini(通常在我的文档中或modelsim安装目录下),去“只读”勾选进行编辑,找到[vsim],添加Veriuser = novas.dll第二步:修改环境变量变量名:D_LIBRARY_PATH变量值:Debussy安装目录下的novas.dll如D:\Debussy\share\pli\modelsim_pli\winnt\novas.dll变量名:PLIOBJS变量值:同上(注:上述步骤只需配置一次)第三步:在testbench中加入如下代码initialbegin$fsdbDumpfile("filename_you_want.fsdb");$fsdbDumpvars;end第四步:在modelsim中进行编译,仿真,run,之后就产生了fsdb文件5.2nWave使用点击工具栏中New Waveform进入nWave。

如何使用debussy与modelsim做co-simulation(soc)(verilog)(v

如何使用D e b u s s y与M o d e l S i m做C o-S i m u l a t i o n(S O C)(V e r i l o g)(V H D L)(D e b u s s y)(M o d e l S i m)-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN如何使用Debussy与ModelSim做Co-Simulation(SOC) (Verilog) (VHDL) (Debussy) (ModelSim)Abstract本文介绍如何使用Debussy与ModelSim做Co-Simulation,并使用Verilog、VHDL以及Verilog搭配VHDL交叉一起simulation。

Introduction使用环境:Debussy 5.4 v9 + ModelSim SE 6.3e我之前一直使用Debussy + NC-Verilog做simulation,Debussy (Verdi)可以说是HDL的Source Insight,是trace与debug的神兵利器,NC-Verilog也是Verilog simulator中速度最快的,可是最近因工作需要,拿到的一包code却是用Verilog写RTL,用VHDL写testbench,所以必须2种语言一起做simulation,我在NC-Verilog一直无法成功让两种语言一起simulation。

ModelSim虽然支援Verilog + VHDL co-simulation,但用惯Debussy的我还是无法忘怀其方便的trace code方式,所以若能让ModelSim也能dump出Debussy所需要的fsdb档案,这样就太完美了。

接下来会分4个方式讨论1.RTL与testbench皆使用Verilog2.RTL与testbench皆使用VHDL3.RTL使用VHDL,testbench使用Verilog4.RTL使用Verilog,testbench使用VHDL1.RTL与testbench皆使用VerilogStep 1:设定ModeSim使用Verilog PLI (因为testbench使用Verilog)将C:\Novas\Debussy\share\PLI\modelsim_pli\WINNT\novas.dll复制到C:\Modeltech_6.3e\win32\下修改C:\Modeltech_6.3e\modelsim.ini,将Veriuser部分修改成如下所示:; List of dynamically loaded objects for Verilog PLI applications; Veriuser = veriuser.sl; use by verilogVeriuser = novas.dll; use by vhdl; Veriuser = novas_fli.dll复制代码modelsim.ini是个read only档,要修改前记得修改其属性才能存档。

利用ise联合modelsim几种仿真

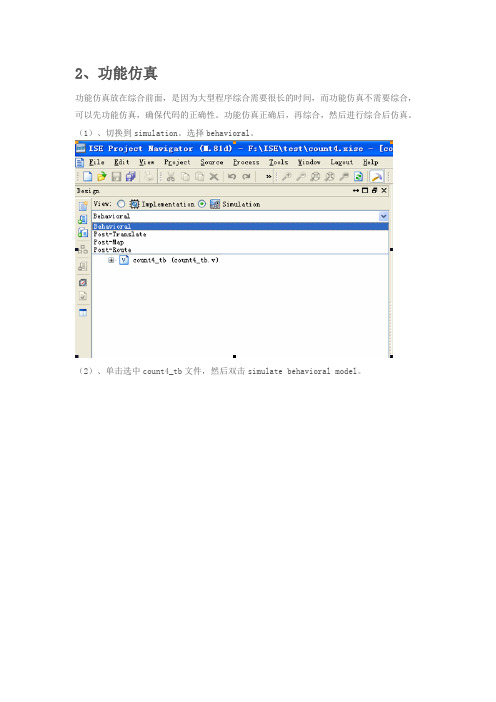

2、功能仿真功能仿真放在综合前面,是因为大型程序综合需要很长的时间,而功能仿真不需要综合,可以先功能仿真,确保代码的正确性。

功能仿真正确后,再综合,然后进行综合后仿真。

(1)、切换到simulation。

选择behavioral。

(2)、单击选中count4_tb文件,然后双击simulate behavioral model。

(3)、在modelsim,查看波形等内容。

3、时序(综合后)仿真时序仿真将时延考虑进去,包括综合后产生的(与、或、非)门时延,还有布局布线产生的时延。

综合(Synthesize),就是将HDL语言设计输入翻译成由与、或、非门和RAM、触发器等逻辑单元组成的网表。

综合后可生成综合后仿真模型(Generate Post-Synthesis Simulation Model)。

综合后,进行ISE的实现(Implement),包括翻译、映射、布局布线。

在这三个过程中都可以生成一个仿真模型(翻译和映射不会产生延时,因此常用布局布线后产生的仿真模型进行时序仿真)(1)、进行综合,双击 Synthesize – XST ,想生成 Post-Synthesis Simulation Model,双击Generate Post-Synthesis Simulation Model即可,会在工程文件夹下生成netgen\synthesis\count4_synthesis.v等文件(2)、进行实现,双击 Implement Design ,完成后,双击Generate Post-Place & Route Simulation Model.。

生成布局布线后仿真模型。

(3)、切换到 Simulation ,选中Post-route。

(4)、然后选中count4_tb文件,双击下面的Simulate Post-Place&Route Model,启动modelsim。

(5)、在modelsim中观察仿真波形。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

如何使用Debussy與ModelSim做Co-Simulation (SOC) (Verilog) (VHDL) (Debussy) (ModelSim) Abstract本文介紹如何使用Debussy與ModelSim做Co-Simulation,並使用Verilog、VHDL以及Verilog搭配VHDL交叉一起simulation。

Introduction使用環境:Debussy v9 + ModelSim SE我之前一直使用Debussy + NC-Verilog做simulation,Debussy (Verdi)可以說是HDL的Source Insight,是trace與debug的神兵利器,NC-Verilog也是Verilog simulator中速度最快的,可是最近因工作需要,拿到的一包code卻是用Verilog寫RTL,用VHDL寫testbench,所以必須2種語言一起做simulation,我在NC-Verilog一直無法成功讓兩種語言一起simulation。

ModelSim雖然支援Verilog + VHDL co-simulation,但用慣Debussy的我還是無法忘懷其方便的trace code方式,所以若能讓ModelSim也能dump出Debussy所需要的fsdb檔案,這樣就太完美了。

接下來會分4個方式討論與testbench皆使用Verilog與testbench皆使用VHDL使用VHDL,testbench使用Verilog使用Verilog,testbench使用VHDL與testbench皆使用VerilogStep 1:設定ModeSim使用Verilog PLI (因為testbench使用Verilog)將C:\Novas\Debussy\share\PLI\modelsim_pli\WINNT\複製到C:\\win32\下修改C:\\,將Veriuser部分修改成如下所示:; List of dynamically loaded objects for Verilog PLI applications; Veriuser =; use by verilogVeriuser =; use by vhdl; Veriuser =复制代码是個read only檔,要修改前記得修改其屬性才能存檔。

Step 2:RTL部分(以4 bit counter為例)/ Verilog1/*2(C) OOMusou 201134Filename :5Simulator : ModelSim , Debussy v96Description : ModelSim with debussy7Release : 01/31/20108 */910module counter (11clk,12rst_n,13cnt14);1516input clk;17input rst_n;18output[3:0] cnt;1920reg[3:0] cnt;2122always@(posedge clk, negedge rst_n) begin 23if(~rst_n)24cnt <= 4'h0;25else26cnt <= cnt + 1'b1;27end2829endmodule复制代码Step 3:Testbench部分/ Verilog1/*2(C) OOMusou 201134Filename :5Compiler : ModelSim , Debussy v96Description : ModelSim with debussy7Release : 01/31/20108 */910module counter_tb;1112reg clk;13reg rst_n;14wire[3:0] cnt;1516 lk(clk),37.rst_n(rst_n),38t(cnt)39);4041endmodule复制代码19行initial begin#0;clk = 1'b0;rst_n = 1'b0;#5;rst_n = 1'b1;#195;$finish;end复制代码一搬來說,若在NC-Verilog做simulation,我們會在testbench內指定結束simulation的時間,不過在ModelSim裡,simulation時間是由ModelSim script控制,在testbench內寫$finish並沒有用,所以會省略$finish時間入下。

initial begin#0;clk = 1'b0;rst_n = 1'b0;#5;rst_n = 1'b1;end复制代码Step 4:ModelSim script部分vlib workvlogvlogvsim counter_tbrun200nsq复制代码其中vlib work建立work library。

vlogvlog复制代码編譯RTL:與testbench:,vlog為modelsim的Verilog compiler。

vsim counter_tb以counter_tb為top module進行simulation。

run200ns命令ModelSim執行200 ns的simulation。

q離開ModelSimStep 5:執行ModelSim的批次檔vsim -c -do-c 表示ModelSim將以console mode執行,因為在Debussy + ModelSim時,只把ModelSim當成NC-Verilog使用,並沒有用到ModelSim的GUI模式。

-do 表示執行ModelSim script。

執行結果D:\0Clare\VerilogLab\ModelSim\counter_verilog>vsim -c -doReading C:/tcl/vsim/## do# ** Warning: (vlib-34) Library already exists at "work".# Model Technology ModelSim SE vlog Compiler Feb 2 2008# -- Compiling module counter## Top level modules:# counter# Model Technology ModelSim SE vlog Compiler Feb 2 2008# -- Compiling module counter_tb## Top level modules:# counter_tb# vsim counter_tb# ** Note: (vsim-3813) Design is being optimized due to module recompilation...# ** Note: (vsim-3865) Due to PLI being present, full design access is being specified. # Loading C:\\win32/# # # # *Novas* Create FSDB file ''# *Novas* Start dumping the scope(counter_tb), layer(0).# *Novas* End of dumping.# ** Note: $finish : (27)# Time: 200 ns Iteration: 0 Instance: /counter_tb复制代码Step 6:執行Debussy批次檔部份debussy -2001 -ssf -sswr-2001表示支援Verilog 2001語法-ssf 載入Debussy dump file-sswr 載入Debussy signal file執行結果與testbench皆使用VHDLStep 1:設定ModelSim使用VHDL FLI (因為testbench使用VHDL)將C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT\複製到C:\\win32\下修改C:\\,將Veriuser部分修改成如下所示:; List of dynamically loaded objects for Verilog PLI applications; Veriuser =; use by verilog;Veriuser =; use by vhdlVeriuser =复制代码是個read only檔,要修改前記得修改其屬性才能存檔。

複製C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT\到自己的project底下(為什麼Verilog不需要這個檔,而VHDL需要這個檔,稍後會解釋)Step 2:RTL部分(以4 bit counter為例)/ VHDL1-- (C) OOMusou 201123 -- Filename :4 -- Simulator : ModelSim , Debussy v95 -- Description : ModelSim with debussy6 -- Release : 02/05/201178library IEEE;9use10use1112entity counter is13port( clk : in std_logic;14rst_n : in std_logic;15cnt : out std_logic_vector(3downto0)); 16end entity counter;1718architecture arc of counter is19signal cnt_r : std_logic_vector(3downto0);20begin21process(clk, rst_n)22begin23if(rst_n = '0') then24cnt_r <= "0000";25elsif rising_edge(clk) then26cnt_r <= cnt_r + 1;27end if;28end process;2930cnt <= cnt_r;31end arc;复制代码Step 3:Testbench部分/ VHDL1-- (C) OOMusou 201123 -- Filename :4 -- Simulator : ModelSim , Debussy v95 -- Description : ModelSim with debussy6 -- Release : 01/31/201078library IEEE;9use10use11use1213entity counter_tb is14end entity counter_tb;1516architecture arc of counter_tb is17component counter18port(19clk : in std_logic;20rst_n : in std_logic;21cnt : out std_logic_vector(3downto0) 22);23end component;2425signal clk : std_logic:= '0';26signal rst_n : std_logic:= '0';27signal cnt : std_logic_vector(3downto0); 2829begin30process31begin-- 50MHz32clk_loop : loop33clk <= '0';34wait for10ns;35clk <= '1';36wait for10ns;37end loop clk_loop;38end process;3940process41begin42wait for5ns;43rst_n <= '1';44end process;4546process48fsdbDumpfile("");49fsdbDumpvars(0, "counter_tb");50wait;51end process;5253u_counter : counter54port map(55clk => clk,56rst_n => rst_n,57cnt => cnt58);59end arc;复制代码11行use這是因為與VHDL FLI的原因,稍後會解釋。