IC datasheet pdf-TLC320AC01,pdf(TLC320AC01C Single-Supply Analog Interface Circuit)

IC datasheet pdf-NCL30001 pdf,detasheet

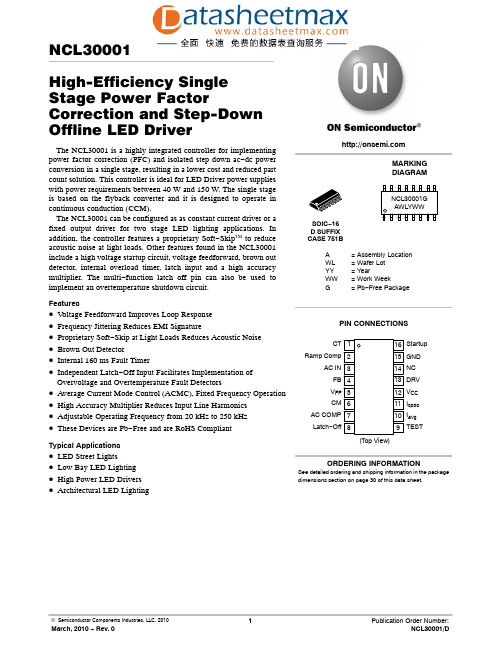

NCL30001High-Efficiency Single Stage Power FactorCorrection and Step-Down Offline LED DriverThe NCL30001 is a highly integrated controller for implementing power factor correction (PFC) and isolated step down ac −dc power conversion in a single stage, resulting in a lower cost and reduced part count solution. This controller is ideal for LED Driver power supplies with power requirements between 40 W and 150 W. The single stage is based on the flyback converter and it is designed to operate in continuous conduction (CCM).The NCL30001 can be configured as as constant current driver or a fixed output driver for two stage LED lighting applications. In addition, the controller features a proprietary Soft −Skip ™ to reduce acoustic noise at light loads. Other features found in the NCL30001include a high voltage startup circuit, voltage feedforward, brown out detector, internal overload timer, latch input and a high accuracy multiplier. The multi −function latch off pin can also be used to implement an overtemperature shutdown circuit.Features•V oltage Feedforward Improves Loop Response •Frequency Jittering Reduces EMI Signature•Proprietary Soft −Skip at Light Loads Reduces Acoustic Noise •Brown Out Detector•Internal 160 ms Fault Timer•Independent Latch −Off Input Facilitates Implementation of Overvoltage and Overtemperature Fault Detectors•Average Current Mode Control (ACMC), Fixed Frequency Operation •High Accuracy Multiplier Reduces Input Line Harmonics •Adjustable Operating Frequency from 20 kHz to 250 kHz •These Devices are Pb −Free and are RoHS Compliant Typical Applications•LED Street Lights•Low Bay LED Lighting •High Power LED Drivers •Architectural LED LightingMARKINGDIAGRAMA = Assembly Location WL = Wafer Lot YY = YearWW = Work WeekG= Pb −Free PackageSOIC −16D SUFFIX CASE 751BNCL30001G AWLYWWSee detailed ordering and shipping information in the package dimensions section on page 30 of this data sheet.ORDERING INFORMATION(Top View )V FF CT Ramp Comp AC IN FB CM AC COMP Latch −Off Startup V CC I spos TESTI avg DRV GND NC PIN CONNECTIONSStartupI sposGNDV CCLatch −DRVI avgTESTV Figure 1. Detailed Block DiagramPIN FUNCTION DESCRIPTIONPin Symbol Description1C T An external timing capacitor (C T) sets the oscillator frequency. A sawtooth between 0.2 V and 4 V sets the oscillator frequency and the gain of the multiplier.2RAMP COMP A resistor (R RC) between this pin and ground adjust the amount of ramp compensation that is added to the current signal. Ramp compensation is required to prevent subharmonic oscillations. This pin should not beleft open.3AC IN The scaled version of the full wave rectified input ac wave is connected to this pin by means of a resistive voltage divider. The line voltage information is used by the multiplier.4FB An error signal from an external error amplifier circuit is fed to this pin via an optocoupler or other isolation circuit. The FB voltage is a proportional of the load of the converter. If the voltage on the FB pin drops be-low 0.41 V (typical) the controller enters Soft−Skip to reduce acoustic noise.5VFF Feedforward input. A scaled version of the filtered rectified line voltage is applied by means of a resistive divider and an averaging capacitor. The information is used by the Reference Generator to regulate thecontroller.6CM Multiplier output. A capacitor is connected between this pin and ground to filter the modulated output of the multiplier.7AC COMP Sets the pole for the ac reference amplifier. The reference amplifier compares the low frequency compon-ent of the input current to the ac reference signal. The response must be slow enough to filter out most ofthe high frequency content of the current signal that is injected from the current sense amplifier, but fastenough to cause minimal distortion to the line frequency information. The pin should not be left open.8Latch Latch−Off input. Pulling this pin below 1.0 V (typical) or pulling it above 7.0 V (typical) latches the controller.This input can be used to implement an overvoltage detector, an overtemperature detector or both. Referto Figure 60 for a typical implementation.9TEST This pin is a TEST pin. A nominal 50K $10% resistor must be connected to GND for proper operation. 10I AVG An external resistor and capacitor connected from this terminal to ground, to set and stabilizes the gain of the current sense amplifier output that drives the ac error amplifier.11I Spos Positive current sense input. Connects to the positive side of the current sense resistor.12V CC Positive input supply. This pin connects to an external capacitor for energy storage. An internal current source supplies current from the STARTUP pin V CC. Once the voltage on V CC reaches approximately 15.3V, the current source turns off and the outputs are enabled. The drivers are disabled once V CC reachesapproximately 10.2 V. If V CC drops below 0.83 V (typical), the startup current is reduced to less than500 m A.13DRV Drive output for the main flyback power MOSFET or IGBT. DRV has a source resistance of 10.8 W (typical) and a sink resistance of 8 W (typical).14NC No Connect15GND Ground reference for the circuit.16HV Connect the rectified input line voltage directly to this pin to enable the internal startup regulator. A con-stant current source supplies current from this pin to the capacitor connected to the V CC pin, eliminatingthe need for a startup resistor. The charge current is typically 5.5 mA. Maximum input voltage is 500 V.MAXIMUM RATINGS (Notes 1 and 2)Rating Symbol Value UnitStart_up Input Voltage Start_up Input Current V HVI HV−0.3 to 500$100VmAPower Supply Input Voltage Power Supply Input Current V CCI CC−0.3 to 20$100VmALatch Input Voltage Latch Input Current V LatchI Latch−0.3 to 10$100VmAAll Other Pins Voltage All Other Pins Current −0.3 to 6.5$100VmAThermal Resistance, Junction−to−Air 0.1 in” Copper0.5 in” Copper q JA130110°C/WThermal Resistance, Junction−to−Lead RΘJL50°C/W Maximum Power Dissipation @ T A = 25°C P MAX0.77W Operating Temperature Range T J−40 to 125°C Storage Temperature Range T STG−55 to 150°C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.This device contains ESD protection and exceeds the following tests:Pin 1−15: Human Body Model 2000 V per MIL−Std−883, Method 3015.Machine Model Method 200 VPin 16 is the high voltage startup of the device and is rated to the maximum rating of the part, 500 V.2.This device contains Latchup protection and exceeds ±100 mA per JEDEC Standard JESD78.NCL30001Figure 2. Typical Application SchematicR L E DTEST RC J JParameter Test Condition Symbol Min Typ Max Unit OSCILLATORFrequency f osc90100110kHz– 6.8–% Frequency Modulation in Percentageof f OSCFrequency Modulation Period– 6.8–ms Ramp Peak Voltage V CT(peak)– 4.0–V Ramp Valley Voltage V CT(valley)–0.10–V Maximum Duty Ratio R TEST = open D94−–% Ramp Compensation Peak Voltage V RCOMP(peak)–4–V AC ERROR AMPLIFIERInput Offset Voltage (Note 3)Ramp I AVG, V FB = 0 V ACV IO40–mV Error Amplifier Transconductance g m–100–m SI EA(source)2570–m A Source Current V AC COMP = 2.0 V, V AC IN = 2.0 V,V FF = 1.0 VSink Current V AC COMP = 2.0 V, V A C_IN = 2.0 V,I EA(sink)−25−70–m AV FF = 5.0 VCURRENT AMPLIFIERTEST RC J JParameter UnitMaxTypMinSymbolTest ConditionAC INPUTInput Bias Current Into ReferenceMultiplier & Current CompensationAmplifierI AC IN(IB)–0.01–m A DRIVE OUTPUTDrive Resistance (Thermally Limited)DRV SinkDRV SourceV DRV = 1 VI DRV = 100 mAR SNKR SRC––810.81824WRise Time (10% to 90%)DRV t r–40–ns Fall Time (90% to 10%)DRV t f–20–ns Driver Out Low VoltageDRV I DRV = 100 m A V DRV(low)– 1.0100mV Soft−SkipSkip Synchronization to ac LineVoltage ThresholdV ACIN Increasing, V FB = 1.5 V V SSKIP(SYNC)210267325mVSkip Synchronization to ac Line Voltage Threshold Hysteresis V ACIN Decreasing V SSKIP(SYNCHYS)–40–mVSkip Ramp Period (Note 3)t SSKIP− 2.5–ms Skip Voltage Threshold V SSKIP360410460V Skip Voltage Hysteresis V SSKIP(HYS)4590140mV Skip Transient Load Detect Threshold(Note 3)V SSKIP(TLD)− 1.75−V FEEDBACK INPUTPull−Up Current Source V FB = 0.5 V I FB600750920m A Pull−Up Resistor R FB– 6.7–k W Open Circuit Voltage V FB(open) 5.3 5.7 6.3V STARTUP AND SUPPLY CIRCUITSSupply VoltageStartup ThresholdMinimum Operating VoltageLogic Reset Voltage V CC IncreasingV CC DecreasingV CC DecreasingV CC(on)V CC(off)V CC(reset)14.39.3–15.410.27.016.311.3–VInhibit Threshold Voltage V HV = 40 V, I inhibit = 500 m A V inhibit−0.83 1.15V Inhibit Bias Current V HV = 40 V, V CC = 0.8 * V inhibit I inhibit40-500m A Minimum Startup Voltage I start = 0.5 mA, V CC = V CC(on) – 0.5 V V start(min)––40V Startup Current V CC = V CC(on) – 0.5 V, V FB = Open I start 3.0 5.628.0mAOff−State Leakage Current V HV = 400 V, T J = 25°CT J = −40°C to 125°C I HV(off)––17154080m ASupply CurrentDevice Disabled (Overload) Device SwitchingV FB = Openf OSC[ 100 kHzI CC1I CC2––0.726.251.27.2mAFAULT PROTECTIONOverload Timer t OVLD120160360ms Overload Detect Threshold V OVLD 4.7 4.9 5.2V 3.Guaranteed by DesignTEST RC J JParameter UnitMaxTypMinSymbolTest ConditionFAULT PROTECTIONBrown−Out Detect Threshold (entering fault mode)V FF Decreasing, V FB = 2.5 V,V AC IN = 2.0 VV BO(low)0.410.450.49VBrown−Out Exit Threshold (exiting fault mode)V FF Increasing, V FB = 2.5 V,V AC IN = 2.0 VV BO(high)0.570.630.69VBrown−Out Hysteresis V BO(HYS)−174−mV LATCH INPUTPull−Down Latch Voltage Threshold V Latch Decreasing V latch(low)0.90.98 1.1V Pull−Up Latch Voltage Threshold V Latch Increasing V latch(high) 5.67.08.4V Latch Propagation Delay V Latch =V latch(high)t latch(delay)305690m s Latch Clamp Current (Going Out)V Latch = 1.5 V I latch(clamp)425158m A Latch Clamp Voltage (I Latch Going In)I Latch = 50 m A V latch(clamp) 2.5 3.27 4.5V Latch−Off Current Shutdown(Going In)V Latch Increasing I latch(shdn)−95−m A 3.Guaranteed by DesignFigure 3. Oscillator Frequency (f OSC ) vs.Junction Temperature6.06.57.07.58.0−50−250255075100125150Figure 4. Oscillator Frequency Modulation in Percentage of f OSC vs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)6.06.57.07.58.0−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 5. Oscillator Frequency ModulationPeriod vs. Junction Temperature3.83.853.93.954.04.054.1−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 6. Ramp Peak Voltage vs. JunctionTemperatureV C T (p e a k ), O S C I L L A T O R R A M P P E A K V O L T A G E (V )9092949698100−50−250255075100125150D , M A X I M U M D U T Y R A T I O (%)Figure 7. Maximum Duty Ratio vs. JunctionTemperature T J , JUNCTION TEMPERATURE (°C)−50−2502550751001251503.83.853.93.954.04.054.1T J , JUNCTION TEMPERATURE (°C)V C O M P (p e a k ), R A M P C O M P P E A K V O L T A G E (V )Figure 8. Ramp Compensation Peak Voltagevs. Junction Temperature9095100105110−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)f O S C , O S C I L L A T O R F R E Q U E N C Y (k H z )O S C I L L A T O R F R E Q U E N C Y M O D U L A T I O N P E R I O D (m s )O S C I L L A T O R F R E Q U E N C Y M O D U L A T I O N (%)505560657075808590−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)I E A (S O U R C E ), E R R O R A M P L I F I E R S O U R C E C U R R E N T (m A )Figure 9. Error Amplifier Source Current vs.Junction Temperature505560657075808590−50−25255075100125150Figure 10. Error Amplifier Sink Current vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)I E A (S I N K ), E R R O R A M P L I F I E R S I N K C U R R E N T (m A )40.042.545.047.550.052.555.057.560.0−50−25255075100125150Figure 11. Current Amplifier Input Bias Current vs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)C A V B I A S , C U R R E N T A M P L I F I E R I N P U T B I A S C U R R E N T (m A )700710720730740750760770−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 12. Current Limit Threshold vs.Junction Temperature V I L I M , C U R R E N T L I M I T T H R E S H O L D (m V )5.05.25.45.65.86.0−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)P W M k , P W M V O L T A G E G A I N (V /V )Figure 13. PWM Output Voltage Gain vs.Junction TemperatureFigure 14. Oscillator CS Limit Voltage Gain vs.Junction Temperature16171819202122−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)I S V k , C U R R E N T L I M I T V O L T A G E G A I N (V /V )5.25T J , JUNCTION TEMPERATURE (°C)Figure 15. Oscillator Reference Generator Output Voltage vs. Junction TemperatureR G o u t , R E F E R E N C E G E N E R A T O R O U T P U T V O L T A G E (V )4.06.08.0101214−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)R S N K 1, D R V S I N K D R I V E R E S I S T A N C E (W )Figure 16. DRV Sink Resistance vs. JunctionTemperature 6.08.010121416−50−250255075100125150Figure 17. DRV Source Drive Resistance vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)R S R C 1, D R V S O U R C E R E S I S T A N C E (W )T J , JUNCTION TEMPERATURE (°C)V D R V (l o w ), D R V L O W V O L T A G E (m V )Figure 18. DRV Low Voltage vs. JunctionTemperature200220240260280300−−250255075100125150Figure 19. Skip Synchronization to ac Line Voltage Threshold vs. Junction Temperature T J , JUNCTION TEMPERATURE (°C)V S S K I P (S Y N C ), S K I P S Y N C T O A C L I N E V O L T A G E T H R E S H O L D (m V )T J , JUNCTION TEMPERATURE (°C)V S S K I P , S K I P V O L T A G E T H R E S H O L D (V )Figure 20. Skip Voltage Threshold vs. JunctionTemperature30507090110130−50−2502550751001251500.3900.3920.3940.3960.3980.4000.4020.4040.4060.4080.41080859095100−50−25255075100125150Figure 21. Skip Voltage Hysteresis vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)V S S K I P , S K I P V O L T A G E H Y S T E R E S I S (m V )680705730755780−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)I F B , F E E D B A C K P U L L −U P C U R R E N T S O U R C E (m A )Figure 22. Feedback Pull −Up Current Sourcevs. Junction Temperature5.25.45.65.86.06.2−50−250255075100125150V F B (o p e n ), F E E D B A C K O P E N C I R C U I T V O L T A G E (V )T J , JUNCTION TEMPERATURE (°C)Figure 23. Feedback Open Circuit Voltage vs.Junction Temperature14.7514.9515.1515.3515.5515.75−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V C C (o n ), S T A R T U P T H R E S H O L D (V )Figure 24. Startup Threshold vs. JunctionTemperature9.59.79.910.110.310.5−50−250255075100125150Figure 25. Minimum Operating Voltage vs.Junction TemperatureV C C (o f f ), M I N I M U M O P E R A T I N G V O L T A G E (V )T J , JUNCTION TEMPERATURE (°C)Figure 26. Inhibit Threshold Voltage vs.Junction Temperature6507007508008509009501000−50−25T J , JUNCTION TEMPERATURE (°C)V i n h i b i t , I N H I B I T T H R E S H O L D V O L T A G E (V )250270290310330350−50−250255075100125150I i n h i b i t , I N H I B I T B I A S C U R R E N T (m A )T J , JUNCTION TEMPERATURE (°C)Figure 27. Inhibit Bias Current vs. JunctionTemperature22.022.523.023.524.024.525.0V s t a r t u p (m i n ), M I N I M U M S T A R T U P V O L T A G E (V )T J , JUNCTION TEMPERATURE (°C)Figure 28. Minimum Startup Voltage vs.Junction Temperature5.05.25.45.65.86.0−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)s t a r t Figure 29. Startup Current vs. JunctionTemperature1015202530−50−250255075100125150Figure 30. Off −State Leakage Current vs.Junction Temperature T J , JUNCTION TEMPERATURE (°C)I H V (o f f ), O F F −S T A T E L E A K A G E C U R R E N T (m A )650675700725750775800825850−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)Figure 31. Supply Current Device Disabled (Overload) vs. Junction TemperatureI C C 1, S U P P L Y C U R R E N T D E V I C E D I S A B L E D (m A )5.755.956.156.356.556.75−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)I C C 2, S U P P L Y C U R R E N T D E V I C E S W I T C H I N G (m A )Figure 32. Supply Current Device Switchingvs. Junction Temperature100120140160180200−50−250255075100125150Figure 33. Overload Timer vs. JunctionTemperatureT J , JUNCTION TEMPERATURE (°C)t O V L D , O V E R L O A D T I M E R (m s )4.54.74.95.15.35.5−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V O V L D , O V E R L O A D D E T E C T T H R E S H O L D (V )Figure 34. Overload Detect Threshold vs.Junction Temperature400420440460480500−50−250255075100125150Figure 35. Brown −Out Detect Threshold vs.Junction TemperatureT J , JUNCTION TEMPERATURE (°C)V B O (l o w ), B R O W N −O U T D E T E C T T H R E S H O L D (m V )600610620630640650−50−250255075100125150V B O (h i g h ), B R O W N −O U T E X I T T H R E S H O L D (m V )Figure 36. Brown −Out Exit Threshold vs.Junction Temperature T J , JUNCTION TEMPERATURE (°C)160165170175180−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V B O (H Y S ), B R O W N −O U T H Y S T E R E S I S (m V )Figure 37. Brown −Out Hysteresis vs. JunctionTemperature9009209409609801000−50−25255075100125150V L A T C H (l o w ), L A T C H P U L L −D O W N V O L T A G E T H R E S H O L D (m V )Figure 38. Latch Pull −Down Voltage Thresholdvs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)−50−2502550751001251506.56.76.97.17.37.5T J , JUNCTION TEMPERATURE (°C)V L A T C H (l o w _H Y S ), L A T C H P U L L −U P T H R E S H O L D (V )Figure 39. Latch Pull −Up Threshold vs.Junction Temperature6.56.76.97.17.37.5−50−250255075100125150Figure 40. Latch Pull −Up Voltage Thresholdvs. Junction TemperatureT J , JUNCTION TEMPERATURE (°C)V L A T C H (l h i g h ), L A T C H P U L L −U P V O L T A G E T H R E S H O L D (V )505254565860−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V L A T C H (d e l a y ), L A T C H P R O P A G A T I O N D E L A Y (m s )Figure 41. Latch Propagation Delay vs.Junction Temperature505152535455−50−250255075100125150Figure 42. Latch Clamp Current vs. JunctionTemperatureT J , JUNCTION TEMPERATURE (°C)I L A T C H (c l a m p ), L A T C H C L A M P C U R R E N T (m A )3.03.13.23.33.43.5−50−25255075100125150T J , JUNCTION TEMPERATURE (°C)V L A T C H (c l a m p ), L A T C H C L A M P V O L T A G E (V )Figure 43. Latch Clamp Voltage vs. JunctionTemperature 9092949698100−50−250255075100125150T J , JUNCTION TEMPERATURE (°C)V L A T C H (s h d n ), L A T C H −O F F C U R R E N T S H U T D O W N (m A )Figure 44. Latch −Off Current Shutdown vs.Junction TemperatureDETAILED DEVICE DESCRIPTIONIntroductionThe NCL30001 is a highly integrated controller combining PFC and isolated step down power conversion in a single stage, resulting in a lower cost and reduced part count solution. This controller is ideal for LED Lighting applications with power requirements between 40 W and 150 W with an output voltage greater than 12 V . The single stage is based on the flyback converter and it is designed to operate in CCM mode.Power Factor Correction (PFC) IntroductionPower factor correction shapes the input current of off −line power supplies to maximize the real power available from the mains. Ideally, the electrical appliance should present a load that emulates a pure resistor, in which case the reactive power drawn by the device is zero. Inherent in this scenario is the freedom from input current harmonics.The current is a perfect replica of the input voltage (usually a sine wave) and is exactly in phase with it. In this case the current drawn from the mains is at a minimum for the real power required to perform the needed work, and this minimizes losses and costs associated not only with the distribution of the power, but also with the generation of the power and the capital equipment involved in the process.The freedom from harmonics also minimizes interference with other devices being powered from the same source.Another reason to employ PFC in many of today’s power supplies is to comply with regulatory requirements. Today,lighting equipment in Europe must comply with IEC61000−3−2 Class C. This requirement applies to most lighting applications with input power of 25 W or greater,and it specifies the maximum amplitude of line −frequency harmonics up to and including the 39th harmonic. Moreover power factor requirements for commercial lighting is included within the ENERGY STAR ® Solid State Lighting Luminaire standard regardless of the applications power level.Typical Power Supply with PFCA typical power supply consists of a boost PFC preregulator creating an intermediate X 400 V bus and an isolated dc −dc converter producing the desired output voltage as shown in Figure 45. This architecture has two power stages.Figure 45. Typical Two Stage Power ConverterRectifier &FilterPFC PreregulatorDC −DC Converter with isolationAC Input V outA two stage architecture allows optimization of each individual power stage. It is commonly used because of designer familiarity and a vast range of availablecomponents. But, because it processes the power twice, the search is always on for a more compact and power efficient solution.The NCL30001 controller offers the convenience of shrinking the front −end converter (PFC preregulator) and the dc −dc converter into a single power processing stage as shown in Figure 46.Figure 46. Single Stage Power ConverterRectifier &FilterNCL30001 Based Single −Stage Flyback ConverterAC InputV outThis approach significantly reduces the component count.The NCL30001 based solution requires only one each of MOSFET, magnetic element, output rectifier (low voltage)and output capacitor (low voltage). In contrast, the 2−stage solution requires two or more of the above −listed components. Elimination of certain high −voltage components (e.g. high voltage capacitor and high voltage PFC diode) has significant impact on the system design. The resultant cost savings and reliability improvement are often worth the effort of designing a new converter.Single PFC StageWhile the single stage offers certain benefits, it is important to recognize that it is not a recommended solution for all requirements. The following three limitations apply to the single stage approach:•The output voltage ripple will have a 2x line frequency component (120 Hz for North American applications)that can not be eliminated easily. The cause of this ripple is the elimination of the energy storage element that is typically the boost output capacitor in the2−stage solution. The only way to reduce the ripple is to increase the output filter capacitance. The required value of capacitance is inversely proportional to the output voltage. Normally the presence of this ripple is not a issue for most LED lighting applications.•The hold −up time will not be as good as the 2−stage approach – again due to the lack of an intermediate energy storage element.•In a single stage converter, one FET processes all the power – that is both a benefit and a limitation as the stress on that main MOSFET is relatively higher.Similarly, the magnetic component (flybacktransformer/inductor) can not be optimized as well as in the 2−stage solution. As a result, potentially higher leakage inductance induces higher voltage spikes (like the one shown in Figure 47) on the MOSFET drain.This may require a MOSFET with a higher voltagerating compared to similar dc −input flybackapplications.Figure 47. Typical Drain Voltage Waveform of aFlyback Main SwitchThere are two methods to clamp the voltage spike on the main switch, a resistor −capacitor −diode (RCD) clamp or a transient voltage suppressor (TVS).RCD V outTVS V outFigure 49. TVS ClampBoth methods result in dissipation of the leakage energy in the clamping circuits – the dissipation is proportional to LI 2 where L is the leakage inductance of the transformer and I is the peak of the switch current at turn −off. An RCD snubber is simple and has the lowest cost, but constantly dissipates power. A TVS provides good voltage clamping ata slightly higher cost and dissipates power only when the drain voltage exceeds the voltage rating of the TVS.Other features found in the NCL30001 include a high voltage startup circuit, voltage feedforward, brown out detector, internal overload timer, latch input and a high accuracy multiplier.NCL30001 PFC LoopThe NCL30001 incorporates a modified version of average current mode control used for achieving the unity power factor. The PFC section includes a variable reference generator, a low frequency voltage regulation error amplifier (AC error AMP), ramp compensation (Ramp Comp) and current shaping network. These blocks are shown in the lower portion of the bock diagram (Figure 45).The inputs to the reference generator include feedback signal (FB), scaled AC input signal (AC_IN) and feedforward input (V FF ). The output of the reference generator is a rectified version of the input sine −wave scaled by the FB and V FF values. The reference amplitude is proportional to the FB and inversely proportional to the square of the V FF . This, for higher load levels and/or lower input voltage, the signal would be higher.The function of the AC error amp is to force the average current output of the current sense amplifier to match the reference generator output. The output of the AC error amplifier is compensated to prevent response to fast events.This output (V error ) is fed into the PWM comparator through a reference buffer. The PWM comparator sums the V error and the instantaneous current and compares it to a 4.0 V threshold to provide the desired duty cycle control. Ramp compensation is also added to the input signal to allow CCM operation above 50% duty cycle.High Voltage Startup CircuitThe NCL30001 internal high voltage startup circuit eliminates the need for external startup components and provides a faster startup time compared to an external startup resistor. The startup circuit consists of a constant current source that supplies current from the HV pin to the supply capacitor on the V CC pin (C CC ). The startup current (I start ) is typically 5.5 mA.The DRV driver is enabled and the startup current source is disabled once the V CC voltage reaches V CC(on), typically 15.4 V . The controller is then biased by the V CC capacitor.The drivers are disabled if V CC decays to its minimum operating threshold (V CC(off)) typically 10.2 V . Upon reaching V CC(off) the gate driver is disabled. The V CC capacitor should be sized such V CC is kept above V CC(off)while the auxiliary voltage is building up. Otherwise, the system will not start.The controller operates in double hiccup mode while in overload or V CC(off). A double hiccup fault disables the drivers, sets the controller in a low current mode and allows V CC to discharge to V CC(off). This cycle is repeated twice to minimize power dissipation in external components during。

LTC3201EMS;LTC3201EMS#PBF;LTC3201EMS#TR;LTC3201EMS#TRPBF;中文规格书,Datasheet资料

I OUT = 100mAI IN = 205mAV IN = 3.6V1/LTC320123201fABSOLUTE AXI U RATI GSW W WU PACKAGE/ORDER I FOR ATIOUUW (Note 1)ELECTRICAL CHARACTERISTICSThe q denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V IN = 3.6V, C FILTER = C FLY = 0.22µF, C IN = C OUT = 1µF,t MIN to t MAX unless otherwise noted.V IN , V FILTER , V OUT , CP, CM to GND..............–0.3V to 6V D0, D1, D2, FB to GND .................–0.3V to (V IN + 0.3V)V OUT Short-Circuit Duration.............................Indefinite I OUT ......................................................................................150mA Operating Temperature Range (Note 2)...–40°C to 85°C Storage Temperature Range.................–65°C to 150°C Lead Temperature (Soldering, 10 sec)..................300°CORDER PART NUMBER MS PART MARKING T JMAX = 150°CθJA = 130°C/W (1 LAYER BOARD)θJA = 100°C/W (4 LAYER BOARD)Consult LTC Marketing for parts specified with wider operating temperature ranges.LTC3201EMS PARAMETER CONDITIONSMIN TYP MAX UNITSV IN Operating Voltage q2.74.5V V IN Operating Current I OUT = 0mAq 4 6.5mA V IN Shutdown Current D0, D1, D2 = 0V, V OUT = 0V q1µA Open-Loop Output Impedance I OUT = 100mA 8ΩInput Current Ripple I IN = 200mA30mA P-P Output Ripple I OUT = 100mA, C OUT = 1µF 30mV P-PV FB Regulation Voltage D0 = D1 = D2 = V INq 0.570.630.66V V FB DAC Step Size 90mV Switching Frequency Oscillator Free Running1.4 1.8MHzD0 to D2 Input Threshold q 0.4 1.1V D0 to D2 Input Current q–11µA V OUT Short-Circuit Current V OUT = 0V 150mA V OUT Turn-On TimeI OUT = 0mA1msLTVB12345V OUT CP FILTER CM GND109876FB V IN D2D1D0TOP VIEWMS PACKAGE10-LEAD PLASTIC MSOP Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.Note 2: The LTC3201E is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the –40°C to 85°C operatingtemperature range are assured by design, characterization and correlation with statistical process controls./3 /4/LTC320153201fAPPLICATIO S I FOR ATIOW UUU Operation (Refer to Simplified Block Diagram)The LTC3201 is a switched capacitor boost charge pump especially designed to drive white LEDs in backlighting applications. The LTC3201’s internal regulation loop maintains constant LED output current by monitoring the voltage at the FB pin. The device has a novel internal filter that, along with an external 0.22µF capacitor, significantly reduces input current ripple. An internal 7-state DAC allows the user to lower the regulation voltage at the FB pin, thus lowering the LED current. To regulate the output current, the user places a sense resistor between FB and GND. The white LED is then placed between V OUT and FB.The value at the FB pin is then compared to the output of the DAC. The charge pump output voltage is then changed to equalize the DAC output and the FB pin. The value of the sense resistor determines the maximum value of the output current.When the charge pump is enabled, a two-phase nonoverlapping clock activates the charge pump switches.The flying capacitor is charged to V IN on phase one of the clock. On phase two of the clock, it is stacked in series with V IN and connected to V OUT . This sequence of charging and discharging the flying capacitor continues at a free run-ning frequency of 1.8MHz (typ) until the FB pin voltage reaches the value of the DAC.In shutdown mode all circuitry is turned off and the LTC3201 draws only leakage current (<1µA) from the V IN supply. Furthermore, V OUT is disconnected from V IN . The LTC3201 is in shutdown when a logic low is applied to all three D0:D2 pins. Note that if V OUT floats to >1.5V,shutdown current will increase to 10µA max. In normal operation, the quiescent supply current of the LTC3201will be slightly higher if any of the D0:D2 pins is driven high with a signal that is below V IN than if it is driven all the way to V IN . Since the D0:D2 pins are high impedance CMOS inputs, they should never be allowed to float.Input Current RippleThe LTC3201 is designed to minimize the current ripple at V IN . Typical charge pump boost converters draw large amounts of current from V IN during both phase 1 and phase 2 of the clocking. If there is a large nonoverlap time between the two phases, the current being drawn from V INcan go down to zero during this time. At the full load of 100mA at the output, this means that the input could potentially go from 200mA down to 0mA during the nonoverlap time. The LTC3201 mitigates this problem by minimizing the nonoverlap time, using a high (1.8MHz)frequency clock, and employing a novel noise FILTER network. The noise filter consists of internal circuitry plus external capacitors at the FILTER and V IN pins. The filter capacitor serves to cancel the higher frequency compo-nents of the noise, while the V IN capacitor cancels out the lower frequency components. The recommended values are 0.22µF for the FILTER capacitor and 1µF for the V IN capacitor. Note that these capacitors must be of the highest possible resonant frequencies. See Layout Considerations.3-Bit DAC for Output Current ControlDigital pins D0, D1, D2 are used to control the output current level. D0 = D1 = D2 = V IN allows the user to program an output LED current that is equal to 0.63V/R SENSE , where R SENSE is the resistor connected to any single LED and connected between FB and ground. Due to the finite transconductance of the regulation loop, for a given diode setting, the voltage at the FB Pin will decrease as output current increases. All LEDs subsequently connected in parallel should then have similar currents. The mismatch-ing of the LED V F and the mismatching of the sense resistors will cause a differential current error between LEDs connected to the same output. Once the sense resistor is selected, the user can then control the voltage applied across that resistor by changing the digital values at D0:D2. This in turn controls the current into the LED.Note that there are only 7 available current states. The 8th is reserved to shutdown. This is the all 0s code. Refer to Table below.D0D1D2FB HIGH HIGH HIGH 0.63V HIGH HIGH LOW 0.54V HIGH LOW HIGH 0.45V HIGH LOW LOW 0.36V LOW HIGH HIGH 0.27V LOW HIGH LOW 0.18V LOW LOW HIGH 0.09V LOWLOWLOWShutdown/LTC320163201fPower EfficiencyThe power efficiency (η) of the LTC3201 is similar to that of a linear regulator with an effective input voltage of twice the actual input voltage. This occurs because the input current for a voltage doubling charge pump is approxi-mately twice the output current. In an ideal regulator the power efficiency would be given by:η===P P V I V I V V OUT IN OUT OUT IN OUTOUTIN ••22At moderate to high output power the switching lossesand quiescent current of LTC3201 are relatively low. Due to the high clocking frequency, however, the current used for charging and discharging the switches starts to reduce efficiency. Furthermore, due to the low V F of the LEDs,power delivered will remain low.Short-Circuit/Thermal ProtectionThe LTC3201 has short-circuit current limiting as well as overtemperature protection. During short-circuit condi-tions, the output current is limited to typically 150mA.On-chip thermal shutdown circuitry disables the charge pump once the junction temperature exceeds approxi-mately 160°C and re-enables the charge pump once the junction temperature drops back to approximately 150°C.The LTC3201 will cycle in and out of thermal shutdown indefinitely without latchup or damage until the short-circuit on V OUT is removed.V OUT Capacitor SelectionThe style and value of capacitors used with the LTC3201determine several important parameters such as output ripple, charge pump strength and minimum start-up time.To reduce noise and ripple, it is recommended that low ESR (<0.1Ω) capacitors be used for C FILTER , C IN , C OUT .These capacitors should be ceramic.The value of C OUT controls the amount of output ripple.Increasing the size of C OUT to 10µF or greater will reduce the output ripple at the expense of higher turn-on times and start-up current. See the section Output Ripple. A 1µF C OUT is recommended.V IN , V FILTER Capacitor SelectionThe value and resonant frequency of C FILTER and C IN greatly determine the current noise profile at V IN . C FILTER should be a high frequency 0.22µF capacitor with a reso-nant frequency over 30MHz. Input capacitor C IN should be a 1µF ceramic capacitor with a resonant frequency over 1MHz. The X5R capacitor is a good choice for both. The values of C FILTER (0.22µF) and C IN (1µF) provide optimum high and low frequency input current filtering. A higher filter cap value will result in lower low frequency input current ripple, but with increased high frequency ripple.The key at the FILTER node is that the capacitor has to be very high frequency. If capacitor technology improves the bandwidth, then higher values should be used. Similarly,increasing the input capacitor value but decreasing its resonant frequency will not really help. Decreasing it will help the high frequency performance while increasing the low frequency current ripple.Direct Connection to BatteryDue to the ultra low input current ripple, it is possible to connect the LTC3201 directly to the battery without using regulators or high frequency chokes.Flying Capacitor SelectionWarning: A polarized capacitor such as tantalum or alumi-num should never be used for the flying capacitor since its voltage can reverse upon start-up. Low ESR ceramic capacitors should always be used for the flying capacitor.The flying capacitor controls the strength of the charge pump. In order to achieve the rated output current it is necessary to have at least 0.22µF of capacitance for the flying capacitor. Capacitors of different materials lose their capacitance with higher temperature and voltage at different rates. For example, a ceramic capacitor made of X7R material will retain most of its capacitance from –40°C to 85°C whereas a Z5U and Y5V style capacitor will lose considerable capacitance over that range. Z5U and Y5V capacitors may also have a very strong voltage coefficient causing them to lose 60% or more of their capacitance when the rated voltage is applied. Therefore,when comparing different capacitors it is often moreAPPLICATIO S I FOR ATIOW UUU /LTC320173201fappropriate to compare the achievable capacitance for a given case size rather than discussing the specified ca-pacitance value. For example, over the rated voltage and temperature, a 1µF, 10V, Y5V ceramic capacitor in an 0603case may not provide any more capacitance than a 0.22µF 10V X7R available in the same 0603 case. The capacitor manufacturer’s data sheet should be consulted to deter-mine what value of capacitor is needed to ensure 0.22µF at all temperatures and voltages.Below is a list of ceramic capacitor manufacturers and how to contact them:AVX (843) Kemet (864) Murata (770) Taiyo Yuden (800) Vishay(610) 644-1300Open-Loop Output ImpedanceThe theoretical minimum open-loop output impedance of a voltage doubling charge pump is given by:R V V I FCOUT MIN IN OUT OUT ()–==21where F if the switching frequency (1.8MHz typ) and C isthe value of the flying capacitor. (Using units of MHz and µF is convenient since they cancel each other). Note that the charge pump will typically be weaker than the theoreti-cal limit due to additional switch resistance. Under normal operation, however, with V OUT ≈ 4V, I OUT < 100mA,V IN > 3V, the output impedance is given by the closed-loop value of ~0.5Ω.Output RippleThe value of C OUT directly controls the amount of ripple for a given load current. Increasing the size of C OUT will reduce the output ripple at the expense of higher minimum turn-on time and higher start-up current. The peak-to-peak output ripple is approximated by the expression:V I F C RIPPLE P P OUT OUT()•−≅2 F is the switching frequency (1.8MHz typ).Loop StabilityBoth the style and the value of C OUT can affect the stability of the LTC3201. The device uses a closed loop to adjust the strength of the charge pump to match the required output current. The error signal of this loop is directly stored on the output capacitor. The output capacitor also serves to form the dominant pole of the loop. To prevent ringing or instability, it is important for the output capaci-tor to maintain at least 0.47µF over all ambient and operating conditions.Excessive ESR on the output capacitor will degrade the loop stability of the LTC3201. The closed loop DC imped-ance is nominally 0.5Ω. The output will thus change by 50mV with a 100mA load. Output capacitors with ESR of 0.3Ω or greater could cause instability or poor transient response. To avoid these problems, ceramic capacitors should be used. A tight board layout with good ground plane is also recommended.Soft-StartThe LTC3201 has built-in soft-start circuitry to prevent excessive input current flow at V IN during start-up. The soft-start time is programmed at approximately 30µyout ConsiderationsDue to the high switching frequency and large transient currents produced by the LTC3201, careful board layout is necessary. A true ground plane is a must. To minimize high frequency input noise ripple, it is especially important that the filter capacitor be placed with the shortest dis-tance to the LTC3201 (1/8 inch or less). The filter capacitor should have the highest possible resonant frequency.Conversely, the input capacitor does not need to be placed close to the pin. The input capacitor serves to cancel out the lower frequency input noise ripple. Extra inductance on the V IN line actually helps input current ripple. Note that if the V IN trace is lengthened to add parasitic inductance,it starts to look like an antenna and worsen the radiated noise. It is recommended that the filter capacitor be placed on the left hand side next to Pin 3. The flying capacitor can then be placed on the top of the device. It is also importantAPPLICATIO S I FOR ATIOW UUU Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights./8Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 qFAX: (408) 434-0507 q © LINEAR TECHNOLOGY CORPORA TION 2001/分销商库存信息:LINEAR-TECHNOLOGYLTC3201EMS LTC3201EMS#PBF LTC3201EMS#TR LTC3201EMS#TRPBF。

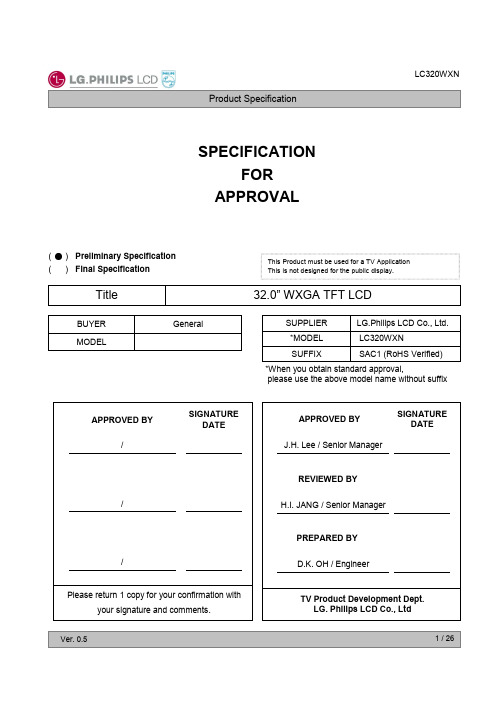

LC320WXN

FOR APPROVALSPECIFICATION32.0”WXGA TFT LCDTitleMODELGeneralBUYER *When you obtain standard approval,please use the above model name without suffixLC320WXN*MODEL SAC1 (RoHS Verified)SUFFIXLG.Philips LCD Co., Ltd.SUPPLIER ))((Final SpecificationPreliminary Specification ●Please return 1 copy for your confirmation withyour signature and comments.///SIGNATUREDATEAPPROVED BYThis Product must be used for a TV ApplicationThis is not designed for the public display.TV Product Development Dept.LG. Philips LCD Co., LtdD.K. OH / EngineerH.I. JANG / Senior ManagerJ.H. Lee / Senior ManagerSIGNATUREDATEREVIEWED BYPREPARED BYAPPROVED BYRECORD OF REVISIONS1. General DescriptionThe LC320WXN is a Color Active Matrix Liquid Crystal Display with an integral External Electrode Fluorescent Lamp(EEFL) backlight system. The matrix employs a-Si Thin Film Transistor as the active element. It is a transmissive type display operating in the normally black mode. It has a 31.51 inch diagonally measured active display area with W XGA resolution (768 vertical by 1366 horizontal pixel array). Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes. Gray scale or the luminance of the sub-pixel color is determined with a 8-bit gray scale signal for each dot, thus presenting a palette of more than 16.7M(true) colors.It has been designed to apply the 8-bit 1-port LVDS interface.It is intended to support LCD TV, PCTV where high brightness, super wide viewing angle, high color gamut, high color depth and fast response time are important.The following items are maximum values which, if exceeded, may cause faulty operation or damage to the LCD module.Table 1. ABSOLUTE MAXIMUM RATINGS2. Absolute Maximum RatingsNotes : 1. Temperature and relative humidity range are shown in the figure below.Wet bulb temperature should be 39 °C Max. and no condensation of water.2. Gravity mura can be guaranteed under 40℃condition.90%1020304050607080-2001020304050Dry Bulb Temperature [°C ]Wet BulbTemperature [°C ]StorageOperationH u m i d i t y [(%)R H ]10%40%60%60It requires two power inputs. One is employed to power for the LCD circuit. The other Is used for the EEFL backlight and inverter circuit.3. Electrical Specifications3-1. Electrical CharacteristicsNotes : 1. The specified current and power consumption are under the V LCD=12.0V, 25 ±2°C, f V =60Hzcondition whereas mosaic pattern(8 x 6) is displayed and f V is the frame frequency.2. The current is specified at full white pattern.3. The duration of rush current is about 2ms and rising time of power input is 1ms (min.).Mosaic Pattern(8 x 6)White : 255 GrayBlack : 0 GrayFull White patternWhite : 255 GrayTable 3. ELECTRICAL CHARACTERISTICS (Continue)Notes :1. Electrical characteristics are determined after the unit has been ‘ON’and stable for approximately 120minutes at 25±2°C. The specified current and power consumption are under the typical supply Input voltage 24Vand V BR(V BR-A: 1.65V & V BR-B :3.3V), it is total power consumption.The ripple voltage of the power supply input voltage is under 0.5 Vp-p. LPL recommend Input Voltage is24.0V ±5%.2. Electrical characteristics are determined within 30 minutes at 25±2°C.The specified currents are under the typical supply Input voltage 24V.3. The brightness of the lamp after lighted for 5minutes is defined as 100%.TS is the time required for the brightness of the center of the lamp to be not less than 95% at typical current.The screen of LCD module may be partially dark by the time the brightness of lamp is stable after turn on.4. Specified Values are for a single lamp which is aligned horizontally.The life time is determined as the time which luminance of the lamp is 50% compared to that of initial value at the typical lamp current (V BR-A : 1.65V & V BR-B:3.3V), on condition of continuous operating at 25±2°C 5. The duration of rush current is about 20 ms.This LCD module employs two kinds of interface connection, a 30-pin connector is used for the module electronics and One connectors(14-pin) are used for the integral backlight system. 3-2-1. LCD Module3-2. Interface ConnectionsTable 4. MODULE CONNECTOR(CN1) PIN CONFIGURATION-LCD Connector(CN1) : FI-X30SSL-HF (Manufactured by JAE) or Equivalent -Mating Connector : FI-X30C2L (Manufactured by JAE) or Equivalent 2Dynamic CR Enable ( ‘L ’= Disable , ‘H ’= Enable )DCR Enable 10LVDS Receiver Signal(+)RD+25LVDS Receiver Signal(-)RD-24GroundGND 23LVDS Receiver Clock Signal(+)RCLK+22LVDS Receiver Clock Signal(-)RCLK-21LVDS Receiver Signal(-)RB-15GroundGND 14LVDS Receiver Signal(+)RA+13LVDS Receiver Signal(-)RA-12GroundGND 11External VBR input from System to LCD module VBR_EXT 28Low : Normal Operating High : Interlace Free Mode Reserved 293GroundGND30Power Supply +12.0V VLCD 2Power Supply +12.0V VLCD 3Power Supply +12.0V VLCD 4Ground GND 5Ground GND 6Ground GND 7GroundGND 71Select LVDS Data formatSelect 9LVDS Receiver Signal(+)RB+16GroundGND 17LVDS Receiver Signal(-)RC-18LVDS Receiver Signal(+)RC+19GroundGND 20GroundGND 26VBR output form LCD moduleVBR_OUT 27NoteDescriptionSymbol Pin No.VLCD Power Supply +12.0V 1Notes: 1. The pin no 9 is an option pin for DISM or LG format. (VESA Format = “GND”/ JEIDA Format =“VCC”)Please refer to Appendix for further details.2. The pin no 10 is an option pin for DCR Function (Enable = “VCC”/ Disable =“GND”)3. The pin no 30 is LCD Test option.LCM operates “AGP”(Auto Generation Pattern) or “NSB”(No Signal Black) is case that LVDS signals are out of frequency or abnormal condition in spite of 12 volt power supply. LPL recommends “NSB”. ( AGP : “VCC”or “OPEN”/ NSB : “GND”)4. All GND (ground) pins should be connected together, which should be also connected to the LCD module’s metal frame.5. All V LCD (power input) pins should be connected together.6. Input Levels of LVDS signals are based on the IEA 664 Standard.Master-Inverter Connector : 20022WR-14B1(manufactured by Yeon-Ho)or Equivalent-Mating Connector : PHR-14 or EquivalentTable 7. INVERTER CONNECTOR PIN CONFIGULATION 3-2-2. Backlight Inverter2, 3V BR-A Analog dimming voltageDC 0.0V ~ 3.3V (Typ : 1.65V)V BR-A 11On/Off 0.0V ~ 5.0VV ON/OFF 124StatusNormal : Upper 3.0V Abnormal : Under 0.7VStatus14V BR -B GND GND GND GND GND V BL V BL V BL V BL V BL Master3Backlight GroundGND 7Backlight GroundGND 81Burst dimming voltage DC 0.0V ~ 3.3V V BR -B 13Backlight GroundGND 10Backlight Ground GND 9Backlight Ground GND 6Power Supply +24.0VV BL 5Power Supply +24.0V V BL 4Power Supply +24.0V V BL 3Power Supply +24.0V V BL 2Power Supply +24.0V V BL 1NoteDescriptionSymbolPin No ◆Rear view of LCMPCBNotes : 1. GND should be connected to the LCD module’s metal frame.2. If Pin #11 is open, V BR -A = 1.65V. When apply over 1.65V( ~3.3V) continuously, its luminance is increasing however lamp’s life time is decreasing.It could be usable for boost up luminance when using DCR (=Dynamic contrast ratio) function only.3. Minimum Brightness : V BR -B =0V Maximum Brightness : V BR -B = 3.3V4. Even though Pin #14 is open, there is no effect on inverter operating, The output terminal of inverter.5. Each impedance of pin #11,12 and 13 is 147[㏀], 38[㏀], 118[㏀]Table 6 shows the signal timing required at the input of the LVDS transmitter. All of the interface signal timings should be satisfied with the following specification for normal operation.3-3. Signal Timing SpecificationsNote :1. The performance of the electro-optical characteristics may be influenced by variance of the vertical refresh rate.2. Above Timing Tables are only valid for DE Mode.Table 6. TIMING TABLE for NTSC &PAL[ DE (Data Enable) Only ]3-4. Signal Timing Waveforms* Reference : Sync. Relation* t HB = t HFP + t WH +t HBP * t VB = t VFP + t WV +t VBP0.7VDD0.3VDDDE, Data3-5. Color Data ReferenceThe brightness of each primary color(red,green,blue) is based on the 8-bit gray scale data input for the color. The higher binary input, the brighter the color. Table 7 provides a reference for color versus data input.3-6. Power Sequence3-6-1. LCD Driving circuitNote : 1. Please avoid floating state of interface signal at invalid period.2. When the interface signal is invalid, be sure to pull down the power supply V LCD to 0V.3. The case when the T2/T5 exceed 3x(1/fv), it operates protection pattern (Black pattern) till valid signal inputted. There is no reliability problem. (ex. 60Hz : 3x(1/60Hz) = 50ms)4. The T3/T4 is recommended value, the case when failed to meet a minimum specification, abnormal display would be shown. There is no reliability problem.5. If the on time of signals(Interface signal and Option signals) precedes the on time of Power(V LCD ),check the LCD logic Power(Vcc) is under 0.8V, otherwise it will be happened abnormal display.6. T6 should be measured after the Module has been fully discharged between power off and on period.T5T2--552,63,5443,5Notess --2.0T6msT8ms 0T7ms 3 x (1/f V )-0.5T2ms ms --200T3--200T4ms --0T5ms 20-0.5T1Max Typ Min Unit ValueParameterTable 9. POWER SEQUENCEInterface Signal (Tx)Power for LampPower Supply For LCD VLCD0VOption SignalNote : 1. T1 describes rising time of 0V to 24V and this parameter does not applied at restarting time2. T4(max) is less than T2.3. In T7 section, V BR -B should be max level(3.3V) and V BR -A should be 1.65V.3-6-2. Sequence for InverterPower Supply For InverterV ON/OFFV BL0VTable 12. Power Sequence for Inverter3-6-3. Deep condition for InverterV BL (Typ.) x 0.80 VBL : 24VV BL (Typ) x 0.8ms 10--T63ms--1000T7-ms --10T52ms 0T41Remarksms --500T2ms --200T3ms --20T1Max Typ Min Units ValuesParameterV BR-A & V BR-BTable 10. OPTICAL CHARACTERISTICSLCD ModuleOptical Stage(x,y)Pritchard 880 orequivalentFIG. 1 Optical Characteristic Measurement Equipment and Method4. Optical SpecificationOptical characteristics are determined after the unit has been ‘ON’and for 30 minutes in a dark environment at 25±2°C. The values are specified at an approximate distance 50cm from the LCD surface at a viewing angle of Φand θequal to 0 °.FIG. 1 shows additional information concerning the measurement equipment and method.Table 11. GRAY SCALE SPECIFICATION10088.075.864.153.343.935.428.021.616.712.18.104.902.601.100.320.10Luminance [%] (Typ.)L239L255L159L175L191L207L111L127L143L223L47L63L79L95L31L15L0Gray LevelNotes :1. Contrast Ratio(CR) is defined mathematically as :CR(Contrast Ratio) = Maximum CRn (n=1, 2, 3, 4, 5)Surface Luminance at position n with all white pixelsCRn =Surface Luminance at position n with all black pixelsn = the Position number(1, 2, 3, 4, 5). For more information, see FIG 2.2. Surface luminance are determined after the unit has been ‘ON’and 30min after lighting the backlight in a dark environment at 25±2°C. Surface luminance is the luminance value at center 1-point across the LCD surface 50cm from the surface with all pixels displaying white.For more information see the FIG. 2.3. The variation in surface luminance , δWHITE is defined as :δWHITE(5P) = Maximum(L on1,L on2, L on3, L on4, L on5) / Minimum(L on1,L on2, L on3, L on4, L on5)Where L on1to L on5are the luminance with all pixels displaying white at 5 locations . For more information, see the FIG. 2.4. Response time is the time required for the display to transition from G(N) to G(M) (Rise Time, Tr R ) and from G(M) to G(N) (Decay Time, Tr D ). For additional information see the FIG. 3. (N<M)5. Viewing angle is the angle at which the contrast ratio is greater than 10. The angles are determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD module surface. For more information, see the FIG. 4.6. Gray scale specificationGamma Value is approximately 2.2. For more information, see the Table 11.FIG. 3 Response TimeResponse time is defined as the following figure and shall be measured by switching the input signal for “Gray(N)”and “Gray(M)”.Measuring point for surface luminance & measuring point for luminance variation.FIG. 2 5 Points for Luminance Measure10090100Optical ResponseA : H / 4 mmB : V / 4 mmH : 697.685mm V : 392.256mm@ H,V : Active AreaDimension of viewing angle rangeFIG. 4 Viewing Angle5. Mechanical CharacteristicsTable 12 provides general mechanical characteristics.Table 12. MECHANICAL CHARACTERISTICSNote : 1.Please refer to a mechanic drawing in terms of tolerance at the next page.<FRONT VIEW><REAR VIEW>Notes : It should be recommended that any exterior materials do not go passing up the red area slanted.( For example, electrical cable, system board , etc ). Otherwise, it could cause that abnormaldisplay happens.6. ReliabilityTable 13. ENVIRONMENT TEST CONDITIONNote : Before and after Reliability test, LCM should be operated with normal function.7. International Standards7-1. Safetya) UL 60065, 7th Edition, dated June 30, 2003, Underwriters Laboratories, Inc.,Standard for Audio, Video and Similar Electronic Apparatus.b) CAN/CSA C22.2, No. 60065:03, Canadian Standards Association,Standard for Audio, Video and Similar Electronic Apparatus.c) IEC60065:2001, 7th Edition CB-scheme and EN 60065:2002,Safety requirements for Audio, Video and Similar Electronic Apparatus..7-2. EMCa) ANSI C63.4 “Methods of Measurement of Radio-Noise Emissions from Low-Voltage Electrical andElectrical Equipment in the Range of 9kHZ to 40GHz. “American National Standards Institute(ANSI), 1992b) CISPR13 "Limits and Methods of Measurement of Radio interference characteristics of Soundand Television broadcast receivers and associated equipment"CISPR22 "Limits and Methods of Measurement of Radio interference characteristics of Information Technology Equipment" International Special Committee on Radio Interference.c) EN55013 "Limits and Methods of Measurement of Radio interference characteristics of Sound andTelevision broadcast receivers and associated equipment"EN55022 "Limits and Methods of Measurement of Radio interference characteristics of Information Technology Equipment" European Committee for Electro Technical Standardization.(CENELEC), 1988(Including A1:2000)8-1. Designation of Lot Marka) Lot MarkA B C D E F G H I J K L MA,B,C : SIZE(INCH) D : YEARE : MONTHF ~ M : SERIAL NO.Note1. YEAR2. MONTHMarkYear 02010620067200782008920094200452005321200320022001BNov MarkMonth AOct 6Jun 7Jul 8Aug 9Sep 4Apr 5May C321Dec Mar Feb Jan b) Location of Lot MarkSerial No. is printed on the label. The label is attached to the backside of the LCD module.This is subject to change without prior notice.8. Packing8-2. Packing Forma) LCM quantity in one pallet : 12 pcs b) Pallet Size : 1030mm X 870mm X 740mm9. PrecautionsPlease pay attention to the followings when you use this TFT LCD module.9-1. Mounting Precautions(1)You must mount a module using specified mounting holes (Details refer to the drawings).(2) You should consider the mounting structure so that uneven force (ex. Twisted stress) is not applied to themodule. And the case on which a module is mounted should have sufficient strength so that external force is not transmitted directly to the module.(3) Please attach the surface transparent protective plate to the surface in order to protect the polarizer.Transparent protective plate should have sufficient strength in order to the resist external force.(4) You should adopt radiation structure to satisfy the temperature specification.(5) Acetic acid type and chlorine type materials for the cover case are not desirable because the formergenerates corrosive gas of attacking the polarizer at high temperature and the latter causes circuit break by electro-chemical reaction.(6) Do not touch, push or rub the exposed polarizers with glass,tweezers or anything harder than HBpencil lead. And please do not rub with dust clothes with chemical treatment.Do not touch the surface of polarizer for bare hand or greasy cloth.(Some cosmetics are detrimental to the polarizer.)(7) When the surface becomes dusty, please wipe gently with absorbent cotton or other soft materials likechamois soaks with petroleum benzine. Normal-hexane is recommended for cleaning the adhesives used to attach front / rear polarizers. Do not use acetone, toluene and alcohol because they cause chemical damage to the polarizer. * Panel push force can be guaranteed under 5kgf / φ10mm(8) Wipe off saliva or water drops as soon as possible. Their long time contact with polarizer causesdeformations and color fading.(9) Do not open the case because inside circuits do not have sufficient strength.9-2. Operating Precautions(1) The spike noise causes the mis-operation of circuits. It should be lower than following voltage:V=±200mV(Over and under shoot voltage)(2) Response time depends on the temperature.(In lower temperature, it becomes longer.)(3) Brightness depends on the temperature. (In lower temperature, it becomes lower.)And in lower temperature, response time(required time that brightness is stable after turned on) becomes longer.(4) Be careful for condensation at sudden temperature change. Condensation makes damage to polarizer orelectrical contacted parts. And after fading condensation, smear or spot will occur.(5) When fixed patterns are displayed for a long time, remnant image is likely to occur.(6) Module has high frequency circuits. Sufficient suppression to the electromagnetic interference shall bedone by system manufacturers. Grounding and shielding methods may be important to minimized the interference.(7) Please do not give any mechanical and/or acoustical impact to LCM. Otherwise, LCM can’t be operatedits full characteristics perfectly.(8) A screw which is fastened up the steels should be a machine screw.(if not, it causes metallic foreign material and deal LCM a fatal blow)(9)Please do not set LCD on its edge.(10) It is recommended to avoid the signal cable and conductive material over the inverter transformerfor it can cause the abnormal display and temperature rising.(11) Partial darkness may happen during 3~5 minutes when LCM is operated initially in condition thatluminance is under 40% at low temperature (under 5℃). This phenomenon which disappears naturally after 3~5 minutes is not a problem about reliability but LCD characteristic.9-3. Electrostatic Discharge ControlSince a module is composed of electronic circuits, it is not strong to electrostatic discharge. Make certain that treatment persons are connected to ground through wrist band etc. And don’t touch interface pin directly.9-4. Precautions for Strong Light ExposureStrong light exposure causes degradation of polarizer and color filter.9-5. StorageWhen storing modules as spares for a long time, the following precautions are necessary.(1) Store them in a dark place. Do not expose the module to sunlight or fluorescent light. Keep the temperaturebetween 5°C and 35°C at normal humidity.(2) The polarizer surface should not come in contact with any other object.It is recommended that they be stored in the container in which they were shipped.9-6. Handling Precautions for Protection Film(1) The protection film is attached to the bezel with a small masking tape.When the protection film is peeled off, static electricity is generated between the film and polarizer.This should be peeled off slowly and carefully by people who are electrically grounded and with well ion-blown equipment or in such a condition, etc.(2) When the module with protection film attached is stored for a long time, sometimes there remains a verysmall amount of glue still on the bezel after the protection film is peeled off.(3) You can remove the glue easily. When the glue remains on the bezel surface or its vestige is recognized,please wipe them off with absorbent cotton waste or other soft material like chamois soaked with normal-hexane.# APPENDIX-I-1■Required signal assignment for Flat Link (DS90C385) Transmitter(Pin9=“L”)Notes:1. The LCD module uses a 100 Ohm(Ω) resistor between positive and negative linesof each receiver input.2. Refer to LVDS transmitter data sheet for detail descriptions. (THC63LVD823 or Compatible)3. ‘7’means MSB and ‘0’means LSB at R,G,B pixel data.# APPENDIX-I-2■Required signal assignment for Flat Link (DS90C385) Transmitter(Pin9=“H”)Notes:1. The LCD module uses a 100 Ohm(Ω) resistor between positive and negative linesof each receiver input.2. Refer to LVDS transmitter data sheet for detail descriptions. (THC63LVD823 or Compatible)3. ‘7’means MSB and ‘0’means LSB at R,G,B pixel data.# APPENDIX-Ⅱ-1■LC320WXN—SAC1 Packing Ass’yPAPER_DW3BOX 6OPP 70MMX300M TAPE 7YUPO PAPER 100X100LABEL8EPS PACKING, TOP R_L5EPS PACKING, BOTTOM 4MASKING 20MM X 50MTAPE3ALBAG 2LCD MODULE1MATERIALDESCRIPTION NO.# APPENDIX-Ⅱ-2■LC320WXN-SAC1 Pallet Ass’yPAPERLABEL6PAPER (DW3)ANGLE, Cover5STEEL CLIP, BAND 4PP BAND 3PlywoodPALLET 2PACKING ASS’Y1MATERIALDESCRIPTIONNO.Box quantity per pallet: 2eaPallet size: L1030 x W870 x H740 Pallet gross weight: 113.0kgLC320WXN■LCM Label■Serial No. (See CAS 26page for more information)InchM Ass’y Factory codeSerial No.MonthYear ModelSerial No.UL, TUV MarkLPL LogoUS PATENT No .# # APPENDIX-III-2■Box Label■Pallet Label# APPENDIX-IV■Option Pin Circuit Block DiagramCircuit Block Diagram of LVDS Format Selection pin。

IC datasheet pdf-REF3012,REF3020,REF3025,REF3033,REF3040,REF3030,pdf(50ppm_°C Max, 50μA in SOT23-3

VOLTAGE (V) 1.25 2.048 2.5 3.0 3.3 4.096

DROPOUT VOLTAGE vs LOAD CURRENT 350

IN 1 REF3012 REF3020 REF3025 REF3030 REF3033 REF3040 SOT23-3

300

Dropout Voltage (mV)

REF3012 REF3020 REF3025 REF3030 REF3033 REF3040

SBVS032F – MARCH 2002 – REVISED AUGUST 2008

50ppm/°C Max, 50µA in SOT23-3 CMOS VOLTAGE REFERENCE

"

R30F

"

REF3033

"

SOT23-3

"

DBZ

"

–40°C to +125°C

"

R30D

"

REF3040

"

SOT23-3

"

DBZ

"

–40°C to +125°C

"

R30E

"

"

"

"

"

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at .

ELECTRICAL CHARACTERISTICS

ccs附录

附录一DES5402PP-U性能介绍★基本配置:1.使用100MIPS的TMS320VC5402,片上有16K Words的存储器,外部扩展32K字的数据存储器,外部扩展64K字的程序存储器。

2.使用TLC320AC01作为模拟接口(AIC)电路,提供A/D和D/A各1个通道(14 bit),最高采样率为25K Sa/s。

2.预留32K字的EPROM插座,方便完成各种代码装入(BOOTLOADER)实验。

也可使该实验设备脱机独立运行。

3.外部主机(PC机)可以通过并口与DSP的HPI接口通讯,直接访问DSP片内存储器。

也可通过HPI接口实现代码装入(BOOTLOADER)功能。

4.丰富的I/O外设,如汉字液晶显示屏,键盘,交通灯,数码管,UART异步串口等。

5.多种模拟信号接口,如麦克风和扬声器接口,普通模拟信号输入/输出接口,电话线接口等。

6.DES5402PP-U预留1个DSP同步串口(McBSP),1组数据、地址以及控制外部扩展总线,保留DSP各种状态显示以及设置开关,方便学生实验。

7.提供直流电机、步进电机驱动电路,方便完成各种电机驱动实验。

8.提供5V,-5V,3.3V,1.8V各种电压输出。

★XDS510仿真调试器DES5402PP-U实验系统板上集成嵌入式JTAG控制电路,无需外部仿真器便可直接使用CCS等调试工具。

同时该实验设备还提供并口型XDS510仿真器功能,全面支持‘C2000,‘C5000,‘C6000,‘VC33各个系列DSP,并全面兼容CCS 2.0。

本实验系统同时具有EVM 评估板和XDS510仿真器两种功能,真正实现一板多用。

★可扩展的接口DES5402PP-U实验仪提供了多个外部扩展接口,方便学生自己动手制作外围接口电路,增强该DSP实验设备的应用范围。

1.通用数据扩展总线:该扩展总线包括16根数据线、4根地址线、1根片选信号线、1根读写信号线、2根通用数字I/O。

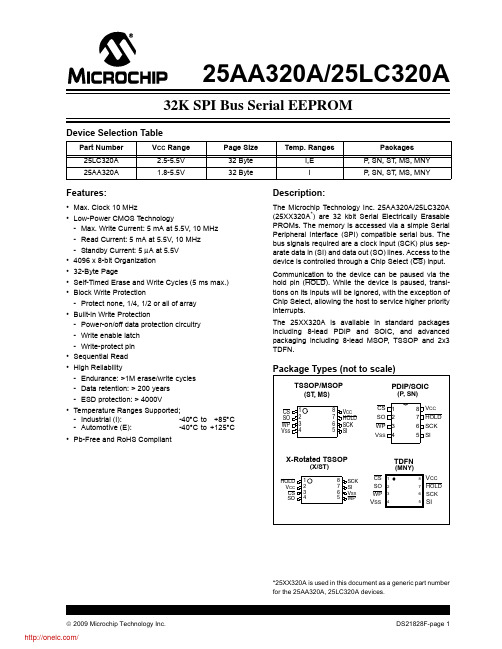

25AA320AT-IMNY;25AA320A-ISN;25LC320A-ISN;25LC320A-IST;25LC320A-IMS;中文规格书,Datasheet资料

TSSOP/MSOP (ST, MS)

CS 1 SO 7 HOLD 6 SCK 5 SI

PDIP/SOIC

(P, SN)

CS 1 SO 2 WP 3 VSS 4

8 VCC 7 HOLD 6 SCK 5 SI

X-Rotated TSSOP (X/ST)

HOLD 1 VCC 2 CS 3 SO 4

† NOTICE: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for an extended period of time may affect device reliability.

- Standby Current: 5 μA at 5.5V

• 4096 x 8-bit Organization

• 32-Byte Page

• Self-Timed Erase and Write Cycles (5 ms max.)

• Block Write Protection

- Protect none, 1/4, 1/2 or all of array

ACD320说明书1.1版2012-6-28

序言本手册为使用者提供了选型、安装、参数设定、现场调试、故障诊断等日常维护本变频器的相关注意事项及指导。

为了确保能够正确地使用本变频器,请在装机之前,详细阅读本说明书,并请妥善保管以备后用。

初次使用:对于初次使用本产品的用户,应先认真阅读本说明书。

若对一些功能及使用性能方面有所疑惑,请咨询我公司的技术支持人员,以获得帮助。

注意事项:◆实施配线,请务必关闭电源。

◆变频器内部的电子元件对静电特别敏感,因此不可将异物置入变频器内部或触摸主电路板。

◆切断交流电源后,变频器显示面板上的指示灯未熄灭之前,表示变频器内部仍有高压,十分危险,请勿触摸内部电路及零部件。

◆务必把变频器端子正确接地。

◆U/T1、V/T2、W/T3。

本说明书适用范围:本说明书适用于本公司生产的ACD320系列通用矢量型变频器。

本手册内容如有改动,恕不另行通知。

第一章安全信息与使用注意事项 (1)1.1安全注意事项 (1)1.2使用范围 (1)1.3使用注意事项 (2)1.4报废注意事项 (3)第二章变频器的型号与规格 (4)2.1购入检查 (4)2.2变频器型号说明 (4)2.3变频器铭牌说明 (4)2.4变频器系列型号说明 (5)2.5变频器外观及部位名称说明 (7)2.6外形尺寸 (8)2.7产品技术指标及规格 (13)第三章变频器的安装及配线 (15)3.1机械安装 (15)3.2电气安装 (16)第四章变频器的运行和操作说明 (29)4.1操作面板说明 (29)4.2功能码查看、修改方法说明: (30)4.3状态参数的查看方法: (31)4.4密码设置: (31)4.5电机参数自学习(请参考功能码F1.11的详细说明) (32)第五章功能参数一览表 (33)5.1表中符号说明 (33)5.2功能参数一览表 (33)第六章功能参数详解 (46)6.1F0基本功能组 (46)6.2F1电机参数组 (54)6.3F2输入输出端子组 (58)6.4F3人机界面组 (65)6.5F4应用功能组 (68)6.6F5保护功能组 (75)6.7F6串行通讯组 (78)6.8F7高级功能组 (81)6.9F8补充功能组1 (84)6.10F9补充功能组2 (86)第七章故障对策及异常处理 (88)7.1故障现象及对策 (88)7.2常见故障及处理方法 (91)7.3故障记录查寻 (99)7.4故障复位 (100)第八章保养和维护 (101)8.1日常保养及维护 (101)8.2易损部件的检查与更换 (101)8.3变频器的保修 (101)8.4变频器的存贮 (102)第九章附录 (103)附录一ACD320系列串行通讯协议 (103)附录二制动单元及其制动电阻的选用 (115)附录三一拖一恒压供水专用变频器参数说明 (116)附录四一拖二恒压供水控制卡及一用一补(一拖二循环)供水模式举例 . 118第一章 安全信息与使用注意事项为了确保您的人身与设备的安全,请您在使用变频器之前,务必认真阅读本章内容。

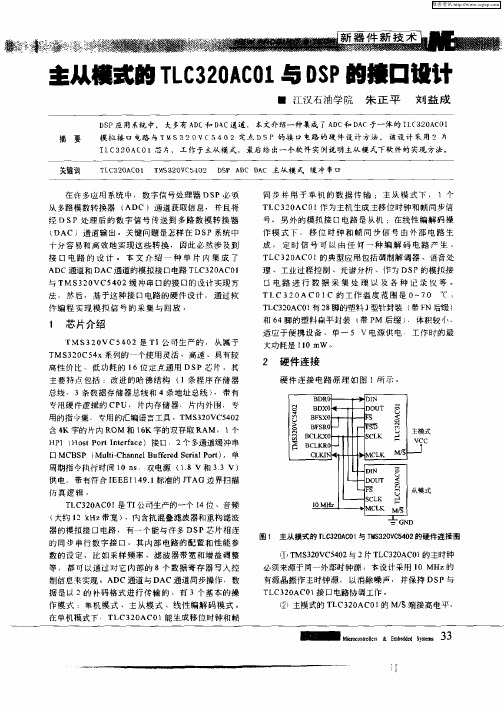

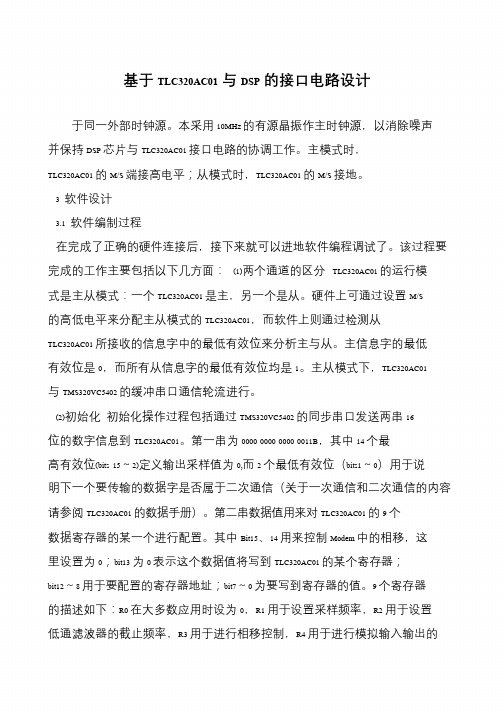

主从模式的TLC320AC01与DSP的接口设计

口 MC P ( l . h n e fee e il ot . 单 BS Mut C a n l i Bu rdS ra P r)

接 口 电路 的 设 计 。 本 文 介绍 一 种 单 片 内集 成 了 A DC通道 和 D AC通 道 的模 拟 接 口电 路 T C 2 A 0 L 30 C 1 与 T S 2 VC5 0 M 0 3 4 2缓 冲 串 口的接 口的 设计 实瑚 方

TL 3 0 C 2 AC0 1的典型应用包括调制解调 器 、语音处 理 、工业 过 程控 制 、光谱 丹析 、作 为 DS P的模 拟 接

维普资讯

圭从模式的 T C 2A O 与 D P L 3 0 C I S 的接口设计

一 江 汉石 油 学 院 朱 正 平 刘 益 成

关 键词

T C E A O T S 2 V 5 0 I P A C D C 主 从模 式 缓冲 串口 L B O C I  ̄ 3 0 C 4 2 ) D A S 同 步 并 用 于 单 机 的 数 据 传 输 j主 从 模 式 下 . 1个

据 是以 2的补码格式 进行传输 的 。有 3个基本的操 作模式 :单机模 式 、主 从模 式 、线性编解 码模式 。 在单机模 式下 .T C3 0 C0 L 2 A 1能生成移位时钟和 帧

维普资讯

新 器 件 新 技 术

从模 式 的 T 3 0 LC 2 AC0 的 M/ 1 g接地 S M # 1hI T 00, MR

RS X I M B NT S B XM S XS

TLC32040资料

TLC32040M ANALOG INTERFACE CIRCUIT

SGLS031 – MAY 1990

• • • • • • •

Advanced LinCMOS™ Silicon-Gate Process Technology 14-Bit Dynamic Range ADC and DAC Variable ADC and DAC Sampling Rate up to 19 200 Samples Per Second Switched-Capacitor Antialiasing Input Filter and Output-Reconstruction Filter Serial Port for Direct Interface to SMJ320E14, SMJ32020, SMJ320C25, and SMJ320C30 Digital Processors Synchronous or Asynchronous ADC and DAC Conversion Rates With Programmable Incremental ADC and DAC Conversion Timing Adjustments Serial Port Interface to SN54299 Serial-to-Parallel Shift Register for Parallel Interface to SMJ320C10, SMJ320C15, SMJ320E15, or Other Digital Processors

DR MSTR CLK VDD REF DGTL GND SHIFT CLK EODX

5 6 7 8 9

FSR EODR RESET NU NU NU IN+

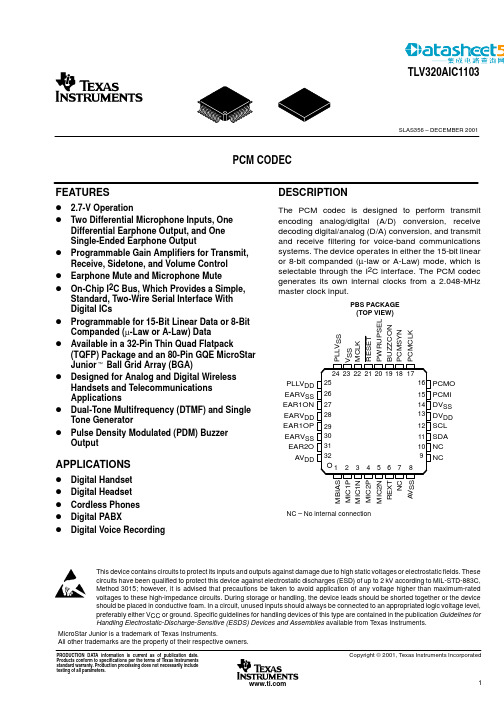

IC datasheet pdf-TLV320AIC1103,pdf(PCM Codec)

Ear Amp1

Ear Amp2 PWRUPSEL (20) VSS AV DD AVSS Power and RESET DV DD DVSS (23) (32) (8) (13) (14)

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

PBS PACKAGE (TOP VIEW)

24 23 22 21 20 19 18 17

PLLVSS VSS MCLK RESET PWRUPSEL BUZZCON PCMSYN PCMCLK PLLVDD EARVSS EAR1ON EARVDD EAR1OP EARVSS EAR2O AVDD

Digital Modulator and Filter

Buzzer Control

PLLV DD (25) PLLV SS (24)

RX Filter and PGA g = –6 dB to +6 dB

EARV DD (28) EARV SS (30, 26) RESET (21)

RX Volume Control g = –18 dB to 0 dB PLL PCM Interface Sidetone g = –24 dB to –12 dB DTMF Generator TX Filter and PGA g = –10 dB to 0 dB REXT (6) MBIAS (1) MCLK (22)

语音信号采集和播放的TLC320AD50的实现

XI N A G n ,WU i g Jn

( co l f no mt c neadE gneig Wum nvri f i c n e n l y W ua 30 1C ia Sh o o Ife i Si c n n i r , l nU iesyo ee adT c o g , h n40 8 , h ) n e n e e n t S n c h o n

语音信号 的采集 和播放是语音 信号处理 的基

础 , 基 于 D P的 语 音 处 理 系 统 中 , S 在 S D P通 过 控 制 AD芯 片采集 和播 放 语 音 信号 , / 再通 过 D P实现 各 S

种语音 处理算法 。在 1 各个系列 DP芯 片中 ,6 r I S l

位 的 C4 X因其指令 简 单 、 口连 接方 便 而 在语 音 5X 接

TLC 2 AD5 . s d o e d f r n e f p rp ea ic i a d s e c rc si g a t mei , t e wh l 30 0 Ba e n t i e e c s o i h r lcr ut n p e h p o e sn r h tc h oe h e i

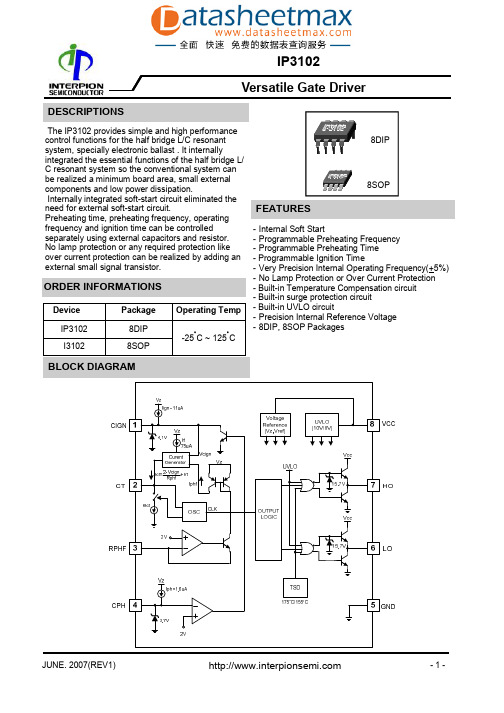

IC datasheet pdf-IP3102,pdf datasheet (Versatile Gate Driver)

PIN CONNECTIONS

PIN DESCRIPTIONS

NO 1 2 3 4 5 6 7 8 SYMBOL CIGN CT RPHF CPH GND LO HO VCC I/O I I I I O O DESCRIPTION Ignition Time Control Pin with external Capacitor Internal Oscillator Timing Control Pin with Capacitor Preheating Frequency Control Pin with external Resistor Preheating Time Control Pin with external Capacitor Ground Low Side Gate Drive Output High Side Gate Drive Output Supply Voltage

ABSOLUTE MAXIMUM RATINGS

CHARACTERISTICS Maximum Supply Voltage Maximum Operating Supply Voltage Totem-pole Output Peak Current Power Dissipation(8DIP) PIN1,2,3,4 Voltage Output Clamp Diode Current Operating Junction Temperature Storage Temperature SYMBOL VCCMAX VOPMAX IPEAK Pd VIN ICLAMP Tj Tstg VALUE 30 24 +1 800 -0.4 ~ 6 30 -25 ~ +125 -65 ~ 150 UNIT V V A mW V mA

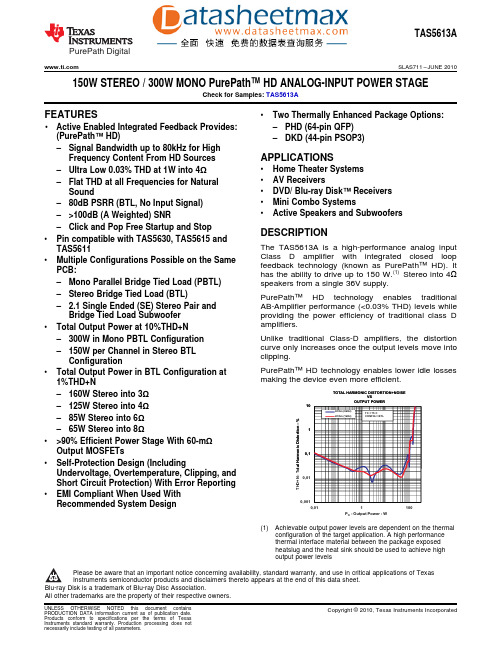

IC datasheet pdf-TAS5613,pdf(150W Stereo_300W Mono PurePath HD Analog-Input Power Stage)

•23 Active Enabled Integrated Feedback Provides: (PurePath™ HD) – Signal Bandwidth up to 80kHz for High Frequency Content From HD Sources – Ultra Low 0.03% THD at 1W into 4Ω – Flat THD at all Frequencies for Natural Sound – 80dB PSRR (BTL, No Input Signal) – >100dB (A Weighted) SNR – Click and Pop Free Startup and Stop

• EMI Compliant When Used With Recommended System Design

• Two Thermally Enhanced Package Options: – PHD (64-pin QFP) – DKD (44-pin PSOP3)

APPLICATIONS

• Home Theater Systems • AV Receivers • DVD/ Blu-ray Disk™ Receivers • Mini Combo Systems • Active Speakers and Subwoofers

PO - Output Power - W

TLC320AIC23在音频处理中的应用

TLC320AIC23在音频处理中的应用摘要介绍了高性能立体声音频编解码芯片TLV320AIC23 的基本特点、性能以及使用方法,并结合DSP芯片TMS 3 2 0 VC5 5 0 9与音频CODEC芯片TLV320AIC23的接口设计,详细阐述了如何通过I2C总线对TLV320AIC23进行初始化设置的过程以及如何根据TLV320AIC23的特点对DSP的串口进行设计等一系列问题。

关键词DSP 音频处理编解码1TLV320AIC23芯片简介TLV320AIC23是TI公司生产的一种高性能立体声音频编解码器该芯片同时高度集成了模拟电路功能。

TLV320AIC23中的模数与数模转换器使用了多比特si gma-deltaX艺,并在内部集成了高采样率的数字内插滤波器。

该器件的数字传输字长可以是16、20、24、32Eit,它支持8〜9 6kHz的采样率。

模数转换器的sigma-delta调制器决定了其三阶多比特结构,这种结构在采样率为9 6kHz的情况下,能够达到90dB信噪比,从而可在小型低功耗设计中实现咼保真录音。

同样在数模转换器中的二阶多比特结构还可在采样率为9 6kHZ的情况下使信躁比达到10 OdE,从而使得高质量的数字音频回放成为可能。

该芯片在回放中的功率消耗小于23mWo因此,对于可移动的数字音频播放和录音使用中的模拟输入输出等应用系统,TLV320AIC23无疑是十分理想的选择。

该芯片主要有如下特性■是一种高性能的立体声编解码器;■通过软件控制能与TI的MCESP相兼容;•音频数据可以通过与TIMCBSP相兼容的可编程音频接口输入输出;■内部集成了驻极体话筒的偏置电压和缓冲器;■带有立体声线路输入;■具有模数转换器的多种输入立体声线路输入和麦克风输入;■具有立体声线路输出;■内含静音功能的模拟音量控制功能;■带有高效率线性耳机放大器;■在总的软件控制下,电源可弹性管理;•采用工业级最小圭寸装;■适合于可移动固态音频播放器录音器。

TLC320AC01与DSP的接口设计

TLC320AC01与DSP的接口设计

丁天然

【期刊名称】《国外电子元器件》

【年(卷),期】2003(000)008

【摘要】介绍一种集成了ADC和DAC通道的TLC320AC01模拟接口电路与TMS320VC5402定点DSP接口电路的硬件设计方法.该设计采用2片

TLC320AC01芯片,可工作于主从模式.文中给出了一个软件实例以说明主从模式下软件的实现方法.

【总页数】3页(P11-13)

【作者】丁天然

【作者单位】济宁师范专科学校

【正文语种】中文

【中图分类】TP334.7

【相关文献】

1.EPP并口与ADSP2181 DSP的接口设计 [J], 陈培玉;阙沛文

2.主从模式的TLC320AC01与DSP的接口设计 [J], 朱正平;刘益成

3.主从模式的TLC320AC01与DSP的接口设计 [J], 朱正平;刘益成

4.基于McBSP实现DSPs与串行AD/DA的接口设计 [J], 杨雪;牟燕妮

5.TLC320AC01与TMS320C5402 DSP接口电路分析 [J], 孙长贵;李兴国;刘磊因版权原因,仅展示原文概要,查看原文内容请购买。

8语音芯片TLC320AD50C接口设计

以一种修养面对两种结果

必须首先学会面对的一种结果----被拒绝

仍然感谢这次机会,因为被拒绝是面试后的两种结 果之一。 被拒绝是招聘单位对我们综合考虑的结果,因为我 们最关心的是自己什么地方与用人要求不一致,而 不仅仅是面试中的表现。 不要欺骗自己,说“我本来就不想去”等等。 认真考虑是否有必要再做努力。

多通道缓冲串行口McBSP(Multi-channel Buffered Serial Port)是在标准串行口的基 础上发展起来的,其硬件部分就有与标准串 行口相同的引脚连接界面。

在现有的C54x DSP中,大多配有McBSP,而 VC5402、VC5410和VC5420则分别配有2、3和6 个McBSP。

Байду номын сангаасDSP原理与应用

电子信息工程学院 李海林

第二阶段学习主题

CCS软件环境上机例题讲解 DSP硬件设计基础

DSP最小系统设计

DSP与ADC/DAC的接口设计

DSP与语音芯片TLC320AD50C的接口设计

语音接口

硬件系统

硬件系统

DSP MIC

PHONE OUT 语音CODEC 语音输出选择

McBSP控制寄存器

McBSP控制寄存器

McBSP控制AD50举例

McBSP控制AD50举例

求职应注意的礼仪

求职时最礼貌的修饰是淡妆 面试时最关键的神情是郑重

无论站还是坐,不能摇动和抖动 对话时目光不能游弋不定 要控制小动作 不要为掩饰紧张情绪而散淡

最优雅的礼仪修养是体现自然

McBSP功能

IC datasheet pdf-TLV320AIC20, TLV320AIC21,TLV320AIC24, TLV320AIC25,TLV320AIC20K,TLV320AIC24K,pdf(Low