一种大规模集成电路测试的修调实现方法

大规模集成电路设计与实现

大规模集成电路设计与实现随着科技的不断发展,大规模集成电路(Very Large Scale Integration,简称VLSI)在现代电子领域中扮演着至关重要的角色。

本文将讨论大规模集成电路的设计和实现过程,并探讨相关的技术和方法。

一、概述大规模集成电路是一种将数百到数十亿个晶体管器件集成到单个芯片上的技术。

这种技术的发展使得我们能够在一个小小的芯片上容纳巨大的功能,从而实现了电子设备的微型化和高性能化。

大规模集成电路被广泛应用于计算机、通信、嵌入式系统等领域,成为现代科技的基础。

二、设计流程1.需求分析在进行大规模集成电路设计之前,首先需要进行需求分析。

这包括对电路功能、性能、功耗和成本等方面的要求进行明确和分析,为后续的设计提供方向。

2.逻辑设计逻辑设计是大规模集成电路设计的核心环节之一。

在逻辑设计阶段,设计师使用硬件描述语言(HDL)来描述电路的逻辑功能和行为。

常用的HDL语言包括VHDL和Verilog。

3.电路设计电路设计阶段是将逻辑电路转化为物理电路的过程。

在这个阶段,设计师使用标准单元库中的基本器件,如逻辑门、触发器等来搭建电路结构。

4.布局与布线布局与布线是将电路设计映射到实际芯片上的过程。

在布局阶段,将电路按照一定的规则进行摆放,以保证电路的性能和可靠性。

在布线阶段,将电路中的连线路径进行规划和布线,使得电路的信号传输效果最优。

5.验证与仿真验证与仿真是确保电路设计正确性的重要环节。

通过仿真工具,设计师可以模拟电路的运行过程,验证电路的功能性和性能指标是否达到设计要求。

三、实现方法1.全定制设计全定制设计是指根据设计要求自定义每个器件的尺寸和布局。

这种方法的优点是可以获得最佳的性能和功耗表现,但开发周期较长且成本较高。

2.半定制设计半定制设计是利用标准单元库中的器件进行设计。

这种方法相比于全定制设计具有更快的设计周期和更低的成本,但性能和功耗的优化程度可能较低。

3.可编程逻辑设计可编程逻辑设计是采用可编程逻辑器件(如FPGA)进行电路设计。

LPCVD设备维修及应用

低压化学气相淀积设备使用与维护技术谭刚吴嘉丽李仁锋中国工程物理研究院电子工程研究所传感器研究中心四川绵阳621900摘要: LPCVD是大规模集成电路(LSI)和超大规模集成电路(VLSI)以及半导体光电器件工艺领域里的主要工艺之一。

PCVD技术可以提高淀积薄膜的质量,使膜层具有均匀性好、缺陷密度低、台阶覆盖性好等优点,成为制备Si3N4薄膜的主要方法。

热壁LPCVD设备使用过程中出现薄膜的淀积速率、薄膜的均匀性、片内均匀性、片间均匀性不理想等问题,提出解决办法。

一、引言PCVD技术可以提高淀积薄膜的质量,使膜层具有均匀性好,缺陷密度低,台阶覆盖性好等优点,成为制备Si3N4薄膜的主要方法。

淀积时,硅片垂直放人反应器中,间隙紧凑,大大提高了设备的加工能力,有利于降低生产成本,与水平放置硅片的系统相比,避免了反应器掉落微粒的沾污。

热壁LPCVD技术有如下特点:淀积温度低、均匀性好,能很好地控制其组分,并有良好的台阶覆盖性、可控性和重复性好,成本低、成品率高、适合大批量生产,且淀积薄膜不受衬底的影响。

二、设备使用中的问题1.薄膜的淀积速率热壁LPCVD Si3N4、Poly—Si薄膜的淀积速率不仅与参加反应的气体、气体流量大小有关,还与炉温、淀积压力等因素有关。

由于热壁LPCVD Si3N4、Poly一Si时,一般在表面反应控制范围内,所以,Si3N4和Poly一Si薄膜的淀积速率随炉温升高而增加,随淀积压力的增大而加快。

目前的SiH2C12+NH3气体体系生成的Si3N4薄膜,淀积温度为740一800℃,在此温度范围内所淀积的薄膜质量没有明显的差别。

在SiH2C12+NH3反应系统中,为防止淀积薄膜中有富硅,使用了较多量的NH3。

一般采用SiH2C12+NH3=1:4一1:6的气体流量比。

在富氨的情况下,淀积速率与NH3流量的关系并不密切,而是随着SiH2C12流量的加大而增高。

值得注意的是,热壁LPCVD Si3N4、Poly—Si的淀积速率与装片量也有关,一般情况下随着装片量的增加淀积速率减慢。

《微处理机》2006年总索引第1~6期

1 2 2 2 2 2

2

在 Ssm ye C中用 I 构造处理器模型方法分析 …………………………………… 邵作之, t S S 曹晓龙 , 刘莉娟 3 开关 电容 ∑△调制器的行为级建模 …… …………………………………・ ………” 徐 健 , 庆元 , 戴 朱华平 3 单片电流模式降压型 D D C— C转换器的设计 ……………………………………… 毛振峰, 王继安 , 强等 3 汪

维普资讯

第 6期

20 06年 1 2月

微

ห้องสมุดไป่ตู้

处

理

机

No 6 . De ., 0 6 c 2 0

MI CROPROC S ES ORS

《 处理机) 0 6年总索引第 1 6期 微 20 ~

・

综述与评论 ・ 大规模集成 电路设计 、 制造与应用 ・

期

页

1—3

PI C 总线的未来发展 ………………………………………………………………… 刘长成 , 来逢昌, 王进祥

・

6

修调技术在高精度集成电路中的实现 ……………………………………………… 李文昌, 王继安 , 威 等 1 李 多场限环的优化设计方法……………………………………………………………………… 张 雯 , 张俊松 1 种 Sa ee — I hr nd CC滤波器的设计及仿真 ………………………………………… 金 晶, 维, 萌等 1 p 孙 王 基于 85 M U核的O D芯片系统设计与实现……………………………………………… 邹连英 。 01 C S 邹雪城 I

BIST测试技术简介

BIST测试技术简介摘要:内建自测试(BIST)是在电路设计时考虑到测试电路的需求,在芯片的内部设计出调试电路,在电路内部植入测试生成、施加、分析和测试控制结构,从而使得调试更加简单。

随着集成电路规模的不断增长,soc的需求也越来越大,soc的测试变得越来越困难和重要,本文介绍内建自测试的基本概念和其特点,并将它与其他测试方法的优缺点做一比较。

关键词:内建自测试;穷举测试;伪随机测试; DFT测试比较正文:在超大规模集成电路(VISL)技术迅猛发展的今天,集成电路工业已经达到了一个的高度:上亿只晶体管集成在一个芯片上,片内时钟信号的频率达到好几个GHZ。

随之而来的,是越来越突出的测试瓶颈问题,一则,自动测试设备的发展很难跟得上芯片的发展步伐(系统时钟,信号精度,存储数据量等),再则,高性能的自动测试设备(ATE)的价格将是令人望而却步的。

而SOC片上系统的出现更是对测试领域提出了新的挑战,为了保证芯片的可靠性,测试是必不可少的手段,而要突破测试瓶颈只有一个唯一的可测试性设计。

常见的有以下几种测试方法:传统的DFT方法,扫描路径发,边界扫描法,BIST(内建自测试法)。

(一) BIST(Built-in Self Test)测试技术BIST测试技术简称BIST是在设计时在电路中植入相关功能电路用于提供自我测试功能的技术,以此降低器件测试对自动测试设备(ATE)的依赖度。

BIST是一种DFT(Design for Testability)技术,它可以应用于几乎所有电路,因此在半导体工业被广泛应用。

举例来说,在DRAM中普遍使用的BIST技术包括在电路中植入测试图形发生电路,时序电路,模式选择电路和调试测试电路。

BIST技术的快速发展很大的原因是由于居高不下的ATE成本和电路的高复杂度。

现在,高度集成的电路被广泛应用,测试这些电路需要高速的混合信号测试设备。

BIST技术可以通过实现自我测试从而减少对ATE的需求。

集成电路中的设计流程和方法

集成电路中的设计流程和方法集成电路(Integrated Circuit,IC)是现代电子技术的重要组成部分,也是各种电子设备的核心。

在集成电路的制作过程中,设计流程和方法起着至关重要的作用。

本文将介绍集成电路中常见的设计流程和方法,以及它们的应用。

一、设计前期准备在进行集成电路设计之前,需要进行一系列的准备工作。

首先,需要明确设计目标和需求,包括电路的功能、性能要求等。

然后,需要对所需芯片的规模和复杂度进行评估和确定。

此外,还需要进行市场研究,了解类似产品的市场需求和竞争情况。

最后,要制定详细的设计计划和时间表。

二、电路设计电路设计是集成电路设计的核心环节之一。

在电路设计过程中,需要进行原理图设计、逻辑设计和电路仿真等工作。

原理图设计是将电路的功能和连接关系用图形和符号表示出来,以便于后续的设计和验证。

逻辑设计是根据功能和性能要求,将电路设计为逻辑门电路、寄存器、时序逻辑等。

电路仿真是利用电子设计自动化(EDA)工具对电路进行仿真和验证,以确保电路的功能和性能满足设计要求。

三、物理设计物理设计是将电路设计转化为实际的物理结构和版图。

物理设计主要包括布局设计和布线设计两个阶段。

布局设计是将电路的各个组成部分进行合理的排列和布局,以保证电路的整体性能和可制造性。

布线设计是根据布局设计的结果,将电路中的导线进行布线,并解决导线间的冲突和干扰问题。

物理设计涉及到的技术包括布局规划、布线规划、时钟分配等。

四、验证和测试在集成电路设计完成后,需要进行验证和测试工作,以验证电路的功能和性能是否满足设计要求。

验证主要包括功能验证和时序验证两个方面。

功能验证是通过编写测试程序,对设计的电路进行功能测试,以确认其能够正常工作。

时序验证是通过时序模拟器和时钟分析工具,对电路的时序性能进行分析和验证。

测试是在电路生产过程中对芯片进行测试和筛选,以确保芯片的质量和可靠性。

五、后期调试和优化在完成验证和测试后,可能还需要进行一些后期的调试和优化工作。

半导体集成电路电压调整器测试方法

半导体集成电路电压调整器测试方法

半导体集成电路电压调整器的测试方法主要包括以下步骤:

1. 确定测试条件:根据具体标准和规范,确定测试环境温度、输入电压及其变化量、输出电压等测试条件。

2. 搭建测试系统:按照测试需求,搭建包含被测器件、电源、负载网络、测量仪器等在内的测试系统。

3. 测试电压调整率:在规定的输入电压下,调节输出电压至规定值,记录相应的输出电压变化,计算电压调整率。

4. 测试电流调整率:在规定的输出电流下,调节输入电压或输出电压,记录相应的输出电压变化,计算电流调整率。

5. 测试电源纹波抑制比:在规定的输入电压和输出电流下,测量电源纹波抑制比。

6. 测试输出电压温度系数:在规定的输入电压和温度下,测量输出电压温度系数。

7. 测试输出电压长期稳定性:在规定的输入电压和输出电流下,长时间运行测试,观察输出电压的变化。

8. 测试输出噪声电压:在规定的输入电压和输出电流下,测量输出噪声电压。

9. 测试耗散电流和耗散电流变化:在规定的输入电压和输出电流下,测量耗散电流和耗散电流变化。

10. 测试短路电流:在规定的输入电压和输出电流下,使输出短路,测量短

路电流。

11. 测试输出阻抗:在规定的输入电压和输出电流下,测量输出阻抗。

12. 分析测试结果:根据测试数据,分析被测器件的性能指标是否满足要求。

需要注意的是,具体的测试方法和步骤可能会因不同的标准和规范而有所差异。

在实际操作中,应根据具体标准和规范进行测试,并遵循安全操作规程。

《计算机组装与维护》第2章教案

教学要求1. 了解主板的基本功能2.掌握主板的分类3.掌握主板的组成结构及设置4.掌握主板的选购方法第 2章主板的使用与维修5.了解主板的常见故障及维修方法2. 1 计算机主板简介主板又叫主机板(Main Board)、系统板(System board或母板 (MotherBoard),它安装在机箱内,是微机最基本的也是最重要的部件之一,因为主板是整个微机内部结构的基础,不管是CPU内存、显示卡还是硬盘、键盘、声卡、网卡等均插在主板上靠主板来协调工作,主板不好,则其他一切插在它上面的部件的性能都不能充分发挥出来。

一、主板的作用主板实际上就是一块电路板,上面安装了各式各样的电子零件并布满了大量电子线路。

当微机工作时由输入设备输入数据,由CPU来完成大量的数据运算,再由主板负责组织输送到各个设备,最后经输出设备反映到我们的感官。

这个过程看上去很简单,输入设备就是键盘、鼠标等,输出设备就是显示器、打印机之类,可是CPU的运算结果哪个先送去,哪个后送走,这些就要靠主板上的系统芯片来控制。

而且主板上还不止系统芯片一个部件,由此看来,主板的地位相当重要。

二、主板的分类1、按主板上的CPU分类按主板上能所使用 CPU的型号可分为386、486、P2、P3、P4、赛扬、K5、 K6等主板。

2、按主板上的CPU插梢按主板上CPU的插梢形式可分为插座式和插梢式两种。

3、按主板的结构分类⑴、AT主板:13英寸X1茨寸,主板上内存被安在一个狭小而又不通风的角落,影响了内存的安装和升级散热。

⑵、BABY AT主板:13.5英寸X 8.骐寸,比AT主板长,但有些不负重荷一方面取消了主板上使用较少的零部件以压缩空间,另一方面将 BABY AT主板适当加宽,以增加使用面积。

⑶ 、 ATX 主板:ATX型主板比AT型主板的结构上有很大的区别。

其优有主要有以下几点:⑴ .主板的长边紧贴机箱后部,使更多的外设接口可以集成到主板上;⑵ .优化了内存及CPU的位置有利于安装和散热;⑶.标准的主板上有两个串行输出口、一个 PS/2鼠标口、一个PS/2键盘口和一个并行输出口,有些主板还固化了声卡及游戏接口;4、按逻辑控制芯片分类⑴ .INTER:LX、BX、I810、I815EP、I845、I850、I865、I915⑵ .非 INTER: APOLLO 、 SIS、 ALI、 OPTI5、一体化主板优点:减少了因接触不良而造成的故障整体设计合理缺点:不利于升级,一个部件的损坏会造成整个主板的损坏三、主板的组成主板是一块安装有各种插件和控制芯片的电路板,其电路结构和工作原理比较复杂。

维修电工高级题库1

A、磁极旋转 B、电枢旋转 C、罩极 D、隐极

46. 凸缘联轴器(A )。

A、属于联性联轴器 B、对联接的轴间的偏移具有补偿能力

C、结构简单,使用方便,可传递较大的扭矩 D、属于可移式联轴器

47. 发电机――电动机组调速系统是一种典型的( B )调速自控系统。

31. 旋转变压器的主要用途是( A )。

A、自动控制系统中的随动系统和解算装置 B、变压变流 C、调节电机转速

D、输出电力传送电能

32. 伺服驱动过载可能是负载过大;或加减速时间设定过小;或( B );或编码器故障(编码器反馈脉冲与电动机转角不成比例地变化,有跳跃)。

A、伺服电动机过载 B、负载有冲击

A、 B、 C、 D、

23. 直流环流的产生原因是( D )。

A、逆变电压平均值大于整流电压平均值 B、整流电压最大值大于逆变电压最大值

C、整流电压最大值大于逆变电压平均值 D、整流电压平均值大于逆变电压平均值

A、信息反馈 B、质量记录 C、质量目标 D、质量水平

14. 反应式步进电动机的转速n与脉冲频率f的关系是:( B )。

A、成正比 B、成反比 C、f2成正比 D、f2成反比

15. 异步电动机的极数越少,则转速越高,输出转矩( D )。

49. 强供电回路的管线尽量避免与可编程序控制器输出、输入回路( B ),且线路不在同一根管路内。

A、交叉 B、平行 C、远离 D、垂直

50. PLC交流集选电梯,当电梯(司机状态)3层向上运动时,2层有人按向上呼梯按钮,4层有人按向下呼梯按钮,同时轿厢内司机接下5层指令按钮与直达按钮,则电梯应停于( D )层。

93k集成电路测试系统校准原理及实现方法研究

作者简介 :贺志容 ( 1980—) ,女 ,工程 师 ,主要研究领域:微电子计量与 测试 。 通讯地址 :武汉市洪山区珞瑜路 718 号 (430074) 电话 : 027 - 87533046 E2mail: hzr_hust@163. com

[ 1 ] 贺志容 ,沈森祖 ,韩宏星 ,等. 93000集成电路测试系统 检定方法研究 [ C ]. 2007计量与测试学术交流会论文 集 , 2007: 187~189.

[ 2 ] Verigy coporation, N IST Traceable Calibration, Verigy V93000 Service Guide.

完整的溯源校准的新型集成电路测试系统 [ 3 ] 。 在系统的长期运行过程中 ,由于测试系统内部

组成元器件性能的微小变化 ,温度 、湿度等外部因 素的影响 ,系统的量值会产生漂移 ,若不对这种漂 移做出修正 ,漂移的累积会严重降低系统精度 。校 准过程中如果不能对量值进行更新修正 ,系统精度 会逐步降低 。内部参考源校准时首先对内部参考 源进行校准 ,并自动更新系统基准量 ,使其误差趋 于零 ,消除了各种因素对基准量值造成的影响 ; 自 动校准的过程利用已经校准合格的基准量对系统 中间量直至系统参量进行校准 ,并产生修正值 ,在 测试过程中引用 ,消除了各种因素对系统参量造成 的影响 ,使测量结果的产生都能依据最新校准的修 正模式 ,保证了测试系统的精度 。

图 6 参考电压校准示意图

图 7 参考电阻校准示意图

© 1994-2010 China Academic Journal Electronic Publishing House. All rights reserved.

怎样用万用表检测集成电路

怎样用万用表检测集成电路————————————————————————————————作者:————————————————————————————————日期:怎样用万用表检测集成电路集成电路的封装材料有:塑料、陶瓷及金属三种。

封装外形最多的是圆筒形、扁平形及双列直插型。

对于圆形和菱形金属封装的集成电路,识别引脚时应面向引脚(正视),由定位标记所对应的引脚开始,按顺时针方向依次数到底即可,常见的定位标记有突耳、圆孔及引脚不均匀排列等。

对于单列直插式集成电路,识别引脚应使引脚向下,面对型号或定位标记,自定位标记对应一侧的头一只引脚数起,依次为1、2、3……。

这类集成电路上常用的定位标记为色点,凹坑、小孔、线条、色带、缺角等。

有的厂家生产的集成电路,本是同一种芯片,为了便于在印刷电路板上灵活安装,其封装外形有多种,例如,为了适合双声道立体声音频功率放大器电路对称性安装的需要,其引脚排列顺序对称相反。

一种按常规排列,即自左向右,另一种则自右向左。

对这类集成电路,若封装上没有设识别标记,按上述规律不难分清其引脚顺序。

但是有少数这类器件上没有引脚识别标记,这时应从它的型号上加以区别,若其型号后缀中有一字母R,则表明其引脚顺序为自右向左反向排列。

(注:R为右,L为左)对于双列直插式集成电路,识别其引脚时,若引脚向下,及其型号、商标向上,定位标记在左边,则从左下角第一只引脚开始,按逆时针方向,依次为1、2、3……。

若引脚向上,即其型号、商标向下,定位标记位于左边,则应从左上角第一只引脚开始,按顺时针方向,依次为1、2、3……。

有的个别型号集成电路的引脚,在其对应位置上有缺脚(即无此输出引脚)。

对于这种型号的集成电路,其引脚编号顺序不受影响。

对于四列集成电路,从识别标记开始顺时针数。

集成电路推荐工作条件。

推荐工作推荐是保证集成电路正常工作的条件,在此条件内使用时,集成电路的特性及正常工作均有保证,对CMOS电路,其电源电压、输入电压、工作温度范围、脉冲宽度等虽然被规定,但是电源电压降低到7V以下时,集成电路的工作不稳定,具体使用时应注意这一点。

NoC测试技术与优化方法研究

NoC测试技术与优化方法研究NoC(网络连接)是一种集成电路设计中的通信架构,被广泛应用于多核处理器、系统芯片、嵌入式系统等领域。

NoC的性能和能耗直接影响到芯片的整体性能和功耗。

因此,对NoC的测试技术与优化方法进行研究具有重要意义。

首先,我们来介绍NoC的测试技术。

在NoC设计中,主要存在两类测试问题:连通性测试和通信质量测试。

连通性测试是指验证NoC中各个节点之间的网络连接是否正常。

通信质量测试是指验证数据在NoC中传输的可靠性和时延。

为了解决这些问题,研究者们提出了一些测试技术。

一种常见的测试技术是利用虚拟链路来进行测试。

虚拟链路允许不同节点之间建立虚拟通信通道,通过发送测试数据来验证NoC的连通性和通信质量。

同时,还可以通过注入错误、延迟等方式模拟不同的通信场景,以评估NoC在各种条件下的性能。

另一种测试技术是利用Agent来进行测试。

Agent是一种运行在NoC节点上的测试程序,用于检测和报告节点和链路的状态。

通过在NoC中部署多个Agent,可以实现对整个NoC的测试覆盖。

除了测试技术,优化方法也是研究人员关注的重点。

NoC的性能和能耗优化是一项复杂的任务,需要考虑多方面的因素。

以下是一些常见的优化方法:首先,我们可以通过优化NoC的拓扑结构来提升性能和减少能耗。

不同的拓扑结构具有不同的特点,例如星型、网格、环形等,研究人员可以根据应用需求选择最适合的拓扑结构。

其次,通过优化NoC的路由算法可以改善数据传输的效率和带宽利用率。

一种常见的优化方法是基于动态路由算法,根据网络负载和拓扑结构的变化,实时调整数据传输路径,从而提高网络的吞吐量。

此外,利用调度算法可以实现对NoC中任务的优化分配和调度。

通过合理地分配任务,最大限度地利用各个节点的计算资源,从而提高系统的整体性能。

另外,可以通过设计有效的容错机制来提高NoC的可靠性和容错性。

例如,使用冗余链路、错误控制编码等技术,可以在链路出现错误时实现数据重传和错误修复。

集成电路测试技术及应用

集成电路测试技术及应用随着信息技术的不断发展,电子产品已经成为人们生活、工作中必不可少的一部分。

而随着集成电路技术的不断更新,集成电路测试技术已经成为集成电路行业中的重要环节。

本文将介绍集成电路测试技术及其应用。

一、集成电路测试技术的概述集成电路是由多个晶体管、电容、电阻等元件在单片硅衬底上制成的一种电子元件,集成电路测试则是指对这些电子元件进行测试,以确定它们在实际使用中的性能指标。

集成电路测试技术在集成电路的生产、研发和应用过程中都具有重要作用。

集成电路测试技术主要涉及到的方面包括芯片测量技术、封装测量技术和系统级测试技术。

芯片测量技术指的是对集成电路芯片中各个单元电路的测试,主要包括数字电路、模拟电路等测试。

封装测量技术则是在芯片封装后对封装后的芯片进行测试,主要包括测试封装合格率和封装工艺的优化。

系统级测试技术则是对整个系统进行测试,主要是针对硬件系统和软件系统的测试。

二、集成电路测试技术的应用集成电路测试技术在各个领域都有广泛的应用。

在电子产品生产中,集成电路测试技术可以检测产品的质量,确保其符合技术标准。

在集成电路的研发中,测试技术可以帮助工程师更好地了解芯片的性能表现,便于后续的优化工作。

在系统集成中,测试技术可以发现整个系统中的问题,及时修复缺陷,保证系统的稳定性和可靠性。

在军事、航空等领域,集成电路测试技术还可以用于电子设备的调试、故障诊断等方面。

三、集成电路测试技术的发展随着集成电路技术的不断发展,集成电路测试技术也在不断更新。

当前,集成电路测试技术主要面临以下几个方面的挑战:1. 节约测试成本:随着集成电路芯片的规模越来越大,测试成本也随之增加。

如何在保证测试质量的前提下控制测试成本,是当前测试技术需解决的问题之一。

2. 提高测试生产率:测试是集成电路生产中不可缺少的一个环节,测试生产率的大小在很大程度上决定了整个生产效率。

如何提高测试生产效率,减少测试时间,目前也是测试技术需要解决的难点。

集成电路测试技术

数字集成电路测试技术

随着数字集成电路的普及,数字集成电路测试技 术逐渐成为主流,如JTAG测试、边界扫描测试等 。

自动测试设备(ATE)

随着集成电路规模的扩大和复杂性的增加,自动测 试设备(ATE)逐渐成为主流的测试工具,能够实 现高效、高精度的测试。

02

集成电路测试技术分类

功能测试

功能测试是集成电路测试中的基础测试,主要目的是验证集成电路的功能是否符合 设计要求。

挑战

随着集成电路封装的小型化,测试的难 度也在增加,因为小型化封装可能导致 引脚间距缩小和引脚数量增加,使得测 试的准确性和可靠性受到影响。

解决方案

采用先进的探针卡和连接器技术,以提 高测试连接的稳定性和可靠性。同时, 开发和应用更先进的测试算法和软件, 以应对小型化封装带来的挑战。

05

集成电路测试技术发展趋势

测试计划制定

确定测试目标

01

明确测试范围、测试项目、测试标准等,为后续测试提供指导。

制定测试方案

02

根据测试目标,设计合理的测试方案,包括测试方法、测试步

骤、测试环境等。

分配测试资源

03

根据测试方案,合理分配测试所需的硬件、软件、人力等资源。

测试硬件与软件选择

选择测试设备

根据测试需求,选择合适的测试设备,如测试机台、探针台、负 载板等。

的性能表现,满足设计要求。

性能测试通常需要在不同的环境 条件下进行,以模拟实际工作情

况。

可靠性测试

可靠性测试是为了评估集成电路在长 时间工作或恶劣环境下的稳定性。

可靠性测试的结果可以用来评估集成 电路的可靠性和寿命,以及预测潜在 的故障风险。

可靠性测试通常包括寿命测试、高低温 循环测试、湿度测试等,以模拟实际使 用过程中可能遇到的各种环境因素。

维修电工(中级)新 可编程控制器控制电路装调部分150608

可编程控制器控制电路装调117.下列选项不是PLC的特点(D)。

A、抗干扰能力强B、编程方便C、安装调试方便D、功能单一118.可编程序控制器采用大规模集成电路构成的(B)和存储器来组成逻辑部分。

A、运算器B、微处理器C、控制器D、累加器119.可编程序控制器系统由(A)、扩展单元、编程器、用户程序、程序存入器等组成。

A、基本单元B、键盘C、鼠标D、外围设备120.FX2N系列可编程序控制器定时器用(C )表示。

A、XB、YC、TD、C121.在一个程序中,同一地址号的线圈(A)次输出,且继电器线圈不能串联只能并联。

A.能有一B.只能有二C.只能有三D.无限122.可编程序控制器(A)中存放的随机数据掉电即丢失。

A、RAMB、ROMC、EPROMD、以上都是123.可编程序控制器在STOP模式下,执行(D)。

A.输出采样8.输入采样C,输出刷新 D.以上都是125.(D )不是PLC主机的技术性能范围。

A、本就I/O 口数量B、高手计数输入个数C、高速脉冲输出D、按钮开关种类126.FX2N可编程序控制器DC 24V输出电源,可以为(C)供电。

A、电磁阀B、交流接触器C、负载D、光电传感器127.FX2N可编程序控制器(B)输出反应速度比较快A.继电器型B.晶体管和晶闸管型C.晶体管和继电器型D.继电器盒晶闸管型128.FX2N-40ER可编程序控制器中的E表示(B)。

A.基本单元B.扩展单元C.单元类型D.输出类型129.对于PLC晶体管输出,带电感性负载时,需要采取(D)的抗干扰措施。

A.在负载两端并联续流二极管和稳压管串联电路B.电源滤波C.可靠接地D.光电耦合130.FX2N系列可编程序控制器中回路并联连接用(D)指令。

A、ANDB、ANIC、ANBD、ORB131.PLC的辅助继电器、定时器、计数器、输入和输出继电器的触点可使用(D)次。

A、一B、二C、三D、无限132.PLC梯形图编程时,右端输出继电器的线圈能并联(B)个。

基于ecc电路的sram自检测修复设计与验证-概述说明以及解释

基于ecc电路的sram自检测修复设计与验证-概述说明以及解释1.引言1.1 概述概述部分的内容可以从以下几个方面入手:首先,我们可以介绍SRAM(Static Random Access Memory)和ECC(Error Correcting Code)电路的基本概念和作用。

SRAM是一种常用的存储芯片,用于在计算机和其他电子设备中存储临时数据。

它具有访问速度快、寿命长等特点。

然而,由于电子设备中存在电磁干扰、温度变化等因素,SRAM容易发生错误。

为了解决这个问题,ECC电路被引入到SRAM中,用于检测和纠正错误。

其次,我们可以介绍自检测修复技术在电子设计中的重要性。

随着电子设备的高度集成和复杂性增加,设计出高可靠性的电路变得越来越重要。

自检测修复技术可以不断监测电路的状态,并在发生错误时进行自动修复。

这种技术不仅可以提高电路的可靠性,还可以减少对外部干预的需求,提高设备的自主性和稳定性。

最后,我们可以说明本文的研究目标和意义。

本文旨在基于ECC电路设计一种可靠的SRAM自检测修复技术,并通过验证实验对其进行验证。

通过详细分析SRAM自检测修复的基本原理,我们希望能够为电子设备设计和制造领域的工程师和研究人员提供参考和指导,同时提高SRAM的可靠性和性能。

通过以上的内容,我们可以完整地概述本文的主题和研究目标,为读者提供一个清晰的引导,帮助他们了解本文的主旨和内容。

1.2 文章结构本文的结构主要分为引言、正文和结论三个部分。

在引言部分,首先进行概述,介绍了本篇文章的主题以及研究的背景和意义。

随后是文章结构,即对整篇文章的组织和内容进行概括和指引。

最后,明确了本文的目的,即通过设计与验证基于ECC电路的SRAM自检测修复方案,为解决SRAM的故障问题提供解决方案。

接下来是正文部分,主要分为两个部分。

首先是对ECC电路的原理和应用进行介绍,详细阐述ECC电路在电子设备中的作用和应用领域,为后续的研究工作铺垫;然后是对SRAM自检测修复的基本原理进行探讨,包括SRAM自检测的原理、修复方案、实现方法等内容。

仿真应用工程师招聘笔试题与参考答案

招聘仿真应用工程师笔试题与参考答案一、单项选择题(本大题有10小题,每小题2分,共20分)1、在仿真软件中,为了模拟真实世界的物理行为,下列哪个选项是实现精确碰撞检测的关键因素?A. 图形渲染质量B. 物理引擎精度C. 网络传输速度D. 用户界面友好度答案:B. 物理引擎精度解析:精确的碰撞检测主要依赖于物理引擎的计算精度,而非图形渲染质量、网络传输速度或用户界面的设计。

2、在进行系统仿真时,为了提高模型的准确性,最应该关注的是哪一项?A. 模型的复杂度B. 数据的准确性和完整性C. 仿真的运行速度D. 软件的品牌知名度答案:B. 数据的准确性和完整性解析:在仿真过程中,数据的准确性和完整性对于建立一个高精度的模型至关重要。

虽然模型复杂度和仿真运行速度也很重要,但它们不如数据质量对结果的影响直接。

软件品牌知名度则不是决定仿真准确性的关键因素。

3、在EDA工具中,将硬件描述语言转化为硬件电路的重要工具软件是 ( )A. 适配器B. 仿真器C. 下载器D. 综合器答案:D解析:综合器(Synthesis Tool)是EDA工具中的一个关键组成部分,它的主要功能是将硬件描述语言(HDL)转化为硬件电路。

这一转化过程包括将HDL描述的逻辑电路设计转化为由一系列门级或更底层逻辑元件(如晶体管、逻辑门等)组成的电路网表,进而生成可以被FPGA或ASIC等硬件实现的物理设计。

适配器、仿真器和下载器在EDA 流程中也扮演重要角色,但它们并不直接负责将HDL转化为硬件电路。

4、以下关于Verilog HDL中赋值语句的描述,正确的是 ( )A. 在组合逻辑电路设计中,应优先使用阻塞赋值(blocking assignment)B. 在时序逻辑电路设计中,非阻塞赋值(non-blocking assignment)会导致仿真结果与预期不符C. 阻塞赋值和非阻塞赋值的主要区别在于它们对仿真时间的处理方式D. 非阻塞赋值在always块中总是优于阻塞赋值答案:C解析:在Verilog HDL中,阻塞赋值和非阻塞赋值的主要区别在于它们对仿真时间的处理方式。

边界扫描在数模混合电路板级测试中的设计与应用

计算机测量与控制!"#"$!$%!%%"!!"#$%&'()'*+%('#',&-!",&(".!!#%%'!#收稿日期 "#"$#*%)$!修回日期 "#"$%#%"%作者简介 王!晴!%'&,"&女&硕士&高级工程师%引用格式 王!晴&王祗文&张栎存!边界扫描在数模混合电路板级测试中的设计与应用'((!计算机测量与控制&"#"$&$%!%%")%%' %"$&%$#!文章编号 %)+%,*'& "#"$ %%#%%'#*!-./ %#!%)*") 0!1234!%%5,+)" 67!"#"$!%%!#%&!中图分类号 []$'%!!文献标识码 9边界扫描在数模混合电路板级测试中的设计与应用王!晴% 王祗文" 张栎存%!%`航天科工空间工程发展有限公司&北京!%##&*,$"`北京控制与电子技术研究所&北京!%###$&"摘要 针对飞控系统某数模混合电路板测试需求&在不利用外部信号源*信号采集设备的条件下&利用边界扫描技术进行测试系统设计$介绍了]C/M,%#边界扫描核心套件和H1J2_L K3O测试软件&对边界扫描测试方法进行研究&详细说明了测试系统方案设计*测试流程开发步骤以及测试程序执行方式&并通过实际测试&验证了设计的可行性&为数字电路板和简单的数模混合电路板的测试提供了实用的测试方法和手段&具有很好的应用价值%关键词 边界扫描$数字电路$数模混合电路$]C/M,%#$H1J2_L K3O6'+07,*,3/$$.01*&0","5K"%,3*(8N+1*,0,K"*(3N.'D'.M'+&"56070&*.N*,*."7[89(03!0(1%0&_9;<=42G%&_9;<@I4W D2"&@>9;<:41B2%!%`C9H/CH7J1D?2G42D D K42G-D R D A L7Q D26C L`&:6P`&^D4042G!%##&*,&C I42J$"`^D4042G/2O646B6D L SC L26K L A J2P?A D16K L241O[D1I2L A L G U&^D4042G!%###$&&C I42J"/9+&(*1&)Y L K6I D6D O642G K D T B4K D Q D26O L S JP4G46J A M J2J A L G I U X K4P14K1B46X L J K PL S6I D S A4G I61L26K L A O U O6D Q&B O D PX L B2P J K U M O1J2 6D1I2L A L G U6LP D O4G26I D6D O6O U O6D Q W46I L B6B O42G D V6D K2J A O4G2J A O L B K1DJ2PO4G2J A J1T B4O464L2D T B47Q D26!/26K L P B1D P6I D]C/M,%# X L B2P J K U O1J21L K D O B46D J2PH1J2_L K3O6D O6O L S6W J K D&O6B P4D P6I D X L B2P J K U O1J26D O6Q D6I L P&P D O1K4X D P6I D6D O6O U O6D QO1I D Q D P D M O4G2&6D O6S A L WP D R D A L7Q D26O6D7O J2P6D O67K L G K J QD V D1B64L2Q D6I L P42P D6J4A&J2P R D K4S4D P6I D S D J O4X4A46U L S6I D P D O4G26I K L B G I7K J164M 1J A6D O642G&W I41I7K L R4P D P7K J1641J A6D O6Q D6I L P O J2PQ D J2O S L K6I D6D O6L S P4G46J A14K1B46X L J K P O J2P O4Q7A D P4G46J A M J2J A L G I U X K4P14K M 1B46X L J K P O&J2PI J P G L L PJ77A41J64L2R J A B D!:'8;"(3+)X L B2P J K U M O1J2$P4G46J A14K1B46$P4G46J A M J2J A L G I U X K4P14K1B46$]C/M,%#$H1J2_L K3O<!引言伴随着集成电路技术的数字化程度越来越高'%(&越来越多的电路板由Y]<9*C]:-*-H]等大规模集成电路组成&这些体积小*集成度高的芯片为电路设计带来了巨大便利'"(%与此同时&超大规模集成电路*表面贴装等新技术也为电路的板级测试带来诸多难题'$(&传统的测试方法包括探针测试方法*内建自测试技术!^/H[&^B4A6M/2H D A S M[D O6"*边界扫描测试技术%探针测试方法需要将物理测试探针置于被测电路的测试点上&从而开展电气性能测试',(&工作准备流程繁琐&且开发人员需要预留一定数量的测试点&随着电路密度的不断增加&绝大部分电路板采用多层设计&几乎不可能设置足够多的探针测试点来完成整个电路的测试覆盖'*(&而且探针属于接触时测量&测试过程中还有对电路板本身造成损坏的潜在风险%内建自测试技术是在电路设计阶段考虑电路设计完成后的测试问题&更倾向于电路的功能性测试&为测试阶段节约了更多的测试时间&降低了成本&但是这种测试方法往往对电路本身的引脚故障测试覆盖不足%边界扫描测试技术作为一种大规模数字集成电路测试标准&提供了一整套标准*完整的电路测设方法&利用移位寄存器和测试向量来控制集成电路管脚的状态&通过边界扫描链路实现对大规模集成电路全部管脚的控制&解决了高密度*高集成度数字电路板测试覆盖不足的难题&实现了电路的功能测试*静态测试*故障定位等'*(%本文从某数模混合电路测试入手&介绍了利用边界扫描测试技术进行数模混合电路测试的设计方法&在不采用外部信号源*采集设备的情况下&最大限度实现电路板的测试覆盖&有效降低的测试过程中的经济成本和时间成本&同时&也提高了测试效率%=!边界扫描测试技术边界扫描!^H&X L B2P J K U O1J2"测试技术&简称边扫&正式命名来源于/???+H;H/H6J2P J K P%%,'`%%''#!后简称/???%%,'`%"'+&(&规定了利用边界扫描进行测试所需要!投稿网址 W W W!0O01A U3Z!1L Q!!计算机测量与控制!第$%""""""""""""""""""""""""""""""""""""""""""""""""""""卷#%"#!#的硬件和软件&为相关的测试设计提供了完整的指导规范''(%/???%%,'`%标准对于被测单元来讲属于非侵入式的测试方法&它不关心被测单元的内部程序&测试过程中在不对被测单元的内部程序做任何修改的情况下&仅依靠([9<接口实现对逻辑电路各个引脚的控制%当前主流的Y ]<9*C ]:-*-H ]等集成电路均支持该规范&利用该规范&也能够达到测试非边界扫描期间的目的'%#(%边界扫描硬件结构组成主要包括,部分)测试访问接口![9]"*测试访问接口控制器*数据寄存器!-\"以及指令寄存器!/\"'%%%,(%%"测试访问接口包括测试数据输入![-/"*测试数据输出![-."*测试时钟![C d "*测试模式选择![N H "*信号复位![?H ["&边界扫描测试运行主要依靠该接口进行数据控制和操作%""[9]控制器作为一个含有%)个工作状态的有限状态机&用于实现对测试访问接口的控制%$"数据寄存器由[9]控制器决定存放测试过程中的测试数据和结果&包括旁路寄存器和边界寄存器%边界寄存器首尾连接构成链路&实现对芯片引脚的输出控制$旁路寄存器为不需要测试的位置提供一条快捷通道&缩短不必要的测试时间%,"指令寄存器包括串行+并行锁存寄存器&用来定义数据寄存器的操作模式%图%!边界扫描硬件结构组成>!边界扫描测试系统设计>@=!边界扫描硬件套件]C /M ,%#边扫测试套件作为美国9H H ?[公司设计的一款([9<控制器&具备高吞吐率*灵活配置和使用的特点&能够用于规模化量产测试以及需要多个([9<端口同时测试的被测电路&可执行边界扫描测试软件开发的测试任务或烧录任务&支持扫描链路测试*互联测试*Y A J O I 测试*存储器测试*用户自定义测试以及电路开短路测试等&依靠高速的[C d 时钟和并行测试烧录能力&可作为大规模数字电路测试诊断的优选解决方案%]C /M ,%#实物套件主要由]C /控制卡*,端口边界扫描适配器以及相应的配套测试线缆组成%[C d 测试时钟最高运行速率可达*#N>Z &适配器与]C /控制卡之间的有效距离最高可达%*米&便于测试系统集成%一个边界扫描控制平台可以支持在一个工作站上同时安装$块]C /控制卡*单块控制卡又可以同时支持"块适配器&每块适配器支持,个[9]边扫接口&所以单个测试平台可以支持的边扫接口高达",个%根据需要可以对被测电路灵活配置&并将多块不同的测试电路上的多个扫描链路串接成%条链路集中管理和测试&避免了过多的*非必要的链路管理%大规模量产测试时&也可以接多块相同的被测电路&对其执行相同的测试&并且([9<接口的数据首发是并行的&可有效降低测试线路搭建*数据烧录的测试时间%同时&为了支持非边扫信号的测试需要&每个适配器还支持可独立控制的"#个离散/+.信号&每一路离散/.的电压可通过软件控制&且都配有终端可供灵活配置%>@>!边界扫描软件平台H 1J 2_L K 3O 嵌入式软件平台是9H H ?[公司基于/???%%,'`%标准设计的边扫测试集成开发环境&同时还支持/???%%,'`)标准&具有较广的应用范围%可提供整套完整的电路板边扫测试方案&对被测电路开展在线编程*测试和调试&并生成测试测试覆盖率报告'%*%)(%H 1J 2_L K 3O软件平台可根据被测电路网表文件以及边扫测试器件的^H M -:模型文件&通过合理配置生成测试需要的测试矢量&在线烧录数据&对测试程序进行单步*连续运行调试和测试执行%通过H 1J 2_L K 3O 软件平台进行测试程序开发前&有一些必要的准备工作需要提前了解)首先&确认被测电路板上的可编程器件是否含有([9<接口&是否符合/???%%,'`%标准&都符合的情况下才可以进行边界扫描测试开发$其次&提前准备边界扫描测试元件的^H -:模型文件&可以向芯片厂商官网下载或者向9H H ?[技术支持请求$再者&提前准备非边扫器件的模型文件&便于互联测试开发$还有&被测电路板中如果含有C ]:-&最好提前将内部程序读取保存&型号较老的元件有可能在边扫测试时被擦除&导致电路板功能失效%>@?!测试系统设计边界扫描测试重点用于测试数字电路'%+%'(&主要包括链路测试*互连测试*Y A J O I 测试*存储器测试以及用户自定义测试&用户自定义测试可以通过特殊设计&达到测试非边界扫描器件以及放大器*9-+-9数模混合电路的目的%本文针对飞控系统某数模混合控制电路板的组成特点和测试需求&在尽量不适用外部外侧设备的条件下&满足被测电路板所有重要测试节点的故障诊断需要&构建如图"所示的边界扫描测试系统&主要包括测试计算机*边界扫描控制器*边界扫描测试软件*程控电源*测试适配板*被测电路板以及若干条配套测试线缆%其中&边界扫描测试硬件选用]C /M ,%#套件$边界扫描测试软件选用H 1J 2M _L K 3O%计算机作为整个测试系统的控制中心&利用H 1J 2M _L K 3O 软件完成边界扫描测试工程的开发*功能测试项的执行&用户自定义测试的激励发送和响应接收%]C /M ,%#套件作为作为连接边扫测试软件和被测电路板的桥梁&用于将边扫测试软件生成的测试矢量下发到被测电路板以及测试数据的采集%程控电源用于系统供电以及测试的自动化!投稿网址 W W W!0O 01A U3Z !1L Q第%%期王!晴&等)""""""""""""""""""""""""""""""""""""""""""""""""""""边界扫描在数模混合电路板级测试中的设计与应用#%"%!#图"!边界扫描测试系统组成运行%对于含有模拟电路*很多没有互联模型的非边扫器件的数模混合电路板测试&为了提高测试覆盖率&关键技术是设计一套用于信号调理*边扫器件互联以及信号闭环的测试适配板&并通过用户自定义脚本的方式实现没有模型的无法进行互联测试的元器件的功能测试%测试适配板主要用于完成如下四部分功能)%"作为程控电源信号的转接接口&便于通过被测电路板供电连接器为被测电路板供电$""信号调理&实现被测信号路由的电平匹配$$"为被测电路板对外输入*输出数字接口提供信号闭环$,"设计边扫器件及外围-9*9-电路&为被测电路板模拟信号接口提供信号闭环&最大程度覆盖电路板可测节点%有了信号闭环回路&便于通过互联测试和用户自定义测试的方式&提高整个电路板的测试覆盖%!混合电路板级测试验证@=!验证电路板需求分析被测验证电路板采用飞控系统某数模混合电路组成&所含芯片种类主要包括型号为g C ,#%$?的Y ]<9*9-转换器9-%)+,*模拟开关N9g $#)*运算放大器9-*')"*电压比较器:N %$'9*差分芯片N9g ,&'*总线缓冲芯片*,Y C [",,和*,Y C [",**存储类]\.N 芯片"+C *%"等%且电路板含有高密度连接器&许多信号通过该连接器输入或输出&单板测试含大量信号未闭环%该验证电路板的边界扫描测试需覆盖所有主要芯片的信号路由通断故障*影响板子正常使用的所有重要数字引脚的开短路等故障&并精确定位到具体信号传输路经或者具体芯片引脚%@>!测试方案详细设计根据被测电路板的测试需求&设计边界扫描测试系统&其测试方案示意图如图$所示&通过合理设计适配板&完成数字电路测试*模拟电路测试以及连接器开环信号的测试%被测电路板的存储器及其他信号闭环通路&可以直接开发测试程序&通过边扫端口%控制g C ,#%$?实现测试覆盖%对于开环信号测试&根据被测电路板的信号类型和数量&适配板选择可编程逻辑器件]N +%"&H =/%##作为边界扫描主控元件&搭配外围电路实现被测电路的测试需求覆盖)图$!验证板测试方案示意图%"边扫主控软件H 1J 2_L K 3O 导入被测板和适配板的网表文件和模型文件&通过配套硬件开发套件]C /M ,%#控制被测板和适配板上的边扫器件Y ]<9和C ]:-&再通过可编程器件的接口控制&实现软硬件接口的匹配$""?]N +%"&H =/%##的部分/.引脚以信号调理或者直接的方式&通过适配板连接器连接至被测板连接器&实现被测电路板开环数字信号的测试$$"针对被测电路多路运算放大器和9-的测试需要&适配板设置-9芯片*电流+电压运算放大器*开关阵列等&通过边扫端口"控制?]N +%"&H =/%##&实现-9信号的输出&进而通过开关阵列和连接器连接至被测电路9-采集通道&通过边扫端口%控制g C ,#%$?实现模拟信号的测试$,"针对被测电路差分信号的测试需要&适配板设置相同的差分电路&单端信号接边界扫描芯片&差分信号通过连接器连接至被测电路的差分通道$*"放置供电连接器&直连程控直流电源的输出通道&进而通过适配板连接器实现被测电路的供电%@?!边界扫描测试流程开发为了完成被测电路板扫描链路完整性测试*互联测试*存储器测试*用户自定义测试等测试需要&边界扫描测试流程开发流程图如图,所示&依次为边扫测试工程新建*网表文件和模型文件的导入*扫描链路测试程序开发*互联测试程序开发*存储器测试程序开发$用户自定义测试程序开发*测试程序的编译和保存等%测试流程开发前&!投稿网址 W W W!0O 01A U3Z !1L Q!!计算机测量与控制!第$%""""""""""""""""""""""""""""""""""""""""""""""""""""卷#%""!#需要提前做一些准备工作)备好被测电路板和适配板的原理图*网表文件*边扫器件的^H -:模型*非边扫数字器件的测试模型等%图,!边界扫描测试流程开发流程$`$`%!边扫测试工程新建工程新建用于为整个工程建立统一管理&同时导入和编译边扫器件的^H -:模型&为后续测试工作做准备&工程新建步骤如下)%"启动H 1J 2_L K 3O 边界扫描开发程序$""在弹出的软件启动向导界面单击,1A L O D -1,<L 6L6I D 426D K S J 1D-进入边扫测试主界面&H 1J 2_L K 3O 自动识别已连接到主机的边扫开发套件]C /M ,%#$$"单击菜单栏,7K L 0D 16-1,2D W -&在新建工程对话框填入工程名称以及存放路径&进行工程创建$,"填入工程设计名称&并手动创建扫描链路)分别添加添加边扫器件的^H -:模型+%"&O T %##`X O P 和V 1,#%$D /7G""$`X O P &并编译检查模型文件是否正确$*"建立><:%`I G A 文件&包含上述的两个^H -:文件&用于描述了测试板的边界扫描器件以及扫描链路信息&并再次编译&根据报告提示进行查看或修改&完成边扫测试工程的建立&><:%`I GA 建立完成的界面如图*所示%图*!新建成功的`I GA 文件$`$`"!网表和模型文件导入H 1J 2_L K 3O 软件支持多个电路板的网表文件自动合并&便于多个电路板的扫描链路集中统一管理&提高了测试效率%网表和模型文件导入步骤如下)%"软件菜单栏单击,P D O 4G2-1,2D 6A 4O 6-$""分别导入被测板和适配板网表文件!也可以提前将被测板原理图和适配板原理图合并&导入一个统一的网表"$$"网表文件添加成功后进行编译&根据报告提示进行查看或修改&完成网表文件的导入$,"指定网表文件中那些的电源和地线网络&测试时忽略该网络的测试$*"导入可以互联测试的非边扫器件模型文件&进行器件位号和模型的关联&并设置每个元器件的测试类型&如协议簇测试*忽略测试等&设置完毕后完成模型文件的导入%$`$`$!扫描链路完整性测试程序开发扫描链路完整性测试可以检测边扫框架的物理故障&比如测试总线*[9]控制器等%同时还可以验证工程建立之初所描述的扫描链路顺序是否正确%H 1J 2W L K 3O 自动产生链路测试集&通过之前的描述&来报告故障位置%扫描链路完整性测试开发步骤如下)%"在H 1J 2W L K 3O 主界面下双击1K D J 6DJ 2J 164L 2栏下的O 1J 27J 6I R D K 4S U &弹出P D S 42D O 1J 27J 6I R D K 4S U J164L 2O 对话框$""在弹出的P D S 42D O 1J 27J 6IR D K 4S U J 164L 2O 对话框中自动罗列测试工程新建过程中导入的两个边扫器件扫描链路&如图)所示$$"在[J K GD 6H 1J 2]J 6I !O "中通过勾选左侧复选框进行边扫链路选择&如果两个同时勾选&软件则会将被测板边扫链路和适配板边扫链路打包成同一个链路进行集中测试$,"在.764L 2O 中可以对要进行的边界扫描测试项进行选择&比如^E ]9H H */-C .-?*F H ?\C .-?*边扫链路长度等$*"单击右上角的编译按钮&查看编译报告&如果编译失败则根据报告窗口信息提示进行修改&直到编译通过为止!有警告也算编译通过"&编译通过后完成扫描链路完整性测试的开发%图)!扫描链路选择$`$`,!互联测试程序开发互联测试允许测试边扫器件互联或者边扫器件与非边扫器件的互联&互联测试可以检测开路*短路*固高固低!投稿网址 W W W!0O 01A U3Z !1L Q第%%期王!晴&等)""""""""""""""""""""""""""""""""""""""""""""""""""""边界扫描在数模混合电路板级测试中的设计与应用#%"$!#或者桥接故障%实际的被测电路中&基本都存在大量的非边扫器件&他们都会与边扫器件构成关联%测试过程中&如果测试程序不能识别非边扫器件&可以将其相关的网络暂时挂起&互联测试时忽略该网络$如果提前准备好了非边扫器件的模型文件&或者这些非边扫器件只是一些简单的缓冲器件*路由选择器件&可以通过互联测试中的簇测试进行测试%互联测试开发步骤如下)%"在H 1J 2W L K 3O 主界面下双击1K D J 6D J 2J 164L 2栏下的426D K 1L 22D 16&弹出P D S 42D J 2426D K 1L 22D 16J 164L 2对话框$$"此时P D S 42D J 2426D K 1L 22D 16J 164L 2界面的Q L P D A P D M R 41D 和P D S 42D 1L 2O 6K J 42O 可能处于非激活状态%进行编译并查看编译报告&如果编译失败则根据报告窗口信息提示进行修改&直到编译通过为止!有警告也算编译通过"$,"单击Q L P D A P D R 41D 打开P D R 41DX K L W O D K 对话框&对非边扫器件进行P D R 41D6U 7D 设置)电容设置为1J 7J 146L K *电阻设置为K D O 4O 6L K 等$*"关闭P D S 42D J 2426D K 1L 22D 16J 164L 2对话框&在边扫主界面可以看到一个名为426D K 1L 22D 16%的互联测试项&将边扫控制的[9]%和[9]"端口分别连接至被测电路板和适配板即可执行互联测试%$`$`*!存储测试程序开发由于被测存储器件没有找到测试模型&所以根据芯片手册的时序逻辑&通过用户自定义的方式进行测试开发&测试步骤如下)%"在H 1J 2W L K 3O 主界面单击P D O 4G21X B O D O 来进行测试总线定义&用于测试存储器的地址写和数据读$""点击2D W 框&创建一个&位数据总线&并打开P D MS 42D JX B O 对话框进行数据总线与存储器数据引脚的匹配设置&在X B OQ J 2J G D K 界面为已经定义的数据总线设置使能控制端$$"点击2D W 框&创建一个%"位地址总线&并打开P D M S 42D JX B O 对话框进行地址总线与存储器地址引脚的匹配设置&在X B OQ J 2J G D K 界面为已经定义的地址总线设置使能控制端$,"双击边扫软件主界面1K D J 6DJ 2J 164L 2下的Q J 1K L &进行测试代码的编辑&编辑完保存关闭$*"在返回的P D S 42D JQ J 1K L J 164L 2界面的6J K G D 6栏下选择D 264K D 7J 6I &并进行编译&查看编译报告&如果编译失败则根据报告窗口信息提示进行修改&直到编译通过为止!有警告也算编译通过"$)"编译通过后保存&完成存储测试程序的开发%$`$`)!用户自定义测试根据$`$`,节存储器测试程序开发步骤&编写Q J 1K L 专用测试代码&实现被测电路板的运算放大器和9-等器件的测试%@A !边界扫描测试程序执行测试程序开发完毕后&连接验证板和边界扫描控制器&利用H 1J 2W L K 3软件进行测试程序执行的步骤如下)%"在H 1J 2W L K 3O 主界面单击菜单栏[..:1O D A D 16I J K P W J K D&选择测试台边扫仿真器件]C /M ,%#$""通过程控直流电源给被测板和适配板供电$$"给被测板加电后选择边扫工程文件下的J 164L 2&单击X B 4A D M K B 2&执行测试并查看结果%A !测试结果与分析为了便于测试程序的自动化运行&通过主控计算机专用测试软件&对H 1J 2W L K 3软件进行二次集成开发&自动调用程控直流电源进行供电&自动调用边界扫描测试程序执行并上传测试结果%被测电路板最终测试报表如图+所示)第%!$项为电路板供电测试&首先判断电路板正常工作的功率是否满足要求$第,!*项为被测电路板和适配板上的边扫器件的扫描链路测试&检查边扫器件是否有故障$第)项为互联测试&检查边扫器件互联和边扫器件与有模型的非边扫器件的互联&判断互联测试的元器件有无开短路*固高固低或者桥接等故障$第+!,"项为用户自定义测试&通过编写测试脚本检查没有模型的非边扫器件的功能是否正常$第,$项为存储器测试%每一项测试记录均设定测试结果的合格判据&自动给出测试结果&可为电路板功能测b 试和故障诊断提供有力支撑%图+!被测电路板测试报表为了进一步验证测试程序的有效性&通过人为焊接方式制造了$处g C ,#%$?的/.引脚短路故障*%处存储器地址引脚短路故障和%处总线缓冲芯片的开路故障%通过测试程序执行&均成功检测出故障并定位故障位置&进一步验证了边界扫描测试系统设计的正确性%B !结束语本文提出的边界扫描测试系统设计方法&适用于不利用!下转第%$#页"!投稿网址 W W W!0O 01A U3Z !1L Q!!计算机测量与控制!第$%""""""""""""""""""""""""""""""""""""""""""""""""""""卷#%$#!#参考文献'%(王占选&陈嘉恒&王!晴!基于仿真的电路板级故障诊断测试方法'((!计算机测量与控制&"#"#&"&!%")"%"*!'"(李光升&欧!博&石海滨!现代模拟电路故障诊断技术发展综述'((!计算机测量与控制&"#%'&"+!*")*&!'$(胡!梅&攀!敏!一种模拟电路功能模块故障诊断的方法'((!电子测量与仪器学报&"#%*&*!"'"))+))&,!',(迮良佳!模拟电路信号特征分析及故障诊断算法优化'-(!桂林)桂林电子科技大学学&"#"%)%*!'*(姜云威!面向模拟电路故障诊断的深度学习方法研究'-(!桂林)桂林电子科技大学学&"#"")%,!')(幸!敏&杨秀谦&龙祖连!基于仿真技术的模拟电路教学演示系统'((!科技论坛&"#""&))%"%%"$!'+(孙!虎!基于故障字典技术的模拟电路故障诊断系统设计'-(!成都)西南石油大学&"#%&)%$!'&(史雨缘&徐立升!电路仿真技术在电路板修理中的研究与应用'((!航空维修与工程&"#%'&%")***&!''(刘春霞&徐爱强&王怡苹&等!基于C ?N 的故障字典诊断模型的建立与g N :描述'((!计算机测量与控制&"#%*&"$!%%")$)%$$)%*!'%#(张雪敏!电子电路仿真技术在集成电路设计中的应用'((!集成电路应用&"#"$&$!,#")"#"%!'%%(何朝稢&于文震&郑元珠!基于_]??M \Y 的模拟电路故障诊断'((!计算机测量与控制&"#"%&"'!&")$%$)!'%"(马春斌&黄!文&李宗泽!基于多种图像的电路板故障诊断系统研究'((!计算机测量与控制&"#""&$#!$")%*%&!'%$(崔!江&王友仁!一种新颖的基于混合故障字典方法的模拟故障诊断策略'((!电工技术学报&"#%$&"&!,")"+""+&!'%,(夏敏芳&刘!牮!基于]H 741D 与:N 算法的模拟电路故障诊断方法'((!电子科技&"#%*&"&!%#")$&,#!'%*(马!敏&刘成中&曾钰琴!电路故障诊断实验教学的探索与创新'((!实验科学与技术&"#"#&%&!*")&*)$!'%)(韩!伟&刘志男&黄文浩&等!模拟电路故障诊断'((!中国科技信息&"#%'!%")$,$*!'%+(杨焕峥&崔业梅&杨国华&等!基于神经网络的模拟电路故障诊断的仿真研究'((!长沙航空职业技术学院学报&"#"#&"#!,")))+"!'%&(周启忠&谢永乐&徐!娟!模拟电路的故障诊断与参数辨识代数方法'((!哈尔滨工程大学学报&"#%+&$&!,")*'*)#%!'%'(董江涛&朱!琳&巨小微!超容差条件下的电路软故障信号诊断方法研究'((!无线电工程&"#"%&*%!+"))"")"+!'"#(吴!凡&张!莉!基于小波神经网络的模拟电路故障诊断技术'((!计算机测量与控制&"#%,&""!%%")''''''''''''''''''''''''''''''''''''''''''''''''''''$*"%$*",!!上接第%"$页"外部信号源*信号采集设备的条件下&仅依靠主控计算机*边界扫描测试软件*边界扫描硬件套件以及供电电源&通过设计专用测试适配板开展被测电路的全流程测试%通过实际测试&验证了设计的可行性&为数字电路板和简单的数模混合电路板的测试提供了实用的测试方法和手段&具有很好的应用价值%不足之处在于&对于较为复杂的非边扫器件和模拟器件的测试&需要依靠用户对器件的清晰把握并编写用户自定义测试代码&对其本身的技术能力要求比较高%参考文献'%(刘云久!雷达数字电路板故障诊断方法研究'-(!南京)东南大学&"#%)!'"(柳!颖&蔡永招!基于H C 9;_.\d H 的模数混合电路板测试程序集设计'((!计算机测量与控制&"#"%&"'!$")%#%$!'$(曹子剑&佘美玲!边界扫描测试在数字电路自动测试系统中的研究与应用'((!计算机测量与控制&"#%*&"$!+")"$%%"$%+!',(李!洋!基于边界扫描技术的电路板测试研究'-(!北京)清华大学&"##&!'*(尤!路!基于H C 9;_.\d H 的边界扫描测试系统设计'((!信息通信&"#%*&%,*!,"))&)'!')(刘!军!基于边界扫描技术的]C ^测试'((!中国科技信息&"#%#&%)!&")%$#%$"!'+(王鏖縮!基于([9<标准的边界扫描测试技术的分析与研究'-(!西安)西安电子科技大学&"#%,!'&(/???H 6J 2P J K P S L K[D O 6911D O O]L K 6J 2P^L B 2P J K UM H 1J 29K 1I 4M 6D 16B K D )/???H 6P %%,'`%"#%$'@(!"#)%$%,,,!''(刘九洲&王!健!边界扫描测试技术发展总数'((!电光与控制&"#%$!""),),'!'%#(张文广&周绍磊&李!新!边界扫描技术及其在]C ^可测性设计中的应用'((!计算机测量与控制&"##)&%,!)")+%$+%*!'%%(钟春丽!基于边界扫描的故障测试诊断系统的设计与实现'-(!郑州)解放军信息工程大学&"#%$!'%"(李!洋!基于边界扫描技术的复杂数字电路板的可测试性分析'-(!西安)西安电子科技大学&"##&!'%$(韦翠荣&颜学龙&尚玉玲!边界扫描测试生成与故障诊断的研究与实现'((!计算机工程&"#%*&%!,%")$#$$#&!'%,(陆云云!基于边界扫描技术实现电路板全面测试'((!国外电子测量技术&"#%)&'!$*")%*!'%*(王宏伟!基于:9H 9\和H C 9;_.\d H 软件的雷达电子设备检测系统的设计'((!信息科技&"#%&&%&!'")')'+!'%)(柳!颖&徐小杰!基于边界扫描技术的某引俄指控系统复杂电路板的[]H 开发'((!舰船电子工程&"#%'&$'!+")%%'%""!'%+(陈宝华&宋晓东&王新洲!基于边界扫描的一种电路板测试技术'((!中国修船&"#%*&))%*%&!'%&(张学锋&王彤威&王国龙!边界扫描技术在微处理器电路板测试与诊断的研究'((!计算机测量与控制&"#%#&%&!)")%"*#%"*"!'%'(刘萌萌&苏!峰&宋成军!装备电子设备边界扫描系列标准及测试性设计技术研究'((!计算机测量与控制&"#%+&"*!"")&%%!'"#(梁晓芬!基于边界扫描的某型电路板测试方法研究'((!科技创新与应用&"#%+&"*!"")&%%!!投稿网址 W W W!0O 01A U3Z !1L Q。

93k集成电路测试系统校准原理及实现方法研究

1 引 言

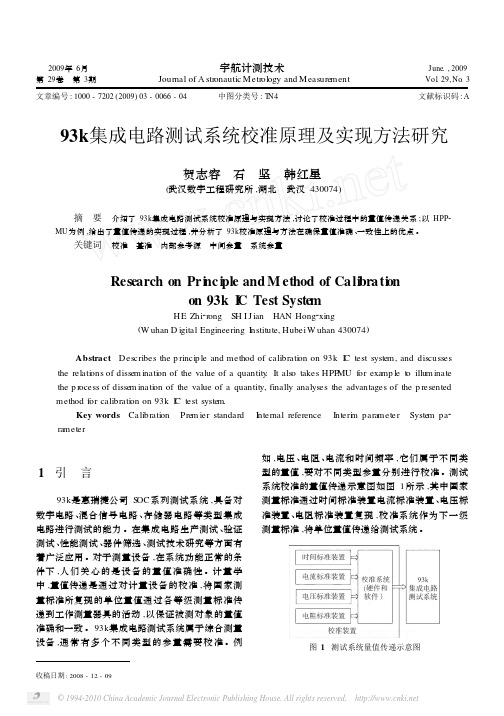

93k是惠瑞捷公司 SOC系列测试系统 ,具备对 数字电路 、混合信号电路 、存储器电路等类型集成 电路进行测试的能力 。在集成电路生产测试 、验证 测试 、性能测试 、器件筛选 、测试技术研究等方面有 着广泛应用 。对于测量设备 ,在系统功能正常的条 件下 ,人们关心的是设备的量值准确性 。计量学 中 ,量值传递是通过对计量设备的校准 ,将国家测 量标准所复现的单位量值通过各等级测量标准传 递到工作测量器具的活动 ,以保证被测对象的量值 准确和一致 。93k集成电路测试系统属于综合测量 设备 ,通常有多个不同类型的参量需要校准 。例

·67·

2 93k集成电路测试系统校准相关概念

93k集成电路测试系统校准过程中 ,对量值可 进行如下的概念划分 [ 1 ] 。

1)内部参考源 93k系统中 ,可直接通过外接仪表进行检定的 交 /直流参量 ,包括参考时钟 、参考电压 、参考电阻 、 测量 /驱动电压 、测量 /驱动电流 。 2)中间参量 中间参数是溯源参数用于量值传递的媒体 ,每 种系统的结构和数量不尽相同 。但对客户而言 ,它 们是透明不可见的 。 3)系统参量 93k系统中 ,用于在通道末端复现微电子参数 的交 /直流参量 ,可通过已溯源的内部参考源实现 检定 。 93k校准过程中 ,内部参考源 、中间参量 、系统 参量间的量值传递关系如图 2所示 。

关键词 校准 基准 内部参考源 中间参量 系统参量

Research on Pr inc iple and M ethod of Ca libra tion

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

提高修调的准确度。

试单位是属于晶圆的中间区域,还是周边区域,从

本文介绍了一种修调方法,在晶圆测试中可以

而使晶圆中间区域的修调目标值和周边区域的修调

有效地解决在电路中因修调参数的多样化而导致了

目标值能够分开。

测试时间的成倍增长问题,并且这些方法较为简练 可靠,缩短测试时间。 2晶圆测试中修调实现方法

在晶圆测试过程中,以每次探针卡能够覆盖的 所有芯片为一个测试单位。图1是探针卡上位为一

also saves more time for adjusting and testing. It improves the efficiency of testing, reduces the cost of

testing products, and effectively guarantees the competitiveness of products. Index Terms — IC manufacturing, trimming, target value, test unit, probe card.

中图分类号:TN407 文章编号:1674-2583(2019)08-0064-02 D01: 10.19339/j.issn.1674-2583.2019.08.022 中文引用格式:辛吉升,谢晋春,桑浚之.一种大规模集成电路测试的修调实现方法[J].集成电路应用, 2019, 36(08): 64-65.

(4) 将步骤(3)中获得的平均值作为该晶

圆上中间区域内部所有测试单位内的所有芯片的修 调目标值,同时写到芯片中(如采用并行写入的方 式),供芯片在后续的测试以及正常工作中使用。

2.2晶圆周边区域的修调目标值的设定方法 (1)在每枚晶圆开始测试前,先在晶圆的周

工艺与制造 Process and Fabrication

一种大规模集成电路测试的修调实现方法

辛吉升,谢晋春,桑浚之 (上海华虹宏力半导体制造有限公司,上海201203 ) 摘要:提出了大规模集成电路在晶圆阶段测试中的一种修调实现方法。这种方法的实间。它提升了测试效率,降低了产品的测试成 本,使产品的竞争力得到有效保障。 关键词:集成电路制造;修调;目标值;测试单位;探针卡。

Abstract — In this paper, a trimming method for large scale integrated circuits in wafer stage testi ng

is proposed. The implementation of this method not only ensures the quality of the tested products, but

2.1晶圆中间区域的修调目标值的设定方法

(1)在每枚晶圆开始测试前,先在晶圆的中

间区域内部选定2个以上的能够代表晶圆面内分 布特征的位置。如上、下、左、右、中间这5个 位置(图2),每个位置选择一个测试单位。图

基金项目:上海市经济和信息化委员会软件和集成电路产业发展专项基金(1500223)。

作者简介:辛吉升,上海华虹宏力半导体制造有限公司,量产开发部部长,硕士,研究方向:集成电路制造。

(lower limit)后,每个芯片存在5个不同的 参数需要进行修调的示意图。

flj

图3是中心区域的修调目标值

另外,本节步骤(2)和下节步骤(2)中,

需要修调的参数可以为芯片电路的基准电压、基准 电流、基准频率以及以它们为参照而生成的其他参 数等。

(3) 所有测试单位的目标值获得之后,取其 平均值。

的,有的芯片的这个特性需要负的修调,而有的则

需要正的修调,导致每个芯片的修调值发生不一致

的情况。

但是大型逻辑测试仪器在测试芯片时,从生产

的角度考虑,往往采用大规模的同时测试,这与上

述修调的目的相矛盾,为了兼顾二者的平衡,需要

找到一种更有效的办法,在保证大规模量产的同时

通过技术判断,能够分析出待需要检测的测

试时间并保障测试品质是一项具有挑战性的任务。

个测试单位可为32个芯片。其他探卡同测数及

随着产品集成度的不断增长,产品日趋复杂,

测试单位例此可知。

产品相关参数精度要求不断变高。现有大规模集成

电路在进行测试时,经常出现某些芯片的参数需要 修调〔2]。因为生产的原因,这些参数的本征值存在

差别,需要修调到一定的范围内。为了达到这个目

收稿日期:2019-06-10,修回日期:2019-07-10.

64 |集成电路应用 第36卷第8期(总第311期)2019年8月

Process and Fabrication I 工艺与制J造

2是测试前在晶圆中间和周边分别选择几个有代表 性的测试单位进行目标值的分析和定义的示意图。

(2)晶圆开始测试时,先移动探针台托盘对 应到探针卡对应的上述测试单位。如上、下、左、 右、中间这5个位置上的5个测试单位,对每 个单位中的每个芯片上的每个需要修调的参数进 行测试,对参数测试数据进行分析,然后将其取平 均值,从而获得与该测试单位相对应的修调目标 值(图3)。其中,该修调目标值由电路设计人 员根据产品的特性需求来进行定义。图3是中心 区域的修调目标值为上限(upper limit)、下限

1引言

次能够扎到16个芯片时,该16个芯片为一个

测试是集成电路的关键技术之一,是集成电路 质量保障的主要技术手段。测时间过长是其中的需 求一个重要问题之一[1],如何优化测试方法缩减测

测试单位的示意图。如图1所示,探针卡上位为 一次能够扎到16个芯片时,该16个芯片为一 个测试单位。如果探针卡为32 DUT同测,那么一

A Method of Trimming for Large Scale Integrated Circuits Testing

XIN Jisheng, XIE Jinchun SANG Junzhi (Shanghai Huahong Grace Semiconductor Manufacturing Corporation, Shanghai 201203, China.)