第10讲——-码敏化和电子存储器测试 超大规模集成电路测试技术课件

超大规模集成电路.pptx

第29页/共155页

1)P阱CMOS集成电路工艺过程简介

一、硅片制备 二、前部工序

Mask 掩膜版

CHIP

29

第30页/共155页

• 掩膜1: P阱光刻

Si-衬底

P-well

具体步骤如下: 1.生长二氧化硅:

SiO2

Si-衬底

30

第31页/共155页

2.P阱光刻: 涂胶、掩膜对准、曝光、显影、刻蚀

§1 双极型(NPN)集成电路工艺 (典型的PN结隔离工艺)

1

第2页/共155页

思考题

1.与分立器件工艺有什么不同? 2.埋层的作用是什么? 3.需要几块光刻掩膜版(mask)? 4.每块掩膜版的作用是什么? 5.器件之间是如何隔离的? 6.器件的电极是如何引出的?

2

第3页/共155页

1.衬底准备 2.第一次光刻——N+隐埋层扩散孔光刻

18

第19页/共155页

1.P阱CMOS工艺

P阱CMOS工艺以N型单晶硅为衬底, 在其上制作P阱。NMOS管做在P阱内, PMOS管做在N型衬底上。

19

第20页/共155页

P阱CMOS工艺

电连接时,P阱接最负电位,N衬底接最正 电位,通过反向偏置的PN结实现PMOS器件和 NMOS器件之间的相互隔离。P阱CMOS芯片剖 面示意图见下图。

艺有时已不满足要求,双阱工艺应 运而生。

26

第27页/共155页

双阱CMOS工艺

• 通常双阱CMOS工艺采用的原始材料是在 N+或P+衬底上外延一层轻掺杂的外延层, 然后用离子注入的方法同时制作N阱和P阱。

27

第28页/共155页

双阱CMOS工艺

集成电路的认识与检测PPT课件

集成电路直接代换时,集成电路的功能、性能指标、封装形式、引脚用途、引脚序号和间隔等几 方面均相同。其中应该注意逻辑极性相同,即输出输入电平极性、电压、电流幅度必须相同。代换时 若输出不同极性AFT电压或者输出不同极性的同步脉冲的集成电路都不能直接代换,即使是同一公司 或厂家的产品,都应注意区分。性能指标是指集成电路的主要电参数、最大耗散功率、最高工作电压、 频率范围及各信号输入、输出阻抗等参数要与原集成电路相近。

集成电路的认识与检测

精选ppt课件2021

1

什么是集成电路

集成电路是将一个单元电路或者是多个单元电路的主要元器件或者全部的元器件 集成在一个单晶硅片上,并封装在特制的外壳中,具备一定功能的电路,其在结构上 已经组成了一个整体。

精选ppt课件2021

2

集成电路的分类

1、按功能结构分类

集成电路按其功能、结构的不同,可以分为模拟集成电路、数字集成电路和数/ 模混合集成电路三大类。

安装集成电路时,要注意方向不要搞错,否则,通电时集成电路很可能被烧毁。而且要注意,有 的单列直插式功放集成电路,虽型号、功能、特性相同,但引脚排列顺序的方向是有所不同的。

不同型号的集成电路,若型号前缀字母相同、数字不同集成电路的代换,只要相互间的引脚功能 完全相同,其内部电路和电参数稍有差异,也可相互直接代换;若型号前缀字母不同、数字相同的集 成电路,一般情况下,前缀字母是表示生产厂家及电路的类别,前缀字母后面的数字相同,大多数可 以直接代换。但也有少数,虽数字相同,但功能却完全不同,这样的不能代换。

模拟集成电路又称线性电路,用来产生、放大和处理各种模拟信号,其输入信号 和输出信号成比例关系。目前,在家电维修中或一般性电子制作中,所遇到的主要是 模拟信号。而数字集成电路用来产生、放大和处理各种数字信号。

超大规模集成电路技术基础课件

Part

03

超大规模集成电路制造工艺

制造流程

制造流程概述

超大规模集成电路的制造流程包 括晶圆制备、外延层生长、光刻 、刻蚀、离子注入、化学机械抛

光、检测与封装等步骤。

晶圆制备

晶圆制备是超大规模集成电路制造 的第一步,涉及到单晶硅锭的切割 和研磨,以获得所需厚度的晶圆。

外延层生长

外延层生长是指在单晶衬底上通过 化学气相沉积等方法生长出与衬底 晶体结构相同或相似的单晶层。

解决方案3

加强环保监管和提高环保意识:通过加强环保监管和提 高环保意识,推动超大规模集成电路制造行业的可持续 发展。

Part

04

超大规模集成电路封装与测试

封装技术

芯片封装

将集成电路芯片封装在管 壳内,以保护芯片免受环 境影响和机械损伤。

封装材料

常用的封装材料包括陶瓷 、金属和塑料等,每种材 料都有其独特的优点和适 用范围。

制造设备

超大规模集成电路制造中需要使用到各种复杂的设备和工具,如光刻机、刻蚀机 、离子注入机、化学机械抛光机等。

制造中的挑战与解决方案

挑战1

高精度制造技术的挑战:随着集成电路规模的不断缩小 ,制造精度和工艺控制的要求也越来越高,需要不断改 进制造工艺和研发新的制造技术。

挑战2

制造成本的不断增加:随着技术不断进步,超大规模集 成电路的制造成本也在不断增加,需要寻求更经济、高 效的制造方法和工艺。

封装形式

根据集成电路的类型和应 用需求,有多种封装形式 可供选择,如DIP、SOP 、QFP等。

测试方法与设备

测试方法

包括功能测试、性能测试、可靠 性测试等,以确保集成电路的性

能和质量。

测试设备

集成运算放大电路PPT培训课件

随着便携式电子设备的普及,低功耗技术成为集成运算放大电路的 重要发展方向,有助于延长设备使用时间。

应用领域拓展

01

02

03

物联网应用

随着物联网技术的发展, 集成运算放大电路在传感 器信号处理、无线通信等 领域的应用越来越广泛。

医疗电子

集成运算放大电路在医疗 电子领域的应用逐渐增多, 如生理信号监测、医学影 像设备等。

详细描述

在高精度测量系统中,集成运算放大电路主要用于信号 调理和信号转换,如电压跟随、跨阻放大等。为了获得 更高的测量精度和更低的误差,需要选用具有低噪声、 低失真、低漂移等性能指标的高品质集成运算放大器, 并通过合理的电路设计和参数调整,实现高精度的测量 结果。同时,还需要注意集成运算放大器的供电电源和 接地方式,以减小电源噪声和接地干扰对测量精度的影 响。

详细描述

音频信号处理应用中,集成运算放大电路常被用于前置放大、功率放大等环节, 实现对声音信号的采集、传输、处理和播放。通过合理选用集成运算放大器,可 以有效地提高音频信号的质量,增强声音的清晰度和动态范围。

案例二:传感器信号放大电路设计

总结词

传感器信号放大电路是集成运算放大电 路的又一典型应用,通过对传感器输出 信号的放大,实现信号的远距离传输和 精确测量。

解决方案

为提高集成运算放大电路的稳定性,可以采取一系列措施,如加入负 反馈、调整元件参数、改善电源供电等。

线性范围问题

总结词

集成运算放大电路的线性范围是 指输入信号在一定范围内时,输 出信号与输入信号呈线性关系。

详细描述

集成运算放大电路的线性范围受 到电子元件性能的限制,当输入 信号过大或过小,超过一定范围 时,输出信号与输入信号不再呈

集成电路测试PPT课件

7

故障的等效和从属

故障等效

s-a-1

A

B

&

C

s-a-0

Z

故障从属

s-a-0

A

B

&

C

s-a-1

Z

12.11.2020

故障类型与测试码

测试码 ABC Z 11 1 0

01 1 1 10 1 1 11 0 1

故障

A/0, B/0, C/0, Z/1 A/1,Z/0 B/1,Z/0 C/1,Z/0

8

基本概念2:测试向量和测试图形

故障:集成电路不能正常工作。 故障模型:物理缺陷的逻辑等效。

12.11.2020

5

故障举例

物理缺陷

逻辑等效

12.11.2020

6

逻辑门故障模型

固定值逻辑:所有缺陷都表现为逻辑门 层次上线网的逻辑值被固定为0或者1。 表示:s-a-1, s-a-0。

桥接 逻辑门故障模型的局限性

12.11.2020

f

(X)

•

d dxi

g(X)

g(X)

•

d dxi

f

(X)

d dxi

f (X)• d dxi

g(X)

d dxi

f

(X)

g(X)

f

(X)

•

d dxi

g(X)

g(X)

•

d dxi

f

(X)

d dxi

f (X)• d dxi

g(X)

12.11.2020

22

差分法

如果g(X)与xi无关,则可以简化为:

esets

Tester_Stro 2

2

集成电路测试概述PPT课件

寿命缺陷——电介质崩溃、电迁移 等。

封装缺陷——触点退化、密封泄露 等。

第6页/共48页

集成电路的不正常状态

• 缺陷(defect) • 故障(fault) • 失效(failure)

集成电路的缺陷导致它的功能发 生变化

第7页/共48页

➢ 成品检测进行随机抽 样,对样品做入厂测 试。

第36页/共48页

按测试目的分类

•

验证测试(特性测试)

•

生产测试

•

验收测试(成品检测)

•

使用测试

系统RMS(Reliability ,Maintainability,Serviceability) 技术的需要。使用测试是在器件使用期间进行的测 试,包括对器件进行各类可靠性试验后的评价测试, 系统使用过程出现故障进行故障芯片检测和定位所 进行的测试等

测试框架结构

➢ 在生产阶段,管芯制 成后和封装后都要进 行电性能和参数测试, 包括性能鉴定、可靠 性试验和失效分析等 测试。 ➢ 作用: 对产品 进行挑 选和分 级;剔 除失效 的芯片;

第44页/共48页

测试框架结构

测试的费用往往会随器件级、板级、 系统级和现场故障寻迹维修测试, 按每级10倍的递增量而逐级递增,

故障检测和故障诊断的首要问题

• 测试图形的生成 • 测试生成过程要能迅速准确地得到测试码,并且能判断测试码的有效性,还要保证测试码尽量简单,必须

讨论测试码与测试图形的各种生成方法和集成电路的各类故障模型。

第19页/共48页

第20页/共48页

• 集成电路测试的基本原理 • 集成电路故障与测试 • 集成电路测试过程 • 集成电路测试分类 • 集成电路测试的意义与作用 • 半导体技术的发展对测试的影响

超大规模集成电路的测试技术

集成电路测试技术的发展与现状集成电路的复杂性在日益增加,自从芯片系统(SOC)实现之后,各种知识产权(IP)模块大量集成在同一芯片内,包括逻辑电路、存储器、模/数和数/模转换器、射频前端等等。

它们的功能互不相同,测量用的算法、定时周期、时序、供电电压都有很大差异,给自动测试系统带来新的挑战。

集成度增加和功能多样的SOC在消费量最大的产品中,如移动通信手机、微控制器、监视器、游戏机等中广泛使用,销售量攀升的同时价格不断地下降,但测试费用却居高不下。

超大规模集成电路不但构造精细、集成度高,而且是经过许多道工序流程制作而成的,难免存在着缺陷导致其不能正常工作。

因此,超大规模集成电路的测试对生产厂商和用户都具有重要意义。

目前的测试方法种类很多,各种测试方法均针对一定特性的故障。

研究发现,要证明所设计的芯片的正确性,在不同设计和生产阶段中才去的不同测试所花费的代价有非常大的差别,甚至可以达到几个数量级的差距,其示意图如图1。

从测试增长代价图可以看出,如果在设计阶段就多体现些主动性,就会极大的降低测试的难度和工作量,并能最大程度的改变测试仅仅将作为附属过程的被动性。

测试的基本原理是:将被测试的电路放在测试仪器上,测试设备根据需要产生一系列测试矢量信号,加到输入端,将得到的测试输出与预期输出进行比较,如果两者相等,表明测试通过。

反之,则不通过.在芯片设计及流片生产的各个阶段,经常需要测试来对得到的阶段性结果进行校验。

在芯片设计过程中,需要进行针对电路设计的测试,及模拟各种输入激励情况下电路的输出响应情况,还有各种参数值的范围,设计过程所依据的是迷你软件及工艺厂家后,厂家在流片的各个主要步骤完成后也会进行测试,其目的除了进一步验证设计的正确性,还要测试生产过程中出现的各种不确定因素带来的影响。

而生产阶段又包括样片和大批量生产两种,每种生产阶段都需要具备这些测试环节。

测试结果的可靠性取决于测试信号的正确性和完整性。

大规模集成电路PPT课件

A0 A0

地 址 译

…

码

An-1

器

存储矩阵

R/W 读/ 写控制电路

CS

…

I/O0 I/O1 … I/Om-1

2n m RAM 的结构图

大规模集成电路

RAM 与 ROM 的比较

相 ★ 都含有地址译码器和存储矩阵 同 处 ★ 寻址原理相同

★ ROM 的存储矩阵是或阵列,是组合逻辑电路。

ROM 工作时只能读出不能写入。掉电后数据

大规模集成电路

(3)编程方式:OE = 1,在 VPP 加入 25 V 编程电压,在地址 线上输入单元地址,数据线上输入要写入的 数据后,在 CS 端送入 50 ms 宽的编程正脉 冲, 数据就被写入到由地址码确定的存储单 元中。

(4) 编程禁止: 在编程方式下,如果 CS 端不送入编程正脉 冲, 而保持低电平,则芯片不能被编程,此时为编 程禁止方式,数据端为高阻隔离态。

大规模集成电路

二、集成 RAM 举例

A6 1 A5 2 A4 3 A3 4 A0 5 A1 6 A2 7 CS 8 GND 9

Intel 2114

18 17 16

VDD A7 A8

A0 ~ A9 为地址码输入端。 4 个 I/O 脚为双向数据线,用 于读出或写入数据。

15 14 13 12

A9 I/O I/O I/O

二、半导体存储器的类型与特点

只读存储器(ROM, 即Read-Only Memory)

随机存取存储器(RAM, 即Random AccessM计算既机能中读的自出检信程息序又、能初

信息而不能写入信息。它用于 存放固定不变的信息,断电后

写始化入程信序息便是。固它化用在于RO存M放中需的经。 常计 对算 计改机 算变接 机的通 硬信电 件源 系息后统,进,断行首自电先检运后和行其初它数始,

大规模集成电路测试

测 被测电路 试

响 应

ATE 比较

合格/ 不合格

BIST

理想结果

Rev.9

西安交通大学微电子系雷绍充

18

测试分类

验证测试、特性测试或设计诊断(Verification testing, characterization testing, or design debug)

一般用于检查设计和制造过程的正确性;

根据ITIS调查, 2009台湾IC制造制造业产值5766亿 元新台币,封装业产值1996亿元新台币,测试业产 值876亿元新台币,总产值达新台币1.249兆元。

全球半导体市场全年总销售值达2,263亿美元。

二、测试技术的发展

Eldred在1959年发表了第一篇关于组合电路的测试报告,应用于第一 代电子管计算机Datamatic-1000的诊断中 1966年,D..B.Armstrong根据Eldred的思想提出了一维通路敏化法 1966年,Roth提出了著名的D算法,并加以证明,其思想为最高点 1968年,Sellers提出了布尔差分法 1981年,Goel给出了改进D算法的PODEM程序 1983年, Fujiwara发表了FAN算法 1984年,Archambeau提出伪穷举法,为解决大型组合电路开辟新的途 径

29

功能测试

对建立的每一类故障模型,生成故障覆盖率高的 测试图形,然后测试CUT中每一个晶体管和每 一根连线。功能测试是非常耗时和开支大的, 是本书研究的主要内容。

Rev.9

西安交通大学微电子系雷绍充

30

错误和故障

错误

*被测电路不能正常工作

*原因:设计、映射、制造 和工作条件等方面的不 正确或不正常

34

测试方法分类标准 测试实施时间

《集成电路速查》课件

目录

• 集成电路基础知识 • 集成电路应用领域 • 集成电路设计流程 • 集成电路制造工艺 • 集成电路封装与测试 • 集成电路发展趋势与挑战

01

集成电路基础知识

集成电路定义

集成电路是将多个电子元件集成在一块衬底上,完成一定的电路或系统功能的微 型电子部件。

它采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布 线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个 管壳内,成为具有所需电路功能的微型结构。

新材料、新器件的研究

03

新型半导体材料如碳纳米管、二维材料等以及新型器件结构如

量子点、忆阻器等成为研究热点,有望在未来带来突破。

市场发展趋势

5G、物联网的推动

随着5G和物联网的快速发展,集成电路市场将迎来新的增 长点,特别是在通信、传感器等领域。

人工智能的普及

人工智能技术的广泛应用对集成电路的性能和功耗提出了 更高的要求,推动了AI芯片的发展。

3

刻蚀技术

通过刻蚀去除不需要的材料,形成电路和元件结 构。

05

集成电路封装与测试

封装材料

塑料

陶瓷

金属

复合材料

成本低,绝缘性好,但 耐热性差。

耐高温,绝缘性好,但 成本高,加工困难。

导热性好,但绝缘性差 。

结合多种材料的优点, 广泛应用于实际生产。

封装类型

SMD(表面贴装器件)

体积小,适合自动化生产,应用广泛 。

物理效应分析

分析集成电路版图中的物理效应 ,如寄生效应、温度效应等,并

进行修正。

04

集成电路制造工艺

制造材料

硅片

作为集成电路的基础材料,硅片的质量和纯度对 集成电路的性能和可靠性有着至关重要的影响。

电子线路第六版第10章半导体存储器与可编程逻辑器件简介课件

➢

➢

➢

➢

➢

➢

CPLD: Complex Programable Logid Device

FPGA: Field Programable Gate Array

PROM:Programable Read-Only Memory

PAL:Programable Array Logic

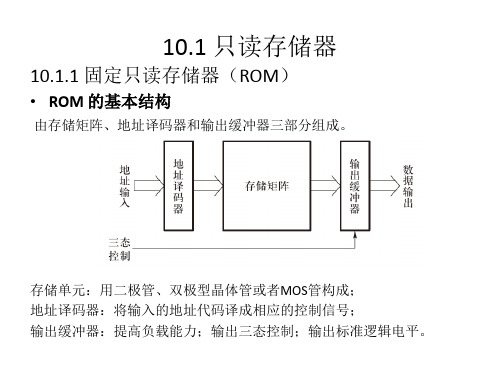

10.1 只读存储器

10.1.1 固定只读存储器(ROM)

• ROM 的基本结构

由存储矩阵、地址译码器和输出缓冲器三部分组成。

存储单元:用二极管、双极型晶体管或者MOS管构成;

地址译码器:将输入的地址代码译成相应的控制信号;

输出缓冲器:提高负载能力;输出三态控制;输出标准逻辑电平。

• ROM的工作原理(2位地址、4位输出的ROM电路为例)

计工具,具备了软硬件联合设计的能力,逐步向SOC平台过渡。

6)内嵌专用硬核

硬核(Hard Core)等效于ASIC电路。

为提高速度,主流的FPGA中都集成了专用乘法器;为适用通信总线与接

口标准,很多高端FPGA都集成了串并收发器(SERDES),可达到数十

Gbps的收发速度。

目前在很多高性能FPGA产品中,已经集成了数字信号处理器、甚至CPU

部分组成。

当读/写控制信号 R/W'=1时,

执行读操作;

当R/W' = 0时,执行写操作。

设有片选输入端 CS'。

当CS ' =0时RAM为正常工作状态;

当CS ‘ =1时输入/输出端均为高阻态。

• SRAM 的存储单元

由锁存器构成,靠锁存器的自保功能存储数据。

虚线框中为六管SRAM存储单元;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020/10/3

VLSI Test: Lecture 16

3

2.2 Type 2 Active NPSF 类型2积极NPSF

Used when diagonal couplings are significant, and do not necessarily cause horizontal/vertical coupling

/ 0 ( /1) -- Base cell fault effect indicating that base cannot change

2020/10/3

VLSI Test: Lecture 16

7

2.4 Static NPSF 静态NPSF

Static: Base cell forced into a particular state when deleted neighborhood contains particular pattern.

pattern makes base cell fail NPSF -- Neighborhood Pattern Sensitive Fault PNPSF -- Passive Neighborhood PSF SNPSF -- Static Neighborhood Pattern Sensitive Fault

➢Patterns: n×2k => (n×2k) / k ➢Only for SNPSF

2020/10/3

VLSI Test: Lecture 16

10

3.3 Two Group Method 两组法

Use checkerboard pattern, cell is simultaneously a base cell in group 1, and a deleted neighborhood cell in 2

➢traverses each graph arc exactly once ➢There is an arc between two nodes, if

and only if they differ by exactly one bit.

➢ANPSF & PNPSF (k×2k)

2020/10/3

Only for Type-1neighborhoods (duality)

2020/10/3

Lecture 10 Pattern Sensitive and Electrical Memory Test

第十讲:码敏化和电子存储器测试

2020/10/3

VLSI Test: Lecture 16

1

Contents 内容目录

1. Notation 符号说明

2. Neighborhood pattern sensitive fault (NPSF) 邻居码敏化故障

Both used for writing shorter patterns

Hamiltonian

➢traverses each graph node once ➢Differ by only 1 bit from their preceding

pattern

➢SNPSF (2k)

Eulerian

3. NPSF testing algorithms NPSF测试算法

4. Cache DRAM testing Cache DRAM测试

5. Functional ROM testing ROM测试

6. Memory Electrical Parametric Tests 存储器电子参数测试

7. Summary 小结

例子:Ci,j < 0, 1, 0, 1; - / 0> and Ci,j < 0, 1, 0, 1; - / 1>

2020/10/3

VLSI Test: Lecture 16

8

3 NPSF Testing Algorithm

--3.1Eulerian / Hamiltonian Graph Tour Sequences NPSF测试算法—欧拉/汉密尔顿图

Differs from active -- need not have a transition to sensitive SNPSF

Condition for detection and location: Apply all 0 and 1 combinations to k-cell neighborhood, and verify that each base cell was written.

2020/10/3

VLSI Test: Lecture 16

6

2.3 Passive NPSF 消极NPSF

Passive: A certain neighborhood pattern prevents the base cell from changing

Condition for detection and location: Each base cell must be written and read in state 0 and in state 1, for all deleted neighborhood pattern changes.

2020/10/3

VLSI Test: Lecture 16

2Leabharlann 1 Notation 符号说明

ANPSF -- Active Neighborhood Pattern Sensitive Fault APNPSF – Active and Passive Neighborhood PSF Neighborhood -- Immediate cluster of cells whose

VLSI Test: Lecture 16

9

3.2 Type 1 Tiling Neighborhoods 类型1瓷砖邻居

Write changes k different neighborhoods

Tiling Method: Cover all memory with nonoverlapping neighborhoods