IT-588 datasheet-201410

CTM1050datasheet

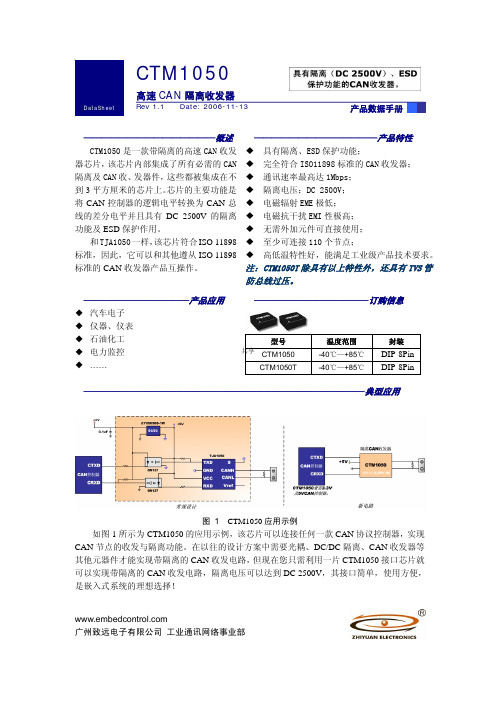

CTM1050广州致远电子有限公司 工业通讯网络事业部———————————————概述CTM1050是一款带隔离的高速CAN 收发器芯片,该芯片内部集成了所有必需的CAN 隔离及CAN 收、发器件,这些都被集成在不到3平方厘米的芯片上。

芯片的主要功能是将CAN 控制器的逻辑电平转换为CAN 总线的差分电平并且具有DC 2500V 的隔离功能及ESD 保护作用。

和TJA1050一样,该芯片符合ISO 11898标准,因此,它可以和其他遵从ISO 11898标准的CAN 收发器产品互操作。

——————————————产品特性 具有隔离、ESD 保护功能;完全符合ISO11898标准的CAN 收发器; 通讯速率最高达1Mbps; 隔离电压:DC 2500V; 电磁辐射EME 极低; 电磁抗干扰EMI 性极高; 无需外加元件可直接使用; 至少可连接110个节点;高低温特性好,能满足工业级产品技术要求。

注:CTM1050T 除具有以上特性外,还具有TVS 管 防总线过压。

————————————产品应用 ◆ 汽车电子 ◆ 仪器、仪表 ◆ 石油化工 ◆ 电力监控 ◆ ……—————————————订购信息型号温度范围 封装CTM1050 -40℃—+85℃ DIP-8Pin CTM1050T-40℃—+85℃DIP-8Pin————————————————————————————————典型应用图 1 CTM1050应用示例如图1所示为CTM1050的应用示例,该芯片可以连接任何一款CAN 协议控制器,实现CAN 节点的收发与隔离功能。

在以往的设计方案中需要光耦、DC/DC 隔离、CAN 收发器等其他元器件才能实现带隔离的CAN 收发电路,但现在您只需利用一片CTM1050接口芯片就可以实现带隔离的CAN 收发电路,隔离电压可以达到DC 2500V ,其接口简单,使用方便,是嵌入式系统的理想选择!共享修订历史版本日期原因Rev X1 2006/6/8 内部制定初稿Rev 1.0 2006/6/16 第一次发布Rev 1.1 2006/11/11 数据手册升级共享目录销售信息 (2)技术支持 (2)1. 功能简介 (3)2. 引脚信息 (4)2.1 CTM1050引脚信息 (4)3. CTM1050特性参数 (5)3.1 参数列表 (5)3.2 电气特性 (5)3.3 绝缘特性 (6)4. 机械尺寸 (7)4.1 CTM1050机械尺寸 (7)5. 电路连接 (8)5.1 CTM1050电路连接 (8)6. 声明 (9)共享销售信息如果需要购买本产品,请在办公时间(星期一至五上午8:30~11:50;下午1:30~5:30;星期六上午8:30~11:50)拨打电话咨询广州致远电子有限公司。

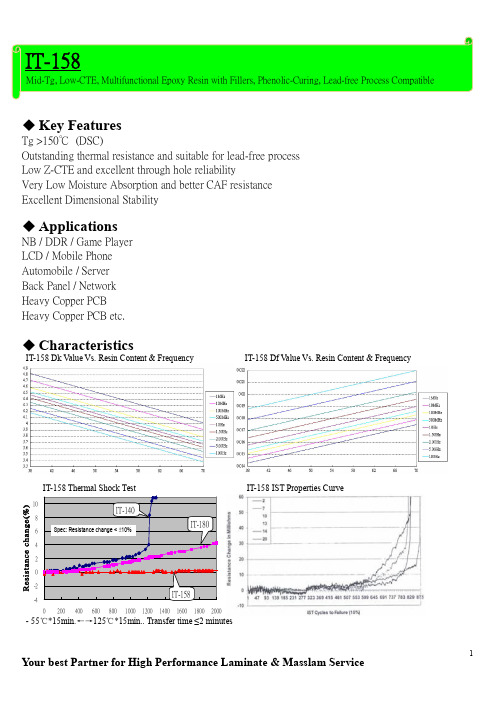

IT-158

IT-158

Mid-Tg, Low-CTE, Multifunctional Epoxy Resin with Fillers, Phenolic-Curing, Lead-free Process Compatible

Process Guideline

1. Prepreg Handling & Storage (1) Shelf life is at least 3 months when prepreg stored in a cool dry environment (Temperature: <20℃ Humidity: <50%).

4. Lamination Overview (1) Stacks must be prepared in lay-up room to avoid moisture absorption.

(2) Stacks with the core and prepreg are recommended to use the vacuum process for 30 minutes before heated. Recommended

Specification

180/90

<1.5 -

V-0 -

Units

Test Method

Days

AABUS

As per IPC-4412 or AABUS

%

2.3.19

AABUS

AABUS

rating

UL94

Ref. Para

3.17

3.9.2.2.8 1.1.7

3.10.2.1

2

Your best Partner for High Performance Laminate & Masslam Service

扫描特龙产品数据表:EXP-W10、EXP-PSU-SM、EXP-PSU-MM、EXP-PSU-LM

Wired expandersAt a glance...EXP-W10•Ten wired zones with 4 outputsEXP-PSU-SM• Ten wired zones with 4 outputs • 1 amp power supply• Capacity for a single 7Ah battery •Contained in a small metal housingEXP-PSU-MM• Ten wired zones with 4 outputs • 2 amp power supply• Capacity for a single 17Ah battery •Contained in a medium metal housingEXP-PSU-LM• Ten wired zones with 4 outputs • 3 amp power supply• Capacity for two 17Ah batteries •Contained in a large metal housingProviding installation flexibility, with ten zones and 4 outputs on board, the expanders give a choice of zone wiring options. These include FSL with various resistor values and 2 wire or 4 wire CC for takeover of legacy systems.A host of installer friendly options are designed to save time on installation and service visits. These include:•Decimal expansion system for more zones per expander. This also makes zone identification easier•Semi-Automatic addressing makes addressing much simpler. No address duplication or lost address links•Device locator to find any expander on the site by simply activating the buzzer inside the expander then walk the site listening for the buzzerA range of wired expanders designed and approved to be used as part of a security grade 2 or 3 system. Bus connected intelligent expanders are intended for use on all i-on control panels.Eaton is a registered trademark of Eaton Corporation.All other trademarks are property of their respective owners.Scantronic product data sheetProduct specificationCompare product compatibility with our easy to read chart: /security-works-withEatonElectrical SectorEMEA Route de la Longeraie 7 1110 Morges, Switzerland Eaton Electrical Products Ltd Security House,Vantage Point Business Village, Mitcheldean, Gloucestershire GL17 0SXTel: +44 (0)1594 545 400Email:***********************Web: 260 m m320 m m239 m m427 m m 160 mm。

浪潮信息技术(英信)服务器NF5488A5技术白皮书说明书

缓

存,支持超级电容掉电数据保护。

使用 后的可靠性远远高于传统机械硬盘,从而能够延长系统运行时间。

面板提供

指示灯、插式蓝牙 管理模块,

管理界面

提供关键部件指示状态,能够指引技术人员快速找到已经发生故障或存在故障风险的

组件,从而简化维护工作、加快解决问题的速度,并且提高系统可用性。

后窗面板提供

直连管理接口,支持

计算性能。 尺寸、冗余供电设计使其适用于更广泛的数据中心部署环境,特别适合于功

耗受限的机柜上架场景;同时

使用更加灵活的集群部署方案,能实现从硬件到

应用的集成部署。此外,系统内采用

供电方案,能效更高;分层分区域散热通道设

计以及智能 调控策略,可获得最佳的散热效率。

能够帮助 用户高效完成

基础设施和开发环境的构建,在享受更高计算性能的同时降低部署、运行成本。

支持灵活的 访问控制策略,提高 管理安全性。

能源效率

提供

功率的

铂金电源模块, 负载下电源模块效率高达 。

支持 电源冗余,支持交直流一体电源,提高电源转换效率。

高效率的单板 电源,降低 转 的损耗。

支持系统散热风扇智能调速、 智能调频,节能降耗。

全方位优化的系统散热设计,高效节能系统散热风扇,降低系统散热能耗。

琥珀色常亮: 发生保护类事件导致关机

琥珀色 闪烁: 发生告警类事件并维持工作

绿色 闪烁: 处于拔出系统状态,但有 输入

绿灯 状态

闪烁, 秒绿, 秒灭: 工作在冷冗余休眠

指示灯

状态说明 绿灯

闪烁:

工作在 刷新状态

风扇电源指示灯 风扇故障指示灯

按键及指示灯

正常亮绿色,风扇工作正常 发生故障时,不亮

Cmsemicon cms8s588x 增强型闪存8位1T 8051微控制器 数据手册说明书

CMS80F251x数据手册ArrayCMS8S588x数据手册增强型闪存8位1T 8051微控制器Rev.1.0.2请注意以下有关CMS知识产权政策*中微半导体(深圳)股份有限公司(以下简称本公司)已申请了专利,享有绝对的合法权益。

与本公司MCU或其他产品有关的专利权并未被同意授权使用,任何经由不当手段侵害本公司专利权的公司、组织或个人,本公司将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨本公司因侵权行为所受的损失、或侵权者所得的不法利益。

*中微半导体(深圳)股份有限公司的名称和标识都是本公司的注册商标。

*本公司保留对规格书中产品在可靠性、功能和设计方面的改进作进一步说明的权利。

然而本公司对于规格内容的使用不负责任。

文中提到的应用其目的仅仅是用来做说明,本公司不保证和不表示这些应用没有更深入的修改就能适用,也不推荐它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。

本公司的产品不授权适用于救生、维生器件或系统中作为关键器件。

本公司拥有不事先通知而修改产品的权利,对于最新的信息,请参考官方网站。

1. 产品特性1.1 功能特性◆兼容MCS-51的1T指令系统- 系统时钟频率最高支持48MHz- 机器周期最快支持1T SYS @ F SYS≤24MHz - 机器周期最快支持2T SYS @ F SYS=48MHz ◆内存- 程序FLASH:32K×8Bit- Data FLASH:1K×8Bit- 通用RAM:256×8Bit- 通用XRAM:2K×8Bit- 支持BOOT功能区,1K/2K/4K可选- 程序FLASH支持分区保护◆4种振荡方式- HSI-内部高速振荡:48MHz- HSE-外部高速振荡:8MHz/16MHz- LSE-外部低速振荡:32.768KHz- LSI-内部低速振荡:125KHz◆GPIO- 最多可达30个GPIO- 均支持上/下拉电阻功能- 均支持边沿(上升沿/下降沿/双沿)中断- 均支持唤醒功能◆中断源- 支持所有的外部端口中断- 7个定时器中断- 其它外设中断◆定时器- WDT定时器(看门狗定时器)- Timer0/1,Timer2,Timer3/4- LSE_Timer(支持休眠唤醒功能)- WUT(唤醒定时器)- BRT(串口波特率时钟发生器)◆循环冗余校验单元- CRC16(CRC16-CCITT)◆蜂鸣器驱动- 50%占空比,频率可自由设置◆PWM- 6通道PWM- 6个相互独立周期计数器- 支持独立/互补/同步/成组模式- 支持边沿对齐方式- 支持互补模式死区延时功能◆通信模块- 1xSPI(通讯速率最高可达6Mb/s)- 1xI2C(通讯速率最高可达400Kb/s)- 2xUART(波特率最高可达1Mb/s)- UART1可任意GPIO映射◆工作电压范围- 2.1V~5.5V◆工作温度范围- -40℃~105℃◆低压复位功能(LVR)- 1.8V/2.0V/2.5V/3.5V◆低压检测功能(LVD)- 2.0V~4.3V 8级可选◆高精度12位ADC- 最多可达30个AD外部通道- 参考电压可选(1.2V/2.0V/2.4V/3.0V/VDD)- 可检测内部1.2V基准电压- 支持硬件触发启动转换功能- 支持一组结果数字比较功能◆低功耗模式- 空闲模式(IDLE)- 休眠模式(STOP)◆支持96位唯一ID号(UID)- 每颗芯片有独立的ID号◆支持两线串行编程与调试1.2 产品对比注:(1)通过系统配置寄存器设置APROM和BOOT空间大小,APROM与BOOT空间总共最大为32K。

IT6251_Datasheet_v02

IT6251LVDS to DispalyPort 1.1a TransmitterPreliminary Datasheet Specification V0.2ITE TECH. INC.General DescriptionThe IT6251 is a high-performance single-chip De-SSC LVDS to DisplayPort converter. Combined with LVDS receiver and DisplayPort Transmitter, the IT6251 supports LVDS input and DisplayPort 1.1a output by conversion function. The build-in LVDS receiver can support single-link and dual-link LVDS inputs, and the build-in DisplayPort transmitter is fully compliant with DisplayPort 1.1a specification. With high speed LVDS RX, the IT6251 can support resolution up to 1080P and UXGA and 10-bit deep colors.In order to reduce the EMI noise on legacy system application, the traditional LVDS source will transmit differential signals with spread spectrum, but this spread spectrum does not be allowed for DisplayPort protocol. The IT6251 also build-in unique De-SSC ( De-Spread Spectrum ) function , it can help customers easily to adopt the IT6251 on the EMI-concerned platform, with SSC has been generated from LVDS source processors.Features ( LVDS RX )• Support LVDS Input modes: Single Link, Dual Link• Support input clock rate up to 165MHz• Support input color depth up to 10bit• Support De-SSC ( De-Spread Spectrum )• Support Data Mapping: Open LDI / JEIDA , VESAFeatures (DisplayPort TX)DisplayPort 1.1a transmitterCompliant with DisplayPort 1.1aSupporting two link speeds, HBR(2.7Gbps) and RBR(1.62Gbps).Various video input interface supporting digital video standards such as:18/24/30/36-bit RGB4:4:4Software programmable DispalyPort output swing and pre-emphasis levelEmbedded full-function pattern generatorMCCS over AUX channelIntelligent, programmable power managementFeatures ( Combined )• Support up to Full-HD/1080P , and WQXGA(2560x1600 RB) display format• Support deep color depth up to 10bit• 64-pin QFN (9mm x 9mm) package• RoHS Compliant ( 100% Green available )Ordering InformationModel Temperature Range Package Type Green/Pb free Option IT6251 0~70 64-pin QFN GreenPin DiagramFigure 1. IT6251 pin diagramPin DescriptionLVDS front-end interface pinsPin Name Direction Description Type Pin No. RXNA1 Analog LVDS first link negative input LVDS 17 RXPA1 Analog LVDS first link positive input LVDS 18 RXNB1 Analog LVDS first link negative input LVDS 19 RXPB1 Analog LVDS first link positive input LVDS 20 RXNC1 Analog LVDS first link negative input LVDS 22 RXPC1 Analog LVDS first link positive input LVDS 23 RXND1 Analog LVDS first link negative input LVDS 27 RXPD1 Analog LVDS first link positive input LVDS 28 RXNE1 Analog LVDS first link negative input LVDS 29 RXPE1 Analog LVDS first link positive input LVDS 30 RXNCLK Analog LVDS negative clock input LVDS 24 RXPCLK Analog LVDS positive clock input LVDS 25 RXNA2 Analog LVDS second link negative input LVDS 34 RXPA2 Analog LVDS second link positive input LVDS 35 RXNB2 Analog LVDS second link negative input LVDS 36 RXPB2 Analog LVDS second link positive input LVDS 37 RXNC2 Analog LVDS second link negative input LVDS 39 RXPC2 Analog LVDS second link positive input LVDS 40 RXND2 Analog LVDS second link negative input LVDS 42 RXPD2 Analog LVDS second link positive input LVDS 43 RXNE2 Analog LVDS second link negative input LVDS 44 RXPE2 Analog LVDS second link positive input LVDS 45Programming PinsPin Name Direction Description Type Pin No. SYSRSTN Input Hardware reset pin. Active LOW (5V-tolerant) LVTTL 7 PCSCL Input Serial Programming Clock for chip programming (5V-tolerant) LVTTL 14 PCSDA I/O Serial Programming Data for chip programming (5V-tolerant) LVTTL 15 PCADR Input Serial programming device address select LVTTL 13 HPD Input Hot Plug Detection (5V-tolerant) LVTTL 5DisplayPort front-end interface pinsPin Name Direction Description Type Pin No. TX3P Analog DisplayPort Lane 3 positive output DP 51 TX3N Analog DisplayPort Lane 3 negative output DP 50 TX2P Analog DisplayPort Lane 2 positive output DP 54 TX2N Analog DisplayPort Lane 2 negative output DP 53 TX1P Analog DisplayPort Lane 1 positive output DP 57 TX1N Analog DisplayPort Lane 1 negative output DP 56 TX0P Analog DisplayPort Lane 0 positive output DP 60 TX0N Analog DisplayPort Lane 0 negative output DP 59 TXAUXP Analog DisplayPort AUX channel positive signal DP 48 TXAUXN Analog DisplayPort AUX channel negative signal DP 47 XTALIN Analog DisplayPort AFE crystal input (27MHz) Analog 3 XTALOUT Analog DisplayPort AFE crystal output (27MHz) Analog 2Analog 62 REXT Analog External resistor for setting DisplayPort output level. Default tied toA VCC via a 820-Ohm SMD resistor.Misc. PinsPin Name Description Type Pin No. DBG0 NC LVTTL 8DBG1 NC LVTTL 9DBG2 NC LVTTL 10NC NC LVTTL 1 Power/Ground PinsPin Name Description Type Pin No. IVDD Digital logic power (1.8V) Power 6, 11, 32, 46 OVDD I/O Pin power (3.3V) Power 12A VCC18 DisplayPort analog frontend power (1.8V) Power 49, 52, 55, 58, 61 PVCC0 DisplayPort core PLL power (1.8V) Power 64PVCC1 DisplayPort core PLL power (1.8V) Power 63PVCC2 Filter PLL power (1.8V) Power 4A VCC LVDS frontend power (3.3V) Power 21, 38 ANVDD LVDS frontend analog power (1.8V) Power 16, 26, 33, 41 APVDD LVDS frontend PLL power (1.8V) Ground 31GND Exposed GND pad Ground 65Functional DescriptionBlock DiagramFigure 2. Functional block diagram of IT6251RXPA1/N RXPB1/N RXPE1/N RXPA2/N RXPB2/N RXPE2/NTX0P/NTX1P/NTX2P/NTX3P/NTXAUXP/NSYSRSTNPCADRPackage DimensionsFigure 3. 64-pin QFN Package Dimensions。

戴尔易安信 PowerEdge 服务器第二代 AMD EPYC 处理器的平衡内存说明书

WhitepaperBalanced Memory with 2nd GenerationAMD EPYC TM Processorsfor PowerEdge ServersOptimizing Memory PerformanceRevision: 1.4Issue Date: 4/21/2020AbstractProperly configuring a server with balanced memory is critical to ensure memorybandwidth is maximized and latency is minimized. When server memory is configured incorrectly, unwanted variables are introduced into the memory controllers’ algorithm, which inadvertently slows down overall system performance. To mitigate this risk of reducing or even bottlenecking system performance, it is important to understand what constitutes balanced, near balanced and unbalanced memory configurations.Dell EMC has published this brief to educate PowerEdge customers on what balanced memory means, why it is important and how to properly populate memory to 2ndGeneration AMD EPYC TM server processors for a balanced configuration.RevisionsDate Description12 September 2019 Initial release for 1st wave of AMD CPUs21 April 2020Includes all AMD CPU SKUs AcknowledgementsThis paper was produced by the following people:Name RoleMatt Ogle Technical Product Marketing, Dell EMC Trent Bates Product Management, Dell EMCJose Grande Software Senior Principal Engineer, Dell EMC Andres Fadul Software Senior Principal Engineer, Dell EMCTable of Contents1.Introduction (4)2.Memory Topography and Terminology (5)3.Memory Interleaving (6)3.1NPS and Quadrant Pairing (6)4.Memory Population Guidelines (9)4.1Overview (9)4.2Memory Channel Population (9)4.3Identical CPU and DIMM Parts (10)4.4Identical Memory Configurations for Each CPU (10)5.Balanced Configurations (Recommended) (11)6.Near Balanced Configurations (12)7.Unbalanced Configurations (13)8.Conclusion (19)9. References (19)1. IntroductionUnderstanding the relationship between a server processor (CPU) and its memory subsystem is critical when optimizing overall server performance. Every processor generation has a unique architecture, with volatile controllers, channels and slot population guidelines, that must be satisfied to attain high memory bandwidth and low memory access latency.2nd Generation AMD EPYC TM server processors, which will be referred to by their code name throughout this white paper, Rome processors, offer a total of eight memory channels with up to two memory slots per channel.1 This presents numerous possible permutations for configuring the memory subsystem with traditional Dual In-Line Memory Modules (DIMMs), yet there are only a couple of balanced configurations that will achieve the peak memory performance for Dell EMC PowerEdge servers.Memory that has been incorrectly populated is referred to as an unbalanced configuration. From a functionality standpoint, an unbalanced configuration will operate adequately, but introduces significant additional overhead that will slow down data transfer speeds. Similarly, a near balanced configuration does not yield fully optimized data transfer speeds but it is only suboptimal to that of a balanced configuration. Conversely, memory that has been correctly populated is referred to as a balanced configuration and will secure optimal functionality and data transfer speeds.This white paper explains how to balance memory configured for Rome processors within Dell EMC PowerEdge servers.2. Memory Topography and TerminologyFigure 1: CPU-to-memory subsystem connectivity for Rome processorsTo understand the relationship between the CPU and memory, terminology illustrated in Figure 1 must first be defined:•Memory controllers are digital circuits that manage the flow of data going from the computer’s main memory to the corresponding memory channels.2 Romeprocessors have eight memory controllers in the processor I/O die, with onecontroller assigned to each channel.•Memory channels are the physical layer on which the data travels between the CPU and memory modules.3 As seen in Figure 1, Rome processors have eightmemory channels designated A, B, C, D, E, F, G and H. These channels wereintended to be organized into pairs such as two-way (AB, CD, EF, GH), four-way (ABCD, EFGH) or eight-way (ABCDEFGH).•The memory slots are internal ports that connect the individual DIMMs to their respective channels.4 Rome processors have two slots per channel, so there are a total of sixteen slots per CPU for memory module population. DIMM 1 slots are the first eight memory modules to be populated while DIMM 0 slots are the last eight.In the illustrations ahead, DIMM 1 slots will be represented with black text marked A1-A8 and DIMM 0 slots will be represented with white text marked A9-A16.•The memory subsystem is the combination of all the independent memory functions listed above.3. Memory InterleavingMemory interleaving allows a CPU to efficiently spread memory accesses across multiple DIMMs. When memory is put in the same interleave set, contiguous memory accesses go to different memory banks. Memory accesses no longer must wait until the prior access is completed before initiating the next memory operation. For most workloads, performance is maximized when all DIMMs are in one interleave set creating a single uniform memory region that is spread across as many DIMMs as possible.5 Multiple interleave sets create disjointed memory regions.3.1 NPS and Quadrant PairingRome processors achieve memory interleaving by using Non-Uniform Memory Access (NUMA) in Nodes Per Socket (NPS).6 There are four NPS options available in the Dell EMC BIOS:1. NPS 0– One NUMA node per system (on two processors systems only). Thismeans all channels in the system are using one interleave set.2. NPS 1– One NUMA node per socket (on one processor systems). This means allchannels in the socket are using one interleave set.3. NPS 2– Two NUMA nodes per socket (one per left/right half). This means eachhalf containing four channels is using one interleave set; a total of two sets.4. NPS 4– Up to four NUMA nodes per socket (one per quadrant). This means eachquadrant containing two channels is using one interleave set; a total of four sets. The simplest visual aid for understanding the NPS system is to divide the CPU into four quadrants. We see below in Figure 2 that each quadrant contains two paired DIMM channels that can host up to two DIMMs. The paired DIMM channels in each quadrant were designed to group and minimize the travel distance for interleaved sets. NPS 1 would correlate to all four quadrants being fully populated. NPS 2 would correlate to having either the left or right half quadrant being fully populated. NPS 4 would correlate to having any one quadrant being fully populated.Figure 2: Quadrant layout of Rome processors3.2 NPS and Quadrant PairingNPS 0 and NPS 1 will typically yield the best memory performance, followed by NPS 2 and then NPS 4. The Dell EMC default setting for BIOS NUMA NPS is NPS 1 and mayneed to be manually adjusted to match the NPS option that supports the CPU model. As seen below in Figure 3 there are various CPUs that will not support NPS 2 or 4 that require awareness of which memory configurations are optimized for each CPU. Figure 4 below shows our recommended NPS setting for each # of DIMMs per CPU:Figure 3: A full list of 2nd Gen AMD EPYC™ CPUs and their respectivesupported NPS models. The CPUs with an asterisk have been optimizedto reduce the performance impact of only filling four DIMM channels.Figure 4: Recommended NPS setting for each# of DIMMs per CPUIf the NPS setting for a memory configuration will limit performance (as seen in Figure 5), Dell EMC BIOS will return the following informative prompts to the user:UEFI0391: Memory configuration supported but not optimal for the enabledNUMA node Per Socket (NPS) setting. Please consider the following actions:1) Changing NPS setting under System Setup>System BIOS>ProcessorSettings>NUMA Nodes Per Socket, if supported.2) For optimized memory configurations please refer to the General MemoryModule Installation Guidelines section in the Installation and ServiceManual, of the respective server model available on the support site.In layman’s terms, a different NPS setting or memory configuration will result in better memory performance. The system is fully functional when this message appears, but it is not fully optimized for best performance.Figure 5: Color-coded table illustrating whenan informative message will occur (yellow) orno message (green)4. M emory Population Guidelines4.1 OverviewDIMMs must be populated into a balanced configuration to yield the highest memory bandwidth and lowest memory access latency. Various factors will dictate whether a configuration is balanced or not. Please follow the guidelines below for best results 7:o Memory Channel Population•Balanced Configuration-All memory channels must be fully populated with one or two DIMMs for best performance; a total of eight or sixteen DIMMs per CPU•Near Balanced Configuration-Populate four or twelve DIMMs per socket-Populate DIMMs in sequential order (A1-A8)o CPU and DIMM parts must be identicalo Each CPU must be identically configured with memory4.2 Memory Channel PopulationTo achieve a balanced configuration, populate either eight or sixteen DIMMs per CPU. By loading each channel with one or two DIMMs, the configuration is balanced and has data traveling across channels most efficiently on one interleave set. Following this guideline will yield the highest memory bandwidth and the lowest memory latency. If a balanced configuration of sixteen or eight DIMMs per CPU cannot be implemented, then the next best option is a near balanced configuration. To obtain a near balanced population, populate four or twelve DIMMs per CPU in sequential order. When any number of DIMMs other than 4, 8, 12 or 16 is populated, disjointed memory regions are created making NPS 4 the only supported BIOS option to select.The last guideline is that DIMMs must be populated in an assembly order because Rome processors have an organized architecture for each type of CPU core count. To simplify this concept, the lowest core count was used as a common denominator, so the assembly order below will apply across all Rome processor types. Populating in this order ensures that for every unique Rome processor, any DIMM configuration is guaranteed the lowest NPS option, therefore driving the most efficient interleave sets and data transfer speeds. Figure 6 illustrates the assembly order in which individual DIMMs should be populated, starting with A1 and ending with A16:Figure 6: DIMM population order, starting with A1 and ending with A164.3 Identical CPU and DIMM PartsIdentical DIMMs must be used across all DIMM slots (i.e. same Dell part number). Dell EMC does not support DIMM mixing in Rome systems. This means that only one rank, speed, capacity and DIMM type shall exist within the system. This principle applies to the processors as well; multi-socket Rome systems shall be populated with identical CPUs.4.4 Identical Memory Configurations for Each CPUEvery CPU socket within a server must have identical memory configurations. When only one unique memory configuration exists across both CPU sockets within a server, memory access is further optimized. Figure 7 below illustrates the expected memory bandwidth curve when these rules are followed:Figure 7: Bar graph illustrating expected performance variation as # of dimms increases 16151413121110987654321M e m o r y B a n d w i d t h #DIMMs per CPU populatedR6525 Memory Bandwidth per DIMM Population BalancedNear-Balanced Unbalanced5. Balanced Configurations (Recommended)Balanced configurations satisfy NPS 0/1 conditions by requiring each memory channel to be populated with one or two identical DIMMs. By doing this, one interleave set can optimally distribute memory access requests across all the available DIMM slots; therefore, maximizing performance. Memory controller logic was designed around fullypopulated memory channels, so it should come as no surprise thateight or sixteen populated DIMMs are recommended. Having eight DIMMs will reap the highestmemory bandwidth while having sixteen DIMMs will yield the highest memory capacity.Figure 8: Eight DIMMs are populated in a balanced configuration, producing the highest memorybandwidth while at a lower capacity than sixteenFigure 9: Sixteen DIMMs are populated in a balanced configuration, producing the highest memorycapacity while at a lower bandwidth than eight6. Near Balanced ConfigurationsNear balanced configurations satisfy NPS 1 or 2 conditions by populating either four or twelve identical DIMMs per CPU. These configurations are not optimized because the channels are partially populated, which creates disjointed memory regions that reduce performance (making it near balanced). Performance for near balanced configurationswill undergo degradation when compared to balanced configurations. Although the below configurations are adequate for implementation, they are not highly recommended. *Note that CPUs 7282, 7252, 7232P and 7272 were designed to reduce the performance impact of populating four DIMM channels.Figure 10: Four DIMMs are populated in a near balanced configurationFigure 11: Twelve DIMMs are populated in a near balanced configuration7. U nbalanced ConfigurationsUnbalanced configurations can only satisfy NPS 4 conditions. More than two interleave sets can now be introduced to the memory controller algorithm which causes very disjointed regions. Memory performance for the unbalanced configurations below are significantly less than balanced or near balanced and are not recommended.Figure 12: One DIMM is populated in an unbalanced configurationFigure 13: Two DIMMs are populated in an unbalanced configurationFigure 14: Three DIMMs are populated in an unbalanced configurationFigure 15: Five DIMMs are populated in an unbalanced configurationFigure 16: Six DIMMs are populated in a near balanced configurationFigure 17: Seven DIMMs are populated in an unbalanced configurationFigure 18: Nine DIMMs are populated in an unbalanced configurationFigure 19: Ten DIMMs are populated in a near balanced configurationFigure 20: Eleven DIMMs are populated in an unbalanced configurationFigure 21: Thirteen DIMMs are populated in an unbalanced configurationFigure 22: Fourteen DIMMs are populated in a near balanced configurationFigure 23: Fifteen DIMMs are populated in an unbalanced configuration8. ConclusionBalancing memory with 2nd Generation EPYC TM server processors increases memory bandwidth and reduces memory access latency. When memory modules are configured in such a way that the memory subsystems are identical, and channels are fully populated with one or two DIMMs, one interleave set will create a single uniform memory region that is spread across as many DIMMs as possible. This allows the distribution of data to perform most efficiently on Dell EMC PowerEdge servers. Applying the balanced memory guidelines demonstrated in this brief will ensure that both memory bandwidth and memory access latency are optimized, therefore ensuring peak memory performance within Dell EMC PowerEdge servers.9. References1 https:///wp-content/resources/56301_1.0.pdf2 https:///travel_guide/124468/hardware/computer_memory_controllers_how_they_work.html3 https:///jargon/d/dual-channel-memory.htm4 https:///jargon/m/memoslot.htm5 https:///memory-interleaving/6 https:///system/files/2018-03/AMD-Optimizes-EPYC-Memory-With-NUMA.pdf7 https:///wp-content/resources/56301_1.0.pdfThe information in this publication is provided “as is.” Dell Inc. makes no representations or warranties of any ki nd withrespect to the information in this publication, and specifically disclaims implied warranties of merchantability or fitness for a particular purpose.Use, copying, and distribution of any software described in this publication requires an applicable software license.© 2020 Dell Inc. or its subsidiaries. All Rights Reserved. Dell, EMC, Dell EMC and other trademarks are trademarks of DellInc. or its subsidiaries. Other trademarks may be trademarks of their respective owners.Dell believes the information in this document is accurate as of its publication date. The information is subject to changewithout notice.。

sadfaaaaaaaaaaa

第一章绪论1.1 选题背景及意义ARM(Advanced RISC Machines)是微处理器行业的一家知名企业设计了大量高性能、廉价、耗能低的RISC处理器、相关技术软件。

ARM公司作为知识产权供应商,其本身不直接从事芯片生产,而是转让设计许可由合作公司生产各具特色的芯片,世界各大半导体生产商从ARM公司购买其设计的ARM微处理器核,然后根据各自不同的应用领域,加入适当的外围电路,从而形成自己的ARM微处理器芯片进入市场。

目前全世界有几十家大的半导体公司都使用ARM公司的授权,因此既使得ARM技术获得更多的第三方工具、制造、软件的支持,又使整个系统成本降低,使产品更容易进入市场被消费者所接受,更有竞争力。

ARM微处理器现已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,基于ARM技术的微处理器应用约占据了32位RISC微处理器75%以上的市场份额,ARM技术正在逐步渗入到日常生活的各个方面。

随着嵌入式产品需求的增加,在嵌入式领域,8位处理器已经不能再胜任一些复杂的应用,例如GUI,TCP/IP,FILESYSTEM等,而ARM芯片凭借强大的处理能力和极低的功耗,非常适合这些场合。

所以现在越来越多的公司在产品选型的时候考虑到使用ARM处理器。

另外,随着ARM功能的增强和完善,某些方面可以取代原先X86架构的单板机,特别是工控领域。

基于以上两个原因,学习和使用A RM是十分有意义的。

1.2 ARM的发展ARM(Advanced RISC Machines),既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。

1991年ARM公司成立于英国剑桥,主要出售芯片设计技术的授权。

目前,采用ARM技术知识产权(IP)核的微处理器,即我们通常所说的ARM微处理器,已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,基于ARM 技术的微处理器应用约占据了32 位RISC 微处理器75%以上的市场份额,ARM技术正在逐步渗入到我们生活的各个方面。

IT-140G datasheet-201410

UL 94 V-0 IPC-4101C Spec /24/ 127 RoHS Compliant

REV 09-14

ITEQ

Property

Laminate/ Prepreg : IT-140GTC/IT-140GBS

IPC-4101A Spec / 24 / 127

X/Y Axis CTE (40℃ to 125℃)

Z-Axis CTE A. Alpha 1 B. Alpha 2 C. 50 to 260 Degrees C

Thermal Resistance A. T260 B. T288

CAF Resistance Halogen Content, maximum

V-0 140 minimum 310 minimum

--

--

35

60 maximum

--

230

300 maximum

--

3.1

4.0 maximum

--

>60

--

--

>60

--

--

Pass

AABUS

900 900 1500

<900 <900 <1500

900 900 1500

Units Metric (English)

2.4.8 2.4.8.2 2.4.8.3

2.5.17.1

2.5.17.1 2.6.2.1 2.5.6

2.5.5.9 2.5.5.13

2.5.5.9 2.5.5.13

2.4.4

2.5.1 2.4.13.1 2.5.6.2

UL94 2.4.25 2.4.24.6 (5% wt loss) 2.4.24 2.4.24

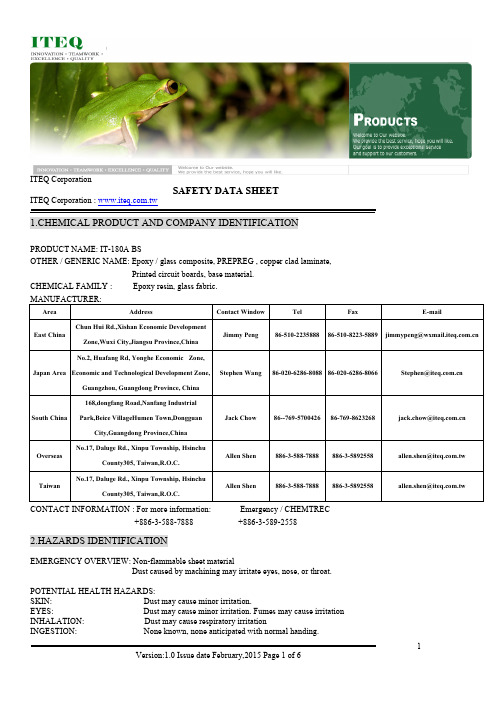

ITEQ Corporation IT-180A BS 安全数据表说明书

ITEQ CorporationSAFETY DATA SHEET1.CHEMICAL PRODUCT AND COMPANY IDENTIFICATIONPRODUCT NAME: IT-180A BSOTHER / GENERIC NAME: Epoxy / glass composite, PREPREG , copper clad laminate,Printed circuit boards, base material.CHEMICAL FAMILY : Epoxy resin, glass fabric.MANUFACTURER:Area Address Contact Window Tel Fax E-mailEast ChinaChun Hui Rd.,Xishan Economic DevelopmentZone,Wuxi City,Jiangsu Province,ChinaJimmy Peng 86-510-2235888 86-510-8223-5889 *********************Japan AreaNo.2, Huafang Rd, Yonghe Economic Zone,Economic and Technological Development Zone,Guangzhou, Guangdong Province, ChinaStephen Wang 86-020-6286-8088 86-020-6286-8066 ****************.cnSouth China168,dongfang Road,Nanfang IndustrialPark,Beice VillageHumen Town,DongguanCity,Guangdong Province,ChinaJack Chow 86--769-5700426 86-769-8623268 ******************.cnOverseasNo.17, Daluge Rd., Xinpu Township, HsinchuCounty305, Taiwan,R.O.C.Allen Shen 886-3-588-7888 886-3-5892558 *******************.tw TaiwanNo.17, Daluge Rd., Xinpu Township, HsinchuCounty305, Taiwan,R.O.C.Allen Shen 886-3-588-7888 886-3-5892558 *******************.tw CONTACT INFORMATION : For more information: Emergency / CHEMTREC+886-3-588-7888 +886-3-589-25582.HAZARDS IDENTIFICATIONEMERGENCY OVERVIEW: Non-flammable sheet materialDust caused by machining may irritate eyes, nose, or throat.POTENTIAL HEALTH HAZARDS:SKIN: Dust may cause minor irritation.EYES: Dust may cause minor irritation. Fumes may cause irritationINHALATION: Dust may cause respiratory irritationINGESTION: None known, none anticipated with normal handing.ITEQ CorporationSAFETY DATA SHEETClassifiable or probably non-carcinogenic (Group 3 ).Ingredients found on any of OSHA’s carcinogen lists are listed below.INGREDIENT NAME: NTP STATUS: IARC STATUS: OSHA LISTNone N/A N/A N/APOSITION / INFORMATION ON INGREDIENTSINGREDIENT NAME: CAS# % w/wGlass cloth 65997-17-3 40~70%B-Stage semi-cured epoxy of Multi-function resin 026265-08-7 40~70%Fillers type SiO2 powder 14808-60-7 10~20%We don’t have PFOSFor local ”Right to Know” compliance and other reasons, trace ingredients not listed above may appear in Section 15, Regulatory Information.4.FIRST AID MEASURESSKIN: Wash promptly with soap and running water. Do not rub or scratch.If irritation persists, consult physician.Remove contaminated clothing and wash thoroughly before reuseEYES: Flush immediately with plenty of low-pressure water for at least 20Minutes.Do not rub or scratch.If irritation persists, consult physician.INHALATION: Move to fresh air.Consult physician.INGESTION: If large amounts are ingested, consult physician.ADVICE TO PHYSICIAN:Treat symptomatically5.FIRE-FIGHTING MEASURESFLASH POINT: N/AFLASH POINT METHOD: N /AAUTOIGNITION TEMP: Not determined.UPPER FLAME LIMIT: N/ALOWER FLAME LIMIT: N/AFLAME PROPAGATION RATE: UL 94 V-0ITEQ CorporationSAFETY DATA SHEETEXTINGUISHING MEDIA: Water, CO2, foam, dry chemical, Halon.UNUSUAL FIRE ANDEXPLOSION HAZARDS:May give off toxic hydrogen bromide fumes when thermallyDecomposed.SPECIAL FIRE-FIGHTINGPROCEDURES:Wear proper protective equipment and self-contained breathingApparatus.6.ACCIDENTAL RELEASE MEASURESRESPONSE TO RELEASE: If material is not contaminated, return to container for use.If material is contaminated, pick up and place in container for disposal.Material is an article. Spill or release to the environment is unlikely. 7.HANDLING AND STORAGENORMAL HANDLING: Always wear recommended personal protective equipment. STORAGE: Store in a cool dry place.8.ENGINEERING CONTROLS / PERSONAL PROTECTIONENGINEERING CONTROLS:VENTILATION: Adequate ventilation should be provided to keep dust concentrationswithin acceptable exposure limits. Discharge from the ventilationsystem should comply with applicable air pollution control regulation GENERAL: Eyewash fountains and safety showers should be easily accessible. PERSONAL PROTECTIVE EQUIPMENT:SKIN PROTECTION: Impervious gloves and clothing should be worn for prolonged orRepeated contact.EYE PROTECTION: Safety glassesRESPIRATORY PROTECTION:Atmospheric levels of fibrous glass, copper, and other dusts should bemaintained below recommended exposure guidelines.If airborne contaminant is likely to exceed acceptable limits, use aNIOSH-approved respirator.ADDITIONAL: N/ARECOMMENDATIONS: N/AEXPOSURE GUIDELINES:INGREDIENT NAME: CAS# ACGIH TLV OSHA PEL OTHER LIMITSITEQ CorporationSAFETY DATA SHEET9.PHYSICAL AND CHEMICAL CHARACTERISTICSAPPEARANCE: Amber, gold, or yellow sheets which may have copper cladding on oneor both sides.PHYSICAL STATE: Solid.ODOR: None unless heated.BOILING POINT: N/AMELTING POINT: N/AMOLECULAR WEIGHT:N/ACHEMICAL FORMULA:N/APH: N/ASOLUBILITY IN WATER:InsolubleVAPOR PRESSURE: N/AVAPOR DENSITY: N/ASPECIFIC GRAVITY: 1.6-1.9EVAPORATION RATE: N/A%VOLATILES: <1.5%10. STABILITY AND REACTIVITYNORMALLY STABLE: YES.INCOMPATIBILITIES: Not determinedHAZARDOUS: CO, CO2, HBr, aromatic or aliphatic hydrocarbons. DECOMPOSITION PRODUCTS: Laser processing may result in copper fumes.HAZARDOUSPOLYMERIZATION: None11.TOXICOLOGICAL INFORMATIONIMMEDIATE ( ACUTE )EFFECTS:Dust may cause eye, skin, and respiratory irritation. DELAYED ( SUBCHRONIC ANDCHRONIC ) EFFECTS:NTP and IARC consider respirable glass wool a possible humanCarcinogen.IARC consider continuous glass filaments unclassifiable orNon-carcinogenic ( Group 3 ).ITEQ CorporationSAFETY DATA SHEET12.ECOLOGICAL INFORMATIONNot biodegradable.13.DISPOSAL CONSIDERATIONSRCRA HAZARDOUS WASTE: No.WASTE DISPOSAL METHOD: Landfill.Do not incinerate.Recycle copper.Disposal must comply with all local, regional, and national regulations. Information supplied here is for the material as shipped. Use or alteration of the product such as mixingwith other materials such as lead solder during the printed circuit boards fabrications process maychange the RCRA classification of the mixture and require alternative disposal procedures.14.TRANSPORTATION INFORATIONUS DOT HAZARD CLASS : Not regulated.US DOT ID NUMBER: N/A15.REGULATORY INFORMATIONTSCA INVENTORY STATUS : Resin system components used in this product are on the TSCAInventory list.OTHER TSCA ISSUES: None.16. Other materialSAFETY DATA SHEETRemark : This MSDS , described as satisfactorily as possible, does not cover every case of danger . Hazard information on paint product is estimated as a mixturebased on that of individual raw materials . Additionally , your use of thisinformation is beyond our control and may be beyond our knowledge.Therefore, the information is provided without any representation orWarranty express or implied.。

IBM错误代码解释以及解决方法

IBM错误代码解释以及解决方法IBM的ThinkPad系列笔记本电脑的错误代码解释以及解决方法,希望能对拥有此款“本本”的朋友们有所帮助。

101:中断失败102:时钟失败103:时间中断失败104:保护模式失败105:最后的 8042命令未接受107:NMI 检测失败108:时钟总线检测失败109:Low meg芯片选择检测以上出错部件及解决措施:请检查主板设置是否正确,严重时需要更换主板。

110:平面奇偶出错部件及解决措施:这种情况一般是内存发生问题,请将内存换一个插槽试试。

不过,如果有连接到电脑的扩展部件,请先移除。

111:I/O奇偶出错部件及解决措施:仍然是首先检查内存条是否损坏,然后请检查扩展部件或端口复制器是否损坏。

0175:CRC1错,EEPROM校验错出错部件及解决措施:系统主板,停止POST任务。

1101: A类设备检测失败出错部件及解决措施:重点检查串口设备、通讯接线等部件。

1201: B类设备检测失败出错部件及解决措施:请检查主板上的红外接口是否损坏。

158:设置了SuperVisor密码但没有设置硬盘密码出错部件及解决措施:请重新设置硬盘密码159:硬盘密码与SuperVisor密码不相同出错部件及解决措施:请将硬盘的密码设置为与SuperVisor密码相同。

161:电池失效。

出错部件及解决措施:这当然是电池的问题,请重新更换电池或检查主板上的现用电池是否有漏电现象。

163:时间和日期未设置出错部件及解决措施:重新设置时间和日期。

173:设备数据丢失出错部件及解决措施:在屏幕上选择OK,然后设置时间和日期,必要时需要更换备用电池。

174:设置错误。

出错部件及解决措施:先去检查一下硬件设备是否配置正确,或者检查硬盘的跳线是否设置正确。

0177: SuperVisor密码检验错出错部件及解决措施:系统主板。

1701:硬盘控制器失败1780, 1790:硬盘0出错1781, 1791:硬盘1出错173 192 163出错,出错部件及解决措施:硬盘错误,当然也不排除主板存在错误。

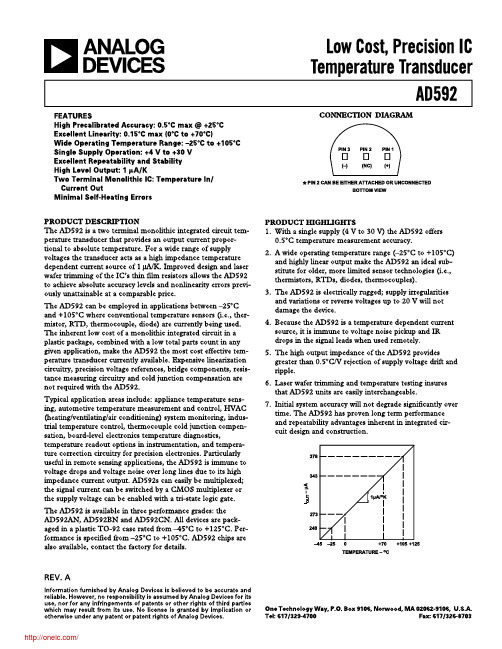

28130;中文规格书,Datasheet资料

METALIZATION DIAGRAM

TEMPERATURE SCALE CONVERSION EQUATIONS

+2.0 +1.5 +1.0 +0.5

0 –0.5 –1.0 –1.5 –2.0

–25

0

+25

+70

TEMPERATURE – oC

+105

AD592BN Accuracy Over Temperature

TOTAL ERROR – oC TOTAL ERROR – oC

+2.0 +1.5 +1.0 +0.5

+1.0

+0.5

MAXIMUM ERROR OVER TEMPERATURE

TYPICAL ERROR

0 CALIBRATION ERROR LIMIT

–0.5

TOTAL ERROR – oC

IOUT – µA

378

+105oC

298

+25oC

–25oC 248

UP TO 30V

0

1

2

3

4

5

6

SUPPLY VOLTAGE – Volts

66MILS

V+

V–

/

Model

AD592CN AD592BN AD592AN

42MILS

؇C = 5 (؇F –32) 9

i3588核心板使用手册说明书

I3588核心板使用手册深圳市九鼎创展科技有限公司版权声明本手册版权归属深圳市九鼎创展科技有限公司所有,并保留一切权力。

非经九鼎创展同意(书面形式),任何单位及个人不得擅自摘录本手册部分或全部,违者我们将追究其法律责任。

敬告:在售开发板的手册会经常更新,请在网站下载最新手册,不再另行通知。

版本说明技术支持如果您对文档有所疑问,您可以在办公时间(星期一至星期五上午9:00~12:00;下午1:30~6:00)通过技术QQ群、E-mail、BBS论坛()、或联系业务人员获取支持。

网址:E-mail:********************销售与服务网络公司:深圳市九鼎创展科技有限公司地址:深圳市宝安区洪浪北二路信义领御研发中心1栋1412-1416电话:*************网址:论坛:,淘宝:阿里:速卖通:/store/2340163技术交流QQ群QQ群号X4418/ibox4418论坛199358213x6818/ibox6818论坛189920370RK平台交流一群159144256RK平台交流二群573696929RK平台交流三群817913100MTK平台交流群630291376全志平台交流群436993280热烈欢迎广大同仁扫描右侧九鼎创展官方公众微信号,关注有礼,您将优先得知九鼎创展最新动态!目录版权声明 (2)第1章i3588核心板简介 (6)1.1产品简介 (6)1.2核心板特性 (6)1.2.1特性参数 (6)1.2.2核心板外观 (7)1.2.3核心板结构图 (9)1.2.4核心板结构参数 (11)第2章引脚定义 (12)2.1核心板引脚定义1 (12)2.2核心板引脚定义2 (16)2.3核心板引脚定义3 (20)2.4核心板引脚定义4 (23)2.5硬件设计 (26)2.5.1管脚描述 (26)2.5.2GPIO电源 (26)2.5.3电源设计 (27)2.5.4USB设计 (27)2.5.5HDMI设计 (27)2.5.6EDP设计 (27)2.5.7MIPI设计 (28)第3章其他产品介绍 (29)3.1核心板系列 (29)3.2开发板系列 (29)3.3卡片电脑系列 (30)第1章i3588核心板简介1.1产品简介I3588CV1是基于瑞芯微RK3588的一款核心板,它由深圳市九鼎创展科技有限公司自主研发,生产并销售。

Ithaqua系列硬盘适配器I说明书

JI-4 OR

POWER-TA8LE GNO IREFIPWR

~ +fv

~Ul~ ~U2~

~U3~

~U4~

~U5~

~U6~

r-L U7 ~

~U8~

~U9~ ~Ulti1~

~’- -I-t- - i7~:~: }CHASSIS

GROUND

+5V"-

14

[E'0' 74LS24ti1

U5-e4-------f (~B2)

Z01-_D__T_R__________________~1 ~~3--

_ _- -_ _- -_ _- - - - - -

l:. + 5V

R9 4.71<'

5

.>-ID_ _.--- 0 B 1

(ZA'3)

Ie POWER TABLE.

RE.F DES. MJ:"G. 1\.10. C;UD:+5V +Iev -IZ" If(PIUS

1460

I6StQQQI+11-92>;,5_-°D-;B8.;p:;'"/'f///'0 , "- OB4

1770 7Q16

~EN rVOAT 18eo

SQI9

087/:\: DB7 " -WR IOOA

~ ~gU6

~~~

54QQ 192

1350

~~~g ~~~~

18 eo S II,--CL_K_ _..JQ19

(385)

(LED) ~~~--------___7

Pyxis Lab ST-588 PTSA Fluorescent Polymer Dual Inl

ST-588PTSA/Fluorescent Polymer DualInline SensorUser ManualOctober12,2020Rev.2.00Pyxis Lab,Inc.1729Majestic Dr.Suite5Lafayette,CO80026USA©2017Pyxis Lab,Inc.Pyxis Lab Proprietary and ConfidentialTable of Contents1Introduction21.1Main Features (2)2Specifications3 3Unpacking Instrument43.1Standard Accessories (4)3.2Optional Accessories (5)4Installation64.1ST-588Piping (6)4.2ST-588SS Piping (6)4.3Wiring (7)4.4Connecting via Bluetooth (8)4.5Connecting via USB (8)5Setup and Calibration with uPyxis®Mobile App95.1Download uPyxis®Mobile App (9)5.2Connecting to uPyxis®Mobile App (9)5.3Calibration Screen and Reading (10)5.4Diagnosis Screen (11)5.5Device Info Screen (12)6Setup and Calibration with uPyxis®Desktop App126.1Install uPyxis®Desktop App (12)6.2Connecting to uPyxis®Desktop App (13)6.3Information Screen (13)6.4Calibration Screen (14)6.5Diagnosis Screen (14)7Outputs157.14–20mA Output Setup (15)7.2Communication using Modbus RTU (15)8Sensor Maintenance and Precaution158.1Methods to Cleaning the ST-588 (16)8.2Storage (16)9Troubleshooting17 10Contact Us18Warranty InformationConfidentialityThe information contained in this manual may be confidential and proprietary and is the property of Pyxis Lab,rmation disclosed herein shall not be used to manufacture,construct,or otherwise reproduce the goods rmation disclosed herein shall not be disclosed to others or made public in any manner without the express written consent of Pyxis Lab,Inc.Standard Limited WarrantyPyxis Lab warrants its products for defects in materials and workmanship.Pyxis Lab will,at its option,repair or replace instrument components that prove to be defective with new or remanufactured components (i.e.,equivalent to new).The warranty set forth is exclusive and no other warranty,whether written or oral, is expressed or implied.Warranty TermThe Pyxis warranty term is thirteen(13)months ex-works.In no event shall the standard limited warranty coverage extend beyond thirteen(13)months from original shipment date.Warranty ServiceDamaged or dysfunctional instruments may be returned to Pyxis for repair or replacement.In some in-stances,replacement instruments may be available for short duration loan or lease.Pyxis warrants that any labor services provided shall conform to the reasonable standards of technical com-petency and performance effective at the time of delivery.All service interventions are to be reviewed and authorized as correct and complete at the completion of the service by a customer representative,or des-ignate.Pyxis warrants these services for30days after the authorization and will correct any qualifying deficiency in labor provided that the labor service deficiency is exactly related to the originating event.No other remedy,other than the provision of labor services,may be applicable.Repair components(parts and materials),but not consumables,provided during a repair,or purchased individually,are warranted for90days ex-works for materials and workmanship.In no event will the in-corporation of a warranted repair component into an instrument extend the whole instrument’s warranty beyond its original term.Warranty ShippingA Repair Authorization(RA)Number must be obtained from Pyxis Technical Support before any product can be returned to the factory.Pyxis will pay freight charges to ship replacement or repaired products to the customer.The customer shall pay freight charges for returning products to Pyxis.Any product returned to the factory without an RA number will be returned to the customer.To receive an RMA you can generate a request on our website at https:///request-tech-support/.Pyxis Technical SupportContact Pyxis Technical Support at+1(866)203-8397,*********************,or by filling out a request for support at https:///request-tech-support/.1IntroductionThe Pyxis ST-588inline fluorometer probe simultaneously measures the concentration of PTSA and Fluores-cent Polymer in water.It can be simply inserted to the compression fitting port of a custom-made tee.The standard ST-001installation tee provided with each ST-588sensor,has two¾inch female NPT ports and can be placed to an existing¾inch sample water line.Pyxis Lab also offers2”and3”Tee formats for larger flow installations.The4–20mA current output of the ST-588probe can be connected to any controller that accepts an isolated or non-isolated4–20mA input.The ST-588probe is a smart device.In addition to mea-suring PTSA and Fluorescent Polymer,the ST-588probe has extra photo-electric components that monitor the color and turbidity of the sample water.This extra feature allows automatic color and turbidity com-pensation to eliminate interference commonly associated with real-world waters.The Pyxis ST-588probe has a short fluidic channel and can be easily cleaned.The fluidic and optical ar-rangement of the ST-588probe is designed to overcome shortcomings associated with other fluorometers that have a distal sensor surface or a long,narrow fluidic cell.Traditional inline fluorometers are susceptible to color and turbidity interference and fouling and are difficult to properly clean.1.1Main FeaturesThe ST-588measures PTSA and Fluorescent Polymer in a water sample and includes the following features:•Easy calibration with using uPyxis®Mobile or Desktop App.•Automatic compensation for turbidity up to150NTU and color created by up to10ppm iron or equivalent to10ppm humic acid.•Diagnostic information(probe fouling,color or turbidity over range,failure modes)are available in uPyxis®App or via Modbus RTU.•Easy to remove from the system for cleaning and calibration without the need for any tools.2SpecificationsTable1.ST-588Specifications*With Pyxis’s continuous improvement policy,these specifications are subject to change without notice.†The fluorescent polymer concentration scale is based on the polymer containing0.25mole%fluorescent monomer.Typical polymer specifications are attached below but may vary by producer.‡See Figure4for ST-588SS dimensions.3Unpacking InstrumentRemove the instrument and accessories from the shipping container and inspect each item for any damage that may have occurred during shipping.Verify that all accessory items are included.If any item is missing or damaged,please contact Pyxis Lab Customer Service at*********************.3.1Standard Accessories•Tee Assembly3/4”NPT(1x Tee,O-ring,and Nut)P/N:ST-001*NOTE*ST-001is not included for ST-588SS•8-Pin Female Adapter/Flying Leads Cable(1.5ft)•User Manual available online at https:///support/3.2Optional AccessoriesFigure1.4Installation4.1ST-588PipingThe provided ST-001Tee Assembly can be connected to a pipe system through the3/4”female ports,either socket or NPT threaded.To properly install the ST-588probe into the ST-001Tee Assembly,follow the steps below:1.Insert the provided O-ring into the O-ring groove on the tee.2.Insert the ST-588probe into the tee.3.Tighten the tee nut onto the tee to form a water-tight,compression seal.Figure2.Dimension of the ST-588and the ST-001Tee Assembly(mm)4.2ST-588SS PipingThe ST-588SS probe has3/4”female NPT threaded ports on the probe itself and therefore does not require a custom tee assembly.It is recommended that two3/4”NPT to1/4”tubing adapters are used to connect the probe to the sampling system.Sample water entering the probe must be cooled down to below104°F (40°C).The probe can be held by a1.75-inch pipe clamp or mounted to a panel with four1/4-28bolts.See Figure4for ST-588SS dimensions.Figure3.Dimension of the ST-588SS(inch)4.3WiringIf the power ground terminal and the negative4–20mA terminal in the controller are internally connected (non-isolated4–20mA input),it is unnecessary to connect the4–20mA negative wire(gray)to the4–20mA negative terminal in the controller.If a separate DC power supply other than that from the controller is used,make sure that the output from the power supply is rated for22–26VDC@85mA.*NOTE*The negative24V power terminal(power ground)and the negative4–20mA ter-minal on the ST-588probe are internally connected.Follow the wiring table below to connect the ST-588probe to a controller:Table2.*Internally connected to the power ground4.4Connecting via BluetoothA Bluetooth adapter(P/N:MA-WB)can be used to connect a ST-588probe to a smart phone with the uPyxis®Mobile App or a computer with the uPyxis®Desktop App.Figure4.Bluetooth connection to ST-588probe4.5Connecting via USBA USB-RS485adapter(P/N:MA-485)can be used to connect a ST-588probe to a computer with the uPyxis®Desktop App.*NOTE*Using non-Pyxis USB-RS485adapters may result in permanent damage of the ST-588probe communication hardware.B connection to ST-588probe5Setup and Calibration with uPyxis®Mobile App5.1Download uPyxis®Mobile AppDownload uPyxis®Mobile App from Apple App Store or Google Play.Figure6.5.2Connecting to uPyxis®Mobile AppTurn on Bluetooth on your mobile phone(Do not pair the phone Bluetooth to the ST-588probe).Open uPyxis®Mobile App.Once the app is open the app will start to search for the sensor.Once the uPyxis®Mobile App connects to the sensor,press the ST-588probe.Figure7.5.3Calibration Screen and ReadingWhen connected,the uPyxis®Mobile App will default to the Calibration screen.From the Calibration screen,you can perform calibrations by pressing on Zero Calibration,Slope Calibration,and4–20mA Span for either Fluorescent Polymer or PTSA,independently.Follow the screen instructions for each calibration step.Figure8.5.4Diagnosis ScreenFrom the Diagnosis screen,you can check the diagnosis condition.This feature may be used for technical support when communicating with*********************.To preform a probe cleaniness check,first select the Diagnosis Condition which defines the fluid type that the ST-588probe in currently measuring,then press Cleanliness Check.If the probe is clean,a Clean mes-sage will be shown.If the probe is severely fouled,a Dirty message will be shown.In this case,follow the procedure in the Methods to Cleaning the ST-588section of this manual.Figure9.5.5Device Info ScreenFrom the Device Info screen.You can name the Device or Product as well as set the Modbus address.Figure10.6Setup and Calibration with uPyxis®Desktop App6.1Install uPyxis®Desktop AppDownload the latest version of uPyxis®Desktop software package from:https:///upyxis/this setup package will download and install the Framework4.5(if not previously installed on the PC),the USB driver for the USB-Bluetooth adapter(MA-NEB),the USB-RS485adapter(MA-485),and the main uPyxis®Desktop application.Double click the uPyxis.Setup.exe file to install.Figure11.Click Install to start the installation process.Follow the screen instructions to complete the USB driver and uPyxis®installation.6.2Connecting to uPyxis®Desktop AppWhen the uPyxis®Desktop App opens,click on Device,then click either Connect via USB-Bluetooth or Connect via USB-RS485depending on the connection type.Figure12.6.3Information ScreenOnce connected to the device,a picture of the device will appear on the top left corner of the window and the uPyxis®Desktop App will default to the Information screen.On the Information screen you can set the information description for Device Name,Product Name,and Modbus Address,then click Apply Settings to save.Figure13.6.4Calibration ScreenTo calibrate the device,click on Calibration.On the Calibration screen there are six calibration options:•Fluorescent Polymer:Zero Calibration,Slope Calibration,and4-20mA Span•PTSA:Zero Calibration,Slope Calibration,and4-20mA SpanThe screen also displays the reading of the device.The reading refresh rate is every4seconds.Figure14.6.5Diagnosis ScreenAfter the device has been calibrated and installation has been completed,to check diagnosis,click on Di-agnosis.When in the Diagnosis screen you can view the Diagnosis Condition of the device.This feature may be used for technical support when communicating with*********************.To preform a probe Cleaniness Check,first select the Diagnosis Condition which defines the fluid type that the ST-588probe inCheck.If the probe is clean,a Clean message will be shown.message will be shown.In this case,follow the procedure in theof this manual.Figure15.7Outputs7.14–20mA Output SetupThe4–20mA output of the ST-588sensor is scaled as:•Fluorescent Polymer:–4mA=0ppm–20mA=20ppm•PTSA:–4mA=0ppb–20mA=200ppb7.2Communication using Modbus RTUThe ST-588probe is configured as a Modbus slave device.In addition to the ppm Fluorescent Polymer and ppb PTSA values,many operational parameters,including warning and error messages,are available via a Modbus RTU connection.Contact Pyxis Lab Customer Service(*********************)for more informa-tion.8Sensor Maintenance and PrecautionThe ST-588probe is designed to provide reliable and continuous Fluorescent Polymer and PTSA readings even when installed in moderately contaminated industrial cooling waters.Although the optics are com-pensated for the effects of moderate fouling,heavy fouling will prevent the light from reaching the sensor, resulting in low readings and the potential for product overfeed if the ST-588probe is used as part of an au-tomated control system.When used to control product dosing,it is suggested that the automation system be configured to provide backup to limit potential product overfeed,for example by limiting pump size or duration,or by alarming if the pumping rate exceeds a desired maximum limit.The ST-588probe is designed to be easily removed,inspected,and cleaned if required.It is suggested that the ST-588probe be checked for fouling and cleaned/calibrated on a monthly basis.Heavily contam-inated waters may require more frequent cleanings.Cleaner water sources with less contamination may not require cleaning for several months.The need to clean the ST-588probe can be determined by the Cleanliness Check using either the uPyxis®Mobile App(see the Mobile Diagnosis Screen section)or the uPyxis®Desktop App(see the Desktop Diagnosis Screen section).8.1Methods to Cleaning the ST-588Any equipment in contact with industrial cooling systems is subject to many potential foulants and con-taminants.Our inline probe cleaning solutions below have been shown to remove most common foulants and contaminants.A small,soft bristle brush,Q-Tips cotton swab,or soft cloth may be used to safely clean the probe housing and the quartz optical sensor channel.These components and more come with a Pyxis Lab Inline Probe Cleaning Solution Kit(P/N:SER-01)which can be purchased at our online Estore/Catalog https:///product/probe-cleaning-kit/Figure16.Inline Probe Cleaning Solution KitTo clean the ST-588probe,soak the lower half of the probe in100mL inline probe cleaning solution for 10minutes.Rinse the ST-588probe with distilled water and then check for the flashing blue light inside the ST-588probe quartz tube.If the surface is not entirely clean,continue to soak the ST-588probe for an e the small,soft bristle brush and Q-Tips cotton swabs as necessary to remove any remaining contaminants in the ST-588probe quartz tube.8.2StorageAvoid long term storage at temperature over100°F.In an outdoor installation,properly shield the ST-588 probe from direct sunlight and precipitation.9TroubleshootingIf the ST-588probe output signal is not stable and fluctuates significantly,make an additional ground con-nection––connect the clear(shield,earth ground)wire to a conductor that contacts the sample water electrically such as a metal pipe adjacent to the ST-588tee.Carry out routine calibration verification against a qualified Fluorescent Polymer and PTSA combined stan-dard.After properly cleaning the ST-588sensor,carry out the zero point calibration with distilled water and slope calibration using the qualified Fluorescent Polymer and PTSA combined standard.10Contact UsPyxis Lab,Inc1729Majestic Dr.Suite5Lafayette,CO80026USAPhone:+1(866)203-8397Email:*********************。

Dell Networking S4148U-ON Product Compliance Datas

Product Compliance DatasheetMARKETING NAME...........Dell Networking S4148U-ON REGULATORY MODEL (20)REGULATORY TYPE………E20W006EMC EMISSIONS CLASS….AEFFECTIVE DATE……November 15, 2017Table of contentsI.Statement of Compliance (2)II.Power Cords and User Documentation (2)III.Trade (Import/Export) Compliance Data (2)IV.Product Dimensions and Weight (3)V.Product Materials Information (3)VI.Packaging (4)VII.Batteries (5)VIII.D esign for Environment (5)IX.Recycling / End-of-Life Service Information (5)X.Helpful Links (5)I. Statement of ComplianceThis equipment has been determined to be compliant with the applicable standards, regulations, anddirectives for the countries where the equipment is marketed. The equipment is affixed with regulatorymarking and text as necessary for the country/agency. Dell manufacturers and markets MultimediaEquipment (MME), Information Technology Equipment (ITE), Audio Visual Equipment (A/V), Industrial,Scientific, Medical Equipment (ISM) or combinations of these. Generally, equipment Safety and EMCcompliance is based on International IEC and CISPR standards and their national equivalent along withnational standards for Radio (wireless), and Energy. Dell products have been verified to comply with the EU RoHS Directive 2011/65/EU. Dell equipment does not contain any of the restricted substances inconcentrations and applications not permitted by the RoHS Directive. EMC Emissions Class refers to one of the following use environments:• EMC Class B equipment is intended for use in residential/domestic environments but may also be used in nonresidential/non-domestic environments.• EMC Class A equipment is intended for use in non-residential/non-domestic environments. Class Aequipment may also be utilized in residential/domestic environments but may cause interference and require the user to take adequate corrective measures.For Safety and EMC compliance, this equipment has been assigned a unique regulatory model andregulatory type that is imprinted on the equipment regulatory labeling to provide traceability to the regulatory approvals noted on this datasheet. This datasheet applies to any equipment that utilizes the assignedregulatory model and type including marketing names other than those listed on this datasheet. ErPcompliance is tied to the CE mark. REACH (Registration, Evaluation, Authorization and Restriction ofChemicals, 1907/2006) is the European Union’s (EU) chemical substances regulatory framework. Dellcomplies with the REACH directive. For information on SVHC (Substances of Very High Concern), see/REACH. Compliance documentation, such as certification or Declaration of Compliance for the equipment is available upon request to ***************************. Please include equipment identifiers such as marketing name, regulatory model, regulatory type and country that compliance information isneeded in request.II. Power Cords and User DocumentationDell products are provided with the power cord and user documentation suitable for the intended country of delivery. Products that are relocated to other countries should use nationally certified power cords and plugs to ensure safe operation of the product. Contact Dell to determine if alternate power cords or userdocumentation in other languages is available for your market.III. Trade (Import/Export) Compliance DataFor any questions related to importing & exporting classification of Dell products, please obtain information from the following link: /import_export_compliance or send request to*****************************.IV. Product Dimensions and WeightV. Product Materials InformationInformation on Dell’s material use is available here.Dell’s Restricted Material for Use guidance document is available here.The case material is, > T=1.0+- 5% JJIS G3302 SGCC – Z08<This product contains 0 % post-consumer recycled plastic/closed loop recycled plastics(Measured as a percentage of total amount of plastic (by weight) in the product as per guidance in EPEAT standard as applies to plastics parts)Flame Retardants Used in MotherboardFlame Retardants Used in Mechanical Plastic Parts > 25 grams1Mechanical plastic part: plastic parts that do not internally carry an electrical signal such as housings, brackets, bezels, latches, etc. that form the basic structure of the product and/or have mechanical functions. Plastic parts such as fans, connectors, printer fuser assemblies, etc. are not considered “mechanical plastic parts” in the context of this specification.Plastics parts do not contain no more than 0,1% weight (1000 ppm) bromine and 0,1% weight (1000 ppm) chlorine attributable to brominated flame retardants, chlorinated flame retardants, and polyvinyl chloride (Per Dell Spec ENV0424)2Dell will adopt the BFR/CFR/PVC-free definition as set forth in the "iNEMI Position Statement on the Definition of 'Low-Halogen' Electronics (BFR/CFR/PVC-Free)." Plastic parts contain <1000 ppm (0.1 percent) of bromine (if the Br source is from BFRs) and <1000 ppm (0.1 percent) of chlorine if the Cl source is from CFRs, PVC or PVC copolymers. All printed circuit board (PCB) and substrate laminates contain bromine/chlorine totaling less than 1,500 ppm (0.15 percent), with maximum chlorine of 900 ppm (0.09 percent) and maximum bromine of 900 ppm (0.09 percent)Mercury InformationRoHS and REACH declaration - see product material information section at:/environmental_informationProducts MSDS (Material Safety Data Sheets):Batteries: Battery MSDS Documentation and DeclarationPrinter Toner and Ink: MSDS DocumentationVI. PackagingInformation on Dell’s sustainable packaging effort available here.3 Non-wood, biobased material may include, but is not limited to: bagasse, bamboo, mushroom, straw, agricultural waste or byproduct. * Recycled content in packaging material is supplier dependent.VII. BatteriesVIII. Design for EnvironmentDell systems are, when applicable, designed for easy assembly, disassembly, and servicing.For more information on product Recyclability please visit /environmental_information IX. Recycling / End-of-Life Service InformationTake back and recycling services are offered for this product in certain countries. If you want to dispose of system components, please visit /recyclingworldwide and select the relevant country. X. Helpful LinksEnvironmental Policy/sites/content/corporate/corp-comm/en/Documents/dell-global-environmental-policy.pdfEnvironment Website/environmental_informationCorporate Sustainability Report/Learn/us/en/uscorp1/report?c=us&l=en&s=corp&delphi:gr=trueISO 14001 Certification/sites/content/corporate/corp-comm/en/Documents/dell-iso14001-worldwide.pdfMaterials Restricted for Use/downloads/global/corporate/environ/restricted_materials_guid.pdfChemical Use Policy/sites/doccontent/corporate/environment/en/Documents/chemical-use-policy.pdfProduct Carbon Footprint/us/en/corp/d/corp-comm/environment_carbon_footprint_productsRoHS Compliance/rohsinfoREACH Compliance/REACHRecycling Information/recyclingSupplier Responsibility/us/en/corp/d/corp-comm/standards-for-suppliers.aspx。

海光BIOS保护卡说明书

海光BIOS保护卡使用手册北京海光科技开发有限公司E-Mail: lwb@本手册使用的所有产品商标与产品名称均属于北京海光科技开发有限公司。

在软件版本升级后,该发行使用手册中的一些界面可能与软件实际界面有出入,请以实际界面为准。

手册内容如有修改将不另行通知。

保护卡上的任何贴纸请勿自行撕毁,否则将会影响到产品的质保期限的认定,本公司有权拒绝更换。

目录第一章海光BIOS保护卡及操作系统的安装 (4)1-1 安装前的准备 (4)1-2 安装发送端 (5)1-3 网络拷贝 (14)1-4 硬盘复制 (19)第二章自动维护 (20)第三章系统设定 (22)第四章Max-Control/USER使用方法 (27)第五章自动分配IP操作流程 (31)附录一热键提示 (35)附录二硬盘大传小功能 (35)附录三 LINUX系统安装说明 (35)附录四网域登录使用方式 (38)附录五常见问题解答 (41)海光BIOS保护卡安装流程第一章海光BIOS保护卡及操作系统的安装首先非常感谢您使用海光产品。

海光BIOS保护卡能大批量地完成整个计算机机房系统及软件的安装或更新。

先将一台安装好海光BIOS 保护卡系统、操作系统及应用软件的计算机设定为发送端,其余所有的计算机利用海光BIOS保护卡附带的SNCOPY网络联机拷贝盘设定为接收端,通过网络将发送端的硬盘数据同时复制到所有的计算机中,并自动修改所有计算机的IP地址等网络设置,完成整个计算机机房系统的安装和更新。

1-1 安装前的准备安装本系统前,请您确认以下相关事项:1、请进入您计算机CMOS管理界面1.将CMOS中的病毒警告关闭。

2.将CMOS中显卡以外的映射地址设为Disable。

3.将CMOS中的Network/LAN引导选项,设为Enabled或设定为网络优先启动(该项没有,可以不设定)。

4.如CMOS中有Fast Boot的选项,请将此项设定为Disable(该项没有,可以不设定)。

ED-588 Digital IO 8 Inputs + 8 Outputs说明书

ED-588 ETHERNET TO Digital IO 8 Inputs + 8 Outputs• 8 Digital Inputs and 8 Digital Outputs• Drives high current and high voltage loads• Ideal for inductive, capacitive & resistive loads• Factory floor process control and automation• Network enable your NuDAM/ADAM modules• -30o C to +80o C Temperature range• +5V to +30V DC Input PowerED-588Usage Model for ED-588Gateway RS485Remote access formaintenance andmonitoringPower from laptopfor configurationDual redundant powersupplyMachines /StepperMotorsAndonLightsASCII softwarecommands - LabView,MATLAB, Agilent VEE8 Digital OutputsRS485 Gateway for NuDAM/ADAM ModulesEthernet port 8 Digital InputsLED Status IndicationIntegral DIN rail mount+5V to +30V Power SupplyEasy to use Interface: Great features for remote monitoringExtended Temperature Range:-30ºC to +80ºC operating range copes with changing temperatures for harsh environments. Monitor CPU temperature via the web interface or programmatically using ASCII commands.Brainboxes’ Easy Wire Feature:Removable screw terminal blocks make installation easier and quicker Colour coded blocks and ports prevents incorrect connection Numbered Pins simplifies wiring and removes confusionSlim Shape:Small foot print for when DIN rail space is a premium Only 22.6mm wideEthernet to DIO Device Server:The Ethernet to DIO device is implemented using a Windows COM port driver that is completely compatible with all popular PC packages such as LabView, MATLAB and Agilent VEE and support a range of popular APIs. Continue to get value from your existing development and process control system.Watchdog feature:Allows independent known good states to be set for power up, comms link watchdog and hardware watchdog. Programmable time range allows full con-trol.Lifetime Warranty and Support:We can help with every aspect of your project, from getting you up and running to custom application.Signed Drivers and Rigorous testing:We use continuous automated testing of our in-house drivers and software to ensure when you install one of our devices ‘it just works’. Our software allows hassle free installation, configuration and monitoring via our easy to use webpage. The software gives local COM ports that are backwards compatible enabling legacy applications and the device to work with a myriad of different 3rd party software. We make all our software versions available to downloadfrom our website.Wide Range Redundant Dual Power Input:+5VDC to +30VDC accommodates variation in the +24VDC factory floor and allows alternative power sources. A second power supply can be fitted as aback-up to prevent down time should one power source fail.Power from any USB Port:Can use 5 Volt power from any computer USB port via optional accessory cable PW-650 - Useful for configuring the device from a laptop in the field. Gateway RS485 Serial Port:Half duplex RS485 port allows connection and control of industry standardNuDAM, eDAM and ADAM modules modules using ASCII protocols.Grounding:Correctly wired grounds help cut down on electromagnetic interference5 pin terminals allow a ground on the 5th pin of each blockFunctional earth connection to the DIN railHundreds of thousands program with these packages every day.supported. With APIs and sample program code for: Microsoft .NET, C#, Visual Basic, C++, JavaScript, PHP, Java, Objective-CLaptops, Tablets, Phones or low cost embedded devices, almost any device you wish.bit Editions / Windows Server 2003 32 bit & 64 bit Editions. TCP and web browser interface for other OS’s & Linux, e.g.$01M read the name of device address 01!01ED-588device 01 replies that its name is ED-588$01F read firmware version number of device address 01!012.54firmware version of device 01 is 2.54@01read digital input output status of device 01>1A45device 01 digital input data= 1A (=00011010) digital output data = 45 (=01000101)$012read configuration of device 01!01400500device 01 40=typecode, 05 =gateway RS485 port is at 4800 Baud, 00=No checksumFamiliar ASCII Command Protocol:The ED range of devices uses the de facto industry standard ASCII command protocol implemented in the popular ADAM/NuDAM/EDAM modules.Typical examples include:The ED device’s webpage has an interactive console where any command can be entered and it is immediately executed showing the device’s response.22.6 mmType of Port TerminalBlock Pin 1Pin 2Pin 3Pin 4Pin 5Digital Out Yellow GND DOut 0DOut 1DOut 2DOut 3Digital Out Orange GND DOut 4DOut 5DOut 6DOut 7Gateway Grey GND RS-485 D-RS-485 D+RS-485 D+RS-485 D-Digital In Green GND DIn 0DIn 1DIn 2DIn 3Digital In Blue GND DIn 4DIn 5DIn 6DIn 7Power Black Power GND+Vin A+Vin B Power GND Func GNDLink LEDStatus LEDActivity LEDGateway LEDReset HoleEthernet PortGB AEOF 00031/11Trademarks and logos are the property of Brainboxes Ltd. All other trademarks are the property of their respective owners.。

VSC8504 VSC8552 VSC8572 VSC8574 过渡设计指南说明书