DSP期末考试重点第二套

DSP历年期末试卷及答案

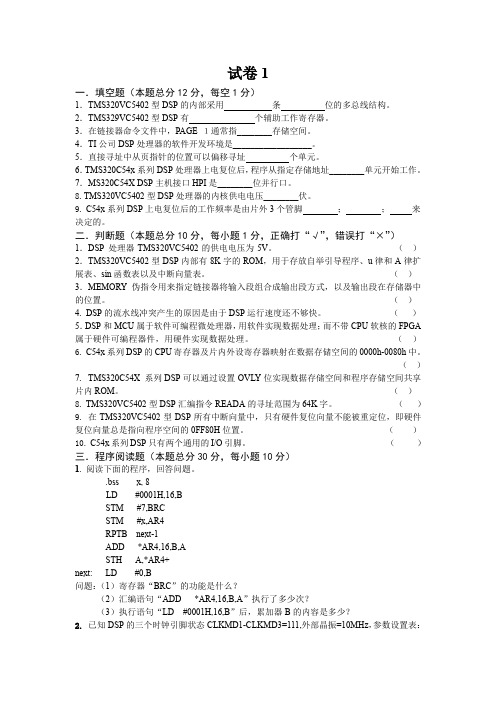

试卷1一.填空题(本题总分12分,每空1分)1.TMS320VC5402型DSP的内部采用条位的多总线结构。

2.TMS329VC5402型DSP有个辅助工作寄存器。

3.在链接器命令文件中,PAGE 1通常指________存储空间。

4.TI公司DSP处理器的软件开发环境是__________________。

5.直接寻址中从页指针的位置可以偏移寻址个单元。

6.TMS320C54x系列DSP处理器上电复位后,程序从指定存储地址________单元开始工作。

7.MS320C54X DSP主机接口HPI是________位并行口。

8.TMS320VC5402型DSP处理器的内核供电电压________伏。

9. C54x系列DSP上电复位后的工作频率是由片外3个管脚;;来决定的。

二.判断题(本题总分10分,每小题1分,正确打“√”,错误打“×”)1.DSP 处理器TMS320VC5402的供电电压为5V。

()2.TMS320VC5402型DSP内部有8K字的ROM,用于存放自举引导程序、u律和A律扩展表、sin函数表以及中断向量表。

()3.MEMORY伪指令用来指定链接器将输入段组合成输出段方式,以及输出段在存储器中的位置。

()4. DSP的流水线冲突产生的原因是由于DSP运行速度还不够快。

()5.DSP和MCU属于软件可编程微处理器,用软件实现数据处理;而不带CPU软核的FPGA 属于硬件可编程器件,用硬件实现数据处理。

()6. C54x系列DSP的CPU寄存器及片内外设寄存器映射在数据存储空间的0000h-0080h中。

()7.TMS320C54X 系列DSP可以通过设置OVL Y位实现数据存储空间和程序存储空间共享片内ROM。

()8. TMS320VC5402型DSP汇编指令READA的寻址范围为64K字。

()9.在TMS320VC5402型DSP所有中断向量中,只有硬件复位向量不能被重定位,即硬件复位向量总是指向程序空间的0FF80H位置。

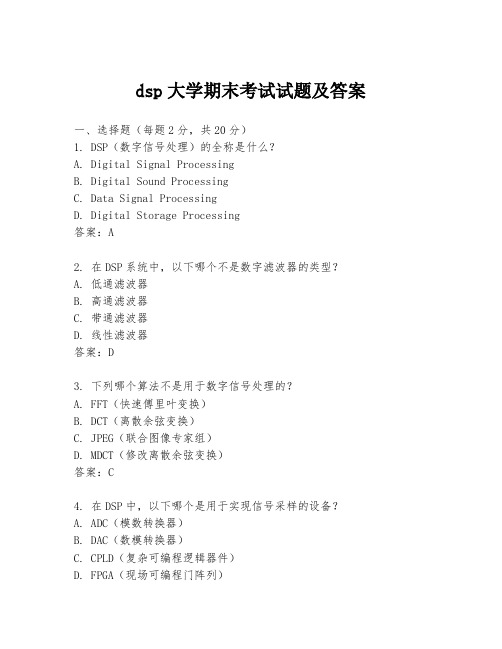

dsp大学期末考试试题及答案

dsp大学期末考试试题及答案一、选择题(每题2分,共20分)1. DSP(数字信号处理)的全称是什么?A. Digital Signal ProcessingB. Digital Sound ProcessingC. Data Signal ProcessingD. Digital Storage Processing答案:A2. 在DSP系统中,以下哪个不是数字滤波器的类型?A. 低通滤波器B. 高通滤波器C. 带通滤波器D. 线性滤波器答案:D3. 下列哪个算法不是用于数字信号处理的?A. FFT(快速傅里叶变换)B. DCT(离散余弦变换)C. JPEG(联合图像专家组)D. MDCT(修改离散余弦变换)答案:C4. 在DSP中,以下哪个是用于实现信号采样的设备?A. ADC(模数转换器)B. DAC(数模转换器)C. CPLD(复杂可编程逻辑器件)D. FPGA(现场可编程门阵列)答案:A5. 下列哪个参数不是描述数字信号的?A. 幅度B. 频率C. 相位D. 电阻答案:D6. 在DSP中,以下哪个指标用于衡量信号的频域特性?A. 幅度谱B. 相位谱C. 功率谱D. 所有选项答案:D7. 下列哪个选项不是DSP系统设计的关键考虑因素?A. 处理速度B. 内存容量C. 电源电压D. 信号带宽答案:C8. 在DSP编程中,以下哪个不是常用的编程语言?A. C语言B. C++语言C. MATLABD. VHDL答案:C9. 下列哪个不是DSP系统的应用领域?A. 音频处理B. 图像处理C. 无线通信D. 机械制造答案:D10. 在DSP系统中,以下哪个是用于实现信号放大的组件?A. 运算放大器B. 滤波器C. 调制器D. 编码器答案:A二、填空题(每题2分,共20分)1. DSP技术在______和______处理中具有广泛应用。

答案:数字信号;模拟信号2. 一个典型的DSP系统包括______、______和______。

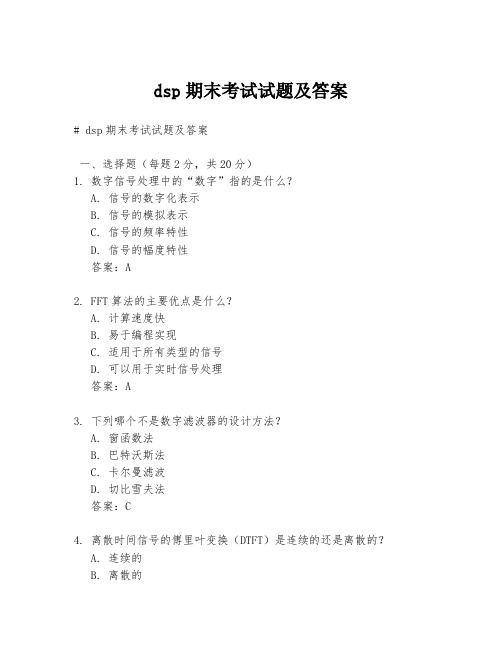

dsp期末考试试题及答案

dsp期末考试试题及答案# dsp期末考试试题及答案一、选择题(每题2分,共20分)1. 数字信号处理中的“数字”指的是什么?A. 信号的数字化表示B. 信号的模拟表示C. 信号的频率特性D. 信号的幅度特性答案:A2. FFT算法的主要优点是什么?A. 计算速度快B. 易于编程实现C. 适用于所有类型的信号D. 可以用于实时信号处理答案:A3. 下列哪个不是数字滤波器的设计方法?A. 窗函数法B. 巴特沃斯法C. 卡尔曼滤波D. 切比雪夫法答案:C4. 离散时间信号的傅里叶变换(DTFT)是连续的还是离散的?A. 连续的B. 离散的C. 既连续又离散D. 都不是答案:A5. 采样定理指出,采样频率至少应该是信号最高频率的多少倍?A. 1倍B. 2倍C. 3倍D. 4倍答案:B...(此处省略其他选择题,共10题)二、简答题(每题10分,共20分)1. 解释什么是离散傅里叶变换(DFT)以及它与连续傅里叶变换(FT)的区别。

答案:离散傅里叶变换(DFT)是一种将离散时间信号转换为频域表示的方法。

它是一种离散的变换,意味着输入和输出都是离散的。

DFT通常用于数字信号处理中,可以计算出信号在各个频率上的幅度和相位。

与DFT不同,连续傅里叶变换(FT)是将连续时间信号转换为连续的频域表示,它适用于模拟信号处理。

2. 简述数字滤波器的基本概念及其分类。

答案:数字滤波器是一种对数字信号进行处理的系统,它允许某些频率的信号通过,同时抑制或减少其他频率的信号。

数字滤波器可以根据它们的频率响应特性进行分类,主要分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

每种类型的滤波器都设计用于处理特定频率范围内的信号。

三、计算题(每题15分,共30分)1. 给定一个离散时间信号 x[n] = {1, 2, 3, 4},计算其DFT X[k]。

答案:X[k] = DFT{x[n]} = Σ_{n=0}^{N-1} x[n] * e^(-j * 2π * k * n / N)其中,N=4,计算得到 X[k] 的值。

DSP期末复习整理

DSP期末复习整理第⼀章绪论1.1 DSP的基本概念1.2.2 DSP芯⽚的特点1) 采⽤哈佛结构2) 采⽤多总线结构3) 采⽤流⽔线结构4) 具有专⽤的硬件乘法-累加器5) 具有特殊的寻址⽅式和指令6) ⽀持并⾏指令操作7) 硬件配置强,具有较强的借⼝功能8) ⽀持多处理器结构1.2.3 DSP芯⽚的分类1)按照数据格式的不同DSP芯⽚可以划分为:定点DSP芯⽚和浮点DSP芯⽚2)按照字长⼤⼩的不同,DSP芯⽚可以划分为:16位、24位、32位3)按照不同⽣产⼚家的产品系列划分,有TI公司的TMS320系列ADI公司的Blackfin、SHARC、TigerSHARCA系列飞思卡尔公司的MSC系列习题1.2简述DSP系统组成1.3DSP芯⽚与普通单⽚机相⽐有什么特点1.5DSP芯⽚有哪些主要特点第⼆章TMS320C55x的硬件结构2.1 TMS320C55x的总体结构2.1.1 C55x CPU内部总线结构C55x CPU含有12组内部独⽴总线,即:程序地址总线(PAB):1组,24位;程序数据总线(PB): 1组,32位;数据读地址总线(BAB、CAB、DAB):3组,24位;数据读总线(BB、CB、DB):3组,16位;数据写地址总线(EAB、FAB):2组,24位;数据写总线(EB、FB):2组,16位。

2.1.2 C55x 的CPU组成C55x的CPU包含5个功能单元:指令缓冲单元(I单元)、程序流单元(P单元)、地址-数据流单元(A单元)、数据运算单元(D单元)和存储器接⼝单元(M单元)。

I单元包括32X16位指令缓冲队列和指令译码器。

此单元主要接收程序代码并负责放⼊指令队列,由指令译码器来解释指令,然后再把指令流传给其他的⼯作单元(P单元、A单元、D单元)来执⾏这些指令P单元包括程序地址发⽣器和程序控制逻辑。

此单元产⽣所有程序空间地址,并送到PAB总线。

A单元包括数据地址产⽣电路(DAGEN)、附加的16位ALU和1组寄存器,此单元产⽣读/写数据空间地址,并送到BAB、CAB、DAB总线。

《DSP原理与应用》期末考试试题

《DSP原理与应用》期末考试试题一、选择题(每题2分,共20分)1、在数字信号处理中,常用的滤波器是()。

A.巴特沃斯滤波器B.贝塞尔滤波器C.拉普拉斯滤波器D.理想滤波器2、在进行傅里叶变换时,如果采样频率为fs,则采样点数为N的信号的离散傅里叶变换的结果中,频域的分辨率是()。

A. fs/NB. 2fs/NC. fs/(2N)D. fs/(2N+1)3、在进行Z变换时,如果时间序列的采样点数为N,则Z变换的收敛域是()。

A. |z|<NB. |z|<N+1C. |z|<N-1D. |z|<N-24、在进行小波变换时,如果小波基为ψ(t),则小波变换的结果是一个()。

A.实数序列B.复数序列C.实数矩阵D.复数矩阵5、在进行离散傅里叶变换时,如果信号的采样点数为N,则其频率分辨率是()。

A. 2π/NB. π/NC. π/(2N)D. π/(N+1)二、填空题(每题3分,共30分)1、在数字信号处理中,常用的滤波器有________、________、________、________。

2、在进行傅里叶变换时,如果采样频率为fs,则采样点数为N的信号的离散傅里叶变换的结果中,频域的分辨率是________。

3、在进行Z变换时,如果时间序列的采样点数为N,则Z变换的收敛域是|z|<________。

4、在进行小波变换时,如果小波基为ψ(t),则小波变换的结果是一个________。

5、在进行离散傅里叶变换时,如果信号的采样点数为N,则其频率分辨率是________。

6、在数字信号处理中,常用的窗函数有________、________、________、________。

7、在进行数字滤波器的设计时,常用的方法有________、________、________。

8、在进行数字信号的分析时,常用的工具包括________、________、________。

《美学原理》期末考试试题及答案一、单项选择题1、下列哪个选项不属于美学的研究范畴?A.绘画、音乐、诗歌等艺术形式的美学原理B.建筑、设计、自然等现实生活中的美学应用C.精神分析学、现象学等其他学科的美学分支D.美食、时尚、旅游等消费领域的美学实践正确答案:C.精神分析学、现象学等其他学科的美学分支。

DSP期末试题与答案,推荐文档

在节电模式下,使之更适合于手机。

(7)在片仿真接口,片上的JTAG接口符合IEEE149.1边界扫描逻辑接口标准,可与主机连接,用于芯片的仿真和测试。

9.定时器由哪些寄存器组成,他们是如何工作的?答:定时器主要由3个寄存器所组成,包括定时寄存器TIM 、定时周期寄存器 PRD 、定时控制寄存器TCR。

定时寄存器TIM是一个减1计数器,提供定时器目前的计数值;周期定时器PRD用来存取定时时间常数;定时控制寄存器TCR中包含定时器的控制位和状态位,可以使能和屏蔽定时器,决定定时器的工作模式,用来控制定时器的操作。

二、指令解释1、MAC *AR3+,*AR4+,A,B;B=A-*AR3+*AR4;AR3=AR3+1;AR4=AR4+12、SUB #12345,8,A,B;B=A-12345<<83、ADD *AR2+,*AR2-,A;A=*(AR2)+*(AR2+1)4、RPT #99NOP;重复NOP100次5、MVDD *AR3+,*AR5+;数据存储器内部传送数据AR3→AR5,且指令结束后AR3与AR5加16、ABDST *AR3+,*AR4+;B=(*AR3-*AR4)<<167、CALA A;按累加器规定的地址调用子程序8、ST T,*AR7- *AR7=T,AR7=AR7-19、DST B,*AR1+ AR1=B,AR1=AR1+110、STA, *AR4+||LD *AR4-,A AR4=A,AR4=AR4+1|| A=AR4,AR4-111、LD #0032H,4,A;立即数0032H先左移4位后,再加载累加器A12、STM #1000H,*AR2;立即数1000H存储到AR2指向的地址单元13、MAC #345,A,B;立即数345与T寄存器内值相乘后与累加器A相加,结果加载累加器B14、MVDD *AR3-,100H;AR3指向的地址单元的值传送给地址100H,AR3中地址减一15、LDM *AR1,A;AR1指向的地址单元的值加载到累加器A16、LD #80H, A 把立即数80H装入累加器17、WRITA SMEM 把Smem所指定的数据存储单元中的一个数传送到累加器A所指定的成序存储单元18、PORTR FIFO,*AR5 把一个数从端口为FIFO的I/O口复制到AR5寄存器所指向的数据存储单元中19、LDM MMR ,A ;将MMR 装入累加器A 中20、MVKD SAMPLE,*AR521、ADD *AR3+,14,A ;将AR3左移14加上A →AAR3=AR3+122、MPYA TEMP2;B<=A.Temp2.T=Temp223、STA , *AR4+||LD *AR4-,A24、DST B ,*AR1-; B 存到长字单元 AR1中,且AR 减125、MACD *AR2-,COEFFS,A26、STL A ,@quot;将 累加器A 的低16位字存放在quot 的存储单元中27、ADD #4568H ,8,A ,B;将4568H 左移8位与A 相加,赋给B28、LDM AR1,A;存储器映像寄存器寻址方式,将映像寄存器加载累加器AR1 → A 的低位,其余位置为029、MVDD *AR3+,*AR5+;数据存储器内部传送数据AR3→AR5,且指令结束后AR3与AR5加130、MPYA TEMP2;B<=A.Temp2.T=Temp2四、编程1.用汇编语言编制计算的程序。

dsp期末考试试题及其答案

dsp期末考试试题及其答案### DSP期末考试试题及其答案#### 一、选择题(每题2分,共20分)1. 在数字信号处理中,DFT(离散傅里叶变换)的主要作用是什么?A. 信号调制B. 信号解调C. 信号滤波D. 频域分析2. 下列哪个不是FIR(有限脉冲响应)滤波器的特点?A. 线性相位B. 无限脉冲响应C. 易于设计D. 稳定的频率响应3. 以下哪个算法是用于快速傅里叶变换的?A. 快速卷积算法B. 快速傅里叶变换(FFT)C. 快速沃尔什变换D. 快速余弦变换4. 在数字滤波器设计中,哪种类型的滤波器可以保证无振铃效应?A. 巴特沃斯滤波器B. 切比雪夫滤波器C. 汉明滤波器D. 理想滤波器5. 下列哪个是数字信号处理中的基本概念?A. 采样B. 量化C. 编码D. 所有选项都是#### 二、简答题(每题10分,共30分)1. 解释什么是窗函数,它在信号处理中的作用是什么?2. 描述IIR(无限脉冲响应)滤波器和FIR滤波器的主要区别。

3. 什么是混叠现象?如何避免它?#### 三、计算题(每题25分,共50分)1. 给定一个离散时间信号 \( x[n] = \{2, 4, 6, 8\} \),请计算其DFT,并说明其频域特性。

2. 设计一个FIR滤波器,其脉冲响应为 \( h[n] = \{1, 2, 3, 4\} \),计算其频率响应,并讨论其滤波特性。

#### 四、分析题(共30分)1. 描述数字信号处理中的去噪技术,并举例说明其在实际应用中的重要性。

#### 参考答案#### 一、选择题1. D2. B3. B4. D5. D#### 二、简答题1. 窗函数是一种在频域中对信号进行加权的技术,它的作用是减少信号的频谱泄漏,提高频谱分析的分辨率。

2. IIR滤波器具有反馈路径,其脉冲响应是无限的,而FIR滤波器没有反馈路径,其脉冲响应是有限的。

3. 混叠现象发生在信号采样频率低于奈奎斯特频率时,可以通过增加采样频率或使用抗混叠滤波器来避免。

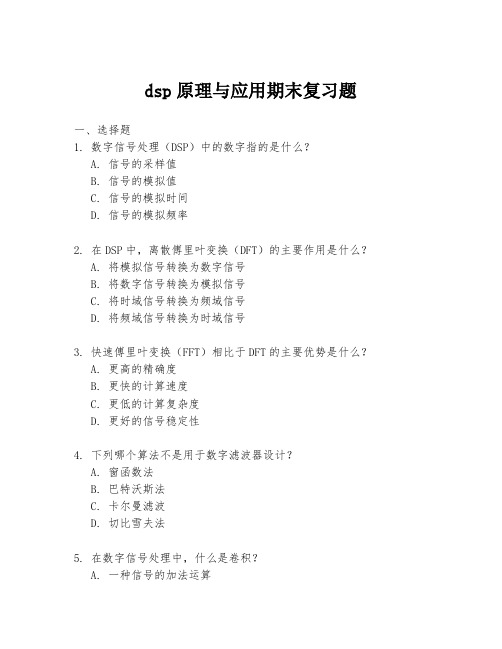

dsp原理与应用期末复习题

dsp原理与应用期末复习题一、选择题1. 数字信号处理(DSP)中的数字指的是什么?A. 信号的采样值B. 信号的模拟值C. 信号的模拟时间D. 信号的模拟频率2. 在DSP中,离散傅里叶变换(DFT)的主要作用是什么?A. 将模拟信号转换为数字信号B. 将数字信号转换为模拟信号C. 将时域信号转换为频域信号D. 将频域信号转换为时域信号3. 快速傅里叶变换(FFT)相比于DFT的主要优势是什么?A. 更高的精确度B. 更快的计算速度C. 更低的计算复杂度D. 更好的信号稳定性4. 下列哪个算法不是用于数字滤波器设计?A. 窗函数法B. 巴特沃斯法C. 卡尔曼滤波D. 切比雪夫法5. 在数字信号处理中,什么是卷积?A. 一种信号的加法运算B. 一种信号的乘法运算C. 一种信号的乘积运算D. 一种信号的时间延迟运算二、简答题1. 解释什么是数字信号处理,并简述其在现代通信系统中的应用。

2. 描述离散傅里叶变换(DFT)和快速傅里叶变换(FFT)的区别和联系。

3. 数字滤波器有哪些类型?请列举至少三种,并简要说明它们的特点。

4. 解释什么是傅里叶变换的时移性质,并给出一个具体的例子。

5. 在数字信号处理中,什么是过采样和欠采样?它们各自的优缺点是什么?三、计算题1. 给定一个离散时间信号 \( x[n] = \{3, 5, 2, 7, 4, 6\} \),请计算其DFT \( X[k] \)。

2. 假设有一个低通滤波器,其理想频率响应为 \( H(\omega) =\begin{cases} 1 & \text{for } 0 \leq \omega \leq \pi/2 \\ 0 & \text{for } \pi/2 < \omega \leq \pi \end{cases} \),请设计一个简单的数字滤波器来近似这个理想频率响应。

3. 给定两个离散信号 \( x[n] = \{1, 2, 3\} \) 和 \( y[n] = \{4, 5, 6\} \),请计算它们的线性卷积 \( z[n] = x[n] * y[n] \)。

dsp期末复习题

dsp期末复习题DSP期末复习题一、选择题1. 数字信号处理(DSP)的核心是:A. 模拟信号处理B. 模拟到数字的转换C. 数字到模拟的转换D. 数字信号的数学处理2. 下列哪个不是DSP系统的基本组成部分?A. A/D转换器B. DSP处理器C. D/A转换器D. 电源3. 在DSP中,FIR滤波器和IIR滤波器的主要区别在于:A. 滤波器的阶数B. 滤波器的类型C. 滤波器的系数D. 滤波器的反馈结构4. 下面哪个算法不是用于数字滤波器设计的?A. 窗函数法B. 频率采样法C. 快速傅里叶变换(FFT)D. 帕克-维纳(Parks-McClellan)算法5. FFT算法的主要优点是:A. 计算复杂度低B. 实现简单C. 适用于所有类型的信号D. 可以实时处理信号二、简答题1. 解释数字信号处理中的“过采样”和“欠采样”概念,并简述它们在实际应用中的意义。

2. 描述FIR滤波器和IIR滤波器的设计方法及其主要区别。

3. 简述快速傅里叶变换(FFT)的基本原理,并说明它在数字信号处理中的重要性。

4. 阐述数字信号处理在现代通信系统中的应用。

三、计算题1. 给定一个信号x[n] = {1, 2, 3, 4, 5, 6},求其DFT X[k]。

2. 设计一个FIR滤波器,其脉冲响应满足h[n] = {1, 0.5, 0.25},求其频率响应H(ω)。

3. 利用帕克-维纳算法设计一个带通滤波器,其通带频率为[0.2π, 0.4π],阻带频率为[0.1π, 0.15π]和[0.45π,0.5π],要求最小阶数。

四、论述题1. 论述数字信号处理在音频处理领域的应用,并举例说明。

2. 讨论数字信号处理技术在图像处理中的应用,以及它如何改善图像质量。

五、综合应用题1. 假设你正在开发一个实时音频处理系统,描述你将如何使用DSP技术来实现噪声抑制和回声消除。

2. 设计一个用于视频压缩的DSP算法,简述其基本原理,并讨论可能遇到的挑战。

DSP原理期末试卷和答案 甄选

最新DSP原理期末试卷和答案(优选.)rd一、单项选择题:(每小题2分,共30分)1、下面对一些常用的伪指令说法正确的是:( D )A、.def所定义的符号,是在当前模块中使用,在别的模块中定义的符号;B、.ref 所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

2、要使DSP能够响应某个可屏蔽中断,下面的说法正确的是( B)A、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置0B、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置1C、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置0D、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置13、对于TMS320C54x系列DSP芯片,下列说法正确的是…………( C )A、8位DSPB、32位DSPC、定点型DSPD、浮点型DSP4、若链接器命令文件的MEMORY部分如下所示:MEMORY{PAGE 0: PROG: origin=C00h, length=1000hPAGE 1: DATA: origin=80h, length=200h}则下面说法不正确的是()A、程序存储器配置为4K字大小B、程序存储器配置为8K字大小C、数据存储器配置为512字大小D、数据存储器取名为DATA5、在串行口工作于移位寄存器方式时,其接收由()来启动。

A、RENB、RIC、REN和RID、TR6、执行指令PSHM AR5之前SP=03FEH,则指令执行后SP=( A )A、03FDHB、03FFHC、03FCHD、0400H7、TMS320C54X DSP采用改进的哈佛结构,围绕____A__组_______位总线建立。

A、8,16B、16,8C、8,8D、16,168、TMS320C54X DSP汇编指令的操作数域中, A 前缀表示的操作数为间接寻址的地址。

(DSP技术及应用)期末复习要点

DSP复习要点1.按数据格式来分,DSP处理器有定点型DSP和浮点型DSP两类,其中TMS320C54x是德州仪器公司TI生产的16位定点型DSP系列芯片。

2.TI公司的DSP处理器常用开发环境是CCS(Code Composer Studio),其目标程序文件扩展名为.out。

3.TMS320C54x采用改进型的哈佛总线结构,由8条16位的多总线来访问程序和数据存储器,哈佛结构特点是数据总线和程序总线分开。

4.冯.诺依曼结构和哈佛结构:冯.诺依曼结构是将指令、数据和地址存储在同意存储器中,统一编址,依靠指令计数器提供的地址来区分是指令、数据还是地址。

哈佛结构是不同于传统冯.诺依曼结构的并行体系结构,其主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

5.TMS320C54X片内总线及其功能:C54X采用先进的哈佛结构并具有八组总线,其独立的程序总线和数据总线允许同时读取指令和操作数。

程序总线传送从程序存储器来的指令代码和立即数。

三组数据总线连接各种元器件。

CB和DB总线传送从数据存储器读出的操作数,EB总线传送写入到存储器中的数据。

四组地址总线PAB、CAB、DAB、EAB用来传送执行指令所需的地址。

6.TMS320C5416处理器内核工作电压为1.6V,IO管脚供电电压为3.3V。

7.C54x DSP复位后的工作频率是由晶体振荡器频率和片外3个管脚CLKMD1、CLKMD2和CLKMD3共同决定。

8.TMS320C5416有两个40位的累加器ACCA、ACCB,其中ACCA分为三部分,分别是AG、AH、AL。

9.TMS320C54x CPU组成:(1)CPU状态和控制寄存器:用于设置各种工作条件和工作方式的状态以及存储器配置状态和控制信息。

(2)40位算术逻辑单元、40位累加器A和B:两者共同完成算术运算和逻辑运算。

(3)桶形移位寄存器:使处理器能完成数字定标,位提取,对累加器进行归一化处理等操作。

DSP考试重点及复习要点(精)

思考题与练习题1.TMS320C54x系列DSP有哪些型号?2.TMS320C54x系列DSP的突出特点是什么?(从内部总线、运算单元、指令系统上看3.什么是循环寻址、位反序寻址,TMS320C54x系列DSP是否支持这种寻址方式?4.TMS320C54x系列DSP使用定点指令操作还是使用浮点指令操作?使用定点指令编程时如何防止溢出?用定点指令编程时是否还应考虑其它影响因素?有哪些影响因素?5.为了利用中断应编写哪些程序?TMS320C54x系列DSP的软件中断和硬件中断用法是否一样,有何不同?6.TMS320C54x系列DSP响应中断的条件有哪些?响应中断时DSP自动进行那些操作?7.TMS320C54x系列DSP的寄存器是通过寄存器名访问,还是对某个存储器地址访问?那种比较方便?8.汇编程序中的伪指令有什么作用?其中定义的段定义伪指令和链接命令文件内容有无联系?9.用C语言设计程序时C编译器会产生哪些代码段?哪些是用户定义的,哪些是C编译器添加的?10.C语言和汇编语言混合编程时,如何进行符号变量的联系?如何进行子程序调用?11.以CCS下的一个例子练习DSP的编程和代码产生过程。

12.DSP的硬件组成有哪些?13.为什么应尽量利用DSP的片内存储器?14.DSP如何与速度不同的片外存储器及其他外设进行数据交换?15.DSP的并口总线与串口各有何用途?16.DSP的定时器有几种用途?是举例说明。

17.如何在DSP系统中实现看门狗功能?18.设计高速数字系统是需要考虑哪些因素?19.如何确定模数转换时的采样率和量化位数?采样率过高有何缺点?20.相对于DFT,FFT的运算量能降低多少?为什么有时仍用DSP进行DFT而非FFT?21.DSP如何高效率地完成FFT?它在计算、寻址、传数上是如何支持FFT的?22.进行FFT时,怎样考虑实数/复数、添0等对FFT的影响?23.定点FFT要考虑数据溢出,为此进行的移位操作是否使程序复杂且执行速度降低?24.循环寻址在FIR滤波中的优点怎样体现?试用所掌握的几种DSP编写循环寻址的小程序?25.IIR与FIR滤波相比有何优缺点?26.利用FFT是否可提高FIR滤波的效率?27.定点DSP设计和浮点DSP设计有何区别?怎样用C或Matlab工具模拟、验证DSP处理程序?28.如何用DSP进行求平方根、三角函数等运算?29.对一个线性调频信号x(n=cos(2π·f·t/f s进行采样,采样率为f s,并进行FFT,观察f s和频谱形状、频谱混叠间的关系。

DSP期末试题与答案

一、填空题:1。

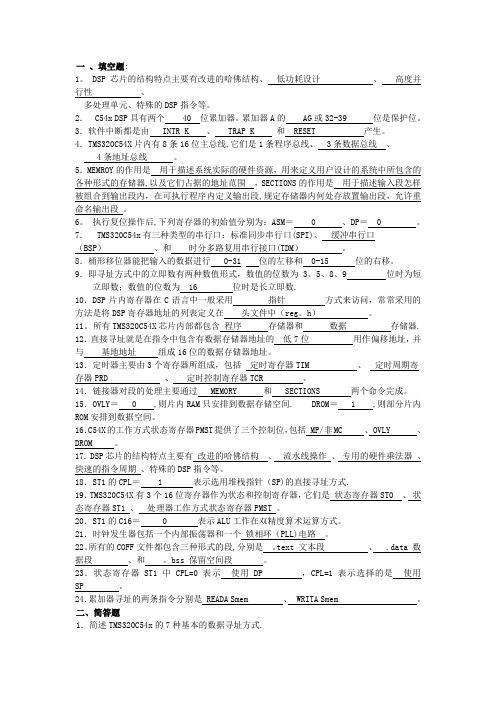

DSP芯片的结构特点主要有改进的哈佛结构、低功耗设计、高度并行性、多处理单元、特殊的DSP指令等。

2.C54x DSP具有两个 40 位累加器。

累加器A的 AG或32-39 位是保护位。

3.软件中断都是由 INTR K 、 TRAP K 和 RESET 产生。

4.TMS320C54X片内有8条16位主总线,它们是1条程序总线、 3条数据总线、4条地址总线。

5.MEMROY的作用是用于描述系统实际的硬件资源,用来定义用户设计的系统中所包含的各种形式的存储器,以及它们占据的地址范围,SECTIONS的作用是用于描述输入段怎样被组合到输出段内,在可执行程序内定义输出段,规定存储器内何处存放置输出段,允许重命名输出段。

6。

执行复位操作后,下列寄存器的初始值分别为:ASM= 0 、DP= 0 。

7.TMS320C54x有三种类型的串行口:标准同步串行口(SPI)、缓冲串行口(BSP)、和时分多路复用串行接口(TDM)。

8.桶形移位器能把输入的数据进行 0-31位的左移和 0-15 位的右移。

9.即寻址方式中的立即数有两种数值形式,数值的位数为 3、5、8、9 位时为短立即数;数值的位数为 16 位时是长立即数.10.DSP片内寄存器在C语言中一般采用指针方式来访问,常常采用的方法是将DSP寄存器地址的列表定义在头文件中(reg。

h)。

11。

所有TMS320C54X芯片内部都包含程序存储器和数据存储器. 12.直接寻址就是在指令中包含有数据存储器地址的低7位用作偏移地址,并与基地地址组成16位的数据存储器地址。

13.定时器主要由3个寄存器所组成,包括定时寄存器TIM 、定时周期寄存器PRD 、定时控制寄存器TCR 。

14.链接器对段的处理主要通过 MEMORY 和 SECTIONS 两个命令完成。

15.OVLY= 0 ,则片内RAM只安排到数据存储空间. DROM= 1 ,则部分片内ROM安排到数据空间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一章1. DSP的基本特点有那些?答:○1采用哈弗结构○2采用多总线技术○3采用流水线技术○4配有专用的硬件乘法——累加器○5具有特殊的DSP指令○6快速的指令周期○7硬件配置强○8支持多处理器结构○9省电管理和低能耗2.数据存储器3个片内DARAM块:B0 、B1 、B2。

B0块即可配置为数据存储器,也可配置为程序存储器;B1和B2块只能配置为数据存储器:其中B0和B1模块各有256个字,B2块有32个字。

双访问随机存储器DARAM 含544个字节;单随机访问SARAM 含2K ;程序存储器中flash 含32K 。

3.JTAG port 在线仿真模块第二章1.DSP 内部总线有6组:数据写总线(DWEB)、数据读总线(DRDB)、程序读总线(PRDB)、程序地址总线(PAB){数据写地址总线、数据读地址总线}2.累加器ACC 为32 位F 片内DARAM(B0)配置位:若CNF=0,可配置的双扣RAM区被映射到数据存储空间;若CNF=1,可配置的双口RAM区被映射到程序存储空间。

CNF位可通过“SETC CNF”、“CLRC CNF”和LST指令修改。

/RS复位时,CNF置为0。

4.DP计算每页128字,全部64k的数据存储器包含512个数据页,其标号范围为0~511。

当前页由状态寄存器ST0中的9位数据页指针(DP)的值来确定。

因此,当使用直接寻址指令时,用户必须事先指定数据页,并在访问数据存储器的指令中指定偏移量。

DP计算方法:DP值乘80H 转十六进制乘法,然后加上偏移量。

5.F240x内核提供一个不可屏蔽的中断NMI和6个按优先级获得服务的可屏蔽中断INT1~INT6。

DSP的中断请求/应答硬件逻辑和中断服务程序软件都是两级的层次:PIE和CPU。

CPU中断寄存器包括:中断标志寄存器(IFR)和中断控制寄存器(IMR)。

外设事件要引起CPU中断,必须保证:外设事件的中断使能位被使能,CPU内核级的6个可屏蔽中断中,能控制外设事件高级中断至少有一个被使能。

在外设事件发生时,首先将其在外设中断控制器中的标志位置1,从而引起CPU内核的INT1~INT6中的一个产生中断。

为清楚一个IFR位,必须向其写1,而不是0。

为了使能中断,应设置相应的IMR位为1,而屏蔽中断时,只需将相应的IMR位设为0。

外设向DSP中断过程方框图的描述:当外设中断事件发出中断请求时,外设中断寄存器PR中的中断标志位IF就被置1,再判断中断使能位IE是否为1,若为1则向PIE发出外设中断请求,若不为1则中断产生逻辑等待直到IE位被置1或IF位被软件清零,才向PIE发出外设中断请求,外设中断请求位就被置1且向INTx发出中断请求,然后CPU接受INTx请求,同时IFR中断标志位被置1,再判断IMR中断屏蔽位是否为1,若不为1则中断产生逻辑等待直到IMR位被置1或IFR位被软件清零;若为1则继续判断INTM是否为0,若不为0则等待被清零,若为0,则CPU辨认INTx并产生中断应答,此时CPU同时做两件事:一件,CPU中断应答且清楚PIE中的中断请求,且PIE逻辑装载中断向量到中断向量寄存器PIVR ,PIE逻辑使能悬挂起INTx,然后下一个悬挂的INTx送到CPU响应;另一件,IFR位被请0 ,INTM位被置1,PC指针跳到INTx的向量地址0000h~000Ch,CPU转入GISR程序进行现场保护,且用户代码保存上下文,从PIVR中读取外设中断向量,再判断PIV是否为假中断,若为假则CPU转入假中断服务子程序,若不是假中断,则CPU 转入SISR子程序,进而到SISR外设终端服务子程序执行中断子程序中的事件,同时并清外设寄存器中的IF标志位和INTN位,执行完返回主程序。

关全局中断指令:SETC INTM 开全局中断指令:CLRC INTM要清除一个INF位,必须向其写1,不是写0第三章1. 3种基本的存储器寻址方式:立即寻址方式、直接寻址方式和间接寻址方式。

举例说明如下:立即寻址:RPT #49 ;将紧跟RPT指令后的那条指令执行50次直接寻址:ADD 9H , 5 ;(DP=4)将数据地址0209h处的内容左移5位后加至累加器间接寻址:SACL *+ ;(ARP=2)将累加器的低16位存于AR2所指向的地址单元,AR2的内容加12. 几种基本指令注释:MAR *+ ,AR3 ;(ARP=5)将当前辅助寄存器设为AR3 ,AR5的内容加1LACL *- ,AR1 ;(ARP=6)将AR6所指向的数据存储器单元的内容装载入ACC低16位,高16位清零,指令执行完后AR6的内容减1,ARP=1SACL *+ ;(ARP=2)将累加器的低16位存于AR2所指向的地址单元,AR2 的内容加1 ADD 9H ,5 ;(DP=4)将数据地址0209h处的内容左移5位后加至累加器LAR AR7 ,6 ;(DP=3:0180h~01FFh)将数据存储器地址0186h的内容装入AR7BIT 3 ,6 ;(DP=5:0280h~02FFh)将0283h 处的位9的值复制到状态寄存器ST1中的TC位BITT (数据位(15 - TREG(3:0)))复制到到TCLACC *,4 ;(ARP=3)将AR3所指向的数据存储器的内容左移4位后装载到累加器ACCMPY#031h ;将临时寄存器TREG的内容乘上031h 的结果放在乘积寄存器PREG中RPT #49 ;将紧跟RPT指令后的那条指令执行50次SPLK #30h ,5 ;(DP=2)将数据0030h存至数据寄存器单元0205处CMPR 00 ;(ARP=6)测试(AR6)与(AR0)是否相等若为01测试是否小于,10是否大于第五章1.定义段的伪指令1). asect 创建具有绝对地址的初始化命名段。

用. asect 定义的段可以包含代码和数据。

在绝对段内,用户可以使用. label 伪指令来定义可重定位标号。

2). bss 为为初始化的变量在. bss 段内保留空间。

3). sect 定义初始化命名段并把后续代码或数据与该段相联系。

用. sect 定义的段可包含代码或数据。

4). text 标示.text 段内代码部分。

. text 段通常包含可执行代码。

5). usect 在初始化命名段内保留空间。

. usect 伪指令和. bss 伪指令相类似,但是它允许用户与段. bss 分开保留空间。

小结:. text ,. data ,. sect ,. asect 创建已初始化段;. bss ,. usect 创建未初始化的段;. sect ,. usect 创建自定义段和子段。

命令文件的后缀为. CMD。

该文件实现对程序存储器空间和数据存储器空间的分配。

其作用是定义空间和目标文件存储空间位置的重新分配。

其常用的伪指令有MEMORY 和SECTIONS 。

第八章1.F2407系列DSP有多达40个通用、双向的数字量I/O(GPIO)引脚。

(基本功能引脚和一般I/O复用引脚所有专用I/O和复用I/O引脚的功能都可通过9个16位控制寄存器来设置。

这些寄存器分为两大类:3个I/O端口复用控制寄存器(MCRx)用来控制选择I/O端口作为基本功能或一般I/O引脚功能。

{MCRA:IOPA0~IOPA7 ,IOPB0~IOPB7 ;MCRB: IOPC0~IOPC7 ,IOPD0; MCRC: IOPE0~IOPE7, IOPF0~IOPF6}6个数据和方向控制寄存器(PxDA TDIR)当I/O端口用作一般I/O引脚功能时,用数据和方向控制寄存器可控制数据和双向I/O引脚的数据方向。

{位15~8 xnDIR 0 输入方式,1输出方式;位7~0 IOPxn 0 低电平方式,1高电平方式}第九章1. 每个F240x器件包括两个事件管理器EV A和EVB,事件管理器模块包括2个通用定时器(GP)、3个比较单元、3个捕获单元以及正交编码脉冲电路QEP。

2. 定时计数器(16位)的计数范围是0~65535 。

定时器为定时比较单元、全比较单元、系统时钟、捕获单元提供时基。

3. 每个通用定时器有4种可选择的操作模式:○1停止/保持模式○2连续增计数模式(产生非对称波形○3定向增/减计数模式○4连续增/减计数模式(产生对称PWM波)第十章F2407的A/D转换模块(ADC)具有以下特点:1)带内置采样和保持(S/H)的10位ADC。

2)多达16个的模拟输入通道(ADCIN0~ADCIN15)。

3)自动排序的能力。

一次可执行最多16个通道的“自动转换”,而每次要转换的通道都可通过编程来选择。

4)两个独立的最多可选择8个模拟转换通道的排序器(SEQ1和SEQ2)可以独立工作在双排序器模式,或者级连之后工作在一个最多可选择16个模拟转换通道的排序器模式。

5)在给定的排序方式下,4个排序控制器(CHSELSEQn)决定了模拟通道转换的顺序。

6)可单独访问的16个结果寄存器(RESULT0~RESULT15)用来存储转换结果。

7)可有多个触发源启动A/D转换:软件:软件立即启动(用SOC SEQn位);EV A:事件管理器A(在EV A中有多个事件源可以启动A/D转换);{下溢、比较匹EVB:事件管理器B(在EVB中有多个事件源可以启动A/D转换);配、周期匹配}8)灵活的中断控制,允许在每一个或每隔一个序列的结束时产生中断请求。

9)排序器可工作在启动/停止模式,允许多个按时间排序的触发源同步转换。

10)EV A和EVB可各自独立地触发SEQ1和SEQ2(仅用于双排序器模式)。

11)采样和保持获取时间窗口有单独的预定标控制。

12)内置校验模式。

13)内置自测试模式。

位13即SOCSEQ1位置1的触发源:1.S/W软件向该位写1,2.EV A,3.EVB(仅在级联模式下)4.EXT外部引脚SOCSEQ2(近适用于双排序器模式)位置1的触发源:1.S/W软件向该位写1,2.EVB试验一程序源程序如下:test.asm 文件.bss x,1 ;定义一个字长的为初始化变量x.text ; 程序代码段ldp #8 ;设置DP=8LAR AR1,#0408h ;将#0408装载到AR1寄存器MAR *,AR1 ;指定当前辅助寄存器为AR1SPLK #2000H,* ;将#2000H 存至AR1所指向的数据存储器单元,即0408h 单元 LACL 8 ;(DP=8:0400h~047F )将0408h 单元的内容装在ACC 低16位, ;高16位清零ADD #05H ;将 05h 加至累加器ACC ,结果放在累加器中LDP #x ;DP指向 x 的首地址SACL x ;将累加器ACC低16位保存到x 单元中.endtest.cmd 文件MEMORY ;用来标示实际存在目标系统中且可被使用的存 ;储器范围{PAGE 0: ;程序存储器PM:ORIGIN=0044H,LENGTH=0100HPAGE 1: ;数据存储器B1:ORIGIN=0300H,LENGTH=0100H}SECTIONS ;描述输入段怎样被组合到输出段内,在可执行程序内定义输出段, ;规定在存储器内何处放置输出段,允许重命名输出端{.text:{}>PM PAGE 0.bss:{}>B1 PAGE 1}用通用定时器1产生1ms的延时中断服务:外部时钟为6MHz 经DSP 内部锁相环4倍频为24MHz ,通过定时器1预分频因子为64,所以计算出延时1ms 周期寄存器的值为0177h 。