数字逻辑电路设计及应用 电子科技大学

电子科技大学数字逻辑设计及应用作业答案

答案+我名字查看考卷——作业提交1当前得分:15 分(总分:100 分),折合成百分制共 15 分。

返回作业提交11.逻辑函数,请问其反函数 。

()()()[参考答案:] 分值:5 得分:分 系统自动批改于2019年9月19日 14点35分2. 有关异或逻辑的描述不正确的是 。

() 异或逻辑的反函数是同或逻辑 () 异或逻辑的对偶逻辑是同或逻辑() 一个逻辑变量和0异或得到的是其反函数 [参考答案:] 分值:5 得分:分 系统自动批改于2019年9月19日 14点35分3. 已知一个逻辑的最小项之和为F(, , )=∑m(0,4,7) ,以下哪个等式成立。

()()()[参考答案:] 分值:5得分:5分系统自动批改于2019年9月19日14点35分4. 下面所描述的逻辑函数表达式中,哪一种可以直接从真值表中得到,而无需其他中间步骤。

() 标准形式() 最简与或式() 与非-与非形式[参考答案:] 分值:5得分:5分系统自动批改于2019年9月19日14点35分5.下面有关最小项的描述正确的是。

()()()[参考答案:] 分值:5得分:0分系统自动批改于2019年9月19日14点35分6. 下面有关逻辑函数的描述中,正确的是。

() 逻辑函数的最小项之和是唯一的() 逻辑函数的最简与或表达式是唯一的() 逻辑函数的与非-与非逻辑表达式是唯一的[参考答案:] 分值:5得分:5分系统自动批改于2019年9月19日14点35分7. 请问或非逻辑的对偶关系是。

() 或非逻辑() 与非逻辑() 与或非逻辑[参考答案:] 分值:5得分:0分系统自动批改于2019年9月19日14点35分8.逻辑函数,请问其最小项之和为。

()()()[参考答案:] 分值:5得分:0分系统自动批改于2019年9月19日14点35分9. 逻辑函数Y(, , , )=∑m(0,2,4,6,9,13) + (1,3,5,7,11,15)的最简与或式为()() +’’() ’+() +[参考答案:] 分值:5得分:0分系统自动批改于2019年9月19日14点35分10.逻辑函数Y的真值表如下:。

数字逻辑电路(数电)课程设计_电子秒表_VHDL实现(含完整源代码!!)

电子科技大学UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA数字逻辑设计实验报告实验题目:电子秒表学生姓名:指导老师:一、实验内容利用FPGA设计一个电子秒表,计时范围00.00 ~ 99.00秒,最多连续记录3个成绩,由两键控制。

二、实验要求1、实现计时功能:域值范围为00.00 ~ 99.00秒,分辨率0.01秒,在数码管上显示。

2、两键控制与三次记录:1键实现“开始”、“记录”等功能,2键实现“显示”、“重置”等功能。

系统上电复位后,按下1键“开始”后,开始计时,记录的时间一直显示在数码管上;按下1键“记录第一次”,次按1键“记录第二次”,再按1键“记录第三次”,分别记录三次时间。

其后按下2键“显示第一次”,次按2键“显示第二次”,再按2键“显示第三次”,数码管上分别显示此前三次记录的时间;显示完成后,按2键“重置”,所有数据清零,此时再按1键“开始”重复上述计时功能。

三、设计思路1、整体设计思路先对按键进行去抖操作,以正确的得到按键信息。

同时将按键信息对应到状态机中,状态机中的状态有:理想状态、开始状态、3次记录、3次显示、以及其之间的7次等待状态。

因为需要用数码管显示,故显示的过程中需要对数码管进行片选和段选,因此要用到4输入的多路选择器。

在去抖、计时、显示的过程中,都需要用到分频,从而得到理想频率的时钟信号。

2、分频设计该实验中有3个地方需要用到分频操作,即去抖分频(需得到200HZ时钟)、计时分频(需得到100HZ时钟)和显示分频(需得到25kHZ时钟)。

分频的具体实现很简单,需首先算出系统时钟(50MHZ)和所需始终的频率比T,并定义一个计数变量count,当系统时钟的上升沿每来到一次,count就加1,当count=T时就将其置回1。

这样只要令count=1~T/2时clk=‘0’,count=T/2+1~T时clk=‘1’即可。

电子科技大学2012年数电半期考试题参考解答

电子科技大学二零壹壹年至二零一贰学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟) 考试日期 2012年4月22日I. To fill the answers in the “( )” (2’ X 20=40) 1. [42.25 ]10 = ( 2A.4 )16 = ( 52.2 )8 .2. The binary two ’s complement is (1011), then its corresponding 8-bit two ’s complement is ( 11111011 ), and 8-bit one ’s complement is ( 11111010 ), and 8-bit signed-magnitude is ( 10000101 ).3. The 8421-BCD code is (10011000)8421-BCD ,then its corresponding decimal number is ( 98 ).4. The binary number code is (10101011)2, then its corresponding Gray code is ( 11111110 ).5. If F = ∏ABC (1,3,5),then its dual expression is =D F ∑ABC ( 2,4,6 ), and the complement expression of the function F is F ’=∑ABC ( 1,3,5)。

6. The range of 8-bit two ’s complement is (-128 ~ 127), and the range of 8-bit unsigned binary number is (0 ~ 255).7. If there are 2012 different states, we need at least ( 11 ) bits binary code to represent them.8. For the two ’s complement addition and subtraction operation, if [ A ] two’s -complement =11011011, and [ B] two’s -complement =10011111 , calculate [-A-B ] two’s -complement , [A-B ] two’s -complement , and indicate whether or not overflow occurs.[-A-B ] two’s -complement = [ 10000110 ], overflow: [ yes ] [A-B ] two’s -complement = [ 00111100 ], overflow: [ no ]9. The maximum LOW-state output current I OLmax for an HC-series CMOS gate driving CMOS inputs is 0.02mA, the maximum HIGH-state output current I OHmax is -0.02mA, and the maximum input current I Imax for an HC-series CMOS input in any states is A μ1±, the DC fanout at HIGH-state is ( 20 ).10. The unused CMOS NAND gate inputs should be tied to logic ( 1 ).11. The following logic diagram Fig.1 implements a function of 3-variable with a 74x138. The logicfunction can be expressed as F (A,B,C) =∏A,B,C ( 2, 3,4,5,7 ).Fig.112. The CMOS circuit is shown in Fig.2. Write the function of the circuit. ( F=(AB+C+D)’ )Fig.2II. There is only one correct answer in the following questions.(3’ X 10=30)1. What is the correct 2’s -complement representation of the decimal number -325?( A ) A) 1010111011 B) 1101000101 C) 1011010011 D) 10101001102. A 20-to-1 multiplexer need ( B ) selection control inputs at least.A) 4B) 5C) 6D) 203. In the 8-radix number system, the result of operation 721/20 is: ( B )A) 36.05B) 35.04C) 35.05D) 36.044. What is the duality logic function of the logic function: F = ∑ABC (0,3,5,7)( C )A),,(1,2,4,6)A B C ∑ B),,(0,2,4,7)A B C ∑ C),,(0,2,4,7)A B C ∏D),,(1,2,4,6)A B C ∏5. The inputs waveform A,B,C and output waveform F of a combinational circuit are shown as Fig.3. The canonical product-of-sums expression of this circuit is ( D )A)(),,2,3,5,7A B C∑B)(),,0,2,4,6A B C∑C) ,,(1,2,4,7)A B C ∏ D),,(0,3,5,6)A B C ∏Fig.36. For each of the following logic expressions, ( B ) is the hazard-free circuit.A) F=A’·B + A·C + B’·C B ) F=A’·B + A·C + B·C C) F=(A+B)·(B’+C)·(C+D) D) F=(A+B’)·(B+C)·(C’+D) 7. For the logic function )''()''(),,,(C B D C AB D C B A F '++=, the corresponding minimal sum is ( A ).A) A’+B+C’D’ B ) (A’+B+C’)(A’+B+D’) C) A’+B+B’C’D’ D ) A’+B+AC’D’8. The INVERTER and AND-OR-INVERTER circuits are shown as Fig.4 (a), (b) respectively, which conclusion below is correct? ( C )A) The delay between input and output of (a) circuit is much less than (b) circuit. B) The delay between input and output of (a) circuit is much greater than (b) circuit. C) The delay between input and output of (a) circuit is about same as (b) circuit. D) The delay relationship between circuit (a) and (b) is uncertainty.Fig.4 (a)Fig.4 (b)9. The circuit shown in Fig.5 realize a logic functin F about input variable W, X, Y . Then, the Fis:( A )A) F=,,,(0,1,3,7,9,13,14)w x y z ∑B) F=,,,(0,2,5,7,9,13,14)w x y z ∑C) F=,,,(0,1,3,7,8,12,15)w x y z ∑D) F=,,,(1,2,5,7,9,12,15)w x y z ∑Fig.510. Which of the following statements are NOT correct about logic function? ( D ) A) There are multi-expressions of a logic function ’s minimal sum. B) The canonical sum of a circuit is a sum of minterms.C) Any logic function can be expressed using a sum of minterms or a product of maxterms. D) A sum of prime implicants must be the logic function ’s minimal sum. III. Combinational Circuit Analysis And Design: [30’]1.Write the truth table and the logic function performed by the CMOS circuit in Figure 6. (7’)Fig.6Solution :Z=S ’A+SB评分标准:真值表正确 4 分, 错一个扣0.5分;表达式正确 3分。

数字电路逻辑设计(第二版) 王毓银 电子科技大学

3.5.4 CMOS逻辑门电路

3.5.5 BiCMOS门电路

3.5.6 CMOS电路的正确使用方法

3.6 VHDL描述逻辑门电路

3.6.1 VHDL描述电路的基本方法

3.6.2 VHDL描述逻辑门电路

习题

第4章 组合逻辑电路

4.1 组合逻辑电路分析

6.4.1 设计给定序列信号的产生电路

6.4.2 根据序列循环长度M的要求设计发生器电路

6.5 时序逻辑电路的VHDL描述

6.5.1 移位寄存器的VHDL描述

6.5.2 计数器的VHDL描述

习题

第7章 半导体存储器

7.1 概述

7.1.1 半导体存储器的特点与应用

5.3 主从触发器

5.3.1 主从触发器基本原理

5.3.2 主从J-K触发器主触发器的一次翻转现象

5.3.3 主从J-K触发器集成单元

5.3.4 集成主从J-K触发器的脉冲工作特性

5.4 边沿触发器

5.4.1 维持一阻塞触发器

5.4.2 下降沿触发的边沿触发器

10.2.6 DAC的转换精度与转换速度

10.3 模数转换器(ADC)

10.3.1 模数转换基本原理

10.3.2 并联比较型ADC

10.3.3 逐次逼近型ADC

10.3.4 双积分型ADC

10.4 集成ADC及其应用举例

双积分型集成ADC

10.4.2 逐次逼近型集成ADC

2.1.3 真值表与逻辑函数

2.1.4 逻辑函数相等

2.1.5 三个规则

2.1.6 常用公式

2.1.7 逻辑函数的标准形式

【电子科技大学】2015下《数字逻辑设计》半期考试-试题及参考答案

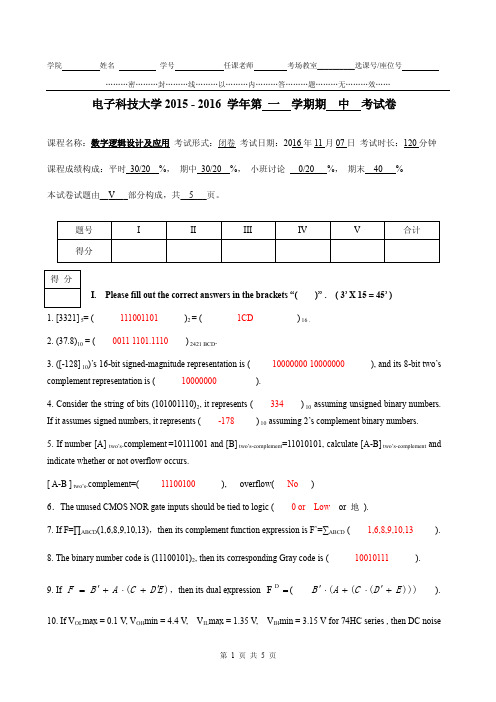

………密………封………线………以………内………答………题………无………效……电子科技大学2015 - 2016 学年第 一 学期期 中 考试卷课程名称:数字逻辑设计及应用 考试形式:闭卷 考试日期:2016年11月07日 考试时长:120分钟 课程成绩构成:平时 30/20 %, 期中 30/20 %, 小班讨论 0/20 %, 期末 40 % 本试卷试题由__V___部分构成,共__5___页。

I. Please fill out the correct answers in th e brackets “( )” . ( 3’ X 15 = 45’ )1. [3321] 5= ( 111001101 )2 = ( 1CD ) 16 .2. (37.8)10 = ( 0011 1101.1110 ) 2421 BCD .3. ([-128] 10)’s 16-bit signed-magnitude representation is ( 10000000 10000000 ), and its 8-bit two’s complement representation is ( 10000000 ).4. Consider the string of bits (101001110)2, it represents ( 334 ) 10 assuming unsigned binary numbers. If it assumes signed numbers, it represents ( -178 ) 10 assuming 2’s complement binary numbers.5. If number [A] two’s -complement =10111001 and [B] two’s -complement =11010101, calculate [A-B] two’s -complement and indicate whether or not overflow occurs.[ A-B ] two’s -complement=( 11100100 ), overflow( No )6.The unused CMOS NOR gate inputs should be tied to logic ( 0 or Low or 地 ).7. If F=∏ABCD (1,6,8,9,10,13),then its complement function expression is F’=∑ABCD ( 1,6,8,9,10,13 ). 8. The binary number code is (11100101)2, then its corresponding Gray code is ( 10010111 ).9. If )(E D C A B F '+⋅+'=,then its dual expression =DF ( )))(((E D C A B +'⋅+⋅' ).10. If V OL max = 0.1 V, V OH min = 4.4 V , V IL max = 1.35 V , V IH min = 3.15 V for 74HC series , then DC noise………密………封………线………以………内………答………题………无………效……margin is V NL = ( 1.25 )V, V NH = ( 1.25 )V.II. Choose the only one correct answer and fill the item number in the brackets. (2’ X 10=20 )1. Which of these four gates is the fastest ? ( C )A. ANDB. ORC. NANDD. NOR2. To Implement this function F=(A’B(D’+C’D)+B(A+A’CD))’(A’B(C+D)’), how many AND gates at least we should use? ( A )A. 0B. 1C. 2D. 33. If we want to use an XOR gate as an Inverter (NOT gate), then the inputs of A and B should connect as the ( A ) .A one of the A andB connect to ‘1’B one of the A and B connect to ‘0’C A and B connect togetherD can’t realize4. The output signal of ( B ) circuit is 1-out-of-M code.A Binary EncoderB Binary DecoderC Seven-Segment DecoderD Multiplexer5.A CMOS circuit is shown as Fig 1,its’ logic function F =(B). (positive logic).A A⋅B+C⋅DB (A⋅B+C⋅D)’C (A+B)⋅(C+D)D ((A+B)⋅(C+D))’Fig 1………密………封………线………以………内………答………题………无………效……6. The following logic expressions, the hazard-free one is ( D ).A F=B’C’+AC+A’B B F=A’C’+BC+AB’C F=A’C’+AC+A’BD F=B’C+AB’+A’C7. A priority encoder 74LS148’s input is:I0-L, I1-L, I2-L, I3-L, I4-L, I5-L, I6-L, I7-L,output is Y2-L,Y1-L,Y0-L.The inputs and output are all active-low. When active-low enable input S_L=0,and I2-L= I3-L=I4-L=I5-L=0, then Y2-L,Y1-L,Y0-L is ( B).A 110B 010C 001D 1018. The truth table of a circuit is shown in Table 2, the logic expression of this circuit is ( C).A. F=A+BB. F=S+A+BC.D.9. In one number system, if an arithmetic operation 302/20=12.1 is correct, its radix is ( C)A. 5B. 6C.4D. 810. If the canonical sum for an n-input logic function is also aminimal sum, how many literals are in eachproduct term of the sum? ( A )A nB 2nC n-1D cannot be determined.III. Given F(W,X,Y,Z) = (W+X+Y’)∙(W+X’+Z)∙(W’+X+Z’). Assume the input variables WXYZ will never be 0000, 0001, 1101 and 1010. Simplify the logic function F(W,X,Y,Z) into the minimal sum-of-products expression using Karnaugh map, and write out NAND-NAND logic expression of the minimal sum-of-products. (10’)………密………封………线………以………内………答………题………无………效……参考评分标准:1.填写F 的卡诺图正确得 5分2.化简的表达式正确得 3分 F (W,X,Y,Z) = X ∙Z + W ∙Z ’3.“与非-与非“表达式正确得 2分F NAND-NAND (W,X,Y,Z) = ( (X ∙Z)’ ∙ (W ∙Z ’)’ )’ IV . A combinational circuit is shown as below. Assume propagation delay for each gate is equal to t pd . (15’)(1) When A=C=D=1, B change from 0 to 1 or from 1 to 0, draw the timing diagram for Y1, Y2 and Y .(2) Analyze the conditions that the static hazard may exit, and write out the sum-of-product expression for the hazard-free.参考评分标准:(1) 定时图 正确得6分(每根线2分,上升沿1分, 下降沿1分)………密………封………线………以………内………答………题………无………效……(2) ①写出原始表达式正确得2分: Y (A,B,C,D) = A ∙B + B ’∙C ∙D②判定冒险条件正确得4分: 当A=C=D=1时,F=B+B' (或B 变化),存在静态1冒险若填卡诺图正确,但判定静态冒险条件不正确,可得 2分:③写出无冒险表达式正确得 3分:Y hazard-free (A,B,C,D) = A ∙B + B ’∙C ∙D + A ∙C ∙DV . Realize two functions F =∏A,B,C (0, 2, 4, 6) and G = F Dby using one 74x139 andsome gates. (10’)参考评分标准:写出函数G 的表达式正确得 2分:G = F D= ∏A,B,C (0, 2, 4, 6) = F ,或 ∑ABC ( 1, 3, 5, 7 ).输入连接正确得4分,输出连正确得4分。

2019秋季电子科技大学数字逻辑设计与应用作业1

作业提交 11.逻辑函数 Y 的电路图如下: 该逻辑最简的与或逻辑函数式为 。

(A)请问,(B)(C ) [参考答案:B] 分值:5 得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分2. 逻辑函数,请问其最小项之和为 。

(A) (B) (C ) [参考答案:C] 分值:5得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分3. 以下逻辑中,与相同的逻辑是 。

(A)(B) (C ) [参考答案:A] 分值:5 得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分4. 以下逻辑函数的描述中,具备唯一性的是 。

(A) 逻辑函数表达式 (B) 逻辑函数真值表 (C 逻辑函数电路图 ) [参考答案:B] 分值:5得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分5. 已知一个逻辑的最小项之和为 F(A, B, C)=∑m(0,4,7) ,以下哪个等式成立 。

(A)(B)(C) [参考答案:B] 分值:5 得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分6. 以下有关描述正确的是 。

(A) 如果 AB=AC,则 B=C (B) 如果 A+B=A+C,则 B=C (C) 以上都不对 [参考答案:C] 分值:5得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分7. 已知逻辑,求出 F 的对偶逻辑。

(A) A+BC+D (B) ABCD (C(A+B)(C+D) ) [参考答案:C] 分值:5得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分8. 一个三变量的组合逻辑系统,最小项的个数有 个。

(A 3) (B6 ) (C8 ) [参考答案:C] 分值:5得分: 分系统自动批改于 2019 年 11 月 17 日 20 点 06 分9. 下面有关逻辑函数的描述中,正确的是 。

数字逻辑电路课程设计_4B5B编码_VHDL实现(含完整代码)

电子科技大学UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA数字逻辑设计实验报告实验题目:4B5B编码器学生:指导老师:一、实验容4B/5B编码是百兆以太网中线路层编码类型之一,该试验需要实现用5bit 的二进制数来表示4bit二进制数。

二、实验要求1、功能性要求:能够实现4B5B编码,即输入4bit数据时能输出正确的5bit编码结果。

2、算法要求:利用卡诺图对编码真值表进行化简,得出其逻辑表达式,并基于此进行硬件设计。

3、设计性要求:使用代码及原理图两种设计方式来进行设计。

采用基本门结构化描述。

能够编写Test Bench文件,并利用Modelsim进行仿真。

三、实验原理及设计思路1、实验原理:在IEEE 802.9a等时以太网标准中的4B:5B编码方案,因其效率高和容易实现而被采用。

这种编码的特点是将欲发送的数据流每4bit作为一个组,然后按照4B/5B编码规则将其转换成相应5bit码。

5bit码共有32种组合,但只采用其中的16种对应4bit码的16种,其他的16种或者未用或者用作控制码,以表示帧的开始和结束、光纤线路的状态(静止、空闲、暂停)等。

4B5B编码表如下:2、设计思路:(1)整体思路:对已知的编码真值表,首先利用卡诺图对其进行化简,得出其逻辑表达式,再用基本门结构将其实现。

(2)卡诺图与表达式:设输入的4位编码为:ABCD,输出的5位编码为:VWXYZ,则分别画出其卡诺图并得出表达式如下:1.V:V=A+B’D’+B’C 2.W:W=B+A’C’.3.X:X=C+A’B’D’4.Y:Y=A’B+AB’+C’D’+AC’.5.Z:Z=D(3)基本门结构设计:由上述表达式可见,用到的基本门有:非门、2输入与门、3输入与门、2输入或门、3输入或门、4输入或门,用not、and、or将其一一表示出即可。

四、程序设计.1、顶层模块:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity main isPort ( a : in STD_LOGIC;b : in STD_LOGIC;c : in STD_LOGIC;d : in STD_LOGIC;v : out STD_LOGIC;w : out STD_LOGIC;x : out STD_LOGIC;y : out STD_LOGIC;z : out STD_LOGIC);end main;architecture Behavioral of main is COMPONENT notiPORT(i : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT and2iPORT(i1 : IN std_logic;i2 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT and3iPORT(i1 : IN std_logic;i2 : IN std_logic;i3 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT or2iPORT(.i1 : IN std_logic;i2 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT or3iPORT(i1 : IN std_logic;i2 : IN std_logic;i3 : IN std_logic;o : OUT std_logic);END COMPONENT;COMPONENT or4iPORT(i1 : IN std_logic;i2 : IN std_logic;i3 : IN std_logic;i4 : IN std_logic;o : OUT std_logic);END COMPONENT;signal nota,notb,notc,notd,v1,v2,v3,w1,w2,x1,x2,y1,y2,y3,y4,vv,ww,xx,yy,zz : std_logic;begin--not--Inst_noti_nota: noti PORT MAP(i => a,o => nota);Inst_noti_notb: noti PORT MAP(i => b,o => notb);Inst_noti_notc: noti PORT MAP(i => c,o => notc);.Inst_noti_notd: noti PORT MAP(i => d,o => notd);--v--v1<=a;Inst_and2i_v2: and2i PORT MAP(i1 => notb,i2 => notd,o => v2);Inst_and2i_v3: and2i PORT MAP(i1 => notb,i2 => c,o => v3);Inst_or3i_vv: or3i PORT MAP(i1 => v1,i2 => v2,i3 => v3,o => vv);--w--w1<=b;Inst_and2i_w2: and2i PORT MAP(i1 => nota,i2 => notc,o => w2);Inst_or2i_ww: or2i PORT MAP(i1 => w1,i2 => w2,o => ww);--x--. x1<=c;Inst_and3i_x2: and3i PORT MAP(i1 => nota,i2 => notb,i3 => notd,o => x2);Inst_or2i_xx: or2i PORT MAP(i1 => x1,i2 => x2,o => xx);--y--Inst_and2i_y1: and2i PORT MAP(i1 => nota,i2 => b,o => y1);Inst_and2i_y2: and2i PORT MAP(i1 => a,i2 => notb,o => y2);Inst_and2i_y3: and2i PORT MAP(i1 => notc,i2 => notd,o => y3);Inst_and2i_y4: and2i PORT MAP(i1 => a,i2 => notc,o => y4);Inst_or4i_yy: or4i PORT MAP(i1 => y1,i2 => y2,i3 => y3,.i4 => y4,o => yy);--z--zz<=d;--not--Inst_noti_v: noti PORT MAP(i => vv,o => v);Inst_noti_w: noti PORT MAP(i => ww,o => w);Inst_noti_x: noti PORT MAP(i => xx,o => x);Inst_noti_y: noti PORT MAP(i => yy,o => y);Inst_noti_z: noti PORT MAP(i => zz,o => z);end Behavioral;2、非门:entity noti isPort ( i : in STD_LOGIC;o : out STD_LOGIC);end noti;architecture Behavioral of noti is begino <= not i;end Behavioral;3、2输入与门:entity and2i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;o : out STD_LOGIC);end and2i;architecture Behavioral of and2i is begino <= i1 and i2;end Behavioral;4、3输入与门:entity and3i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;i3 : in STD_LOGIC;o : out STD_LOGIC);end and3i;architecture Behavioral of and3i isbegino<=i1 and i2 and i3;end Behavioral;5、2输入或门:entity or2i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;o : out STD_LOGIC);end or2i;architecture Behavioral of or2i is begino<=i1 or i2;end Behavioral;6、3输入或门:entity or3i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;i3 : in STD_LOGIC;o : out STD_LOGIC);end or3i;architecture Behavioral of or3i isbegino <= i1 or i2 or i3;end Behavioral;7、4输入或门:entity or4i isPort ( i1 : in STD_LOGIC;i2 : in STD_LOGIC;i3 : in STD_LOGIC;i4 : in STD_LOGIC;o : out STD_LOGIC);end or4i;architecture Behavioral of or4i isbegino<=i1 or i2 or i3 or i4;end Behavioral;五、仿真与硬件调试1、仿真:(1)顶层仿真:1.仿真文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY test1 ISEND test1;ARCHITECTURE behavior OF test1 IS-- Component Declaration for the Unit Under Test (UUT) COMPONENT mainPORT(a : IN std_logic;b : IN std_logic;c : IN std_logic;d : IN std_logic;v : OUT std_logic;w : OUT std_logic;x : OUT std_logic;y : OUT std_logic;z : OUT std_logic);END COMPONENT;--Inputssignal a : std_logic := '0';signal b : std_logic := '0';signal c : std_logic := '0';signal d : std_logic := '0';--Outputssignal v : std_logic;signal w : std_logic;signal x : std_logic;signal y : std_logic;signal z : std_logic;-- No clocks detected in port list. Replace <clock> below with -- appropriate port nameBEGIN-- Instantiate the Unit Under Test (UUT)uut: main PORT MAP (a => a,b => b,c => c,d => d,v => v,w => w,x => x,y => y,z => z);-- Stimulus processstim_proc: processbegina<='0';b<='0';c<='0';d<='0';wait for 100 ns;a<='0';b<='0';c<='0';d<='1';wait for 100 ns;a<='0';b<='0';c<='1';d<='0'; wait for 100 ns;a<='0';b<='0';c<='1';d<='1'; wait for 100 ns;a<='0';b<='1';c<='0';d<='0'; wait for 100 ns;a<='0';b<='1';c<='0';d<='1'; wait for 100 ns;a<='0';b<='1';c<='1';d<='0'; wait for 100 ns;a<='0';b<='1';c<='1';d<='1'; wait for 100 ns;a<='1';b<='0';c<='0';d<='0'; wait for 100 ns;a<='1';b<='0';c<='0';d<='1'; wait for 100 ns;a<='1';b<='0';c<='1';d<='0'; wait for 100 ns;a<='1';b<='0';c<='1';d<='1'; wait for 100 ns;a<='1';b<='1';c<='0';d<='0'; wait for 100 ns;a<='1';b<='1';c<='0';d<='1'; wait for 100 ns;a<='1';b<='1';c<='1';d<='0'; wait for 100 ns;a<='1';b<='1';c<='1';d<='1'; -- insert stimulus herewait;end process;END;2.仿真结果:(2)非门仿真:(3)2输入与门仿真:(4)2输入或门仿真:(5)3输入或门仿真:(6)4输入或门仿真:2、硬件调试:(1)管脚配置:NET "a" LOC = P6; #sb1NET "b" LOC = P141;NET "c" LOC = P136;NET "d" LOC = P129;NET "v" LOC = P122;NET "w" LOC = P123;NET "x" LOC = P124;NET "y" LOC = P125;NET "z" LOC = P126;(2)调试结果:如上图所示,4B码为“0000”,其对应的5B码为“11110”。

数字逻辑设计及应用课程教学大纲

《数字逻辑设计及应用》课程教学大纲课程编号:53000540适用专业:电子信息、电气工程、自动控制及其他应用数字技术的相关专业学时数:64 学分数:4 开课学期:第4学期先修课程:《大学物理》、《软件技术基础》、《电路分析基础》、《模拟电路基础》执笔者:姜书艳编写日期:2011.9 审核人(教学副院长):一、课程性质和目标授课对象:全日制大学本科二年级课程类别:学科基础课教学目标(本课程对实现培养目标的作用;学生通过学习该课程后,在思想、知识、能力和素质等方面应达到的目标):“数字逻辑设计及应用”课程是信息技术类专业所共有的一门重要学科基础课程,同时也是一门重要工程技术课程,是研究数字系统硬件设计的入门课程。

在本课程中,将介绍数字逻辑电路的分析设计方法和基本的系统设计思想;培养同学综合运用知识分析解决问题的能力和在工程性设计方面的基本素养。

通过实验和课外上机实验的方式,使同学深入了解和掌握数字逻辑电路的分析设计方法和电路的运用过程。

通过本课程的学习,使学生掌握数字逻辑电路的基本理论、基本分析和设计方法,为学习后续课程准备必要的数字电路知识。

本课程在培养学生严肃认真的科学作风和逻辑思维能力、分析设计能力、归纳总结能力等方面起重要作用。

二、课程内容安排和要求(一)教学内容、要求及教学方法1. 课堂理论教学(64学时)第一章引论(2学时)了解:数字电路的发展及其在信息技术领域中的地位;数字信号与模拟信号之间的关系及数字信号的特点;数字系统输入输出特性及其逻辑特点,数字逻辑电路的主要内容。

第二章信息的数字表达(4学时)掌握:十进制、二进制、八进制和十六进制数的表示方法以及它们之间的相互转换、二进制数的运算;符号数的表达:符号-数值码(Signed-Magnitude System、原码),二进制补码(two's complement,补码)、二进制反码(ones' complement, 反码)表示以及它们之间的相互转换;符号数的运算;溢出的概念。

电子科技大学自动化学院研究生复试大纲

自动化工程学院复试考试大纲更新时间:2012/9/27 点击数:2585微机原理及数字电路复试考试大纲(闭卷)(200分)(推免生复试总分100分,微机原理和数字电路各占50%)对象:报考自动化工程学院080400仪器科学与技术、081100控制科学与工程、085203仪器仪表工程、085210控制工程的学生《微机原理及应用》(100分)一.参考书目:《微处理器系统结构及嵌入式系统设计(第二版)》李广军电子工业出版社《微机系统原理与接口技术》李广军电子科技大学出版社二.本大纲适合专业本大纲适用于自动化、仪器与测量技术等各类工科电子类非计算机专业。

三.内容要求1.概述要求内容:计算机发展历程,集成电路与SoC设计,先进的处理器技术,信息在计算机中的表示方法。

指令、程序的概念以及程序的执行过程。

嵌入式系统的概念、特点、组成、发展现状与趋势。

2.计算机系统的结构组成与工作原理要求内容:计算机系统的基本结构与组成,计算机系统的工作原理,微处理器体系结构的改进,计算机主要性能评测指标。

3.微处理器体系结构及关键技术要求内容:微处理器体系结构,处理器设计技术,指令系统设计,流水线技术,典型微处理体系结构。

4.总线技术与总线标准要求内容:总线技术概述、总线仲裁、总线操作与时序,总线标准(片内AMBA总线、PCI系统总线、异步串行通信总线。

5.存储器系统要求内容:存储器件的分类,半导体存储器的基本结构与性能指标;存储系统的层次结构,主存储器设计技术(存储器地址分配原则;译码电路设计方法;存储器接口设计设计;存储器系统设计方法)。

6.输入输出接口要求内容:输入/输出接口基础(接口和端口的概念,输入/输出接口功能与结构,端口的编址方法,端口地址的分配原则);接口地址译码;接口信息传输方式;并行接口,串行接口,定时/计数接口、AD/DA 接口的结构特点及设计要点7.ARM微处理器编程模型要求内容:ARM 内核体系结构,ARM 编程模型(处理器工作状态、处理器运行模式、寄存器组织、数据类型和储存格式、异常)。

电子科技大学2013考研专业课入学复试资料大全

∙出版社:机械工业出版社;∙作者:林生、葛红等译∙原价:75.00∙本店促销价:RBM30元/本(数量有限,售完为止)购买全套资料如果还需要教材,请另外留言注明加购,全套资料不含教材!2.《数字逻辑设计及应用》∙出版社:清华大学出版社∙作者:姜书艳林水生等∙原价:29.00本店促销价:RBM12元/本(二手,数量有限,售完为止)购买全套资料如果还需要教材,请另外留言注明加购,全套资料不含教材![全套资料构成]序列一:数字逻辑设计(科大内部资料)全程导学资料简介:本资料作为指定教材同步辅导,由电子科大数字逻辑课程组编写。

内容包括各章知识要点、典型例题解析、同步练习题及解答,建议作为第一阶段基础复习使用。

序列二:数字逻辑设计及应用本科教学课件内容简介:本科课件是科大教研中心授课的重点教案,里面包含了本科教学的内容及要求;本科教学的重点难点以及解决办法;本科教学的重点作业习题。

第一轮复习参考本科课堂讲义,就相当于与本校学生一样听了该校老师讲授的课程,众所周知,考研专业课之所以对本校学生有很大优势,其中最重要方面考研专业课的出题的重点难点和本科要求差不多。

所以本科讲义对外校考研把握科大最新出题动向和最新大纲要求具有重要参考价值。

所以第一轮复习我们建议看教材的同时结合本科讲义,当然也要认真做本科教学老师布置的作业。

这样专业课基础知识更牢,对后继阶段复习帮助很大。

建议第一阶段基础复习使用。

序列三:数字设计原理与实践第四版(习题答案+复习总结)内容简介:关于本科教学老师布置的作业一定要认真完成,这些作业题体现了这门课程的重点难点疑点,这些题目都很典型,和代表性,对巩固教材知识和提高自己解题能力都很有帮助,这些题目有时也会出现在真题的原题中。

建议第一阶段基础复习使用。

序列四:数字逻辑电路本科期末考题合集(6套试卷附答案)资料简介:期末试题难度要低于考研试题,多少重点难点差不多,有时考研真题也会出自于往届期末题库里面,所以期末题库含金量还是很高,可以在专业课第一轮基础复习后检验自己复习效果。

电子科技大学《数字逻辑设计及应用》20春期末考试

(单选题)1: EPROM是指()

A: 随机读写存储器

B: 只读存储器

C: 可擦可编程只读存储器

D: 电可擦可编程只读存储器

正确答案: C

(单选题)2: 下面各个组成部分,对于一个时序逻辑来说,不可缺少的是()A: mealy型输出

B: 输入

C: moore型输出

D: 存储单元

正确答案: D

(单选题)3: n级触发器构成的环形计数器,其有效循环的状态数为()

A: n个

B: 2n个

C: 2n-1个

D: 2n个

正确答案: A

(单选题)4: 脉冲异步时序逻辑电路的输入信号可以是()

A: 模拟信号

B: 电平信号

C: 脉冲信号

D: 以上都不正确

正确答案: C

(单选题)5: 组合逻辑电路输出与输入的关系可用()描述

A: 真值表

B: 状态表

C: 状态图

D: 以上均不正确

正确答案: A

(单选题)6: 一块十六选一的数据选择器,其数据输入端有(??? ??)个

A: 16

B: 8

C: 4

D: 2

正确答案: A

(单选题)7: 数字系统中,采用()可以将减法运算转化为加法运算

A: 原码。

成都电子科技大学自动化工程学院2014-2015学年度专业课考试安排

课程代码课程名称课程类别教师上课人数实际人数考座数校区开课院系H0710530虚拟仪器与网专业选修课詹惠琴804050清水河校区自动化工程学H0710530虚拟仪器与网专业选修课詹惠琴804055清水河校区自动化工程学H0710530虚拟仪器与网专业选修课古军794045清水河校区自动化工程学H0710530虚拟仪器与网专业选修课古军793945清水河校区自动化工程学H0710530虚拟仪器与网专业选修课罗光坤723645清水河校区自动化工程学H0710530虚拟仪器与网专业选修课罗光坤723645清水河校区自动化工程学0711220精密仪器专业核心课程玉华1314445清水河校区自动化工程学0711220精密仪器专业核心课程玉华1314445清水河校区自动化工程学0711220精密仪器专业核心课程玉华1314345清水河校区自动化工程学0711220精密仪器专业核心课白利兵1005155清水河校区自动化工程学0711220精密仪器专业核心课白利兵1005155清水河校区自动化工程学白利兵25155清水河校区自动化工程学0711230精密仪器电路学科基础课(必修)0718330计算机控制系专业选修课康波814150清水河校区自动化工程学0718330计算机控制系专业选修课康波814050清水河校区自动化工程学0718330计算机控制系专业选修课李云霞1304445清水河校区自动化工程学0718330计算机控制系专业选修课李云霞1304345清水河校区自动化工程学0718330计算机控制系专业选修课李云霞1304345清水河校区自动化工程学I0740120C语言素质教育选修袁渊1594050清水河校区自动化工程学I0740120C语言素质教育选修袁渊1594055清水河校区自动化工程学I0740120C语言素质教育选修袁渊1594055清水河校区自动化工程学I0740120C语言素质教育选修袁渊1593955清水河校区自动化工程学I0740120C语言素质教育选修白新跃814145清水河校区自动化工程学I0740120C语言素质教育选修白新跃814045清水河校区自动化工程学I0740120C语言素质教育选修彭晓明1584045清水河校区自动化工程学I0740120C语言素质教育选修彭晓明1584045清水河校区自动化工程学I0740120C语言素质教育选修彭晓明1583945清水河校区自动化工程学I0740120C语言素质教育选修彭晓明1583945清水河校区自动化工程学H0740220C语言专业选修课程何建1344550清水河校区自动化工程学H0740220C语言专业选修课程何建1344550清水河校区自动化工程学H0740220C语言专业选修课程何建1344455清水河校区自动化工程学H0740220C语言专业选修课程杨成林1254255清水河校区自动化工程学H0740220C语言专业选修课程杨成林1254255清水河校区自动化工程学H0740220C语言专业选修课程杨成林1254155清水河校区自动化工程学H0740220C语言专业选修课程于力1383745清水河校区自动化工程学H0740220C语言专业选修课程于力1383745清水河校区自动化工程学H0740220C语言专业选修课程于力1383745清水河校区自动化工程学H0740220C语言专业选修课程于力1383645清水河校区自动化工程学于力93645清水河校区自动化工程学0708330C语言学科基础课(必修)E0700140数字逻辑设计专业选修课袁渊1123845清水河校区自动化工程学E0700140数字逻辑设计专业选修课袁渊1123745清水河校区自动化工程学E0700140数字逻辑设计专业选修课袁渊1123745清水河校区自动化工程学E0700140数字逻辑设计专业选修课王振松733745清水河校区自动化工程学E0700140数字逻辑设计专业选修课王振松733645清水河校区自动化工程学E0700140数字逻辑设计专业选修课张刚1133845清水河校区自动化工程学E0700140数字逻辑设计专业选修课张刚1133845清水河校区自动化工程学E0700140数字逻辑设计专业选修课张刚1133745清水河校区自动化工程学E0700140数字逻辑设计专业选修课姜书艳1123850清水河校区自动化工程学E0700140数字逻辑设计专业选修课姜书艳1123755清水河校区自动化工程学E0700140数字逻辑设计专业选修课姜书艳1123755清水河校区自动化工程学E0700140数字逻辑设计专业选修课王宏292945清水河校区自动化工程学E0700140数字逻辑设计学科基础课王宏904560沙河校区自动化工程学E0700140数字逻辑设计学科基础课王宏904560沙河校区自动化工程学E0700140数字逻辑设计学科基础课袁渊1184045清水河校区自动化工程学E0700140数字逻辑设计学科基础课袁渊1183945清水河校区自动化工程学E0700140数字逻辑设计学科基础课袁渊1183945清水河校区自动化工程学0725140数字逻辑设计学科基础课723660沙河校区自动化工程学0725140数字逻辑设计学科基础课723660沙河校区自动化工程学0725140数字逻辑设计学科基础课姜书艳1224150清水河校区自动化工程学0725140数字逻辑设计学科基础课姜书艳1224150清水河校区自动化工程学0725140数字逻辑设计学科基础课姜书艳1224050清水河校区自动化工程学E0700140数字逻辑设计学科基础课王振松131755清水河校区自动化工程学E0700140数字逻辑设计学科基础课张刚31755清水河校区自动化工程学0725140数字逻辑设计学科基础课张刚11755清水河校区自动化工程学H0720125电力电子技术专业核心课李洪814145清水河校区自动化工程学H0720125电力电子技术专业核心课李洪814045清水河校区自动化工程学H0720125电力电子技术专业核心课李凯1284345清水河校区自动化工程学H0720125电力电子技术专业核心课李凯1284345清水河校区自动化工程学H0720125电力电子技术专业核心课李凯1284245清水河校区自动化工程学H0710420数据采集与处专业选修课曾浩582945清水河校区自动化工程学H0710420数据采集与处专业选修课曾浩582945清水河校区自动化工程学H0710420数据采集与处专业选修课蒋俊512645清水河校区自动化工程学H0710420数据采集与处专业选修课蒋俊512545清水河校区自动化工程学H0710420数据采集与处专业选修课潘卉青593045清水河校区自动化工程学H0710420数据采集与处专业选修课潘卉青592945清水河校区自动化工程学H0710420数据采集与处专业选修课邓罡603045清水河校区自动化工程学H0710420数据采集与处专业选修课邓罡603045清水河校区自动化工程学0707530通信技术与电专业选修课师奕兵1594145清水河校区自动化工程学0707530通信技术与电专业选修课师奕兵1594145清水河校区自动化工程学0707530通信技术与电专业选修课师奕兵1594145清水河校区自动化工程学0707530通信技术与电专业选修课师奕兵1594045清水河校区自动化工程学0707530通信技术与电学科基础课(必修)师奕兵44045清水河校区自动化工程学0707530通信技术与电专业选修课张治国1634145清水河校区自动化工程学0707530通信技术与电专业选修课张治国1634145清水河校区自动化工程学0707530通信技术与电专业选修课张治国1634145清水河校区自动化工程学0707530通信技术与电专业选修课张治国1634055清水河校区自动化工程学H0710920电路与电子系专业选修课马敏804045清水河校区自动化工程学H0710920电路与电子系专业选修课马敏804045清水河校区自动化工程学H0710920电路与电子系专业选修课杨忠孝753845清水河校区自动化工程学H0710920电路与电子系专业选修课杨忠孝753745清水河校区自动化工程学H0710920电路与电子系专业选修课龙兵703650清水河校区自动化工程学H0710920电路与电子系专业选修课龙兵703550清水河校区自动化工程学龙兵13550清水河校区自动化工程学0703120电路与电子系学科基础课(必修)0726320人工智能导论专业选修课郑亚莉252555清水河校区自动化工程学0726320人工智能导论专业选修课刘珊1574045清水河校区自动化工程学0726320人工智能导论专业选修课刘珊1573945清水河校区自动化工程学0726320人工智能导论专业选修课刘珊1573945清水河校区自动化工程学0726320人工智能导论专业选修课刘珊1573945清水河校区自动化工程学0726320人工智能导论专业选修课闫斌1304445清水河校区自动化工程学0726320人工智能导论专业选修课闫斌1304345清水河校区自动化工程学0726320人工智能导论专业选修课闫斌1304355清水河校区自动化工程学专业选修课王振松1604045清水河校区自动化工程学H0710630数字系统EDA技术H0710630数字系统EDA技术专业选修课王振松1604045清水河校区自动化工程学专业选修课王振松1604045清水河校区自动化工程学H0710630数字系统EDA技术专业选修课王振松1604045清水河校区自动化工程学H0710630数字系统EDA技术专业选修课黄志奇1234245清水河校区自动化工程学H0710630数字系统EDA技术专业选修课黄志奇1234150清水河校区自动化工程学H0710630数字系统EDA技术专业选修课黄志奇1234150清水河校区自动化工程学H0710630数字系统EDA技术H0710630数字系统EDA技术专业选修课孟劲松1553950清水河校区自动化工程学专业选修课孟劲松1553945清水河校区自动化工程学H0710630数字系统EDA技术H0710630数字系统EDA技术专业选修课孟劲松1553945清水河校区自动化工程学专业选修课孟劲松1553845清水河校区自动化工程学H0710630数字系统EDA技术学科基础课(必修)黄志奇14150清水河校区自动化工程学0703430数字系统EDA技术0708320现代控制理论专业核心课刘晓云723650清水河校区自动化工程学0708320现代控制理论专业核心课刘晓云723650清水河校区自动化工程学0708320现代控制理论专业核心课李瑞703545清水河校区自动化工程学0708320现代控制理论专业核心课李瑞703545清水河校区自动化工程学0708320现代控制理论专业核心课李云霞713645清水河校区自动化工程学0708320现代控制理论专业核心课李云霞713545清水河校区自动化工程学考试时间考试地点监考学院监考1监考2监考3监考4第15周星期二(20141209) 14:30-16:30B401第15周星期二(20141209) 14:30-16:30B403第15周星期二(20141209) 14:30-16:30B405第15周星期二(20141209) 14:30-16:30B404第15周星期二(20141209) 14:30-16:30B406第15周星期二(20141209) 14:30-16:30B407第18周星期天(20150104) 14:30-16:30A207第18周星期天(20150104) 14:30-16:30A206第18周星期天(20150104) 14:30-16:30A205第18周星期天(20150104) 14:30-16:30A209第18周星期天(20150104) 14:30-16:30A208第18周星期天(20150104) 14:30-16:30A208第19周星期二(20150106) 19:00-21:00A102第19周星期二(20150106) 19:00-21:00A101第19周星期二(20150106) 19:00-21:00A105第19周星期二(20150106) 19:00-21:00A104第19周星期二(20150106) 19:00-21:00A103第17周星期五(20141226) 19:00-21:00A301第17周星期五(20141226) 19:00-21:00A314第17周星期五(20141226) 19:00-21:00A309第17周星期五(20141226) 19:00-21:00A308第17周星期五(20141226) 19:00-21:00A305第17周星期五(20141226) 19:00-21:00A304第17周星期五(20141226) 19:00-21:00A311第17周星期五(20141226) 19:00-21:00A310第17周星期五(20141226) 19:00-21:00A307第17周星期五(20141226) 19:00-21:00A306第18周星期一(20141229) 19:00-21:00A202第18周星期一(20141229) 19:00-21:00A201第18周星期一(20141229) 19:00-21:00A203第18周星期一(20141229) 19:00-21:00A213第18周星期一(20141229) 19:00-21:00A209第18周星期一(20141229) 19:00-21:00A208第18周星期一(20141229) 19:00-21:00A207第18周星期一(20141229) 19:00-21:00A210第18周星期一(20141229) 19:00-21:00A206第18周星期一(20141229) 19:00-21:00A212第18周星期一(20141229) 19:00-21:00A212第19周星期四(20150108) 19:00-21:00A105第19周星期四(20150108) 19:00-21:00A104第19周星期四(20150108) 19:00-21:00A103第19周星期四(20150108) 19:00-21:00A108第19周星期四(20150108) 19:00-21:00A106第19周星期四(20150108) 19:00-21:00A111第19周星期四(20150108) 19:00-21:00A110第19周星期四(20150108) 19:00-21:00A109第19周星期四(20150108) 19:00-21:00A202第19周星期四(20150108) 19:00-21:00A208第19周星期四(20150108) 19:00-21:00A203第19周星期四(20150108) 19:00-21:00A204第19周星期四(20150108) 19:00-21:00第二教学樓105第19周星期四(20150108) 19:00-21:00第二教学樓104第19周星期四(20150108) 19:00-21:00A207第19周星期四(20150108) 19:00-21:00A206第19周星期四(20150108) 19:00-21:00A205第19周星期四(20150108) 19:00-21:00第二教学樓107第19周星期四(20150108) 19:00-21:00第二教学樓106第19周星期四(20150108) 19:00-21:00A201第19周星期四(20150108) 19:00-21:00A102第19周星期四(20150108) 19:00-21:00A101第19周星期四(20150108) 19:00-21:00A209第19周星期四(20150108) 19:00-21:00A209第19周星期四(20150108) 19:00-21:00A209第17周星期五(20141226) 09:30-11:30C413第17周星期五(20141226) 09:30-11:30C415第17周星期五(20141226) 09:30-11:30C437第17周星期五(20141226) 09:30-11:30C433第17周星期五(20141226) 09:30-11:30C435第17周星期五(20141226) 14:30-16:30A305第17周星期五(20141226) 14:30-16:30A304第17周星期五(20141226) 14:30-16:30A307第17周星期五(20141226) 14:30-16:30A306第17周星期五(20141226) 14:30-16:30A311第17周星期五(20141226) 14:30-16:30A310第17周星期五(20141226) 14:30-16:30A313第17周星期五(20141226) 14:30-16:30A312第19周星期五(20150109) 19:00-21:00A106第19周星期五(20150109) 19:00-21:00A103第19周星期五(20150109) 19:00-21:00A104第19周星期五(20150109) 19:00-21:00A105第19周星期五(20150109) 19:00-21:00A105第18周星期一(20141229) 14:30-16:30A210第18周星期一(20141229) 14:30-16:30A207第18周星期一(20141229) 14:30-16:30A206第18周星期一(20141229) 14:30-16:30A208第18周星期三(20141231) 09:30-11:30A104第18周星期三(20141231) 09:30-11:30A103第18周星期三(20141231) 09:30-11:30A106第18周星期三(20141231) 09:30-11:30A105第18周星期三(20141231) 09:30-11:30A101第18周星期三(20141231) 09:30-11:30A102第18周星期三(20141231) 09:30-11:30A102第18周星期三(20141231) 14:30-16:30A203第18周星期三(20141231) 14:30-16:30A207第18周星期三(20141231) 14:30-16:30A206第18周星期三(20141231) 14:30-16:30A205第18周星期三(20141231) 14:30-16:30A204第18周星期三(20141231) 14:30-16:30A210第18周星期三(20141231) 14:30-16:30A211第18周星期三(20141231) 14:30-16:30A208第18周星期三(20141231) 19:00-21:00A108第18周星期三(20141231) 19:00-21:00A106第18周星期三(20141231) 19:00-21:00A105第18周星期三(20141231) 19:00-21:00A104第18周星期三(20141231) 19:00-21:00A103第18周星期三(20141231) 19:00-21:00A101第18周星期三(20141231) 19:00-21:00A102第18周星期三(20141231) 19:00-21:00A202第18周星期三(20141231) 19:00-21:00A110第18周星期三(20141231) 19:00-21:00A111第18周星期三(20141231) 19:00-21:00A109第18周星期三(20141231) 19:00-21:00A102第18周星期天(20150104) 09:30-11:30A102第18周星期天(20150104) 09:30-11:30A101第18周星期天(20150104) 09:30-11:30A104第18周星期天(20150104) 09:30-11:30A103第18周星期天(20150104) 09:30-11:30A106第18周星期天(20150104) 09:30-11:30A105。

数字逻辑电路课程设计bit模加法器VHDL实现含完整样本

电子科技大学UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA数字逻辑设计实验报告实验题目: 4bit模9加法器学生姓名:指引教师:一、实验内容设计一种4bit模9加法器。

输入为两个4bit二进制数, 输出为两数相加后模9成果。

其数学表达式为: y=(x1+x2)mod 9。

二、实验规定1.功能性规定:可以实现4bit无符号数模9加法运算, 即输入两个4比特数据时可以对的输出其相加并模9运算成果。

2.算法规定:模加法器有各种算法, 可采用任意算法进行设计。

3.设计性规定:采用全加器、半加器和基本门构造化描述。

可以编写Test Bench文献, 并运用Modelsim进行仿真。

在Modelsim仿真对的基本上, 可以生成bit文献并上板验证其对的性。

4.基本上板规定:在上板实验时, 输入两个4bit数采用拨码开关输入, 输出采用LED灯进行显示。

三、设计思路1.整体思路:为了实现4bit无符号数模9加法运算, 可以先将两个4bit加数a和b先分别模9, 相加之后再模9得到最后成果。

2.模9器:先找出读入5bit数与模9后4bit数之间关系, 画出卡诺图, 再依照卡诺图得出其相应逻辑表达式即可。

设读入5bit数为carry、a、b、c、d, 模9后得到4bit 数为w、x、y、z。

则化简后得到逻辑表达式分别为:w = carry’ab’c’d’,x= carry’bc + carry’a’b + carry’bd + carrya’b’c’d’,y = carry’a’c + carry’cd + carry’abc’d’+ carrya’b’c’d’,z= carry’a’d + carry’acd’ + carry’abd’ + carry a’b’c’d’。

3.全加器:全加器可以实现两个1bit数a、b和进位输入cin相加, 其真值表如下所示:这里全加器由半加器和或门构成, 其原理图如下:半加器:半加器是全加器基本构成单元, 可以实现两个1bit数a和b相加, 并将进位输出, 其真值表如下:半加器由一种异或门和一种与门构成, 其原理图如下所示:5.数码管显示:单个数码管一共有7个端(不含小数点), 用来表达构成一种数字7个某些, 故只要找到这7个段和模9后4bit数间相应关系, 将其画出卡诺图并化简成逻辑表达式即可。

数字逻辑实验报告

F 表示进位

A0

B0

A1

B1

C1

C2

F

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

1

0

1

0

0

0

0

1

1

1

1

0

0

1

0

0

0

1

0

0

1

0

1

1

0

0

0

1

1

0

1

1

0

0

1

1

1

0

0

1

1

0

0

0

1

0

0

1

0

0

1

1

1

0

1

0

1

0

0

0

1

1

0

1

1

0

1

1

1

1

0

0

0

0

1

1

1

0

1

0

0

1

1

1

1

0

0

1

1

1

1

1

1

1

0

1

实现电路:(两个全加器)

选做第二题:

五、实验记录

实验(1)

第一题:

1. 步骤:接好电路,接通电源,进行逻辑特性验证实验 1)7400 引脚的接法: 1 接 k11,L1 2 接 k10,L2 ,3 接 L3

2、真值表:

A

B

F

0

0

1

0

电子科技大学中山学院全院各专业介绍

电子科技大学中山学院各个专业介绍计算机工程系--专业介绍计算机科学与技术(本科,学制四年,工学学士)专业特色:本专业侧重于嵌入式系统及其应用,培养系统掌握计算机工程技术领域的基本理论、基本知识和基本技能,掌握计算机软硬件开发的主流技术、平台和工具,接受嵌入式系统应用开发严格训练的高素质应用型人才。

本专业具有完善的实验实习条件,并依托建设在我院的中山市嵌入式系统公共实验室,为学生提供参与实际产品和项目应用开发和实践机会,让学生熟悉嵌入式产品的实际开发过程,掌握嵌入式产品开发的基本方法和技能。

核心课程:电路与模拟电子技术、数字逻辑设计及应用、C++面向对象程序设计、数据结构、计算机组成原理、计算机网络、操作系统、嵌入式系统概论、嵌入式操作系统及其程序设计、嵌入式软件开发、嵌入式软件测试方法、单片机及其应用开发、DSP软件开发技术、数据通信与工业控制、可编程器件、J2ME应用开发、Windows CE与嵌入式软件开发、移动设备应用软件开发、手机软件开发、嵌入式系统应用开发、DSP及其应用开发等。

就业方向:该专业毕业生具有广阔的就业前景,除了从事计算机软硬件系统的开发、应用与管理工作外,还能够从事消费类电子、信息家电、网络通信、工业控制、汽车电子等领域的嵌入式系统的设计、开发、测试及应用推广工作,能够从事面向手机、PDA、仪器仪表、移动电视、MP3/MP4等便携设备的嵌入式系统软件的设计、开发、测试及管理工作。

软件工程(软件开发技术)(本科,学制四年,工学学士)专业特色:本专业方向侧重于微软软件开发平台和技术,课程体系借助微软.Net平台战略,根据IT企业对人才职业素质与技能的要求,结合在校学生的具体情况,在学习计算机基础课程和核心课程的同时,强化学生软件开发实践能力的培养。

本专业具有完善的实验实践环境,学生可在微软虚拟开发平台上进行项目实训。

学生通过应用平台的案例教学与实践实训,可以熟悉软件项目的实际开发过程,掌握软件项目开发的基本方法和技能。

电子科技大学各专业介绍

通信与信息工程学院1.通信工程专业专业介绍:本专业培养具有扎实通信系统及通信网理论基础、利用现代电子技术,研究各种信息传输、存储、交换、处理、监测与显示等技术和系统,研究近代通信技术、通信系统、通信网络与各种媒体处理的人才。

本专业方向口径宽、适应性强、服务面广。

毕业生具有创新能力和工程实践能力,能够从事通信领域和信息系统的研究、设计、制造、分析和运行管理等工作。

主修课程:电路分析基础、数字逻辑设计与应用、信号与系统、模拟电路基础、微机原理及应用、通信原理、程控交换原理、计算机通信网、宽带通信网、卫星通信、移动通信、无线网络技术、接入网技术、电磁场与电磁波、数字信号处理( DSP 技术)、 ASIC 技术、 EDA 技术等。

2.网络工程专业专业介绍:本专业培养具有扎实的现代网络工程理论与现代通信理论基础、计算机应用能力强,研究网络规划工程设计、运行管理和性能分析及网络维护的人才。

本专业方向口径宽,适应性强、服2.务面广。

毕业生具有创新能力和工程实践能力,能够从事网络的规划和组网规划、网络工程设计和建设、运行维护和管理、安全防护和性能分析等网络工程领域的研究、设计、开发、应用以及管理和教育工作。

主修课程:电路分析基础、数字逻辑设计与应用、信号与系统、模拟电路基础、微机原理及应用、通信原理、程控交换原理、电磁场与电磁波、数字信号处理(DSP 技术)、TCP/IP 协议、软件技术基础宽带通信网、网络互联与路由技术、网络设备原理与技术、网络系统工程、网络规划与网络管理等。

3.物联网。

资料暂缺电子工程学院1.电子信息工程专业专业介绍:电子信息工程专业是我校最早设立的宽口径电子系统专业,是各发达国家中的热门专业之一,是四川省品牌专业。

本专业旨在培养德智体全面发展、知识结构合理、基础扎实、勇于创新、个性突出、具有国际竞争力的优秀的电子信息工程领域内高级技术人才。

有以下四个各具特色的培养方向:电子工程方向:培养学生掌握电子电路、信息系统的基本理论和工程技术,掌握信息获取与处理的基本理论及应用的一般方法,具备设计、开发、应用、集成电子设备和信息系统的能力。

电子科技大学_数字逻辑综合实验_4个实验报告_doc版

电子科技大学计算机学院标准实验报告(实验)课程名称数字逻辑综合实验xxx20160xxxxxxxxx电子科技大学教务处制表电子科技大学实验报告 1学生姓名:xxx 学号:指导教师:吉家成米源王华一、实验项目名称:中小规模组合逻辑设计二、实验目的:1.掌握非门、或门、与非门、异或门、数据选择器的逻辑功能。

2.掌握常有逻辑门电路的引脚排列及其使用方法。

3.采用中小规模逻辑门进行组合逻辑设计,掌握组合逻辑的设计方法。

三、实验内容:1.逻辑输入采用实验箱的K1-K11,逻辑输出接L1-L10。

测试实验箱上的HD74LS04P(非门)、SN74LS32N(或门)、SN74LS00N(与非门)、SN74HC86N(异或门)、SN74HC153(数据选择器、多路复用器)的逻辑功能。

2.采用小规模逻辑器件设计一位数据比较器:设一位数据比较器的输入为A、B,比较A>B,A=B,A<B,输出三个比较结果,输出采用低电平有效。

3.分别用小规模和中规模逻辑器件设计3输入多数表决器:设输入为A、B、C,当三个输入有两个或两个以上同意时,输出结果为同意,输入、输出的同意均为高电平有效。

四、实验原理:1.一块74LS04芯片上有6个非门。

非门的逻辑功能如表1所示,74LS04(非门、反相器)的逻辑符号和引脚排列如下图所示。

图1 74LS04的逻辑符号和引脚排列2.74LS32(或门)的逻辑符号、引脚排列如下图所示。

图2 74LS32的逻辑符号和引脚排列输入输出YA BL L LL H HH L HH H H3.74LS00输入输出YA BL L HL H HH L HH H L图3 74LS00逻辑符号和引脚排列4.一块74HC86芯片上有4个异或门。

异或门的逻辑功能如表4所示,74HC86(异或门)的逻辑符号、引脚排列如图4所示。

表4异或门的逻辑功能输入输出YA BL L LL H HH L HH H L图4 74HC86逻辑符号和引脚排列5.74HC153芯片上有两个4选1数据选择器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

门电路的工作原理和特性、CMOS传输门、施密特触发器结构和工作原理。逻辑电路的静态、动态特性分析;三态输出结构、漏极开路输出结构;

3、逻辑代数基础 ~15%

逻辑代数的公理、定理,对偶关系;逻辑函数的表达形式:积之和与和之积标准型、真值表;组合电路的分析:逻辑函数的化简,无关项的处理、冒险问题和多输出逻辑化简的方法。

存储器(ROM,SRAM)的基本工作原理和结构;存储器在数字逻辑系统设计的硬件实现中的运用。

8、模数转换器、数模转换器(ADC/DAC)原理及应用简介 ~5%

模拟-数字转换器、数字-模拟转换器(ADC/DAC)的基本电路结构、工作原理和应用。

9、脉冲电路 ~10%

单稳态电路工作原理、电路结构和工程应用,限幅电路工作原理和电路结构,多谐振荡器工作原理和电路结构、工程应用,555定时器的工作原理和应用。

4、组合逻辑设计 ~20%

利用基本的逻辑门完成组合逻辑电路的设计,利用基本的逻辑门和已有的中规模集成电路(MSI)逻辑器件如译码器、编码器、多路选择器、多路分配器、异或门、比较器、全加器、三态器件等作为设计的基本元素完成更为复杂的组合逻辑电路设计的方法。

5、时序逻辑基础与分析 ~15%

基本时序元件R-S型,D型,J-K型,T型锁存器、触发器的电路结构,工作原理,时序特性, 功能表,特征方程表达式,不同触发器之间的相互转换;钟控同步状态机的模型图,状态机类型及基本分析方法和步骤,使用状态表表示状态机状态转换关系;钟控同步状态机的设计:状态转换过程的建立,状态的化简与编码赋值、使用状态转换表的设计方法、使用状态图的设计方法。

考试科目 复试 数字逻辑电路设计及应用 考试形式 笔试(闭卷)

考试时间 120分钟 考试总分 100分

一、总体要求

掌握数字逻辑电路的基本原理与特性、数字逻辑电路的基本分析方法和设计方法,具备数字逻辑电路设计和综合的基本技能。

二、内容及比例

1、数系与代码 ~5%

数的十进制、二进制、八进制和十六进制表示以及它们之间的相互转换,符号数的S-M码,补码,反码表示以及它们之间的相互转换;带符号数的补码的加减运算;BCD码、GREY码;

6、时序逻辑设计 ~20%

利用基本的逻辑门、时序元件作为设计的基本元素完成规定的钟控同步状态机电路的设计任务:计数器、位移寄存器、序列检测电路和序列发生器的设计;利用基本的逻辑门和已有的中规模集成电路(MSI)时序功能器件作为设计的基本元素完成更为复杂的时序逻辑电路设计的方法。

7、存储器及其在数字逻辑系统实现中的运用 ~5%

三、题型及分值比例

1、选择题:10%

2、填空题:10%

3、画图题:10%

4、化简题:10%

5、分析题:30%