MC74AC138中文资料

74LVC138AD-T中文资料

15 14 13 12 11 10 9 7

1 2 3

A0 A1 A2

Y0 Y1 Y2 Y3

15 14 13 12 11 10 9 7

1 2 3

0 G 2 0 7

2 3 4

4 5 6

E1 E2 E3

Y4 Y5 Y6 Y7

MNA370

4 5 6

&

5 6 7

EN 7

MNA371(a)源自(b)Fig.3 Logic symbol.

74LVC138A

MATERIAL plastic plastic plastic plastic

CODE SOT109-1 SOT338-1 SOT403-1 SOT763-1

Y5 H H H H H H H H L H H

Y6 H H H H H H H H H L H

Y7 H H H H H H H H H H L

Fig.1 Pin configuration SO16 and (T)SSOP16.

Fig.2 Pin configuration DHVQFN16.

2003 May 06

4

元器件交易网

Philips Semiconductors

Product specification

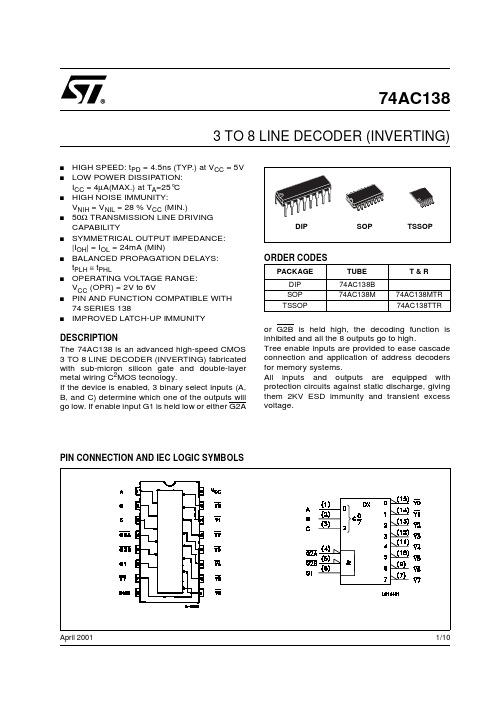

ORDERING INFORMATION PACKAGE TYPE NUMBER TEMPERATURE RANGE 74LVC138AD 74LVC138ADB 74LVC138APW 74LVC138ABQ FUNCTION TABLE See note 1. INPUT E1 H X X L L L L L L L L Note 1. H = HIGH voltage level; L = LOW voltage level; X = don’t care. E2 X H X L L L L L L L L E3 X X L H H H H H H H H A0 X X X L H L H L H L H A1 X X X L L H H L L H H A2 X X X L L L L H H H H Y0 H H H L H H H H H H H Y1 H H H H L H H H H H H Y2 H H H H H L H H H H H OUTPUT Y3 H H H H H H L H H H H Y4 H H H H H H H L H H H −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C PINS 16 16 16 16 PACKAGE SO16 SSOP16 TSSOP16 DHVQFN16

74ALS138中文资料

Product specificationDIP16:plastic dual in-line package; 16 leads (300 mil)SOT38-4SO16:plastic small outline package; 16 leads; body width 3.9 mm SOT109-1Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products,including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright,or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.LIFE SUPPORT APPLICATIONS Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices,or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale.This data sheet contains preliminary data, and supplementary data will be published at a later date. PhilipsSemiconductors reserves the right to make changes at any time without notice in order to improve designand supply the best possible product.Philips Semiconductors811 East Arques AvenueP .O. Box 3409Sunnyvale, California 94088–3409Telephone 800-234-7381DEFINITIONSData Sheet IdentificationProduct Status Definition Objective Specification Preliminary Specification Product Specification Formative or in Design Preproduction Product Full ProductionThis data sheet contains the design target or goal specifications for product development. Specificationsmay change in any manner without notice.This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changesat any time without notice, in order to improve design and supply the best possible product.© Copyright Philips Electronics North America Corporation 1997All rights reserved. Printed in U.S.A.。

MC74HCT138ADTR2G,MC74HCT138ADR2G,MC74HCT138ADG,MC74HCT138AN,MC74HCT138AD, 规格书,Datasheet 资料

MC74HCT138A1-of-8 Decoder/ Demultiplexer with LSTTL Compatible InputsHigh−Performance Silicon−Gate CMOSThe MC74HCT138A is identical in pinout to the LS138. The HCT138A may be used as a level converter for interfacing TTL or NMOS outputs to High Speed CMOS inputs.The HCT138A decodes a three−bit Address to one−of−eight active−lot outputs. This device features three Chip Select inputs, two active−low and one active−high to facilitate the demultiplexing, cascading, and chip−selecting functions. The demultiplexing function is accomplished by using the Address inputs to select the desired device output; one of the Chip Selects is used as a data input while the other Chip Selects are held in their active states.Features•Output Drive Capability: 10 LSTTL Loads•TTL/NMOS Compatible Input Levels•Outputs Directly Interface to CMOS, NMOS, and TTL •Operating V oltage Range: 4.5 to 5.5 V•Low Input Current: 1.0 m A•In Compliance with the Requirements Defined by JEDEC Standard No. 7A•Chip Complexity: 122 FETs or 30.5 Equivalent Gates•Pb−Free Packages are Available**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting TechniquesReference Manual, SOLDERRM/D.MARKINGDIAGRAMSSOIC−16D SUFFIXCASE 751BTSSOP−16DT SUFFIXCASE 948FPDIP−16N SUFFIXCASE 648116MC74HCT138ANAWLYYWWG116HCT138AGAWLYWWA=Assembly LocationWL, L=Wafer LotYY, Y=YearWW, W=Work WeekG or G=Pb−Free Package(Note: Microdot may be in either location)See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATIONHCT138AALYW GG116InputsOutputs CS1CS2CS3A2A1A0Y0Y1Y2Y3Y4Y5Y6Y7X X H X X X H H H H H H H H X HX X X X H H H H H H H H L X X X X X H H H H H H H H H L L L L L L H H H H H H H H L L L LH H L H H H H H H H L L L H L H HL H H H H H H L L L H H H H H L H H H H H L L H L L H H H H L H H H H L L H L H H H H H H LH H H L L H H L H H H H H H L H HLLHHHHHHHHHHLFUNCTION TABLEH = high level (steady state)L = low level (steady state)X = don’t careLOGIC DIAGRAMY6Y5Y4Y3Y2Y1Y0Y7CS1CS2ACTIVE-LOW OUTPUTSADDRESS INPUTSCS3CHIP-SELECT INPUTSCC PIN ASSIGNMENTA0CS2A2A1Y7CS1CS3GNDY3Y2Y1Y0V CC Y5Y4Y6Design Criteria Value Units Internal Gate Count*30.5ea.Internal Gate Propagation Delay 1.5nsInternal Gate Power Dissipation 5.0m W Speed Power Product.0075pJ*Equivalent to a two −input NAND gate.ORDERING INFORMATIONDevicePackage Shipping †MC74HCT138ANG PDIP −16(Pb −Free)500 Units / Box MC74HCT138ADG SOIC −16(Pb −Free)48 Units / Rail MC74HCT138ADR2G SOIC −16(Pb −Free)2500 Units / Tape & Reel MC74HCT138ADTR2TSSOP −16*2500 Units / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage (Referenced to GND)– 0.5 to + 7.0V V in DC Input Voltage (Referenced to GND)– 0.5 to V CC + 0.5V V out DC Output Voltage (Referenced to GND)– 0.5 to V CC + 0.5VI in DC Input Current, per Pin±20mAI out DC Output Current, per Pin±25mAI CC DC Supply Current, V CC and GND Pins±50mAP D Power Dissipation in Still Air Plastic DIP†SOIC Package†TSSOP Package†750500450mWT stg Storage Temperature– 65 to + 150_C T L Lead Temperature, 1 mm from Case for 10 Seconds(Plastic DIP, TSSOP or SOIC Package)260_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.†Derating—Plastic DIP: – 10 mW/_C from 65_ to 125_CSOIC Package: – 7 mW/_C from 65_ to 125_CTSSOP Package: − 6.1 mW/_C from 65_ to 125_CRECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC DC Supply Voltage (Referenced to GND) 4.5 5.5VV in, V out DC Input Voltage, Output Voltage (Referenced to GND)0V CC V T A Operating Temperature, All Package Types– 55+ 125_C t r, t f Input Rise and Fall Time (Figure 1)0500ns DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)Symbol Parameter Test Conditions V CCVGuaranteed LimitUnit – 55 to25_C v85_C v 125_CV IH Minimum High−Level Input Voltage V out = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.52.02.02.02.02.02.0VV IL Maximum Low−Level Input Voltage V out = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.50.80.80.80.80.80.8VV OH Minimum High−Level Output Voltage V in = V IH or V IL|I out| v 20 m A4.55.54.45.44.45.44.45.4VV in = V IH or V IL|I out| v 4.0 mA 4.5 3.98 3.84 3.7V OL Maximum Low−Level Output Voltage V in = V IH or V IL|I out| v 20 m A4.55.50.10.10.10.10.10.1VV in = V IH or V IL|I out| v 4.0 mA 4.50.260.330.4I in Maximum Input Leakage Current V in = V CC or GND 6.0±0.1±1.0±1.0m AI CC Maximum Quiescent SupplyCurrent (per Package)V in = V CC or GNDI out = 0 m A5.5 4.040160m AD I CC Additional Quiescent SupplyCurrentV in = 2.4 V, Any One InputV in = V CC or GND, Other Inputsl out = 0 m A 5.5≥ − 55_C25_C to 125_CmA2.9 2.4This device contains protectioncircuitry to guard against damagedue to high static voltages or electricfields. However, precautions mustbe taken to avoid applications of anyvoltage higher than maximum ratedvoltages to this high−impedance cir-cuit. For proper operation, V in andV out should be constrained to therange GND v (V in or V out) v V CC.Unused inputs must always betied to an appropriate logic voltagelevel (e.g., either GND or V CC).Unused outputs must be left open.AC ELECTRICAL CHARACTERISTICS (V CC = 5.0 V ± 10%, C L = 50 pF, Input t r = t f = 6.0 ns)Symbol ParameterGuaranteed LimitUnit – 55 to 25_C v 85_C v 125_Ct PLH ,t PHL Maximum Propagation Delay, Input A to Output Y (Figures 1 and 4)303845ns t PLH ,t PHL Maximum Propagation Delay, CS1 to Output Y (Figures 2 and 4)273441ns t PLH ,t PHL Maximum Output Transition Time, CS2 or CS3 to Output Y (Figures 3 and 4)303845ns t TLH ,t THL Maximum Output Transition Time, Any Output (Figures 2 and 4)151922ns t r , t f Maximum Input Rise and Fall Time 500500500ns C inMaximum Input Capacitance101010pFC PDPower Dissipation Capacitance (Per Enabled Output)*Typical @ 25°C, V CC = 5.0 VpF51*Used to determine the no −load dynamic power consumption: P D = C PD V CC f + I CC V CC .EXPANDED LOGIC DIAGRAMA0A1A2CS3CS2CS1SWITCHING WAVEFORMSFigure 1.3 VGNDFigure 2.3 V GND t OUTPUT YINPUT CS2, CS33 V GNDFigure 3.*Includes all probe and jig capacitanceFigure 4.C L *TEST POINT TEST CIRCUITPDIP −16N SUFFIX CASE 648−08ISSUE TSOIC −16D SUFFIX CASE 751B −05ISSUE JNOTES:1.DIMENSIONING AND TOLERANCING PERANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION L TO CENTER OF LEADSWHEN FORMED PARALLEL.4.DIMENSION B DOES NOT INCLUDEMOLD FLASH.5.ROUNDED CORNERS OPTIONAL.MSEATING PLANEMAM0.25 (0.010)T DIM MIN MAX MIN MAX MILLIMETERS INCHES A 0.7400.77018.8019.55B 0.2500.270 6.35 6.85C 0.1450.175 3.69 4.44D 0.0150.0210.390.53F 0.0400.70 1.02 1.77G 0.100 BSC 2.54 BSC H 0.050 BSC 1.27 BSC J 0.0080.0150.210.38K 0.1100.130 2.80 3.30L 0.2950.3057.507.74M 0 10 0 10 S0.0200.0400.51 1.01____NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION ATMAXIMUM MATERIAL CONDITION.SBM0.25 (0.010)AST DIM MIN MAX MIN MAX INCHESMILLIMETERS A 9.8010.000.3860.393B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2290.244R0.250.500.0100.019____TSSOP −16DT SUFFIX CASE 948F −01ISSUE ADIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.180.280.0070.011J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

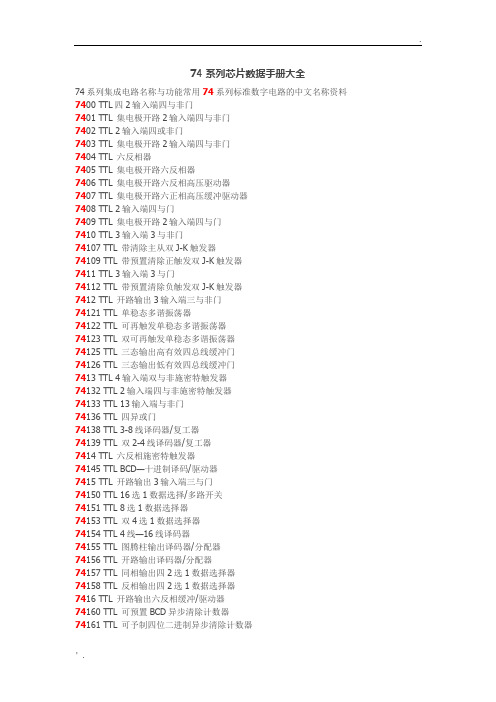

74系列芯片简介——功能与描述

7400、74H00、74L00、74LS00、74S00、74HC00、74C00、74F00、74ALS00四2输入与非门Y=\AB。

7401、74LS01、74HC01、74ALS01四2输入与非门(OC)Y=\AB。

7402、74L02、74LS02、74S02、74HC02、74C02、74ALS02、74F02四2输入或非门。

Y=/A+B。

7403、74L03、74LS03、74ALS03、74S03、74HC037404、74H04、74L04、74S04、74HC04、74C04、74F04、74ALS04六反相器Y=/A。

7405、74H05、74LS05、74S05、74HC05、74F05、74ALS05六反相器(OC)Y=/A。

7406、74LS06六反相缓冲器/驱动器(OC、高压输出)Y=/A;是7405高耐压输出型,耐压30V。

7407、74LS07、74HC07六缓冲器/驱动器(OC、高压输出)Y=A; 30V耐高压输出。

7408、74LS08、74F08、74ALS08、74S08、74HC08、74C08四2输入与门Y=AB。

7409、74LS09、74F09、74ALS09、74S09、74HC09四2输入与门(OC)Y=AB。

7410、74H10、74L10、74LS10、74ALS10、74S10、74HC10、74C1074H11、74LS11、74S11、74F11、74ALS11、74HC11三3输入与门Y=ABC。

7412、74LS12、74ALS12三3输入与非门(OC)Y=\ABC。

7413、74LS13双4输入与非门Y=\ABCD。

7414、74LS14、74HC14、74C1474H15、74LS15、74ALS15、74S15三3输入与门(OC)Y=ABC。

7416、74LS16六反相缓冲器/驱动器Y=/A;7417、74LS17六缓冲器/驱动器(OC、高压输出)Y=A;15V耐压输出。

MC74AC57中文资料

LOGIC SYMBOL

PIN NAMES D0–D7 CP OE O0–O7 Data Inputs Clock Pulse Input 3-State Output Enable Input 3-State Outputs D0 D1 D2 D3 D4 D5 D6 D7 CP OE O0 O1 O2 O3 O4 O5 O6 O7

FACT DATA 5-2

元器件交易网

MC74AC57 MC74ACT574

MAXIMUM RATINGS*

Symbol VCC Vin Vout Iin Iout ICC Tstg Parameter DC Supply Voltage (Referenced to GND) DC Input Voltage (Referenced to GND) DC Output Voltage (Referenced to GND) DC Input Current, per Pin DC Output Sink/Source Current, per Pin DC VCC or GND Current per Output Pin Storage Temperature Value –0.5 to +7.0 –0.5 to VCC +0.5 –0.5 to VCC +0.5 ±20 ±50 ±50 –65 to +150 Unit V V V mA mA mA °C

H H

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial Z = High Impedance = LOW-to-HIGH Clock Transition NC = No Change

MC74AC174M资料

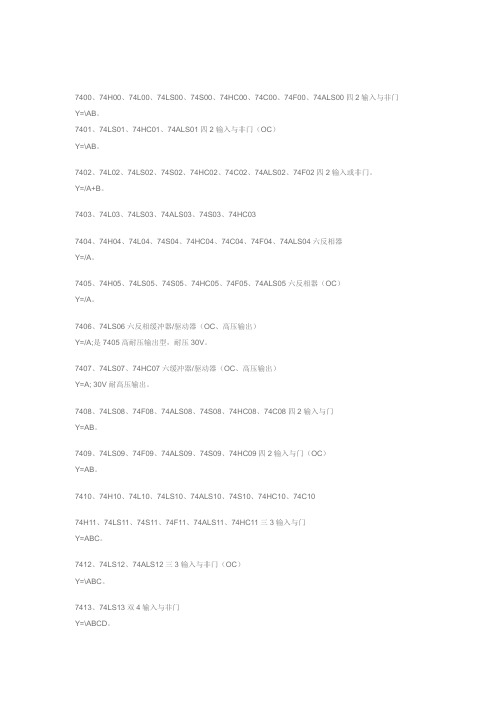

MC74AC174, MC74ACT174 Array Hex D Flip−Flopwith Master ResetThe MC74AC174/74ACT174 is a high−speed hex D flip−flop. Thedevice is used primarily as a 6−bit edge−triggered storage register. Theinformation on the D inputs is transferred to storage during theLOW−to−HIGH clock transition. The device has a Master Reset toDEVICE MARKING INFORMATIONSee general marking information in the device markingsection on page 6 of this data sheet.Figure 2. Logic SymbolFUNCTIONAL DESCRIPTIONLOW −to −HIGH Clock (CP) transition. A LOW input to the Master Reset (MR) will force all outputs LOW independent *Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recom-mended Operating Conditions.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Max UnitV CC Supply Voltage′AC 2.0 5.0 6.0V ′ACT 4.5 5.0 5.5V IN, V OUT DC Input Voltage, Output Voltage (Ref. to GND)0−V CC Vt r, t f Input Rise and Fall Time (Note 1)′AC Devices except Schmitt Inputs V CC @ 3.0 V−150−V CC @ 4.5 V−40−ns/V V CC @ 5.5 V−25−t r, t f Input Rise and Fall Time (Note 2)′ACT Devices except Schmitt Inputs V CC @ 4.5 V−10−ns/V V CC @ 5.5 V−8.0−T J Junction Temperature (PDIP)−−140°C T A Operating Ambient Temperature Range−402585°C I OH Output Current − High−−−24mAI OL Output Current − Low−−24mA1.V IN from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.2.V IN from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)74AC74ACUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 3.0 1.5 2.1 2.1V OUT = 0.1 V4.5 2.25 3.15 3.15V or V CC− 0.1 V5.5 2.75 3.85 3.85V IL Maximum Low LevelInput Voltage 3.0 1.50.90.9V OUT = 0.1 V4.5 2.25 1.35 1.35V or V CC− 0.1 V5.5 2.75 1.65 1.65V OH Minimum High LevelOutput Voltage 3.0 2.99 2.9 2.9I OUT = −50 m A4.5 4.49 4.4 4.4V5.5 5.49 5.4 5.4V*V IN = V IL or V IH3.0− 2.56 2.46−12 mA4.5− 3.86 3.76I OH−24 mA5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 3.00.0020.10.1I OUT = 50 m A4.50.0010.10.1V5.50.0010.10.1V*V IN = V IL or V IH3.0−0.360.4412 mA4.5−0.360.44I OL24 mA5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0m A V I = V CC, GNDI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V Min I CC Maximum QuiescentSupply Current 5.5−8.080m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V CC.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74AC74ACUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxf max Maximum Clock 3.390100−70−MHz3−3 Frequency 5.0100125−100−t PLH Propagation Delay 3.3 2.09.011.5 1.512.5ns3−6 CP to Q n 5.0 1.5 6.08.5 1.09.5t PHL Propagation Delay 3.3 2.08.511.0 1.512.0ns3−6 CP to Q n 5.0 1.5 6.08.0 1.09.0t PHL Propagation Delay 3.3 2.59.011.5 2.012.5ns3−6 MR to Q n 5.0 1.57.09.0 1.510.5*Voltage Range 3.3 V is 3.3 V ±0.3 V.*Voltage Range 5.0 V is 5.0 V ±0.5 V. AC OPERATING REQUIREMENTSSymbol Parameter V CC*(V)74AC74ACUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFTyp Guaranteed Minimumt s Setup Time, HIGH or LOW 3.3 2.5 6.57.0ns3−9 D n to CP 5.0 2.0 5.0 5.5t h Hold Time, HIGH or LOW 3.3 1.0 3.0 3.0ns3−9 D n to CP 5.00.5 3.0 3.0t w MR Pulse Width, LOW 3.3 1.0 5.57.0ns3−6 5.0 1.0 5.0 5.0t w CP Pulse Width 3.3 1.0 5.57.0ns3−6 5.0 1.0 5.0 5.0t rec Recovery TIme 3.30 2.5 2.5ns3−6 MR to CP 5.00 2.0 2.0*Voltage Range 3.3 V is 3.3 V ±0.3 V. *Voltage Range 5.0 V is 5.0 V ±0.5 V.DC CHARACTERISTICSSymbol Parameter V CC(V)74ACT74ACTUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 4.5 1.5 2.0 2.0VV OUT = 0.1 V 5.5 1.5 2.0 2.0or V CC− 0.1 VV IL Maximum Low LevelInput Voltage 4.5 1.50.80.8VV OUT = 0.1 V 5.5 1.50.80.8or V CC− 0.1 VV OH Minimum High LevelOutput Voltage 4.5 4.49 4.4 4.4VI OUT = −50 m A5.5 5.49 5.4 5.4*V IN = V IL or V IH4.5− 3.86 3.76VI OH−24 mA 5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 4.50.0010.10.1VI OUT = 50 m A5.50.0010.10.1*V IN = V IL or V IH4.5−0.360.44VI OL24 mA 5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0m A V I = V CC, GND D I CCT Additional Max. I CC/Input 5.50.6− 1.5mA V I = V CC−2.1 VI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V Min I CC Maximum QuiescentSupply Current 5.5−8.080m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74ACT74ACTUnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxf max Maximum ClockFrequency5.0165−−140−MHz3−3t PLH Propagation DelayCP to Q n5.0 1.5−10.5 1.511.5ns3−6t PHL Propagation DelayCP to Q n5.0 1.5−10.5 1.511.5ns3−6t PHL Propagation DelayMR to Q n5.0 1.5−9.5 1.511.0ns3−6 *Voltage Range 5.0 V is 5.0 V ±0.5 V.WW, W= Work WeekPACKAGE DIMENSIONSPDIP −16N SUFFIX16 PIN PLASTIC DIP PACKAGECASE 648−08PACKAGE DIMENSIONSTSSOP−16DT SUFFIX16 PIN PLASTIC TSSOP PACKAGECASE948F−01ISSUE O16X REFand are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liabilityPUBLICATION ORDERING INFORMATION。

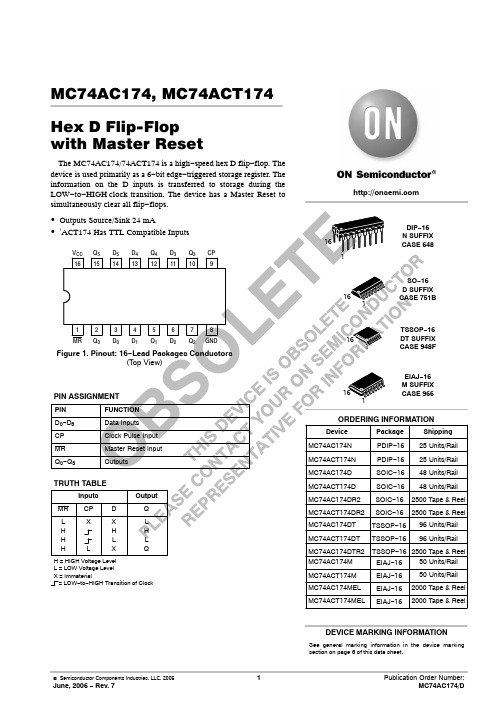

MC74AC4040中文资料

FUNCTION TABLE

Clock Reset L L X H Output State No Change Advance to next state All Outputs are low CLOCK

LOGIC DIAGRAM

9 7 6 5 10 3 2 4 13 12 14 15 1 11 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q10 Q11 Q12

VIL

Maximum Low Level Input Voltage

V

VOH

Minimum High Level Output Voltage

V

V

µA mA mA

* All outputs loaded; thresholds on input associated with output under test. ** Maximum test duration 2.0 ms, one output loaded at a time.

FACT DATA 5-2

元器件交易网

MC74AC4040

DC CHARACTERISTICS (unless otherwise specified)

Symbol ICC Parameter Maximum Quiescent Supply Voltage Value 80 Unit µA Vin = VCC or GND VCC = 5.5 V, TA = Worst Case Vin = VCC or GND VCC = 5.5 V, TA = 25°C

VCC 16 Q11 15 Q10 14 Q8 13 Q9 12 RESET CLK 11 10 Q1 9

12-STAGE BINARY RIPPLE COUNTER

MC74AC245 74ACT245八路双向转发器说明书

MC74AC245, MC74ACT245Octal BidirectionalTransceiver with 3-State Inputs/OutputsThe MC74AC245/74ACT245 contains eight non−inverting bidirectional buffers with 3−state outputs and is intended for bus−oriented applications. Current sinking capability is 24 mA at both the A and B ports. The Transmit/Receive (T/R) input determines the direction of data flow through the bidirectional transceiver. Transmit (active−HIGH) enables data from A ports to B ports; Receive (active−LOW) enables data from B ports to A ports. The Output Enable input, when HIGH, disables both A and B ports by placing them in a High Z condition.Features•Noninverting Buffers •Bidirectional Data Path•A and B Outputs Source/Sink 24 mA •′ACT245 has TTL Compatible Inputs •These are Pb−Free DevicesPIN ASSIGNMENTPIN FUNCTION OE Output Enable Input T/R Transmit/Receive InputA 0−A 7Side A 3−State Inputs or 3−State OutputsB 0−B 7Side B 3−State Inputs or 3−State OutputsTRUTH TABLESInputs Outputs OE T/R L L Bus B Data to Bus A L H Bus A Data to Bus B HXHigh Z StateH = HIGH Voltage Level L = LOW Voltage Level X = ImmaterialFigure 1.V CC OE B 0B 1B 2B 3B 4B 5B 6B 7T/RA 0A 1A 2A 3A 4A 5A 6A 7GNDSOIC−20W DW SUFFIX CASE 751DTSSOP−20DT SUFFIX CASE 948E1See detailed ordering and shipping information in the package dimensions section on page 6 of this data sheet.ORDERING INFORMATIONSee general marking information in the device marking section on page 7 of this data sheet.DEVICE MARKING INFORMATIONMAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage (Referenced to GND)−0.5 to +7.0V V IN DC Input Voltage (Referenced to GND)−0.5 to V CC +0.5V V OUT DC Output Voltage (Referenced to GND) (Note 1)−0.5 to V CC +0.5VI IK DC Input Diode Current±20mAI OK DC Output Diode Current±50mAI OUT DC Output Sink/Source Current±50mAI CC DC Supply Current, per Output Pin±50mA I GND DC Ground Current, per Output Pin±100mA T STG Storage Temperature Range*65 to )150_C T L Lead temperature, 1 mm from Case for 10 Seconds260_C T J Junction Temperature Under Bias140_Cq JA Thermal Resistance (Note 2)SOICTSSOP 65.8110.7_C/WMSL Moisture Sensitivity Level 1F R Flammability Rating Oxygen Index: 30% − 35%UL94V−*********V ESD ESD Withstand Voltage Human Body Model (Note 3)Machine Model (Note 4)Charged Device Model (Note 5)> 2000> 200> 1000VI Latchup Latchup Performance Above V CC and Below GND at 85_C (Note 6)±100mA Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.I OUT absolute maximum rating must be observed.2.The package thermal impedance is calculated in accordance with JESD 51−7.3.Tested to EIA/JESD22−A114−A.4.Tested to EIA/JESD22−A115−A.5.Tested to JESD22−C101−A.6.Tested to EIA/JESD78.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Max UnitV CC Supply Voltage ′AC 2.0 5.0 6.0V ′ACT 4.5 5.0 5.5V IN, V OUT DC Input Voltage, Output Voltage (Ref. to GND)0−V CC Vt r, t f Input Rise and Fall Time (Note 7)′AC Devices except Schmitt InputsV CC @ 3.0 V−150−V CC @ 4.5 V−40−ns/VV CC @ 5.5 V−25−t r, t f Input Rise and Fall Time (Note 8)′ACT Devices except Schmitt InputsV CC @ 4.5 V−10−ns/VV CC @ 5.5 V−8.0−T A Operating Ambient Temperature Range−402585°CI OH Output Current − High−−−24mAI OL Output Current − Low−−24mA Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.7.V IN from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.8.V IN from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)74AC74ACUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 3.0 1.5 2.1 2.1V OUT = 0.1 V4.5 2.25 3.15 3.15V or V CC − 0.1 V5.5 2.75 3.85 3.85V IL Maximum Low LevelInput Voltage 3.0 1.50.90.9V OUT = 0.1 V4.5 2.25 1.35 1.35V or V CC − 0.1 V5.5 2.75 1.65 1.65V OH Minimum High LevelOutput Voltage 3.0 2.99 2.9 2.9I OUT = −50 m A4.5 4.49 4.4 4.4V5.5 5.49 5.4 5.4V*V IN = V IL or V IH3.0− 2.56 2.46−12 mA4.5− 3.86 3.76I OH−24 mA5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 3.00.0020.10.1I OUT = 50 m A4.50.0010.10.1V5.50.0010.10.1V*V IN = V IL or V IH3.0−0.360.4412 mA4.5−0.360.44I OL24 mA5.5−0.360.4424 mAI IN Maximum InputLeakage Current5.5−±0.1±1.0m A V I = V CC, GNDI OZT Maximum3-StateCurrentV I(OE) = V IL, V IH 5.5−±0.6±6.0m A V I = V CC, GNDV O = V CC, GNDI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V MinI CC Maximum QuiescentSupply Current5.5−8.080.0m A V IN = V CC or GND*All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC@**************************************************************CC.Symbol Parameter V CC*(V)UnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay 3.3 1.5 5.08.5 1.09.0ns3−5 A n to B n or B n to A n 5.0 1.5 3.5 6.5 1.07.0t PHL Propagation Delay 3.3 1.5 5.08.5 1.09.0ns3−5 A n to B n or B n to A n 5.0 1.5 3.5 6.0 1.07.0t PZH Output Enable Time 3.3 2.57.011.5 2.012.5ns3−7 5.0 1.5 5.08.5 1.09.0t PZL Output Enable Time 3.3 2.57.512.0 2.013.5ns3−8 5.0 1.5 5.59.0 1.09.5t PHZ Output Disable Time 3.3 2.0 6.512.0 1.012.5ns3−7 5.0 1.5 5.59.0 1.010.0t PLZ Output Disable Time 3.3 2.07.011.5 1.513.0ns3−8 5.0 1.5 5.59.0 1.010.0*Voltage Range 3.3 V is 3.3 V ±0.3 V. Voltage Range 5.0 V is 5.0 V ±0.5 V. DC CHARACTERISTICSSymbol Parameter V CC(V)74ACT74ACTUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 4.5 1.5 2.0 2.0VV OUT = 0.1 V 5.5 1.5 2.0 2.0or V CC − 0.1 VV IL Maximum Low LevelInput Voltage 4.5 1.50.80.8VV OUT = 0.1 V 5.5 1.50.80.8or V CC − 0.1 VV OH Minimum High LevelOutput Voltage 4.5 4.49 4.4 4.4VI OUT = −50 m A5.5 5.49 5.4 5.4*V IN = V IL or V IH4.5− 3.86 3.76V I OH−24 mA5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 4.50.0010.10.1VI OUT = 50 m A5.50.0010.10.1*V IN = V IL or V IH4.5−0.360.44VI OL24 mA 5.5−0.360.4424 mAI IN Maximum InputLeakage Current5.5−±0.1±1.0m A V I = V CC, GNDD I CCT Additional Max. I CC/Input 5.50.6− 1.5mA V I = V CC −2.1 VI OZT Maximum3−StateCurrentV I(OE) = V IL, V IH 5.5−±0.6±6.0m A V I = V CC, GNDV O = V CC, GNDI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V MinI CC Maximum QuiescentSupply Current5.5−8.080.0m A V IN = V CC or GND*All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.Symbol Parameter V CC*(V)UnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay, A n to B n or B n to A n 5.0 1.5 4.07.5 1.58.0ns3−5 t PHL Propagation Delay, A n to B n or B n to A n 5.0 1.5 4.08.0 1.09.0ns3−5 t PZH Output Enable Time 5.0 1.5 5.010 1.511.0ns3−7 t PZL Output Enable Time 5.0 1.5 5.510 1.512.0ns3−8 t PHZ Output Disable Time 5.0 1.5 5.510 1.011.0ns3−7 t PLZ Output Disable Time 5.0 2.0 5.010 1.511.0ns3−8 *Voltage Range 5.0 V is 5.0 V ±0.5 V.CAPACITANCESymbol Parameter ValueTypUnit Test ConditionsC IN Input Capacitance 4.5pF V CC = 5.0 V C I/O Input/Output Capacitance15pF V CC = 5.0 V C PD Power Dissipation Capacitance45pF V CC = 5.0 VORDERING INFORMATIONDevicePackage Shipping †MC74AC245DWG SOIC−20(Pb−Free)38 Units / Rail MC74AC245DWR2G SOIC−20(Pb−Free)1000 / Tape & Reel MC74ACT245DWG SOIC−20(Pb−Free)38 Units / Rail MC74ACT245DWR2G SOIC−20(Pb−Free)1000 / Tape & Reel MC74AC245DTG TSSOP−20(Pb−Free)75 Units / Rail MC74AC245DTR2G TSSOP−20(Pb−Free)2500 / Tape & Reel MC74ACT245DTG TSSOP−20(Pb−Free)75 Units / Rail MC74ACT245DTR2GTSSOP−20(Pb−Free)2500 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.MARKING DIAGRAMSSOIC−20W TSSOP−20120AC 245ALYW G GA = Assembly Location WL, L = Wafer Lot YY , Y = YearWW, W = Work Week G or G = Pb−Free Package(Note: Microdot may be in either location)120ACT 245ALYW GGTSSOP−20DT SUFFIX CASE 948E−02ISSUE CDIM A MIN MAX MIN MAX INCHES 6.600.260MILLIMETERS B 4.30 4.500.1690.177C 1.200.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSCH 0.270.370.0110.015J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M 0 8 0 8 ____NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION:MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSIONSHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W−.DETAIL E6.400.252------16X0.360.65PITCH*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOIC−20WDW SUFFIXCASE 751D−05ISSUE GM0.25SA SBTDIM MIN MAXMILLIMETERSA 2.35 2.65A10.100.25B0.350.49C0.230.32D12.6512.95E7.407.60e 1.27 BSCH10.0510.55h0.250.75L0.500.90q0 7NOTES:1.DIMENSIONS ARE IN MILLIMETERS.2.INTERPRET DIMENSIONS AND TOLERANCESPER ASME Y14.5M, 1994.3.DIMENSIONS D AND E DO NOT INCLUDE MOLDPROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.5.DIMENSION B DOES NOT INCLUDE DAMBARPROTRUSION. ALLOWABLE PROTRUSIONSHALL BE 0.13 TOTAL IN EXCESS OF BDIMENSION AT MAXIMUM MATERIALCONDITION.__PUBLICATION ORDERING INFORMATIONON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at /site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.。

MC74ACT125中文资料

FACT DATA 5-3

元器件交易网

V

V

V

µA

5.5 5.5 5.5 5.5 5.5 0.6

±0.5

±5.0 1.5 75 –75

µA mA mA mA µA

∆ICCT IOLD IOHD ICC

8.0

80

* All outputs loaded; thresholds on input associated with output under test. † Maximum test duration 2.0 ms, one input loaded at a time.

DC CHARACTERISTICS

74AC Symbol Parameter VCC (V) TA = +25°C Typ VIH Minimum High Level Input Voltage Maximum Low Level Input Voltage Minimum High Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 VOL Minimum Low Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 IIN IOZ Maximum Input Leakage Current VI (OE) = VIL, VIH VI = VCC, GND VO = VCC , GND †Minimum Dynamic Output Current Maximum Quiescent Supply Current 5.5 0.002 0.001 0.001 1.5 2.25 2.75 1.5 2.25 2.75 2.99 4.46 5.49 74AC TA = –40°C to +85°C Unit Conditions

CD74ACT138E,CD74ACT138M96E4,CD74ACT138M96G4,CD74ACT138ME4,CD74ACT138MG4, 规格书,Datasheet 资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)CD54ACT138F3A ACTIVE CDIP J 161TBD A42N /A for Pkg Type CD74ACT138E ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type CD74ACT138EE4ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type CD74ACT138M ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT138M96ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT138M96E4ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT138M96G4ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT138ME4ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM CD74ACT138MG4ACTIVESOICD1640Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemptionfor either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM15-Oct-2009TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD74ACT138M96SOICD162500330.016.46.510.3 2.18.016.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) CD74ACT138M96SOIC D162500333.2345.928.6IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and /automotiveAutomotiveMicrocontrollers Video and Imaging /videoRFID Wireless /wireless-appsRF/IF and ZigBee®Solutions /lprfTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

74AC138M中文资料

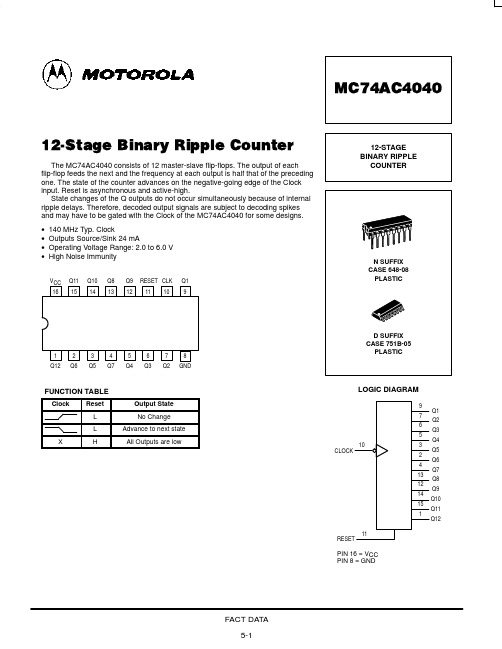

1/10April 2001s HIGH SPEED: t PD = 4.5ns (TYP.) at V CC = 5V sLOW POWER DISSIPATION:I CC = 4µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)s50Ω TRANSMISSION LINE DRIVING CAPABILITYsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 24mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 138sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe 74AC138 is an advanced high-speed CMOS 3 TO 8 LINE DECODER (INVERTING) fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS tecnology.If the device is enabled, 3 binary select inputs (A,B, and C) determine which one of the outputs will go low. If enable input G1 is held low or either G2Aor G2B is held high, the decoding function is inhibited and all the 8 outputs go to high.Tree enable inputs are provided to ease cascade connection and application of address decoders for memory systems.All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74AC1383 TO 8 LINE DECODER (INVERTING)PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & R DIP 74AC138B SOP 74AC138M74AC138MTR TSSOP74AC138TTR74AC1382/10INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEX : Don’t CareLOGIC DIAGRAMPIN No SYMBOL NAME AND FUNCTION 1, 2, 3A, B, C Address Inputs 4, 5G2A, G2BEnable Inputs 6G1Enable Input 15, 14, 13, 12, 11, 10, 9,7Y0 to Y7Outputs8GND Ground (0V)16V CCPositive Supply VoltageINPUTSOUTPUTS ENABLE SELECTG2B G2A G1C B A Y0Y1Y2Y3Y4Y5Y6Y7X X L X X X H H H H H H H H X H X X X X H H H H H H H H H X X X X X H H H H H H H H L L H L L L L H H H H H H H L L H L L H H L H H H H H H L L H L H L H H L H H H H H L L H L H H H H H L H H H H L L H H L L H H H H L H H H L L H H L H H H H H H L H H L L H H H L H H H H H H L H LLHHHHHHHHHHHL74AC1383/10ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.RECOMMENDED OPERATING CONDITIONS1) V IN from 30% to 70% of V CCSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 50mA I CC or I GND DC V CC or Ground Current± 400mA T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature-55 to 125°C dt/dvInput Rise and Fall Time V CC = 3.0, 4.5 or 5.5V (note 1)8ns/V74AC1384/10DC SPECIFICATIONS1) Maximum test duration 2ms, one output loaded at time2) Incident wave switching is guaranteed on transmission lines with impedances as low as 50ΩSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage3.0V O = 0.1 V or V CC -0.1V 2.1 1.5 2.1 2.1V4.5 3.15 2.25 3.15 3.155.5 3.852.753.853.85V ILLow Level Input Voltage3.0V O = 0.1 V or V CC -0.1V 1.50.90.90.9V4.5 2.25 1.35 1.35 1.355.5 2.75 1.651.651.65V OHHigh Level Output Voltage3.0I O =-50 µA 2.9 2.99 2.9 2.9V4.5I O =-50 µA 4.4 4.49 4.4 4.45.5I O =-50 µA 5.4 5.495.4 5.43.0I O =-12 mA 2.56 2.46 2.44.5I O =-24 mA 3.86 3.76 3.75.5I O =-24 mA 4.864.764.7V OLLow Level Output Voltage3.0I O =50 µA 0.0020.10.10.1V4.5I O =50 µA 0.0010.10.10.15.5I O =50 µA 0.0010.10.10.13.0I O =12 mA 0.360.440.54.5I O =24 mA 0.360.440.55.5I O =24 mA 0.360.440.5I I Input Leakage Current5.5V I = V CC or GND ± 0.1± 1± 1µA I CC Quiescent Supply Current5.5V I = V CC or GND 44080µA I OLD Dynamic Output Current (note 1, 2)5.5V OLD = 1.65 V max 7550mA I OHDV OHD = 3.85 V min-75-50mA74AC1385/10AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, R L = 500 Ω, Input t r = t f = 3ns)(*) Voltage range is 3.3V ± 0.3V(**) Voltage range is 5.0V ± 0.5VCAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /n (per circuit)TEST CIRCUITC L = 50pF or equivalent (includes jig and probe capacitance)R L = R 1 = 500Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t PLH t PHL Propagation Delay TimeA, B, C to Y3.3(*)1.5 5.510.5 1.514.0 1.515.4ns 5.0(**) 1.5 4.59.0 1.510.0 1.511.0t PLH t PHL Propagation Delay TimeG1 to Y3.3(*)1.5 6.010.5 1.514.0 1.515.4ns5.0(**) 1.5 4.511.0 1.510.0 1.511.0t PLH t PHL Propagation Delay TimeG2A or G2B to Y3.3(*)1.5 5.510.5 1.512.7 1.514.0ns5.0(**) 1.54.59.01.510.01.510.0SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.04pF C PDPower Dissipation Capacitance (note 1)5.0f IN = 10MHz60pF74AC138WAVEFORM 1: PROPAGATION DELAYS FOR INVERTING OUTPUTS (f=1MHz; 50% duty cycle)WAVEFORM 2: P ROPAGATION D ELAYS F OR N ON-INVERTING O UTPUTS(f=1MHz; 50% d uty c ycle)6/1074AC138Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 10/10。

74系列芯片数据手册大全

74系列芯片数据手册大全74系列集成电路名称与功能常用74系列标准数字电路的中文名称资料7400 TTL四2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压缓冲驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相高压缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器7425 双4输入端或非门(有选通端74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门缓冲器74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器7443 4线-10线译码器(余3码输入)7444 4线-10线译码器(余3葛莱码输入) 74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动7449 4线-7段译码器74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门7452 4路2-3-2-2输入与或门7453 4路2-2-2-2输入与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器7460 双4输入与扩展器7461 三3输入与扩展器7462 4路2-3-3-2输入与或扩展器7464 4路4-2-3-2输入与或非门74645 TTL 三态输出八同相总线传送接收器7465 4路4-2-3-2输入与或非门(OC)74670 TTL 三态输出4×4寄存器堆7470 与门输入J-K触发器√7471 与或门输入J-K触发器√7472 与门输入J-K触发器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双上升沿D触发器7476 TTL 带预置清除双J-K触发器7478 双D型触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7487 4位二进制原码/反码7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器74101 与或门输入J-K触发器74102 与门输入J-K触发器74107 双主-从J-K触发器74108 双主-从J-K触发器74109 双主-从J-K触发器74110 与门输入J-K触发器74111 双主-从J-K触发器74112 双下降沿J-K触发器74113 双下降沿J-K触发器74114 双下降沿J-K触发器74116 双4位锁存器74120 双脉冲同步驱动器74121 单稳态触发器74122 可重触发单稳态触发器74123 可重触发双稳态触发器74125 四总线缓冲器74126 四总线缓冲器74128 四2输入端或非线驱动器74132 四2输入端与非门。

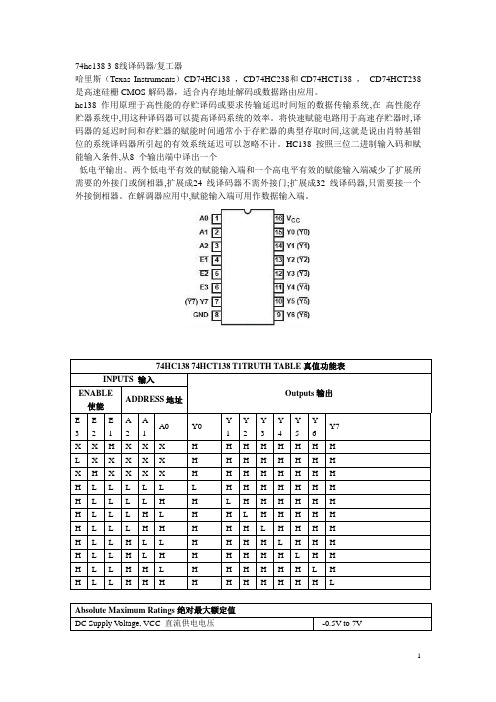

74hc138 74HC138芯片资料 74HC138芯片

74hc138 3-8线译码器/复工器哈里斯(Texas Instruments)CD74HC138 ,CD74HC238和CD74HCT138 ,CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

74HC138 74HCT138 T1TRUTH TABLE真值功能表INPUTS输入Outputs输出ENABLE使能ADDRE SS地址E 3E2E1A2A1A0Y0Y1Y2Y3Y4Y5Y6Y7X X H X X X H H H H H H H HL X X X X X H H H H H H H HX H X X X X H H H H H H H HH L L L L L L H H H H H H HH L L L L H H L H H H H H HH L L L H L H H L H H H H HH L L L H H H H H L H H H HH L L H L L H H H H L H H HH L L H L H H H H H H L H HH L L H H L H H H H H H L HH L L H H H H H H H H H H LAbsolute Maximum Ratings绝对最大额定值DC Supply V oltage, VCC 直流供电电压-0.5V to 7VDC Input Diode Current, IIKFor VI < -0.5V or VI > VCC + 0.5V 输入二极管电流±20mADC Output Diode Current, IOKFor VO < -0.5V or VO > VCC + 0.5V直流输出二极管电流±20mADC Output Source or Sink Current per Output Pin, IOFor VO > -0.5Vor VO < VCC + 0.5V±25mADC VCC or Ground Current, ICC or IGND直流电流虚拟通道连接或接地±50mA Operating Conditions 操作条件Temperature Range (TA) 温度范围-55℃ to 125℃Supply V oltage Range, VCC 电源电压范围,虚拟通道连接HC Types2V to 6V HCT Types 4.5V to 5.5VDC Input or Output V oltage, VI, VO 输入或输出直流电压0V to VCCInput Rise and Fall Time输入上升和下降时间2V 1000ns (Max) 4.5V 500ns (Max) 6V . 400ns (Max)Thermal Information热特性Thermal Resistance (Typical, Note 3)热电阻qJA (℃/W) PDIP 封装90SOIC 封装115SSOP 封装155 Maximum Junction Temperature最高结温150℃Maximum Storage Temperature Range储存温度范围-65℃ to 150℃Maximum Lead Temperature 焊接温度(Soldering 10s)(SOIC -Lead Tips Only)300℃DC SPECIFICA TIONS直流电气规格:Paramete r 参数符号T est Condition测试条件VCC25℃-40℃TO85℃-55℃to125℃Unit单位VI(V)IO(mA)(V)最小典型最大最小最大最小最大High Level Input VIH--21.5-- 1.5- 1.5-V4.5 3.-- 3.1- 3.15-V oltage输入高电平电压15564.2-- 4.2- 4.2-Low LevelInputV oltage输入低电平电压VIL--2--0.5-0.5-0.5V4.5--1.35-1.35- 1.356-- 1.8- 1.8- 1.8High Level OutputV oltage输出高电平电压CMOS Loads VOHVIHorVIL-0.0221.9-- 1.9- 1.9-V4.54.4-- 4.4- 4.4-65.9-- 5.9- 5.9-High Level OutputV oltage输出高电平电压TTL Loads ----------4 4.53.98--3.84- 3.7--5.265.48--5.34- 5.2-Low Level OutputV oltage输出低电平电压CMOS Loads VOLVIHorVIL0.022--0.1-0.1-0.1V4.5--0.1-0.1-0.16--0.1-0.1-0.1Low Level OutputV oltage输出低电平电压TTL Loads ---------4 4.5--0.26-0.33-0.4 5.26--0.26-0.33-0.4InputLeakage Current输入漏电流IIVCCorGND-6--±0.1-±1-±1μAQuiescent Device Current静ICCVCCor06--8-80-160μA态电源电流GN DDC SPECIFICA TIONS直流电气规格(续)Parameter 参数SYMBOL符号T est Condition测试条件VCC25℃-40℃ TO85℃-55℃ TO 125℃Unit单位VI(V)IO (mA)(V)最小典型最大最小最大最小最大High Level Input V oltage VIH-- 4.5 to 5.52--2-2-VLow Level Input V oltage输入低电平电压VIL-- 4.5 to 5.5--0.8-0.8-0.8VHigh Level OutputV oltage输出高电平电压CMOS LoadsVOH VIHorVIL-0.024.54.4--4.4-4.4-VHigh Level OutputV oltage输出高电平电压TTL Loads -4 4.53.98--3.84-3.7-VLow Level OutputV oltage输出低电平电压CMOS Loads VOL VIHorVIL0.024.5--0.1-0.1-0.1VLow Level OutputV oltage输出低电平电压TTL Loads 4 4.5--0.26-0.33-0.4VInput Leakage Current输入漏电流IIVCCandGND0 5.5-±0.1-±1-±1μAQuiescent Device Current ICCVCCorGN0 5.5--8-80-160μADAdditional Quiescent Device Current Per Input Pin: 1 Unit 单位 Load (Note 4)DI CCV C C -2.1-4.5 to5.5- 100 360-450-490μASwitching Specifications Input tr, tf = 6ns 开关规格Parameter 参数SYM BOL 符号T est Condition 测试条件SVC C (V ) 25℃ -40℃ TO 85℃-55℃ TO 125℃ Unit 单位S最小 典型 最大最小最大 最小最大Propagation Delay 传播延迟 Address to Output 地址输出 tPLH, tPHLCL = 50pF2- - 150 -190 - 225 ns4.5 - -30 - 38 - 45 ns CL = 15pF 5 - 13 - - - - - ns CL = 50pF6- -26- 33-38ns应用电路(点击放大):舞台发光二极管灯光可编程时钟定时器电路74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL(LSTTL)系列。

HD74LVC138T中文资料

HD74LVC1383-to-8-line Decoder / DemultiplexerREJ03D0349–0300Z(Previous ADE-205-068B (Z))Rev.3.00Jul. 23, 2004 DescriptionThe HD74LVC138 has three binary select inputs in a 16 pin package. If the device is enabled these inputs determine which one of the eight normally high outputs will go low. Two active low and one active high enables are provided to ease the cascading of decoders. Low voltage and high-speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.Features•V CC = 2.0 V to 5.5 V•All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)•Typical V OL ground bounce < 0.8 V (@V CC = 3.3 V, Ta = 25°C)•Typical V OH undershoot > 2.0 V (@V CC = 3.3 V, Ta = 25°C)•High output current ±24 mA (@V CC = 3.0 V to 5.5 V)•Ordering InformationPart Name Package Type Package Code PackageAbbreviation Taping Abbreviation (Quantity)HD74LVC138FPEL SOP–16 pin (JEITA)FP–16DAV FP EL (2,000 pcs/reel) HD74LVC138TELL TSSOP–16 pin TTP–16DAV T ELL (2,000 pcs/reel) Note: Please consult the sales office for the above package availability.Function TableInputsEnable Select OutputsG1G2A G2B C B A Y0Y1Y2Y3Y4Y5Y6Y7 X X H X X X H H H H H H H H X H X X X X H H H H H H H H L X X X X X H H H H H H H H H L L L L L L H H H H H H H H L L L L H H L H H H H H H H L L L H L H H L H H H H H H L L L H H H H H L H H H H H L L H L L H H H H L H H H H L L H L H H H H H H L H H H L L H H L H H H H H H L H H L L H H H H H H H H H H L H:High levelL:Low levelX:ImmaterialPin ArrangementAbsolute Maximum RatingsItemSymbol Ratings Unit Conditions Supply voltage V CC –0.5 to 6.0V Input diode current I IK –50mA V I = –0.5 V Input voltageV I –0.5 to 6.0V –50V O = –0.5 V Output diode current I OK50mA V O = V CC +0.5 VOutput voltage V O –0.5 to V CC +0.5V Output currentI O±50mA V CC , GND current / pin I CC or I GND 100mA Storage temperatureTstg–65 to +150°CNote:The absolute maximum ratings are values, which must not individually be exceeded, and furthermore, no two ofwhich may be realized at the same time.Recommended Operating ConditionsItemSymbol Ratings Unit Conditions 1.5 to 5.5Data retention Supply voltage V CC 2.0 to 5.5V At operation V I 0 to 5.5V G, A, B, C Input / output voltage V O 0 to V CC V Y 0 to Y 7Operating temperature Ta –40 to 85°C –12V CC = 2.7 VI OH –24mA V CC = 3.0 V to 5.5 V 12V CC = 2.7 VOutput currentI OL24*2mA V CC = 3.0 V to 5.5 VInput rise / fall time t r , t f10ns/VNotes: 1.This item guarantees maximum limit when one input switches.Waveform: Refer to test circuit of switching characteristics.2.Duty cycle ≤ 50%Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)Min Max Unit Test Conditions2.7 to3.6 2.0—V IH 4.5 to 5.5V CC ×0.7—V 2.7 to 3.6—0.8Input voltageV IL4.5 to5.5—V CC ×0.3V 2.7 to 5.5V CC –0.2—I OH = –100 µA 2.7 2.2—3.0 2.4—I OH = –12 mA 3.0 2.0—V OH4.53.8—VI OH = –24 mA2.7 to 5.5—0.2I OL = 100 µA 2.7—0.4I OL = 12 mA3.0—0.55Output voltageV OL4.5—0.55VI OL = 24 mAInput currentI IN 0 to 5.5—±5.0µA V IN = 5.5 V or GND I CC 5.5—20µA V IN = V CC or GNDQuiescent supply current∆I CC 3.0 to 3.6—500µAV IN = one input at(V CC –0.6)V, other inputs at V CC or GND Switching CharacteristicsTa = –40 to 85°CItemSymbol V CC (V)Min Typ Max Unit From (Input)To(Output)2.7—7.010.03.3±0.3 1.5 5.09.0Propagation delay timet PLH t PHL 5.0±0.5— 3.57.5nsG, A, B, C Y 0 to Y 7Input capacitance C IN 2.7— 3.0—pF Output capacitance C O2.7—15.0—pFTest CircuitWaveformsPackage Dimensions RENESAS SALES OFFICESRenesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500 Fax: <1> (408) 382-7501Renesas Technology Europe Limited.Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United KingdomTel: <44> (1628) 585 100, Fax: <44> (1628) 585 900Renesas Technology Europe GmbHDornacher Str. 3, D-85622 Feldkirchen, GermanyTel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11Renesas Technology Hong Kong Ltd.7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong KongTel: <852> 2265-6688, Fax: <852> 2375-6836Renesas Technology Taiwan Co., Ltd.FL 10, #99, Fu-Hsing N. Rd., Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology (Shanghai) Co., Ltd.26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, ChinaTel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952Renesas Technology Singapore Pte. Ltd.1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001© 2004. Renesas Technology Corp., All rights reserved. Printed in Japan.Colophon .1.0。

MC74AC378中文资料

FACT DATA 5-1

元器件交易网

MC74AC378 MC74ACT378

FUNCTIONAL DESCRIPTION

The MC74AC378/74ACT378 consists of six edgetriggered D-type flip-flops with individual D inputs and Q outputs. The Clock (CP) and Enable (E) inputs are common to all flip-flops. When the E input is LOW, new data is entered into the register on the LOW-to-HIGH transition of the CP input. When the E input is HIGH, the register will retain the present data independent of the CP input.

FACT DATA 5-2

元器件交易网

MC74AC378 MC74ACT378

RECOMMENDED OPERATING CONDITIONS

Symbol VCC Vin, Vout Supply Voltage DC Input Voltage, Output Voltage (Ref. to GND) VCC @ 3.0 V tr, tf Input Rise and Fall Time (Note 1) ′AC Devices except Schmitt Inputs VCC @ 4.5 V VCC @ 5.5 V tr, tf TJ TA IOH IOL Input Rise and Fall Time (Note 2) ′ACT Devices except Schmitt Inputs Junction Temperature (PDIP) Operating Ambient Temperature Range Output Current — High Output Current — Low –40 25 VCC @ 4.5 V VCC @ 5.5 V Parameter ′AC ′ACT Min 2.0 4.5 0 150 40 25 10 ns/V 8.0 140 85 –24 24 °C °C mA mA ns/V Typ 5.0 5.0 Max 6.0 5.5 VCC V Unit V

ON Semiconductor MC74AC139 MC74ACT139 数据手册

MC74AC139, MC74ACT139Dual 1-of-4Decoder/DemultiplexerThe MC74AC139/74ACT139 is a high–speed, dual 1–of–4decoder/demultiplexer. The device has two independent decoders,each accepting two inputs and providing four mutually–exclusive active–LOW outputs. Each decoder has an active–LOW Enable input which can be used as a data input for a 4–output demultiplexer. Each half of the MC74AC139/74ACT139 can be used as a function generator providing four minterms of two variables.•Multifunctional Capability•Two Completely Independent 1–of–4 Decoders •Active LOW Mutually Exclusive Outputs •Outputs Source/Sink 24 mA•′ACT139 Has TTL Compatible InputsE O O O OFigure 1. Pinout: 16–Lead Packages Conductors(Top View)PIN ASSIGNMENTH = HIGH Voltage Level L = LOW Voltage Level X = ImmaterialDIP–16N SUFFIXCASE 6481SO–16D SUFFIXCASE 751BDevice Package Shipping ORDERING INFORMATIONMC74AC139N PDIP–1625 Units/Rail MC74AC139D SOIC–1648 Units/Rail MC74AC139DR22500 Tape & Reel TSSOP–16DT SUFFIX CASE 948FMC74AC139DT TSSOP–1696 Units/Rail MC74AC139DTR2TSSOP–16SOIC–162500 Tape & Reel MC74ACT139N PDIP–1625 Units/Rail MC74ACT139D SOIC–1648 Units/Rail MC74ACT139DR22500 Tape & Reel MC74ACT139DT TSSOP–1696 Units/RailSOIC–16See general marking information in the device marking section on page 6 of this data sheet.DEVICE MARKING INFORMATIONEIAJ–16M SUFFIX CASE 966MC74AC139M EIAJ–16MC74AC139MEL EIAJ–162000 Tape & Reel MC74ACT139M EIAJ–16MC74ACT139MELEIAJ–162000 Tape & Reel50 Units/Rail 50 Units/Rail 查询MC74AC139供应商00a 01a 02a 03a 00b 01b 02b 03bNOTE:This diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.Figure 3. Logic DiagramFUNCTIONAL DESCRIPTIONThe MC74AC139/74ACT139 is a high–speed dual 1–of–4 decoder/demultiplexer. The device has two independent decoders, each of which accepts two binary weighted inputs (A 0–A 1) and provides four mutually exclusive active–LOW outputs (O 0–O 3). Each decoder has an active–LOW enable (E). When E is HIGH all outputs are forced HIGH. The enable can be used as the data input for a 4–output demultiplexer application. Each half of the MC74AC139/74ACT139 generates all four minterms of two variables. These four minterms are useful in some applications, replacing multiple gate functions as shown in Figure 4, and thereby reducing the number of packages required in a logic network.E A 0A 1E A 0A 1E A 0A 1E A 0A 1O 0O 1O 2O 3Figure 4. Gate Functions (Each Half)*Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recom-mended Operating Conditions.IN CC2.V IN from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC@**************************************************************CC.*Voltage Range 3.3 V is 3.3 V ±0.3 V.*Voltage Range 5.0 V is 5.0 V ±0.5 V.*All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.*Voltage Range 5.0 V is 5.0 V ±0.5 V.MARKING DIAGRAMSA = Assembly Location WL, L = Wafer Lot YY , Y = YearWW, W = Work WeekAC139AWLYWWMC74AC139N AWLYYWWAC 139ALYWACT139AWLYWWACT 139ALYWMC74ACT139N AWLYYWW DIP–16SO–16TSSOP–16EIAJ–1674AC139ALYW74ACT139ALYWNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.4.DIMENSION B DOES NOT INCLUDE MOLD FLASH.5.ROUNDED CORNERS OPTIONAL.MDIM MIN MAX MIN MAX MILLIMETERSINCHES A 0.7400.77018.8019.55B 0.2500.270 6.35 6.85C 0.1450.175 3.69 4.44D 0.0150.0210.390.53F 0.0400.70 1.02 1.77G 0.100 BSC 2.54 BSC H 0.050 BSC 1.27 BSC J 0.0080.0150.210.38K 0.1100.130 2.80 3.30L 0.2950.3057.507.74M 0 10 0 10 S0.0200.0400.51 1.01____N SUFFIX16 PIN PLASTIC DIP PACKAGECASE 648–08NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION ATMAXIMUM MATERIAL CONDITION.SBM0.25 (0.010)AST DIM MIN MAX MIN MAX INCHESMILLIMETERS A 9.8010.000.3860.393B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2290.244R0.250.500.0100.019____SO–16D SUFFIX16 PIN PLASTIC SOIC PACKAGECASE 751B–05ISSUE JDT SUFFIX16 PIN PLASTIC TSSOP PACKAGECASE948F–01ISSUE ODIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C --- 1.20---0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.180.280.0070.011J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH.PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15(0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.____16X REF EIAJ–16M SUFFIX16 PIN PLASTIC EIAJ PACKAGECASE966–01ISSUE ONOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.Notes11ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others.SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. PUBLICATION ORDERING INFORMATIONJAPAN: ON Semiconductor, Japan Customer Focus Center4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031Phone: 81–3–5740–2700Email:*****************。

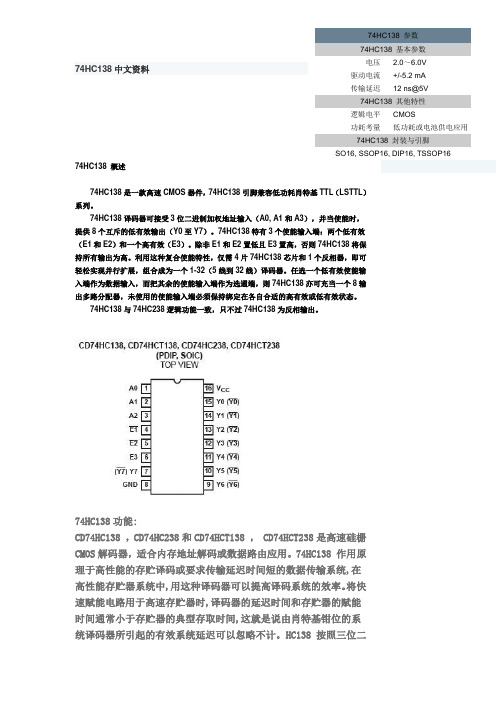

74HC138

74HC138中文资料74HC138 概述74HC138是一款高速CMOS 器件,74HC138引脚兼容低功耗肖特基TTL (LSTTL )系列。

74HC138译码器可接受3位二进制加权地址输入(A0, A1和A3),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

74HC138与74HC238逻辑功能一致,只不过74HC138为反相输出。

74HC138功能:CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅栅CMOS 解码器,适合内存地址解码或数据路由应用。

74HC138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在 高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二74HC138 参数 74HC138 基本参数电压 2.0~6.0V 驱动电流 +/-5.2 mA 传输延迟 12 ns@5V 74HC138 其他特性逻辑电平 CMOS功耗考量低功耗或电池供电应用74HC138 封装与引脚 SO16, SSOP16, DIP16, TSSOP16进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

LOGIC DIAGRAM

A2 A1 A0 E1 E2 E3

07

06

05

04

03

02

01

00

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

FACT DATA 5-3

元器件交易网

MC74AC138 MC74ACT138

DC CHARACTERISTICS

74AC Symbol Parameter VCC (V) TA = +25°C Typ VIH Minimum High Level Input Voltage 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 VOL Maximum Low Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 IIN IOLD IOHD ICC Maximum Input Leakage Current †Minimum Dynamic Output Current Maximum Quiescent Supply Current 5.5 5.5 5.5 5.5 8.0 0.002 0.001 0.001 1.5 2.25 2.75 1.5 2.25 2.75 2.99 4.49 5.49 74AC TA = –40°C to +85°C Unit Conditions

00 01 02 03 04 05 06 07

00 01 02 03 04 05 06 07

00 01 02 03 04 05 06 07 031

Figure a: Expansion to 1-of-32 Decoding

MAXIMUM RATINGS*

Symbol VCC Vin Vout Iin Iout ICC Tstg Parameter DC Supply Voltage (Referenced to GND) DC Input Voltage (Referenced to GND) DC Output Voltage (Referenced to GND) DC Input Current, per Pin DC Output Sink/Source Current, per Pin DC VCC or GND Current per Output Pin Storage Temperature Value –0.5 to +7.0 –0.5 to VCC +0.5 –0.5 to VCC +0.5 ±20 ±50 ±50 –65 to +150 Unit V V V mA mA mA °C

VCC 16 O0 15 O1 14 O2 13 O3 12 O4 11 O5 10 O6 9

1-OF-8 DECODER/ DEMULTIPLEXER

N SUFFIX CASE 648-08 PLASTIC

PIN NAMES A0–A2 E1–E2 E3 O0–O7 Address Inputs Enable Inputs Enable Input Outputs D SUFFIX CASE 751B-05 PLASTIC

1. Vin from 30% to 70% VCC; see individual Data Sheets for devices that differ from the typical input rise and fall times. 2. Vin from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

1 A0

5 E2

6 E3

7 O7

8 GND

LOGIC SYMBOL

A0 A1 A2

E1 E2 E3

O0 O1 O2 O3 O4 O5 O6 O7

FACT DATA 5-1

元器件交易网

MC74AC138 MC74ACT138

FUNCTIONAL DESCRIPTION

The MC74AC138/74ACT138 high-speed 1-of-8 decoder/ demultiplexer accepts three binary weighted inputs (A0, A 1, A2) and, when enabled, provides eight mutually exclusive active-LOW outputs (O0–O7). The MC74AC138/74ACT138 features three Enable inputs, two active-LOW (E1, E2) and one active-HIGH (E3). All outputs will be HIGH unless E1 and E2 are LOW and E3 is HIGH. This multiple enabled function allows easy parallel expansion of the device to a 1-of-32 (5 lines to 32 lines) decoder with just four MC74AC138/ 74ACT138 devices and one inverter (See Figure a). The MC74AC138/74ACT138 can be used as an 8-output demultiplexer by using one of the active LOW Enable inputs as the data input and the other Enable inputs as strobes. The Enable inputs which are not used must be permanently tied to their appropriate active-HIGH or active-LOW state.

* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

元器件交易网

MC74AC138 MC74ACT138

1 of 8 Decoder/Demultiplexer

The MC74AC138/74ACT138 is a high-speed 1-of-8 decoder/demultiplexer. This device is ideally suited for high-speed bipolar memory chip select address decoding. The multiple input enables allow parallel expansion to a 1-of-24 decoder using just three MC74AC138/74ACT138 devices or a 1-of-32 decoder using four MC74AC138/ 74ACT138 devices and one inverter. • • • • • Demultiplexing Capability Multiple Input Enable for Easy Expansion Active LOW Mutually Exclusive Outputs Outputs Source/Sink 24 mA ′ACT138 Has TTL Compatible Inputs

RECOMMENDED OPERATING CONDITIONS

Symbol VCC Vin, Vout Supply Voltage DC Input Voltage, Output Voltage (Ref. to GND) VCC @ 3.0 V tr, tf Input Rise and Fall Time (Note 1) ′AC Devices except Schmitt Inputs VCC @ 4.5 V VCC @ 5.5 V tr, tf TJ TA IOH IOL Input Rise and Fall Time (Note 2) ′ACT Devices except Schmitt Inputs Junction Temperature (PDIP) Operating Ambient Temperature Range Output Current — High Output Current — Low –40 25 VCC @ 4.5 V VCC @ 5.5 V Parameter ′AC ′ACT Min 2.0 4.5 0 150 40 25 10 ns/V 8.0 140 85 –24 24 °C °C mA mA ns/V Typ 5.0 5.0 Max 6.0 5.5 VCC V Unit V

TRUTH TABLE

Inputs E1 H X X L L L L L L L L E2 X H X L L L L L L L L E3 X X L H H H H H H H H A0 X X X L H L H L H L H A1 X X X L L H H L L H H A2 X X X L L L L H H H H O0 H H H L H H H H H H H O1 H H H H L H H H H H H O2 H H H H H L H H H H H Outputs O3 H H H H H H L H H H H O4 H H H H H H H L H H H O5 H H H H H H H H L H H O6 H H H H H H H H H L H O7 H H H H H H H H H H L