VT361716中文资料

使用说明书(4)(1)

VT RTA-168 使用说明书高精度声级计、实时频谱分析仪、失真分析仪……注意:虚仪科技保留在任何时候无需预先通知而对本使用说明书进行修改的权利。

本使用说明书可能包含有文字错误。

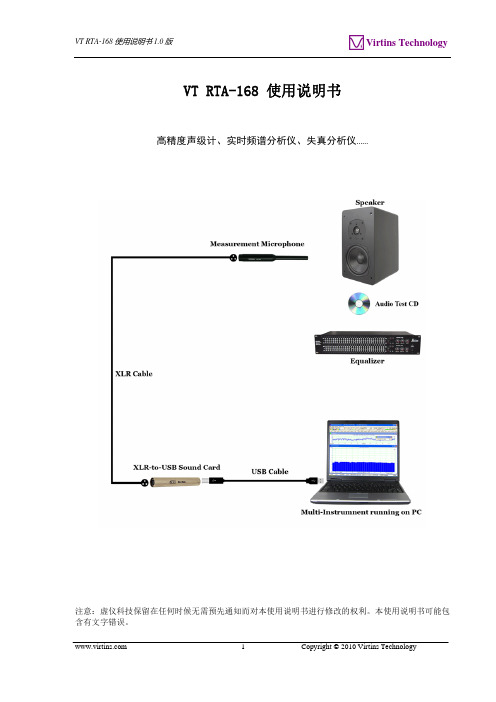

目录1 安装及快速上手指南 (3)1.1系统组成 (3)1.2硬件连接图 (4)1.3安装硬件驱动程序 (6)1.4软件M ULTI-I NSTRUMENT的安装和配置 (6)1.4.1 安装Multi-Instrument软件 (6)1.4.2 启动Multi-Instrument软件 (6)1.4.3 配置Multi-Instrument软件 (7)1.5声级计标定参数的录入和输入增益的调节 (9)1.5.1 在Windows XP或更早的Windows版本下 (10)1.5.2 在Windows Vista下 (10)1.5.3 在Windows 7下 (11)1.5.4 通过硬件增益开关调节输入增益 (13)1.6最常用的20种测量的参数设置 (14)1.7音频测试CD音轨列表 (16)1.8操作注意事项 (18)1.9话筒频率补偿 (18)2 性能指标 (19)2.1VT RTA-168系列的硬件配置 (19)2.2VT RTA-168性能指标 (19)2.3测量话筒ECM999性能指标 (19)2.4测量话筒EMM-6性能指标 (21)2.5VT XLR-TO-USB P RE 性能指标 (22)2.6M ULTI-I NSTRUMENT软件性能指标 (24)3 MULTI-INSTRUMENT软件使用许可证信息 (28)3.1软件使用许可证类别 (28)3.2软件使用许可证升级 (29)3.3同级软件版本升级 (29)4 产品质保 (29)5 免责声明 (30)1 安装及快速上手指南1.1 系统组成一套标准的VT RTA-168系统包括以下部件:1)测量话筒及其附件(挡风罩和话筒夹子)话筒挡风罩话筒夹子2)XLR转USB声卡3)USB电缆(1.5米)4)CD(包含经加密的Multi-Instrument软件)5)USB硬匙(包含Multi-Instrument标准版软件使用许可证)6)音频测试CD(包含一系列的测试信号和噪声)7) 3.5毫米立体声电缆(1.8米)8) 黑色软质工具小包9)一对一的声压标定数据10)一对一的话筒标定数据 (仅RTA-168B提供)1.2 硬件连接图有两种连接方式,区别只在于在测量话筒与XLR转USB声卡之间采用或不采用XLR电缆来连接。

AA16中文资料

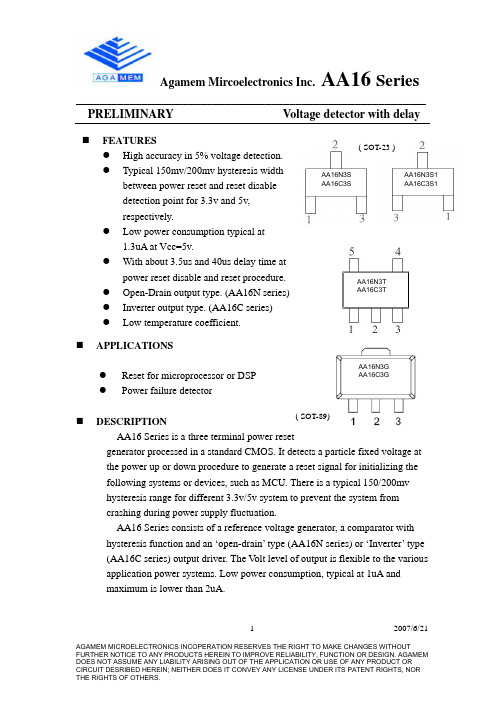

2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT1___________________________________________________________ PRELIMINARY Voltage detector with delay`APPLICATIONSz Reset for microprocessor or DSP z Power failure detectorDESCRIPTIONAA16 Series is a three terminal power resetgenerator processed in a standard CMOS. It detects a particle fixed voltage at the power up or down procedure to generate a reset signal for initializing the following systems or devices, such as MCU. There is a typical 150/200mv hysteresis range for different 3.3v/5v system to prevent the system from crashing during power supply fluctuation.AA16 Series consists of a reference voltage generator, a comparator with hysteresis function and an ‘open-drain’ type (AA16N series) or ‘Inverter’ type (AA16C series) output driver. The V olt level of output is flexible to the various application power systems. Low power consumption, typical at 1uA and maximum is lower than 2uA.FEATURESz High accuracy in 5% voltage detection. z Typical 150mv/200mv hysteresis widthbetween power reset and reset disable detection point for 3.3v and 5v, respectively.z Low power consumption typical at1.3uA at Vcc=5v.z With about 3.5us and 40us delay time atpower reset disable and reset procedure. z Open-Drain output type. (AA16N series)z Inverter output type. (AA16C series) z Low temperature coefficient. ( SOT-25 )AA16N3G AA16C3GAA16N3T AA16C3TAA16N3S AA16C3SAA16N3S1 AA16C3S1( SOT-23 )( SOT-89)2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT2___________________________________________________________ PRELIMINARY Voltage detector with delaySOT-23 SOT-89 PIN DESCRIPTIONSymbol Pin-No TypeFunctionV out 1 O Power Reset signal output. It’s an Open –Drain or Inverter outputtype. Its output state level like belowReset : Low ; Reset disable : High ImpedanceVcc 2 Supply Power GND 3Ground SOT-25 PIN DESCRIPTIONSymbol Pin-No TypeFunctionNc 1 O Not Connect Sub 2 substrate GND 3 GroundV out 4 Power Reset signal output. It’s an Open –Drain or Inverter output type. Its output state level like belowReset : Low; Reset disable : High ImpedanceVcc 5 Supply PowerBLOCK DIAGRAM2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT3Agamem Mircoelectronics Inc. AA16 Series___________________________________________________________ PRELIMINARY Voltage detector with delayELECTRICAL CHARACTERISTICSABSOLUTE MAXIMUM RATINGS (See NOTE) RatingParameter SymbolMINTYPMAXUNIT CONDITIONSupply V olateg Vcc -0.3 7 V Output V olatge V OUT -0.3Vcc+0.3VTa = +25 ; GND = 0V Operating Ambient Temperature Ta -20 70 Storage TemperatureTs -55 125NOTE: Stress above those listed under “Absolute Maximum Rating” may cause the device permanent damage. This is a stress rating only factor and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for an extending period of time may affect the reliability of the device.RECOMMENDED OPERATING CONDITIONS Ta = 25* Output can’t be described because the system isn’t stable when the supply voltage Vcc is less than 1.5V2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT4___________________________________________________________ PRELIMINARY Voltage detector with delaySUPPLY CURRENT MEASUREMENT CHART* V out is an ‘Open-Drain’ output type. A resistance between it and Vcc is necessary to pick it up.* V out is an ‘Inverter’ output type. No resistance between it and Vcc.2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT5___________________________________________________________ PRELIMINARY Voltage detector with delayOUTPUT CHARACTERISTIC TESTING CONDITION* V out is an ‘Open-Drain’ output type. A resistance between it and Vcc isnecessary to pick it up.* V out is an ‘Inverter’ output type. No resistance between it and Vcc.2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT6___________________________________________________________ PRELIMINARY Voltage detector with delayFig-1 : Reset & Reset Disable Transfer Point* V RSD , reset disable voltage, is the detected output point when Vcc is increasing. V RS , resetvoltage, is the detected output point when Vcc is decreasing. T RSD and T RS is the correspondingdelay time between the V RSD and V RS to the rising edge and falling edge of V out.** After V out is settled, its rising and falling slope should be equal to the slope of Vcc because there is only a resistance between Vcc and V out. The maximum value of V out is equal to the one of Vcc, too.t2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT7___________________________________________________________ PRELIMINARY Voltage detector with delayFig-2 : Hysteresis Chart* Output can’t be described correctly because the system isn’t stable when the supply voltage Vcc is less than 1.5V** In the Vcc increasing procedure, V out equal to Vcc as Vcc is larger than V RSD . In the Vcc decreasing procedure, V out won’t be change to Vcc until Vcc is smaller than V RS . The width between V RS and V RSD is so called ‘Hysteresis range’V2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT8___________________________________________________________ PRELIMINARY Voltage detector with delayFig-3 : Output Delay Timing ChartThere existing an output identification range as Vcc is less than 1.5V sounder the testing condition this area should be keep off.2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT9Agamem Mircoelectronics Inc. AA16 Series___________________________________________________________ PRELIMINARY Voltage detector with delaySOT-23 OUTLINEDRAWINGDIMENSIONS IN MILLIMETERSSYMBOLS MIN NOM MAX A 1.00 1.10 1.30 A1 0.00 - - - 0.10 A2 0.70 0.80 0.90 0.35 0.40 0.50 C 0.10 0.15 0.25D 2.70 2.90 3.10E 1.40 1.60 1.80 - - - 1.90(TYP)- - - H 2.60 2.80 3.000.37 - - - - - - 1 1 5 9NOTES: 1. Package body sizes excludemold flash protrusions orgate burrs 2. Tolerance 0.1000 (4 mil) unless otherwise specified3. Coplanarity:0.10004. Dimension l is measured in gage plane2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT10Agamem Mircoelectronics Inc. AA16 Series___________________________________________________________ PRELIMINARY Voltage detector with delaySOT-25 OUTLINE DRAWINGDIMENSIONS IN MILLIMETERSSYMBOLS MIN NOM MAX A 1.00 1.10 1.30 A1 0.00 - - - 0.10 A2 0.70 0.80 0.90 0.35 0.40 0.50 C 0.10 0.15 0.25 D 2.70 2.90 3.10 E 1.50 1.60 1.80 - - - 1.90(TYP)- - - H 2.60 2.80 3.00 0.37 - - - - - -1 1 5 9 - - - 0.95(TYP)- - -NOTES:1. Package body sizes excludemold flash protrusions or gate burrs2. Tolerance 0.1000 (4mil) unless otherwise specified3. Coplanarity:0.10004. Dimension l is measured ingage plane2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT11___________________________________________________________ PRELIMINARY Voltage detector with delaySOT-89 OUTLINE DRAWINGDIMENSIONS INMILLIMETERSDIMENSIONS ININCHESSYMBOLSMIN NOM MAX MINNOM MAX A 1.40 1.50 1.60 0.055 0.059 0.063A1 0.80 1.04 --- 0.031 0.041 --- b 0.36 0.42 0.48 0.014 0.016 0.018b1 0.41 0.47 0.53 0.016 0.018 0.020C 0.38 0.40 0.43 0.014 0.015 0.017D 4.40 4.50 4.60 0.173 0.177 0.181 D1 1.40 1.60 1.75 0.055 0.062 0.069--- --- 4.25 --- --- 0.1672.40 2.50 2.60 0.094 0.098 0.1022.903.00 3.10 0.114 0.118 0.122 0.35 0.40 0.45 0.014 0.016 0.018S 0.65 0.75 0.85 0.026 0.030 0.0341.40 1.50 1.60 0.054 0.059 0.063NOTES:1. Package body sizes excludemold flash protrusions or gate burrs2. Tolerance 0.1000 (4mil) unless otherwise specified3. Coplanarity:0.10004. Dimension l is measured in gage plane2007/6/21AGAMEM MICROELECTRONICS INCOPERATION RESERVES THE RIGHT TO MAKE CHANGES WITHOUT12___________________________________________________________ PRELIMINARY Voltage detector with delayORDERING INFORMATIONNote: For there being two kinds of pin assignment in SOT-23 package, we mark S and S1 to distinguish.S S1AA16 X Y Z1。

AVXX16中文资料

GENERAL DESCRIPTION:The AVH316B, AVH316C, AVH316D, AV0716C, AV0716D, AV1416D, AV2116A, AV2816A is a single-chip synthesizing CMOS VLSI that can synthesize voice up to 3.5,7,14,21,28 seconds using APLUS qualified coding algorithm (LOGPCM).Customer speech data will be edited and programmed into ROM by changing one mask during one mask during the device fabrication.FEATURES:1. Single power supply can operate from2.4v through 5v.2. The total voice duration is about3.5,7,14,21,28,42 seconds could be partitioned up to 16 voice sections.Each voice section could have 4 playing lengths; the longest one is the origional voice+mute length.3. Voice + mute length could up to 22 seconds ( 11 seconds in AVH316 ) (6k sampling rate) for each voice section.4. One 112 voice-steps table, could be partitioned up to 16 subtables of steps.5. 5 mask option of playback speed : 1> 4.3K ; 2> 5.0K ; 3>6.0K ; 4>7.5K ; 5> 10.0K ( Hz )6. 1 trigger input (TG): with resistive schmitt input (270K---1M) for CDS interface.sequential function : once the input was triggered sequentially the device will response by one subtable of voice_stepsequentially and cyclically , from subtable_m ( m= 1 -16 ) to user defined subtable_n ( n= 1 - 16 ) .random function : Once the input was trigger , the device will response from subtable_m ( m: 1 - 16 ) to subtable_n( n: 1 - 16 ) at random .snooze function : use 2 subtables : 1st stores ringing voice , playing when time's up.2nd stores ( greeting sound + ) snooze time .7.Has two debounce time : 10 ms, 50 us. with following mask optionA>50us B>10ms C>IO1(VDD-50us,GND-10ms) D>IO2(VDD-50us,GND-10ms) E>IO3(VDD-50us,GND-10ms)C,D,E;could only be selected when IO1,IO2,IO3 are mask_option as control input .8. Automatic Rosc selection : enable - the device will use external Rosc if it has external Rosc ; the device will use internal Roscautomatically if it hasn't external Rosc . ( It must be determined before operation )disable - use external Rosc only . IO2 - VDD : disable GND : enableInternal Rosc options : (mask option)For VH316B ,AVH316C ,AVH316D ,AV0716C ,AV0716D ,AV1416D ,AV2116A , AV2816A :playbackA B C D E F G H I J K L Mspeed(khz)4.38.98.67.97 6.35.8 5.4 5.1 4.7 4.3 4.1 3.9 3.6510.3109.28.27.3 6.8 6.3 5.9 5.55 4.8 4.6 4.2612.412119.88.88.17.57.1 6.66 5.7 5.557.515.51513.812.31110.19.48.98.37.57.1 6.9 6.31020.72018.316.314.713.512.511.811109.59.28.39. Playing mode :EDGEL/LEVEL , HOLD/UNHOLD , RETRIGGER/IRRETRIGGER with following mask options :EDGE/LEVEL HOLD/UNHOLD RETRIGGERING/IRRETRIGGERA>EDGE A>HOLD A>IRRETRIGGERB>LEVEL B>UNHOLD B>RETRIGGERC>IO1(VDD-edge.GND-level) C>IO1(VDD-hold,GND-unhold) C>IO1(VDD-irretrigger,GND-retrigger)D>IO2(VDD-edge.GND-level) D>IO2(VDD-hold,GND-unhold) D>IO2(VDD-irretrigger,GND-retrigger)E>IO3(VDD-edge.GND-level) E>IO3(VDD-hold,GND-unhold) E>IO3(VDD-irretrigger,GND-retrigger)C, D, E could only be selected when IO1,IO2,IO3 are mask_option as control input .10. 3 I/O PINS WITH FOLLOWING OPTIONS:* IO1 * IO2 * IO3A>COUT B>STOPH C>STOPL A>PWM1 B>STOPH C>STOPL A>PWM2 B>STOPH C>STOPLD>BUSYH E>BUSYL F>6HZ D>BUSYH E>BUSYL F>6HZ D>BUSYH E>BUSYL F>6HZG>DYNA1/4 H>DYN2/4 I>DYN3/4 G>DYNA1/4 H>DYN2/4 I>DYN3/4 G>DYNA1/4 H>DYN2/4 I>DYN3/4J>USED AS CONTROL INPUT J>USED AS CONTROL INPUT J>USED AS CONTROL INPUTItem_F : 0.75Hz or 1.5Hz or 3Hz or 6Hz(mask option)Item_B~I : with one subtable enable status option for IO1, IO2, IO3.COUT : 3 current output levels, with 4 mask options (1.5mA;3mA;4.5mA;IO3<GND-3mA,VDD-4.5mA>).PWM1, PWM2 : must be selected on the same time ,direct driving buzzer or 8 or 32 or 64 ohm speaker.STOPH, STOPL : 40 ms high/low output when device stop playing.(drive 1.8 mA,sink 10mA;3v).BUSYH, BUSYL : high/low output during device playing (drive 1.8 mA,sink 10mA;3v).6Hz/3Hz, DYNA1/4, 2/4, 3/4 : LED driving. (drive 1.8 mA, sink 10mA;3v)Used as control input : internal pull GND (0.5uA,3V)For all the IO options : the dynamic should choice same level.If IO2 and IO3 are both at 6Hz(3Hz), they will flash alternatively.When used as control input, they could be used to control following options by bonding or toggle switch.EDGE/LEVEL, HOLD/UNHOLD, RETRIGGER/IRRETRIGGER, DEBOUNCE 10ms/50us㆒般規格:AVH316B ,AVH316C ,AVH316D ,AV0716C ,AV0716D ,AV1416D ,AV2116A,AV2816A 乃㆒單晶片CMOS VLSI語音合成器,它以LOGPCM編碼方式,合成長達3.5、7、14、21、28、42 秒之語音。

iW3617 datasheet

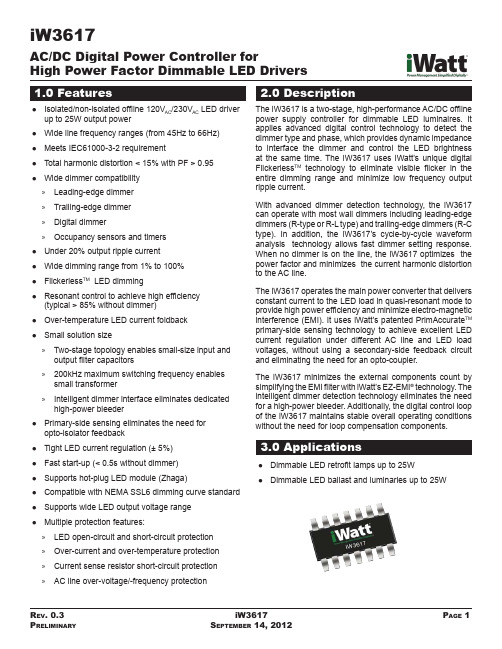

High Power Factor Dimmable LED Drivers●Isolated/non-isolated offline 120VAC /230VACLED driverup to 25W output power●Wide line frequency ranges (from 45Hz to 66Hz)●Meets IEC61000-3-2 requirement●Total harmonic distortion < 15% with PF > 0.95●Wide dimmer compatibilityx Leading-edge dimmerx Trailing-edge dimmerx Digital dimmerx Occupancy sensors and timers●Under 20% output ripple current●Wide dimming range from 1% to 100%●Flickerless TM LED dimming●Resonant control to achieve high efficiency(typical > 85% without dimmer)●Over-temperature LED current foldback●Small solution sizex Two-stage topology enables small-size input and output filter capacitorsx200kHz maximum switching frequency enables small transformerx Intelligent dimmer interface eliminates dedicated high-power bleeder●Primary-side sensing eliminates the need foropto-isolator feedback●Tight LED current regulation (± 5%)●Fast start-up (< 0.5s without dimmer)●Supports hot-plug LED module (Zhaga)●Compatible with NEMA SSL6 dimming curve standard ●Supports wide LED output voltage range●Multiple protection features:x LED open-circuit and short-circuit protectionx Over-current and over-temperature protectionx Current sense resistor short-circuit protectionx AC line over-voltage/-frequency protection The iW3617 is a two-stage, high-performance AC/DC offline power supply controller for dimmable LED luminaires. It applies advanced digital control technology to detect the dimmer type and phase, which provides dynamic impedance to interface the dimmer and control the LED brightness at the same time. The iW3617 uses iWatt’s unique digital Flickerless TM technology to eliminate visible flicker in the entire dimming range and minimize low frequency output ripple current.With advanced dimmer detection technology, the iW3617 can operate with most wall dimmers including leading-edge dimmers (R-type or R-L type) and trailing-edge dimmers (R-C type). In addition, the iW3617’s cycle-by-cycle waveform analysis technology allows fast dimmer setting response. When no dimmer is on the line, the iW3617 optimizes the power factor and minimizes the current harmonic distortion to the AC line.The iW3617 operates the main power converter that delivers constant current to the LED load in quasi-resonant mode to provide high power efficiency and minimize electro-magnetic interference (EMI). It uses iWatt’s patented PrimAccurate TM primary-side sensing technology to achieve excellent LED current regulation under different AC line and LED load voltages, without using a secondary-side feedback circuit and eliminating the need for an opto-coupler.The iW3617 minimizes the external components count by simplifying the EMI filter with iWatt’s EZ-EMI® technology. The intelligent dimmer detection technology eliminates the need for a high-power bleeder. Additionally, the digital control loop of the iW3617 maintains stable overall operating conditions without the need for loop compensation components.●Dimmable LED retrofit lamps up to 25W●Dimmable LED ballast and luminaries up to 25WHigh Power Factor Dimmable LED DriversBooster ConverterFlyback ConverterFigure 3.1 : iW3617 Simplified SchematicHigh Power Factor Dimmable LED DriversiW3617High Power Factor Dimmable LED DriversNotes:Note 1. ψJB [Psi Junction to Board] provides an estimation of the die junction temperature relative to the PCB surfacetemperature. This data is measured at the ground pins (pin 8 and pin 9) without using any thermal adhesives.Absolute maximum ratings are the parameter values or ranges which can cause permanent damage if exceeded. For maximum safe operating conditions, refer to Electrical Characteristics in Section 6.0.High Power Factor Dimmable LED Drivers V = 12 V, -40°C ≤ T ≤ 85°C, unless otherwise specified (Note 1)High Power Factor Dimmable LED DriversV = 12 V, -40°C ≤ T ≤ 85°C, unless otherwise specified (Note 1)High Power Factor Dimmable LED DriversNotes:Note 1. Adjust V CC above the start-up threshold before setting at 12V.Note 2. Operating frequency varies based on the line and load conditions. See the Theory of Operation section for moredetails.Note 3. These parameters refer to digital preset values, and they are not 100% tested.V CC = 12 V, -40°C ≤ T A≤ 85°C, unless otherwise specified (Note 1)High Power Factor Dimmable LED DriversV CC (V)V C C S u p p l y S t a r t -u p C u r r e n t (µA )Figure 7.1 : V CC vs. V CCSupply Start-up CurrentAmbient Temperature (°C)V C C S t a r t -u p T h r e s h o l d (V )11.811.6Figure 7.2 : Start-Up Threshold vs. TemperatureAmbient Temperature (°C)% D e v i a t i o n o f S w i t c h i n g F r e q u e n c y f r o m I d e a l0.3 %Figure 7.3 : % Deviation of Switching Frequency toIdeal Switching Frequency vs. Temperature1.982.001.992.01Ambient Temperature (°C)I n t e r n a l R e f e r e n c e V o l t a g e (V )Figure 7.4 : Internal Reference vs. TemperatureHigh Power Factor Dimmable LED DriversFigure 8.1 : iW3617 Functional Block DiagramThe iW3617 consists of two function blocks: ●Power factor correction and dimmer interface ●LED current regulation and dimming controlThe power factor correction (PFC) and dimmer interfacing block control the boost converter as the first power stage in the iW3617 system (shown in Figure 3.1). It analyzes the rectified AC waveform and determines whether a dimmer is connected on the line. If no dimmer is connected, the block switches the boost BJT (B DRV pin) for PFC and stores the energy in the boost output capacitor. The PFC operation is based on the input voltage (V IN pin), the boost output voltage (V CB pin), and the magnetic flux status of the boost inductor (BV SENSE pin). If a dimmer is connected, the block detects the type of dimmer by analyzing the shape of the rectified AC waveform (V IN pin). It then provides dynamic impedance to interface the dimmer by driving the boost BJT (B DRV pin). The purpose is to match the load requirement of the dimmerwhile storing the energy in the boost output capacitor. To provide accurate impedance, the gain (β) of the boost BJT is calibrated (BI SENSE pin). The block also measures the dimmer phase conduction angle to determine the dimming level (refer to Section 9.2 for details).The LED current regulation and dimming control block control the flyback or buck/boost converter as the second power stage (shown in Figure 3.1). It switches the flyback MOSFET (F DRV pin) to supply constant current to LED load from the energy stored in the boost output capacitor. The constant current regulation algorithm is based on the information of the transformer primary-side peak current (FI SENSE pin) and magnetic flux status of transformer (FV SENSE pin). The block also dims LEDs by adjusting the output current based on dimmer phase conduction angle provided by power factor correction and dimmer interface block. (refer to Section 9.2 for details).V IN BV SENSEV CCV T BI SENSEF DRVV CBCFGB DRVFV SENSE FI SENSEPGND AGNDASUHigh Power Factor Dimmable LED Drivers9.1 System Start UpThis section provides information about iW3617 system start up, which include the IC startup, wall dimmer detection, and the LED current soft start.9.1.1 IC StartupWhen AC voltage is applied, the boost output capacitor in (C3 in Figure 11.1) is charged to the peak of line voltage. ASU pin is open by default so that ASU BJT (Q3 in Figure 11.1) is turned on and V CC capacitors (C8 and C9 in Figure 11.1) is charged through ASU resistor (R9 in Figure 11.1) and ASU BJT. When the V CC voltage reaches start-up threshold V CC(ST), the iW3617’s control logic is activated and the IC starts up. The ASU pin is kept open and the ASU circuit continues charging V CC until 50ms after the main flyback converter starts.Start-up SequencingFigure 9.1 : Start-up Sequencing Diagram9.1.2 Wall Dimmer DetectionThere are two basic categories of phase- cut wall dimmers: leading-edge dimmers and trailing-edge dimmers. If the AC voltage rises at the phase-cut edge, the dimmer is calledleading-edge dimmer (shown in Figure 9.2). Otherwise it is called trailing-edge dimmer (shown in Figure 9.3). Normallyspeaking, leading-edge dimmer is TRIAC based (R-type,RL-type); trailing-edge dimmer is MOSFET or IGBT based(RC-type).AC line before Wall-dimmerAC line after Wall-dimmerFigure 9.2 : Leading-Edge Wall Dimmer WaveformsAC line after Wall-dimmerAC line before Wall-dimmerFigure 9.3 : Trailing-Edge Wall Dimmer WaveformsThe dimmer detection stage occurs in the iW3617 immediately after IC starts up. The iW3617 is driving the boost BJT (Q2 in Figure 11.1) constantly on to do currentsinking during the wall dimmer detection. The purposes of current sinking at startup are: ●Calibrate the sinking current to 200mA to compensatefor the BJT gain variation. This 200mA current sinking is used to latch the leading-edge dimmer during the phase-cut in normal operation. ●Place a low impedance resistance on the AC line toaccurately detect whether a dimmer is connected and the type of dimmer connected.The dimmer type can be determined by looking at the derivative of the input AC voltage. A large positive derivative value indicates a leading-edge dimmer. Otherwise, trailing- edge dimmer or no dimmer is detected.High Power Factor Dimmable LED Drivers Once the dimmer type is determined, the iW3617 needs toqualify the AC input signal before delivering current to theLED load. If under any condition the iW3617 does not seethe peak of VIN signal above VIN_ST(MIN)for two consecutiveAC half-cycles or the AC line frequency is out of range, the AC input signal is considered as unqualified. The iW3617 will continuously monitor the AC input signal until it sees a qualified AC input signal and then starts to deliver currentto the LED load. Or if the VCC drops under VCC(UVL)in thisprocess, the iW3617 will reset and the VCC voltage willcharge up again for a fresh start-up.9.1.3 LED Current Soft-StartAfter the iW3617 qualifies the AC input signal, the flyback converter will immediately start to deliver constant current to the LED load. A soft-start algorithm is applied to the flyback converter to gradually ramp up the LED current, thus reducing the stress on the LEDs. If no dimmer or a trailing-edge dimmer is detected, the output current will ramp up to the target current level within several AC half cycles. If a leading-edge dimmer is detected, the ramp up of the LED current is slower to avoid current over-shoot or under-shoot. This is because the leading-edge dimmer’s phase conduction angle is usually not stable when the load on the dimmer is light.If a dimmer is connected, the boost converter will start immediately into leading-edge or trailing-edge mode operation (refer to Section 9.31 and 9.32 for details) to interface the dimmer. If no dimmer is connected, the boost converter will start PFC operation (refer to Section 9.33 for details).9.2 Phase Measurement and DimmingCurveThis section provides information about iW3617 phase measurement and dimming curve.9.2.1 Phase MeasurementDimmer phase conduction angle is measured every AC half cycle. Dimmer phase is determined by the time periodthat VIN stays above the zero-crossing threshold (tCROSS) asshown in Figure 9.4. The threshold is 140mV.V CROSStPERIODtCROSSFigure 9.4 : Dimmer Phase MeasurementAnd the dimmer phase ratio (D ratio) is calculated as:Dimmer Phase Ratio (D ratio) = tCROSS/tPERIOD(9.1)The tPERIODis the period of AC half cycle, which is measured by the time span between the moments that VINrises above the 140mV reference in two consecutive AC half cycles. If the D ratio is above 90%, the iW3617 considers no dimmer is on the line.9.2.2 Dimming CurveThe iW3617 dims the LED by reducing the output current to a certain percentage of the LED current level when there is no dimmer, which is called dimming percentage. A mapping between the D ratio and the dimming percentage is pre-determined in the iW3617. There are two different mapping options, or dimming curves, that can be selected with the CFG pin (refer to Section 9.5 for details). Both dimming curves fall within the limits of the NEMA SSL6 standard (as shown in Figure 10.6). The iW3617 updates the dimming percentage based on the D ratio measurement every AC half cycle to ensure fast dimmer response.9.3 Dimmer Interface and Power FactorCorrection Block OperationThis section provides information about iW3617 dimmer interface and power factor correction block’s operation, which includes leading-edge dimmer mode, trailing-edge dimmer mode, no dimmer mode, and transition between these operation modes.9.3.1 Leading-Edge Dimmer ModeIf a leading-edge dimmer is detected on the line, the boost converter is operated in leading-edge dimmer mode. This mode provides dynamic impedance matching for the leading-edge dimmers. The leading-edge mode operation can be split into five intervals, as shown in Figure 9.5.During interval 0, the TRIAC in the leading-edge dimmer is turned off and the dimmer requires a low impedance load to charge its internal timing circuit. The boost BJT (Q2 in Figure 11.1) is driven in current sink mode to provide such low impedance load. When the TRIAC inside the dimmer is fired, the operation enters interval 1. Interval 1 is a short period of time after the TRIAC fires. The boost BJT is kept in current sink mode to provide 200mA latching current for the TRIAC. Then the operation enters interval 2. The boost BJT is in switching mode during interval 2. Interval 2 ends at 90˚ of the phase angle. During Interval 2, the iW3617 boosts the energy into the boost output capacitor and provides the holding current of the TRIAC at the same time. Interval 3 is a 400µs blanking time to ensure the TRIAC turns off after enough energy is boosted into the boost output capacitor. Then the operation enters interval 4 in which the boost BJT is in light duty-cycle switching mode to discharge the EMI filter capacitors of the LED driver.9.3.2 Trailing-Edge Dimmer ModeIf a trailing-edge dimmer is detected on the line, the boost converter is operated in trailing-edge dimmer mode. This mode provides dynamic impedance matching for trailing-edge dimmers. The operation can be split into four intervals, as shown in Figure 9.6.During interval 0, the boost BJT is driven in current sink mode to reset the dimmer with a low impedance load. Interval 1 begins as the VINrises above the zero crossing reference. The boost BJT is driven in switching mode to boost energy into the boost output capacitor. Then interval 2 starts at a short period of time before the phase-cut edge to increase the switching duty cycle as a transition state between interval 1 and interval 3. Interval 3 begins right at the phase-cut edge. The boost BJT switches with four times of the duty cycle as in interval 1 to quickly discharge the EMI capacitor inside the dimmer so as to ensure the accurate phase.9.3.3 No Dimmer Mode (PFC Operation)If there is no dimmer on the line, boost converter is operated in PFC mode for optimal power factor and minimum harmonic distortion. The iW3617 switches the boost BJT in valley mode switching to minimize the switching loss and EMI. Input current will follow the input voltage as shown in Figure 9.7.V AC InductorCurrentInputCurrentFigure 9.7 : No Dimmer Boost Mode OperationThe iW3617’s PFC algorithm is based on fixed on-time switching with the compensation of dead-time after the boost inductor resets. The dead-time is measured from the moment that boost inductor resets (determined by BVSENSEHigh Power Factor Dimmable LED Driverspin) to the following boost BJT turn-on moment (determined by B DRV pin). To maximize the power efficiency, the boost output capacitor voltage is set to be 30V above the peak AC line voltage for 230V AC input and 15V above for 120V AC input.9.3.4 Transition Between Operation Modes The iW3617 constantly monitors the derivative of the V IN signal every AC half cycles to ensure the boost converter’s operation is in the correct mode. The mode of the operation is continuously updated based on the latest detected dimmer type.The iW3617 also monitors dimmer existence by looking atthe D ratio. If the D ratio is greater than 90% at any time, theboost converter will enter the No Dimmer mode immediately. 9.4 LED Current Regulation andDimming Control Block OperationThis section provides information about iW3617 LED current regulation and dimming control block operation.9.4.1 Cycle-by-Cycle LED Current Regulation The LED current regulation and dimming control block incorporates the iWatt-patented PrimAccurate TM technology. Constant current is guaranteed regardless of the input voltage (boost output capacitor voltage) or the output voltage (LED load forward voltage) of the flyback converter. Figure 9.8 shows the basic principle of this constant current regulation algorithm.I PI Ot ONt OFFt SFigure 9.8 : Constant Current RegulationThe flyback converter is operated in critical discontinuousconduction mode (CDCM). When the flyback MOSFET (Q1 in Figure 11.1) turns on, the transformer primary winding current ramps up linearly and energy builds up in the transformer. The iW3617 turns off the MOSFET when the primary winding current reaches the peak current regulation level. At this moment, the transformer maintains the magnetic flux so that the energy in the transformer generates the secondary winding current that equals to the peak primary winding current multiplied by primary-secondary turns-ratio. Then the secondary winding current ramps down linearly until all the energy in transformer is discharged. After the energy in the transformer is discharged, the iW3617 starts the next switching cycle. The LED load current is the average of the saw-tooth shaped secondary winding current.The LED load current can be determined by an equation asshown below.I OUT = 0.5 × N TR × I PK × T R / T P(9.2)where I PK is the peak of primary winding current. N TR is the primary-secondary turns ratio. T R is the secondary winding current ramp-down time, or the transformer reset time. T P isthe entire switching period.The I PK is determined by the voltage generated on thecurrent-sense resistor: I PK = V PK / R S . Therefore, the equation can be written as:I OUT = 0.5 × N TR / R S × (V PK × T R / T P )(9.3)The iW3617 measures T R and T P on a cycle-by-cycle basis and controls V PK so that the K CC = V PK × T R / T P is always a constant. The K CC is an internally defined constant that equals to 0.7V. Therefore, the I OUT can be determined by the turns-ratio and current sense resistor at the design time of the application circuit. 9.4.2 Dimming ControliW3617 has two dimming scheme options which can be selected by the CFG pin (refer to Section 9.5 for details). The first one is pulse width modulation (PWM) dimming. The second one is constant current pulse frequency modulation (CC-PFM) dimming. ●PWM Dimming ModeFrom 100% to 25% dimming percentage, the iW3617 employs the same constant current regulation algorithm as described in section 9.4.1 while reducing the K CC constant. As a result, the I OUT will proportionally decrease as the K CC decreases. In this process, the switching frequency of the flyback converter will increase. The maximum switching frequency is clamped at 200kHz.At 25% dimming percentage, the iW3617 will clamp the K CC value and switch to the 630Hz PWM dimming. FurtherHigh Power Factor Dimmable LED Driversdimming is achieved by only activating the flyback converter during a certain percentage of time in every 630Hz period. ●CC-PFM Dimming ModeFrom 100% to 25% dimming percentage, the iW3617 operates in the same K CC -reduction dimming method as described in PWM dimming, except that the frequency clamp changes linearly from 200kHz at 100% dimming percentage to 50kHz at 25% dimming percentage. Below 25% dimming percentage, the iW3617 will switch to the CC-PFM mode, which keeps the V PK a constant and increase the T P to achieve further dimming.9.5 CFG PinThe CFG pin is used to select between the two dimming modes (described in Section 9.42) and the two dimming curves (see Figure 10.6). At startup, the CFG pin outputs I CFG after V CC reaches V CC(ST). The iW3617 reads the CFG pin voltage after 40µs. The dimming curve and dimming mode are selected by connecting a resistor with different values to the CFG pin as shown in Table 9.1CFG Option NumberCFG Pin ResistorDimming Curve Number (Fig. 10.6)DimmingControlValueTolerance120k W ≤ 5%1PWM 212.7k W ≤ 5%1CC-PFM 38.87k W ≤ 5%2PWM 45.62k W≤ 5%2CC-PFMTable 9.1 CFG Pin Resistor9.6 Protection FeaturesThis section provides information about iW3617 protectionfeatures.9.6.1 Output Over-Voltage/LED Open ProtectionThe iW3617 includes a function that protects against an output over-voltage.The output voltage is monitored by the FV SENSE pin. The ratio between the FV SENSE pin voltage and output voltage is equal to the transformer auxiliary to secondary winding turns-ratio multiplied by the FV SENSE resistor divider ratio (R20, R21 in Figure 11.1). If the voltage at the FV SENSE pin exceeds V SENSE(MAX), the iW3617 shuts down immediately. After the shutdown, the iW3617 remains powered which discharges the V CC . In order to avoid over-charging the output voltage, the iW3617 employs an extended discharge time as described below. Under the fault condition, the iW3617 tries to start up for three consecutive times. If all three start-up attempts fail, the iW3617 enters the inactive mode, during which the iW3617 does not respond to the V CC power-on requests. The iW3617 is activated again after it sees 29 start-up attempts. The iW3617 can also be reset to the initial condition if the V CC is completely discharged. Typically, this extended discharge time is around three to five seconds, and it allows the iW3617 to support hot-plug LED modules without causing ouput over-voltage while maintaining a quick recovery.9.6.2 Output Short ProtectionThe iW3617 includes a function that protects against an output short-circuit fault.If the voltage at the FV SENSE pin is below 0.228V, the iW3617 shuts down immediately. After the shutdown, the iW3617 remains powered, which discharges the V CC . In order to avoid excessive power stress due to auto-restart, the iW3617 employs an extended discharge time (as described in Section 9.61).To support applications with high output capacitance, output short protection is not activated in the initial LED current soft start period. This allows the voltage to build up in the output capacitor without mis-triggering the protection.9.6.3 Over-Temperature ProtectionIf an NTC thermistor is connected between the V T pin and the GND, the iW3617 is able to detect and protect against an over-temperature event.The iW3617 provides an I VT to the V T pin and detects thevoltage on the pin. Based on this voltage, the iW3617 canmonitor the resistance of the NTC thermistor, which is related to the temperature of the thermistor. As the V T pin voltagereduces, the iW3617 reduces the power in boost and flybackconverter.High Power Factor Dimmable LED DriversFigure 9.9 : V T Pin Voltage vs. % of Nominal Output CurrentWhen the V T pin voltage reaches V P-LIM(HI) the output current begins to reduce linearly from 100% to 20% as shown in Figure 9.9. At V P-LIM(LO) the output current will be clamped to1%. If the V T pin voltage further decreases to below V SH_TH , the iW3617 will shut down.The iW3617 will remain in shut-down mode as long as the V T pin voltage is below V SH_TH . If the V T pin voltage rises above V SH_TH at any time, the device will start up and the output will be clamped at 1%. Once the V T pin voltage reaches V P-LIM(LO), the output current will increase to 20%. From V P-LIM(LO) to V P-LIM(HI), the output current will increase linearly from 20% to 100% as shown in Figure 9.9. Finally, the device will go back to normal operation when the V T pin voltage rises above V P-LIM(HI).This bi-directional operation of the V T pin enables the LED current thermal foldback instead of an abrupt shut-down of the light. As the output power decreases under the mild over-temperature condition, the amount of heat generated by the LED also decreases, which reduces the possibility of furthertemperature rise of the system.9.6.4 Over-Current ProtectionOver-current protection (OCP) is a feature that is built into theiW3617.With the FI SENSE pin the iW3617 is able to monitor the primary peak current of the flyback converter. This allows for cycle-by-cycle peak current control and limit. When the primary peak current multiplied by the FI SENSE sense resistor(R15 in Figure 11.1) is greater than V OCP(FLYBACK), over-current is detected and the iW3617 immediately turns off the gate drive until the next cycle. The F DRV pin sends out switching pulse in the next cycle, and the switching pulse continues if the V OCP(FLYBACK) is not reached; or, the switching pulse turns off again if the V OCP(FLYBACK) is still reached.The BI SENSE pin provides the same protection mechanism for the boost converter. The BI SENSE OCP threshold is V OCP(BOOST) in no dimmer or trailing-edge dimmer mode. The BI SENSE OCP threshold is 1.5V in leading-edge dimmer mode.9.6.5 Sense Resistor Short ProtectionIf the FI SENSE sense resistor is shorted there is a potential danger of the over-current condition not being detected. Thus the iW3617 is designed to detect this sense-resistor short fault. If the voltage on the FI SENSE pin is belowV RSENSE(FLYBACK) after 15.6µs of turning on, the sense-resistorshort protection is triggered and the iW3617 shuts down immediately. After the shutdown, the V CC is dischargedsince the iW3617 remains powered. The iW3617 employsan extended discharge time (as described in Section 9.61) before restart. If the BI SENSE resistor is shorted, the iW3617 cannotdetermine the emitter current of the boost BJT, which can ultimately result in the boost BJT exceeding its safeoperating area. Thus the iW3617 is designed to detect this boost sense-resistor short fault. When the iW3617 detects a boost-sense-resistor short fault at the detection cycle, the iW3617 shuts down immediately. In the leading-edge and trailing-edge modes, the detection cycle is the zero crossing period in an AC half cycle. If there is no dimmer on the line, the only detection cycle is at start-up. After the shutdown,the V CC is discharged since the iW3617 remains powered. To prevent over-stress on the boost circuit components, theiW3617 employs an extended discharge time (as described in Section 9.61) before restart. 9.6.6 Boost Inductor Short-Protection The boost inductor is protected from short condition in no dimmer mode. If the BV SENSE pin is not able to see the reset of the boost inductor, the boost inductor short is detected. The iW3617 will short down immediately.9.6.7AC Input and Boost Output Over-Voltage ProtectionThe iW3617 supports the over-voltage protection of AC input and boost output voltage. If the V IN pin voltage is higher than V IN_OVP for continuous 2ms within every 16ms period, and this condition lasts for eight consecutive AC half cycles, the iW3617 shuts down both the boost and flyback converters. After the shutdown, the V CC is discharged since the iW3617 remains powered.When V CC drops below below V CC(UVL), the iW3617 resets itself and then initiates a new soft-start cycle.。

INFINEON XE167xM XE164xM XE 16 位单片实时信号控制器 说明书

16位架构XE167xM/XE164xM/XE 162xM衍生产品16位单片实时信号控制器XE166家族用户手册V2.0 2009-03Edition 2009-03Published byInfineon Technologies AG81726 Munich, Germany© 2009 Infineon Technologies AGAll Rights Reserved.Legal DisclaimerThe information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.InformationFor further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office ().WarningsDue to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.16位架构XE167xM/XE164xM/XE 162xM衍生产品16位单片实时信号控制器XE166家族用户手册V2.0 2009-03XC2200M版本信息:V2.0, 2009-03先前的版本:V1.2, 2008-09(V1.1略去)V1.0, 2008-06页内容(对上一版本的主要修正)所有两卷(系统单元,外设单元)合并为一个文档页3-5 增加IMB寄存器的描述增加SBRAM的描述页3-11页12-3页3-15 增加保护位的描述(从架构概述一章移至此处)页5-59 改进位保护部分的内容页6-3 增加对256字节最小地址分区进行MPU编程的提示页7-37 更正ERU中断控制寄存器的名称页8-2 更新图:时钟产生单元页8-21 更新WUOSSCON的描述页8-23 改变位域HPOSCCON.MODE的描述页8-85 更新一些位域的描述(EVR控制寄存器)页8-96 改变保留位的描述(GSCEN、GSCPERSTAT、GSCPERSTATEN)页8-119 更正EXOCON的复位值页8-121 更新图:SCU中断结构页8-122 更正唤醒中断的缩写名页8-137 更新位描述页8-149 增加位WDTCS.OE的描述注解页8-151 图更新:SCU强制中断结构页8-152 更正缺省PLL强制中断页8-171 改进ECC错误处理的描述XC2200M版本信息:V2.0, 2009-03 页8-183增加寄存器IDDMPM 和IDDMP1 页9-5增加关于复位操作的描述 页9-34规定重叠的模拟输入通道(ADC0/ADC1) 页9-35增加信号U3C1_SELO1 页12-29更正引导程序加载配置表 页16-35,页16-63重新组织GPT 定时器寄存器,删去中断控制寄存器页16-69增加寄存器表 页16-74增加端口控制部分的内容 页17-9增加信号T14INT 页19-26重新组织CCU2寄存器,将其集中到一节中。

TPS3617-50资料

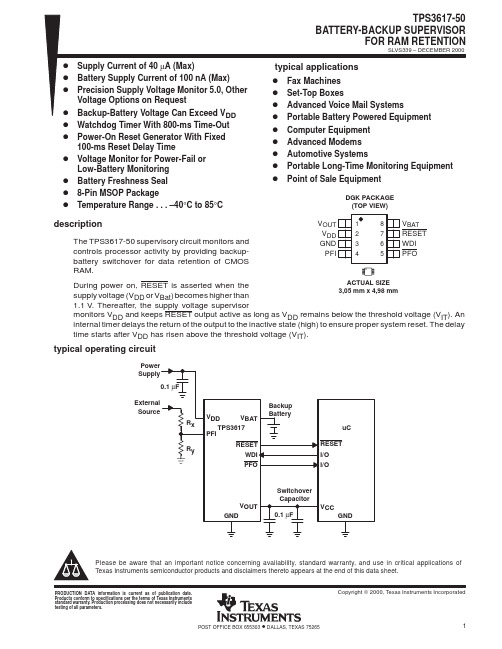

IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.Customers are responsible for their applications using TI components.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 2000, Texas Instruments Incorporated。

iw3616、3617、3630datasheet中文翻译(绝对真实)解析

产品特色大幅简化离线式LED驱动器设计●单级功率因数校正(PFC)与精确恒流(CC)输出相结合●输入/输出电容和变压器体积小●一次侧反馈控制,无需光耦电路,简化了电路设计●简化初级侧PWM调光接口●符合IEC61000-3-2标准高效节能和高兼容性●大幅提升效率,可达到85%以上●减少元件数量●总谐波失真<15%且PF>0.95●前沿、后沿和数字调光器●传感器和定时器精确稳定的性能●LED负载恒流精度不低于±5%●支持LED负载热插拔●1%-100%宽范围调光,调光无闪烁先进的保护及安全特性●通过自动重启动提供短路保护●开路故障检测模式●自动热关断重启动无论在PCB板上还是在封装上,都保证高压漏极引脚与其他所有信号引脚之间满足高压爬电要求应用●LED离线固态照明说明G7617 是一款的适用于LED调光控制的离线式两级交流/直流电源控制器,是适用于25W 输出功率的可调光LED 灯具的最优之选。

G7617符合电磁兼容性(EMC) IEC61000-3-2 标准,在120V AC或230V AC输入电压下其功率因数(PF) 可达到0.95 以上。

采用先进的数控技术来检测调光器的类型和相位,为调光器提供动态阻抗的同时可调节LED发光亮度,自动检测调光器类型和相位,从而实现了业内与模拟及数字调光器最广泛的兼容性。

G7617工作于准谐振工作模式,工作效率高,可工作于前沿后沿调光模式,也可工作于R 型、R-C型或R-L型调光控制模式。

G7617 符合热插拔LED 模块的固态照明行业标准Zhaga,同时还集成了调光功能的映射选项(位于白炽灯替代灯的NEMA SSL6 调光曲线内)。

G7617 系列有两个版本:针对120V AC输入应用进行优化的G7617-00 和针对230V AC 应用进行优化的G7617-01。

订购信息应用框图图1典型应用内部框图Vcc VinVcbVT CFGASU BisenseBdrvFdrvFisensePGNDAGND C O R E图2 内部框图引脚功能描述BV SENSE V IN BI SENSE B DRV CFG ASU V CCV CBV TFV SENSEFI SENSEF DRVAGNDPGND 图3. 引脚布局BV SENSE引脚:PFC电感电压反馈点,用于感知Boost电感的磁通状态。

ht1621中文资料_数据手册_参数

TV160高速编程器 说明书

TV160高速编程器使用说明书(用户手册1.0版)目录1、TV160编程器产品简介^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^2页2、TV160编程器随机标配件与选购件^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^3页3、TV160编程器脱机拷贝使用图示^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^6页4、TV160编程器支持芯片表^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^7页5、TV160编程器读写软件操作说明^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^8页6、TV160编程器固件升级介绍^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^11页7、TV160编程器USB驱动安装介绍^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^12页8、TV160编程器支持创维平板FLASH器件表^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^16页9、TV160编程器价格及购买介绍^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^17页感谢您选择使用《彩电维修资料网》开发生产的TV160-FLASH的高速编程器,在使用此产品时请先仔细阅读本产品的使用说明书,本编程器主要解决一线维修CRT彩电、平板彩电、卫星接收机、DVD机的程序烧写问题。

Synology RS3617RPxs 企业级存储设备说明书

出色性能RS3617RPxs 在启用 10GbE Link Aggregation 且存储空间配置为 RAID 5 的情况下,可提供每秒高于 3,829 MB 及 433,873 IOPS 的出色传输性能1。

使用先进的 ash 技术,结合硬盘和 SSD 缓存,能有效提高传输效率并同时减少每 GB 的使用成本。

除了内置的四个 1GbE RJ-45 网络端口之外,RS3617RPxs 配备双 PCIe 3.0 x8 插槽让您安装两个 10GbE 的网络接口卡 (NIC),藉以满足处理大量数据的应用程序的需要。

RS3617RPxs 配备了 8GB DDR4 ECC UDIMM 并支持扩充高达 64GB ,确保数据准确和优越的性能,为您的企业提供强有力的后盾来处理关键任务。

Btrfs :下一代存储效率RS3617RPxs 引进了 Btrfs 文件系统,采用了更先进的存储技术以满足现代大型企业的管理需求:●灵活的共享文件夹/用户配额系统,可提供对所有用户帐户和共享文件夹的全面配额控制能力。

●先进快照技术及自定义的备份计划可以实现高达 1,024 个共享文件夹和 65,000 个系统智能快照的备份,而无需占用大量存储空间和系统资源。

●文件或文件夹层级数据还原为希望仅存储特定文件或文件夹的用户带来了巨大的方便并节省了时间。

●使用 Cloud Station 版本功能与 ext4 文件系统相比降低了一半的存储空间消耗。

虚拟化功能完备RS3617RPxs 可为虚拟化环境(包括 VMware 、Citrix 、Hyper-V 和 OpenStack Cinder )提供无缝存储空间解决方案。

RS3617RPxs 已获得 VMware vSphere 6 和 VAAI 统一认证,能够在 VMware 环境下帮助分流特定的存储操作并优化计算能力,以获得无与伦比的性能及效率。

RS3617RPxs 作为虚拟环境中的集中式存储,启用虚拟机迁移功能后,不仅免去服务维修时间及对使用者造成的干扰,还可让您在不同服务器上操作。

DS36179J中文资料

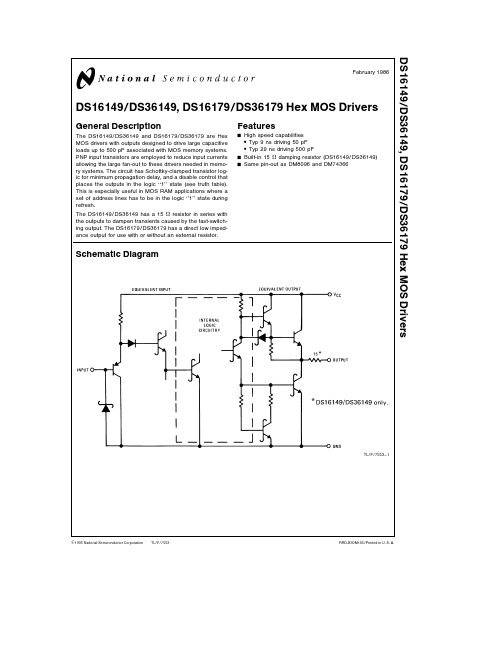

TL F 7553DS16149 DS36149 DS16179 DS36179Hex MOS DriversFebruary 1986DS16149 DS36149 DS16179 DS36179Hex MOS DriversGeneral DescriptionThe DS16149 DS36149and DS16179 DS36179are Hex MOS drivers with outputs designed to drive large capacitive loads up to 500pF associated with MOS memory systems PNP input transistors are employed to reduce input currents allowing the large fan-out to these drivers needed in memo-ry systems The circuit has Schottky-clamped transistor log-ic for minimum propagation delay and a disable control that places the outputs in the logic ‘‘1’’state (see truth table) This is especially useful in MOS RAM applications where a set of address lines has to be in the logic ‘’1’’state during refreshThe DS16149 DS36149has a 15X resistor in series with the outputs to dampen transients caused by the fast-switch-ing output The DS16179 DS36179has a direct low imped-ance output for use with or without an external resistorFeaturesYHigh speed capabilities Typ 9ns driving 50pF Typ 29ns driving 500pFY Built-in 15X damping resistor (DS16149 DS36149)YSame pin-out as DM8096and DM74366Schematic DiagramTL F 7553–1C 1995National Semiconductor Corporation RRD-B30M105 Printed in U S AAbsolute Maximum Ratings(Note1)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage7 0V Logical‘‘1’’Input Voltage7 0V Logical‘‘0’’Input Voltage b1 5V Storage Temperature Range b65 C to a150 C Maximum Power Dissipation at25 CCavity Package1371mW Molded Package1280mW Lead Temperature(Soldering10seconds)300 C Derate cavity package9 1mW C above25 C derate molded package 10 2m W C above25 C Operating ConditionsMin Max Units Supply Voltage(V CC)4 55 5V Temperature(T A)DS16149 DS16179b55a125 C DS36149 DS361790a70 CDC Electrical Characteristics(Notes2and3)Symbol Parameter Conditions Min Typ Max Units V IN(1)Logical‘‘1’’Input Voltage2 0V V IN(0)Logical‘‘0’’Input Voltage0 8V I IN(1)Logical‘‘1’’Input Current V CC e5 5V V IN e5 5V0 140m A I IN(0)Logical‘‘0’’Input Current V CC e5 5V V IN e0 5V b50b250m A V CLAMP Input Clamp Voltage V CC e4 5V I IN e b18mA b0 75b1 2VV OH Logical‘‘1’’Output VoltageV CC e4 5V I OH e b10m A DS16149 DS161793 44 3V(No Load)DS36149 DS361793 54 3VV OL Logical‘‘0’’Output VoltageV CC e4 5V I OL e10m A DS16149 DS161790 250 4V(No Load)DS36149 DS361790 250 35V V OH Logical‘‘1’’Output Voltage DS161492 43 5V (With Load)V CC e4 5V I OH e b1 0mADS161792 53 5VDS361492 63 5VDS361792 73 5V V OL Logical‘‘0’’Output Voltage DS161490 61 1V (With Load)V CC e4 5V I OL e20mADS161790 40 5VDS361490 61 0VDS361790 40 5V I ID Logical‘‘1’’Drive Current V CC e4 5V V OUT e0V (Note4)b250mA I OD Logical‘‘0’’Drive Current V CC e4 5V V OUT e4 5V (Note4)150mAI CC Power Supply Current Disable Inputs e0V3360mAV CC e5 5VAll Other Inputs e3VAll Inputs e0V1420mA Switching Characteristics(V CC e5V T A e25 C)(Note4)Symbol Parameter Conditions Min Typ Max Unitst S g Storage Delay Negative Edge(Figure1)C L e50pF4 57ns C L e500pF7 512nst S’Storage Delay Positive Edge(Figure1)C L e50pF58ns C L e500pF813nst F Fall Time(Figure1)C L e50pF58nsC L e500pF2235ns 2Switching Characteristics (V CC e 5V T A e 25 C)(Note 4)(Continued)Symbol Parameter ConditionsMinTyp Max Units t R Rise Time(Figure 1)C L e 50pF 69ns C L e 500pF2635ns t LH Delay from Disable Input R L e 2k X to Gnd 1522ns to Logical ‘‘1’’C L e 50pF (Figure 2)t HLDelay from Disable Input R L e 2k X to V CC 1118nsto Logical ‘‘0’’C L e 50pF (Figure 3)Note 1 ‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaranteed Except for ‘‘Operating Temperature Range’’they are not meant to imply that the devices should be operated at these limits The table of ‘‘Electrical Characteristics’’provides conditions for actual device operationNote 2 Unless otherwise specified min max limits apply across the b 55 C to a 125 C temperature range for the DS16149and DS16179and across the 0 C to a 70 C range for the DS36149and DS36179 All typical values are for T A e 25 C and V CC e 5VNote 3 All currents into device pins shown as positive out of device pins as negative all voltages referenced to ground unless otherwise noted All values shown as max or min on absolute value basisNote 4 When measuring output drive current and switching response for the DS16179and DS36179a 15X resistor should be placed in series with each output This resistor is internal to the DS16149 DS36149and need not be addedConnection DiagramDual In-Line PackageTL F 7553–2Top ViewOrder Number DS16149J DS36149J DS16179JDS36179J DS36149N or DS36179N See NS Package Number J16A or N16ATruth TableDisable Input Input Output DIS 1DIS20001001001X 110X 111X1X e Don’t careAC Test Circuits and Switching Time Waveformst S g t S g t R t FTL F 7553–3FIGURE 13AC Test Circuits and Switching Time Waveforms(Continued)TL F 7553–4FIGURE2TL F 7553–5FIGURE3Internal on DS16149and DS36149Note1 The pulse generator has the following characteristics Z OUT e50X and PRR s1MHz Rise and fall times between10%and90%points s5ns Note2 C L includes probe and jig capacitanceTypical ApplicationsTL F 7553–64Physical Dimensions inches(millimeters)Ceramic Dual-In-Line Package(J)Order Number DS16149J DS36149JDS16179J or DS36179JNS Package Number J16A5D S 16149 D S 36149 D S 16179 D S 36179H e x M O S D r i v e r sPhysical Dimensions inches (millimeters)(Continued)Molded Dual-In-Line Package (N)Order Number DS36149N DS36149NNS Package Number N16ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

iw3616、3617、3630datasheet中文翻译(绝对真实)

产品特色大幅简化离线式LED驱动器设计●单级功率因数校正(PFC)与精确恒流(CC)输出相结合●输入/输出电容和变压器体积小●一次侧反馈控制,无需光耦电路,简化了电路设计●简化初级侧PWM调光接口●符合IEC61000-3-2标准高效节能和高兼容性●大幅提升效率,可达到85%以上●减少元件数量●总谐波失真<15%且PF>0.95●前沿、后沿和数字调光器●传感器和定时器精确稳定的性能●LED负载恒流精度不低于±5%●支持LED负载热插拔●1%-100%宽范围调光,调光无闪烁先进的保护及安全特性●通过自动重启动提供短路保护●开路故障检测模式●自动热关断重启动无论在PCB板上还是在封装上,都保证高压漏极引脚与其他所有信号引脚之间满足高压爬电要求应用●LED离线固态照明说明G7617 是一款的适用于LED调光控制的离线式两级交流/直流电源控制器,是适用于25W 输出功率的可调光LED 灯具的最优之选。

G7617符合电磁兼容性(EMC) IEC61000-3-2 标准,在120V AC或230V AC输入电压下其功率因数(PF) 可达到0.95 以上。

采用先进的数控技术来检测调光器的类型和相位,为调光器提供动态阻抗的同时可调节LED发光亮度,自动检测调光器类型和相位,从而实现了业内与模拟及数字调光器最广泛的兼容性。

G7617工作于准谐振工作模式,工作效率高,可工作于前沿后沿调光模式,也可工作于R 型、R-C型或R-L型调光控制模式。

G7617 符合热插拔LED 模块的固态照明行业标准Zhaga,同时还集成了调光功能的映射选项(位于白炽灯替代灯的NEMA SSL6 调光曲线内)。

G7617 系列有两个版本:针对120V AC输入应用进行优化的G7617-00 和针对230V AC 应用进行优化的G7617-01。

订购信息应用框图图1典型应用内部框图Vcc VinVcbVT CFGASU BisenseBdrvFdrvFisensePGNDAGND C O R E图2 内部框图引脚功能描述BV SENSE V IN BI SENSE B DRV CFG ASU V CCV CBV TFV SENSEFI SENSEF DRVAGNDPGND 图3. 引脚布局BV SENSE引脚:PFC电感电压反馈点,用于感知Boost电感的磁通状态。

ht1621中文资料

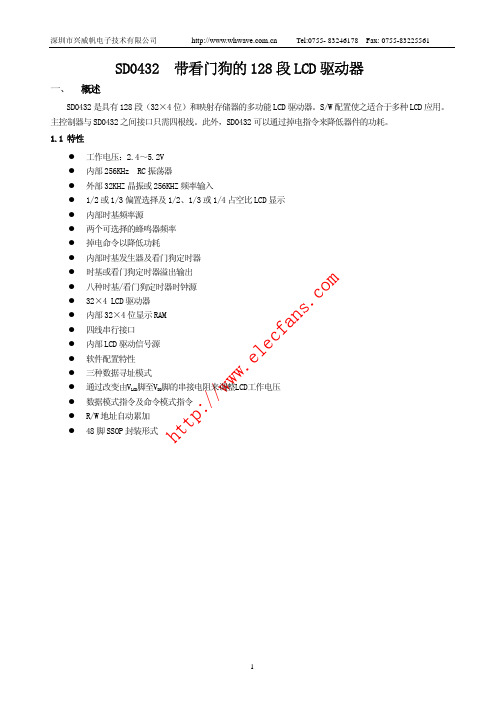

SD0432 中集成了一个简单的声音发生器,此发声器可输出一对不同的驱动信号至 BZ 和 BZ 以产生单音,执 行 TONE 4K 与 TONE 2K 命令,可选择两个不现的音频输出,即 4KHZ 与 2KHZ 这两个频率,TONE ON 及 TONE OFF 命令可打开或关闭语音输出,语音输出 BZ 和 BZ,是一对不同的带驱动蜂鸣器。当系统关闭或语音输出被禁止时, BZ 及 BZ 将处于低电平状态。

命令 LCD OFF 是通过关闭 LCD 偏压发生器来关闭 LCD 显示器。反之,LCD ON 则启动 LCD 显示。BIAS COM 是与

LCD 屏面相关命令。使用 LCD 相关命令,SD0432 可与绝大多数类型的 LCD 屏面兼容。

3. 6 命令格式

SD0432 可由 S/W 设置来配置。有两种命令模式分别用来配置 SD0432 和传送 LCD 显示数据。配置 SD0432 的命

令模式(普通模式)识别码为 100,此命令模式由系统配置命令、LCD 配置命令、音频选择命令、定时器/看门狗

定时器设置命令及操作命令组成。另一方面,数据模式包括 READ、WRITE 及 READ-MODIFY-WRITE 操作。下表为数

据模式及命令模式识别码:

com 操

作

. READ

s WRITE

le RAM 中的数据由 READ、WRITE 以及 READ-MODIFY-WRITE 指令进行存取,下图为由 RAM 控制 LCD 的映象图。

e SEG

COM

COM3

COM2

COM1

COM0

六位地址(A5,A4…A0)

. SEG0

0

ww SEG1

1

w SEG2

PC716V中文资料

1. DC-DC SSRs

2. Power monitors, welding machines

3. System appliances, measuring instruments 4. Signal transmission between circuits of

different potentials and impedances

24

20

0.5mA

16

12

0.4mA

8 0.3mA

4

0.2mA

0

0.1mA

0 1 2 3 4 5 6 7 8 9 10

Collector-emitter voltage V CE (V)

Fig. 7 Relative Current Transfer Ratio vs. Ambient Temperature

Collector-emitter voltage VCE (V)

Fig. 8 Collector-emitter Saturation Voltage vs. Ambient Temperature

1.0 IF = 20mA IC = 10mA

0.8

Collector emitter saturation voltage VCE(sat) (V)

60

50

Forward current I F ( mA )

40

30

20

10

0 - 25

0

25 5055 75 100 125

Ambient temperature T a (˚C)

Fig. 3 Peak Forward Current vs. Duty Ratio

10 000 5 000

深圳唯创知音电子有限公司WTVxxxx芯片扩展说明书

深圳唯创知音电子有限公司Shenzhen Waytronic Electronic Co.,LtdWTVxxxx芯片资料(B001)(扩展说明)版本号:V1.00Note:WAYTRONIC ELECTRONIC CO.,LTD.reserves the right to change this document without prior rmation provided by WAYTRONIC is believed to be accurate and reliable.However,WAYTRONIC makes no warranty for any errors which may appear in this document.Contact WAYTRONIC to obtain the latest version of device specifications before placing your orders.No responsibility is assumed by WAYTRONIC for any infringement of patent or other rights of third parties which may result from its use.In addition,WAYTRONIC products are not authorized for use as critical components in life support devices/systems or aviation devices/systems,where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of WAYTRONIC.目录目录 01.产品简介 (1)2.产品特点 (1)3.选型表 (3)4.管脚相关 (3)4.1.QFN32封装管脚 (3)5.控制模式 (3)5.1.UART控制模式 (6)5.1.1.协议命令格式 (6)5.2.LED显示部分 (7)5.2.1.数码管显示(0XB0) (7)5.2.2.数码管固定模式(0XB1) (8)5.2.3.单个led设置(0XB5) (9)5.2.4.亮度参数设置(0XB6) (10)5.2.5.数字动态闪烁设置(0XB7) (10)5.2.6.图形动态显示设置(0XB8) (11)5.2.7.圆点动态闪烁设置(0XB9) (12)5.3.按键部分 (12)5.3.1.按键获取模式(0XB2) (13)5.3.2.按键主动上报按下模式(0XB3) (13)5.3.3.按键主动上报抬起模式(0XB4) (13)5.4.写操作指令 (14)5.4.1.写操作指令返回码格式 (14)5.4.2.指定Flash根目录索引播放(A0) (14)5.4.3.指定Flash根目录文件名播放(A1) (15)5.4.4.暂停放音命令(AA) (15)5.4.5.停止命令(AB) (15)5.4.6.下一曲命令(AC) (15)5.4.7.上一曲命令(AD) (16)5.4.8.音量控制命令(AE) (16)5.4.9.指定播放模式(AF) (16)5.4.10.组合播放指令(B0) (17)5.4.11.插播指令(B1) (17)5.4.12.进入低功耗(B800) (18)5.4.13.查询当前软件版本(C0) (18)5.4.14.查询当前设置音量(C1) (18)5.4.15.读取当前工作状态(C2) (18)5.4.16.查询FLASH内音乐文件总数(C3) (19)5.4.17.查询当前播放文件地址(C9) (19)5.4.18.波特率切换指令(FB) (19)5.5.一线串口控制模式 (20)5.5.1.一线语音地址对应关系 (20)5.5.2.一线语音及命令码对应表 (20)5.5.3.一线串口时序图 (21)5.6.两线串口控制模式 (22)5.6.1.两线语音地址对应关系 (22)5.6.2.两线语音及命令码对应表 (23)5.6.3.两线串口时序图 (23)6.电路设计参考 (24)6.1.QFN32封装电路设计参考 (24)6.2.电路设计意事项 (25)7.程序范例 (26)7.1.一线串口程序示例 (26)7.1.1.一线串口控制程序(单字节) (26)7.1.2.一线串口程序(切换DAC输出&播放固定地址) (27)7.1.3.一线串口控制程序(连码播放:F3+01+F3+02+F3+03) (28)7.2.两线串口程序示例 (28)7.2.1.两线线串口控制程序(单字节) (28)7.2.2.两线串口控制程序(连码播放:F3+01+F3+02+F3+03) (29)8.电气参数 (30)8.1.QFN32封装电气参数 (30)8.1.1.绝对最大额定参数 (30)8.1.2.PMU特性 (30)8.1.3.IO输入/输出电气逻辑特性 (31)9.封装信息 (31)9.1.QFN32封装尺寸 (31)10.修订版本 (32)WTVxxxx是一款功能强大的高品质语音芯片,采用了高性能32位处理器、最高频率可达120MHz。

ht1621中文资料

典型 值

150 300 60 120

最大 值 5.2 300 600 120 240

单位

V

A A A A

rm.

IDD 工作电流

3V 不带负载 5V 外部时钟源

100 200 A 200 400 A

a

ISTB VIL VIH IOL1 IOH1 IOL2 IOH2 IOL3 IOH3 RPH

待机电流

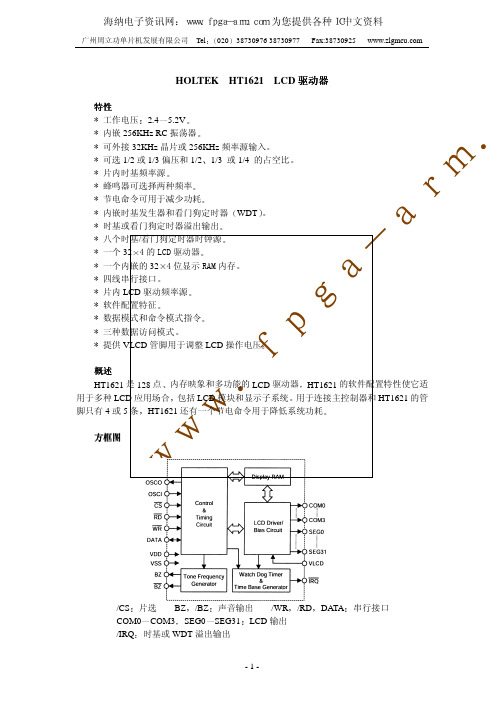

时基和看门狗定时器 WDT 时基发生器是一个 8 态增值尖峰计数器 可以产生准确的时基 WDT 由时基发生器和 一个 2 态增值尖峰计数器组成 它可以在主控制器或其它子系统处于异常状态时产生中断 WDT 溢出时产生片内 WDT 溢出标志 可用一命令选项使时基发生器和 WDT 溢出标志输 出到/IRQ 管脚 时基发生器和 WDT 时钟频率有 8 种 fWDT=32KHz/2n 这里的 n 值为 0 7 由命令项决定 等式中 32KHz 为系统频率 由晶振 32.768KHz 片内振荡器 (256KHz)

海纳电子资讯网:www.fpga-arm.com 为您提供各种IC中文资料

广州周立功单片机发展有限公司 Tel 020 38730976 38730977 Fax:38730925

HOLTEK HT1621 LCD 驱动器

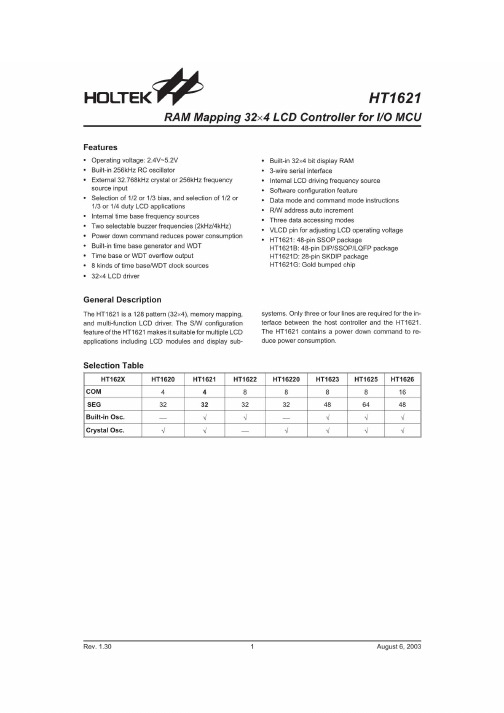

特性

* 工作电压 2.4 5.2V

* 内嵌 256KHz RC 振荡器 * 可外接 32KHz 晶片或 256KHz 频率源输入

32.768 32.768 256 256 fSYS1/102 4 fSYS2 /128 fSYS3/102 4

n/ fLCD

KHz KHz KHz KHz

Hz

Hz

rm.

a Hz

-s

VG3617161DT资料