GAL课件

合集下载

PAL,PLA,GAL数字逻辑系统

基本组成包括:输入互补缓冲; 的组合逻辑函数。 可编程与阵列;固定或阵列; ❖ PAL和触发器可构成时序电路。

特定的输出电路。

❖ 与阵列可编程使输入项增多,或

❖ 采用双极型熔丝工艺,工作速 阵列固定使器件简化。

度较高(10-35ns)。

❖ 或阵列固定明显影响了器件编程

的灵活性。

精选课件

9

4输入4输出16乘积项PAL器件的基本结构图

组合可编程逻辑阵列PLA的逻辑结构:由一个“与” 阵列和一个“或”阵列构成,“与”阵列和“或”阵 列都是可编程的。

时序可编程逻辑阵列PLA的逻辑结构:由“与”阵列 “或”阵列和一个用于存储以前状态的触发器网络构成

精选课件

5

可编程逻辑阵列应用

▪ 在可编程逻辑阵列PLA的应用中,有一种是用来 控制资料路径,在指令集内事先定义好逻辑状态, 并用此来产生下一个逻辑状态(透过条件分支)。

• 2. 异步可编程I/O结构

• 3. 寄存(时序)输出结构 • 4. 异或-寄存器型输

出结构 • 5. 运算选通反馈结构

精选课件

12

专用电平输出。

一个输入

如输出采用或门,为高电平有效PAL器件。 若采用互补输出的或门,为互补输出器件。

▪ 举例来说,如果目前机器(指整个逻辑系统)处于 二号状态,如果接下来的执行指令中含有一个立 即值(侦测到立即值的栏位)时,机器就从第二状 态转成四号状态,并且也可以进一步定义进入第 四状态后的接续动作。因此PLA等于扮演(晶片) 系统内含的逻辑状态图(statediagram)角色。

精选课件

6

可编程逻辑阵列应用

触发器Q非输出经过一个互补缓冲器反馈到与阵 列输入端上。

输出三态缓冲器由公共控制线控制。 用途:组成各类时序逻辑电路。 这种结构的产品有PAL16R4、 PAL16R8 等。

特定的输出电路。

❖ 与阵列可编程使输入项增多,或

❖ 采用双极型熔丝工艺,工作速 阵列固定使器件简化。

度较高(10-35ns)。

❖ 或阵列固定明显影响了器件编程

的灵活性。

精选课件

9

4输入4输出16乘积项PAL器件的基本结构图

组合可编程逻辑阵列PLA的逻辑结构:由一个“与” 阵列和一个“或”阵列构成,“与”阵列和“或”阵 列都是可编程的。

时序可编程逻辑阵列PLA的逻辑结构:由“与”阵列 “或”阵列和一个用于存储以前状态的触发器网络构成

精选课件

5

可编程逻辑阵列应用

▪ 在可编程逻辑阵列PLA的应用中,有一种是用来 控制资料路径,在指令集内事先定义好逻辑状态, 并用此来产生下一个逻辑状态(透过条件分支)。

• 2. 异步可编程I/O结构

• 3. 寄存(时序)输出结构 • 4. 异或-寄存器型输

出结构 • 5. 运算选通反馈结构

精选课件

12

专用电平输出。

一个输入

如输出采用或门,为高电平有效PAL器件。 若采用互补输出的或门,为互补输出器件。

▪ 举例来说,如果目前机器(指整个逻辑系统)处于 二号状态,如果接下来的执行指令中含有一个立 即值(侦测到立即值的栏位)时,机器就从第二状 态转成四号状态,并且也可以进一步定义进入第 四状态后的接续动作。因此PLA等于扮演(晶片) 系统内含的逻辑状态图(statediagram)角色。

精选课件

6

可编程逻辑阵列应用

触发器Q非输出经过一个互补缓冲器反馈到与阵 列输入端上。

输出三态缓冲器由公共控制线控制。 用途:组成各类时序逻辑电路。 这种结构的产品有PAL16R4、 PAL16R8 等。

地球物理学基础ppt课件

(一)岩(矿)石的密度的一般规律

1、火成(岩浆)岩密度>变质岩密度>沉积岩密度

根据长期研究的结果,认为决定岩、矿石密 度的主要因素为:

※ 组成岩石的各种矿物成分及其含量的多少; ※ 岩石中孔隙度大小及孔隙中的充填物成分; ※ 岩石所承受的压力等。

2、火成岩(2.5~3.6 g /cm³)

(1)主要取决于矿物成分及其含量的百分比,由 酸性→基性→超基性岩,随着密度大的铁镁 暗色矿物含量增多密度逐渐加大。

Δg = gg

+

0

-

σ1

σ2

σ3

σ0

σ1>σ0

σ2<σ0

σ3=σ0

4、引起重力异常的条件

(1)探测对象与围岩要有一定的密度差。 (2)岩层密度必须在横向上有变化,即岩层内有密度不同的地

质体存在,或岩层有一定的构造形态。 (3)剩余质量不能太小(即探测对象要有一定的规模) (4)探测对象不能埋藏过深

(1)重力观测是在地球的自然表面上而不是在大地 水准面上进行的(自然表面与大地水准面间的 物质及测点与大地水准面间的高差会引起重力 的变化)

(2)地壳内物质密度的不均匀分布;

(3)重力日变化

3、重力异常的物理意义

A

大地水准面

σ0

△F

σ V

g0 △g

△F

g观

△σ =σ–σ0 △m=Δσ×V

g观 g0 F

由上式可见:重力场强度,无论在数值上,还是 量纲上都等于重力加速度,而且两者的方向也一致。 在重力勘探中,凡是提到重力都是指重力加速度(或 重力场强度)。

2、重力的单位(gravity unit)

在SI制中:g(重力加速度)的单位为1m/s2,规定 1m/s2的百万分之一为国际通用重力单位(gravity unit),简写为g.u,即:

1、火成(岩浆)岩密度>变质岩密度>沉积岩密度

根据长期研究的结果,认为决定岩、矿石密 度的主要因素为:

※ 组成岩石的各种矿物成分及其含量的多少; ※ 岩石中孔隙度大小及孔隙中的充填物成分; ※ 岩石所承受的压力等。

2、火成岩(2.5~3.6 g /cm³)

(1)主要取决于矿物成分及其含量的百分比,由 酸性→基性→超基性岩,随着密度大的铁镁 暗色矿物含量增多密度逐渐加大。

Δg = gg

+

0

-

σ1

σ2

σ3

σ0

σ1>σ0

σ2<σ0

σ3=σ0

4、引起重力异常的条件

(1)探测对象与围岩要有一定的密度差。 (2)岩层密度必须在横向上有变化,即岩层内有密度不同的地

质体存在,或岩层有一定的构造形态。 (3)剩余质量不能太小(即探测对象要有一定的规模) (4)探测对象不能埋藏过深

(1)重力观测是在地球的自然表面上而不是在大地 水准面上进行的(自然表面与大地水准面间的 物质及测点与大地水准面间的高差会引起重力 的变化)

(2)地壳内物质密度的不均匀分布;

(3)重力日变化

3、重力异常的物理意义

A

大地水准面

σ0

△F

σ V

g0 △g

△F

g观

△σ =σ–σ0 △m=Δσ×V

g观 g0 F

由上式可见:重力场强度,无论在数值上,还是 量纲上都等于重力加速度,而且两者的方向也一致。 在重力勘探中,凡是提到重力都是指重力加速度(或 重力场强度)。

2、重力的单位(gravity unit)

在SI制中:g(重力加速度)的单位为1m/s2,规定 1m/s2的百万分之一为国际通用重力单位(gravity unit),简写为g.u,即:

动漫PPT课件

10

♦~动漫的定义

动漫学是以漫画、动画、游戏(即通常所说的ACG) 为研究核心内容的,研究探讨其三者起源、发展经 过、融合历程以及未来发展走向等内容,包括人物 形象设计、动画制作、故事情节创作、网络游戏、 图书小说、动画电影、周边玩具、人物配音、音乐 制作、服装设计、动漫产业链等各个与动漫相关的 领域的一门综合性学科。简言之,研究一切与动漫 相关的学问。

• 动漫、动画和漫画三个词语 从一开始就有着明确的指代, 错误的用法只会令原本清晰 的词义变得模糊,以讹传讹 并不可取。

4

♫~所谓动画 • 动画的定义:动画是指由许多帧 静止的画面,以一定的速度连续 播放时,肉眼因视觉残象产生错 觉,而误以为画面活动的作品。

• 由此,动画只是一种形式,与其 制作、出品国,由何改编而来、 播放形式等事项毫无关系。

景音乐(BGM)。 • 动画原创:依漫画改编的动画,由于动画的更新速度比

漫画快的关系,当动画的剧集快赶上漫画时,动画的剧 情就要脱离漫画剧情,开始动画原创。 • 同人:也叫二次创作,由漫画、动画、游戏、小说、影 视等作品甚至现实里已知的人物、设定衍生出来的文章 及其他如图片影音游戏等等,或“自主”的创作。 • COS:全称COSPLAY,装扮成漫画、动画、游戏、小说等 中的人物,也可以是原创。

7

♠~动漫的概论

动漫领域衍生出的许多术语均已经被广泛应用, 例如:正太、萝莉、御姐、百合、BL等。

• 动漫产业日益与游戏产业结合紧密,在日本已经 形成一个成熟的产业链,动漫已经从单单的平面 媒体和电视媒体扩展到游戏,书籍,网络,玩具 等众多领域。许多动漫游戏应运而生,例如《死 神bleach》PSP平台的游戏,也有许GALGAME 被改编成动漫作品。

• 当前,世界动漫发展正处于黄金期,而国产动漫正

♦~动漫的定义

动漫学是以漫画、动画、游戏(即通常所说的ACG) 为研究核心内容的,研究探讨其三者起源、发展经 过、融合历程以及未来发展走向等内容,包括人物 形象设计、动画制作、故事情节创作、网络游戏、 图书小说、动画电影、周边玩具、人物配音、音乐 制作、服装设计、动漫产业链等各个与动漫相关的 领域的一门综合性学科。简言之,研究一切与动漫 相关的学问。

• 动漫、动画和漫画三个词语 从一开始就有着明确的指代, 错误的用法只会令原本清晰 的词义变得模糊,以讹传讹 并不可取。

4

♫~所谓动画 • 动画的定义:动画是指由许多帧 静止的画面,以一定的速度连续 播放时,肉眼因视觉残象产生错 觉,而误以为画面活动的作品。

• 由此,动画只是一种形式,与其 制作、出品国,由何改编而来、 播放形式等事项毫无关系。

景音乐(BGM)。 • 动画原创:依漫画改编的动画,由于动画的更新速度比

漫画快的关系,当动画的剧集快赶上漫画时,动画的剧 情就要脱离漫画剧情,开始动画原创。 • 同人:也叫二次创作,由漫画、动画、游戏、小说、影 视等作品甚至现实里已知的人物、设定衍生出来的文章 及其他如图片影音游戏等等,或“自主”的创作。 • COS:全称COSPLAY,装扮成漫画、动画、游戏、小说等 中的人物,也可以是原创。

7

♠~动漫的概论

动漫领域衍生出的许多术语均已经被广泛应用, 例如:正太、萝莉、御姐、百合、BL等。

• 动漫产业日益与游戏产业结合紧密,在日本已经 形成一个成熟的产业链,动漫已经从单单的平面 媒体和电视媒体扩展到游戏,书籍,网络,玩具 等众多领域。许多动漫游戏应运而生,例如《死 神bleach》PSP平台的游戏,也有许GALGAME 被改编成动漫作品。

• 当前,世界动漫发展正处于黄金期,而国产动漫正

数字图象处理课件(喻莉)-内部结构

数字电路的基本组成

任何组合电路都可表示为其所有输入信 号的最小项的和或者最大项的积的形式。 时序电路包含可记忆器件(触发器), 其反馈信号和输入信号通过逻辑关系再 决定输出信号。

输入项

输入 电路

与 阵 列

乘积项

或 阵 列

或项

输出 电路

ቤተ መጻሕፍቲ ባይዱ

PLD的逻辑符号表示方法

与门

乘积项

PROM结构

与阵列为全译码阵 列,器件的规模将 随着输入信号数量 n的增加成2n指数 级增长。因此 PROM一般只用于 数据存储器,不适 于实现逻辑函数。 EPROM和EEPROM

内部晶体震荡器

高速反向放大 器用于和外部 晶体相接,形 成内部晶体振 荡器。 提供将振荡波 形二分频成对 称方波的功能。

CPLD与FPGA的区别

CPLD 内部结构 Product-term 程序存储 内部EEPROM 资源类型 组合电路资源丰富 集成度 低 使用场合 完成控制逻辑 速度 慢 其他资源 保密性 - 可加密 FPGA Look-up Table SRAM,外挂EEPROM 触发器资源丰富 高 能完成比较复杂的算法 快 EAB,锁相环 一般不能保密

FPGA与CPLD的区别

FPGA为非连续式布线,CPLD为连续式布线。 FPGA器件在每次编程时实现的逻辑功能一样, 但走的路线不同,因此延时不易控制,要求开 发软件允许工程师对关键的路线给予限制。 CPLD每次布线路径一样,CPLD的连续式互连 结构利用具有同样长度的一些金属线实现逻辑 单元之间的互连。连续式互连结构消除了分段 式互连结构在定时上的差异,并在逻辑单元之 间提供快速且具有固定延时的通路。CPLD的 延时较小。

输出使 能选择

输出 选择

任何组合电路都可表示为其所有输入信 号的最小项的和或者最大项的积的形式。 时序电路包含可记忆器件(触发器), 其反馈信号和输入信号通过逻辑关系再 决定输出信号。

输入项

输入 电路

与 阵 列

乘积项

或 阵 列

或项

输出 电路

ቤተ መጻሕፍቲ ባይዱ

PLD的逻辑符号表示方法

与门

乘积项

PROM结构

与阵列为全译码阵 列,器件的规模将 随着输入信号数量 n的增加成2n指数 级增长。因此 PROM一般只用于 数据存储器,不适 于实现逻辑函数。 EPROM和EEPROM

内部晶体震荡器

高速反向放大 器用于和外部 晶体相接,形 成内部晶体振 荡器。 提供将振荡波 形二分频成对 称方波的功能。

CPLD与FPGA的区别

CPLD 内部结构 Product-term 程序存储 内部EEPROM 资源类型 组合电路资源丰富 集成度 低 使用场合 完成控制逻辑 速度 慢 其他资源 保密性 - 可加密 FPGA Look-up Table SRAM,外挂EEPROM 触发器资源丰富 高 能完成比较复杂的算法 快 EAB,锁相环 一般不能保密

FPGA与CPLD的区别

FPGA为非连续式布线,CPLD为连续式布线。 FPGA器件在每次编程时实现的逻辑功能一样, 但走的路线不同,因此延时不易控制,要求开 发软件允许工程师对关键的路线给予限制。 CPLD每次布线路径一样,CPLD的连续式互连 结构利用具有同样长度的一些金属线实现逻辑 单元之间的互连。连续式互连结构消除了分段 式互连结构在定时上的差异,并在逻辑单元之 间提供快速且具有固定延时的通路。CPLD的 延时较小。

输出使 能选择

输出 选择

《可编程逻辑器件》PPT课件

13

2) 与、或全编程: 代表器件是FPLA(Field Programmable Logic

Array) 3)与编程、或固定: 代表器件PAL(Programmable Array Logic) 和GAL(Generic Array Logic) 、EPLD、FPGA (Field Programmable Gate Array )。

2021/7/10

35

GAL16V8逻辑图及引脚图

1

0

8

16

24

31

CK

0

19

OLM C

2

( 19)

8

18

OLM C

3

( 18)

16

4

17 OLM C ( 17)

24

16

5

OLM C ( 16)

可编程逻辑器件PLD

LDPLD (低密度 PLD)

HDPLD (高密度PLD)

PROM FPLA PAL GAL EPLD iSP FPGA

2021/7/10

16

8.2 现场可编程逻辑阵列(FPLA)

组合电路和时序电路结构的通用形式

A0~An-1

W0 D0

W(2n-1) Dm

2021/7/10

17

32

卡诺图化简:

YL 0 B A

00 DC

00 1 01 1

01 11 10

1 1 11

11

10

YL 1

BA 00

01

11 10

DC

00

01

11

11

10 1 1

1

YL 2

BA 00

01

DC

00

糖蛋白 PPT课件

(二)O-连接糖蛋白

糖蛋白糖链与蛋白部分的丝/苏氨酸残基的羟基相 连,称为O-连接糖蛋白。

目录

(一) N—连接糖链的糖基化位点:

携带N—寡糖链的天冬酰胺也有一定 的位置特征,它总是出现在多肽链的 Asn-X—Ser或 Asn-X—Thr序列中。其 中的X可为脯氨酸以外的任意氨基酸。

目录

N—连接糖链的糖基化位点:

定义

一条或多条糖胺聚糖以共价键与核心蛋白形成的 化合物。

特点

糖占比例大,约一半以上,具有多糖性质。

分布

分布于软骨、结缔组织、角膜基质、关节 滑液、粘液、眼玻璃体等组织。

目录

蛋白聚糖的结构

组成

核心蛋白

葡萄糖胺

糖胺 糖胺聚糖

半乳糖胺 葡萄糖醛酸

糖醛酸 艾杜糖醛酸

目录

一、重要的糖胺聚糖

糖胺聚糖由二糖单位重复连接而成,不分支。

目录

二、糖蛋白寡糖链的功能

1. 对糖蛋白新生肽链的影响

参与新生肽链的折叠并维持蛋白质的正确 的空间构象;影响亚基聚合;糖蛋白在细胞内 的分拣和投送。

2. 对糖蛋白的生物活性的影响

保护糖蛋白不受蛋白酶的水解,延长其半衰期。

3. 参与分子的识别作用

目录

第二节 蛋白聚糖

Proteoglycan

目录

概述

目录

N—糖链的分类:

目录

糖蛋白中,肽链部 分的丝氨酸和苏氨酸含量常可达到氨基酸 总数的50%。这种糖蛋白的糖链中不具有 共同的核心序列,常见的核心至少有8种, 因此糖链的结构相互之间差异较大。

目录

O—连接糖链的糖基化位点:

O—连接糖链的糖基化位点通常存在 于糖蛋白分子表面丝氨酸和苏氨酸比较 集中且周围常有脯氨酸的序列中。

糖蛋白糖链与蛋白部分的丝/苏氨酸残基的羟基相 连,称为O-连接糖蛋白。

目录

(一) N—连接糖链的糖基化位点:

携带N—寡糖链的天冬酰胺也有一定 的位置特征,它总是出现在多肽链的 Asn-X—Ser或 Asn-X—Thr序列中。其 中的X可为脯氨酸以外的任意氨基酸。

目录

N—连接糖链的糖基化位点:

定义

一条或多条糖胺聚糖以共价键与核心蛋白形成的 化合物。

特点

糖占比例大,约一半以上,具有多糖性质。

分布

分布于软骨、结缔组织、角膜基质、关节 滑液、粘液、眼玻璃体等组织。

目录

蛋白聚糖的结构

组成

核心蛋白

葡萄糖胺

糖胺 糖胺聚糖

半乳糖胺 葡萄糖醛酸

糖醛酸 艾杜糖醛酸

目录

一、重要的糖胺聚糖

糖胺聚糖由二糖单位重复连接而成,不分支。

目录

二、糖蛋白寡糖链的功能

1. 对糖蛋白新生肽链的影响

参与新生肽链的折叠并维持蛋白质的正确 的空间构象;影响亚基聚合;糖蛋白在细胞内 的分拣和投送。

2. 对糖蛋白的生物活性的影响

保护糖蛋白不受蛋白酶的水解,延长其半衰期。

3. 参与分子的识别作用

目录

第二节 蛋白聚糖

Proteoglycan

目录

概述

目录

N—糖链的分类:

目录

糖蛋白中,肽链部 分的丝氨酸和苏氨酸含量常可达到氨基酸 总数的50%。这种糖蛋白的糖链中不具有 共同的核心序列,常见的核心至少有8种, 因此糖链的结构相互之间差异较大。

目录

O—连接糖链的糖基化位点:

O—连接糖链的糖基化位点通常存在 于糖蛋白分子表面丝氨酸和苏氨酸比较 集中且周围常有脯氨酸的序列中。

《逻辑器件FPGA》PPT课件

(4) EAB 构成查找表LUT ;

EAB在只读模式下编程,可构成查找表,用LUT查找表结果比用算法计算 快得多, 可实现乘法器, 数字滤波器等.

2)逻辑阵列块(L2A) 逻B)辑阵列(LAB)是由一系列的相邻LE构成的

图2-12

14

逻辑阵列块 (ALB)

1) LAB由8个LE

( 逻辑单元 ) 组成;

7

一般多个输入的查找表采用多个逻辑块级连的方式

d[3..0] 查找表 d[7..4] 查找表 d[11..0] 查找表

与门 与门 与门

(2 ) Altera 系列器件

8

Altera系列产品主要性能

Altera FLEX10K系列器件 9

FLEX10K系列器件特点如下:高密度阵列, 嵌入式可编程逻辑器件。 这类器件最大可达10万个典型门,5392个寄存器;采用0.5 μm CMOS SRAM工艺制造;具有在系统可配置特性 ( ISP );在所有 I/O端口中有输入/输出寄存器;3.3 V或5.0 V工作模式;由Altera公 司的MAX+plusⅡ开发系统提供软件支持。 包括嵌入式阵列、多组 低延时时钟和内部三态总线等结构特性,提供了复杂逻辑设计所需 的性能和集成系统级的要求。

2.4 现场可编程门阵列(FPGA) P26

3

FPGA : Field Programmable Gate Array 现场可编程门阵列

FLEX 10K系列器件

FPGA/CPLD 技

4

术

FPGA 与 CPLD 都是可编程逻辑器件。它们的规 模比较大,适合于时序,组合等逻辑电路应用场合, 它可以替代几十甚至上百块通用IC芯片。

全局信号和EAB的局部互连都可以驱 动写使能信号、时钟信号

GAL可编程逻辑器件的简介PPT课件

XOR(n)

XOR(n)=1时,

CLK

异或门相当于反相器

XOR(n)=0时, 异或门相当于跟随器

EDA讲座

Q 10 11 01 00

AC0 AC1(n)

来自相邻引脚

20

99(-72) 专用组合输出方式

来自 与阵

反馈

CLK

OE OLMC(n)

NC

NC

VCC

I/O(n)

XOR(n) NC CLK

EDA讲座

来自相邻引脚

26

99-7(4) 时序电路中的组合输出方式

来自 与阵

反馈

CLK

OE OLMC(n)

NC

XOR(n)

EDA讲座

CLK

NC OE

I/O(n)

27

99-7

OLMC的五种工作模式

SYN AC0 10 10

11 01 01

AC1(n) XOR(n) 输出极性

1

/

/

0 低电平有效 0

1 高电平有效

来自 与阵

反馈

CLK

OE OLMC(n)

NC

NC

I/O(n)

XOR(n) NC

CLK

EDA讲座

NC

OE

来自相邻引脚

24

99-7

OLMC的五种工作模式

SYN AC0 10 10

11 01 01

AC1(n) XOR(n) 输出极性

1

/

/

0 低电平有效 0

1 高电平有效

0 低电平有效

1

1 高电平有效

1

0 低电平有效 1 高电平有效

0 低电平有效

0

1 高电平有效

数字电子技术基础阎石课件

2006年

数字电子技术基础阎石课件

返回

8.4.3 GAL的输入特性和输出特性

数字电子技术基础阎石课件

【例8.3.2 】 用PAL设计一个4为循环码计数器,并 要求所设计的计数器具有置零和对输出进行三态 控制的功能.

2006年

数字电子技术基础阎石课件

2006年

数字电子技术基础阎石课件

8.4 通用阵列逻辑GAL

GAL是在PAL器件的基础上发展起来的。它的基本结构 与PAL相同,即“与阵列可编程或阵列可固定”。但 GAL采用了电可擦除,电可改写的CMOS半导体制造工 艺,使得GAL器件不仅可以反复擦除、改写,为修改 设计带来了灵活性,而且降低了功耗,集成度也大大 提高。另外,GAL的逻辑结构采用了输出逻辑宏单元 OLMC,可以根据应用的不同配置成不同的输出结构。 一片GAL即可以配置为组合逻辑电路,也可以使时序 逻辑电路或者是两者的组合,很灵活。

数字电子技术基础阎石 课件

2020/11/21

数字电子技术基础阎石课件

8.1 概 述

l 图8.1.1 PLD电路中门电路的惯用画法 (a)与门

l (b)输出恒等于0的与门 l (c)或门 l (d)互补输出的缓冲器 l (e)三态输出的缓冲器

2006年

数字电子技术基础阎石课件

返回

图8.1.1 PLD电路中门电路的惯用画法

(a)与门(b)输出恒等于0的与门(c)或门 (d)互补输出的缓冲器(e)三态输出的缓冲器

2006年

数字电子技术基础阎石课件

返回

*8.2 现场可编程逻辑阵列(FPLA)

l 图8.2.1 FPLA的基本电路结构 l 图8.2.2 FPLA的异或输出结构 l 图8.2.3 时序逻辑型 FPLA的电路结构

Linux第6章图形界面应用程序开发ppt课件

其次,图形引擎中存在一些低效算法。不过 MicroWindows支持中文、日文、韩文等多种语言,而且 也支持Truetype字体,目前可知的MicroWindows版本是 0.91。

Page 13

精选课件ppt

6.2.4 OpenGUI

OpenGUI在 Linux 系统上存在已经很长时间了。最初 的名字叫 FastGL,只支持 256 色的线性显存模式,但目

OpenGUI 采用 LGPL 条款发布。OpenGUI 比较适合 于基于 x86 平台的实时系统,可移植性稍差,目前的发展 也基本停滞。

Page 14

精选课件ppt

6.2.5 GTK+简介

GTK+即GIMP ToolKit,是一套跨平台的图形工具包, 它来源于GIMP(GNU Minipulation Prigram),是使用C 语言作为其开发语言的,它基于LGPL授权,是源代码开 放完全免费的。

Page 23

精选课件ppt

.1MiniGUI程序框架

在 MiniGUI 中,窗口主函数名 字叫MiniGUIMain(),它负责创建 程序的主窗口。在这个过程中, MiniGUI 使 用 MAINWINCREATE 结构把Windows 中的创建窗口类和创 建窗口风格合二为一

Page 22

精选课件ppt

MiniGUI-Lite:MiniGUI-Lite上每个程序是单 独的进程,每个进程可创建多个窗口。 MiniGUI-Lite适合于具有完整UNIX特性的嵌 入式操作系统,如Linux。

MiniGUI-Standalone:MiniGUI-Standalone模 式下可以独立进程方式运行,不需多线程也不 需要多进程的支持。MiniGUI-Standalone模式 适合功能单一的应用场合,可以支持几乎所有 的操作系统。

Page 13

精选课件ppt

6.2.4 OpenGUI

OpenGUI在 Linux 系统上存在已经很长时间了。最初 的名字叫 FastGL,只支持 256 色的线性显存模式,但目

OpenGUI 采用 LGPL 条款发布。OpenGUI 比较适合 于基于 x86 平台的实时系统,可移植性稍差,目前的发展 也基本停滞。

Page 14

精选课件ppt

6.2.5 GTK+简介

GTK+即GIMP ToolKit,是一套跨平台的图形工具包, 它来源于GIMP(GNU Minipulation Prigram),是使用C 语言作为其开发语言的,它基于LGPL授权,是源代码开 放完全免费的。

Page 23

精选课件ppt

.1MiniGUI程序框架

在 MiniGUI 中,窗口主函数名 字叫MiniGUIMain(),它负责创建 程序的主窗口。在这个过程中, MiniGUI 使 用 MAINWINCREATE 结构把Windows 中的创建窗口类和创 建窗口风格合二为一

Page 22

精选课件ppt

MiniGUI-Lite:MiniGUI-Lite上每个程序是单 独的进程,每个进程可创建多个窗口。 MiniGUI-Lite适合于具有完整UNIX特性的嵌 入式操作系统,如Linux。

MiniGUI-Standalone:MiniGUI-Standalone模 式下可以独立进程方式运行,不需多线程也不 需要多进程的支持。MiniGUI-Standalone模式 适合功能单一的应用场合,可以支持几乎所有 的操作系统。

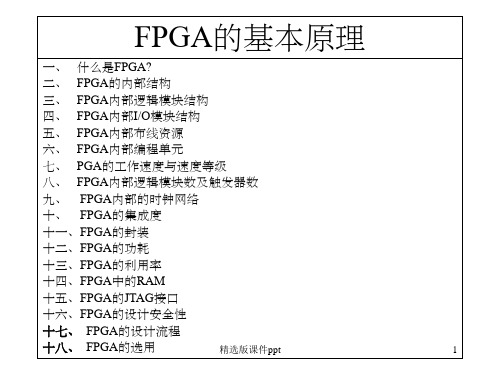

FPGA的基本原理(详细+入门)

l 闪速存储器(FLASH MEMORY):完全擦除或擦除一段。

精选版课件ppt

16

3、 晶体管开关

80年代中期,XILINX和Altera推出了利用晶体管 作为开关单元的FPGA器件。存储器单元来控制开关, 而存储单元是可以擦除和重新编程的,从而使得采用 这种技术的FPGA具有可重复编程性。

SRAM 开关单元由一个5个晶体管组成的RAM单元和1 个通过晶体管(称为可编程互连点,PIP: Programmable Interconnect Point)组成。PIP控制分段 连线的连接情况(即:连或不连),PIP受RAM单元控 制,位于PIP晶体管两边的分段连线是连还是不连由 RAM单元的值决定。

精选版课件ppt

11

• ACT1模块是如何实现三输入与门的?

GND Y

Y A B C

精选版课件ppt

12

2、查表型FPGA结构

两输入与门:

4 X 1 RAM 表:

精选版课件ppt

13Biblioteka 四、 FPGA内部I/O模块结构

FPGA的I/O引脚都可设置为:输入、输出、 双向、三态四种状态

精选版课件ppt

l PAL 即 Programmable array logic,是70年代末80年代初由Monolithic Memories Inc。(现为AMD的一部分)首先推出。它是一种熔丝可编 程的器件,采用双极性工艺生产,可用来把几片分立的TTL电路集成 到一片PAL中。PAL是一次性编程的可编程逻辑器件。

精选版课件ppt

24

十四、FPGA中的RAM

l 单口RAM l 同步双口RAM:Actel 公司的3200DX 系列、42MX系列。 l FPGA中RAM的容量 l FPGA中RAM的速度:Actel公司的 42MX系列FPGA的SRAM读写时间为5ns。

精选版课件ppt

16

3、 晶体管开关

80年代中期,XILINX和Altera推出了利用晶体管 作为开关单元的FPGA器件。存储器单元来控制开关, 而存储单元是可以擦除和重新编程的,从而使得采用 这种技术的FPGA具有可重复编程性。

SRAM 开关单元由一个5个晶体管组成的RAM单元和1 个通过晶体管(称为可编程互连点,PIP: Programmable Interconnect Point)组成。PIP控制分段 连线的连接情况(即:连或不连),PIP受RAM单元控 制,位于PIP晶体管两边的分段连线是连还是不连由 RAM单元的值决定。

精选版课件ppt

11

• ACT1模块是如何实现三输入与门的?

GND Y

Y A B C

精选版课件ppt

12

2、查表型FPGA结构

两输入与门:

4 X 1 RAM 表:

精选版课件ppt

13Biblioteka 四、 FPGA内部I/O模块结构

FPGA的I/O引脚都可设置为:输入、输出、 双向、三态四种状态

精选版课件ppt

l PAL 即 Programmable array logic,是70年代末80年代初由Monolithic Memories Inc。(现为AMD的一部分)首先推出。它是一种熔丝可编 程的器件,采用双极性工艺生产,可用来把几片分立的TTL电路集成 到一片PAL中。PAL是一次性编程的可编程逻辑器件。

精选版课件ppt

24

十四、FPGA中的RAM

l 单口RAM l 同步双口RAM:Actel 公司的3200DX 系列、42MX系列。 l FPGA中RAM的容量 l FPGA中RAM的速度:Actel公司的 42MX系列FPGA的SRAM读写时间为5ns。

双荧光素酶报告基因 ppt课件

ppt课件

8

在这个过程中:

1.“基因剪刀”

剪切DNA的酶就像一把“基因剪刀”

2.“缝纫针”

连接不同来源DNA分子的酶就像一根“缝纫针”,使 二者连在一起

3.“交通工具”

使用载体好比一辆车子

4.“乘客”

有用基因如IL2好比乘客,车子把乘客送进理想天堂 (宿主细胞)去繁衍生息,春华秋实,生产我们需要的产

品或开展基因治疗(IL2/LAppKt课→件 抗癌)。

9

一、目的基因的获取

1. 直接从染色体DNA中分离 2. 通过mRNA反的基因 5. PCR扩增目的基因 6. 人工体外合成基因片段

ppt课件

10

ppt课件

11

PUC8 PBUDCE41 YE

pGEX-4T M13 pAdV5

(1)M13 (2)plasmid (3)λ phage (4)casmid (5)BAC (6)YAC 13

常用的报告基因载体类型: 1)basic 载体:不含 P/E,用于检测启动 子活性。 2)control载体:含启动子,用于检测增 强子或沉默子的活性。

受态 2 加入重组质粒,冰浴30分钟,不要震荡 3 42℃水浴60~90S,热休克 4 马上冰浴

ppt课件

17

第七节 筛

抗药性筛选:ampr tetr kanr 插入表达筛选: 蓝白斑筛选: 测序 菌落或噬菌斑杂交筛选 酶切鉴定:插入否?插入方向?

ppt课件

18

转染 :指真核细胞由于外源DNA掺入而获得新 的遗传标志的过程 。 若此DNA未与宿主细胞DNA整合而获表达,称 “瞬时转染(transient transfection)”; 若与宿主细胞DNA整合并随后者的复制而复制 称“稳定转染(stable transfection)”。

课程资料:课件四:Galios理论

正规扩张 定义、性质、正规包

可分正规扩张 3个等价条件

Galios群与Galios对应

Galios群的定义 Galios对应 Galios群一些性质

有限群一些性质

有限群正规序列 有限群的合成因子 导子群 可解群

多项式的根塔与根号解

根塔、多项式可根号解 Galios基本定理 尺规作图问题

应用

有理数域上根不可根 多多边形

Galios理论复习提纲

Galios理论

主要研究的问题: 域F上的多项式的根是否可“根号”解出

主要研究方法: 域的代数扩张

重点: Calios对应

域的扩张

单扩张:代数扩张、超越扩张

有限代数扩张:扩张次数[E:F]

可分代数扩张:可分多项式、不可约多项 式的重根

分裂域

F上多项式的分裂域 分裂域的唯一性、自同构的个数

可分正规扩张 3个等价条件

Galios群与Galios对应

Galios群的定义 Galios对应 Galios群一些性质

有限群一些性质

有限群正规序列 有限群的合成因子 导子群 可解群

多项式的根塔与根号解

根塔、多项式可根号解 Galios基本定理 尺规作图问题

应用

有理数域上根不可根 多多边形

Galios理论复习提纲

Galios理论

主要研究的问题: 域F上的多项式的根是否可“根号”解出

主要研究方法: 域的代数扩张

重点: Calios对应

域的扩张

单扩张:代数扩张、超越扩张

有限代数扩张:扩张次数[E:F]

可分代数扩张:可分多项式、不可约多项 式的重根

分裂域

F上多项式的分裂域 分裂域的唯一性、自同构的个数

cDNA文库的构建和筛选PPT课件

Bait plasmid

AD gene prey gene

prey plasmid

诱饵与靶蛋白之间的 相互作用激活了报告 基因的表达

AD Gal4激活域

Prey (Y)

Bait (X)

BD

Gal4结合域

operator

LacZ

Repotep-

精选PPT课件

特点是:已知蛋 白产物,但对其 核酸序列或氨基 酸序列基本未知

25

C、利用同源基因中的目标基因序列

用不同来源的DNA分子制备成探针进行检测。 如:用来自鼠的基因A去检测人类中基因A 或基因家族中成员A去检测成员B

精选PPT课件

26

D、利用差异表达基因的扣除cDNA探针

表达目标基因

TTTTTTTTTTTTTTT

逆转录polyT引物

C、随机引物

精选PPT课件

15

第一节:将mRN有以下二种种方法:

A、降解mRNA-cDNA杂合链中的RNA, cDNA第一链3’端回折充当引物,形成第 二链

mRNA cDNA

E、洗脱的噬菌体感染宿主细胞后经繁殖扩增, 进行下一轮洗脱

F、经过3轮~5轮的“吸附-洗脱-扩增”后,与 靶分子特异结合的噬菌体得到高度富集。所得 的噬菌体制剂可用来做进一步富集有期望结合 特性的目标噬菌体。

精选PPT课件原理

A、转录激活因子GAL4

基因重组

cDNA

精选官或组织中的 比较多,在中 也有少数的克隆代表稀少mRNAs

如果某个基因有多种拼接方式,在中 也有代表该基因不同拼接方式的克隆。

精选PPT课件

✓ N端:147个氨基酸组成的DNA结合域(DNA binding domain,BD)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2016/10/12

7

9.4通用阵列逻辑GAL

➢ 9.4.3 GAL器件的结构控制字 GAL器件的输出形式取决于它的输出逻辑宏单元中的控制信号AC0

、AC1(n)及XOR(n)。在GAL器件中,这些控制信号的取值是由它的 结构控制字编程确定的。

2016/10/12

GAL16V8的控制字结构

8

SYN

同PAL一样,GAL有一个可编程的与阵列和一个不可编程的或阵列 ,

为了通用,GAL在或阵列之后接一个输出逻辑宏单元(Output Logic Macro Cell,OLMC)。

2016/10/12

3

9.4通用阵列逻辑GAL

该器件由10个输入缓冲 器、8个输出逻辑宏单元 、8个三态输出缓冲器和8 个输出反馈缓冲器、一 个可编程与阵列组成。

2016/10/12

13

9.4通用阵列逻辑GAL

➢ 结构控制字各位功能: (1)同步位SYN

该位用以确定GAL器件具有组合型输出能力还是寄存器型输出能力 。 当SYN=1时,仅具有组合型输出能力; 当SYN=0时,可具有寄存器型输出能力。

2016/10/12

9

9.4通用阵列逻辑GAL

(2)结构控制位AC0 该位是公共控制位,与各OLMC(n)的AC1(n)位配合,控制OLMC(n)

2016/10/12

1

1

9.4通用阵列逻辑GAL

(5)乘积项(PT)禁止位 共有64位,分别控制逻辑图中与阵列的64个乘积项(与项PT0~PT63

),以便屏蔽某些不使用的乘积项。

2016/10/12

1

2

9.4通用阵列逻辑GAL

通过设置结构控制字同步位SYN、控制位AC0和AC1(n),可将 OLMC设置为5种不同的功能组合。

GAL16V8的逻辑结构示意图

2016/10/12

4

9.4通用阵列逻辑GAL

每个与门的输入端既可以接收8个固定的输入信号,也可以接收将输 出端配置成输入模式的8个信号。因此,GAL16V8最多有16个输入信 号,8个输出信号。组成或阵列的8个或门分别包含于8个OLMC中, 它们和与阵列的连接是固定的。

数字电路与系统

东南大学信息科学与工程学院

第九章 可编程逻辑器件

➢ 可编程逻辑器件的基本结构和电路表示方法 ➢ 可编程逻辑阵列PLA ➢ 可编程阵列逻辑PAL ➢ 通用阵列逻辑GAL ➢ 复杂可编程逻辑器件CPLD ➢ 现场可编程门阵列FPGA

2016/10/12

2

9.4通用阵列逻辑GAL

➢ 9.4.1 GAL器件的基本结构 特点:可多次编程,通常采用CMOS工艺。

中各数据选择器。

2016/10/12

1

0

9.4通用阵列逻辑GAL

(3)结构控制位AC1 共有8位,每个OLMC(n)均有单独的AC1(n)。

(4)相位控制位XOR(n) 当XOR(n)=1时,异或门起反相器作用,再经输出三态缓冲门反 相,引脚信号是与或阵列输出的同相信号; 当XOR(n)=0时,引脚输出反相信号。

2016/10/12

5

9.4通用阵列逻辑GAL

➢ 9.4.2 输出逻辑宏单元OLMC GAL16V8宏单元结构示意图

2016/10/12

6

9.4通用阵列逻辑GAL

OLMC是由一个8输入或门、一个异或门、一个D触发器和4个数据选 择器组成。8输入或门接收来自可编程与阵列的7个或8个与门输出, 完成或运算;异或门用来控制输出极性。