6 第六章 FlashROM与EMIF的接口(17张)

外部存储器接口

6.2 SDRAM接口设计

SRAM是Static Random Access Memory的缩写,中文含义为静态 随机访问存储器,它是一种类型的半导体存储器。“静态”是指只要 不掉电,存储在SRAM中的数据就不会丢失。这一点与DRAM不同, DRAM需要进行周期性的刷新操作。 同时,我们不应将SRAM与只 读存储器(ROM)和Flash Memory相混淆,因为SRAM是一种易失性 存储器,它只有在电源保持连续供应的情况下才能够保持数据。“随 机访问”是指存储器的内容可以任意顺序访问,而不管前一次访问的 是哪一个位置。

ACTV命令的作用是激活存储器中的相关页,以尽量降低后续访问的延迟。 每次读/写SDRAM中新的一行之前,EMIF会自动发出ACTV命令。

READ 读命令

对SDRAM的突发访问,读取3个数据

WRT 写命令

对SDRAM写3个数据

接口时序的设计

EMIF与SDRAM的接口时序由SDCTL、SDTIM和SDEXT寄存器 控制,如何设置上述时间参数,需要用户去查看具体SDRAM芯 片的器件手册

写操作保持时间,写触发之后地址、片选和字节使能信号的时钟周期数

读操作建立时间,读触发之前地址、片选和字节使能信号的时钟周期数 对外部CE空间两次访问的最小时间间距 读操作触发时间 8位异步接口 16位异步接口 32位异步接口 32位SDRAM 32位SBSRAM 8位SDRAM 16位SDRAM 8位SBSRAM 16位SBSRAM 读操作保持时间,读触发之后地址、片选和字节使能信号的时钟周期数

CE1CTL控制寄存器

参数 W_SETUP/R_SETUP

说明 读/写建立时间宽度

W_STROBE/R_STROBE 读/写触发时间宽度 W_HOLD/R_HOLD 读写保持时间宽度 异步器件数据总线宽度 MTYPE = 0时选择8位总线 MTYPE = 1时选择16位总线 MTYPE = 2时选择32位总线 配置ASIZE位确定了EM_A和EM_BA引脚的功能

EEPROM和FLASH的区别,单片机中为啥很少有EEPROM

EEPROM和FLASH的区别,单片机中为啥很少有EEPROMROM的发展ROM:Read-Only Memory,只读存储器。

以非破坏性读出方式工作,只能读出无法写入信息,信息一旦写入后就固定下来,即使切断电源,信息也不会丢失,所以又称为固定存储器。

最早的ROM是不能编程的,出厂时其存储内容(数据)就已经固定了,永远不能修改,也不灵活。

因为存在这种弊端,后来出现了PROM(Programmable read-only memory,可编程只读存储器),可以自己写入一次,要是写错了,只能换一块芯片。

因为只能写一次,还是存在很多不方便,于是出现了EPROM (Erasable Programmable Read-Only Memory,可擦除可编程只读存储器),这种存储器就可以多次擦除,但是这种可擦除的存储是通过紫外线进行擦除,擦除的时候也不是很方便。

引用一个比如:如果你往单片机下载一个程序之后发现有个地方需要加一句话,为此你要把单片机放紫外灯下照半小时,然后才能再下一次,这么折腾一天也改不了几次。

随着技术的不断进步,EEPROM(Electrically Erasable Programmable Read-Only Memory,电可擦除可编程只读存储器)来了,解决了ROM过去历史中存在一些问题。

早期的EEPROM:早期的EEPROM的特点是可以随机访问和修改任何一个字节,可以往每个bit中写入0或者1,现在基本以字节为单位了。

早期的EEPROM具有较高的可靠性,但是电路更复杂,其成本也更高,因此EEPROM的容量都很小,从几KB到几百KB不等。

(有点类似前面说的因为工艺和制造成本的原因,RAM的容量也不大)。

如今的EEPROM支持连续多字节读写操作了,算是已经发展到很先进的水平了。

至此,大家今天看到的EEPROM,基本都是发展的很成熟的EEPROM 了。

Flash的发展Flash,又叫Flash Memory,即平时所说的“闪存”。

微机原理与接口技术第六章习题解答

微机原理与接口技术(楼顺天第二版)习题解答第6章 总线及其形成6、1答:内存储器按其工作方式的不同,可以分为随机存取存储器(简称随机存储器或RAM)与只读存储器(简称ROM)。

随机存储器。

随机存储器允许随机的按任意指定地址向内存单元存入或从该单元取出信息,对任一地址的存取时间都就是相同的。

由于信息就是通过电信号写入存储器的,所以断电时RAM 中的信息就会消失。

计算机工作时使用的程序与数据等都存储在RAM 中,如果对程序或数据进行了修改之后,应该将它存储到外存储器中,否则关机后信息将丢失。

通常所说的内存大小就就是指RAM 的大小,一般以KB 或MB 为单位。

只读存储器。

只读存储器就是只能读出而不能随意写入信息的存储器。

ROM 中的内容就是由厂家制造时用特殊方法写入的,或者要利用特殊的写入器才能写入。

当计算机断电后,ROM 中的信息不会丢失。

当计算机重新被加电后,其中的信息保持原来的不变,仍可被读出。

ROM 适宜存放计算机启动的引导程序、启动后的检测程序、系统最基本的输入输出程序、时钟控制程序以及计算机的系统配置与磁盘参数等重要信息。

6、2 答:存储器的主要技术指标有:存储容量、读写速度、非易失性、可靠性等。

6、3 答:在选择存储器芯片时应注意就是否与微处理器的总线周期时序匹配。

作为一种保守的估计,在存储器芯片的手册中可以查得最小读出周期t cyc (R)(Read Cycle Time)与最小写周期t cyc (W)(Write Cycle Time)。

如果根据计算,微处理器对存储器的读写周期都比存储器芯片手册中的最小读写周期大,那么我们认为该存储器芯片就是符合要求的,否则要另选速度更高的存储器芯片。

8086CPU 对存储器的读写周期需要4个时钟周期(一个基本的总线周期)。

因此,作为一种保守的工程估计,存储器芯片的最小读出时间应满足如下表达式:t cyc (R)<4T -t da -t D -T其中:T 为8086微处理器的时钟周期;t da 为8086微处理器的地址总线延时时间;t D 为各种因素引起的总线附加延时。

微机原理与接口技术(楼顺天第二版)第六章习题解答

微机原理与接口技术(楼顺天第二版)第六章习题解答微机原理与接口技术(楼顺天第二版)习题解答第6章总线及其形成6.1答:内存储器按其工作方式的不同,可以分为随机存取存储器(简称随机存储器或RAM)和只读存储器(简称ROM)。

随机存储器。

随机存储器允许随机的按任意指定地址向内存单元存入或从该单元取出信息,对任一地址的存取时间都是相同的。

由于信息是通过电信号写入存储器的,所以断电时RAM中的信息就会消失。

计算机工作时使用的程序和数据等都存储在RAM中,如果对程序或数据进行了修改之后,应该将它存储到外存储器中,否则关机后信息将丢失。

通常所说的内存大小就是指RAM 的大小,一般以KB或MB为单位。

只读存储器。

只读存储器是只能读出而不能随意写入信息的存储器。

ROM中的内容是由厂家制造时用特殊方法写入的,或者要利用特殊的写入器才能写入。

当计算机断电后,ROM中的信息不会丢失。

当计算机重新被加电后,其中的信息保持原来的不变,仍可被读出。

ROM适宜存放计算机启动的引导程序、启动后的检测程序、系统最基本的输入输出程序、时钟控制程序以及计算机的系统配置和磁盘参数等重要信息。

6.2 答:存储器的主要技术指标有:存储容量、读写速度、非易失性、可靠性等。

6.3答:在选择存储器芯片时应注意是否与微处理器的总线周期时序匹配。

作为一种保守的估计,在存储器芯片的手册中可以查得最小读出周(R)(Read Cycle Time)和最小写周期期tcyct(W)(Write Cycle Time)。

如果根据计算,微cyc处理器对存储器的读写周期都比存储器芯片手册中的最小读写周期大,那么我们认为该存储器芯片是符合要求的,否则要另选速度更高的存储器芯片。

8086CPU对存储器的读写周期需要4个时钟周期(一个基本的总线周期)。

因此,作为一种保守的工程估计,存储器芯片的最小读出时间应满足如下表达式:t cyc(R)<4T-t da-t D-T其中:T为8086微处理器的时钟周期;t da 为8086微处理器的地址总线延时时间;t D为各种因素引起的总线附加延时。

非易失性存储器Flash和EEPROM之间的差异与优缺点

非易失性存储器Flash和EEPROM之间的差异与优缺点在嵌入式系统中,Flash和EEPROM能够存储可用于通信或执行某些功能的数据。

它们可以通过多种不同的串行协议(包括SPI或串行外围设备接口)来连接存储设备。

在单片机中也集成了多种不同类型的SPI存储设备,包括Flash和EEPROM。

一、Flash和EEPROM之间的差异Flash和EEPROM均被视为非易失性存储器。

非易失性存储器意味着该设备能够保存数据且无需持续供电,即使关闭电源也能保存数据信息。

它们都是电子可写和可擦除存储器,用以存储单片机的应用程序及数据信息。

这些数据可在芯片上或芯片外存储信息。

尽管Flash和EEPROM设备都可以存储嵌入式设备中使用的信息,但是它们的体系结构和用于读取,写入和擦除数据的操作略有不同。

而EEPROM指的是电可擦可编程只读存储器是一种存储器,可以在字节级别读取,写入和擦除数据。

另一方面Flash是EEPROM的一种,在结构上以块的形式排列,在块中擦除数据,并且可以在字节级别读取或写入数据。

二、使用闪存与EEPROM有什么优缺点?使用闪存或EEPROM设备有很多优点和缺点:由于EEPROM以字节为单位运行其擦除功能,因此这增加了清除和编辑设备所花费的时间,但允许开发人员在需要时编辑特定部分。

闪存能够擦除大量数据,从而大大提高了擦除速度,并使设备可以更紧凑地存储信息。

但是由于这个原因,它也失去了编辑某些字节的能力,从而迫使开发人员在进行任何更改时都重写整个数据块。

在存储设备上执行多个擦除和写入周期将导致其最终随着时间的推移而降级。

使用EEPROM的优点之一是使用寿命更长。

EEPROM在其生命周期内最多可以执行1000000个擦除/重写周期。

根据闪存的类型,闪存的使用寿命会缩短,大多数闪存产品在磨损开始恶化存储完整性之前,能够承受大约10000至1000000次擦除/写入循环。

就大小和成本而言,闪存具有比EEPROM更小的存储单元尺寸,并且实现成本更低。

EMIF_NandFlash文档

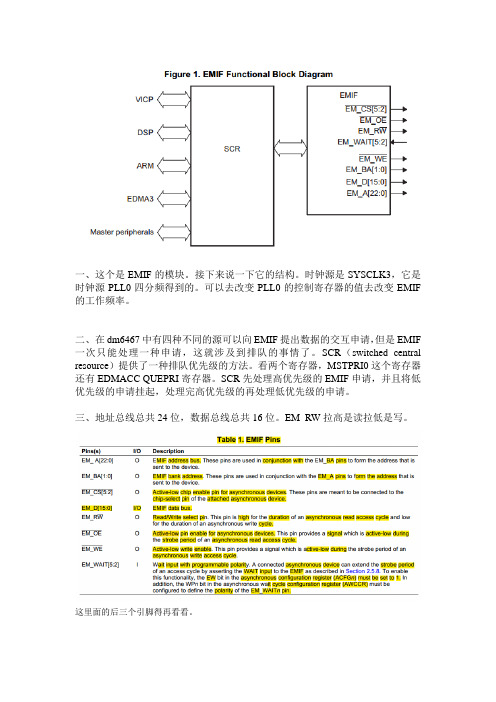

一、这个是EMIF的模块。

接下来说一下它的结构。

时钟源是SYSCLK3,它是时钟源PLL0四分频得到的。

可以去改变PLL0的控制寄存器的值去改变EMIF 的工作频率。

二、在dm6467中有四种不同的源可以向EMIF提出数据的交互申请,但是EMIF 一次只能处理一种申请,这就涉及到排队的事情了。

SCR(switched central resource)提供了一种排队优先级的方法。

看两个寄存器,MSTPRI0这个寄存器还有EDMACC QUEPRI寄存器。

SCR先处理高优先级的EMIF申请,并且将低优先级的申请挂起,处理完高优先级的再处理低优先级的申请。

三、地址总线总共24位,数据总线总共16位。

EM_RW拉高是读拉低是写。

这里面的后三个引脚得再看看。

四、EMIF的三种工作模式,一个是normal模式,另一个是select strobe模式,第三个是NAND flash 模式。

normal的工作模式在整个异步的访问期间,select strobe模式是在strobe期间。

这两个模式好理解,主要指的是EM_CS这个信号的持续时间做区分。

对于NAND_FLASH模式,EMIF的硬件能计算出ECC(error correction code)在每512个字节数据的传输。

五、EM_BA[1:0]这里的bit1用的对应的16位的传输,bit0对应的是8bit位的传输。

EM_BA[1]如果连到A[0],就是16bit的数据传输。

六、读写操作的正常模式写时序:与NANDFLASH互联模式。

驱动CLE和ALE。

如果用EM_A2和EM_A1这个去连接CLE和ALE,00h是让这两个信号都为低。

10HS是CLE高ALE低。

01H是CLE低ALE高。

如果连接到NANDFLASH的基地址是42000000,如果想让CLE高ALE低。

映射地址应该是0x42000010hNAND的读操作NAND访问周期由命令,地址,还有数据三个阶段。

存储器及其接口课件

PART 03

常见存储器类型及其特点

REPORTING

DRAM(动态随机存取存储器)

特点

DRAM是计算机中最常用的存储器 类型,它具有容量大、价格低廉等优 点。但是,DRAM需要定期刷新以 保持数据存储,因此功耗相对较高。

应用

计算机的内存条(RAM)就是由 DRAM芯片组成的。

SRAM(静态随机存取存储器)

CPU通过地址总线向存储器发送地址信号,指定 需要访问的存储单元的位置。

CPU通过控制总线访问存储器

CPU通过控制总线向存储器发送控制信号,如读 /写信号,以指导要执行的操作。

3

CPU通过数据总线访问存储器

CPU通过数据总线从存储器读取数据或向存储器 写入数据。

存储器对CPU的响应过程

存储器接收到CPU的访问要求 后,根据地址信号找到相应的 存储单元。

随着半导体技术的发展,出现了 基于晶体管的随机访问存储器( RAM)和只读存储器(ROM) 。这些存储器具有更高的速度和

更小的体积。

现代存储器

随着集成电路技术的发展,出现 了更小、更快、更可靠的存储器

,如动态随机访问存储器( DRAM)、静态随机访问存储器

(SRAM)和闪存等。

存储器的应用领域

计算机系统

特点

SRAM的读写速度非常快,但是 它的功耗也相对较高。由于 SRAM的制造工艺复杂,因此价 格也相对较高。

应用

计算机的CPU缓存(Cache)就 是由SRAM芯片组成的。

ROM(只读存储器)

特点

ROM可以存储大量数据,但是一旦写入,就不能修改或只能以困难的方式修改 。因此,ROM通常用于存储固件或其他不需要更改的数据。

数据传输与CPU的时钟 信号不同步,适用于较

外部存储器接口 SDRAM实验_PPT幻灯片

配置CE空间

详解全局控制寄存器(EGCR) 0x221= 0000 0010 0010 0001

ARDY: EMIF没有准

备好

EMIF不会接 受HOLD请

求

0000001000100001

MEMFREQ:01 CLKMEM 频率=CPU时钟频率的1/2

WPE:写后 使能bit

MEMCEN: 1 CLKMEM 引脚提供存

重新使能 写成功

再重跑程序,即配置好EMIF,SDRAM

外部存储器接口 EMIF

外部存储器接口(EMIF),External Memory Interface,是TMS DSP 器件上的一种接口。 EMIF控制DSP和外部存储器之间的所有数据传输 一般来说,EMIF可实现DSP与不同类型存储器的连接。 3种类型的存储器提供无缝接口:

异步存储器,比如ROM,FLASH 同步突发SRAM(SBSRAM) 同步DRAM(SDRAM)

HX-5509开发板 EMIF

EMIF上扩 展CPLD对 CE空间读 写进行控

制

HX-5509开发板 EMIF

接CPLD和不接CPLD的操作区别: 不接CPLD,对EMIF的操作,就只需要要配置好相关存储器的寄存器 之后,就可以直接进行读写访问 接CPLD,相当于在EMIF操作的前期映射了一个全局的管理寄存器, 要对EMIF操作,就必须先对CPLD进行读写,再进行EMIF的读写操作

SDRAM的访问

SDRAM数据操作的流程图

注意:此处 是字地址!

此时在 CE0

SDRAM的访问

修改buffer数据增量的步长再测试:

SDRAM的访问

注释掉EMIF的配置再测试(注意:要重新上电再跑程序)

第6讲 外设应用之EMIF篇..

SRAM vs DRAM

SRAM是Static

Random Access Memory的缩写 ,中文含义为静态随机访问存储器,它是一种类 型的半导体存储器。“静态”是指只要不掉电, 存储在SRAM中的数据就不会丢失。这一点与 DRAM不同,DRAM需要进行周期性的刷新操作 。

同只读存储器(ROM)和Flash

NOR 的特点是芯片内执行(XIP,eXecute In Place),这样应用程序可以直接在闪存内运行 ,不必再把代码读到系统 RAM 中。NOR 的传输 效率很高,在 1~4MB 的小容量时具有很高的成 本效益,但是很低的写入和擦除速度大大影响了 它的性能。

NAND 结构能提供极高的单元密度,可以达到高存 储密度,并且写入和擦除的速度也很快,这也是 为何所有的 U 盘都使用 NAND 闪存做为存储介 质的原因。应用 NAND 的困难在于闪存和需要特 殊的系统接口。

NAND flash和NOR flash的对比

易于使用

可以非常直接地使用基于NOR的闪存,可以像其 它内存那样连接,并可以在上面直接运行代码。 由于需要I/O接口,NAND要复杂得多。各种 NAND器件的存取方法因厂家而异。在使用 NAND器件时,必须先写入驱动程序,才能继续 执行其它操作。向NAND器件写入信息需要相当 的技巧,因为设计师绝不能向坏块写入,这就意 味着在NAND器件上自始至终都必须进行虚拟映 像。

4Ch

60h 64h 70h

EIMCR

NANDFCR NANDFSR NANDF1ECC

第六讲 DSP外设之 外部存储器接口 (EMIF)

内容概述

各存储器间的对比

EMIF与存储器间的接口

C55xEMIF C55xEMIF

微机原理与接口技术(楼顺天)-第6章1

6.1 存储器分类

微机系统中存储器的层次结构如下图所示. 微机系统中存储器的层次结构如下图所示.

CPU内部寄存器组 及内部一级Cache

系统板上 二级Cache

主存储器(半导体存储器) 虚拟存储器 辅助存储器(磁盘,磁带,光盘)

6.2 存储器主要技术指标

1. 存储容量 2. 读写速度 半导体存储器芯片的速度一般用存取时间和 存储周期两个指标来衡量. 存储周期两个指标来衡量. 在选择存储器芯片时应注意是否与微处理器的 总线周期时序匹配.作为一种保守的估计, 总线周期时序匹配.作为一种保守的估计,在 存储器芯片的手册中可以查得最小读出周期 tcyc(R)(Read Cycle Time)和最小写周期 和最小写周期 tcyc(W)(Write Cycle Time). .

1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15

VCC WE CS2 A3 A2 A1 OE A0 CS1 D7 D6 D5 D4 D3

I几种常用存储器芯片介绍

本章要点

最后需要指出的是, 最后需要指出的是,在8086微机系统中 微机系统中 进行内存电路设计时, 进行内存电路设计时,一定要注意寄片存储器 与偶片存储器要分开设计,并注意数据总线的 与偶片存储器要分开设计, 连接及片选信号的产生. 连接及片选信号的产生.

本教案内容

第6章 存储器设计 章 1.存储器分类及主要技术指标

2.常用存储器芯片介绍 常用存储器芯片介绍

位扩展 字节扩展 字节和位扩展 存储器地址译码 扩展存储器接口电路设计 总线负载能力

3.扩展存储器设计 扩展存储器设计

6.1 存储器分类

分析ARM外设flash及SDRAM的地址连接

分析ARM外设flash及SDRAM的地址连接分析ARM外设flash及SDRAM的地址连接先提一下位宽的概念,对于具体器件而言,它的位宽是一定的,所谓位宽,指的是“读/写操作时,最小的数据单元”──别说最小单元是“位”,一般设备上没有单独的“位操作”,修改位时通过把整个字节、字或双字读出来、修改,再回写。

AM29L800BB 这种nor flash位宽是16位。

K4S561632C这种SDRAM位宽是32位。

对于CPU来说,一个地址对应的是一个字节(8位),也就是说CPU的地址线(A0~A20)对应的最小数据单元是字节。

这里需要注意的是,不要把“外设的位宽”和“CPU的位数”这两个概念混淆了。

外设的位宽是读写外设的最小数据单元,CPU位数是CPU可以一次处理的字节数,32位CPU 可以一次处理4字节数据。

好了,相信你也已经发现问题了吧。

既然CPU最小数据单元是8位,flash位宽是16位,那在我们写程序时会特意进行16位操作吗?显然不会,我们写代码时,可不管外设到底是多少位。

这是如何实现的呢?原因在于存储控制器(Memory Controller)这个中间层。

存储控制器根据NOR FLASH的位宽,每次总是读/写16位数据。

以读操作为例:CPU进行8位操作时,它选择其中的8位返回给CPU;CPU进行16位操作时,它直接把这16位数据返回给CPU;CPU进行32位操作时,它发起2次读/写,把结果组合成32位返回给CPU。

现在的连线是:CPU的(ADDR1-ADDR20)接到16位的NOR FLASH (A0-A19),即CPU的ADDR0不接──这说明:不管ADDR0是0还是1,NOR FLASH接收到的地址是一样的。

CPU发出地址0bxxxxxxxxx0、0bxxxxxxxxx1时,NOR FLASH 看到的都是0bxxxxxxxxx,返回给存储控制器的都是同一个16位数据。

再由Memory Controller选择其中的低8位或高8位给CPU。

外部存储器接口优秀课件

Hold≥(th-toh(f))/E=(1-0)/10=0.1 一般Setup可取1,这样由第1个条件便可以得出Strobe的值为 10;再由第2和第3个条件得到Hold的值为1。

FLASH 的写时序

FLASH 的写时序

FLASH 的写时序

DRAM是Dynamic RAM的缩写,中文含义为动态随机存取存储器, 需要不断的刷新,才能保存数据。而且是行列地址复用的,许多都有 页模式。SDRAM:Synchronous DRAM,即数据的读写需要时钟 来同步。

一个是静态的,一个是动态的,静态的是用的双稳态触发器来保存信 息,而动态的是用电子,要不时的刷新来保持。

CExCTL寄存器

SDCTL寄存器

SDTIM寄存器

SDEXT寄存器

6.2 SDRAM接口设计

SRAM是Static Random Access Memory的缩写,中文含义为静态 随机访问存储器,它是一种类型的半导体存储器。“静态”是指只要 不掉电,存储在SRAM中的数据就不会丢失。这一点与DRAM不同, DRAM需ห้องสมุดไป่ตู้进行周期性的刷新操作。 同时,我们不应将SRAM与只 读存储器(ROM)和Flash Memory相混淆,因为SRAM是一种易失性 存储器,它只有在电源保持连续供应的情况下才能够保持数据。“随 机访问”是指存储器的内容可以任意顺序访问,而不管前一次访问的 是哪一个位置。

CE1CTL控制寄存器

FLASH 的读时序

FLASH 的读时序

数据是在Strobe阶段结束,ARE信号变高之前的时钟上升沿处 被DSP读取,因此可以得出读操作中CE1空间控制寄存器有关 参数设定的3个限制条件,设EMIF时钟频率为100MHz,得时 钟周期E为10ns,则计算如下:

EMIF接口

外部设备连接接口包括外部存储器连接接口(EMIF)、主机接口(HPI)等。

外部存储器接口主要用来同并行存储器连接,这些存储器包括SDRAM、SBSRAM、Flash、SRAM存储器等,外部存储器接口还可以同外部并行设备进行连接,这些设备包括并行A/D、D/A转换器、具有异步并行接口的专用芯片,并可以通过外部存储器接口同FPGA、CPLD等连接;主机接口主要用来为主控CPU和C55x处理器之间提供一条方便、快捷的并行连接接口,这个接口用来对DSP进行控制、程序加载、数据传输等工作。

这里主要是EMIF。

EMIF输入输出信号图:EMIF为3种类型的存储器提供了无缝接口:1 异步存储器,包括ROM,FLASH,异步SRAM2 同步突发静态存储器(SBSRAM)3 同步动态存储器(SDRAM)异步存储器可以是静态随机存储器(SRAM)、只读存储器(ROM)和闪存存储器等存储器,在实际使用中还可以用异步接口连接并行A/D采样器件、并行显示接口等外围设备,但使用这些非标准设备时需要增加一些外部逻辑来保证设备的正常使用。

在使用外部存储器接口时应区分字寻址和字节寻址之间的区别,当TMS320C55x访问数据时,CPU用23位地址访问16位字,该方式下数据空间被分成128页,每页字长64K。

CPU访问程序代码时,用24位地址访问8位字节,DMA控制器访问存储器时也采用字节寻址方式。

如果多个请求服务同时到达,EMIF会根据每个请求优先级来进行处理。

最高为HOLD,最低为刷新。

对EMIF编程时,必须了解外部存储器地址如何分配给片使能空间,即CE空间,每个CE空间可以同那些类型的存储器连接,以及用那些寄存器位来配置CE空间。

TMS320C55x的外部存储器映射在存储空间的分布,相应于EMIF的片选使能信号,例如CE1空间的存储器,则必须将其片选引脚连接到EMIF的CE1引脚。

当EMIF访问CE1空间时,驱动CE1变低。

数据页字寻址方式地址范围(16进制)外部存储器字节寻址方式地址范围(16进制)第2页后64K字节3-3102 8000-1F FFFFCE0空间(4M-320K)字节05 0000-3F FFFF32-6320 0000-3F FFFF CE1空间4M字节40 0000-7F FFFF64-9540 0000-5F FFFF CE2空间4M字节80 0000-BF FFFF96-12760 0000-7F FFFF 当MP/MC=0CE3空间长度为(4M-32K)字节剩余地址空间被片上ROM占用当MP/MC=1CE3空间长度为4M字节C0 0000-FF FFFFTMS320C5510外部存储器映射中的最高地址单独分配给CE3空间,或由CE3及内部的DSP ROM共享。

FX系列PLC编程及应用(廖常初)第6章

3.计算机链接 计算机链接用于一台计算机与一台配有 RS232C 通信接口的 PLC 通信,计算机也可以通 过 RS-485 通信网络与最多 16 台 PLC 通信, RS485 网络与计算机的 RS-232C 通信接口之间需 要使用FX-485PC-IF转换器。 计算机链接与Modbus通信协议中的ASCII模 式相似,由计算机发出读、写PLC中的数据的 命令帧,PLC收到后自动生成和返回响应帧。

2.现场总线AS-i网络 AS-i (执行器传感器接口)网络已被纳入 IEC 62026 标准,响应时间小于 5ms,由总线提供电源。AS-i用两芯电缆连接现场的传感器和执行器。 三菱的 FX2N-32ASI-M 是AS-i网络的主站模块,最长通信距离 100m,使用 两个中继器可以扩展到300m。波特率为167kbit/s,最多可以接31个从站。

6.2 计算机通信的国际标准 6.2.1 开放系统互连模型

物理层的下面是物理媒体,例如双绞线、同轴电缆和光纤等。物理层定义 了传输媒体端口的机械、电气功能和规程的特性。 数据链路层的数据以帧为单位传送,每一帧包含数据和同步信息、地址信 息和流量控制信息等。通过校验、确认和要求重发等方法实现差错控制。 应用层为用户的应用服务提供信息交换,为应用接口提供操作标准。

7.校验和代码 校验和代码用来校验接收到的信息中的数据是否正确。将报文的第一个控 制代码与校验和代码最低两位十六进制数作为校验和代码,以 ASCII 码的形式放在报文的末 尾。接收方收到校验和后,根据接收到的字符计算出校验和代码,并与接收 到的校验和代码比较,可以检查出接收到的数据是否出错。 D8120的b13位为1时,要求有校验和代码。 8.控制代码CR/LF 选择控制协议格式4时,PLC会在它发出的报文的最后面自动加上回车和换 行符,即控制代码CR/LF,对应的十六进制数为0DH和0AH。 11.计算机链接通信的错误诊断 有通信错误时,无法确认(NAK)的响应报文中的错误代码见表6-8。 PLC的错误不是用NAK报文发送出去,错误代码储存在D8063中。

华客PC3000flashFE教材目录

目录第一章FLASH 存储芯片的介绍1.1 FLASH存储芯片类型1.2 NAND FLASH 存储芯片的分类1.2.1 SLC1.2.2 MLC1.2.3 TLC1.2.4 SLC、MLC、TLC闪存芯片的区别1.3 FLASH存储芯片的物理构成1.4 FLASH存储芯片的逻辑结构1.4.1 通道1.4.2 总线宽度1.4.3 页1.4.4 块1.5 FLASH存储芯片的数据存储原理1.5.1 块间页交换1.5.2 通道(dump plane)间页交换1.5.3 通道间块交换1.5.4 通道间块间页交换1.5.5 通道间字节交换1.6 FLASH存储的工作原理1.6.1 引脚定义1.6.2 NAND FLASH命令1.6.3 地址周期1.6.4 坏块1.6.5 ECC校验1.7 FLASH存储芯片的型号及FLASH ID的含义1.7.1 FLASH芯片的型号1.7.2 FLASH芯片的ID1.8 NAND FLASH存储芯片的应用1.8.1 CF卡1.8.2 SD卡1.8.3 TF卡1.8.4 U盘1.8.5 SSD固态硬盘第二章U盘的介绍2.1 U盘的介绍2.1.1 U盘基础知识2.1.2 常见的主控型号2.2 U盘物理故障的表现及分类2.2.1 U盘物理故障的表现2.2.2 U盘物理故障的分类2.2.3 U盘物理故障处理方法第三章固态硬盘的介绍3.1 固态硬盘的结构3.2 固态硬盘的优缺点3.3 固态硬盘常见主控型号第四章工具PC3000 FLASH介绍4.1 PC3000 FLASH硬件介绍4.1.1 PC3000 FLASH 电路飞线板介绍4.1.2 PC3000 FLASH TSOP-48座子介绍4.1.3 PC3000 FLASH TSOP-48座子介绍4.1.4 PC3000 FLASH LGA/TLGA-52座子介绍4.2 PC3000 FLASH程序主界面介绍4.2.1 创建数据恢复任务4.2.2 打开已创建过的任务4.3 如何用PC3000FLASH恢复NAND 芯片数据4.3.1 芯片读取4.3.2 芯片镜像文件的导入4.3.3 创建转换图形4.3.4 查看有无坏字节4.3.5 用ECC修复bit错误4.3.6 分析页结构4.3.7 查看有无异或(XOR)4.3.8 解析异或数据4.3.9 编辑页结构4.3.10 分析有无分离与结合4.3.11 去除分离与结合4.3.12 选择编译方式4.3.13 调整分析第五章PC3K FLASH分析操作案例5.1 主控PS2251分析案例5.2 主控SM3257分析案例5.3 主控IS916分析案例5.4 主控AU6989分析案例5.5 主控AU6998AN分析案例5.6 主控IS916EN分析案例5.7 主控TC58NC6623分析案例5.8 主控闪迪20-82-00198-3分析案例第六章工具Flash Extractor介绍6.1 Flash Extractor(简称FE)设备介绍6.1.1 FE设备结构6.1.2 如何更换座子6.1.3 FE TSOP-48座子介绍6.1.4 FE TSOP-56座子介绍6.1.5 FE TLGA座子介绍6.1.6 FE VBGA-100座子介绍6.1.7 FE BGA-152座子介绍6.1.8 FE飞线板6.2 Flash Extractor程序主界面介绍6.2.1 NAND Flash Reader读取芯片6.2.1.1 拆芯片6.2.1.2 芯片放置6.2.1.3 NAND的读取6.2.1.4 读取重试6.2.1.5 DDR的选择6.2.1.6 WL V2的选择6.3 Flash Extractor菜单基础介绍6.3.1 Model6.3.2 Mix Editor6.3.3 Mix Editor Functions6.3.4 Layout6.3.5 Layout name6.3.6 Chip numbers6.3.7 ECC6.3.8 Common errors6.4 Flash Extractor 编译程序6.4.1 Block Number6.4.2 Virtual Translator6.4.3 Sector Number Slow第七章Flash Extractor分析操作案例7.1 主控SSS6695分析案例7.2 主控IS916分析案例7.3 主控TC58NC6623分析案例7.4 主控PS2251分析案例7.5 主控SANDISK 82-00523-1分析案例7.6 主控CBM2090分析案例7.7 SSD主控PS3109分析案例第八章定义图8.1 SD卡8.2 TF卡8.3 U盘。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9

读操作时序

编程操作的流程

10

11

编程操作时序

擦除操作的 流程和时序

12

+3.3V 37

C2 GND 29 31 33 35 38 40 42 44 30 32 34 36 39 41 43 45 DSP_ED0 DSP_ED1 DSP_ED2 DSP_ED3 DSP_ED4 DSP_ED5 DSP_ED6 DSP_ED7 DSP_ED8 DSP_ED9 DSP_ED10 DSP_ED11 DSP_ED12 DSP_ED13 DSP_ED14 DSP_ED15 DSP_ED[15:0]

14

读操作参数的约束条件: 读操作参数的约束条件:

SETUP + STROBE ≥ (tacc(m) + tsu + tdmax)/tcyc SETUP + STROBE + HOLD≥(trc(m))/tcyc HOLD ≥ (th – tdmin – toh(m))/tcyc

写操作参数的约束条件: 写操作参数的约束条件: STROBE ≥ (twp(m))/tcyc SETUP + STROBE ≥(txw(m))/tcyc HOLD ≥(max(tih(m), twr(m)))/tcyc SETUP + HOLD + STROBE ≥(twc (m)) / tcyc

2

TMS320C6201/6701 EMIF与 与 FlashROM接口的设计原理

• FlashROM不在DSP时钟指导工作下, 为异步工作方式; • DSP具有专门的FlashROM控制信号, 可支持任何类型的异步FlashROM存储 器; • 16 位FlashROM数据接口。

3

4

EMIF与FlashROM接口信号 与 接口信号

FlashROM(AM29LV160DB)的

特点和工作原理

• 具有自动的嵌入式编程写入和擦除算法; • 具有Data# Polling and toggle软件标示位, 可以利用软件方法检测编程操作的成功状 态; • 具有RY/BY管脚,可以利用硬件方法检测 编程写入/擦除操作的状态(不适合44脚 SO封装); • 具有硬件复位引脚 和准确的复位逻辑。

1 硬件复位 2 通用命令 Read(读)命令 ( Program(编程)命令 (编程) Chip Erase(擦除)命令 (擦除)

7

硬件复位

因为Flash中主要包含了 中主要包含了DSP的运行程序,所以要保证 的运行程序, 因为 中主要包含了 的运行程序 所以要保证Flash的复位时间 的复位时间 少于DSP的复位时间。所以复位主要以上电复位为主。 的复位时间。 少于 的复位时间 所以复位主要以上电复位为主。

25 24 23 22 21 20 19 18 8 7 6 5 4 3 2 1 48 17 16 9 11 26 28

DSP_AWE# DSP_CE1# DSP_AOE#

+3.3V

A0 DQ0 A1 DQ1 A2 DQ2 A3 DQ3 A4 DQ4 A5 DQ5 A6 DQ6 A7 DQ7 A8 DQ8 A9 DQ9 A10 DQ10 A11 DQ11 A12 DQ12 A13 DQ13 A14 DQ14 A15 DQ15/A-1 A16 A17 AM29LV160DB A18 A19/NC NC WE# NC CE# NC OE# Vcc BYTE# RY/BY RESET# Vss Vss

14 13 10

R2 10K

47 15 12

R1 2K 27 C1 0.01uF GND 46 GND

TMS320C6201/6701与AM29LV160DB的硬件接口

13

TMS320C6201/6701与Am29LV160DB接口的寄存器配置 与 接口的寄存器配置

可编程参数包括:

• 读建立 写建立 读建立/写建立 写建立(Read setup/write setup)时间 时间: 时间 存储器周期开始(CE#低电平,地址有效)到激活 读或写选通之间的时间。 • 读选通 写选通 读选通/写选通 写选通(Read strobe/write strobe)时间: 时间: 时间 激活和撤销读选通(ARE#)或写选通(AWE#)之 间的时间。 • 读保持 写保持 读保持/写保持 写保持(Read hold/write hold)时间: 时间: 时间 撤销读或写选通到周期结束(可能是地址改变或 AOE#信号撤销)之间的时间。

15

根据上面读操作和写操作参数约束和计算得到的 结果配置EMIF CE1存储空间的控制寄存器: 存储空间的控制寄存器: 结果配置 存储空间的控制寄存器

CE1空间控制寄存器的值设置为0x1B10A12。

16

17

DSP_EA[21:2]

DSP_EA2 DSP_EA3 DSP_EA4 DSP_EA5 DSP_EA6 DSP_EA7 DSP_EA8 DSP_EA9 DSP_EA10 DSP_EA11 DSP_EA12 DSP_EA13 DSP_EA14 DSP_EA15 DSP_EA16 DSP_EA17 DSP_EA18 DSP_EA19 DSP_EA20 DSP_EA21

第六章 FlashROM在核心电路中与DSP EMIF的

接口和地址分配

1 TMS320C6201/6701 EMIF与FlashROM 接 口的设计原理、EMIF接口特点和信号; 2 FlashROM(AM29LV160DB)的工作原理、 主要参数和接口时序; 3 EMIF与FlashROM(AM29LV160DB)的接口 逻辑、硬件接口、寄存器配; 4 FlashROM在DSP核心系统中的地址分配; 5 FlashROM的操作电源、功耗和封装。

5

AM29LV160DB原理结构

6

AM29LV160DB功能和通用命令 功能和通用命令

• AM29LV160DB是一种只读存储器,具有被写的能力。由

于它具有多次烧录和掉电信息不丢失的特点,可以在系统 中保存程序或常数据。 •FlashROM的读周期与C6000提供的时序是兼容的。 •对FlashROM写入数据比较复杂,为了执行一个写数据命 令需要对AM29LV160DB命令寄存器进行一系列写操作。 AM29LV160DB •主要的硬件和通用命令有: