基于FPGA的存储解决方案——闪存

闪存解决方案

闪存解决方案

《闪存解决方案》

随着科技的不断进步,人们对于存储设备的要求也越来越高。

传统的硬盘在速度和耐用性上逐渐显得有些滞后,而闪存作为一种新兴的存储解决方案,正逐渐受到人们的关注和青睐。

闪存技术是一种基于固态存储介质的存储技术,它具有速度快、体积小、耐用性强等优点。

因此,越来越多的电子产品开始采用闪存作为存储介质,比如智能手机、平板电脑、数码相机等。

而在计算机领域,固态硬盘(SSD)正逐渐取代传统的机械硬盘,成为新一代的存储解决方案。

闪存解决方案不仅在个人消费电子产品中得到应用,也在企业级应用中发挥着重要的作用。

比如,在数据中心中,人们正在大规模地部署闪存阵列来提高数据处理的速度和效率。

而在云存储领域,闪存也被广泛应用,以满足用户对于高速、稳定存储的需求。

然而,闪存技术也面临着一些挑战,比如成本高、容量有限、寿命有限等问题。

但随着技术的不断进步,这些问题也在逐渐得到解决。

未来,闪存技术有望进一步发展,成为更为成熟和稳定的存储解决方案。

总的来说,闪存解决方案正逐渐成为未来存储领域的主流。

它的出现或许会改变人们对于存储设备的认知和需求,也会为我们的生活和工作带来更多便利和可能性。

基于FPGA与NAND闪存的固态存储系统设计

d t t rg em o ua ei , n e o e i s g VHDL ln u g , o t r n io me t n I E9 1p o esc n r l aas a e Th d lr s o d g i tr rd s n i n g ui n g a e sf a wae e v r n n S r c s o t i o

a A N D a h nd N Fl s

Gu e gi g, u igYo ebn oP nxa Z n , uW n i n J ( e aoa r o s me tinSi c&D nm c a rme t r ie i f hn) K yLb rt y fnt o I r na o c ne y a i Mes e nf c Un rt o ia u t e u No h v sy C

2D 1年 1 1 2月 繁1 2期

电 子 测 试

EL ECT RON I C T ES T

De . c2o1 1 No.2 1

基于F G P A与NAND闪 的固态存储 系统设 计 存

郭鹏翔 ,祖静 ,尤文斌

( 中北大学仪器科学与动态测试教 育部重点实验室

太原

005 ) 301

AD变换器采用 AN OG D V C S生产的 l AL E I E 2位并

行输 出 A 79 . D 42 它是 A 公司推出的 1 位高速 、 D 2 低功耗 、

逐次逼近式 AD转换器 。它可在 27~5 5 的电压下工 . . 2v

பைடு நூலகம்

录器 (S ,sl a cre 。S R使 用半导体 器件 作 S R odst r o r S i te e d ) 为存储 介质 ,具 有无机 械部件 、抗振动 、温度适 应范 围 宽等优 点 , 逐渐成为动态存储测试中数据记录的主流方案。

基于FPGA的闪存XX29F系列读写装置的设计

A bstract:In view 0±the current state that series of the XX29F memories are widely used in airborne electronic equipm ent circuit board,in order to meet the need for this series of memories read/write operation,a device based on FPGA is designed to read and write the series of a1l kinds of XX29F memories.Based on the interpre—

tation of device’S function and project design in a systematic way,the hardware circuit designs of various func—

tion modules are provided and the software codes of corresponding modules based on Verilog language are COB — piled.Finally,RS232 is used to control the reading and writing of the device data and comm unicate with PC software.The experimental results show that the device’S reading and writing operation is simple,performance is stable and reliable.It can be applied to repair and test of all kinds of airborne PCB that uses XX29F series m emory· K ey w ords:Am29F400B;FPGA;m em ory operation;serial com munication;airborne PCB repair

基于FPGA的SPIFLASH数据存储系统设计

第24卷 第6期2017年6月仪器仪表用户INSTRUMENTATIONEIC Vol.242017 No.6基于FPGA的SPI FLASH数据存储系统设计李嘉琛,杨 光(长春理工大学 电子信息工程学院,长春 130022)摘 要:SPI串行Flash作为一种新兴的高性能非易失存储器,广泛用于嵌入式数据存储设备中。

针对SPI Flash芯片的操作命令和时序比较复杂,通过对SPI总线协议的深入研究,提出采用现场可编程门阵列(FPGA)作为主控制器,SPI Flash芯片为从设备,设计一个高速数据存储系统。

采用Verilog语言在Xilinx ISE14.7环境下进行硬件描述,加入在线调试软件ChipScope进行逻辑、时序辑分析。

实验结果表明系统能够快速实现用户应用程序和大容量数据的存储和读取,且系统具有耗能低、移植性高、实用性强等优点。

关键词:FPGA;SPI;Flash中图分类号:TP332.1 文献标志码: ADesign of SPI FLASH Data Storage System Based on FPGALi Jiachen ,Yang Guang(School of Electronics and Information Engineering,Changchun University of Science and Technology,Changchun,130022,China)Abstract: As a new kind of high performance nonvolatile memory, SPI serial Flash is widely used in embedded data storage de-vices. Operation command and timing for the SPI Flash chip is more complex, through in-depth study of SPI bus protocol, using field programmable gate array (FPGA) as the main controller, SPI Flash chip from the equipment, design a data storage ing Verilog language in Xilinx ISE14.7 environment for hardware description,Join online debugging software ChipScope for logic and timing analysis. The experimental results show that the system can quickly realize the user application and large capacity data storage and reading, and the system has the advantages of low energy consumption, high portability, strong practicability and so on.Key words:fpga;spi;flashDOI:10.3969/j.issn.1671-1041.2017.06.005文章编号:1671-1041(2017)06-0016-04收稿日期:2017-04-12作者简介: 李嘉琛(1991-),男,河南安阳市人,硕士研究生,主要从事FPGA/CPLD的研究应用。

基于FPGA的外部存储器设计

基于FPGA的外部存储器设计FPGA是一种可编程逻辑设备,可以被重新编程用于实现不同的功能。

在计算机系统中,外部存储器是一种用于保存数据的设备,例如硬盘、固态硬盘(SSD)和闪存。

在本文中,我们将探讨如何设计基于FPGA的外部存储器。

外部存储器在计算机系统中起着至关重要的作用,它可以保存大量的数据,并且在计算机断电后,数据仍然可以保持完整。

外部存储器的性能和容量对计算机系统的整体性能具有重要影响。

在大数据应用和高性能计算中,对外部存储器的需求越来越高。

在设计基于FPGA的外部存储器时,我们需要考虑以下几个方面:1.存储介质选择:选择适合的存储介质对于设计外部存储器非常重要。

常见的存储介质包括硬盘、固态硬盘(SSD)和闪存。

每种存储介质都具有不同的性能和容量特性,我们需要根据具体的应用场景进行选择。

2.存储器控制器设计:存储器控制器是FPGA与外部存储器之间的接口。

它负责实现数据的读写操作,以及处理错误检测和纠正功能。

存储器控制器还需要支持各种不同的存储介质和接口标准。

3.存储器接口设计:存储器接口是FPGA与外部存储器之间的物理连接。

常见的存储器接口包括SATA、PCIe和USB。

我们需要根据具体的应用场景选择适合的存储器接口,并确保接口带宽满足数据传输的需求。

4.数据传输优化:在设计外部存储器时,我们需要考虑如何优化数据传输的性能。

这可以通过使用数据缓存、并行数据传输和数据压缩等技术来实现。

优化数据传输可以提高存储器的访问速度和效率。

5.容量扩展性:外部存储器的容量通常是根据应用需求选择的。

在设计存储器时,我们需要考虑到容量的扩展性,以便将来能够方便地增加存储容量。

6.可靠性和可用性:对于外部存储器来说,可靠性和可用性是非常重要的。

我们需要设计一种容错机制,以确保即使在存储设备出现故障的情况下,数据仍然可以安全地存储和恢复。

7.能耗和成本:在设计外部存储器时,我们需要考虑到能耗和成本的限制。

通过采用低功耗设计和选择适当的存储介质,我们可以有效地减少能耗和成本。

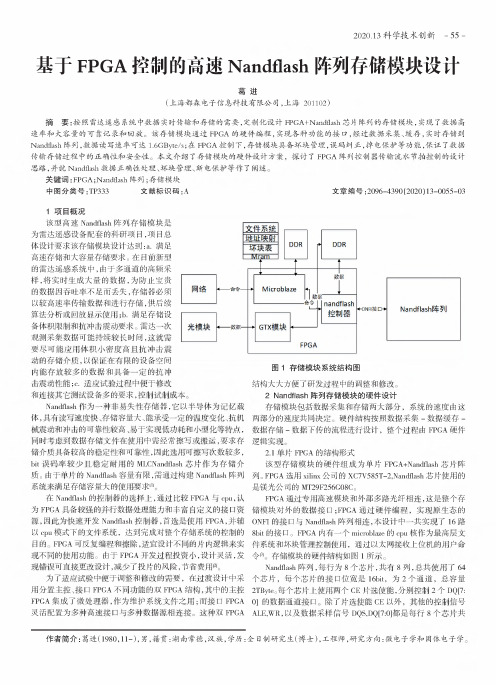

基于FPGA控制的NAND Flash存储设计

该存储 电路 主要完成对数据 的实时存储及操

作, 电源模块对其他模块供 电, 使其 进入正常工作

状态 ; 高速数据接收发送模块实现数据的高速 长距

离传输 , 其 一般采 用 L V D S , H o t l i n k芯片实 现此功 能; F P G A作为整个存储 电路的控制核心 , 接收上级

以扩展 到所有类似 F l a s h存储 系统 中, 对其他 的电路具 有一定 的借鉴意义。 关键词 F la s h F P G A 三线控制 无效块地址列表

中图法分类号

T P 3 3 3 ;

文献标志码

A

现代信息存 储技术 中对存储器 的容量和速度 及存储可靠性提出越来越高 的要求 , 而传统的存储 器件如 D R A M, S R A M, E P R O M, E E P R O M 等 由于 容 量小 、 速度低等缺点无法满足高速大容量存储 的技 术要求 , F l a s h因其具有体积小 、 成本低 、 功耗小 、 寿 命长 、 存储密度 高等特点 , 逐 渐成为高速 大容量存 储系统设计 的主流方案 。F l a s h存储是一种非易

图2 F P G A控 制模 块 设 计 框 图

表 1 状态线组合指令定义

制模块 , 另一个功能是将接收或发送 的数据进行 串

图 1 系 统 硬 件 结 构 框 图

易实现大容 量存储 , 而且其读写 和擦除速度很 快 , 其缺点是逻辑控制 比较复杂, 需要 相应 的逻辑控制

器件如单片机 , C P L D , F P G A等对 其进行逻辑控 制 , 其中 F P G A由于时钟频率高、 内部延时小 、 全部控制 逻辑 由硬件完成 、 速度快 、 效率高 以及丰富 的逻

基于FPGA的存储解决方案

基于FPGA的存储解决方案——片内存储器片内存储器是基于FPGA的嵌入系统可使用的最简单的存储器。

由于存储是在FPGA内部完成,电路板上无需外部连线。

可以简单地选择SOPC builder中System Contents-> On-Chip Memory选项,来完成设计中的片内存储器。

也可以根据需求定义片内存储器的大小、带宽、种类、及特殊的片内存储器性质,如DDR等。

优点片内存储器在基于FPGA的嵌入系统可使用的存储器中是具有最高吞吐量和最低反应延时的。

它的反应延时通常仅为一个时钟周期。

通过存储处理管道化,可以使吞吐量达到每个时钟周期进行一次处理。

有些片内存储器被设计成可以在DDR模式下进行存取,其中读和写是分别进行操作的。

DDR模式能够有效地实现双倍存储带宽,允许存储器在一个通道进行写入,同时在另一个通道进行读取。

片内存储器的另一个好处是,由于它是在FPGA上直接实现的,它无需在板上或电路中进行写入。

使用片内存储器可以节省开发时间和成本。

一些片内存储器可以在FPGA配置时自动初始化。

这种存储器可以被用来保持小数据量的启动代码或重启动所需的LUT数据。

缺点尽管速度很快,片内存储器在一定程度上会受到其容量的限制。

FPGA可用的片内存储器的数量由使用的特定FPGA器件决定,容量范围从最小的Cyclone II device中15KB到最大的Stratix III device中近2MB。

因为多数片内存储器都是易失性的,它在断电后丢失数据。

然而,某些片内存储器可以在FPGA配置时自动初始化,相当于提供了一种非易失性的功能。

最佳应用场合以下是片内存储器适宜的一些应用。

缓存由于其具有低反应延时,片内存储器在微处理器中作为缓存表现良好。

Nios II处理器使用片内存储器作为引导和数据缓存。

片内存储器有限的容量作为缓存通常不是一个问题,因为缓存本身都相对很小。

点到点的缓存能够在低反应时间下进行存取也使得片内存储器适用于做器件间的缓存,即点到点的缓存,它是指处于正常的寻址空间,但与微处理器有专用接口的存储器。

基于FPGA的闪存阵列高速数据存储

制 数 辑 通 器 l

l l I I

避 :

J

』

# F L A S  ̄ J

F L A S

…

H 』 F : L A S H : d F L A S H [

图 1 原理 Biblioteka 图 系统 的成本 ,而且能够提高 系统的性能 ,保证可靠性。

2 存 储 系统

2 0 1 4 年1 0

为 判 断 状 态 :若 此 时 写逻 辑 内 部 存 储 块 计 数器 达 到 要 求 的 块 数 , 此 次 写 操 作 结 束 :若 存 储 块 计 数 器 未 到 达 指 定 值 , 并 且 页计 数 器 值 等 :  ̄ : 6 4 ( K 9 F 8 G0 8 UO A- - 个 块 包含 6 4 页) ,则

2 0 1 4 年1 O

基于F P GA的 闪存 阵列 高速数据存储

太原铁路局党校 孙楠楠 刘望

摘 要 :本文介绍一种 以F P GA为控制器 ,F L AS H作为主存储器的大容量高速阵

列 存 储 系 统 。针 对 单 片 闪速 存储 器 N AN D F L ASH容 量 相 对 较 小 、存 储 速 度 相 对

较低且存在随机无效块 等问题 ,提出一种 由单片NAND F L ASH构建大容量高速

存 储 阵 列 ,并 根 据 阵列 的结 构特 点 管 理 无 效 块 的 方 法 。实 验 结 果 证 明 ,该 系 统 稳 定 可 靠 且 达 到 预 期 的存 储 容 量 和 存 储 速 度 。 关键词 :F PGA 高 速 存 储 F L ASH存 储 无 效块 管理

“ 0 ” 的位 所 对 应 的 块 地 址 就 是 无效 块 ,其 余 为 有 效块 图 3 为 无 效块 的标 识 。

基于FPGA的Nandflash存储模块设计

2021.13科学技术创新表4优化前后性能值比较通常在实际项目中,开发者无法针对特定的模型制定合理的切片方式,因此会出现大型3D 场景无法加载的问题。

通过模型切片数据加载及贴图切片数据渲染的优化,使得效率有一定程度的提升,特别对于大型的切片方式及小型的切片方式。

算法提高了各种不同大小切片方式下的效率值,并使得在加载大型的切片和小型的切片时,终端运行正常,不会出现卡死等情况,运行得到保障。

3结论目前类似于智慧社区的大规模型3D 场景基本都是基于客户端程序,大多使用U3D 工具开发,开发周期长,且移植性和扩展性不是很好。

本课题通过算法研究,使大型3D 场景能以网页的形式展示,通过加载渲染优化算法,方便了产品的部署和维护,并能和其他网页直接交互,有更强的适应性和交互性。

通过研究,使得大型3D 实景能通过WebGL 框架展现在任意载体上,达到自适应效果。

同时使得实景加载渲染效率有大幅度的提升,从而能更好地与其他页面完美交互,节省了大量的接口开发成本,从而获得一定的经济价值。

目前的初步研究成果虽然能应用于大多数的3D 场景,但还不是非常完美,在今后有进一步的提升空间,主要包含如下方面:目前的研究主要在保持加载渲染时间稳定的基础上,避免了终端资源的利用超负荷,今后可以进一步通过算法节省加载和渲染时间;在研究过程使用的社区案例具有一定的规模,在加载和渲染过程需要等待,今后可考虑设计预加载的技术来提高用户体验;目前的模型和贴图切割方法可以进一步优化,在保证质量的情况下进行压缩,控制模型切片数据加载及贴图切片数据大小。

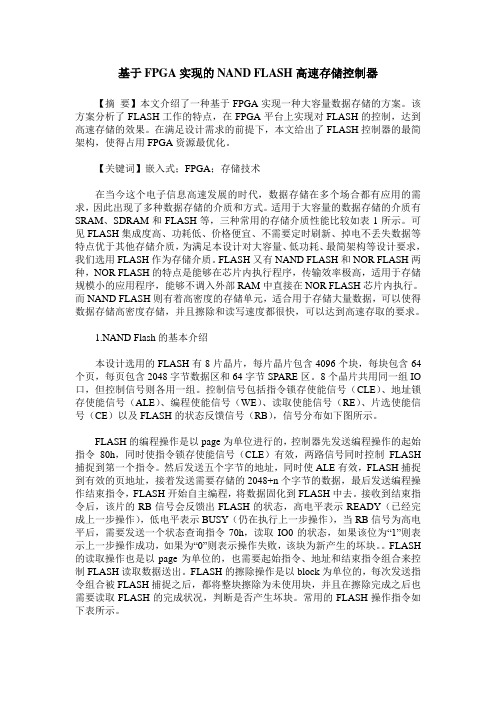

参考文献[1]叶梦轩.基于HTML5和WebGL 的三维点云可视化方法[J].工程勘察,2017(01):40-44+63.[2]郑华.基于WebGL 的三维模型及其信息化技术研究[J].石家庄铁路职业技术学院学报,2017(01):64-70.[3]周昌权.基于HTML5WebGL 技术的校园全景漫游系统研究[J].电脑知识与技术,2016(35):86-88.组号M1M2M3M4M5M6M7M8原始效率值 22.2 24.1 37.5 36.7 23.6 13 9.7 3.2优化后效率值 29.7 31.5 37.6 38 36 35.5 27.8 21.1效率值增量7.5 7.4 0.1 1.3 12.4 22.5 18.1 17.9基于FPGA 的Nandflash 存储模块设计唐超(深圳市汇顶科技股份有限公司,四川成都610041)1概述该基于FPGA 的Nandflash 存储模块的设计是隶属于随钻测井系统的科研子项目,总体上要求该模块达到以下指标:a.数据出错概率不大于0.1%。

基于fpga控制的高速nandflash阵列存储模块设计

储模块对外的数据 FPGA通过硬编:实原生态的

J!FK 的

!a#$%lash 阵列相 , 设计中 共实 了 L6 路

以+89模式下的 系统,达到完成对整个存储系统的 的 9的 FPGA 可*+, 和 -, .设=不 的 /0 实

不的

能。由于FPGA 发 投 ,设计灵活,发

5 可6 7 设=,8 91 的:;,<=> 1:3

数据存储-数据下传的流程进行设计,整个 /0实

由FPGA硬件

2.1

FPGA的结形式

该型存储模块的硬组成为单片FPGA+Nan$&ash

阵

列。FPGA选用xilinx公司的XC7@585T-2,Nan$&ash芯片使用的

是镁光公司的MT29F256G08C。

FPGA通专高速模块和外部多路光纤相,这是整个存

X =? X !"#$%& !"!"#$%

CE7-1.CE7-2

CE1-1.CE1-2

CEO-l.CEO-2 ---------------- ]

Nandflash

Nandflash

IIII

chip 0

chip 1

DQ.0[7:0LDQS0,DQl[7:0], DQSXALE0.ALE1

------------- ;

Nandf&ash阵列,每行为8个 ,共 8列,总共 了 6S

个芯片:每个 的 位宽是16bit,为2个通道,总容量

2TByte。每个

两个CV

能,分别 2个DQ[7:

03的数据通道

除了

能cv以外, 他的 信号

ALE,WR,以及数据采样信号DQS,DQ[7:0]都是每行8个 共

基于FPGA和FLASH的多路数据存储技术

基于FPGA和FLASH的多路数据存储技术作者:吴嘉伟魏志强张会新来源:《现代电子技术》2020年第04期摘; 要:针对多路数据存储中所采集数据传输与存储速率不匹配的问题,提出一种基于FPGA和FLASH的多路数据存储技术。

FPGA芯片可以通过RS 422串并转换模块将输入的串行数据转换为并行数据存入第一级数据缓存,主控模块对其重新编帧后存入第二级数据缓存中,最后在FLASH控制模块作用下把数据存入FLASH存储器中。

经测试,从FLASH存储器中读取的数据正确,该系统工作可靠。

关键词:多路数据存储; FPGA; FLASH; 串并转换; 数据缓存; 数据重新编帧中图分类号: TN919⁃34; ; ; ; ; ; ; ; ; ; ; ; ; ; ;文献标识码: A; ; ; ; ; ; ; ; ; ; ; 文章编号:1004⁃373X(2020)04⁃0034⁃04Multi⁃channel data storage technology based on FPGA and FlashWU Jiawei1,2, WEI Zhiqiang3, ZHANG Huixin1,2(1. Key Laboratory of Electronic Measurement Technology, North University of China,Taiyuan 030051, China;2. MOE Key Laboratory of Instrumentation Science & Dynamic Measurement, North University of China, Taiyuan 030051, China;3. Beijing Institute of Aerospace Metrology and Testing Technology, Beijing 100076,China)Abstract: A multi⁃channel data storage technology based on FPGA and Flash is proposed to improve the mismatch between the collected data transmission rate and its storage rate inmulti⁃channel data storage. The FPGA chip is adopted to convert the inputted serial data into the parallel data by means of the RS⁃422 serial⁃to⁃parallel conversion module and store them into the first⁃level data caching, refresh their frame and store them in the second⁃level data caching by means of the master control module, and store the data in Flash memory by means of the Flash control module. The testing results show that the data read from the flash memory is correct and the system is provided with reliable run.Keywords: multi?channel data storage; FPGA; FLASH, serial⁃to⁃parallel conversion; data⁃caching; data frame refreshing随着我国工业、农业、军事、航天等事业的不断发展,各种电子系统、自动化装置以及传感器等也在不断对其功能和结构进行改进,需要记录和存储的数据也越来越多,常常需要同时采集和存储多个通道的数据。

fpga中flash存储数据和程序的方法

fpga中flash存储数据和程序的方法

在FPGA中,通常使用flash存储器来存储数据和程序。

FPGA开发板上一

般都有一个或多个flash存储器芯片,如NOR flash或NAND flash。

以下是fpga中flash存储数据和程序的方法:

1. 编程flash存储器:使用FPGA开发工具(如Xilinx Vivado、Altera Quartus等)将数据和程序编译成二进制文件,然后将这些文件下载到FPGA的flash存储器中。

在FPGA上电后,这些数据和程序会自动从flash 存储器中加载到FPGA的内部RAM中,供FPGA使用。

2. 擦除和重新编程:如果需要更新FPGA中的数据或程序,可以使用FPGA 开发工具重新编译和下载新的二进制文件到flash存储器中。

在更新之前,

需要先擦除旧的二进制文件。

可以使用FPGA开发工具提供的擦除功能来擦除整个flash存储器,或者只擦除特定的区域。

3. 保护和加密:为了保护flash存储器中的数据和程序不被非法访问或修改,可以使用FPGA开发工具提供的保护和加密功能。

这些功能可以限制对flash存储器的访问权限,或者对flash存储器中的数据进行加密和解密。

4. 硬件锁:一些FPGA开发板还提供了硬件锁功能,用于锁定整个flash存储器或其中的特定区域。

通过使用硬件锁,可以防止未经授权的访问和修改flash存储器中的数据和程序。

需要注意的是,不同的FPGA开发工具和flash存储器芯片可能有不同的操作方法和特性。

因此,在使用之前,建议先仔细阅读相关的技术文档和用户手册。

基于FPGA实现的NAND FLASH高速存储控制器

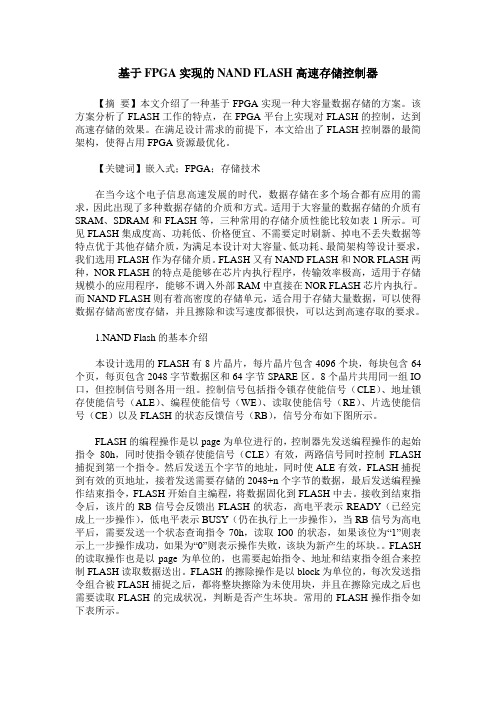

基于FPGA实现的NAND FLASH高速存储控制器【摘要】本文介绍了一种基于FPGA实现一种大容量数据存储的方案。

该方案分析了FLASH工作的特点,在FPGA平台上实现对FLASH的控制,达到高速存储的效果。

在满足设计需求的前提下,本文给出了FLASH控制器的最简架构,使得占用FPGA资源最优化。

【关键词】嵌入式;FPGA;存储技术在当今这个电子信息高速发展的时代,数据存储在多个场合都有应用的需求,因此出现了多种数据存储的介质和方式。

适用于大容量的数据存储的介质有SRAM、SDRAM和FLASH等,三种常用的存储介质性能比较如表1所示。

可见FLASH集成度高、功耗低、价格便宜、不需要定时刷新、掉电不丢失数据等特点优于其他存储介质,为满足本设计对大容量、低功耗、最简架构等设计要求,我们选用FLASH作为存储介质。

FLASH又有NAND FLASH和NOR FLASH两种,NOR FLASH的特点是能够在芯片内执行程序,传输效率极高,适用于存储规模小的应用程序,能够不调入外部RAM中直接在NOR FLASH芯片内执行。

而NAND FLASH则有着高密度的存储单元,适合用于存储大量数据,可以使得数据存储高密度存储,并且擦除和读写速度都很快,可以达到高速存取的要求。

1.NAND Flash的基本介绍本设计选用的FLASH有8片晶片,每片晶片包含4096个块,每块包含64个页,每页包含2048字节数据区和64字节SPARE区。

8个晶片共用同一组IO 口,但控制信号则各用一组。

控制信号包括指令锁存使能信号(CLE)、地址锁存使能信号(ALE)、编程使能信号(WE)、读取使能信号(RE)、片选使能信号(CE)以及FLASH的状态反馈信号(RB),信号分布如下图所示。

FLASH的编程操作是以page为单位进行的,控制器先发送编程操作的起始指令80h,同时使指令锁存使能信号(CLE)有效,两路信号同时控制FLASH 捕捉到第一个指令。

基于FPGA实现的NAND FLASH高速存储控制器

基于FPGA实现的NAND FLASH高速存储控制器【摘要】本文介绍了一种基于FPGA实现一种大容量数据存储的方案。

该方案分析了FLASH工作的特点,在FPGA平台上实现对FLASH的控制,达到高速存储的效果。

在满足设计需求的前提下,本文给出了FLASH控制器的最简架构,使得占用FPGA资源最优化。

【关键词】嵌入式;FPGA;存储技术在当今这个电子信息高速发展的时代,数据存储在多个场合都有应用的需求,因此出现了多种数据存储的介质和方式。

适用于大容量的数据存储的介质有SRAM、SDRAM和FLASH等,三种常用的存储介质性能比较如表1所示。

可见FLASH集成度高、功耗低、价格便宜、不需要定时刷新、掉电不丢失数据等特点优于其他存储介质,为满足本设计对大容量、低功耗、最简架构等设计要求,我们选用FLASH作为存储介质。

FLASH又有NAND FLASH和NOR FLASH两种,NOR FLASH的特点是能够在芯片内执行程序,传输效率极高,适用于存储规模小的应用程序,能够不调入外部RAM中直接在NOR FLASH芯片内执行。

而NAND FLASH则有着高密度的存储单元,适合用于存储大量数据,可以使得数据存储高密度存储,并且擦除和读写速度都很快,可以达到高速存取的要求。

1.NAND Flash的基本介绍本设计选用的FLASH有8片晶片,每片晶片包含4096个块,每块包含64个页,每页包含2048字节数据区和64字节SPARE区。

8个晶片共用同一组IO 口,但控制信号则各用一组。

控制信号包括指令锁存使能信号(CLE)、地址锁存使能信号(ALE)、编程使能信号(WE)、读取使能信号(RE)、片选使能信号(CE)以及FLASH的状态反馈信号(RB),信号分布如下图所示。

FLASH的编程操作是以page为单位进行的,控制器先发送编程操作的起始指令80h,同时使指令锁存使能信号(CLE)有效,两路信号同时控制FLASH 捕捉到第一个指令。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

闪存存储器是嵌入系统中经常使用的非易失性存储器。在基于FPGA的嵌入系统中,由于FPGA没有包括闪存,所以闪存始终是外置设备。由于闪存存储器能够在断电后保持数据内容,它经常用于存储微处理器启动代码及其它需要在无电情况下继续保持的数据。闪存存储器既适用于并行接口又适用于串行接口。并行闪存设备与串行闪存设备的基本存储技术是相同的。不像SRAM,闪存不能通过简单的写入操作进行更新。对闪存设备的每一次写入操作都需要一个写指令,包含一组固定的读写操作序列。闪存在写入前需要先进行擦除。所有的闪存设备都被划分为一定数量的可擦模块,或扇区,二者的差异是可擦区域的大小,依据闪存厂商和设备大小而定。优点闪存存储器的主要的优点是非易失性。现代嵌入系统广泛使用闪存来存储启动代码和设置值,以及较大的数据模块如音频或视频流等。很多嵌入系统使用闪存作为硬盘驱动的低能耗、高稳定性的替代品。相对与其它非易失性存储器,闪存由于下面四种原因更加常用:健壮性可擦性可重复擦写成本低闪存存储器可以与共享其它闪存设备共享总线,甚至与其它种类的外部存储器,如外部SRAM或SDRAM。缺点闪存的主要缺点是它的写入速度。由于你只能通过专用的命令写入闪存设备,每次闪存写入都需要多个总线转换操作。更进一步说,一旦送出写入命令,实际的写入时间可能达到几微秒。依据时钟速度,实际写入时间可达几百个时钟周期。由于扇区擦除受到约束,如果你需要改变闪存中的一个字数据,你必须完成下面步骤:1. 复制整个扇区的内容到暂时的缓冲区2. 擦除整个扇区3. 改变在缓冲区中的单个字数据4. 缓冲区内容写回到闪存这个流程导致闪存存储器设备的写入速度较慢。由于其糟糕的写入速度,闪存通常只用于存储必须断电后保持的数据。最佳应用场合闪存存储器适用于储存任何你希望在断电后保持的数据。常见的闪存应用与存储下面项目:微处理器的启动代码微处理器在系统开始时复制到RAM中的应用程序代码恒定的系统设置,例如:网卡MAC地址、校准数据、用户信息FPGA参数图像多媒体(音频、视频)不适于应用场合由于闪存存储器是写入速度较慢,不应使用闪存存储不需要断电后保持的数据。如果可以使用易失性存储器时可以选用SRAM。使用闪存存储器的系统通常也会同时使用SRAM。一个很不适于闪存的应用场合是在微处理器的应用程序代码的直接执行。如果这些代码的可写部分被部署在闪存中,这些软件根本不会工作,因为闪存不使用专用的写入命令便不能够写入。将应用程序代码储存在闪存中的系统通常会在执行之前先将这些应用程序复制到SRAM中。闪存的种类闪存设备有多种,最常用的种类如下:CFI闪存 – 这是最常用的闪存存储器种类。它使用并行接口。CFI代表常见闪存接口,这er和Nios II processor都有对CFI闪存的内置支持。串行闪存 – 这种闪存使用串行接口以节省Pin脚和板上空间。由于很多串行闪存设备都有自己专用的接口协议,最好是先通读串行闪存设备的数据表然后进行选择。Altera ECOS配置设备便是一种串行闪存。NAND闪存 – NAND闪存是最近才兴起的一种新型的闪存存储器。NAND闪存可以达到很高的数据容量,单个设备可高达数GB。相对于CFI闪存,NAND闪存的接口稍有变复杂。它需要一个专用的控制器或是智能的低级驱动软件。你可以在Altera FPGA中使用NAND闪存,但是Altera不会提供任何内置的支持。