MT-027_ADC架构VIII:积分ADC_cn

实验8 adc采样和信号滤波实验

实验8 adc采样和信号滤波实验1.实验目的熟悉adc模块的各个寄存器,学会如何通过程序语言配置adc的各种属性并采集模拟信号,并使用过采样和数字滤波算法减小噪声。

2.实验主要内容(1)在CCS软件中,用C语言编写程序配置adc的各种属性并采集到模拟信号。

(2)编写程序配置epwm的各种属性,使其以100kHZ的频率触发adc进行采样。

(3)编写程序进行过采样,以及数字滤波。

3.实验基本原理(1)adc模块模数转换模块ADC有16个通道,可配置为2个独立的8通道模块,服务于ePWM模块。

两个独立的8通道模块也可以级联构成一个16通道模块。

尽管在模数转换模块中有多个输入通道和两个排序器,但仅有一个转换器。

ADC模块的功能框图如图所示。

(2)数字滤波器原理一阶低通滤波器的公式为:()c 11y G s s x ω==+将其离散化后,可得到:()()()s c s c s c1111T y k y k x k T T ωωω=-+++可通过程序的编写来实现此低通滤波器。

4. 实验过程和关键程序解读(1) 打开AD 实验的工程(2) 阅读adc 配置的代码,本工程内对adc 配置的主要代码如下:配置的主要属性有,adc采样时间窗ACQ_PS、内核时钟分频ADCCLKPS,级联操作选择SEQ_CASC,SEQ中断使能,SOCA触发允许等。

(3)修改主程序,使得能够完成实验要求i.首先,配置epwm,使其产生出发adc的SOC信号,SOCASEL设定为4,代表达到CMPA触发。

ii.修改EPWM时钟频率,EPWM时钟频率= SYSCLK / (HSPCLKDIV * CLKDIV ),及150M/2 = 75MHZ。

iii.设定技术周期和比较周期:计数周期设为749,则触发adc的周期为75M/(749+1) = 100KHZA通道比较值的设定即可比较随意,每周期只会达到一次。

iv.编写过采样的代码简单来说就是同时采集多次取平均。

ADC芯片介绍

ADC芯片介绍ADC,即模数转换器(Analog-to-Digital Converter),是一种将模拟信号转换成数字信号的电子设备。

它是数字系统中的重要组成部分,广泛应用于通信系统、仪器仪表、工业自动化、医疗设备等领域。

本文将介绍ADC芯片的基本原理、分类、特点以及应用领域等相关内容。

一、ADC芯片的基本原理1.采样:采样是指将模拟信号在一定时间间隔内取样,即在一段时间内获取一系列的模拟信号值。

采样过程中需要考虑采样频率和抗混叠滤波等问题。

2.量化:量化是指将采样到的模拟信号值转换为具有离散数值的数字信号。

量化过程中需要确定量化位数和量化级数等参数,并利用ADC芯片内部的比较器和计数器等电路实现。

通过采样和量化两个过程,ADC芯片可以将模拟信号转换为数字信号,进而被数字系统所处理。

二、ADC芯片的分类根据其工作原理和结构,ADC芯片可以分为几种不同的类型。

1.逐次逼近型ADC:逐次逼近型ADC芯片是一种常见的ADC芯片类型,它通过逐次逼近的方式进行模拟信号到数字信号的转换。

逐次逼近型ADC芯片具有较高的分辨率和较低的功耗,适用于对精度要求较高的应用领域。

2.并行型ADC:并行型ADC芯片是一种将模拟信号同时转换为多个比特的数字信号的ADC芯片类型。

它具有高速和高精度的特点,但功耗较大。

并行型ADC芯片适用于对采样速度要求较高的应用场景,如通信系统中的信号处理和无线电频谱分析等。

3. Sigma-Delta型ADC:Sigma-Delta型ADC芯片主要应用于对信噪比要求较高的应用场景。

它通过过采样和累积量化的方式实现高精度的模数转换。

Sigma-Delta型ADC芯片适用于音频处理、音频编解码等领域。

三、ADC芯片的特点1.分辨率高:ADC芯片的分辨率是指其能够表示的电压值的最小差值。

分辨率越高,ADC芯片对模拟信号的转换精度越高。

2.采样速度快:ADC芯片的采样速度是指其每秒钟能够进行的采样次数。

adc芯片内部等效电路

adc芯片内部等效电路

ADC芯片内部等效电路:

ADC(模数转换器)芯片是一种电子器件,用于将模拟信号转换为数字信号。

为了实现这一转换功能,ADC芯片内部采用了一系列的等效电路。

以下是ADC芯片内部等效电路的主要组成部分:

1. 输入信号缓冲器:ADC芯片通常具有输入信号缓冲器,它用于对输入信号进行放大和隔离。

输入信号缓冲器能够调整信号的幅值和电平,以适应ADC芯片的工作范围。

2. 采样保持电路:为了将连续的模拟信号转换为离散的数字信号,ADC芯片需要在信号采样期间保持输入信号的稳定。

采样保持电路能够在采样期间存储输入信号的电压,并在转换过程中保持稳定。

3. 参考电压源:ADC芯片需要一个参考电压源来确定转换后的数字信号的电平。

参考电压源提供了ADC芯片的基准电压,确保转换结果的可靠性和准确性。

4. 编码器:编码器是ADC芯片的核心部分,它将连续的模拟信号转换为离散的数字代码。

编码器根据输入信号的幅值和精度,根据一定的量化规则,将模拟信号转换为对应的数字代码。

5. 数字信号处理器:ADC芯片通常还包含一些数字信号处理器,用于对转换后的数字信号进行校正、滤波和增强等处理。

这些处理器可以提高转换结果的精度和可靠性。

总而言之,ADC芯片内部等效电路由输入信号缓冲器、采样保持电路、参考电压源、编码器和数字信号处理器等组成。

这些等效电路协同工作,将模拟信号转换为数字信号,并对转换结果进行处理,以满足各种应用领域对信号转换的需求。

ADC芯片在通信、仪器仪表、嵌入式系统等领域起着重要的作用。

MT-024:Pipelined Decimation ADCs说明书

MT-024指南ADC架构V:流水线式分级ADC作者:Walt Kester简介目前对于需要5 MSPS至10 MSPS以上采样速率的应用,流水线式分级ADC架构占优势。

尽管flash(全并行)架构(参见指南MT-020)在上世纪80年代和90年代早期主导8位视频IC ADC市场,但现代应用中流水线式架构已大面积取代Flash ADC。

也有少量采样速率高于1 GHz的高功率砷化镓(GaAs)工艺Flash转换器,但分辨率仅限于6或8位。

不过,Flash转换器仍然是较高分辨率流水线式ADC的常用构建模块。

流水线式ADC的应用包括视频、图像处理、通信和各种其他应用。

该架构有助于较低成本的IC工艺,最常见的有CMOS和BiCMOS。

目前的技术在高于100 MSPS的采样速率下可产生12至16位分辨率。

基本分级ADC架构流水线式ADC源于上世纪50年代首次使用的分级架构,该架构用于减少隧道二极管和真空管Flash ADC 中的元件数和功率(参见参考文献1、2)。

分级架构的框图如图1所示,其中显示了一个6位、二级ADC。

Array图1:6位、二级分级ADC通过第一级3位子ADC(SADC)——Flash转换器,将输入采样保持电路(SHA)的输出数字化。

接着使用3位子DAC (SDAC)将粗略3位MSB转换结果转换回至模拟信号。

SDAC输出则从SHA输出减除,经放大后施加于第二级3位SADC。

接着通过3位第二级SADC数字化“残余信号”,从而产生总共6位输出字的三个LSB。

此类型的ADC通常称为“分级”ADC,因为输入范围细分为若干个较小范围(子范围),这些较小范围又可进一步细分。

通过考察第二级ADC输入端的残余波形,可对此分级ADC执行最佳分析,如图2所示。

该波形假定整体ADC接收的是低频斜坡输入信号。

为了确保无失码,残余波形必须恰好填满第二级ADC的输入范围,如图2A的理想情况所示。

这意味着N1 SADC和N1 SDAC的精度必须均优于N1 + N2位,所示例子中,N1 = 3,N2 = 3,N1 + N2 = 6。

0华为ADC培训胶片

S

目录 SLA 管理 服务

身份 管理

业务 管理

集流管成程理总线计费

OAM

Service Service Service

ADC

B

O

EEnnaabblelerr

S

ADC 内部实现与BOSSLSA,管理目服业集录务成务身管业份理务部E总业管n线务理件a(b流管之I程理lSeB)计r间费的OAM接口,实S 现统一的

功能

•

• •

• • • • •

ADC门户建设(客 户经理管理、SI管 理、企业管理) Si管理系统与ADC 的融合 与BOSS建立数据 同步接口(开销户、 业务定购、产品和 客户信息同步) 实现ADC平台与SI 业务应用系统接口 单点登录 权限管理 日志管理 统计报表

基础建设阶段

• 完善客服保障系统 (BOSS/CSS)

• 支撑灵活计费(包 括IT业务计费:一 次性设备和服务费 用话单生成、上传)

• 完善SI管理系统功 能

• 优化与周边系统的 接口(网关、BOSS、 网维、业务系统、 CSS)

平台扩展完善阶段

•根据企业行业业务应 用的拓展需求加强统 一门户、统一数据、 统一接入、统一业务

管理、内容管理功能

业务/行业拓展阶段

加强对业务价值链的控制,体现中国移动的核心地位

Business

承

载

网

Family

络

ADC:应用数据中心

用户管理 业务管理 SI管理 认证授权 融合计费 统一配置 内容管理 终端管理 统计分析 通知中心 门户

用户接入

IP网络 业务引擎

Core Network

中国移动

Customer

用户

Information Flow

MTK平台ADC学习笔记

作者: Darren完成日期: 2010-06-28 Page 1 of 14 e-mail:*******************目录1.基本概念 (2)2.MT6225 ADC简介 (3)3.MT6253 ADC简介 (3)4.两种操作模式 (3)5.用于电池电量显示的ADC检测 (4)5.1.主要流程图 (4)5.2.流程说明 (6)5.3.创建步聚 (6)6.充电时ADC的检测 (7)6.1充电时ADC的调度流程 (7)7.工程模式查看电池电压ADC (8)8.MT6225平台区分USB和CHARGER的ADC通道 (8)9.ADC校准 (10)10.ADC检测的主要API (11)11.ADC调度器的成员变量 (13)作者: Darren完成日期: 2010-06-28 Page 2 of 14 e-mail:*******************1.基本概念ADC ,即analog to digital converter,模拟信号至数字信号的转换器。

主要的ADC转换算法有逐次逼近法,双积分法。

它们一般由芯片内部的硬件电路实现,但外部的电路接法会有所不同。

MTK平台ADC采样的可使用外部电路:y=((a*x+b)/100)*factor(如adc_adc2vol()中的算式)x为ADC采样值,y为测量点的实际电压如图2所示,(a*x+b)为A点的电压值,((a*x+b)/100)*factor才是我们要测量的Ui的电压值。

由于ADC的量程有限,故需要进行分压才能测量比较大的电压,之后再根据分压电阻的比值转换成要测量点的电压。

a为每单位表示的电压。

MTK的ADC量程为2.8V,ADC为10位的,故a=2800000/2^10=2734(uV)。

通常为了扩大测量范围,需要把a扩大约一倍(记为a1),之后再通过factor校正。

比如变成5524,是原来的2.02倍b是偏移量,需要测量确定。

ADC选型经典指南

ADC选型手册一ADC的定义模数转换器即A/D转换器,或简称ADC,(简称a/d转换器或adc,analog to digital converter)通常是指一个将模拟信号转变为数字信号的电子元件。

通常的模数转换器是将一个输入电压信号转换为一个输出的数字信号。

由于数字信号本身不具有实际意义,仅仅表示一个相对大小。

故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。

而输出的数字量则表示输入信号相对于参考信号的大小。

二ADC的基本原理在A/D转换中,因为输入的模拟信号在时间上是连续的,而输出的数字信号是离散量,所以进行转换时只能按一定的时间间隔对输入的模拟信号进行采样,然后再把采样值转换为输出的数字量。

通常A/D转换需要经过采样、保持量化、编码四个步骤。

也可将采样、保持合为一步,量化、编码合为一步,共两大步来完成。

(1)采样和保持:采样,就是对连续变化的模拟信号进行定时测量,抽取其样值。

采样结束后,再将此取样信号保持一段时间,使A/D转换器有充分的时间进行A/D转换。

采样-保持电路就是完成该任务的。

其中,采样脉冲的频率越高,采样越密,采样值就越多,其采样-保持电路的输出信号就越接近于输入信号的波形。

因此,对采样频率就有一定的要求,必须满足采样定理即:fs≥2fImax其中fImax 是输入模拟信号频谱中的最高频率(2)量化和编码:所谓量化,就是把采样电压转换为以某个最小单位电压△的整数倍的过程。

分成的等级称为量化级,A 称为量化单位。

所谓编码, 就是用二进制代码来表示量化后的量化电平。

采样后得到的采样值不可能刚好是某个量化基准值, 总会有一定的误差, 这个误差称为量化误差。

显然, 量化级越细, 量化误差就越小, 但是, 所用的二进制代码的位数就越多, 电路也将越复杂。

量化方法除了上面所述方法外, 还有舍尾取整法, 这里不再赘述。

采样的话时间非常短,起动AD转换后,就把模拟值读进去了。

通信行业名词缩写解释

3G-SGSN 3rd Generation Serving GPRS Support Node第三代服务 GPRS 的节 占八、、ATM Asynchronous Transfer Mode AAL2 ATM Adaptation Layer type 2 AS Access StratumBSSMAP Base Station Subsystem Management Application Part 分SMpSDU Support Mode for predefined SDU size SAP Service Access PointSRNS Serving RNSTrM Transparent ModeTNL Transport NetworkLayer UE UserEquipmentUPUser Plane UTRANUMTS Terrestrial Radio Access Network控制业务接入点 小区广播中心 小区广播业务 公共业务信道 公共业务信道块集 千比特/秒 Layer 1 (physical layer) Layer 2 (data link layer) Layer 3 (network layer) 网络层业务接入点 用户设备CC Connection Confirm CN Core Network CS Circuit Switched PS Packet Switched PVC Permanent Virtual Circuit RLP Radio Link Protocol RNC Radio Network Controller RNL Radio Network Layer RFC RAB sub Flow Combination RFCI RFC IndicatorSVC Switched Virtual Circuit SDU Service Data Unit异步传递模式ATM 适配层类型2 接入层基站子系统管理应用部 连接确认 核心网 电路交换分组交换 永久虚电路 无线链路协议 无线网络控制器 无线网络层 RAB 子流组合 RAB 子流组合指示 交换虚电路 服务数据单元预定义SDU 大小的支持模式 业务接入点服务无线网络子系统 透明模式 传输网络层 用户设备 用户平面UMTS 陆地无线接入网VC Virtual CircuitC-SAP CBC CBSCTCH CTCH-BS kbps L1 L2 L3 NSAPI UE本文档用到下列缩略语ASC 接入业务类别BCCH 广播控制信道C- 控制-CCCH 公共控制信道DCH 专用信道DL 下行链路DSCH 下行链路共享信道DTCH 专用业务信道FAUSCH 快速上行链路信令信道L1 Layer 1 (物理层)L2 Layer 2 (数据链路层)L3 Layer 3 (网络层)PCCH 寻呼控制信道PHY 物理层PhyCH 物理信道RNC 无线网络控制器RNS 无线网络子系统RNTI 无线网络临时识别RRC 无线资源控制SAP 业务接入点SDU 业务数据单元SHCCH 共享信道控制信道SRNC 服务RNCSRNS 服务RNSTFI 传输格式指示U- 用户-UE 用户设备UL 上行链路UMTS 通用移动通信系统USCH 上行链路共享信道UTRA UMTS 陆地无线接入UTRAN UMTS 陆地无线接入网本文档中应用以下缩略语:AS 接入层C-SAP 控制服务接入点IETF Internet 工程任务组L2 层 2 (数据链路层)L3 层 3 (网络层)PID 分组标示RFC 请求注解RRC 无线资源控制RTP 实时协议SDU 服务数据单元TCP 传输控制协议UE 用户设备UMTS 通用移动通信系统UTRA UMTS 陆地无线接入UTRAN UMTS 陆地无线接入网缩略语ARQ 自动重发请求BCCH 广播控制信道C- 控制-CCCH 公共控制信道文档来源为:从网络收集整理.word 版本可编辑.欢迎下载支持CCH CN DC DCH DL DSCH DTCH FCS GC HO ITU kbps L1 L2 L3 MS Nt PCCH PU PHY PhyCH RNTI RRC SAP SDU SHCCH TDD TFI U- UE UL UMTS UTRA UTRAN 控制信道核心网专用控制(SAP)专用信道下行下行共享信道专用业务信道帧校验序列通用控制(SAP)切换国际电信联盟每秒千比特层 1 (物理层)层2 (数据链路层)层 3 (网络层)移动站通知(业务接入点)寻呼控制信道净荷物理层物理信道无线网络临时标识无线资源控制业务接入点业务数据单元共享信道控制信道时分复用传输格式指示用户- 用户设备上行链路全球移动通信系统UMTS 陆地无线接入UMTS 陆地无线接入网GPRS General Packet Radio ServiceAA ATM BG BSSGP CCU CGI DNS GGSN GSN ICMP IETF IPv4 IPv6 L3MM LL-PDU LLC MDFG MNRF MSP MTP2 MTP3 Anonymous Access Asynchronous Transfer Mode Border Gateway Base Station System GPRS Protocol Channel Codec Unit Cell Global Identity Domain Name System Gateway GPRS Support Node GPRS Support Node Internet Control Message Protocol Internet Engineering Task Force Internet Protocol version 4 Internet Protocol version 6 Layer 3 Mobility Management LLC PDULogical Link ControlMobile Detached Flag for GPRS Mobile station Not Reachable Flag Multiple Subscriber Profile Message Transfer Part layer 2 Message Transfer Part layer 3文档来源为:从网络收集整理.word版本可编辑•欢迎下载支持NSAPI Network layer Service Access Point IdentifierNSS Network SubSystemPCU Packet Control UnitPDCH Packet Data CHannelPDN Packet Data NetworkPDP Packet Data Protocol, e.g., IP or X.25PTM Point To MultipointPTP Point To PointPVC Permanent Virtual CircuitRAI Routeing Area IdentityRRM Radio Resource ManagementSGSN Serving GPRS Support NodeSM Short MessageSM-SC Short Message service Service CentreSMS-GMSC Short Message Service Gateway MSCSMS-IWMSC Short Message Service Interworking MSCSN-PDU SNDCP PDUSNDC SubNetwork Dependent ConvergenceSNDCP SubNetwork Dependent Convergence ProtocolTCAP Transaction Capabilities Application PartTCP Transmission Control ProtocolTID Tunnel IdentifierTLLI Temporary Logical Link IdentityTRAU Transcoder and Rate Adaptor Un缩略BCC:BaseStationColourCode.基站色码。

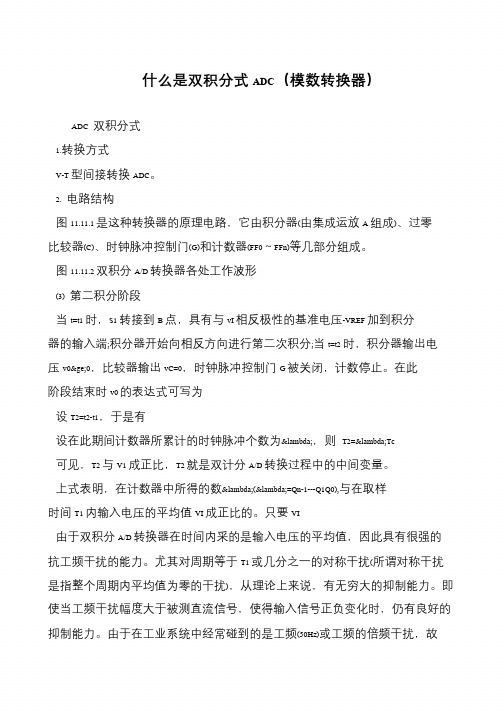

什么是双积分式ADC(模数转换器)

什么是双积分式ADC(模数转换器)

ADC 双积分式

1.转换方式

V-T 型间接转换ADC。

2. 电路结构

图11.11.1 是这种转换器的原理电路,它由积分器(由集成运放A 组成)、过零比较器(C)、时钟脉冲控制门(G)和计数器(FF0~FFn)等几部分组成。

图11.11.2 双积分A/D 转换器各处工作波形

(3) 第二积分阶段

当t=t1 时,S1 转接到B 点,具有与vI 相反极性的基准电压-VREF 加到积分器的输入端;积分器开始向相反方向进行第二次积分;当t=t2 时,积分器输出电压v0≥0,比较器输出vC=0,时钟脉冲控制门G 被关闭,计数停止。

在此阶段结束时v0 的表达式可写为

设T2=t2-t1,于是有

设在此期间计数器所累计的时钟脉冲个数为λ,则T2=λTc 可见,T2 与V1 成正比,T2 就是双计分A/D 转换过程中的中间变量。

上式表明,在计数器中所得的数λ(λ=Qn-1---Q1Q0),与在取样时间T1 内输入电压的平均值VI 成正比的。

只要VI

由于双积分A/D 转换器在时间内采的是输入电压的平均值,因此具有很强的抗工频干扰的能力。

尤其对周期等于T1 或几分之一的对称干扰(所谓对称干扰是指整个周期内平均值为零的干扰),从理论上来说,有无穷大的抑制能力。

即使当工频干扰幅度大于被测直流信号,使得输入信号正负变化时,仍有良好的抑制能力。

由于在工业系统中经常碰到的是工频(50Hz)或工频的倍频干扰,故。

自学单片机之ADC 模数转换

之用,电池监测的电压范围可以从 0V 到 6V。XPT2046 片内集成有一个温度传感器。 在 2.7V 的典型工作状态

下,关闭参考电压,功耗可小于 0.75mW。

X、Y、Z、VBAT、Temp和AUX模拟信号经过片内的控制寄存器选择后进入ADC,ADC可以配置为单端或差分模式。选择VBAT、Temp和AUX时应该配置为单端模式;作为触摸屏应用时,应该配置为差分模式,这可有效消除由于驱动开关的寄生电阻及外部的干扰带来的测量误差,提高转换精度。

CLK = 1; //开始读

CLK = 0;

dat |= DOUT;用“与”符号是防止干扰只要DOUT有1则dat就有1

}

return dat;返回值

}

uint Read_AD_Data(uchar cmd)单片机读取AD值函数

{

uchar i;

uint AD_Value;

CLK = 0;

CS = 0;

return AD_Value;返回值等待调用

}

void datapros()数据处理函数

{

u16 temp;

static u8 i;

if(i==50)

{

i=0;

temp = Read_AD_Data(0x94);//

}

i++;

disp[0]=smgduan[temp/1000];//千位

disp[1]=smgduan[temp%1000/100];//百位

1.3编程相关

通信时序:程序:程思路:1首先我们要定义一个全局变量来存储我们读到的AD(模数转换)值;

最新ADC基础课件ppt

采样后频谱,如右图

36k

72k

108k

结论: 当IFS>FS/4时,ΔBW=FS/2-IFS-BW/2; 当IFS<FS/4时,ΔBW=IFS-BW/2; 18k 0.5fs 54k 1fs 90k 1.5fs 当IFS=FS/4时,ΔBW=FS/4-BW/2(b,)、ΔFBs=W72最KH大z, ΔBW=36-18-12.5=5.5KHz

2 * Fc

FS

ev, eF vIFrem C,F(S)F

od, d FIFFS-rem C,FS()F

[ ]表示取整数,rem() 表示取余数

以450KHz中频信号,采样频率为72KHz为例 采样后的频谱如图2.3所示 中频频率由450KHz 降为18KHz

图2.3 欠采样频谱

采样与量化

ADC基础

Contents

1

ADC简介

2

采样与量化

3

ADC工作原理

4

ADC选型

5

checklist

低通采样理论

采样与量化

乃奎斯特采样定理: 对于频率在(0,fH)区间内的时间连续信号m(t),如果以fS≥2*fH的频率进行采样, 则采样后的频谱不会发生混叠,m(t)可以由采样信号无失真的还原

N -

2

T k

1

M S(f) M(fkSf) Tk

结论:采样后的信号在频域上是原信号以采样频率fS为周期进行频谱扩展

采样与量化

模拟信号采样过程

采样与量化

带通采样理论

?思考:

前面的乃奎斯特采样理论指出针对频率在(0,fH)的信号,要求采样率fs≥2fH 那么针对频率在(fL,fH)的带通信号,其采样率是否仍然要求fs≥2fH?

高性能32位ADC芯片架构

高性能32位ADC芯片架构杭州恒芯微电子科技有限公司钟书鹏[摘要]HCT680x系列32位高精度、低零漂模数转换器为适用于分析天平、工业过程控制等衡器领域的ADC芯片。

通过ADC模型架构、电路结构、器件参数等方面的优化设计以及专利技术,ADC的实际有效精度(ENOB)达到24.3BIT@1倍PGA、22.9BIT@64倍PGA,等效输入噪声低至3nV/Hz姨,零漂0.5uV,零漂的温度系数低于5nV/℃,增益温漂系数也低至1ppm/℃。

PGA放大倍数为1~128倍,输出码率可在6.25Hz至51200Hz的宽范围内进行配置,以满足更多应用领域的需求。

[关键词]分析天平;高精度;低零漂;ADC[中图分类号]TH715.1[文献标识码]B[文章编号]1003-5729(2020)10-0031-05High-performance32-bit ADC chip architectureArticle abstract:HCT680x series32bit high precision,low zero drift ADC for analytical balance,industrial process control and other weighing equipment.Through the optimization design of ADC model architecture,circuit structure,device parameters and patented technology,the actual effective accuracy(ENOB)of ADC reaches24.3bit@1PGA and22.9bit@64PGA,the equivalent input noise is as low as3nV/Hz姨,zero drift is0.5uV,the zero drift temperature coefficient is lower than5nV/℃,and the gain temperature drift coefficient is as low as1ppm/℃.The PGA magnification is1~128times,and the output bit rate can be configured in a wide range of 6.25Hz to51200Hz to meet the needs of more application areas.Key words:analytical balance;high precision;low zero drift;ADC1背景高精度衡器应用领域如分析天平,其信号一般来自于精密桥式电阻传感器。

MT-026_cn ADC架构VII:计数ADC

2.

3. 4. 5.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

该脉宽调制pwm脉冲控制一个选通振荡器选通振荡器输出的脉冲数量代表模拟信号的量化值通过一个计数器很容易将该脉冲串转换成一个二进制字

MT-026 指南

ADC架构VII:计数ADC

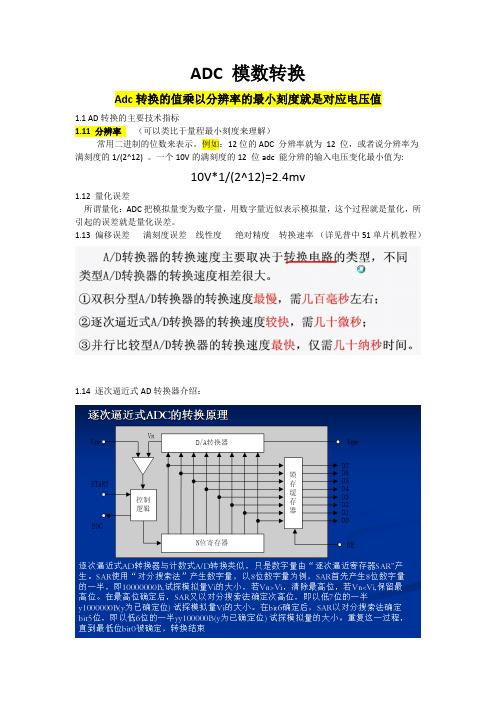

作者:Walt Kester和James Bryant 简介 计数ADC虽然不太适合高速应用,但却是高分辨率低频应用的理想之选,特别是结合使用 双斜式积分、三斜式积分、四斜式积分等技术时。 A. H. REEVES的5位计数ADC 计数ADC起源于1930年代末的早期实验性脉冲码调制(PCM)系统。A. H. Reeves在其内容全 面的1939年PCM专利档案(参考文献1)中描述了第一款适合PCM应用的ADC,图1是该ADC 的简化框图。早期用于PCM的ADC通常具有5到7位分辨率,采样速率为6 kSPS到10 kSPS。 非常有趣的是,Reeves的ADC是基于一种计数技术,原因很可能是他对计数器具有浓厚的 兴趣——就在几年前,Eccles-Jordan双稳态多谐振荡器刚刚问世。然而,在后来的PCM应 用中,其它架构的使用更为广泛,如Flash型(指南MT-020)、逐次逼近型(指南MT-021)、分 级和流水线型(指南MT-024)、每级一位型(指南MT-025)等。

ADC综述

ADC简介ADC分类模数转换包括采样、保持、量化和编码四个过程。

目前,世界上有多种类型的ADC,有传统的积分型、逐次逼近型、并行ADC,也有近年来新发展起来的流水线型、折叠型和Sigma-Delta型ADC,多种类型的ADC各有其优缺点并能满足不同的具体应用要求。

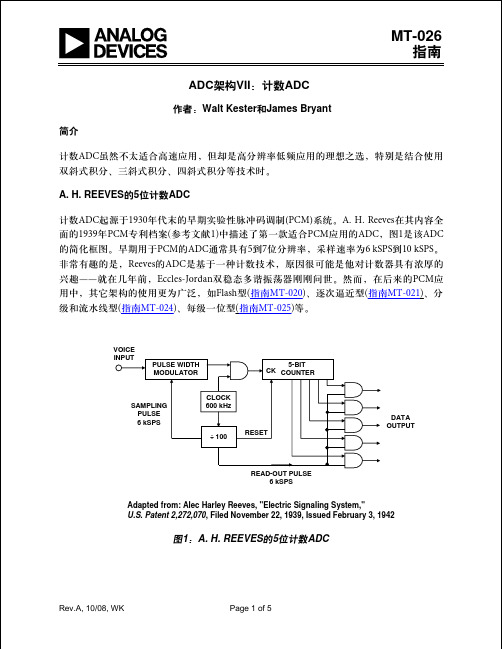

积分型ADC采样原理积分型模数转换器称双斜率或多斜率数据转换器,是应用最为广泛的转换器类型。

典型的是双斜率转换器,我们就以其为例说明积分型模数转换器的工作原理,如图1所示图1积分模数转换器的结构框图双斜率转换器由1个带有输入切换开关的模拟积分器、1个比较器和1个计数单元构成。

积分器对输入电压在固定的时间间隔内积分,该时间间隔通常对应于内部计数单元的最大的数。

时间到达后将计数器复位并将积分器输入连接到反板性(负)参考电压。

在这个反极性信号作用下,积分器被“反向积分”直到输出回到零,并使计数器终止,积分器复位。

积分型模数转换器的采样速度和带宽都非常低,但它们的精度可以做得很高,并且抑制高频噪声和固定的低频干扰(如50Hz或60Hz),使其对于嘈杂的工业环境以及不要求高转换速率的应用很有用(如热电偶输出的量化)。

因此积分型模数转换技术在低速、高精度测量领域有着广泛的应用,特别是在数字仪表领域。

其优点是:分辨率高(可达22bits),功耗低,成本低。

缺点是:转换速率低,转换精度为12bits时,它的转换速度为100~300sps。

逐次逼近(SAR)型ADC采样原理逐次逼近型ADC是应用非常广泛的模/数转换方法,它按照二分搜索法的原理,类似于天平称物的一种模数转换过程。

也就是将需要进行转换的模拟信号与已知的不同的参考电压进行多次比较,使转换后的数字量在数值上逐次逼近输入模拟量的对应值。

逐次逼近型ADC由比较器、D/A转换器、比较寄存器SAR、时钟发生器以及控制逻辑电路组成,将采样输入信号与已知电压不断进行比较,然后转换成二进制数。

其原理如图2所示,首先将DAC的最高有效位MSB保存到SAR,接着将该值对应的电压与输入电压进行比较。

adc芯片内部等效电路

adc芯片内部等效电路(原创实用版)目录1.ADC 芯片概述2.ADC 芯片的内部等效电路3.ADC 芯片的应用4.总结正文1.ADC 芯片概述ADC(Analog-to-Digital Converter,模拟 - 数字转换器)是一种将连续的模拟信号转换为离散的数字信号的设备。

这种设备在各种电子系统中都有广泛的应用,例如计算机、通信系统、仪器仪表等。

ADC 芯片是实现这种功能的核心部件,它通过内部的电路将输入的模拟电压信号转换成数字信号,并输出给后续的数字电路。

2.ADC 芯片的内部等效电路ADC 芯片的内部等效电路主要包括以下几个部分:(1)输入端:输入端用于接收输入的模拟电压信号。

通常,输入端需要进行信号放大和滤波处理,以确保输入信号的准确性和稳定性。

(2)比较器:比较器是 ADC 芯片的核心部分,它将输入的模拟电压信号与内部的参考电压进行比较,并输出相应的数字信号。

比较器的性能直接影响到 ADC 芯片的转换精度和速度。

(3)数字电路:数字电路用于对比较器输出的数字信号进行处理,例如进行编码、存储和传输等。

数字电路的性能也直接影响到 ADC 芯片的整体性能。

(4)参考电压:参考电压是 ADC 芯片内部电路的一个重要部分,它用于为比较器提供参考电压。

参考电压的稳定性和准确性对 ADC 芯片的转换精度有重要影响。

3.ADC 芯片的应用ADC 芯片广泛应用于各种电子系统中,例如计算机、通信系统、仪器仪表等。

在这些系统中,ADC 芯片主要用于实现模拟信号与数字信号的转换,以满足系统的信号处理和控制需求。

4.总结ADC 芯片是一种重要的模拟 - 数字转换设备,它通过内部的等效电路实现模拟信号与数字信号的转换。

ADC 芯片在各种电子系统中都有广泛的应用,其性能直接影响到整个系统的性能。

adc转换芯片

adc转换芯片ADC转换芯片(Analog-to-Digital Converter)是一种能够将连续的模拟信号转化为离散的数字信号的集成电路。

它广泛应用于各种领域,如测量、仪器、通信等。

在本文中,将介绍ADC转换芯片的原理、分类、工作过程以及应用。

原理:ADC转换芯片的原理是根据采样定理,通过固定的时间间隔采样模拟信号,并将采样值转化为相应的数字表示。

采样定理指的是,如果信号的最高频率为f,则采样频率应大于2f,以确保能够准确还原模拟信号。

分类:根据转换方式的不同,ADC转换芯片可以分为逐次逼近型(Successive Approximation)和并行型(Parallel)两种。

逐次逼近型ADC通过逐步逼近的方式将输入信号与一个内部的比较器进行比较,并根据比较结果改变内部的参考电压,最终获得与输入信号相匹配的数字表示。

并行型ADC则同时对输入信号进行多个采样,并将采样结果通过编码器转化为相应的数字表示。

工作过程:ADC转换芯片的工作过程主要包括采样、量化和编码三个步骤。

首先,芯片会根据设定的采样频率对输入信号进行采样,采样结果会存储在一个缓冲区中。

接下来,采样结果会经过量化处理。

量化是将连续的模拟信号转化为离散的数字表示,通常使用的方法是将模拟信号分成若干个等间隔的区间,并将采样结果映射到相应的区间中。

最后,采样结果经过编码器转化为对应的数字表示。

编码器可以是十进制编码、二进制编码等不同的形式。

应用:ADC转换芯片的广泛应用可以从以下几个方面来介绍:1. 测量和仪器领域:ADC转换芯片可以将模拟传感器(如温度传感器、压力传感器等)输出的模拟信号转化为数字信号,以便进行数字处理和分析。

2. 通信领域:ADC转换芯片可以将模拟音频信号(如语音、音乐等)转化为数字信号,以便在数字通信系统中进行传输和处理。

3. 控制系统:ADC转换芯片可以将模拟控制信号(如温度、湿度等)转化为数字信号,以便进行精确的控制和调节。

ad转换工作原理

ad转换工作原理

AD转换(Analog-to-digital conversion)是指将连续模拟信号

转换为离散数字信号的过程。

这个过程可以分为两个主要的步骤,采样和量化。

首先是采样,采样是指在连续时间域内按照一定频率(采样率)对模拟信号进行抽样,取样数据的间隔是固定的。

采样率决定了每秒采集多少个样本,一般以赫兹(Hz)表示,常见的采

样率有8kHz、16kHz、44.1kHz等。

采样率需要满足奈奎斯特

定理,即采样率要大于信号中最高频率的两倍,以避免采样失真。

接下来是量化,量化是指将每个采样值近似地表示为离散的数字值。

在量化过程中,采样值被映射到离散的数字级别中。

一般情况下,采样值在一个范围内,如-1到1之间,通过将这个范围划分为固定的间隔,每个间隔对应一个数字值。

量化的精度通过比特数来表示,比特数越高,表达能力越强,精度越高。

在实际的AD转换中,通常使用模数转换器(ADC)来完成

这个过程。

ADC包括一个采样保持电路,用于捕捉并保持模

拟信号的电压值,在采样期间保持不变;以及一个量化电路,将保持的模拟信号电压转换为离散的数字值。

总结起来,AD转换的工作原理是通过采样和量化这两个步骤,将连续模拟信号转换为离散数字信号。

这个过程可以通过

ADC实现,其中采样保持电路用于捕捉并保持模拟信号的电

压值,而量化电路则将保持的模拟信号电压转换为离散的数字值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MT-027

指南

ADC架构VIII:积分ADC

作者:Walt Kester和James Bryant

简介

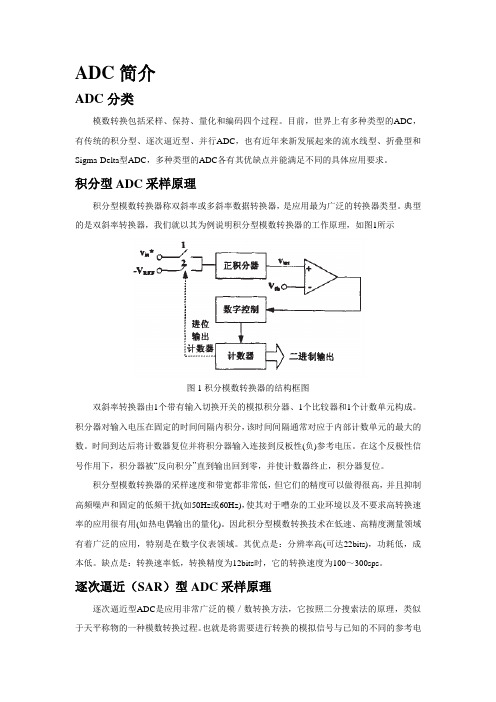

在发现基本计数ADC架构(参见教程MT-026)后,通过结合集成和计数技术就能实现更高精度,进而推动了高精度双斜率、三斜率和四斜率ADC的开发。

随着高分辨率Σ-Δ型ADC的迅速普及,集成架构不再像以前那样流行,不过仍用于各种精密应用,例如数字电压表等。

多斜率ADC

1950年代推出的“双斜率”ADC架构,对高分辨率应用中的ADC(例如数字电压表)确实是一大突破(参见参考文献1至4)。

简单示意图如图1所示,积分器输出波形如图2所示。

ANALOG

INPUT

V IN

–V REF

图1:双斜率积分ADC

计数器开始计算时钟脉冲的同时,输入信号施加于积分器。

经过预定时间(T)后,具有相反极性的基准电压施加于积分器。

此时,积分电容上的累积电荷与输入在间隔T内的平均值成正比。

基准电压积分是反向斜坡,斜率为V REF/RC。

同时,计数器重新从零计数。

当积分器输出到达零,计数停止,模拟电路复位。

由于所得电荷与V IN × T成正比,且相等数量的丢失电荷与V REF × t x成正比,因此相对于满量程计数的计数次数与t x/T或V IN/V REF 成正比。

如果计数器输出是二进制数,那么就是代表输入电压的二进制形式。

V IN RC T

V REF

RC

=t x

t x=V IN

V REF

T

HIGH NORMAL MODE REJECTION AT MULTIPLES OF 1

T

图2:双斜率ADC积分器输出波形

双斜率积分具有许多优点。

由于转换精度以相同比率影响上行斜率和下行斜率,所以与电容和时钟频率均无关。

固定输入信号积分周期抑制了模拟输入(其周期等于积分时间T或为其约数)上的噪声频率。

因此,只要正确选择T,就能实现对50 Hz和60 Hz线路纹波的极佳抑制,如图3所示。

利用额外充电/放电循环测量“零”和“满量程”,并借助测量结果对初始测量值进行数字校正,可以消除由偏置电流、积分放大器的失调电压和比较器造成的误差以及增益误差,如参考文献5所述的四斜率架构。

三斜率架构(参见参考文献6至8)保留了双斜率的优点,同时大幅提升了转换速度,但是增加了复杂性。

提升转换速度通过在两个不同速率下完成基准电压积分(斜降)来实现,即高速速率和“游标”低速速率。

计数器同样分成两部分,一部分用于MSB,一部分用于LSB。

在正确设计的三斜率转换器中,可以实现速度的大幅提升,同时保留双斜率ADC固有的线性度、微分线性和稳定性特性。

图3:积分ADC的频率响应

参考文献

1. Robin N. Anderson and Howard A. Dorey, "Digital V oltmeters," U.S. Patent 3,267,458, filed August 20, 1962,

issued August 16, 1966. (charge balance dual slope voltmeter ADC).

2. Richard Olshausen, "Analog-to-Digital Converter," U.S. Patent 3,281,827, filed June 27, 1963, issued October

25, 1966. (charge balance dual slope ADC).

3. Roswell W. Gilbert, "Analog-to-Digital Converter," U.S. Patent 3,051,939, filed May 8, 1957, issued August 28,

1962. (dual-slope ADC).

4. Stephan K. Ammann, "Integrating Analog-to-Digital Converter," U.S. Patent 3,316,547, filed July 15, 1964,

issued April 25, 1967. (dual-slope ADC).

5. Ivar Wold, "Integrating Analog-to-Digital Converter Having Digitally-Derived Offset Error Compensation and

Bipolar Operation without Zero Discontinuity," U.S. Patent 3,872,466, filed July 19, 1973, issued March 18, 1975. (quad-slope ADC).

6. Hans Bent Aasnaes, "Triple Integrating Ramp Analog-to-Digital Converter," U.S. Patent 3,577,140, filed June

27, 1967, issued May 4, 1971. (triple-slope ADC).

7. Frederick Bondzeit, Lewis J. Neelands, "Multiple Slope Analog-to-Digital Converter," U.S. Patent 3,564,538,

filed January 29, 1968, issued February 16, 1971. (triple-slope ADC).

8. Desmond Wheable, "Triple-Slope Analog-to-Digital Converters," U.S. Patent 3,678,506, filed October 2, 1968,

issued July 18, 1972. (triple-slope ADC).

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.。