ARM指令 中文全称及功能应用详解

arm的原理与应用领域

ARM的原理与应用领域1. 简介ARM(Advanced RISC Machine)是一种精简指令集计算机(RISC)体系结构,广泛用于移动设备、嵌入式系统和服务器等领域。

它以其低功耗、高性能和可扩展性而闻名,成为当今计算领域最为流行的架构之一。

本文将介绍ARM架构的原理和其在各个应用领域中的应用情况。

2. ARM架构原理ARM架构采用了精简指令集计算机(RISC)的设计原理,其核心思想是通过优化指令集,提高指令执行效率,从而提高处理器的性能和功耗效率。

2.1 精简指令集ARM采用精简指令集,指令长度固定为32位,指令格式规范简单。

这样做的好处是指令的译码执行速度更快,从而加快了处理器的运行速度。

2.2 多级流水线ARM处理器采用多级流水线,将指令执行过程划分为若干个阶段,每个阶段由一个专门的硬件电路来执行。

这样做的好处是可以实现指令的并行执行,提高了处理器的吞吐量。

2.3 按需执行和条件执行ARM架构支持按需执行和条件执行的特性。

按需执行意味着只有在需要的时候才执行指令,可以节省处理器的功耗。

条件执行意味着根据条件判断是否执行某条指令,可以提高程序的执行效率。

3. ARM的应用领域ARM架构由于其低功耗和高性能的特点,被广泛应用于各个领域。

下面将介绍ARM在移动设备、嵌入式系统和服务器等领域的应用情况。

3.1 移动设备ARM架构在移动设备领域应用广泛。

例如,大部分智能手机和平板电脑都使用ARM架构的处理器。

ARM处理器低功耗的特点使得移动设备可以更长时间地使用电池,同时其高性能也能够满足现代移动应用的需求。

3.2 嵌入式系统嵌入式系统是指将计算机系统集成到特定应用领域中的系统。

ARM架构在嵌入式系统领域应用广泛,例如,智能家居系统、智能交通系统、工业自动化系统等都使用了ARM架构的处理器。

ARM处理器的低功耗和高性能使得嵌入式系统可以实现更高的效能和更好的稳定性。

3.3 服务器ARM架构在服务器领域的应用也在不断增加。

ARM常用概念及基本功能使用说明

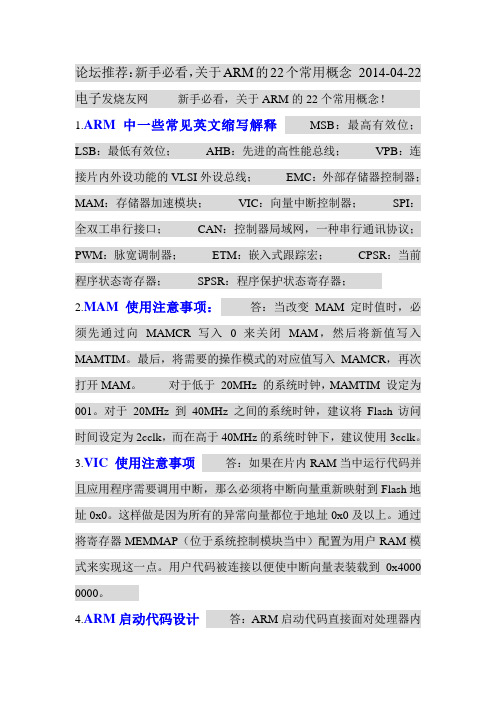

论坛推荐:新手必看,关于ARM的22个常用概念2014-04-22 电子发烧友网新手必看,关于ARM的22个常用概念!1.ARM中一些常见英文缩写解释MSB:最高有效位;LSB:最低有效位;AHB:先进的高性能总线;VPB:连接片内外设功能的VLSI外设总线;EMC:外部存储器控制器;MAM:存储器加速模块;VIC:向量中断控制器;SPI:全双工串行接口;CAN:控制器局域网,一种串行通讯协议;PWM:脉宽调制器;ETM:嵌入式跟踪宏;CPSR:当前程序状态寄存器;SPSR:程序保护状态寄存器;2.MAM 使用注意事项:答:当改变MAM 定时值时,必须先通过向MAMCR 写入0 来关闭MAM,然后将新值写入MAMTIM。

最后,将需要的操作模式的对应值写入MAMCR,再次打开MAM。

对于低于20MHz 的系统时钟,MAMTIM 设定为001。

对于20MHz 到40MHz 之间的系统时钟,建议将Flash访问时间设定为2cclk,而在高于40MHz的系统时钟下,建议使用3cclk。

3.VIC 使用注意事项答:如果在片内RAM当中运行代码并且应用程序需要调用中断,那么必须将中断向量重新映射到Flash地址0x0。

这样做是因为所有的异常向量都位于地址0x0及以上。

通过将寄存器MEMMAP(位于系统控制模块当中)配置为用户RAM模式来实现这一点。

用户代码被连接以便使中断向量表装载到0x4000 0000。

4.ARM启动代码设计答:ARM启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。

启动代码一般包括:中断向量表初始化存储器系统初始化堆栈初始化有特殊要求的端口、设备初始化用户程序执行环境改变处理器模式呼叫主应用程序5.IRQ 和FIQ 之间的区别答:IRQ和FIQ是ARM处理器的两种编程模式。

IRQ是指中断模式,FIR是指快速中断模式。

对于FIQ 你必须尽快处理你的事情并离开这个模式。

IRQ 可以被FIQ 所中断,但IRQ 不能中断FIQ。

常用arm指令集

常用arm指令集ARM指令集是一种广泛使用的指令集架构,被广泛应用于各种嵌入式系统、移动设备和服务器等领域。

它具有高效、灵活、可扩展等特点,是现代计算机体系结构的重要组成部分。

本文将介绍常用的ARM指令集。

一、ARM指令集概述ARM指令集是一种精简指令集(RISC)架构,它采用了精简的指令集来提高执行效率和降低功耗。

由于其精简化的设计,ARM处理器可以在更小的面积内实现更高的性能和更低的功耗。

目前,ARM处理器已经广泛应用于各种嵌入式系统、移动设备和服务器等领域。

二、常用ARM指令集1.数据处理指令数据处理指令是最基本和最常用的ARM指令之一。

它包括加法、减法、乘法、除法等运算操作。

这些操作不涉及内存访问,只对寄存器中的数据进行操作。

例如:ADD R1, R2, R3:将R2和R3中的值相加,并将结果存储到R1中。

SUB R1, R2, #10:将R2中的值减去10,并将结果存储到R1中。

MUL R1, R2, R3:将R2和R3中的值相乘,并将结果存储到R1中。

2.数据传输指令数据传输指令是用于在寄存器和内存之间传输数据的指令。

它包括从内存读取数据、向内存写入数据等操作。

例如:LDR R1, [R2]:从地址为R2的内存单元中读取一个字节的数据,并将其存储到寄存器R1中。

STR R1, [R2]:将寄存器R1中的值写入地址为R2的内存单元中。

3.分支指令分支指令用于实现程序跳转,包括无条件跳转、有条件跳转等操作。

它是实现程序控制流程的关键指令之一。

例如:B label:无条件跳转到标记为label的位置。

BEQ label:如果前一次比较结果为相等,则跳转到标记为label的位置。

4.逻辑运算指令逻辑运算指令用于实现与、或、非、异或等逻辑运算操作。

它通常用于实现位操作和掩码操作等功能。

例如:AND R1, R2, #0xFF:将寄存器R2和0xFF进行按位与操作,并将结果存储到寄存器R1中。

ORR R1, R2, #0xFF:将寄存器R2和0xFF进行按位或操作,并将结果存储到寄存器R1中。

常用ARM指令

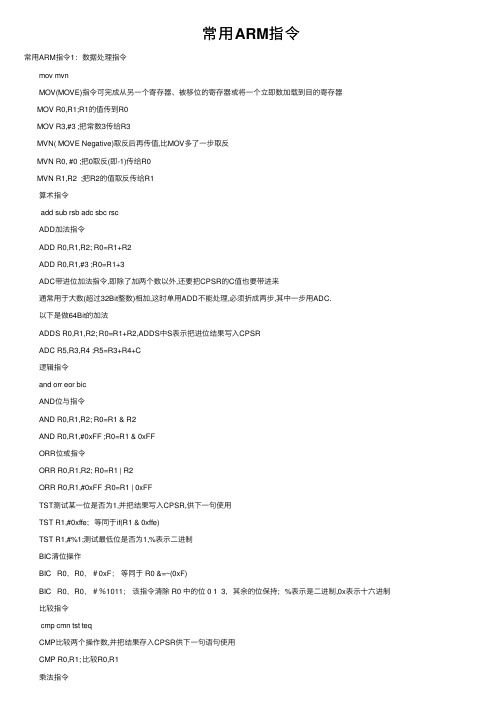

常⽤ARM指令常⽤ARM指令1:数据处理指令 mov mvn MOV(MOVE)指令可完成从另⼀个寄存器、被移位的寄存器或将⼀个⽴即数加载到⽬的寄存器MOV R0,R1;R1的值传到R0MOV R3,#3 ;把常数3传给R3MVN( MOVE Negative)取反后再传值,⽐MOV多了⼀步取反MVN R0, #0 ;把0取反(即-1)传给R0MVN R1,R2 ;把R2的值取反传给R1 算术指令 add sub rsb adc sbc rsc ADD加法指令 ADD R0,R1,R2; R0=R1+R2 ADD R0,R1,#3 ;R0=R1+3 ADC带进位加法指令,即除了加两个数以外,还要把CPSR的C值也要带进来 通常⽤于⼤数(超过32Bit整数)相加,这时单⽤ADD不能处理,必须折成两步,其中⼀步⽤ADC. 以下是做64Bit的加法 ADDS R0,R1,R2; R0=R1+R2,ADDS中S表⽰把进位结果写⼊CPSR ADC R5,R3,R4 ;R5=R3+R4+C 逻辑指令 and orr eor bic AND位与指令 AND R0,R1,R2; R0=R1 & R2 AND R0,R1,#0xFF ;R0=R1 & 0xFF ORR位或指令 ORR R0,R1,R2; R0=R1 | R2 ORR R0,R1,#0xFF ;R0=R1 | 0xFF TST测试某⼀位是否为1,并把结果写⼊CPSR,供下⼀句使⽤ TST R1,#0xffe; 等同于if(R1 & 0xffe) TST R1,#%1;测试最低位是否为1,%表⽰⼆进制 BIC清位操作 BIC R0,R0,#0xF;等同于 R0 &=~(0xF) BIC R0,R0,#%1011;该指令清除 R0 中的位 0 1 3,其余的位保持; %表⽰是⼆进制,0x表⽰⼗六进制 ⽐较指令 cmp cmn tst teq CMP⽐较两个操作数,并把结果存⼊CPSR供下⼀句语句使⽤ CMP R0,R1; ⽐较R0,R1 乘法指令 mvl mla umull umlal smull small MUL R0,R1,R2 ;R0 = R1 × R2MULS R0,R1,R2 ;R0 = R1 × R2,同时设置CPSR中的相关条件标志位 MLA R0,R1,R2,R3 ;R0 = R1 × R2 + R3MLAS R0× R2 + R3,同时设置CPSR中的相关条件标志位 SMULL R0,R1,R2,R3 ;R0 = (R2 × R3)的低32位 ;R1 = (R2 × R3)的⾼32位 加载/存储指令 LDR,STR LDR R0,[R1]; R1的值当成地址,再从这个地址装⼊数据到R0 (R0=*R1) LDR R1,=0x30008000 ; 把地址0x30008000的值装⼊到R1中 STR R0,[R1] ; 把R0的值,存⼊到R1对应地址空间上(*R1 = R0)。

arm 汇编 指令

arm 汇编指令ARM汇编指令是一种用于编写ARM处理器程序的语言。

ARM处理器广泛应用于嵌入式系统和移动设备等领域。

ARM汇编指令与x86汇编指令有所不同,它基于RISC(精简指令集计算机)架构。

下面是一些基本的ARM汇编指令:1. 数据传输指令:用于在寄存器之间传输数据。

例如:- mov:将数据从一个寄存器传输到另一个寄存器。

- ldr:将数据从内存传输到寄存器。

2. 算术指令:用于执行加法、减法、乘法和除法等操作。

例如:- add:加法操作。

- sub:减法操作。

- mull:乘法操作。

- div:除法操作。

3. 逻辑指令:用于执行逻辑操作,如与、或、非等。

例如:- and:与操作。

- or:或操作。

- xor:异或操作。

4. 移位指令:用于对数据进行左移、右移或无符号右移。

例如:- lsr:无符号右移。

- asr:带符号右移。

- ror:循环右移。

5. 比较指令:用于比较两个寄存器的值。

例如:- cmp:比较两个寄存器的值,若相等则返回0,否则返回1。

6. 跳转指令:用于改变程序的执行流程。

例如:- b:条件跳转。

- bl:无条件跳转。

- bx:带状态跳转。

7. 循环指令:用于实现循环操作。

例如:- loop:内部循环。

- ldp:外部循环。

8. 调用指令:用于实现函数调用。

例如:- blx:带状态调用。

- bx:不带状态调用。

9. 系统调用指令:用于实现与操作系统交互的功能。

例如:- swi:执行系统调用。

10. 存储器访问指令:用于访问内存数据。

例如:- str:将数据存储到内存。

- ldr:从内存中加载数据。

以上仅为ARM汇编指令的一部分,实际上,ARM汇编指令还有很多其他功能。

为了更好地理解和使用ARM汇编指令,可以参考相关的教程和手册,并进行实际操作。

ARM简介

6.移动互联网领域

ARM技术打造世界级的Web2.0产品

目前大多数智能手机采用ARM11处理器 基于Cortex-A处理器的Web2.0手机 ARMv7架构的设计为Web2.0做了专门设计

矢量浮点运算单元 Thumb-2和Thumb-2 EE指令用于解释器和JITs NEON SIMD技术

美国加州大学伯克利分校的Patterson教授领导 的研究生团队设计和实现了“伯克利RISC I”处理 器,他们在此基础之上又发展了后来SUN公司的 SPARC系列RISC处理器,并使得采用该处理器的 SUN工作站名振一时。 与此同时,斯坦福大学也在RISC研究领域取得了 重大进展,开发并产业化了MIPS( Million Instructions Per Second )系列RISC处理器。

ARM是什么? ARM为什么存在? ARM有什么优势? ARM体系结构的发展历程? ARM可以应用在哪些方面?

二、ARM为什么存在

RISC体系结构 ARM的诞生

1.RISC体系结构

传统的CISC(Complex Instruction Set Computer,复杂 指令集计算机)体系由于指令集庞大,指令长度不固定,指 令执行周期有长有短,使指令译码和流水线的实现在硬件上 非常复杂,给芯片的设计开发和成本的降低带来了极大困难。 随着计算机技术的发展需要不断引入新的复杂的指令集, 为支持这些新增的指令,计算机的体系结构会越来越复杂。然 而,在CISC指令集的各种指令中,其使用频率却相差悬殊,大约 有 20%的指令会被反复使用,占整个程序代码的80%。而余 下的80%的指令却不经常使用,在程序设计中只占20%,显然, 这种结构是不太合理的。

5.arm和x86的常用指令用法

Arm和x86是两种常见的指令集架构,分别用于移动设备和个人电脑。

它们的指令集有很多共同之处,但也有一些差异。

本文将介绍Arm和x86的常用指令用法,以帮助读者更好地理解这两种架构的特点和优劣势。

一、Arm指令集架构(Arm ISA)Arm是一种RISC(Reduced Instruction Set Computer)架构,其指令集相对较小,执行效率较高。

Arm指令集包括以下几类指令:1. 数据传送指令:包括MOV(数据传送)、LDR(加载)、STR(存储)等指令,用于在寄存器和内存之间传递数据。

2. 算术运算指令:包括ADD(加法)、SUB(减法)、MUL(乘法)、DIV(除法)等指令,用于进行各种算术运算。

3. 逻辑运算指令:包括AND(与)、ORR(或)、EOR(异或)、NOT(取反)等指令,用于执行逻辑运算。

4. 分支跳转指令:包括B(无条件跳转)、BEQ(等于时跳转)、BNE(不等于时跳转)等指令,用于在程序中实现跳转功能。

5. 特权指令:包括MRS(读特权寄存器)、MSR(写特权寄存器)、SVC(软中断)等指令,用于管理处理器的特权模式和中断处理。

以上是Arm指令集中的一些常用指令,通过它们可以实现各种功能和操作。

二、x86指令集架构(x86 ISA)x86是一种CISC(Complex Instruction Set Computer)架构,其指令集较大且复杂,包括以下几类指令:1. 数据传送指令:包括MOV(数据传送)、LEA(加载有效位置区域)、XCHG(交换数据)等指令,用于在寄存器和内存之间传递数据。

2. 算术运算指令:包括ADD(加法)、SUB(减法)、IMUL(整数乘法)、IDIV(整数除法)等指令,用于进行各种算术运算。

3. 逻辑运算指令:包括AND(与)、OR(或)、XOR(异或)、NOT(取反)等指令,用于执行逻辑运算。

4. 分支跳转指令:包括JMP(无条件跳转)、JE(等于时跳转)、JNE(不等于时跳转)等指令,用于在程序中实现跳转功能。

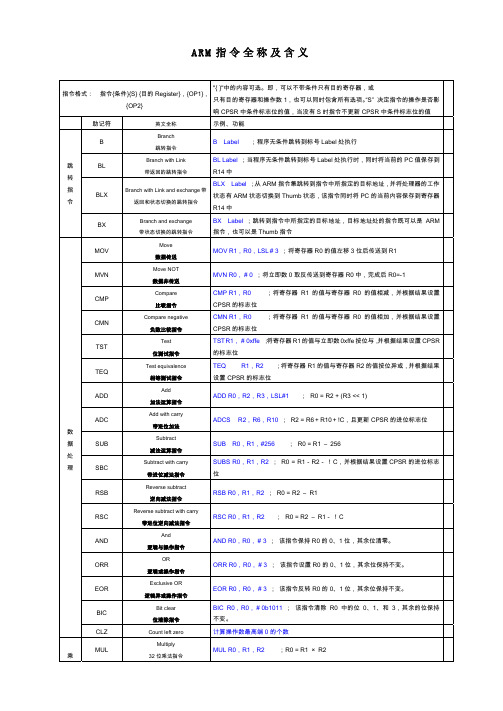

ARM指令全称及含义

PSR 3 field

F (Flags field mask byte)

S (Stats field mask byte)

X (Extension field mask byte)

C (control field mask byte)

CPSR 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Swap byte

AND R0,R0,#3 ; 该指令保持 R0 的 0、1 位,其余位清零。 ORR R0,R0,#3 ; 该指令设置 R0 的 0、1 位,其余位保持不变。 EOR R0,R0,#3 ; 该指令反转 R0 的 0、1 位,其余位保持不变。 BIC R0,R0,#0b1011 ; 该指令清除 R0 中的位 0、1、和 3,其余的位保持不变。 计算操作数最高端 0 的个数 MUL R0,R1,R2 ;R0 = R1 × R2 MLAS R0,R1,R2,R3 ;R0 = R1 × R2 + R3,同时设置 CPSR 中的相关条件标志位 SMULL R0,R1,R2,R3 ;R0 = (R2 × R3)的低 32 位 R1 = (R2 × R3)的高 32 位 SMLAL R0,R1,R2,R3;R0 =(R2 × R3)的低 32 位+R0; R1 =(R2 × R3)的高 32 位+ R1 UMULL R0,R1,R2,R3;R0 = (R2 × R3)的低 32 位;R1 =(R2 × R3)的高 32 位 UMLAL R0,R1,R2,R3;R0 =(R2 × R3)的低位+R0;R1 =(R2 × R3)的高 32 位+R1 MRS R0,CPSR ;传送 CPSR 的内容到 R0 MSR CPSR_c ,R0 ;传送 R0 的内容到 SPSR,但仅仅修改 CPSR 中的控制位域 LDR R0,[R1,R2]! ;将存储器地址为 R1+R2 的字数据读入 R0,并将新地址 R1+R2 写入 R1。 LDRB R0,[R1,#8] ;将存储器地址为 R1+8 的字节数据读入 R0,并将 R0 的高 24 位清零 LDRH R0,[R1] ;将存储器地址为 R1 的半字数据读入寄存器 R0,并将 R0 的高 16 位清零 LDMFD R13!,{R0,R4-R12,PC} ;将堆栈内容恢复到寄存器(R0,R4 到 R12,LR) STR R0,[R1],#8 ;将 R0 中的字数据写入 R1 为地址的存储器中,并将新地址 R1+8 写入 R1 STRB R0,[R1,#8] ;将寄存器 R0 中的字节数据写入以 R1+8 为地址的存储器中 STRH R0,[R1,#8] ;将寄存器 R0 中的半字数据写入以 R1+8 为地址的存储器中 STMFD R13!,{R0,R4-R12,LR};将寄存器列表中的寄存器(R0,R4 到 R12,LR)存入堆栈 SWP R0,R1,[R2] ;R2 所指的字数据传送到 R0,同时 R1 的数据传送到 R2 所指的单元 SWPB R0,R1,[R2] ;R2 所指的字节数据传送到 R0,R0 高 24 位清零,同时 R1 低 8 位送 R2 所指单元。

arm指令

一、加减法指令:1、MOV(move):数据传送指令2、MVN(move negative):数据取反传送指令3、ADD(add):加法4、ADC(add with carry):带进位加法5、SUB(subtract):减法6、RSB(reverse subtract):反向减法7、SBC(subtract with carry):带借位的减法SBC{<cond>}{S} <Rd>,<Rn>,<op2> ;Rd=Rn-op2-carry8、RSC(reverse subtract with carry):带借位的反向减法RSC{<cond>}{S} <Rd>,<Rn>,<op3> ;Rd= op3-Rn-!carry二、逻辑指令1、AND:逻辑与2、ORR(logical or):逻辑或3、EOR(exclusive or):逻辑异或4、BIC(bit clear):位清零5、CLZ(count leading zeros):位计数。

CLZ{<cond>} <Rd>,<Rm>;计算存储在Rm寄存器中各位为0的总个数。

三、乘法指令1、MUL(multiply):32位乘法2、MLA(multiply accumulate):32位乘加MLA{<cond>} {S} <Rd>,<Rn>,<op2>,<op3>;3、SMULL(signed multiplication long):64位有符号数乘法SMULL {<cond>}{S} <Rdl>,<Rdh>,<Rn>,<op2>;Rdh Rdl=Rn×op2,结果的高32位存入Rdh,低32位存入Rdl。

arm架构指令集

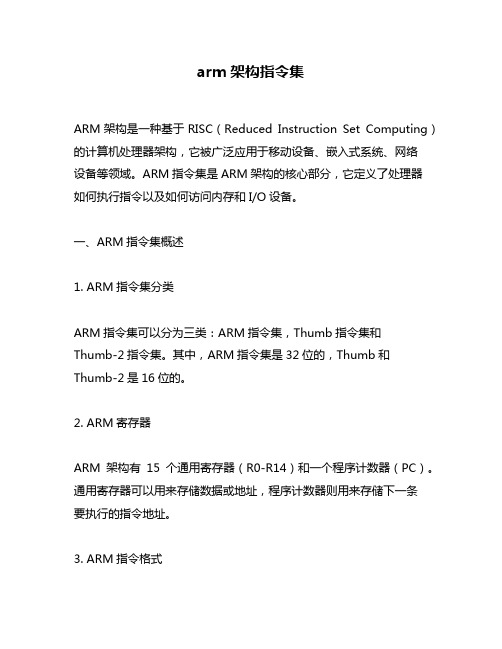

arm架构指令集ARM架构是一种基于RISC(Reduced Instruction Set Computing)的计算机处理器架构,它被广泛应用于移动设备、嵌入式系统、网络设备等领域。

ARM指令集是ARM架构的核心部分,它定义了处理器如何执行指令以及如何访问内存和I/O设备。

一、ARM指令集概述1. ARM指令集分类ARM指令集可以分为三类:ARM指令集,Thumb指令集和Thumb-2指令集。

其中,ARM指令集是32位的,Thumb和Thumb-2是16位的。

2. ARM寄存器ARM架构有15个通用寄存器(R0-R14)和一个程序计数器(PC)。

通用寄存器可以用来存储数据或地址,程序计数器则用来存储下一条要执行的指令地址。

3. ARM指令格式ARM指令格式包括操作码、操作数和条件码。

操作码表示要执行的操作类型,操作数表示要进行操作的数据或地址,条件码表示在何种情况下执行该条指令。

4. ARM访问内存在ARM中,访问内存需要使用Load和Store指令。

Load用于将数据从内存中读取到寄存器中,Store用于将数据从寄存器中写入到内存中。

5. ARM流水线流水线是ARM处理器中的一种指令执行方式,它将指令执行过程分为若干个阶段,每个阶段可以同时执行不同的指令。

ARM流水线包括取指、译码、执行、访存和写回等阶段。

二、ARM指令集详解1. ARM指令集ARM指令集是32位的,它支持数据处理、分支跳转、访存和其他操作。

以下是一些常用的ARM指令:(1)MOV:将一个寄存器中的值移动到另一个寄存器中。

(2)ADD:将两个寄存器中的值相加,并将结果存储到另一个寄存器中。

(3)SUB:将两个寄存器中的值相减,并将结果存储到另一个寄存器中。

(4)MUL:将两个寄存器中的值相乘,并将结果存储到另一个寄存器中。

(5)CMP:比较两个寄存器中的值是否相等,并设置条件码。

2. Thumb指令集Thumb指令集是16位的,它可以减小程序大小和内存占用。

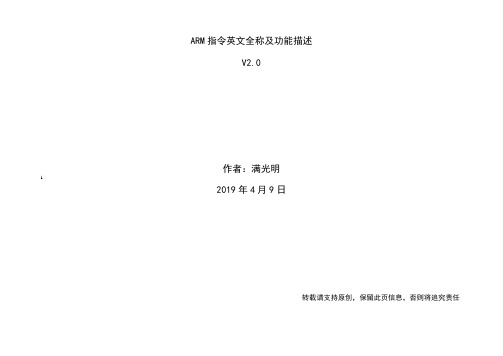

(完整版)ARM汇编指令英文全称及功能描述V2.0

1 ARM指令英文全称及功能描述V2.0作者:满光明2019年4月9日转载请支持原创,保留此页信息,否则将追究责任前言我在工作前买了一本关于ARM指令的书籍,当时出于方便记忆理解的考量,整理了ARM指令,并且加入了英文的全称。

了解了英文的全称,能够好的帮助记忆和理解。

百度网盘里分享出来的ARM 指令英文全称我看了一下都是我当年整理的版本,但他们把作者的名字去掉了。

几年过去了,ARM技术取得了巨大的进步,ARM以其低功耗、低成本、高性能的优势抢占了移动市场。

相信在不远的未来,ARM会普遍运行在个人电脑和服务器上。

在可穿戴、边缘计算等前沿领域ARM拥有无与伦比的优势。

作为一个技术控,工作以来我一直从事ARM相关的开发工作,计算机领域需要学习的东西太多,但很多基础知识都是相通的。

我也希望能把自己这么多年的技术积累拿出来分享给即将走上硬件开发、底层驱动开发的同仁们本篇仍然以介绍ARM架构以及ARM指令为主,在原来的基础上重新调整了指令顺序,首先介绍ARM 架构不同版本的区别,进而引出基本指令结构,最后详细列出所有指令详表,增强可读性,易于理解。

2一、ARM指令集版本历史计算机完成一定的操作通过指令来实现,不同的指令方式被称为计算机架构,目前计算机主要有两大架构阵营,一是CISC (Complex Instruction Set Computers)复杂指令集架构,另一种是RISC(Reduced Instruction Set Computers)精简指令集架构。

采用CISC架构的代表是Intel和AMD的X86指令集,采用RISC架构的代表是ARM指令集和PowerPC指令集。

ARM架构从诞生到今天从V1版本已经升级到了V8版本,各版本代表的分支型号如下表所示。

从图中可以看出,Cortex-A9 架构的CPU采用的是ARMv7的指令集,目前高性能的64位视频处理,比如Cortex-A72,采用的是ARMv8指令集。

ARM指令全称及含义

Great than or equal, or unordered Less than Less than Greater than or equal , or unordered Unordered

域

VC

HI

LS

GE

LT

GT

LE

AL

V=0 C=1 且 Z=0 C=0 或 Z=1 N=1 且 V=1 或 N=0 且 V=0 N=1 且 V=0 或 N=0 且 V=1 Z=0 或 N=V Z=1 或 N!=V

M[4:0]

0b10000 0b10001 0b10010 0b10011 0b10111 0b11011 0b11111

User FIQ IRQ Supervisor Abort Undefined System

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Signed saturating arithmetic

Signed arithmetic, halving results

Swap byte

AND R0,R0,#3 ; 该指令保持 R0 的 0、1 位,其余位清零。 ORR R0,R0,#3 ; 该指令设置 R0 的 0、1 位,其余位保持不变。 EOR R0,R0,#3 ; 该指令反转 R0 的 0、1 位,其余位保持不变。 BIC R0,R0,#0b1011 ; 该指令清除 R0 中的位 0、1、和 3,其余的位保持不变。 计算操作数最高端 0 的个数 MUL R0,R1,R2 ;R0 = R1 × R2 MLAS R0,R1,R2,R3 ;R0 = R1 × R2 + R3,同时设置 CPSR 中的相关条件标志位 SMULL R0,R1,R2,R3 ;R0 = (R2 × R3)的低 32 位 R1 = (R2 × R3)的高 32 位 SMLAL R0,R1,R2,R3;R0 =(R2 × R3)的低 32 位+R0; R1 =(R2 × R3)的高 32 位+ R1 UMULL R0,R1,R2,R3;R0 = (R2 × R3)的低 32 位;R1 =(R2 × R3)的高 32 位 UMLAL R0,R1,R2,R3;R0 =(R2 × R3)的低位+R0;R1 =(R2 × R3)的高 32 位+R1 MRS R0,CPSR ;传送 CPSR 的内容到 R0 MSR CPSR_c ,R0 ;传送 R0 的内容到 SPSR,但仅仅修改 CPSR 中的控制位域 LDR R0,[R1,R2]! ;将存储器地址为 R1+R2 的字数据读入 R0,并将新地址 R1+R2 写入 R1。 LDRB R0,[R1,#8] ;将存储器地址为 R1+8 的字节数据读入 R0,并将 R0 的高 24 位清零 LDRH R0,[R1] ;将存储器地址为 R1 的半字数据读入寄存器 R0,并将 R0 的高 16 位清零 LDMFD R13!,{R0,R4-R12,PC} ;将堆栈内容恢复到寄存器(R0,R4 到 R12,LR) STR R0,[R1],#8 ;将 R0 中的字数据写入 R1 为地址的存储器中,并将新地址 R1+8 写入 R1 STRB R0,[R1,#8] ;将寄存器 R0 中的字节数据写入以 R1+8 为地址的存储器中 STRH R0,[R1,#8] ;将寄存器 R0 中的半字数据写入以 R1+8 为地址的存储器中 STMFD R13!,{R0,R4-R12,LR};将寄存器列表中的寄存器(R0,R4 到 R12,LR)存入堆栈 SWP R0,R1,[R2] ;R2 所指的字数据传送到 R0,同时 R1 的数据传送到 R2 所指的单元 SWPB R0,R1,[R2] ;R2 所指的字节数据传送到 R0,R0 高 24 位清零,同时 R1 低 8 位送 R2 所指单元。

arm的原理与应用

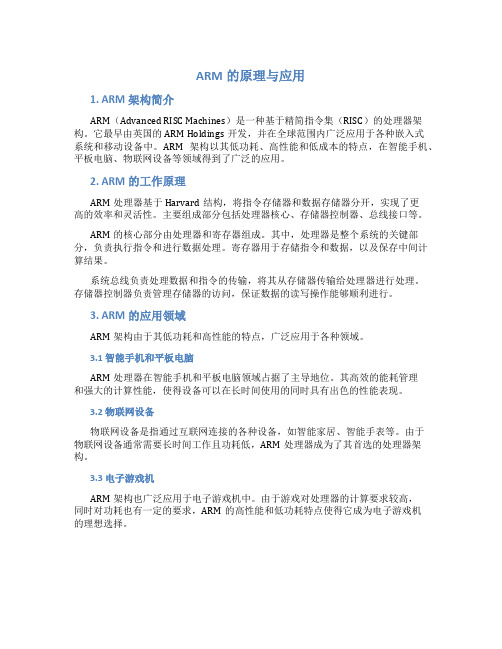

ARM的原理与应用1. ARM架构简介ARM(Advanced RISC Machines)是一种基于精简指令集(RISC)的处理器架构。

它最早由英国的ARM Holdings开发,并在全球范围内广泛应用于各种嵌入式系统和移动设备中。

ARM架构以其低功耗、高性能和低成本的特点,在智能手机、平板电脑、物联网设备等领域得到了广泛的应用。

2. ARM的工作原理ARM处理器基于Harvard结构,将指令存储器和数据存储器分开,实现了更高的效率和灵活性。

主要组成部分包括处理器核心、存储器控制器、总线接口等。

ARM的核心部分由处理器和寄存器组成。

其中,处理器是整个系统的关键部分,负责执行指令和进行数据处理。

寄存器用于存储指令和数据,以及保存中间计算结果。

系统总线负责处理数据和指令的传输,将其从存储器传输给处理器进行处理。

存储器控制器负责管理存储器的访问,保证数据的读写操作能够顺利进行。

3. ARM的应用领域ARM架构由于其低功耗和高性能的特点,广泛应用于各种领域。

3.1 智能手机和平板电脑ARM处理器在智能手机和平板电脑领域占据了主导地位。

其高效的能耗管理和强大的计算性能,使得设备可以在长时间使用的同时具有出色的性能表现。

3.2 物联网设备物联网设备是指通过互联网连接的各种设备,如智能家居、智能手表等。

由于物联网设备通常需要长时间工作且功耗低,ARM处理器成为了其首选的处理器架构。

3.3 电子游戏机ARM架构也广泛应用于电子游戏机中。

由于游戏对处理器的计算要求较高,同时对功耗也有一定的要求,ARM的高性能和低功耗特点使得它成为电子游戏机的理想选择。

3.4 嵌入式系统ARM处理器广泛应用于各种嵌入式系统中,如数字电视机顶盒、路由器等。

由于嵌入式系统通常需要在有限的资源下运行,ARM处理器的高效能和低功耗使得它成为嵌入式系统的常用处理器。

4. ARM的优势ARM架构相比于其他处理器架构具有以下优势:•低功耗:ARM处理器以其低能耗的特点,能够在较长时间内保持设备的稳定工作,适用于移动设备等对功耗要求较高的场景。

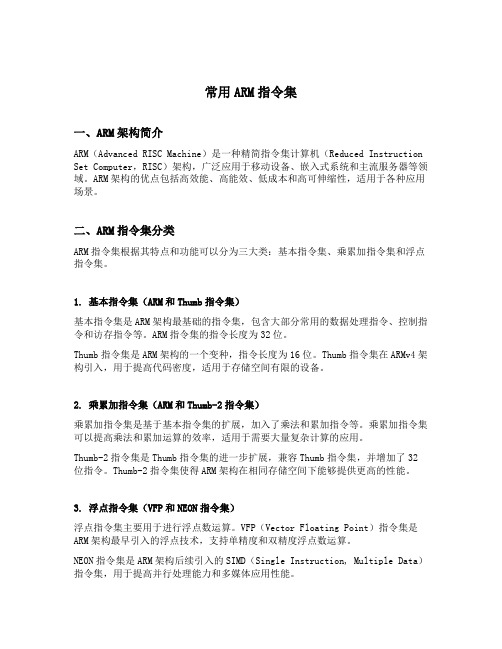

常用arm指令集

常用ARM指令集一、ARM架构简介ARM(Advanced RISC Machine)是一种精简指令集计算机(Reduced Instruction Set Computer,RISC)架构,广泛应用于移动设备、嵌入式系统和主流服务器等领域。

ARM架构的优点包括高效能、高能效、低成本和高可伸缩性,适用于各种应用场景。

二、ARM指令集分类ARM指令集根据其特点和功能可以分为三大类:基本指令集、乘累加指令集和浮点指令集。

1. 基本指令集(ARM和Thumb指令集)基本指令集是ARM架构最基础的指令集,包含大部分常用的数据处理指令、控制指令和访存指令等。

ARM指令集的指令长度为32位。

Thumb指令集是ARM架构的一个变种,指令长度为16位。

Thumb指令集在ARMv4架构引入,用于提高代码密度,适用于存储空间有限的设备。

2. 乘累加指令集(ARM和Thumb-2指令集)乘累加指令集是基于基本指令集的扩展,加入了乘法和累加指令等。

乘累加指令集可以提高乘法和累加运算的效率,适用于需要大量复杂计算的应用。

Thumb-2指令集是Thumb指令集的进一步扩展,兼容Thumb指令集,并增加了32位指令。

Thumb-2指令集使得ARM架构在相同存储空间下能够提供更高的性能。

3. 浮点指令集(VFP和NEON指令集)浮点指令集主要用于进行浮点数运算。

VFP(Vector Floating Point)指令集是ARM架构最早引入的浮点技术,支持单精度和双精度浮点数运算。

NEON指令集是ARM架构后续引入的SIMD(Single Instruction, Multiple Data)指令集,用于提高并行处理能力和多媒体应用性能。

三、常用ARM指令以下是常用的ARM指令及其功能:1.数据处理指令–加法指令:ADD、ADC(带进位的加法指令)–减法指令:SUB、SBC(带借位的减法指令)–乘法指令:MUL、SMULL(有符号乘法指令)、UMULL(无符号乘法指令)–除法指令:SDIV(有符号除法指令)、UDIV(无符号除法指令)–移位指令:LSL(逻辑左移)、LSR(逻辑右移)、ASR(算术右移)、ROR(循环右移)2.控制指令–条件分支指令:B(无条件分支指令)、BEQ(等于零条件分支指令)、BNE(不等于零条件分支指令)等–无条件分支指令:BX(无条件跳转指令,用于实现函数调用)–跳转指令:BL(带链接跳转指令,用于实现函数调用,并将返回地址保存在链接寄存器中)3.访存指令–数据传送指令:LDR(加载指令,用于将数据从内存中加载到寄存器中)、STR(存储指令,用于将数据从寄存器中存储到内存中)–堆栈指令:PUSH(将数据压入堆栈)、POP(将数据从堆栈中弹出)–字节和半字操作指令:LDRB(加载字节指令)、LDRH(加载半字指令)、STRB(存储字节指令)、STRH(存储半字指令)4.特殊指令–中断指令:SWI(软中断指令,用于触发软件中断)–协处理器指令:CDP(协处理器数据处理指令)、MCR、MRC(协处理器寄存器传递指令)四、ARM指令优化技巧为了提高ARM指令执行效率和代码性能,可以采取以下优化技巧:1.使用适当的数据处理指令,避免不必要的指令执行和数据拷贝。

arm的指令集

arm的指令集

ARM(Advanced RISC Machine)是一种基于RISC(Reduced Instruction Set Computing)架构的处理器指令集。

ARM的指令集可以分为不同的版本和产品系列,主要包括以下几个主要的指令集:1. ARMv4:最早的ARM架构,包含基本的32位指令集。

支持基本的数据处理、数据传输、控制流和内存访问指令等。

2. ARMv5:在ARMv4的基础上添加了一些新的特性,如乘法指令、Jazelle Java加速指令等。

3. ARMv6:引入了Thumb指令集,将每个32位指令压缩为16位,以提高代码密度和节省存储空间。

4. ARMv7:包括ARMv7-A、ARMv7-R和ARMv7-M三个不同的配置。

ARMv7-A是面向应用处理器的指令集,增加了一些新的功能和内核特性,如NEON浮点数SIMD指令集、虚拟化扩展等。

ARMv7-R是面向实时处理器的指令集,增加了对实时操作系统和实时任务的支持。

ARMv7-M是面向嵌入式微控制器的指令集,专注于低功耗、低成本和实时性能。

5. ARMv8:引入了AArch64指令集,支持64位处理器架构,同时保持对32位指令的向后兼容。

ARMv8-A广泛用于高性能服务器、移动设备和嵌入式系统。

除了上述主要的指令集版本外,ARM还有一些针对特定应用领域的扩展指令集,如SIMD指令集(NEON)用于增强媒体和信号处理能力,以及加密扩展指令集(Crypto Extensions)用于加速数据加解密操作等。

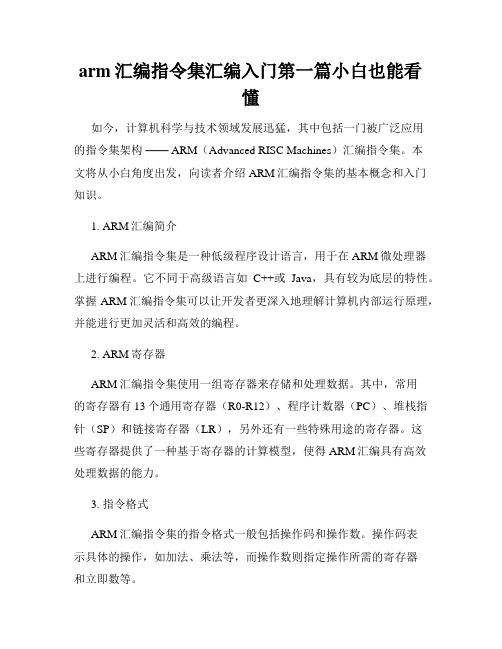

arm汇编指令集汇编入门第一篇小白也能看懂

arm汇编指令集汇编入门第一篇小白也能看懂如今,计算机科学与技术领域发展迅猛,其中包括一门被广泛应用的指令集架构—— ARM(Advanced RISC Machines)汇编指令集。

本文将从小白角度出发,向读者介绍ARM汇编指令集的基本概念和入门知识。

1. ARM汇编简介ARM汇编指令集是一种低级程序设计语言,用于在ARM微处理器上进行编程。

它不同于高级语言如C++或Java,具有较为底层的特性。

掌握ARM汇编指令集可以让开发者更深入地理解计算机内部运行原理,并能进行更加灵活和高效的编程。

2. ARM寄存器ARM汇编指令集使用一组寄存器来存储和处理数据。

其中,常用的寄存器有13个通用寄存器(R0-R12)、程序计数器(PC)、堆栈指针(SP)和链接寄存器(LR),另外还有一些特殊用途的寄存器。

这些寄存器提供了一种基于寄存器的计算模型,使得ARM汇编具有高效处理数据的能力。

3. 指令格式ARM汇编指令集的指令格式一般包括操作码和操作数。

操作码表示具体的操作,如加法、乘法等,而操作数则指定操作所需的寄存器和立即数等。

4. 数据处理指令ARM汇编指令集提供了一系列的数据处理指令,用于对寄存器中的数据进行处理。

这些指令包括基本的算术运算、逻辑运算以及移位操作等,可以实现各种数据处理需求。

5. 分支指令分支指令是ARM汇编指令集中常用的一类指令,用于根据条件进行跳转。

跳转指令可以在程序执行过程中改变程序执行的顺序,实现条件判断和循环等功能。

6. 存储器访问指令存储器访问指令用于在ARM汇编中对内存进行读写操作。

通过这些指令,可以将数据从寄存器中存储到内存中,或者将内存中的数据加载到寄存器中进行处理。

7. 输入输出指令输入输出指令用于实现与外部设备的交互。

例如,通过输入指令可以从键盘或其他输入设备中获取用户输入的数据,而通过输出指令可以将数据输出到显示器或其他输出设备中。

8. 常用例程ARM汇编指令集中有一些常用的例程,可以用于处理常见的编程任务。

ARM名词解释

ARM名词解释ARM是一种基于RISC架构的微处理器架构,它最初由英国的Acorn计算机公司开发,现在已经成为全球最流行的嵌入式处理器架构之一。

ARM处理器被广泛应用于移动设备、智能家居、工业自动化、汽车电子等领域。

ARM是Advanced RISC Machine(高级精简指令集机器)的缩写,其设计理念是通过精简指令集和优化流水线结构来提高处理器性能。

相比于复杂指令集(CISC)架构,RISC架构具有更简单的指令集、更短的指令周期和更高效的流水线结构,因此能够提供更高的性能和更低的功耗。

ARM架构可以分为三个不同级别:应用级(Application-level)、操作系统级(Operating System-level)和体系结构级(Architecture-level)。

其中,应用级主要包括软件开发工具和运行时环境;操作系统级则包括针对不同操作系统的驱动程序和库文件;体系结构级则包括处理器核心、内存管理单元、总线接口等硬件组成部分。

ARM架构还有一些重要概念需要了解:1. ARM Cortex:Cortex是ARM公司推出的一系列处理器核心,包括Cortex-A、Cortex-R和Cortex-M三个系列。

其中,Cortex-A系列是面向高性能应用的处理器核心,适用于智能手机、平板电脑、笔记本电脑等设备;Cortex-R系列是面向实时应用的处理器核心,适用于工业控制、汽车电子等领域;Cortex-M系列是面向低功耗嵌入式应用的处理器核心,适用于智能家居、传感器网络等领域。

2. Thumb指令集:Thumb指令集是ARM公司推出的一种16位指令集,可以在保持与32位指令集兼容的同时提高代码密度和节省存储空间。

Thumb-2指令集则进一步扩展了Thumb指令集的功能,并支持更多高级操作。

3. NEON技术:NEON技术是ARM公司推出的一种SIMD(单指令多数据)加速技术,可以在处理图像、音频等数据密集型应用时提高计算效率。

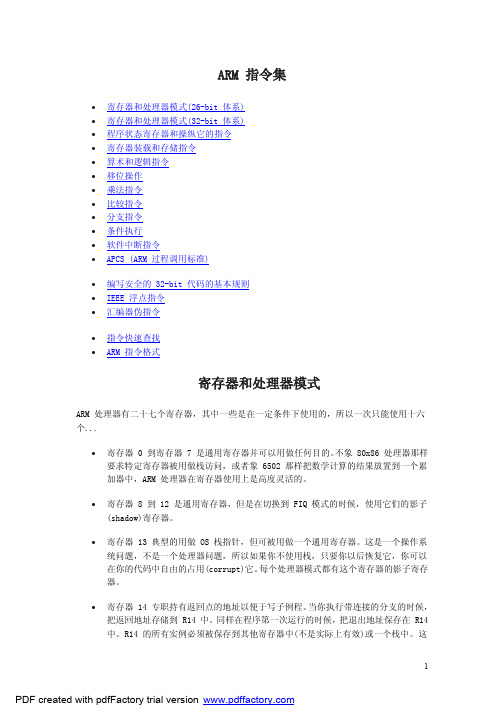

ARM 指令集(中文版)

ARM 指令集•寄存器和处理器模式(26-bit 体系)•寄存器和处理器模式(32-bit 体系)•程序状态寄存器和操纵它的指令•寄存器装载和存储指令•算术和逻辑指令•移位操作•乘法指令•比较指令•分支指令•条件执行•软件中断指令•APCS (ARM 过程调用标准)•编写安全的 32-bit 代码的基本规则•IEEE 浮点指令•汇编器伪指令•指令快速查找•ARM 指令格式寄存器和处理器模式ARM 处理器有二十七个寄存器,其中一些是在一定条件下使用的,所以一次只能使用十六个...•寄存器 0 到寄存器 7 是通用寄存器并可以用做任何目的。

不象 80x86 处理器那样要求特定寄存器被用做栈访问,或者象 6502 那样把数学计算的结果放置到一个累加器中,ARM 处理器在寄存器使用上是高度灵活的。

•寄存器 8 到 12 是通用寄存器,但是在切换到 FIQ 模式的时候,使用它们的影子(shadow)寄存器。

•寄存器 13 典型的用做 OS 栈指针,但可被用做一个通用寄存器。

这是一个操作系统问题,不是一个处理器问题,所以如果你不使用栈,只要你以后恢复它,你可以在你的代码中自由的占用(corrupt)它。

每个处理器模式都有这个寄存器的影子寄存器。

•寄存器 14 专职持有返回点的地址以便于写子例程。

当你执行带连接的分支的时候,把返回地址存储到 R14 中。

同样在程序第一次运行的时候,把退出地址保存在 R14 中。

R14 的所有实例必须被保存到其他寄存器中(不是实际上有效)或一个栈中。

这个寄存器在各个处理器模式下都有影子寄存器。

一旦已经保存了连接地址,这个寄存器就可以用做通用寄存器了。

•寄存器 15 是程序计数器。

它除了持有指示程序当前使用的地址的二十六位数之外,还持有处理器的状态。

为更清晰一些... 提供下列图表:User 模式 SVC 模式 IRQ 模式 FIQ 模式 APCSR0 ------- R0 ------- R0 ------- R0 a1R1 ------- R1 ------- R1 ------- R1 a2R2 ------- R2 ------- R2 ------- R2 a3R3 ------- R3 ------- R3 ------- R3 a4R4 ------- R4 ------- R4 ------- R4 v1R5 ------- R5 ------- R5 ------- R5 v2R6 ------- R6 ------- R6 ------- R6 v3R7 ------- R7 ------- R7 ------- R7 v4R8 ------- R8 ------- R8 R8_fiq v5R9 ------- R9 ------- R9 R9_fiq v6R10 ------ R10 ------ R10 R10_fiq slR11 ------ R11 ------ R11 R11_fiq fpR12 ------ R12 ------ R12 R12_fiq ipR13 R13_svc R13_irq R13_fiq spR14 R14_svc R14_irq R14_fiq lr------------- R15 / PC ------------- pc最右侧的列是 APCS 代码使用的名字,关于 APCS 的详情参见这里。

ARM指令全称及含义

TST

位测试指令

的标志位

TEQ

Test equivalence 相等测试指令

TEQ R1,R2 ;将寄存器 R1 的值与寄存器 R2 的值按位异或,并根据结果 设置 CPSR 的标志位

ADD

Add 加法运算指令

ADD R0,R2,R3,LSL#1 ; R0 = R2 + (R3 << 1)

ADC

数

据

ORR

OR 逻辑或操作指令

ORR R0,R0,#3 ; 该指令设置 R0 的 0、1 位,其余位保持不变。

EOR

Exclusive OR 逻辑异或操作指令

EOR R0,R0,#3 ; 该指令反转 R0 的 0、1 位,其余位保持不变。

Bit clear

BIC R0,R0,#0b1011 ; 该指令清除 R0 中的位 0、1、和 3,其余的位保持

64 位有符号数乘加指令

R3)的高 32 位+ R1

Unsigned multiply long

UMULL R0,R1,R2,R3 ;R0 = (R2 × R3)的低 32 位;R1 =(R2 × R3)

64 位无符号数乘法指令

的高 32 位

Unsigned mul&accumulate lon UMLAL R0,R1,R2,R3 ;R0 =(R2 × R3)的低位+R0;R1 =(R2 × R3)

LR)

Store

STR R0,[R1],#8 ;将 R0 中的字数据写入 R1 为地址的存储器中,并将新地址

字数据存储指令

R1+8 写入 R1

Store byte

STRB R0,[R1,#8] ;将寄存器 R0 中的字节数据写入以 R1+8 为地址的存储

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

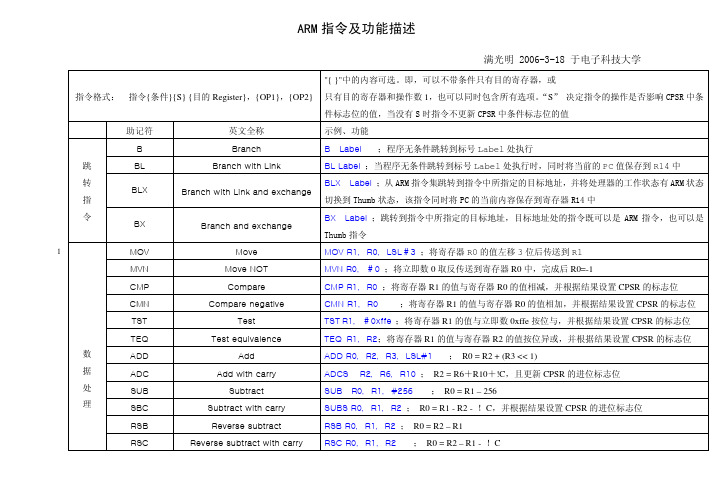

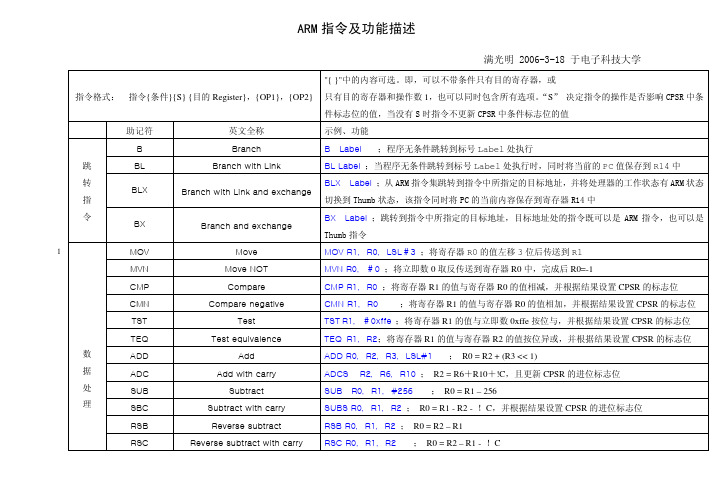

指令格式:指令{条件}{S} {目的Register},{OP1},{OP2} "{ }"中的内容可选。

即,可以不带条件只有目的寄存器,或只有目的寄存器和操作数1,也可以同时包含所有选项。

“S”决定指令的操作是否影响CPSR中条件标志位的值,当没有S时指令不更新CPSR中条件标志位的值助记符英文全称示例、功能跳转指令BBranch跳转指令B Label;程序无条件跳转到标号Label处执行BLBranch with Link带返回的跳转指令BL Label ;当程序无条件跳转到标号Label处执行时,同时将当前的PC值保存到R14中BLXBranch with Link and exchange带返回和状态切换的跳转指令BLX Label;从ARM指令集跳转到指令中所指定的目标地址,并将处理器的工作状态有ARM状态切换到Thumb状态,该指令同时将PC的当前内容保存到寄存器R14中BXBranch and exchange带状态切换的跳转指令BX Label ;跳转到指令中所指定的目标地址,目标地址处的指令既可以是ARM指令,也可以是Thumb指令数据处理MOVMove数据传送MOV R1,R0,LSL#3;将寄存器R0的值左移3位后传送到R1MVNMove NOT数据非传送MVN R0,#0 ;将立即数0取反传送到寄存器R0中,完成后R0=-1CMPCompare比较指令CMP R1,R0;将寄存器R1的值与寄存器R0的值相减,并根据结果设置CPSR的标志位CMNCompare negative负数比较指令CMN R1,R0 ;将寄存器R1的值与寄存器R0的值相加,并根据结果设置CPSR的标志位TSTTest位测试指令TST R1,#0xffe ;将寄存器R1的值与立即数0xffe按位与,并根据结果设置CPSR的标志位TEQTest equivalence相等测试指令TEQ R1,R2;将寄存器R1的值与寄存器R2的值按位异或,并根据结果设置CPSR的标志位ADDAdd加法运算指令ADD R0,R2,R3,LSL#1; R0 = R2 + (R3 << 1)ADCAdd with carry带进位加法ADCS R2,R6,R10; R2 = R6+R10+!C,且更新CPSR的进位标志位SUBSubtract减法运算指令SUB R0,R1,#256; R0 = R1 – 256SBCSubtract with carry带进位减法指令SUBS R0,R1,R2 ; R0 = R1 - R2 - !C,并根据结果设置CPSR的进位标志位RSBReverse subtract逆向减法指令RSB R0,R1,R2 ; R0 = R2 – R1RSCReverse subtract with carry带进位逆向减法指令RSC R0,R1,R2; R0 = R2 – R1 - !CANDAnd逻辑与操作指令AND R0,R0,#3;该指令保持R0的0、1位,其余位清零。

ORROR逻辑或操作指令ORR R0,R0,#3;该指令设置R0的0、1位,其余位保持不变。

EORExclusive OR逻辑异或操作指令EOR R0,R0,#3 ;该指令反转R0的0、1位,其余位保持不变。

BICBit clear位清除指令BIC R0,R0,#0b1011;该指令清除 R0 中的位 0、1、和 3,其余的位保持不变。

CLZ Count left zero 计算操作数最高端0的个数乘加指令MULMultiply32位乘法指令MUL R0,R1,R2 ;R0 = R1 × R2MLAMultiply and accumulate32位乘加指令MLAS R0,R1,R2,R3;R0 = R1 × R2 + R3,同时设置CPSR中的相关条件标志位SMULLSigned multiply long64位有符号数乘法指令SMULL R0,R1,R2,R3;R0 = (R2 × R3)的低32位 R1 = (R2 × R3)的高32位SMLALSigned mul l and accumulate l64位有符号数乘加指令SMLAL R0,R1,R2,R3;R0 =(R2 × R3)的低32位+R0; R1 =(R2 × R3)的高32位+ R1UMULLUnsigned multiply long64位无符号数乘法指令UMULL R0,R1,R2,R3 ;R0 = (R2 × R3)的低32位;R1 =(R2 × R3)的高32位UMLALUnsigned mul&accumulate lon64位无符号数乘法指令UMLAL R0,R1,R2,R3 ;R0 =(R2 × R3)的低位+R0;R1 =(R2 × R3)的高32位+R1PSR 访问MRSMove PSR to register程序状态寄存器到通用寄存器的数据传送指令MRS R0,CPSR;传送CPSR的内容到R0MSRMove register to PSR通用寄存器到程序状态寄存器的数据传送指令MSR CPSR_c ,R0;传送R0的内容到SPSR,但仅仅修改CPSR中的控制位域加载/ 存储指令LDRLoad word字数据加载指令LDR R0,[R1,R2]!;将存储器地址为R1+R2的字数据读入R0,并将新地址R1+R2写入R1。

LDRBLoad byte字节数据加载指令LDRB R0,[R1,#8] ;将存储器地址为R1+8的字节数据读入R0,并将R0的高24位清零LDRHLoad half word半字数据加载指令LDRH R0,[R1];将存储器地址为R1的半字数据读入寄存器R0,并将R0的高16位清零LDMLoad multiple批量数据加载指令LDMFD R13!,{R0,R4-R12,PC};将堆栈内容恢复到寄存器(R0,R4到R12,LR)STRStore字数据存储指令STR R0,[R1],#8 ;将R0中的字数据写入R1为地址的存储器中,并将新地址R1+8写入R1STRBStore byte字节数据加载存储指令STRB R0,[R1,#8];将寄存器R0中的字节数据写入以R1+8为地址的存储器中STRHStore half word半字数据存储指令STRH R0,[R1,#8];将寄存器R0中的半字数据写入以R1+8为地址的存储器中STMStore multiple批量数据存储指令STMFD R13!,{R0,R4-R12,LR};将寄存器列表中的寄存器(R0,R4到R12,LR)存入堆栈数据交换SWPSwap word字数据交换指令SWP R0,R1,[R2];R2所指的字数据传送到R0,同时R1的数据传送到R2所指的单元SWPBSwap byte字节数据交换指令SWPB R0,R1,[R2] ;R2所指的字节数据传送到R0,R0高24位清零,同时R1低8位送R2所指单元。

移位指令LSLLogic shift left逻辑左移操作MOV R0, R1, LSL#2(ASL#2);将R1中的内容左移两位后传送到R0中,低位用0填充ASLArithmetic shift left算术左移操作LSRLogic shift right逻辑右移操作MOV R0, R1, LSR#2 ;将R1中的内容右移两位后传送到R0中,左端用零来填充ASRArithmetic shift right算术右移操作MOV R0, R1, ASR#2 ;将R1中的内容右移两位后传送到R0中,左端用第31位的值来填充RORRotate right循环右移操作MOV R0, R1, ROR#2;将R1中的内容循环右移两位后传送到R0中RRXRotate right extended带拓展的循环右移操作左端用进位标志位C来填充协处理器CDP Data operations 协处理器数操作指令LDC Load 协处理器数据加载指令STC Store 协处理器数据存储指令MCR Move to coproc fr ARM reg 处理器寄存器到协处理器寄存器的数据传送指令MRC M to ARM reg fr coprocessor 协处理器寄存器到处理器寄存器的数据传送指令PSRfield F (Flags field mask byte) S (Stats field mask byte)X (Extension field maskbyte)C (control field mask byte)CPSR 313292827262524232221219181716 151413121119 8 7 6 5 4 3 2 1 0意义N Z C V Q DNZ (RAZ) 系统扩展用I F T M4 M3 M2 M1 M0CPSR 各位详细意义N 当前指令运算结果为负时,N = 1; 结果为非负时,N = 0 Z 运算结果为0,Z=1;否则Z=0C 上溢出、进位C=1;下溢出、借位C=0V 加减法V=1表示符号位溢出I I=1时,禁止IRQ中断F F=1时,禁止FIQ中断T T=0,ARM指令;T=1,Thumb指令M[4:0]0b10000 User0b10001 FIQ0b10010 IRQ0b10011 Supervisor0b10111 Abort0b11011 Undefined0b11111 System指令格式313292827262524232221219181716151413121119 8 7 6 5 4 3 2 1 0Cond Opcode S Rn Rd Shift_operandopcode 指令操作符编码S 决定指令的操作是否影响CPSR的值Rd 目标寄存器编码Rn 包含第一个操作数的寄存器编码Shift_oprand表示第二个操作数Cond 指令执行的条件编码,详细如下所示条件域EQ Z=1 EqualNE Z=0 Not equal, or unorderedCS/HS C=1 Carry set / Unsigned higher or sameGreat than or equal, orunorderedCC/LO C=0 Carry clear / Unsigned lower Less thanMI N=1 Negative Less thanPL N=0 Positive or zeroGreater than or equal , orunorderedVS V=1 Overflow UnorderedVC V=0 No overflow Not unorderedHI C=1且Z=0 Unsigned higher Greater than, or unordered LS C=0或Z=1 Unsigned lower or same Less than or equalGE N=1且V=1 或N=0且V=0 Signed greater than or equal Greater than or equalLT N=1且V=0 或N=0且V=1 Signed less than Less than , or unorderedGT Z=0或N=V Signed greater than Great thanLE Z=1或N!=V Signed less than or equal Less than or equal , or unorderedAL Always (normally omitted)并行指令前缀S Signed arithmetic modulo 28 or 216 ,sets CPSR GE bitQ Signed saturating arithmeticSH Signed arithmetic, halving resultsU Unsigned arithmetic modulo 28 or 216 ,sets CPSR GE bit UQ Unsigned saturating arithmeticUH Unsigned arithmetic ,halving results批量传输地址模式Block load / store Stack pop / pushIA Increment after FD Full descending IB Increment before ED Empty descending DA Decrement after FA Full ascending DB Decrement before EA Empty ascendingARM 指令寻址方式立即寻址ADD R0,R0,#0x3f R0←R0+0x3f寄存器寻址ADD R0,R1,R2 R0←R1+R2间接寻址ADD R0,R1,[R2] R0←R1+[R2]变址寻址LDR R0,[R1,#4] R0←[R1+4]LDR R0,[R1,#4]!R0←[R1+4]、R1←R1+4LDR R0,[R1] ,#4 R0←[R1]、R1←R1+4LDR R0,[R1,R2] R0←[R1+R2]多寄存器寻址LDMIA R0,{R1,R2,R3,R4} R1←[R0];R2←[R0+4];R3←[R0+8];R4←[R0+12]伪指令及伪操作符号定义GBLA / LCLA 定义一个全局 / 局部的数字变量,并初始化为0GBLL / LCLL 定义一个全局 / 局部的逻辑变量,并初始化为F(假)GBLS / LCLS 定义一个全局 / 局部的字符串变量,并初始化为空SETA / SETL / SETS 给一个数学 / 逻辑 / 字符串变量赋值RLIST对一个通用寄存器列表定义名称,访问次序为根据寄存器的编号由低到高,与排列次序无关数据定义DCB(=)/ DCW(DCWU)分配一片连续的字节 / 半字存储单元并用指定的数据初始化后缀U表示不要求对齐DCFS(DCFSU)/DCFD(DCFDU)分配一片连续的(单 / 双精度的浮点数)字存储单元并用指定的数据初始化DCQ(DCQU)/ DCD(DCDU)用于分配一片以双字 / 字为单位的连续的存储单元并用指定的数据初始化DCDO 分配字内存但愿,初始化为标号基于静态基址寄存器R9的偏移量DCI 和DCD类似,不同处在于DCI内存中的数据被标识为指令SPACE(%)DataSpace SPACE 100 ;分配连续100字节的存储单元并初始化为0MAP(^)MAP 0x100,R0 ;定义结构化内存表首地址的值为0x100+R0FIELD(#) A FIELD 16 ;定义A的长度为16字节控制伪指令IF、ELSE、ENDIFIF 逻辑表达式指令序列1ELSE指令序列2ENDIFIF、ELSE、ENDIF伪指令能根据条件的成立与否决定是否执行某个指令序列。