基于FPGA的verilog万年历程序

【优秀WORD论文】基于FPGA的全功能万年历电子钟的设计

基于FPGA的全功能万年历电子钟的设计提要本文主要介绍了基于FPGA的万年历电子钟的设计方案,从而介绍了可编程逻辑器件的发展及应用。

基于FPGA的电子钟的设计与实现介绍了基于FPGA芯片的系统设计,并对系统的软硬件构成、FPGA内部逻辑设计工作原理等进行了详细说明。

论文第一部分对FPGA进行概述,讲述了可编程逻辑器件的发展与应用及论文题目的意义、目的和内容编排;第二部分:叙述了系统设计方案,介绍了FPGA应用的特点和电子钟的方案概述及实现语言和调试平台MAX+plusⅡ开发工具;第三部分:叙述了基于FPGA的电子钟系统的设计的硬件设计和软件设计;第四部分:对系统实现的外围电路进行概述。

第五部分:再次说明本设计的系统方案和得到的结论。

目录第一章序论 (1)1.1研究目的和意义: (1)1.2可编程逻辑器件的发展与应用: (1)1.2.1可编程逻辑单元CLB (3)1.2.2输入/输出模块IOB (3)1.2.3可编程内部连线PI (4)1.2.4 FPGA芯片的特点 (4)1.3FPGA国内外的发展状况及应用 (5)1.4本课题所能实现的功能: (8)第二章总体方案的设计 (9)2.1万年历电子钟的设计原理: (9)2.2FPGA的设计方法 (11)2.2.1 FPGA的器件设计流程 (11)2.2.2 MAX+plusⅡ开发工具 (13)2.2.3 VHDL语言 (17)2.3系统设计方案 (18)第三章系统的硬件设计与实现 (19)3.1功能模块设计 (19)3.2系统功能实现 (21)3.2.1底层元件设计 (22)3.2.2顶层元件设计 (32)3.3芯片的选择 (41)第四章设计应用电路 (45)4.1整体电路 (45)4.2电源电路 (46)4.3键盘部分 (49)4.4主动配置电路 (53)第五章总结 (61)5.1概述: (61)5.2设计方案: (62)参考文献 (64)致谢 (67)摘要 (I)ABSTRACT (II)第一章序论1.1研究目的和意义:通过对FPGA的了解,我们要应用FPGA来设计全功能万年历的设计,主要实现电子钟的所有功能,万年历是一种应用非常广泛的日常计时工具,具有时分秒计时功能,还有日历、年历功能,涉及计数、显示、参数输入技术,能够实时显示年、月、日和时间,并具有校准和闹铃等功能。

基于FPGA的数字日历设计

基于FPGA的数字日历设计

基于FPGA设计数字日历可以实现以软件方式设计硬件的目的,无需购买专用数字芯片,从而克服了传统利用多片数字集成电路设计数字日历存在

焊接麻烦、调试繁琐、成本较高等问题。

而且,基于FPGA的数字日历与传统系统相比,在设计灵活、开发速度、降低成本、计时精度、功能实现上都得到

大幅度提升,能够更好地满足人们日常生活的需要。

本文介绍如何利用VHDL硬件描述语言设计一个具有年、月、日、星期、时、分、秒计时显示功能,时间调整功能和整点报时功能的数字日历。

在QuartusⅡ开发环境下,采用自顶向下的设计方法,建立各个基本模块,再构建成一个完整的基于FPGA设计的数字日历的顶层模块,然后对其进行编译、仿真、引脚锁定,最终下载到可编程逻辑器件上进行结果验证。

1数字日历整体设计方案

基于FPGA的数字日历设计分为硬件设计和软件设计两大部分。

其原理框

2数字日历的工作原理

首先由外部振荡器产生稳定的高频脉冲信号,作为数字日历的时间基准,然后经过分频器输出标准秒脉冲,输入到FPGA的CLOCK端,实现计数。

当秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照24进1规律计数。

计满后各计数器清零,重新计数。

日部分由于

日有28天、29天、30天、31天4种情况,故日由年和月共同判断其天数,日计满后向月进位,月满后向年进位。

计数器的输出分别经译码器送数码管显示。

计时出现误差时,可以用校时电路校时、校分、校秒和校年、校月、校日。

基于FPGA的万年历程序设计

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clock isport(rst:in std_logic;clk:in std_logic;clr:in std_logic;display_mode: in std_logic;inc:in std_logic;mode:in std_logic;seg8:out std_logic_vector(7 downto 0);scan:out std_logic_vector(7 downto 0);led:out std_logic_vector(3 downto 0) );end;architecture one of clock is--signal state:std_logic_vector(2 downto 0);--signal dis_mode:std_logic_vector(1 downto 0);signal state:integer range 0 to 7;signal dis_mode:integer range 0 to 3;--signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qm1,qm2,qd1,qd2:std_logic_vector(3 downto 0);signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qmonl,qmonh,qdl,qdh:integer range 0 to 15; signal data:integer range 0 to 15 ;signal cnt:integer range 0 to 7;signal clk1khz,clk1hz,clk2hz,clk5ms:std_logic;--signal blink:std_logic_vector(2 downto 0);--signal inc_reg:std_logic;signal sec,min:integer range 0 to 59;signal hour:integer range 0 to 23;signal year:integer range 1 to 9999;signal month:integer range 1 to 12;signal day,day_limit:integer range 1 to 31;beginprocess(clk)variable count:integer range 0 to 30000;beginif clk'event and clk='1' thenif count=25000 then clk1khz<=not clk1khz;count:=0;else count:=count+1;end if;end if;end process;-------------------------------------------------------process (clk)variable cnte:integer range 0 to 30000000;beginif clk'event and clk ='1' thenif cnte=25000000 then clk1hz<=not clk1hz; cnte:=0;else cnte:=cnte+1;end if ;end if ;end process ;-----------------------------------------------------process (clk)variable cnt2:integer range 0 to 25000000;beginif clk'event and clk='1' thenif cnt2=12500000 then clk2hz<=clk2hz;cnt2:=0;else cnt2:=cnt2+1;end if ;end if ;end process;-----------------------------------------------------process(clk)variable cnnt:integer range 0 to 600000;beginif clk'event and clk='1' thenif cnnt=500000 then clk5ms<=clk5ms;cnnt:=0;else cnnt:=cnnt+1;end if ;end if ;end process;-----------------------------------------------------------------------------------------process(display_mode , clk1hz)beginif display_mode'event and display_mode='0' then dis_mode<=dis_mode+1;if dis_mode=1 thendis_mode<=0;end if;end if;end process;-------------------------------------------process(clk)beginyear<=year;month<= month;day<=day;hour<=hour;min<=min;sec<=sec;end process;-----------------------------------------process(mode , clr,clk1hz)beginif clr='0' thenstate<=0;elsif mode'event and mode='0' thenstate<=state+1;if state=6 thenstate<=0;end if;end if ;end process;----------------------------------------------------------------------------------- process(clk1hz,state,dis_mode,inc,clr,hour,sec,min,rst,year,month,day) beginif rst='0' thenyear<=2000;month<=2;day<=25;hour<=0;min<=0;sec<=0;--state<=0;--dis_mode<=0;elsif clr='0' thenhour<=23;min<=59;sec<=55;year<=4164;month<=1;day<=25;elsif clk1hz'event and clk1hz='1' thencase state iswhen 0 => led<="0000";if((month=1)or(month=3)or(month=5)or(month=7)or(month=8)or(month=10)or(month=12)) thenday_limit<=31;end if;if month=2 then----if((year%4==0&&year%100!=0)||(year%400==0))if ((((year rem 4)=0) and ((year rem 100)/=0)) or ((year rem 400=0))) thenday_limit<=29;elseday_limit<=28;end if;end if;if((month=4)or(month=6)or(month=9)or(month=11)) thenday_limit<=30;end if;sec<=sec+1;if sec=59 thensec<=0;min<=min+1;if min=59 thenmin<=0;hour<=hour+1;if hour =23 thenhour<=0;day<=day+1;if day=day_limit thenday<=1;month<=month+1;if month=12 thenmonth<=1;year<=year+1;if year=9999 thenyear<=1;end if;end if;end if;end if;end if;end if;--if sec=59 then sec<=0;--if min=59 then min<=0;--if hour=23 then hour<=0;--else--hour<=hour+1;--end if;--else--min<=min+1;--end if;--else--sec<=sec+1;--end if;when 1=> led<="0001";if inc='0' thenif hour=23 thenhour<=0;else hour<=hour+1;end if;end if;when 2=>led<="0010" ;if inc='0' thenif min=59 thenmin<=0;elsemin<=min+1;end if;end if;when 3=>led<="0011" ;if inc='0' thenif sec=59 thensec<=0;elsesec<=sec+1;end if;end if;when 4 =>led<="0100";if inc='0' thenif year=9999 thenyear<=1;elseyear<=year+1;end if;end if;when 5=> led <="0101";if inc='0' thenif month=12 thenmonth<=1;elsemonth<=month+1;end if;end if;when 6 =>led <="0110";if inc='0' thenif day=day_limit thenday<=1;elseday<=day+1;end if;end if;when others =>null;end case;end if;--end if;end process;---------------------------------------------------------------------- process(sec)begincase sec iswhen 0|10|20|30|40|50 => qsl<=0;when 1|11|21|31|41|51 => qsl<=1;when 2|12|22|32|42|52 => qsl<=2;when 3|13|23|33|43|53 => qsl<=3;when 4|14|24|34|44|54 => qsl<=4;when 5|15|25|35|45|55 => qsl<=5;when 6|16|26|36|46|56 => qsl<=6;when 7|17|27|37|47|57 => qsl<=7;when 8|18|28|38|48|58 => qsl<=8;when 9|19|29|39|49|59 => qsl<=9;when others =>null;end case;case sec iswhen 0|1|2|3|4|5|6|7|8|9 => qsh<=0;when 10|11|12|13|14|15|16|17|18|19 => qsh<=1;when 20|21|22|23|24|25|26|27|28|29 => qsh<=2;when 30|31|32|33|34|35|36|37|38|39 => qsh<=3;when 40|41|42|43|44|45|46|47|48|49 => qsh<=4;when 50|51|52|53|54|55|56|57|58|59 => qsh<=5;when others =>null;end case;end process;-------------------------------------------------------------------- process(min)begincase min iswhen 0|10|20|30|40|50 => qml<=0;when 1|11|21|31|41|51 => qml<=1;when 2|12|22|32|42|52 => qml<=2;when 3|13|23|33|43|53 => qml<=3;when 4|14|24|34|44|54 => qml<=4;when 5|15|25|35|45|55 => qml<=5;when 6|16|26|36|46|56 => qml<=6;when 7|17|27|37|47|57 => qml<=7;when 8|18|28|38|48|58 => qml<=8;when 9|19|29|39|49|59 => qml<=9;when others =>null;end case;case min iswhen 0|1|2|3|4|5|6|7|8|9 => qmh<=0;when 10|11|12|13|14|15|16|17|18|19 => qmh<=1;when 20|21|22|23|24|25|26|27|28|29 => qmh<=2;when 30|31|32|33|34|35|36|37|38|39 => qmh<=3;when 40|41|42|43|44|45|46|47|48|49 => qmh<=4;when 50|51|52|53|54|55|56|57|58|59 => qmh<=5;when others =>null;end case;end process;----------------------------------------------------------------------- process(hour)begincase hour iswhen 0|10|20 => qhl<=0;when 1|11|21 => qhl<=1;when 2|12|22 => qhl<=2;when 3|13|23 => qhl<=3;when 4|14 => qhl<=4;when 5|15 => qhl<=5;when 6|16 => qhl<=6;when 7|17 => qhl<=7;when 8|18 => qhl<=8;when 9|19 => qhl<=9;when others =>null;end case;case hour iswhen 0|1|2|3|4|5|6|7|8|9 => qhh<=0;when 10|11|12|13|14|15|16|17|18|19 => qhh<=1;when 20|21|22|23 => qhh<=2;when others => null;end case;end process;---------------------------------------------------------------process(year)beginqy1<=year/1000;qy2<=(year rem 1000)/100;qy3<=((year rem 1000)rem 100)/10;qy4<=((year rem 1000)rem 100) rem 10;--qy1<=year/1000;--qy2<=(year rem 1000)/100;--qy3<=((year-(year/1000)*1000)-((year-(year/1000)*1000)/100)*100)/10; --qy4<=((year rem 1000)rem 100)rem 10;end process;----------------------------------------------------------------process(month)beginqmonh<=month/10;qmonl<=month rem 10;end process;-----------------------------------------------------------------process(day)beginqdh<=day/10;qdl<=day rem 10;end process;----------------------------------------------------------------process(clk1khz)beginif clk1khz'event and clk1khz='1' thenif cnt=7 thencnt<=0;else cnt<=cnt+1;end if;end if;end process;----------------------------------------------------------process (cnt,qhh,qhl,qmh,qml,qsh,qsl,dis_mode)begincase dis_mode iswhen 0 => case cnt iswhen 0 => data<=qsl; scan<="11111110";when 1 => data<=qsh; scan<="11111101";when 2 => data<=15 ; scan<="11111111";when 3 => data<=qml; scan<="11110111";when 4 => data<=qmh; scan<="11101111";when 5 => data<=15; scan<="11111111";when 6 => data<=qhl; scan<="10111111";when 7 => data<=qhh; scan<="01111111";when others => null;end case;when 1=> case cnt iswhen 0 => data<=qdl; scan<="11111110";when 1 => data<=qdh; scan<="11111101";when 2 => data<=qmonl ; scan<="11111011";when 3 => data<=qmonh; scan<="11110111";when 4 => data<=qy4; scan<="11101111";when 5 => data<=qy3; scan<="11011111";when 6 => data<=qy2; scan<="10111111";when 7 => data<=qy1; scan<="01111111";when others =>null;end case;when others => null;end case;end process;----------------------------------------------------------------------------------process(data)begincase data iswhen 0 =>seg8<="11000000";when 1 =>seg8<="11111001";when 2 =>seg8<="10100100";when 3 =>seg8<="10110000";when 4 =>seg8<="10011001";when 5 =>seg8<="10010010";when 6 =>seg8<="10000010";when 7 =>seg8<="11111000";when 8 =>seg8<="10000000";when 9 =>seg8<="10010000";when others =>seg8<="11111111";end case ;end process;end;。

基于fpga的多功能万年历

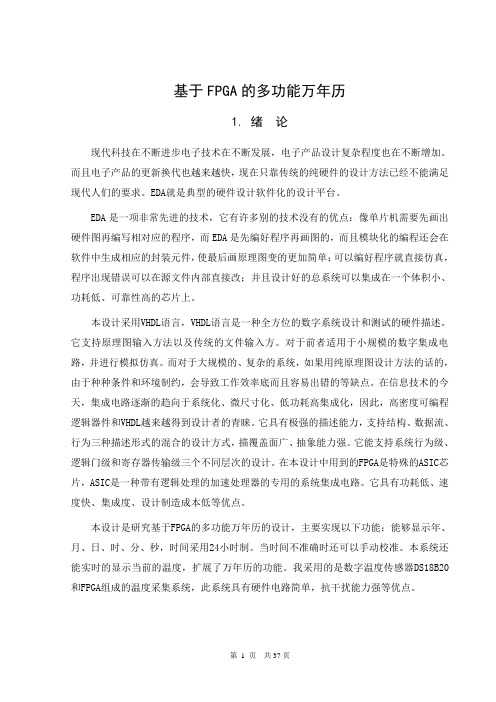

基于FPGA的多功能万年历1. 绪论现代科技在不断进步电子技术在不断发展,电子产品设计复杂程度也在不断增加。

而且电子产品的更新换代也越来越快,现在只靠传统的纯硬件的设计方法已经不能满足现代人们的要求。

EDA就是典型的硬件设计软件化的设计平台。

EDA是一项非常先进的技术,它有许多别的技术没有的优点:像单片机需要先画出硬件图再编写相对应的程序,而EDA是先编好程序再画图的,而且模块化的编程还会在软件中生成相应的封装元件,使最后画原理图变的更加简单;可以编好程序就直接仿真,程序出现错误可以在源文件内部直接改;并且设计好的总系统可以集成在一个体积小、功耗低、可靠性高的芯片上。

本设计采用VHDL语言,VHDL语言是一种全方位的数字系统设计和测试的硬件描述。

它支持原理图输入方法以及传统的文件输入方。

对于前者适用于小规模的数字集成电路,并进行模拟仿真。

而对于大规模的、复杂的系统,如果用纯原理图设计方法的话的,由于种种条件和环境制约,会导致工作效率底而且容易出错的等缺点。

在信息技术的今天,集成电路逐渐的趋向于系统化、微尺寸化、低功耗高集成化,因此,高密度可编程逻辑器件和VHDL越来越得到设计者的青睐。

它具有极强的描述能力,支持结构、数据流、行为三种描述形式的混合的设计方式,描覆盖面广、抽象能力强。

它能支持系统行为级、逻辑门级和寄存器传输级三个不同层次的设计。

在本设计中用到的FPGA是特殊的ASIC芯片,ASIC是一种带有逻辑处理的加速处理器的专用的系统集成电路。

它具有功耗低、速度快、集成度、设计制造成本低等优点。

本设计是研究基于FPGA的多功能万年历的设计,主要实现以下功能:能够显示年、月、日、时、分、秒,时间采用24小时制。

当时间不准确时还可以手动校准。

本系统还能实时的显示当前的温度,扩展了万年历的功能。

我采用的是数字温度传感器DS18B20和FPGA组成的温度采集系统,此系统具有硬件电路简单,抗干扰能力强等优点。

万年历的设计与实现

学校代码 ***** 学号 ******** 分类号 TP 密级公开本科毕业论文(设计)学院、系鄂尔多斯学院电子信息工程系专业名称自动化年级 2011 级学生姓名张文博指导教师王俊林2013年 6月 8 日万年历的设计与实现摘要本设计为一个多功能的万年历,具有年、月、日、时、分、秒计数显示功能,以24小时循环计数,具有校对功能。

本设计采用EDA 技术,以硬件描述语言verilog HDL和VHDL为系统逻辑描述手段设计文件,在Quartus II工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于KH-310开发工具的万年历。

系统主芯片采用EP1C12Q240C8,由主程序和BCD模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,本系统通过控制能够完成年、月、日和时、分、秒的分别显示,由按键输入进行数字钟的校时、切换、扫描功能。

关键字:VHDL Verilog HDL EDA 万年历目录1绪论 (1)1.1选题背景 (1)1.2课题相关技术的发展 (1)1.3课题研究的必要性 (2)1.4课题研究的内容 (3)2 EDA技术 (4)2.1 EDA概述 (4)2.2什么是EDA (4)2.3 EDA的特点 (5)3 FPGA简介 (7)3.1 FPGA概述 (7)3.2 FPGA开发编程原理 (7)3.3FPGA基本结构 (8)3.4 FPGA系统设计流程 (10)4万年历设计方案 (14)4.1万年历的原理 (14)4.2 实验程序 (14)4.3 实验连接 (34)4.4 实验仿真与实现 (36)5实验结论与研究展望 (38)5.1实验结论 (38)5.2研究展望 (38)致谢 (39)参考文献 (40)内蒙古大学本科实训论文(设计)1绪论1.1选题背景20世纪末,数字电子技术飞速发展,有力的推动了社会生产力的发展和社会信息化的提高。

在其推动下,数字技术的应用已经渗透到人类生活的各个方面。

VHDL设计FPGA数字系统:电子万年历.

大连海事大学毕业论文Array二○一四年六月VHDL设计FPGA数字系统:电子万年历专业班级: 电子信息工程10-2班姓名: 牛舒雅指导老师: 严飞信息科学技术学院摘要随着EDA(电子设计自动化)技术的发展和应用领域的扩大,EDA技术在电子信息、通信、自动化控制及计算机应用领域的重要性日益突出。

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭路灯等。

所有这些,都是以钟表数字化为基础的。

因此,研究基于FPGA的电子万年历及扩大其应用,有非常现实的意义。

EDA的关键技术之一是用形式化方法来描述数字系统的硬件电路、即用所谓的硬件描述语言来描述硬件电路。

本设计是用VHDL语言编程实现基于FPGA的电子万年历。

在设计中,首先介绍了万年历的设计思路,确定各功能模块,而后在Quartus II开发环境中用VHDL语言对各模块进行编程,编译成功后完成仿真,并逐一调试程序使各模块达到设计目的。

然后,将各模块生成的元器件连接起来,形成顶层原理图文件,进行系统仿真。

最后,对顶层原理图进行引脚设定,并下载到试验箱验证,证明系统的可行性。

关键字:EDA;VHDL ;万年历;Quartus IIABSTRACTWith the development of EDA (electronic design automation) technology and expansion of application fields ,the importance of EDA technology in electronic information, communication, auto control, and computer applications is becoming increasingly prominent. EDA technology is the core of the modern electronic design techniques, which rely on powerful computers . In EDA tools software platform, computer automatically completes logic simplification,logical partitions, logic synthesis , logic optimization ,logical simulation and other functions until the electronic circuit system achieves the stated performance. However, the realization of these function bases on the description of the system using the hardware description language HDL (Hardware Description language) . One of the key technologies of the EDA is to use formal methods to describe digital systems hardware circuit, which uses the so-called hardware description language to describe the hardware circuit.The design is the calendar based on VHDL language. Firstly, in which ,I introduce ideas about designing the calendar. In addition, I compile and simulate the program of different modules in the Quartus II development environment and debug one by one to make different modules meet objectives of the design. Secondly, I take advantage of all components,which is created according to program to generate top-level file . Finally, I make pin settings and download to the test chamber to prove the feasibility of the system.Key words: EDA;VHDL ;calendar;Quartus II目录第1章绪论 (1)1.1钟的起源 (1)1.2钟的现状以及发展 (1)1.3电子万年历的简介 (1)1.4VHDL设计FPGA数字系统:电子万年历的设计要求 (2)1.5 本章小结 (2)第2章开发技术基础 (3)2.1 EDA技术简介 (3)2.1.1 EDA技术基本概述 (3)2.1.2EDA技术发展与发展方向 (3)2.2FPGA基本介绍 (4)2.2.1FPGA简介 (4)2.2.1FPGA组成 (5)2.3VHDL语言概述 (5)2.3.1VHDL语言特点 (6)2.3.2VHDL语言结构 (7)2.4Quartus II软件介绍 (7)2.5ZY11EDA13BE实验系统介绍 (8)2.5.1 ZY11EDA13BE实验系统的特点 (8)2.5.2ZY11EDA13BE实验系统主板组成 (8)2.6本章小结 (9)第3章电子万年历的设计 (10)3.1设计思想 (10)3.2 设计框图 (11)3.3 设计流程图 (12)3.4 本章小结 (15)第4章电子万年历的设计、仿真与展示 (16)4.1 模块分析 (16)4.1.1 秒与分的计数器模块 (16)4.1.3 日计数器模块 (18)4.1.4月计数器模块 (21)4.1.5年低位计数器模块 (22)4.1.6年高位计数器模块 (23)4.1.7校准模块 (24)4.1.8 显示以及显示内容切换模块 (26)4.2顶层原理图 (27)4.3 管脚锁定 (29)4.4电子万年历的展示 (29)4.5本章小结 (30)第5章总结 (31)参考文献 (32)致谢 (33)第1章绪论1.1钟的起源中国古代很早就用日晷计时。

基于FPGA的万年历程序

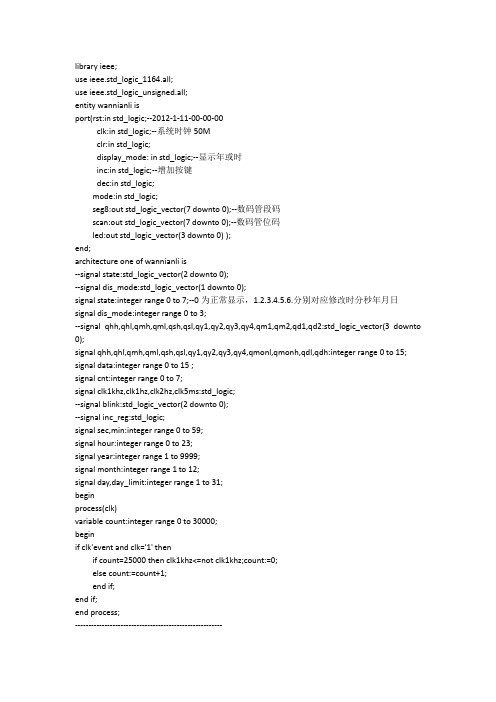

use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity wannianli isport(rst:in std_logic;--2012-1-11-00-00-00clk:in std_logic;--系统时钟50Mclr:in std_logic;display_mode: in std_logic;--显示年或时inc:in std_logic;--增加按键dec:in std_logic;mode:in std_logic;seg8:out std_logic_vector(7 downto 0);--数码管段码scan:out std_logic_vector(7 downto 0);--数码管位码led:out std_logic_vector(3 downto 0) );end;architecture one of wannianli is--signal state:std_logic_vector(2 downto 0);--signal dis_mode:std_logic_vector(1 downto 0);signal state:integer range 0 to 7;--0为正常显示,1.2.3.4.5.6.分别对应修改时分秒年月日signal dis_mode:integer range 0 to 3;--signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qm1,qm2,qd1,qd2:std_logic_vector(3 downto 0);signal qhh,qhl,qmh,qml,qsh,qsl,qy1,qy2,qy3,qy4,qmonl,qmonh,qdl,qdh:integer range 0 to 15; signal data:integer range 0 to 15 ;signal cnt:integer range 0 to 7;signal clk1khz,clk1hz,clk2hz,clk5ms:std_logic;--signal blink:std_logic_vector(2 downto 0);--signal inc_reg:std_logic;signal sec,min:integer range 0 to 59;signal hour:integer range 0 to 23;signal year:integer range 1 to 9999;signal month:integer range 1 to 12;signal day,day_limit:integer range 1 to 31;beginprocess(clk)variable count:integer range 0 to 30000;beginif clk'event and clk='1' thenif count=25000 then clk1khz<=not clk1khz;count:=0;else count:=count+1;end if;end if;end process;-------------------------------------------------------variable cnte:integer range 0 to 30000000;beginif clk'event and clk ='1' thenif cnte=25000000 then clk1hz<=not clk1hz; cnte:=0;else cnte:=cnte+1;end if ;end if ;end process ;-----------------------------------------------------process (clk)variable cnt2:integer range 0 to 25000000;beginif clk'event and clk='1' thenif cnt2=12500000 then clk2hz<=clk2hz;cnt2:=0;else cnt2:=cnt2+1;end if ;end if ;end process;-----------------------------------------------------process(clk)variable cnnt:integer range 0 to 600000;beginif clk'event and clk='1' thenif cnnt=500000 then clk5ms<=clk5ms;cnnt:=0;else cnnt:=cnnt+1;end if ;end if ;end process;-----------------------------------------------------------------------------------------process(display_mode , clk1hz)beginif display_mode'event and display_mode='0' then dis_mode<=dis_mode+1;if dis_mode=1 thendis_mode<=0;end if;end if;end process;-------------------------------------------beginyear<=year;month<= month;day<=day;hour<=hour;min<=min;sec<=sec;end process;-----------------------------------------process(mode , clr,clk1hz)beginif clr='0' thenstate<=0;elsif mode'event and mode='0' thenstate<=state+1;if state=6 thenstate<=0;end if;end if ;end process;-----------------------------------------------------------------------------------process(clk1hz,state,dis_mode,inc,dec,clr,hour,sec,min,rst,year,month,day) beginif rst='0' thenyear<=2012;month<=1;day<=11;hour<=0;min<=0;sec<=0;--state<=0;--dis_mode<=0;elsif clr='0' thenhour<=23;min<=59;sec<=55;year<=2013;month<=1;day<=12;elsif clk1hz'event and clk1hz='1' thencase state iswhen 0 =>led<="0000";if((month=1)or(month=3)or(month=5)or(month=7)or(month=8)or(month=10)or(month=12)) thenday_limit<=31;end if;if month=2 then----if((year%4==0&&year%100!=0)||(year%400==0))if ((((year rem 4)=0) and ((year rem 100)/=0)) or ((year rem 400=0))) thenday_limit<=29;elseday_limit<=28;end if;end if;if((month=4)or(month=6)or(month=9)or(month=11)) thenday_limit<=30;end if;sec<=sec+1;if sec=59 thensec<=0;min<=min+1;if min=59 thenmin<=0;hour<=hour+1;if hour =23 thenhour<=0;day<=day+1;if day=day_limit thenday<=1;month<=month+1;if month=12 thenmonth<=1;year<=year+1;if year=9999 thenyear<=1;end if;end if;end if;end if;end if;end if;--if sec=59 then sec<=0;--if min=59 then min<=0;--if hour=23 then hour<=0;--else--hour<=hour+1;--end if;--else--min<=min+1;--end if;--else--sec<=sec+1;--end if;when 1=> led<="0001";if inc='0' thenif hour=23 thenhour<=0;else hour<=hour+1;end if;elsif dec='0' thenif hour=0 thenhour<=23;else hour<=hour-1;end if;end if;when 2=>led<="0010" ;if inc='0' thenif min=59 thenmin<=0;elsemin<=min+1;end if;elsif dec='0' thenif min=0 thenmin<=59;elsemin<=min-1;end if;end if;when 3=>led<="0011" ;if inc='0' thenif sec=59 thensec<=0;elsesec<=sec+1;end if;elsif dec='0' thenif sec=0 thensec<=59;elsesec<=sec-1;end if;end if;when 4 =>led<="0100";if inc='0' thenif year=9999 thenyear<=1;elseyear<=year+1;end if;elsif dec='0' thenif year=1990 thenyear<=2020;elseyear<=year-1;end if;end if;when 5=> led <="0101";if inc='0' thenif month=12 thenmonth<=1;elsemonth<=month+1;end if;elsif dec='0' thenif month=0 thenmonth<=12;elsemonth<=month-1;end if;end if;when 6 =>led <="0110";if inc='0' thenif day=day_limit thenday<=1;elseday<=day+1;end if;elsif dec='0' thenif day=0 thenday<=day_limit;elseday<=day-1;end if;end if;when others =>null;end case;end if;--end if;end process;----------------------------------------------------------------------process(sec)begincase sec iswhen 0|10|20|30|40|50 => qsl<=0;when 1|11|21|31|41|51 => qsl<=1;when 2|12|22|32|42|52 => qsl<=2;when 3|13|23|33|43|53 => qsl<=3;when 4|14|24|34|44|54 => qsl<=4;when 5|15|25|35|45|55 => qsl<=5;when 6|16|26|36|46|56 => qsl<=6;when 7|17|27|37|47|57 => qsl<=7;when 8|18|28|38|48|58 => qsl<=8;when 9|19|29|39|49|59 => qsl<=9;when others =>null;end case;case sec iswhen 0|1|2|3|4|5|6|7|8|9 => qsh<=0;when 10|11|12|13|14|15|16|17|18|19 => qsh<=1;when 20|21|22|23|24|25|26|27|28|29 => qsh<=2;when 30|31|32|33|34|35|36|37|38|39 => qsh<=3;when 40|41|42|43|44|45|46|47|48|49 => qsh<=4;when 50|51|52|53|54|55|56|57|58|59 => qsh<=5;when others =>null;end case;end process;--------------------------------------------------------------------process(min)begincase min iswhen 0|10|20|30|40|50 => qml<=0;when 1|11|21|31|41|51 => qml<=1;when 2|12|22|32|42|52 => qml<=2;when 3|13|23|33|43|53 => qml<=3;when 4|14|24|34|44|54 => qml<=4;when 5|15|25|35|45|55 => qml<=5;when 6|16|26|36|46|56 => qml<=6;when 7|17|27|37|47|57 => qml<=7;when 8|18|28|38|48|58 => qml<=8;when 9|19|29|39|49|59 => qml<=9;when others =>null;end case;case min iswhen 0|1|2|3|4|5|6|7|8|9 => qmh<=0;when 10|11|12|13|14|15|16|17|18|19 => qmh<=1;when 20|21|22|23|24|25|26|27|28|29 => qmh<=2;when 30|31|32|33|34|35|36|37|38|39 => qmh<=3;when 40|41|42|43|44|45|46|47|48|49 => qmh<=4;when 50|51|52|53|54|55|56|57|58|59 => qmh<=5;when others =>null;end case;end process;-----------------------------------------------------------------------process(hour)begincase hour iswhen 0|10|20 => qhl<=0;when 1|11|21 => qhl<=1;when 2|12|22 => qhl<=2;when 3|13|23 => qhl<=3;when 4|14 => qhl<=4;when 5|15 => qhl<=5;when 6|16 => qhl<=6;when 7|17 => qhl<=7;when 8|18 => qhl<=8;when 9|19 => qhl<=9;when others =>null;end case;case hour iswhen 0|1|2|3|4|5|6|7|8|9 => qhh<=0;when 10|11|12|13|14|15|16|17|18|19 => qhh<=1;when 20|21|22|23 => qhh<=2;when others => null;end case;end process;---------------------------------------------------------------process(year)beginqy1<=year/1000;qy2<=(year rem 1000)/100;qy3<=((year rem 1000)rem 100)/10;qy4<=((year rem 1000)rem 100) rem 10;--qy1<=year/1000;--qy2<=(year rem 1000)/100;--qy3<=((year-(year/1000)*1000)-((year-(year/1000)*1000)/100)*100)/10;--qy4<=((year rem 1000)rem 100)rem 10;end process;----------------------------------------------------------------process(month)beginqmonh<=month/10;qmonl<=month rem 10;end process;-----------------------------------------------------------------process(day)beginqdh<=day/10;qdl<=day rem 10;end process;----------------------------------------------------------------process(clk1khz)beginif clk1khz'event and clk1khz='1' thenif cnt=7 thencnt<=0;else cnt<=cnt+1;end if;end if;end process;----------------------------------------------------------process (cnt,qhh,qhl,qmh,qml,qsh,qsl,dis_mode)begincase dis_mode iswhen 0 => case cnt iswhen 0 => data<=qsl; scan<="11111110";when 1 => data<=qsh; scan<="11111101";when 2 => data<=15 ; scan<="11111111";when 3 => data<=qml; scan<="11110111";when 4 => data<=qmh; scan<="11101111";when 5 => data<=15; scan<="11111111";when 6 => data<=qhl; scan<="10111111";when 7 => data<=qhh; scan<="01111111";when others => null;end case;when 1=> case cnt iswhen 0 => data<=qdl; scan<="11111110";when 1 => data<=qdh; scan<="11111101";when 2 => data<=qmonl ; scan<="11111011";when 3 => data<=qmonh; scan<="11110111";when 4 => data<=qy4; scan<="11101111";when 5 => data<=qy3; scan<="11011111";when 6 => data<=qy2; scan<="10111111";when 7 => data<=qy1; scan<="01111111";when others =>null;end case;when others => null;end case;end process;----------------------------------------------------------------------------------process(data)begincase data iswhen 0 =>seg8<="11000000";when 1 =>seg8<="11111001";when 2 =>seg8<="10100100";when 3 =>seg8<="10110000";when 4 =>seg8<="10011001";when 5 =>seg8<="10010010";when 6 =>seg8<="10000010";when 7 =>seg8<="11111000";when 8 =>seg8<="10000000";when 9 =>seg8<="10010000";when others =>seg8<="11111111";end case ;end process;end;。

基于FPGA的多功能电子万年历毕业设计说明

毕业设计中期报告题目名称:基于FPGA的万年历设计院系名称:电气学院班级:应电学号:0832100589学生:梁启超指导教师:金凤2011年06月目录一、多功能电子万年历及FPGA简介 (1)1.1电子万年历的发展 (1)1.2 FPGA简介 (1)1.3 电子万年历的工作原理 (2)二、多功能电子万年历各功能模块实现 (4)2.1 时钟问题 (4)2.1.1 全局时钟 (4)2.1.2 门控时钟 (4)2.1.3 多级逻辑时钟 (5)2.1.4 波动式时钟 (5)2.2 电子万年历的控制系统 (6)2.3 主控制模块 maincontrol (7)2.4 时间及其设置模块 time_auto_and_set (8)2.2.1 时间模块 timepiece_main (8)2.2.2 时间设置模块 timeset (9)2.2.3 时间数据与时间设置数据多路选择模块 time_mux (11)2.3 时间显示动态位选模块 time_disp_select (13)2.4 显示模块 disp_data_mux (14)2.5 秒表模块 stopwatch (15)2.6 日期显示与设置模块 date_main (16)2.6.1 日期自动工作模块 autodate (17)2.6.2 日期设置模块 setdate (17)2.7 闹钟模块alarmclock (18)2.8 分频模块 fdiv (19)2.9 顶层模块图 (21)三、附录 (23)电子万年历系统的Verilog HDL语言程序设计部分代码 (23)3.1主控制模块 (23)3.2秒自动计时子模块 (25)3.3时间自动工作控制 (25)3.4时间数据与时间设置数据多路选择模块 (26)3.5时间及其设置模块 (27)3.6时间显示动态位选模块 (28)3.7秒表模块 (29)3.8分频模块 (29)参考文献 (31)1 引言1.1 选题意义钟表的数字化给人们生产生活带来了极大的方便,而且大扩展了钟表原先的报时功能,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭路灯等。

26_毕业设计基于fpga的万年历设计[管理资料]

![26_毕业设计基于fpga的万年历设计[管理资料]](https://img.taocdn.com/s3/m/521fb3f2de80d4d8d05a4f3a.png)

基于FPGA的万年历电路的设计目录摘要 ........................................................................................................................................... Abstract (I)前言 0第1章万年历的发展及FPGA简介 (1)万年历的发展 (1)FPGA简介 (1)第2章设计原理 (2)组成模块 (2)系统设计图 (2)第3章各功能模块介绍 (4)分频模块(fenpin) (4)控制模块(countr) (4)时间显示调整模块(mux_4) (4)时分秒模块(timeve) (5)年月日模块(nyr2009) (5)显示控制模块(mux_16) (6)译码器(yimaqi) (6)第4章模拟仿真 (8)年月日模块仿真 (8)时分秒模块仿真 (8)结论 (9)总结与体会 (10)谢辞 (11)参考文献 (12)附录一 (13)附录二 (24)附录三 (30)基于FPGA的万年历电路的设计摘要基于FPGA的万年历设计,主要完成的任务是使用Verilog语言,在Quartis2上完成电路设计,程序开发模拟,基本功能是能够显示/修改年月日时分秒。

电路设计模块中分为几个模块:分频、控制、时间显示调整、时分秒、年月日、显示控制、译码器。

各个模块完成不同的任务,合在一起就构成了万年历的系统电路设计。

至于程序编写,使用Verilog语言,根据各个模块的不用功能和它们之间的控制关系进行编写。

软件模拟直接在Quartis2上进行。

进入信息时代,时间观念越来越重,但是老式的钟表以及日历等时间显示工具已经不太适合。

如钟表易坏,需要经常维修,日历需要每天翻页等。

对此,数字万年的设计就有了用武之地。

基于FPGA的万年历设计,采用软件开发模拟,开发成本低,而且再功能设计上有很大的灵活度,只要在软件上进行简单的修改就能实现不同的功能要求,能够满足不同环境要求。

利用VHDL语言与FPGA器件设计数字日历

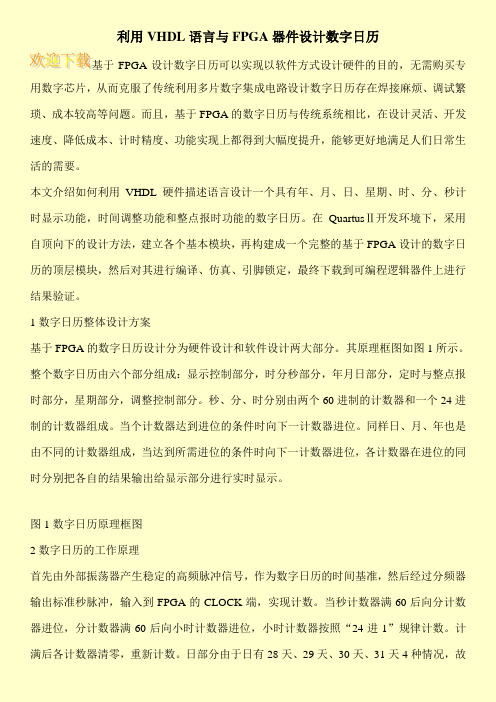

利用VHDL语言与FPGA器件设计数字日历基于FPGA设计数字日历可以实现以软件方式设计硬件的目的,无需购买专用数字芯片,从而克服了传统利用多片数字集成电路设计数字日历存在焊接麻烦、调试繁琐、成本较高等问题。

而且,基于FPGA的数字日历与传统系统相比,在设计灵活、开发速度、降低成本、计时精度、功能实现上都得到大幅度提升,能够更好地满足人们日常生活的需要。

本文介绍如何利用VHDL硬件描述语言设计一个具有年、月、日、星期、时、分、秒计时显示功能,时间调整功能和整点报时功能的数字日历。

在QuartusⅡ开发环境下,采用自顶向下的设计方法,建立各个基本模块,再构建成一个完整的基于FPGA设计的数字日历的顶层模块,然后对其进行编译、仿真、引脚锁定,最终下载到可编程逻辑器件上进行结果验证。

1数字日历整体设计方案基于FPGA的数字日历设计分为硬件设计和软件设计两大部分。

其原理框图如图1所示。

整个数字日历由六个部分组成:显示控制部分,时分秒部分,年月日部分,定时与整点报时部分,星期部分,调整控制部分。

秒、分、时分别由两个60进制的计数器和一个24进制的计数器组成。

当个计数器达到进位的条件时向下一计数器进位。

同样日、月、年也是由不同的计数器组成,当达到所需进位的条件时向下一计数器进位,各计数器在进位的同时分别把各自的结果输出给显示部分进行实时显示。

图1数字日历原理框图2数字日历的工作原理首先由外部振荡器产生稳定的高频脉冲信号,作为数字日历的时间基准,然后经过分频器输出标准秒脉冲,输入到FPGA的CLOCK端,实现计数。

当秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“24进1”规律计数。

计满后各计数器清零,重新计数。

日部分由于日有28天、29天、30天、31天4种情况,故。

基于FPGA电子万年历的设计与实现

本科毕业设计(论文)论文题目:基于FPGA的公农历显示系统设计系所:电子工程系专业:学生姓名:学生学号:指导教师:导师职称:讲师完成日期:2013年5月2日基于FPGA的公农历显示系统设计摘要万年历是采用数字电路实现对、时、分、秒数字显示的计时装置,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度,远远超过老式钟表, 钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的功能。

万年历具有读取方便、显示直观、功能多样、成本低廉等诸多优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。

本设计基于FPGA 芯片,系统集成化程度高,精度高,采用Verilog HDL语言程,用软件的方式设计硬件,灵活性好,方便以后的产品升级。

设计过程先对万年历进行系统分析确定需要的主要功能。

然后对电子万年历进行系统分析,画出每个模块的流程图、数据通道等,最后对每个模块进行代码编写。

本论文分别介绍八个模块:电子万年历核心控制模块、时间计时及其调整模块、时间显示动态位选模块、数码管显示模块、秒表模块、日期计时与调整模块、闹钟模块、分频模块。

在系统分析章节对整体设计的概况以及对每个模块进行描述,在系统实现章节每个模块具有单独的系统流程图,以及功能模块图。

在系统测试章节有对每个模块的测试后的波形图。

关键词:FPGA芯片,Verilog HDL语言,电子万年历Design of Calendar and Traditional Chinese Calendar System Based on FPGAAbstractThis calendar is the timing device that use of digital circuit to achieve, display the hours, minutes, seconds on digital display screen as well. Because of digital integrated circuit development and wide application of quartz crystal oscillators, the digital clock has become more accurate than the old-fashioned clocks. The digitalization of the clocks has brought great convenience to people, and also greatly expanded the original clock function. Calendar has plenty of advantages such as easy to read, displayed with intuition, low cost and so on. The calendar meet the nowadays' development trend of electronic instrumentation, and has a broad market prospect.The design is based on FPGA chip with a high degree of system integration and precision. This design uses Verilog HDL, so it can be flexible and easy to update in the future. The first step of design process is analysis system and determine the system's main function. Then we should draw flow charts of each module and data channels of the system. Finally write the code for each module.This thesis will introduce eight modules of the calendar system individually. Including electronic calendar center control module, Timing and adjustment module,dynamic time display selection module, LED display module, the stopwatch module, date and adjustment module, alarm module and frequency module. The chapter of systems analysis including the overall design of the profile and the description of each module. The chapter of system implementation has a separate section for each module system flowchart and functional block diagram. The chapters of system test will show the test waveform of each module.Key words: FPGA chip , Verilog HDL language , Electronic Calendar目录摘要 (II)第1章绪论 (1)1.1选题原因 (1)1.2国内外产品研究综述 (1)第2章关键技术介绍 (3)2.1电子万年历的发展 (3)2.2FPGA简介 (3)2.3电子万年历的工作原理 (3)第3章系统分析 (5)3.1计时流程 (5)3.2功能按键 (5)3.3功能框架 (6)第4章系统设计 (8)4.1时钟问题 (8)4.2电子万年历的控制系统 (9)4.3主控制模块MAINCONTROL (9)4.4时间及其设置模块TIME_AUTO_AND_SET (9)4.5时间数据与时间设置数据多路选择模块TIME_MUX (10)4.6时间显示动态位选模块TIME_DISP_SELECT (11)4.7显示模块DISP_DATA_MUX (11)4.8日期显示与设置模块DA TE_MAIN (12)4.9闹钟模块ALARMCLOCK (12)4.10分频模块FDIV (12)第5章系统实现 (14)5.1电子万年历的控制系统 (14)5.2主控制模块MAINCONTROL (14)5.3时间及其设置模块TIME_AUTO_AND_SET (15)5.3.1时间模块timepiece_main (15)5.3.2时间设置模块timeset (16)5.4时间数据与时间设置数据多路选择模块TIME_MUX (17)5.5时间显示动态位选模块TIME_DISP_SELECT (18)5.6显示模块DISP_DATA_MUX (18)5.7闹钟模块ALARMCLOCK (19)5.8分频模块FDIV (20)第6章系统测试 (21)6.1主控制模块MAINCONTROL (21)6.2时间及其设置模块TIME_AUTO_AND_SET (21)6.3时间设置模块TIMESET (22)6.4时间数据与时间设置数据多路选择模块TIME_MUX (22)6.5时间显示动态位选模块TIME_DISP_SELECT (22)6.6显示模块DISP_DATA_MUX (23)6.7秒表模块STOPWATCH (24)6.8日期显示与设置模块DA TE_MAIN (24)6.9闹钟模块ALARMCLOCK (24)6.10分频模块FDIV (25)第7章结论 (26)参考文献 (27)致谢 (28)第1章绪论1.1选题原因万年历给人们日常生活带来极大的方便,而且扩展了原先的报时功能,例如日期提醒,整点报时等。

基于FPGA的具有闰年补偿功能的数字日历

课程设计任务书课程名称:EDA技术题目:基于FPGA的具有闰年补偿功能的数字日历目录一、设计总体思路1.1课程设计内容-------------------------------------------------1 1.2课程设计要求-------------------------------------------------1 1.3课程设计的意义----------------------------------------------2 1.4设计总体思路-------------------------------------------------2 1.5设计框图-------------------------------------------------------3 二单元电路设计2.1天模块----------------------------------------------------------4 2.2月模块----------------------------------------------------------5 2.3年模块. ---------------------------------------------------------7 2.4星期模块-------------------------------------------------------8 2.5提醒模块-------------------------------------------------------92.6控制模块------------------------------------------------------102.7显示模块------------------------------------------------------11三、总电路设计--------------------------------------------------13四、电路调试----------------------------------------------------14五、设计调试总结与体会--------------------------------------16六、附录-----------------------------------------------------------17七、参考文献-----------------------------------------------------18附:课程设计评分表一、设计总体思路1.1设计总体内容用FPGA为核心器件,用VHDL为设计手段设计制作一个具有大小月份自动调节和闰年补偿功能的数字日历,具体设计要求如下:1、用7个数码管从左到右分别显示年(后两位)、月、日和星期;星期与日之间隔开一位。

(整理)基于FPGA的日历、时间、闹铃系统.

基于FPGA的日历、时间、闹铃系统前言:由于本人刚刚入门,只用了最基本的设计思维,所以可能浪费了许多芯片资源,要是哪位高手能帮忙把系统优本人定然感激不尽。

系统功能:显示当前日期,时间,到点报时。

可通过按键来调整日期时间,并且设置闹铃时间,闹铃响后,必须手动模块说明:系统的顶层模块如下图所示,该系统由六个模块组成,分别为分频模块,按键模块,计数模块,LCD液晶除法器模块,以及铃声模块。

皆为可综合模块,可综合为门级网表,并在FPGA芯片上验证了其正确性。

由于涉及版严禁用于商业目的,违者必究!按键示意图:各模块的verilog代码如下:1,、分频器:module div_1hz(clk,clock);output reg clock;input clk;//外部50MHZ时钟输入reg[24:0] i;always@(posedge clk)begini=i+1;if(i==25'h17d7840)begini=0;clock=~clock; //产生1HZ频率信号。

endendendmodule2、按键模块:module key(num,keyout,targe,keyout_en,keyin,rst,clk); output reg [3:0] keyout;output [3:0] num;output targe;output reg keyout_en;input rst,clk;input [3:0]keyin;reg [7:0] i;reg [3:0] num;reg [23:0] count;reg [5:0] state,next_state;reg [3:0] keyout_reg,keyin_reg;parameter s0=6'b000001,s1=6'b000010,s2=6'b000100,s3=6'b001000,s4=6'b010000,s5=6'b100000;wire clock;always@(posedge clk or negedge rst)beginif(!rst)i<=0;elsei<=i+1;endassign clock=i[7];always@(posedge clock or negedge rst)beginif(!rst)begincount<=0;keyout_en<=0;endelse beginif(keyin!=4'hf)beginif(count<'h4bb3)//去抖动count<=count+1;elsekeyout_en<=1;endelse if(state[5]||state[0])begincount<=0;keyout_en<=0;endendendassign targe=(!(state==s0||state==s5))&&(keyin!=4'hf); always@(posedge clock)beginif(targe)beginkeyout_reg<=keyout;keyin_reg<=keyin;endelsebeginkeyout_reg<=keyout_reg;keyin_reg<=keyin_reg;endendalways@(keyout_reg or keyin_reg or clock)begincase({keyin_reg,keyout_reg})8'b1110_1110: num <= 1 ;8'b1110_1101: num <= 2 ;8'b1110_1011: num <= 3 ;8'b1110_0111: num <= 10 ;8'b1101_1110: num <= 4 ;8'b1101_1101: num <= 5 ;8'b1101_1011: num <= 6 ;8'b1101_0111: num <= 11 ;8'b1011_1110: num <= 7 ;8'b1011_1101: num <= 8 ;8'b1011_1011: num <= 9;8'b1011_0111: num <= 12;8'b0111_1110: num <= 0;8'b0111_1101: num <= 15;8'b0111_1011: num <= 14;8'b0111_0111: num <= 13;endcaseendalways@(posedge clock or negedge rst) beginif(!rst)state<=s0;elsestate<=next_state;endalways@(keyin or state or keyout_en) beginkeyout=4'b0000;case(state)s0: beginkeyout=4'b0000;if(keyout_en)next_state=s1;elsenext_state=s0;ends1: beginkeyout=4'b1110;if(keyin!=4'hf)next_state=s5;elsenext_state=s2;ends2: beginkeyout=4'b1101;if(keyin!=4'hf)next_state=s5;elsenext_state=s3;ends3: beginkeyout=4'b1011;if(keyin!=4'hf)next_state=s5;elsenext_state=s4;ends4: beginkeyout=4'b0111;if(keyin!=4'hf)next_state=s5;elsenext_state=s0;ends5: beginkeyout=4'b0000;if(keyin==4'hf)next_state=s0;elsenext_state=s5;enddefault next_state=s0;endcaseendendmodule计数器模块:module jishuqi(out_4,out_400,nian,yue,ri,shi,fen,miao,n,speaker,ns,nf,clk_1hz,yushu1,yushu2,num,keyout_en);//shuzimiaobiaooutput reg[15:0]nian;output reg[7:0]yue,ri,shi,fen,miao,ns,nf;output [11:0] out_4,out_400;output reg [1:0]n;output reg speaker;input clk_1hz;input [15:0]yushu1,yushu2;input [3:0] num;input keyout_en;reg [3:0]cunt;reg[2:0] cnt;reg [15:0] ni;reg [7:0] y,r,s,f,m;assign out_4='d4;assign out_400='d400;wire [15:0]yushu;assign yushu=!((yushu1==0)||(yushu2==0))?0:1;initial begin ns<=8;speaker<=1;endalways@(posedge clk_1hz)beginif(n==3)begin speaker<=1;endelse if((shi==ns)&&(fen==nf))begin speaker<=0;endelsespeaker<=speaker;endalways@(negedge keyout_en)beginif(num=='ha)begin n<=1;cunt<=0;endelse if(num=='hd)beginn<=0;cunt<=0;cnt<=0;endelse if(num=='hb)n<=2;else if(num=='hc)n<=3;elsen<=n;if(n==2)beginif((num==1)||(num==2)||(num==3)||(num==4)||(num==5)||(num==6) ||(num==7)||(num==8)||(num==9||num==0))begin cnt<=cnt+1;endelsecnt<=cnt;endif(n==1)beginif((num==1)||(num==2)||(num==3)||(num==4)||(num==5)||(num==6) ||(num==7)||(num==8)||(num==9||num==0))begin cunt<=cunt+1;endelsecunt<=cunt;endcase(cnt)0:ns[7:4]<=num;1:ns[3:0]<=num;2:nf[7:4]<=num;3:nf[3:0]<=num;4:cnt<=0;endcasecase(cunt)0:begin ni[15:12]<=num;end1:begin ni[11:8]<=num;end2:begin ni[7:4]<=num;end3:begin ni[3:0]<=num;end4:begin y[7:4]<=num;end5:begin y[3:0]<=num;end6:begin r[7:4]<=num;end7:begin r[3:0]<=num;end8:begin s[7:4]<=num;end9:begin s[3:0]<=num;end10:begin f[7:4]<=num;end11:begin f[3:0]<=num;end12:begin m[7:4]<=num;end13:begin m[3:0]<=num;end14:cunt<=0;endcaseendalways@(posedge clk_1hz)//suan fa shi xian beginif(n!=1)beginmiao<=miao+1;if(yue=='h13)beginyue<=0;nian[3:0]<=nian[3:0]+1;if(nian[3:0]=='d9)beginnian[3:0]<=0;nian[7:4]<=nian[7:4]+1;if(nian[7:4]=='d9)beginnian[7:4]<=0;nian[11:8]<=nian[11:8]+1;if(nian[11:8]=='d9)beginnian[11:8]<=0;nian[15:12]<=nian[15:12]+1;if(nian[15:12]=='d9)endendendendif(miao[3:0]==4'd9)beginmiao[3:0]<=0;miao[7:4]<=miao[7:4]+1;if(miao[7:4]==4'd5)beginmiao[7:4]<=0;fen[3:0]<=fen[3:0]+1;if(fen[3:0]==9)beginfen[3:0]<=0;fen[7:4]<=fen[7:4]+1;if(fen[7:4]==4'd5)beginfen[7:4]<=0;shi[3:0]<=shi[3:0]+1;if(shi[3:0]=='d9)beginshi[3:0]<=0;shi[7:4]<=shi[7:4]+1;endif((shi[7:4]==2)&&(shi[3:0]==3))beginshi[7:4]<=0;shi[3:0]<=0;ri[3:0]<=ri[3:0]+1;if(ri[3:0]=='d9)beginri[3:0]<=0;ri[7:4]<=ri[7:4]+1;endif(((yue[3:0]==1)&&(yue[7:4]==0))||((yue[3:0]==3)&&(yue[7:4]==0))||(yue[3:0]==5)||(yue[3:0]==7)||( =8)||((yue[3:0]==0)&&(yue[7:4]==1))||((yue[3:0]==2)&&(yue[7:4]==1))||((yue[3:0]==3)&&(yue[7:4]==1))beginif(!((yue[3:0]==3)&&(yue[7:4]==1)))beginif((ri[7:4]==3)&&(ri[3:0]==1))beginri[7:4]<=0;ri[3:0]<=1;endendif((yue[3:0]==4)||(yue[3:0]==6)||(yue[3:0]==9)||((yue[3:0]==1)&&(yue[7:4]==1))) beginif((ri[7:4]==3)&&(ri[3:0]==0))beginri[7:4]<=0;ri[3:0]<=1;yue[3:0]<=yue[3:0]+1;endendif((yue[3:0]==2)&&(yue[7:4]==0))beginif(yushu==0)beginif((ri[7:4]==2)&&(ri[3:0]==9))beginri[7:4]<=0;ri[3:0]<=1;yue[3:0]<=yue[3:0]+1;endendelsebeginif(ri[7:4]==2&&ri[3:0]==9)beginri[7:4]<=0;ri[3:0]<=1;yue[3:0]<=yue[3:0]+1;endendendif(yue[3:0]=='d10)beginyue[3:0]<=0;yue[7:4]<=yue[7:4]+1;endendendendendendendendif(n==1)beginnian<=ni;yue<=y;ri<=r;shi<=s;fen<=f;miao<=m;endendendmodule4、LCD液晶显示模块:module lcd1602(nian,yue,ri,shi,fen,miao,clk,n,ns,nf,rs,rw,en,dat); function [7:0]data;input [3:0] num;begincase(num)0:begin data=8'h30;end1:data=8'h31;2:data=8'h32;3:data=8'h33;4:data=8'h34;5:data=8'h35;6:data="6";7:data=8'h37;8:data=8'h38;9:data=8'h39;endcaseendendfunctioninput [15:0] nian;input [7:0] yue,ri,shi,fen,miao;input [7:0]ns,nf;input clk;input [1:0] n;output rs,rw,en;output[7:0] dat;reg rs,rw;wire en;reg[7:0] dat;reg[5:0] counter;reg[1:0] state;reg [15:0] count;reg clkr;parameter init=0,write_data=1;assign en=clkr;always @(posedge clk)begincount=count+1;if(count==16'h000f)clkr=~clkr;endalways@(posedge clkr)begincase(state)init:beginrs=0;rw=0;counter=counter+1;case(counter)1:dat='h38;2:dat='h08;3:dat='h01;4:dat='h06;5:dat='h0c;6:begindat='h80;state=write_data;counter=0;enddefault: counter=0;endcaseendwrite_data:beginif(n!=2)begincase(counter)0:begin rs<=0;dat=0+8'h80;end1:begin rs<=1;dat=data(nian[15:12]);end2:begin rs<=0;dat=1+8'h80;end3:begin rs<=1;dat=data(nian[11:8]);end4:begin rs<=0;dat=2+8'h80;end5:begin rs<=1;dat=data(nian[7:4]);end6:begin rs<=0;dat=3+8'h80;end7:begin rs<=1;dat=data(nian[3:0]);end8:begin rs<=0;dat=4+8'h80;end9:begin rs<=1;dat="-";end10:begin rs<=0;dat=5+8'h80;end11:begin rs<=1;dat=data(yue[7:4]);end12:begin rs<=0;dat=6+8'h80;end13:begin rs<=1;dat=data(yue[3:0]);end14:begin rs<=0;dat=7+8'h80;end15:begin rs<=1;dat="-";end16:begin rs<=0;dat=8+8'h80;end17:begin rs<=1;dat=data(ri[7:4]);end18:begin rs<=0;dat=9+8'h80;end19:begin rs<=1;dat=data(ri[3:0]);end20:begin rs<=0;dat=0+8'hc0;end21:begin rs<=1;dat=data(shi[7:4]);end22:begin rs<=0;dat=1+8'hc0;end23:begin rs<=1;dat=data(shi[3:0]);end24:begin rs<=0;dat=2+8'hc0;end25:begin rs<=1;dat=":";end26:begin rs<=0;dat=3+8'hc0;end27:begin rs<=1;dat=data(fen[7:4]);end28:begin rs<=0;dat=4+8'hc0;end29:begin rs<=1;dat=data(fen[3:0]);end30:begin rs<=0;dat=5+8'hc0;end31:begin rs<=1;dat=":";end32:begin rs<=0;dat=6+8'hc0;end33:begin rs<=1;dat=data(miao[7:4]);end34:begin rs<=0;dat=7+8'hc0;end35:begin rs<=1;dat=data(miao[3:0]);end36:beginrs=0; dat='h80;enddefault: counter=0;endcaseif(counter==37) counter=0;else counter=counter+1;endelsebegincase(counter)0:begin rs<=0;dat=0+8'h80;end1:begin rs<=1;dat=data(ns[7:4]);end2:begin rs<=0;dat=1+8'h80;end3:begin rs<=1;dat=data(ns[3:0]);end4:begin rs<=0;dat=2+8'h80;end5:begin rs<=1;dat=":";end6:begin rs<=0;dat=3+8'h80;end7:begin rs<=1;dat=data(nf[7:4]);end 8:begin rs<=0;dat=4+8'h80;end9:begin rs<=1;dat=data(nf[3:0]);end10:begin rs<=0;dat=5+8'h80;end11:begin rs<=1;dat=" ";end12:begin rs<=0;dat=6+8'h80;end13:begin rs<=1;dat=" ";end14:begin rs<=0;dat=7+8'h80;end15:begin rs<=1;dat=" ";end16:begin rs<=0;dat=8+8'h80;end17:begin rs<=1;dat=" ";end18:begin rs<=0;dat=9+8'h80;end19:begin rs<=1;dat=" ";end20:begin rs<=0;dat=0+8'hc0;end21:begin rs<=1;dat=" ";end22:begin rs<=0;dat=1+8'hc0;end23:begin rs<=1;dat=" ";end24:begin rs<=0;dat=2+8'hc0;end25:begin rs<=1;dat=" ";end26:begin rs<=0;dat=3+8'hc0;end27:begin rs<=1;dat=" ";end28:begin rs<=0;dat=4+8'hc0;end29:begin rs<=1;dat=" ";end30:begin rs<=0;dat=5+8'hc0;end31:begin rs<=1;dat=" ";end32:begin rs<=0;dat=6+8'hc0;end33:begin rs<=1;dat=" ";end34:begin rs<=0;dat=7+8'hc0;end35:begin rs<=1;dat=" ";end36: beginrs=0; dat='h80;enddefault:counter<=0;endcaseif(counter==37) counter<=0;else counter<=counter+1;endenddefault: state=init;endcaseendendmodule5、除法器模块,module divider(quotient,remainder,ready,error,word1,word2,start,clock,reset);parameter L_divn=16,L_divr=12,S_idle=0,S_adivr=1,S_adivn=2,S_div=3,S_err=4,L_state=3,L_cnt=4,Max_cnt=L_divn-L_divr;output [L_divn-1:0] quotient,remainder;output ready,error;input [L_divn-1:0] word1;//dividendinput [L_divr-1:0] word2;//divisorinput start,clock,reset;//0,start,1,resetreg [L_state-1:0] state,next_state;reg Load_words,Subtract,Shift_dividend,Shift_divisor;reg [L_divn-1:0] quotient;reg [L_divn:0] dividend;reg [L_divr-1:0] divisor;reg [L_cnt-1:0] num_Shift_dividend,num_Shift_divisor;reg [L_divr:0] comparison;wire MSB_divr=divisor[L_divr-1];wire ready=((state==S_idle)&&reset);wire error=(state==S_err);wire Max=(num_Shift_dividend==Max_cnt+num_Shift_divisor);wire sign_bit=comparison[L_divr];assign remainder=(dividend[L_divn-1:L_divn-L_divr])>num_Shift_divisor;/////////always @(state or dividend or divisor or MSB_divr)case(state)S_adivr: if(MSB_divr==0)comparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~(divisor<<1)}+1'b1;elsecomparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~divisor[L_divr-1:0]} default: comparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~divisor[L_divr-1:0]}+1'b1;endcasealways @(posedge clock or negedge reset)if(!reset) state<=S_idle; else state<=next_state;always @(state or word1 or word2 or start or comparison or sign_bit or Max)beginLoad_words=0;Subtract=0;Shift_dividend=0;Shift_divisor=0;case(state)S_idle: case(!start)0: next_state=S_idle;1: if(word2==0) next_state=S_err;else if(word1) begin next_state=S_adivr;Load_words=1;else next_state=S_idle;endcaseS_adivr: case(MSB_divr)0: if(sign_bit==0) begin next_state=S_adivr;Shift_divisor=1else if(sign_bit==1) next_state=S_adivn;1: next_state=S_div;endcaseS_adivn: case({Max,sign_bit})2'b00: next_state=S_div;2'b01: begin next_state=S_adivn;Shift_dividend=1; end2'b10: begin next_state=S_idle;Subtract=1; end2'b11: next_state=S_idle;endcaseS_div: case({Max,sign_bit})2'b00: begin next_state=S_div;Subtract=1; end2'b01: next_state=S_adivn;2'b10: begin next_state=S_div;Subtract=1; end2'b11: begin next_state=S_div;Shift_dividend=1; endendcasedefault: next_state=S_err;endcaseendalways @(posedge clock or negedge reset)beginif(!reset)begindivisor<=0;dividend<=0;quotient<=0;num_Shift_dividend<=0;num_Shift_divisor<=0;endelse if(Load_words==1)begindividend<=word1;divisor<=word2;quotient<=0;num_Shift_dividend<=0;num_Shift_divisor<=0;endelse if(Shift_divisor)begindivisor<=divisor<<1;num_Shift_divisor<=num_Shift_divisor+1;endelse if(Shift_dividend)begindividend<=dividend<<1;quotient<=quotient<<1;num_Shift_dividend<=num_Shift_dividend+1;endelse if(Subtract)begindividend[L_divn:L_divn-L_divr]<=comparison;quotient[0]<=1;endendendmodule6、铃声模块:module liangzhu(sys_clk,rst_n,sp);input sys_clk,rst_n;output sp;reg sp;reg[3 :0] high,med,low;reg[13:0] divider,origin;reg[7 :0] counter;reg[23:0] clk_cnt;always @ (posedge sys_clk or posedge rst_n)if (rst_n)clk_cnt <= 24'd0;elseclk_cnt <= clk_cnt + 1'b1;wire clk_6mhz = clk_cnt[2];wire clk_4hz = clk_cnt[23];wire carry=(divider==16383);always @(posedge clk_6mhz)beginif(carry)divider=origin;elsedivider=divider+1'b1;endalways@(posedge carry)beginsp =~sp;endalways@(posedge clk_4hz)begincase({high ,med ,low})12'b000000000011: origin=14'd7281;12'b000000000101: origin=14'd8730;12'b000000000110: origin=14'd9565;12'b000000000111: origin=14'd10310;12'b000000010000: origin=14'd10647;12'b000000100000: origin=14'd11272;12'b000000110000: origin=14'd11831;12'b000001010000: origin=14'd12556;12'b000001100000: origin=14'd12974;12'b000100000000: origin=14'd13516;12'b000000000000: origin=14'd16383;default:origin=14'd0;endcaseendalways@(posedge clk_4hz)beginif(counter==8'd50)counter=8'd0;elsecounter=counter+1'b1;case(counter)8'd 0:{high,med,low}=12'b0000_0000_0011; 8'd 1:{high,med,low}=12'b0000_0000_0011;8'd 2:{high,med,low}=12'b0000_0000_0011;8'd 3:{high,med,low}=12'b0000_0000_0011;8'd 4:{high,med,low}=12'b0000_0000_0101;8'd 5:{high,med,low}=12'b0000_0000_0101;8'd 6:{high,med,low}=12'b0000_0000_0101;8'd 7:{high,med,low}=12'b0000_0000_0110;8'd 8:{high,med,low}=12'b0000_0001_0000;8'd 9:{high,med,low}=12'b0000_0001_0000;8'd10:{high,med,low}=12'b0000_0001_0000;8'd11:{high,med,low}=12'b0000_0010_0000;8'd12:{high,med,low}=12'b0000_0000_0110;8'd13:{high,med,low}=12'b0000_0001_0000;8'd14:{high,med,low}=12'b0000_0000_0101;8'd15:{high,med,low}=12'b0000_0000_0101;8'd16:{high,med,low}=12'b0000_0101_0000;8'd17:{high,med,low}=12'b0000_0101_0000;8'd18:{high,med,low}=12'b0000_0101_0000;8'd19:{high,med,low}=12'b0001_0000_0000;8'd20:{high,med,low}=12'b0000_0110_0000;8'd21:{high,med,low}=12'b0000_0101_0000;8'd22:{high,med,low}=12'b0000_0011_0000;8'd23:{high,med,low}=12'b0000_0101_0000;8'd24:{high,med,low}=12'b0000_0010_0000;8'd25:{high,med,low}=12'b0000_0010_0000;8'd26:{high,med,low}=12'b0000_0010_0000;8'd27:{high,med,low}=12'b0000_0010_0000;8'd28:{high,med,low}=12'b0000_0010_0000;8'd29:{high,med,low}=12'b0000_0010_0000;8'd30:{high,med,low}=12'b0000_0010_0000;8'd31:{high,med,low}=12'b0000_0010_0000;8'd32:{high,med,low}=12'b0000_0010_0000;8'd33:{high,med,low}=12'b0000_0010_0000;8'd34:{high,med,low}=12'b0000_0010_0000;8'd35:{high,med,low}=12'b0000_0011_0000;8'd36:{high,med,low}=12'b0000_0000_0111;8'd37:{high,med,low}=12'b0000_0000_0111;8'd38:{high,med,low}=12'b0000_0000_0110;8'd39:{high,med,low}=12'b0000_0000_0110;8'd40:{high,med,low}=12'b0000_0000_0101;8'd41:{high,med,low}=12'b0000_0000_0101;8'd42:{high,med,low}=12'b0000_0000_0101;8'd43:{high,med,low}=12'b0000_0000_0110;8'd44:{high,med,low}=12'b0000_0001_0000;8'd45:{high,med,low}=12'b0000_0001_0000;8'd46:{high,med,low}=12'b0000_0010_0000;8'd47:{high,med,low}=12'b0000_0010_0000;default:{high,med,low}=12'd0;endcase//后边乐曲片断此处省略endendmodule后记:本人深深的体会到语法的重要性,一个小小的语法问题有时候可以折磨人几天甚至几个月。

单片机万年历设计

若采用CPU设计数字万年历,可以实现年、月、日、星期、时、分、秒基本功能,但是在软件编程时要设计很多语句,语句调用频繁。显然不能达到课题设计的要求。所以用FPGA设计数字万年历。

六预期成果:

万年历具有年、月、日、星期、时、分、秒等功能;时间与阴、阳历能够自动关联;具备年、月、日、星期、时、分、秒校准功能

[5]崔葛瑾主编,基于FPGA数字电路系统设计2008-7-1西安电子科技大学出版社

[6]全国大学生电子设计竞赛组委会编.全国大学生电子设计竞赛获奖作品选编(2003).北京理工大学出版社,2005.3

[7]陈耀和,VHDL语言设计技术2004-4电子工业出版社

[8]刘韬楼兴华, FPGA数字电子系统设计与开发实例导航2005-6-1人民邮电出版社

程序流程框图

注:读、写日期、时间和温度,分离日期、时间、温度显示值。

图-1主程序流程图

图-2计算阳历程序流程图

注:计算阳历天数结束,总天数中的数据为当前日期在阳历中的第几天。

图-3时间调整程序流程图

注:实现年、月、日、星期、时、分、秒等功能;时间与阴、阳历能够自动关联;具备年、月、日、星期、时、分、秒校准功能

综上所述此万年历具有读取方便、显示直观、功能多样、电路简洁、成本低廉等诸多优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。

三设计方案心,需要考虑一下闰年。农历60年一个循环,

阴历阳历分开算,最后数据组合就是既有阴历又有阳历了

2.总体结构

框图

四软件设计:

课题名称

基于FPGA的数字万年历的设计与制作

一课题任务:

以FPGA适配板为核心,设计并制作一款数字万年历。此数字万年历以“日”为基本计时单位,用8只数码管适时显示“年、月、日”。