Verilog行为仿真

vcs的仿真流程

vcs的仿真流程

VCS(Verilog Compiler Simulator,Verilog编译器和仿真器)是一款常用的硬件描述语言(HDL)仿真工具。

以下是VCS 的仿真流程:

1. 设计编写:使用硬件描述语言(一般是Verilog或SystemVerilog)编写设计代码,描述电子系统的行为模型和结构。

2. 编译:将设计代码输入VCS编译器进行编译,生成仿真所需的模块。

3. 链接:将编译生成的模块和其他库文件进行链接,生成仿真所需的可执行文件。

4. 仿真设置:配置仿真环境,包括定义输入文件、仿真时钟频率、仿真时长等参数。

5. 仿真运行:运行仿真程序,根据输入文件和时钟来模拟电路的行为,产生输出。

6. 波形查看:打开仿真产生的波形文件,可以观察电路中信号的变化和时序。

7. 仿真分析:对仿真结果进行分析,比较波形与预期结果,发现和调试设计中的问题。

8. 优化调试:根据仿真结果,修改设计代码,重新进行编译、链接和仿真,直到获得满意的结果。

9. 性能分析:对仿真的性能进行评估,包括仿真时间、内存占用等指标。

10. 验证验证:使用不同的测试用例对设计进行验证,以确保设计满足规格和要求。

11. 完成仿真:当设计达到预期的性能和功能时,完成仿真过程。

NC-Verilog仿真详解

NC-Verilog仿真详解ncverilog仿真详解发表在ASIC/FPGA/汇编, 学习笔记, 编程开发 | 由阿布 | ⼗⼀⽉26, 2011 | 0标签: ncverilog, 仿真数位IC⼯具简介——Simulator ⼯具ModelSimModelSim是Mentor公司所推出的软体, 主要⽤来当作VHDL的模拟器, 也是⽬前CIC在VHDL⽅⾯的主要的模拟软体;但ModelSim不仅⽀援VHDL的模拟,同样也可⽤来当Verilog的模拟器, 更进⼀步的, ModelSim也⽀援VHD&Verilog的混合模拟, 这对於单晶⽚系统(SoC)的发展上, 矽智产(IP)是来源来⾃不同的地⽅, 有些矽智产是采⽤VHDL描述,有些是Verilog描述, 因此这是不可或缺的功能. 所以CIC引进ModelSim这⼀套软体.NCSimNC-SIM 为Cadence 公司之VHDL与Verilog混合模拟的模拟器(simulator),可以帮助IC 设计者验证及模拟其所⽤VHDL与Verilog混合计设的IC功能.NCVerilogNC-Verilog 为Cadence 公司之Verilog 硬体描述语⾔模拟器(simulator),可以帮助IC 设计者验证及模拟所设计IC 的功能.使⽤NC-Verilog软体,使⽤者必须使⽤Verilog 硬体描述语⾔的语法来描述所要设计的电路.VCSVCS 为Synopsys 公司之Verilog 硬体描述语⾔模拟器(simulator),可以帮助IC设计者验证及模拟所设计IC 的功能.使⽤VCS 软体,使⽤者必须使⽤Verilog 硬体描述语⾔的语法来描述所要设计的电路.ncverilog使⽤ncverilog是shell版的,nclaunch是以图形界⾯为基础的,⼆者调⽤相同内核;ncverilog的执⾏有三步模式和单步模式,在nclaunch中对应multiple step和single stepncverilog的三步模式为:ncvlog(编译) ncelab(建⽴snapshot⽂件) ncsim(对snapshot⽂件进⾏仿真)基于shell的ncverilog操作(尤其是单步模式)更适合于⼤批量操作ncverilog的波形查看配套软件是simvision,其中包含原理图、波形、信号流等查看⽅式三命令模式:ncvlog -f run.fncelab tb -access wrcncsim tb -gui第⼀个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb⽂件放在⾸位,这样可以避免出现提⽰timescale 的错误注意:ncvlog执⾏以后将产⽣⼀个名为INCA_libs的⽬录和⼀个名为worklib的⽬录第⼆个命令中,access选项是确定读取⽂件的权限。

Modelsim NC-Verilog仿真理解

Modelsim/NC-Verilog仿真理解仿真(Simulation),也称为模拟,是对所有集成电路或系统的一种检测方法。

用户可以在设计过程中对整个系统和部分模块进行仿真,即在计算机上用仿真软件验证功能是否正确、各部分的时序配合是否正确。

如果有问题可以随时进行修改,从而避免逻辑错误。

高级的仿真软件还可以整个系统设计性能进行评估。

设计规模越大就越需要进行仿真。

仿真包括功能仿真和时序仿真。

在设计输入阶段按进行仿真,不考虑信号延时等因素成为功能仿真,又称前仿真;时序仿真又称为后仿真,他在选择了具体器件并完成了布局布线以后进行的含定时关系的仿真。

由于不同器件的内部延时不同,不同的布局、布局方案也给延时造成了很大的影响,因此在设计实现后,对网络和逻辑块进行延时仿真,分析定时关系,估计设计性能非常有必要。

要进行电路仿真必须有仿真器的支持。

常用的Verilog仿真器有:ModelSim、Verilog-XL、NC-Verilog和VCS等。

下面我们简单介绍下我们常用到的ModelSim、NC-Verilog两款仿真软件特点、区别。

一、ModelSimModelSim是Mentor Graphics子公司ModelSim Technology的产品,是业界优秀的HDL 语言仿真软件之一,它是编译型的VerilogHDL/VHDL混合仿真器。

MoselSim可以在同一设计中单独或混合使用Verilog HDL和VHDL,允许Verilog HDL模块调用VHDL的实体,或用VHDL模块调用Verilog HDL的实体。

由于ModelSim是编译型仿真器,使用编译后的HDL 库进行仿真,因此在进行仿真前,必须所有待仿真的HDL文件编译成为HDL仿真库,在编译时使源文件获得优化,提高了仿真速度。

Model Sim只完成逻辑功能的仿真,并不考虑具体使用什么器件,学习HDL或者设计逻辑的时候compile一次所用的时间很短,便于调试找出逻辑的错误。

verilog仿真课程设计

verilog仿真课程设计一、教学目标本课程的教学目标旨在让学生掌握Verilog仿真基本原理和方法,具备使用Verilog进行数字电路设计和仿真的能力。

知识目标:使学生了解Verilog语言的基本语法、数据类型、运算符、表达式以及常用的建模方法。

技能目标:培养学生运用Verilog进行数字电路设计、仿真和测试的能力,能够独立完成简单的数字系统设计。

情感态度价值观目标:培养学生对电子信息科学的兴趣,提高学生创新实践能力,培养学生团队合作精神。

二、教学内容本课程的教学内容主要包括Verilog语言的基本语法、数据类型、运算符、表达式、建模方法以及数字电路的设计与仿真。

1.Verilog语言基本语法:介绍Verilog模块的结构、参数、端口以及语句的书写规范。

2.数据类型和运算符:讲解Verilog中的基础数据类型、复合数据类型以及常用运算符。

3.表达式:讲解Verilog中的算术表达式、关系表达式和逻辑表达式。

4.建模方法:介绍Verilog中的线网建模、模块实例化以及参数传递。

5.数字电路设计与仿真:以实例形式讲解如何使用Verilog进行组合逻辑电路、时序逻辑电路以及复杂数字系统的设计与仿真。

三、教学方法为提高教学效果,本课程将采用讲授法、案例分析法、实验法等多种教学方法相结合。

1.讲授法:通过讲解Verilog语言的基本语法、数据类型、运算符、表达式以及建模方法,使学生掌握理论知识。

2.案例分析法:通过分析实际案例,让学生了解Verilog在数字电路设计与仿真中的应用。

3.实验法:安排实验课程,让学生动手实践,巩固所学知识,提高实际操作能力。

四、教学资源为实现教学目标,我们将为学生提供丰富的教学资源,包括教材、参考书、多媒体资料以及实验设备。

1.教材:选用权威、实用的Verilog教材,为学生提供系统性的理论知识学习。

2.参考书:推荐学生阅读相关Verilog参考书籍,拓展知识面。

3.多媒体资料:制作精美的PPT课件,为学生提供直观的学习体验。

NC-verilog 仿真教程和实验实例

Cadence IC设计实验实验六 NC-Verilog Simulator实验实验目的:NC_verilog仿真器的使用,包括编译、运行和仿真。

预备工作:cp /eva01/cdsmgr/ training_IC_data/NCVlog_5_0.tarZ .tar -vxfZ NCVlog_5_0.tarZLab1。

运行一个简单的Verilog设计[1]、设置设计环境1.cd NCVlog_5_0/lab1-mux这个目录包含了用来描述一个多路选择器和其测试平台的verilog 模块。

以下是mux_test.v模块内功能模块的端口框图。

建议:如果有时间,你最好看一看各模块(module)的Verilog代码!2.创建cds.lib文件,vi cds.lib(回车)按小写”i”切换到编辑模式,在其中写入:Define lab1muxlib ./lab1-mux.lib有关vi的编辑命令,请参阅相关资料。

如”Esc”键切换到命令状态,在命令状态下,”x”是删除当前字符,”a”是在当前光标后写入,”:wq”是存盘退出,”:!q”是不保存退出。

存盘退出3.创建(库)文件夹(即目录):mkdir lab1-mux.lib (回车)4.类似步骤1,创建hdl.var文件,在其中写入:Define WORK lab1muxlib存盘退出5.查看verilog源文件。

mux.v是2选1多路选择器MUX2_1 的门级建模源文件,mux_test.v是mux.v的测试台,包含了输入激励信号和监控程序运行的任务语句。

[2]、编译源文件(ncvlog命令):当前目录应为。

/你的学号/NCVlog_5_0/lab1-mux。

1.ncvlog mux.v –messages ,这条指令是编译mux.v。

2.vi hdl.var打开hdl.var文件,在其中添加:Define NCVLOGOPTS –messages 存盘退出注:用NCVLOGOPTS变量定义常用的ncvlog命令行操作,从而避免每次都敲入同样的命令行。

verilog仿真流程

verilog仿真流程When it comes to the verilog simulation process, it is important to understand the various steps involved in ensuring a successful simulation. Verilog is a hardware description language that is commonly used in the design and verification of digital circuits. The simulation process is essential for testing the functionality of the design and identifying any potential issues before the actual hardware implementation.The first step in the verilog simulation process is to write the verilog code for the digital circuit. This involves describing the behavior of the circuit using verilog constructs such as modules, signals, and processes. It is important to ensure that the code is written accurately and efficiently to avoid any errors during the simulation.Once the verilog code is written, the next step is to compile the code using a verilog compiler. The compilertranslates the verilog code into a format that can be understood by the simulation tool. During the compilation process, the compiler checks for syntax errors and other issues that may prevent the code from being successfully simulated.After the code is compiled, the next step is to set up the simulation environment. This involves specifying the simulation parameters such as the input stimulus, simulation time, and any other relevant settings. It is important to carefully configure the simulation environment to ensure that the desired behavior of the circuit is accurately captured during the simulation.Once the simulation environment is set up, the next step is to run the simulation using a verilog simulator. The simulator executes the verilog code and simulates the behavior of the digital circuit based on the specified input stimulus. During the simulation, it is important to monitor the output waveforms and other relevant data to verify the functionality of the design.After the simulation is complete, the next step is to analyze the simulation results. This involves examining the output waveforms and other relevant data to identify any potential issues or discrepancies in the behavior of the circuit. If any issues are identified, it may be necessaryto make changes to the verilog code and re-run thesimulation to verify the effectiveness of the modifications.In conclusion, the verilog simulation process is a critical step in the design and verification of digital circuits. By following the necessary steps such as writing the verilog code, compiling the code, setting up the simulation environment, running the simulation, and analyzing the results, it is possible to ensure the functionality and reliability of the design before proceeding to the actual hardware implementation. The simulation process requires careful attention to detail and thorough analysis to identify and address any potential issues, ultimately leading to a successful and reliable digital circuit design.。

verilog仿真验证流程

verilog仿真验证流程Verilog simulation verification flow is a crucial step in the development process of digital designs. It ensures that the design functions as expected before moving on to the implementation stage. The process involves writing testbenches to stimulate the design and check its outputs against the expected results. This iterative process helps uncover bugs and issues early on, saving time and effort in the long run.Verilog仿真验证流程在数字设计开发过程中是一个至关重要的步骤。

它确保设计在进入实现阶段之前能如预期地工作。

该过程涉及编写测试平台来激励设计并检查其输出与预期结果是否一致。

这个迭代过程有助于及早发现错误和问题,从而节省时间和精力。

When it comes to Verilog simulation verification flow, there are several key components to consider. First, the design under test (DUT) should be thoroughly understood to create effective testbenches. Understanding the functionality and expected behavior of the DUT is crucial in writing stimuli that will exercise all aspects of the design. Next, the testbench itself needs to be carefully crafted toensure comprehensive coverage of the design. This includes creating test cases that cover both typical and edge-case scenarios to verify the robustness of the design.说到Verilog仿真验证流程,有几个关键组成部分需要考虑。

modelsim进行verilog的仿真---(Quartus中调用RTL仿真)

modelsim进⾏verilog的仿真---(Quartus中调⽤RTL仿

真)

RTL即寄存器Register Transfer level,译为寄存器传输级,在quartus II的tool⼯具栏⾥有⼀个选项:Run EDA Simulation tool->Run RTL Simulation,我⼀直没弄明⽩这个和功能仿真有什么区别,下⾯开始通过实践来确定⼀下这个两者有什么不同吧。

还是以⼀个D触发器为例,源码在功能仿真的⽂章⾥已经有了,下⾯进⾏设置:在quartus II中新建⼀个⼯程,添加simualte1.v和testbetch1.v到⼯程中,然后设置simulate1为顶层⼊⼝⽂件。

接下来点击Assignment->setting..,然后点击EDA Tool Setting->simulation,如图进⾏设置

点击test Benches按钮,然后如下图点击new:

按照下⾯进⾏设置:

设置好了就⼀路点OK回到quartus主界⾯,然后ctrl+K或者processing->start->analysis & sythesis,然后点击Tool->Run EDA Simulation tool->Run RTL Simulation,quartus会⾃动调⽤modelsim进⾏仿真,仿真图如下:

发现没有,跟功能仿真时⼀样的,由此可见RTL级仿真也就是功能仿真,只不过在quartus⾃带仿真中需先⽣成功能仿真⽹表,然后进⾏功能仿真。

第11章 Verilog仿真与验证

11.2 用户自定义元件(UDP)

利用UDP(User Defined Primitives)用户可以自己 定义基本逻辑元件的功能,用户可以象调用基本门元件一样 来调用这些自己定义的元件。 UDP关键词为primitive和endprimitive。与一般的模 块相比,UDP模块具有下面一些特点: ◆ UDP的输出端口只能有一个,且必须位于端口列表的 第一项。只有输出端口能被定义为reg类型。 ◆ UDP的输入端口可有多个,一般时序电路UDP的输入 端口可多至9个,组合电路UDP的输入端口可多至10个。 ◆ 所有的端口变量必须是1位标量。 ◆ 在table表项中,只能出现0、1、x三种状态,不能出 现z状态。

只用于时序元件的输出

从逻辑v到逻辑y的转变 表示输入端有任何变化 表示上升沿 表示下降沿 包含x态的上升沿跳变 包含x态的下降沿跳变

11.3 延时模型的表示

延时包括门延时、assign赋值延时和连线延时等。

门延时是从门输入端发生变化到输出端发生变化的延

迟时间; assign赋值延时指等号右端某个值发生变化到等号左 端发生相应变化的延迟时间; 连线延时则体现了信号在连线上的传输延时。 如果没有定义时延值,缺省时延为0。

verilog仿真文件例程

verilog仿真文件例程Verilog是一种硬件描述语言,用于描述数字电路和系统的行为,结构和功能。

仿真文件是使用Verilog语言编写的,用于验证和验证你的电路设计是否按预期工作的模拟文件。

下面是一个简单的Verilog仿真文件例程,以帮助您更好地理解如何编写和使用仿真文件:`module my_design_testbench;// 定义仿真时钟信号reg clk;// 定义要测试的信号reg input_signal;wire output_signal;// 被测试设计的实例化my_design dut (.clk(clk),.input(input_signal),.output(output_signal));// 定义仿真时钟行为always beginclk = 0;#5; // 延迟5个仿真时间单位clk = 1;#5; // 延迟5个仿真时间单位end// 定义输入信号行为always begininput_signal = 0;#10; // 延迟10个仿真时间单位input_signal = 1;#10; // 延迟10个仿真时间单位end// 定义仿真结束条件initial begin#50; // 延迟50个仿真时间单位后结束仿真$finish; // 结束仿真endendmodule`上面的例程展示了一个简单的测试台,在其中实例化了一个名为"my_design"的设计。

这个设计有一个时钟输入信号(clk),一个输入信号(input_signal),一个输出信号(output_signal)。

仿真时钟信号通过一个`always`块来控制,并在每次上升沿延迟一个固定的时间单位。

输入信号通过另一个`always`块控制,并在每个循环中切换两个不同的输入值。

仿真结束条件由`initial`块定义,其中仿真将在延迟50个时间单位后终止。

通过运行仿真文件,你可以观察到设计在给定的输入下产生的输出信号,并验证设计是否按照预期工作。

verilog仿真器原理

verilog仿真器原理

Verilog仿真器是一种软件工具,用于生成并模拟Verilog编写的数字逻辑电路设计。

它是通过将Verilog代码转换成一系列仿真指令来运行仿真器。

仿真指令通常包括读取输入信号,执行逻辑操作,计算输出信号等。

Verilog仿真器的工作原理可以分为以下几个步骤:

1. 编译:将Verilog源代码转换成仿真器可识别的二进制文件。

2. 加载:将编译后的仿真器文件加载到仿真器中。

3. 初始化:仿真器会将所有信号设置为默认初始值,并且执行激励文件中的操作。

4. 仿真:当仿真器接收到激励信号时,它会模拟电路设计的行为,并计算出输出信号。

5. 结束:仿真器会在仿真完成后输出仿真波形图和其他结果。

Verilog仿真器的优点在于可以模拟复杂的数字电路行为,而无需实际实现电路。

这使得设计人员可以在电路实际建立之前验证设计的正确性和可行性。

verilog仿真激励的写法

verilog仿真激励的写法Verilog仿真激励的写法是对待仿真电路进行功能验证的重要步骤。

在编写仿真激励时,我们需要定义输入信号的变化规律,以模拟各种场景下的电路行为。

本文将介绍一些常用的Verilog仿真激励的写法,并提供相关参考内容。

首先,我们需要定义一个时间轴,以确定信号变化的时序。

在Verilog中,我们可以使用`#`表示时间延迟,例如`#10`表示延迟10个时间单位。

要控制信号的变化,可以使用`always`关键字配合`@`符号来编写always块。

假设我们有一个简单的电路,包含一个4位输入信号`input`和一个2位输出信号`output`,我们可以通过仿真激励来验证电路的功能。

首先,在模块的顶层,我们需要定义输入和输出信号的端口。

可以使用`input`和`output`关键字进行定义,例如:```module top(input [3:0] input,output [1:0] output);```在仿真激励中,我们可以通过`initial`关键字来编写初始状态的代码。

例如,我们可以将输入信号初始化为`0`,并在2个时间单位后给输入信号赋予不同的值。

可以这样编写:```initial begininput = 4'b0000; // 初始化为0000#2;input = 4'b0101; // 在t=2时设置为0101end```上述代码中,`4'b0000`表示一个4位二进制数,初始状态将输入信号设置为`0000`。

之后,使用`#2`延迟2个时间单位,然后将输入信号设置为`0101`。

在仿真激励中,我们可以使用`always`块来控制信号的变化。

例如,我们可以定义一个时钟信号,每个时间单位将输入信号向左位移一位。

可以这样编写:```always #1 input = input << 1;```上述代码中,`<<`运算符表示位移操作,每个时间单位将输入信号向左位移1位。

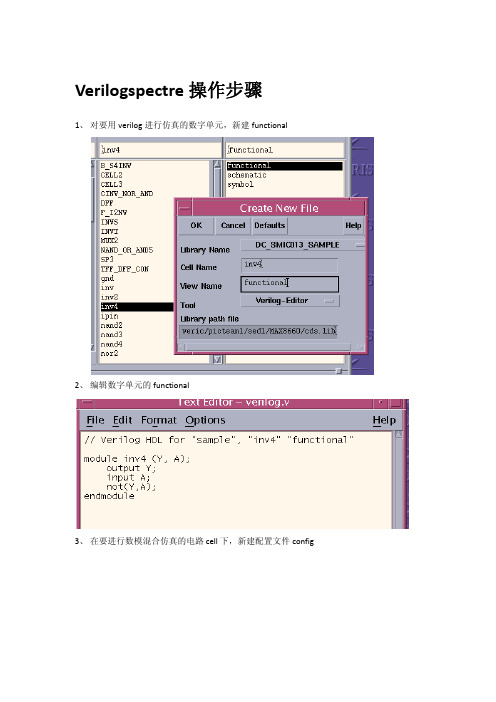

SpectreVerilog仿真使用方法

Verilogspectre操作步骤

1、对要用verilog进行仿真的数字单元,新建functional

2、编辑数字单元的functional

3、在要进行数模混合仿真的电路cell下,新建配置文件config

4、配置文件config建立后,自动弹出初始化配置窗口。

单击Browse,将config文件链接到

要数模混合仿真的电路原理图文件,点击OK保存。

5、点击Use Template… 选择要数模混合仿真的模板,这里选择spectreVerilog。

单击OK完

成初始化。

6、对要数模混合仿真的电路进行配置。

如下,将sample库内的数字单元设置用verilog仿

真,在view found栏内显示functional,表示其已经设置成数字仿真。

如果需要用模拟仿真,右击此栏,弹出如下子窗口,选择用schematic。

7、配置完成后单击保存,退出配置窗口。

双击config弹出如下窗口,上面表示打开配置文

件,下面表示打开原理图文件,这里已经配置完成,只打开原理图文件。

8、打开电路原理图后,点击tools‐> analog enviroment,弹出仿真对话框,点击setup,选

择simulator/Directory/Host…

9、弹出选择仿真器窗口,在simulator栏内选择spectreverilog作为仿真工具,点击OK。

自

动载入数模混合仿真环境。

接下来设置和spectre仿真相同,不再赘述。

verilog tb 仿真基本结构

verilog tb 仿真基本结构Verilog testbench simulation is an essential aspect of designing and verifying digital circuits. It provides a way to test the functionality of a design before implementing it in hardware. A well-designed testbench can help identify bugs and ensure that the design meets the required specifications. By simulating the behavior of the circuit under various conditions, designers can gain confidence in the correctness of their implementation.Verilog仿真测试台是设计和验证数字电路的一个重要方面。

它提供了一种在硬件中实施之前测试设计功能的方式。

一个设计良好的测试台可以帮助识别错误并确保设计符合要求的规格。

通过在各种条件下模拟电路的行为,设计人员可以增加对其实现正确性的信心。

The basic structure of a Verilog testbench includes the instantiation of the DUT (Design Under Test), the creation of input stimuli, and the monitoring of output signals. The DUT represents the component or module being tested, while the input stimuli drive the DUT and the output signals are compared against expected results. By setting upthis environment, designers can control the simulation and analyze the behavior of the DUT under different test scenarios.Verilog测试台的基本结构包括DUT(被测试设计)的实例化、输入刺激的创建和输出信号的监视。

定时器设计——Verilog代码及仿真实例

定时器设计——Verilog代码及仿真实例在Verilog中,我们可以使用定时器来生成一系列的时钟脉冲。

定时器通常由一个计数器和一个比较器组成,计数器用于计算时间的过程,比较器用于比较计数器的值是否达到了设定的阈值,如果达到了阈值,比较器会产生一个输出信号。

下面是一个简单的定时器的Verilog代码示例:```verilogmodule Timerinput clk, // 输入时钟input reset, // 复位信号output reg out // 输出信号reg [15:0] count; // 计数器,16位beginif (reset)count <= 0; // 复位计数器else if (count == 16'd9999)count <= 0; // 当计数器达到9999时复位elsecount <= count + 1; // 计数器加1endbeginif (count == 16'd9999)out <= 1'b1; // 当计数器达到9999时输出高电平elseout <= 1'b0;endendmodule```在这个例子中,定时器接收一个时钟信号`clk`和一个复位信号`reset`作为输入,产生一个输出信号`out`。

计数器`count`是一个16位的寄存器,用于记录时间的过程。

当复位信号为高电平时,计数器会被复位为0;当计数器达到9999时,会被自动复位为0。

输出信号`out`在计数器达到9999时变为高电平,否则为低电平。

下面是一个定时器的仿真实例,使用iverilog和gtkwave工具进行仿真。

假设我们的时钟频率为100MHz,我们希望定时器的时间间隔为10ms,即每当计数器达到9999时,输出信号变为高电平。

我们可以通过仿真来验证这个设计是否正确。

首先,我们需要创建一个测试文件testbench.v,用于生成时钟和复位信号,并将输出信号保存到一个文件中:```verilogmodule testbench;reg clk;reg reset;wire out;.clk(clk),.reset(reset),.out(out)initial beginclk = 1'b0;reset = 1'b1;reset = 1'b0;$finish;endalways beginclk = ~clk;endendmodule```然后,我们可以使用iverilog编译并运行仿真:``````最后,使用gtkwave打开生成的.vcd文件,我们可以观察到时钟和输出信号的波形:```gtkwave testbench.vcd```通过观察波形,我们可以验证定时器的设计是否正确。

verilog仿真流程

verilog仿真流程一、环境搭建在进行Verilog仿真前,首先需要搭建仿真环境。

常用的Verilog仿真工具有ModelSim、VCS等。

这里以ModelSim为例来介绍环境搭建步骤。

1. 下载ModelSim软件并安装到电脑中,根据软件的安装向导逐步操作即可。

2. 创建一个新的工程,选择File -> New -> Project来创建一个新的工程。

3. 在工程中添加需要仿真的Verilog文件,选择File -> Add to Project -> Existing File来添加Verilog文件。

4. 配置仿真波形,选择Simulate -> Start Simulation来开始仿真。

二、编写Verilog代码在搭建好仿真环境后,接下来就是编写Verilog代码。

Verilog是一种硬件描述语言,通常用来描述数字电路的行为。

Verilog代码由模块、端口和信号等组成,下面是一个简单的Verilog模块示例:```verilogmodule adder(input [7:0] a,input [7:0] b,output [8:0] sum);assign sum = a + b;endmodule```在这个示例中,我们定义了一个名为adder的模块,它有两个8位输入端口a和b,以及一个9位输出端口sum。

在模块体中,我们使用assign语句来实现a和b的加法运算,并将结果赋给sum。

三、编译Verilog代码在编写好Verilog代码后,需要对代码进行编译。

编译的目的是将Verilog代码转换成仿真可执行的二进制文件。

在ModelSim中,可以通过点击Compile按钮或者在命令行中输入vlog命令来进行编译。

```verilogvlog adder.v```这样就会生成一个adder.v文件,里面包含了编译后的二进制代码。

四、仿真测试在编译成功后,接下来就是对设计的Verilog模块进行仿真测试。

Verilog非阻塞赋值的仿真综合问题(转)

Verilog非阻塞赋值的仿真综合问题(转)在Verilog语言最难弄明白的结构中“非阻塞赋值”要算一个。

甚至是一些很有经验的工程师也不完全明白“非阻塞赋值”在仿真器(符合IEEE标准的)里是怎样被设定执行的,以及什么时候该用“非阻塞赋值”。

这篇文章将介绍怎样设定“非阻塞赋值”和“阻塞赋值”,给出了重要的使得编码可以被正确地综合的编码指导方针,和避免仿真竞争的编码风格细节。

1.0 介绍众所周知的逻辑建模方针是:* 在always 块里用“阻塞赋值”产生组合逻辑。

* 在always 块里用“非阻塞赋值”产生时序逻辑。

但是为什么?(外注:在实现组合逻辑的assign结构中,当然采用阻塞赋值语句否则的话编译工具会提醒你进行修改的。

)普通的回答是:那只是关于仿真的,即使不遵照上面的规则也照样可以产生正确的综合结果。

但问题是综合前的仿真结果也许会跟综合后的电路行为仿真不匹配。

要明白上述建模方针背后的原因,就必须明白“非阻塞赋值”和“阻塞赋值”它们的功能和时序安排(the functionality and schedulingof blocking and nonblocking assignments.)。

这篇文章将详细描述有关问题。

文章里将用到两个缩写形式:RHS(right-hand-side)和LHS(left-hand-side)。

前者指等式右边的表达式或者变量(RHS expression or RHS variable),后者指指等式左边的表达式或者变量(RHS expression or RHS variable)。

2.0 Verilog 仿真竞争条件IEEE Verilog Standard [2] 定义:“保证性的赋值描述”和“非保证性的赋值”描述分别用“非阻塞赋值”和“阻塞赋值”。

("Determinism", section 5.4.1;"Nondeterminism", section 5.4.2 & "Race conditions", section 5.5)IEEE Verilog 标准允许在同一仿真时间里赋值竞争的产生。

verilog仿真中激励文件中控制仿真结束的方法

Verilog仿真的激励文件中如何控制仿真结束是一个在数字电路设计和验证过程中非常重要的问题。

本文将探讨一些常用的方法和技巧,帮助读者更好地掌握这一关键技术。

1. 使用$finish系统任务Verilog语言提供了一个系统任务$finish,可以用来结束仿真过程。

当激励文件中的某个条件满足时,可以调用$finish任务,终止仿真过程。

这个条件可以是一个特定的时钟周期数,也可以是某个特定的状态达到。

2. 使用$stop系统任务除了$finish任务外,Verilog还提供了$stop任务来结束仿真过程。

$stop任务可以带一个整数参数,表示仿真结束的状态码。

这样可以在激励文件中根据需要来控制仿真结束的条件和状态。

3. 设计专用的结束条件在激励文件中,可以根据仿真的具体需求,设计专门的结束条件。

比如在测试一个模块的功能时,可以设置一个计数器,当某个特定的输入序列经过一定数量的时钟周期后,触发结束条件,终止仿真过程。

这种方法可以更灵活地控制仿真的结束条件。

4. 使用PLI/ VPI接口Verilog语言提供了PLI(Programming Language Interface)和VPI(Verilog Procedural Interface)接口,允许用户编写C/C++程序来控制仿真过程。

通过这些接口,用户可以在激励文件中调用自定义的C/C++函数,实现更加灵活和复杂的仿真结束条件和控制逻辑。

5. 结合仿真工具的特性不同的仿真工具可能有不同的特性和扩展功能,可以根据具体的仿真工具来选择合适的方法和技巧来控制仿真结束。

比如一些仿真工具提供了丰富的命令行控制接口,可以通过命令行参数或者特定的命令来控制仿真的结束条件。

总结在Verilog仿真中,控制仿真结束的方法有很多种,可以根据具体的需求和场景来选择合适的方法和技巧。

需要特别注意的是,在设计结束条件和控制逻辑时,要考虑到仿真的完整性和准确性,以及仿真结果的可靠性。

第5讲 Verilog HDL行为建模方法

10

• 非阻塞赋值使用“<=”作为赋值符。

x = 0与y = 1同时执行 仿真0时刻执行

仿真时刻15执行

仿真时刻10执行 仿真0时刻执行

注意:不要在同一个always块中混合使用阻塞和非阻塞赋值语句。 硬件描述语言

11

• •

非阻塞赋值语句的应用 对程序:

• 有如下的特点: 1.在每个时钟上升沿到来时读取in1,in2,in3和reg1,计算右侧表达式的值; 2.对左值的赋值由仿真器调度到相应的仿真时刻,延迟时间由语句中内嵌的延迟 值确定。在本例中,对reg1的赋值需要等一个时间单位,对reg2的赋值需要等到 时钟信号下降沿到来的时刻,对reg3的赋值需要等一个时间单位; 3.每个赋值操作在被调度的仿真时刻完成。注意,对左侧变量的赋值使用的是由 仿真器保存的表达式“旧值”。在本例中,对reg3赋值使用的是reg1的“旧值” ,而不是在此之前对reg1赋予的新值,reg1的“旧值”是在赋值事件调度时由仿 真器保存的。

尽量不要使用零延迟控制 具有零延迟,语句被最后执行,仿 真0时刻结束时,x和y的值都为1, 但它们的执行顺序是不确定的。

硬件描述语言

17

5.4 基于事件的时序控制

• 在Verilog中,事件是指某一个寄存器或线网变量的值发生了变化。 Verilog提供了4种类型的事件控制:常规事件控制、命名事件控制、 OR(或)事件控制和电平敏感时序控制。 • 常规事件控制 事件控制使用符号@来说明,语句继续执行的条件是信号的值发生变化 、发生正向跳变和负向跳变。关键字posedge用于指明正向跳变, negedge用于指明负向跳变。

硬件描述语言

20

• 如果组合逻辑块语句的输入变量很多,那么编写敏感列表 会很繁琐并且容易出错。针对这种情况,Verilog提供了另 外两个特殊的符号:@*和@(*),它们都表示对其后语句 块中的所有输入变量的变化是敏感的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

测试程序TestBench 测试程序

一个完整的简单例子 test fixture

•Hale Waihona Puke 被测试器件DUT是一个二选一多路器。测试程序(test fixture)提 是一个二选一多路器。测试程序 被测试器件 是一个二选一多路器 提 供测试激励及验证机制。 供测试激励及验证机制。 Test fixture使用行为级描述,DUT采用门级描述。下面将给出 使用行为级描述, 采用门级描述。 使用行为级描述 采用门级描述 Test fixture的描述、DUT的描述及如何进行混合仿真。 的描述、 的描述及如何进行混合仿真。 的描述 的描述及如何进行混合仿真

4.$finish与$stop . 与

系统任务$finish与$stop用于对仿真过程进行控制,分 与 用于对仿真过程进行控制, 系统任务 用于对仿真过程进行控制 别表示结束仿真和中断仿真。 别表示结束仿真和中断仿真。 $finish与$stop 的使用格式如下: 的使用格式如下: 与 $stop; $stop(n); $finish; $finish(n); n是$finish和$stop的参数,n 可以是 、1、2等值,分 的参数, 可以是0、 、 等值 等值, 是 和 的参数 别表示如下含义。 别表示如下含义。 0:不输出任何信息; :不输出任何信息; 1:给出仿真时间和位置; :给出仿真时间和位置; 2:给出仿真时间和位置,还有其他一些运行统计数据。 :给出仿真时间和位置,还有其他一些运行统计数据。

例子中, s说明为reg类数据 说明为reg类数据。 例子中,a, b, s说明为reg类数据。reg 类数据是寄存器类数据信号, 类数据是寄存器类数据信号,在重新赋值 前一直保持当前数据。 前一直保持当前数据。 用于指示等待5个时间单位。 #5 用于指示等待5个时间单位。 是结束仿真的系统任务。 $finish是结束仿真的系统任务。

为什么没 有端口? 有端口?

// Instantiate modules

// Apply stimulus

// Display results

由于testfixture是最顶层模 是最顶层模 由于 不会被其它模块实例化。 块,不会被其它模块实例化。 因此不需要有端口。 因此不需要有端口。

endmodule

格式控制符

格式控制符 %h或%H 或 %d或%D 或 %o或 %o或%O %b或%B 或 %c或%C 或 %v或%V 或 %m或%M 或 %s或%S 或 %t或%T 或 说明 转义字符 以16进制形式显示 进制形式显示 \n 以10进制形式显示 进制形式显示 \t 8进制形式显示 以8进制形式显示 以2进制形式显示 进制形式显示 以ASCII字符形式显示 字符形式显示 显示net型数据的驱动强度 型数据的驱动强度 显示 显示层次名 以字符串形式输出 以当前的时间格式显示 \\ \“ \ ddd %%

完整的Test Fixture

module testfixture; 结果输出 // 数据类型说明 0 o= 0 a= 0 b= 1 reg a, b, s; wire o; 5 o= 0 a= 0 b= 0 // MUX实例化 实例化 10 o= 1 a= 0 b= 1 MUX2_1 mux (o, a, b, s); // 施加激励 15 o= 1 a= 1 b= 1 initial begin a = 0; b = 1; s = 0; #5 b = 0; #5 b = 1; s = 1; #5 a = 1; #5 $finish; end // 显示结果 initial $monitor($time,," o=%b a=%b b=%b s=%b", o, a, b, s); endmodule

s= 0 s= 0 s= 1 s= 1

系统任务与系统函数

系统任务和系统函数一般以符号“ 开头 例如: 开头。 ◆ 系统任务和系统函数一般以符号“$”开头。例如: $monitor,$finish等。 , 等 使用不同的Verilog仿真工具(如:VCS、Verilog-XL、 仿真工具( ◆ 使用不同的 仿真工具 、 、 ModelSim等)进行仿真时,这些系统任务和系统函数在 等 进行仿真时, 使用方法上可能存在差异,应根据使用手册来使用。 使用方法上可能存在差异,应根据使用手册来使用。 一般在intial或always过程块中,调用系统任务和系统 过程块中, ◆ 一般在 或 过程块中 函数。 函数。 用户可以通过编程语言接口( ◆ 用户可以通过编程语言接口(PLI)将自己定义的系统 ) 任务和系统函数加到语言中,以进行仿真和调试。 任务和系统函数加到语言中,以进行仿真和调试。

Test Fixture — 如何说明实例

module MUX2_1 (out, a, b, sel); // Port declarations module testfixture; output out; // Data type declaration input a, b, sel; wire out, a, b, sel; wire sel_, a1, b1; // Instantiate modules // The netlist MUX2_1 mux (o, a, b, s); not (sel_, sel); and (a1, a, sel_); // MUX2_1 mux (.out(o), .a(a), .b(b), .sel(s)); and (b1, b, sel); // Apply stimulus or (out, a1, b1); endmodule // Display results MUX的实例化语句包括: MUX的实例化语句包括: 的实例化语句包括 • 模块名称:与引用模块相同 模块名称: endmodule • 实例名称:任意,但要符合标记命名规则 实例名称:任意, • 端口列表:与引用模块的次序相同 端口列表:

•

// The netlist not (sel_, sel); and (a1, a, sel_); and (b1, b, sel); or (out, a1, b1); endmodule 已定义的 Verilog基 基 本单元的 实例

Test Fixture template

module testfixture; // Data type declaration

Test fixture 激励描述

module testfixture; // Data type declaration reg a, b, s; wire o; // MUX instance MUX2_1 mux (o, a, b, s); // Apply stimulus initial begin a = 0; b = 1; s = 0; #5 b = 0; • #5 b = 1; s = 1; #5 a = 1; #5 $finish; end • // Display results • endmodule Time 0 5 10 15 Values a b s 0 1 0 0 0 0 0 1 1 1 1 1

6.$random 和文件操作 .

$random: : 产生随机数的系统函数,每次调用该函数将返回一个32 产生随机数的系统函数,每次调用该函数将返回一个 位的随机数,该随机数是一个带符号的整数。 位的随机数,该随机数是一个带符号的整数。

一般用法为: 一般用法为: $random % b 其中b>0,它给出了一个范围在0~b-1之间的随机数。 ,它给出了一个范围在 之间的随机数。 其中 之间的随机数 $random%15通过位拼接操作,产生一个0~14之间的随机数。 通过位拼接操作,产生一个 之间的随机数。 通过位拼接操作 之间的随机数

3.$time与$realtime . 与

$time、$realtime是属于显示仿真时间标度的系统函数。 、 是属于显示仿真时间标度的系统函数。 是属于显示仿真时间标度的系统函数 这两个函数被调用时, 这两个函数被调用时,都返回当前时刻距离仿真开始时 刻的时间量值。 刻的时间量值。 $time 函数以 位整数值的形式返回模拟时间, 函数以64位整数值的形式返回模拟时间 位整数值的形式返回模拟时间, $realtime 函数则以实数型数据返回模拟时间。 函数则以实数型数据返回模拟时间。

文件操作: 文件操作:

语言类似, 也提供了很多文件输出类的系统任务, 与c 语言类似,Verilog也提供了很多文件输出类的系统任务,可 也提供了很多文件输出类的系统任务 将结果输出到文件中。这类任务有: 将结果输出到文件中。这类任务有: $fopen用于打开某个文件并准备写操作, 用于打开某个文件并准备写操作, 用于打开某个文件并准备写操作 $fclose用于关闭文件, 用于关闭文件, 用于关闭文件 $fdisplay、$fwrite、$fmonitor等系统任务则用于把文本写入文 、 、 等系统任务则用于把文本写入文 件。

转义字符

说明 换行 TAB键 键 符号\ 符号 符号“ 符号“ 八进制数ddd对应的 对应的ASCII字符 八进制数 对应的 字符 符号% 符号

2.$monitor与$strobe . 与

$monitor、$strobe与$display、$write一样也是属 、 与 、 一样也是属 于输出控制类的系统任务, 于输出控制类的系统任务,$monitor与$strobe都提供 与 都提供 了监控和输出参数列表中字符或变量的值的功能,其使 了监控和输出参数列表中字符或变量的值的功能, 用格式为: 用格式为: $monitor(“格式控制符”,输出变量名列表); 格式控制符” 输出变量名列表 格式控制符 $strobe(“格式控制符”,输出变量名列表); 格式控制符” 输出变量名列表 格式控制符 这里的格式控制符、输出变量名列表与 这里的格式控制符、输出变量名列表与$display和 和 $write中定义的完全相同。 中定义的完全相同。 中定义的完全相同