VHDL实验(完整版)

VHDL实验报告

VHDL实验报告《创新实验》实验报告—基于vhdl的编程和硬件实现一、实验目的1.2.3.4. 熟悉和掌握硬件描述语言vhdl的基本语法及编写;掌握软件xilinx ise 10.1的使用;熟悉sdz-6电子技术实验箱的使用;了解节拍脉冲发生器等基本电路的实现;5. 了解八位二进制计数器的功能与设计;6. 学习键盘和七段数码管显示的控制和设计。

二、实验内容1. xilinx ise 10.1软件的使用;2. 节拍脉冲发生器等基本电路的实现;3. 八位二进制计数器的实现4. 键盘扫描及显示的实现三、实验器材1、 pc机2、 sdz-6电子技术实验箱3、正负5v电源4、 i/o接口线四、软件的使用在安装xilinx10.1软件时,需要一个id号,其实这个id号是可以重复使用的,几个同学在官网注册后就可以共享id号了。

安装完成之后就可以使用这个软件编写相应的vhdl的程序。

1.新建工程file—>new project 弹出下面的对话框输入工程名后单击next。

然后根据本实验的实验箱进行以下设置。

以后的步骤一般都是单击next(有些资料上会介绍有些这些步骤的具体功能,但对于本实验不必用到),最后单击finish,完成新建一个工程。

在窗口的左边会出现刚刚新建的工程,如下: 2.新建一个vhdl的源文件。

在上图中,右击工程选择new source ,弹出如下对话框。

在对画框的左边选择vhdl module,输入文件的名字(改名字最好是你定义的实体的名字)。

单击next。

出现下面的对话框。

该对话框主要是对外部端口的编辑。

可以直接跳过,即单击next,在源文件上编辑端口。

然后在接下来的对话框中单击finish。

完成建立一个源文件。

窗口右边就会出现刚才编辑的源文件。

3.编写和编译代码将事先编好的代码复制到源文件里,然后保存文件。

选中左边的文件名,在窗体的左边出现如下编辑文档内容。

选择synthesize —xst—》check syntax,双击check syntax,开始编译源文件。

VHDL实验报告

6

#50 S1=1;S2=0; #50 A=0;B=0;C=1;D=0; #50 S1=0;S2=1; #50 A=1;B=0;C=0;D=1; #200 $stop; end MUX41b MUX41b1 (.A(A),.B(B),.C(C),.D(D),.S1(S1),.S2(S1),.Y(Y));//元件例化 endmodule If else 方法仿真图:

实验一 半加器电路的设计

一.实验目的 (1)掌握 Modelsim 软件的编译、仿真方法 (2)熟练运用 Modelsim 软件进行 VHDL 程序设计开发 (3)掌握基于 Modelsim 的组合逻辑电路设计方法 (4)利用 VHDL 的逻辑表达式描述门电路 (5)利用 VHDL 的代码完成半加器设计 二.实验内容 1.实验要求:设计一个两位二进制半加器,半加器只考虑了两个加数本身,没有考虑由低位 来的进位。 2.半加器的输入为 A 和 B。输出为 SO 和 CO。 使用 Verilog HDL 程序实现上述实验内容,并使用 modelsim 仿真 半加器主程序为: module adder(A,B,SO,CO); input A,B; output SO,CO; assign SO=A^B; //和值数据输出 assign CO=A&B; //进位数据输出 endmodule 测试程序为: `timescale 1ns/1ns //时间精度 `include "adder.v"; module addertest; reg A,B; //输入变量类型定义 wire SO,CO; //输出变量类型定义 initial begin A=0;B=0; #100 A=0;B=1 ; #100 A=1;B=1 ; #100 A=1;B=0 ; #100 $stop; end adder adder1(.SO(SO),.CO(CO),.A(A),.B(B)); endmodule

VHDL数码管动态扫描显示实验完整版

学生实验报告实验课名称:VHDL硬件描述语言实验项目名称:七段数码管译码扫描显示专业名称:电子科学与技术班级:***学号:***学生姓名:***教师姓名:***__2020__年_11_月_06_日组别_____________________同组同学_______________________实验日期_____年___月___日实验室名称______________成绩_____一、实验名称:七段数码管译码扫描显示二、实验目的与要求:实验目的:通过对译码和串行扫描电路的设计,理解多位数码管串行扫描输出的工作原理以及七段数码管的译码以及串行扫描输出的设计方法。

实验要求:通过VHDL编程,实现7段数码管的译码输出,并通过所设计的串行扫描控制,对8个7段数码管扫描输出,要求8个数码管从左到右分别显示“1”、“2” 、“3” 、“4” 、“5” 、“6” 、“7” 、“8”,并且每一位都对应有一个显示控制端,当控制端为高电平时,对应数码管点亮,否则熄灭。

具体接口如下所示:clk:时钟输入端,此信号是串行扫描的同步信号。

data_control[7..0]:8个分别控制数码管显示的输入信号;led_addr[7..0]:对8个数码管进行串行扫描的输出控制信号;seg7_data[6..0]:驱动7段数码管各显示段的输出信号;首先在QuartusII上进行功能和时序仿真,之后通过器件及其端口配置下载程序到SOPC开发平台中。

在硬件实现中,要求:1. 用实验平台的8个数码管输出显示(共阴接法),并且用其下方的8个按键分别控制对应数码管的显示与否。

注:采用I/O模式5实现输入控制和输出显示方式。

为了实现数码管的串行扫描,必须把数码管连接成串行控制输出电路。

2. 扫描所用的时钟信号采用实验平台的clock0时钟资源:可以通过跳线选择不同的时钟频率,此频率不能选择的太高或太低,频率太低将不满足人眼视觉暂留特性的要求,频率太高,器件速度跟不上,地址和数据无法在1个时钟周期大部分时间内对准,造成显示模糊不清。

VHDL实验

班级:2009211411 学号:09211999 姓名:陈东东三十进制和六分频计数电路设计1.实验目的:(1)计数器设计设计一个三十进制计数器,要求用两位七段数码管显示(计时电路)(2)分频电路设计,六分频电路设计,在前面三十进制计数器基础上设计六分频电路,并同时用七段数码管显示。

2.实验内容和原理:采用几个触发器的状态,按照一定规律随时钟变化来记忆时钟的个数。

一个4位二进制计数器可以构成1位十进制计数器,即1位BCD计数器。

2位十进制计数器连起来可以构成一个30进制计数器.当时钟个数记到30时,十位和各位都变为0000,否则的话,每来一个时钟,个位就加1,当各位为1001时,时钟到来十位加1.再分别将个位十位bcd码转换为七段数码管对应的数字。

校正函数:function zhuan(j:in std_logic_vector(3 downto 0))return std_logic_vector isvariable k:std_logic_vector(6 downto 0);begincase j iswhen "0000"=>k:="1111110";--不显示00首两位表示数码管是(0)否(1)显示when "0001"=>k:="0110000";when "0010"=>k:="1101101";when "0011"=>k:="1111001";when "0100"=>k:="0110011";when "0101"=>k:="1011011";when "0110"=>k:="0011111";when "0111"=>k:="1110000";when "1000"=>k:="1111111";when "1001"=>k:="1110011";when others=>k:="1000000";end case;return(k);end zhuan;3.程序框图:机器频率=》分频得到目的频率=》对上升沿个数计数=》十位各位对上升沿到来时相应的变化=》BCD码与七段数码管的转化关系=》六分频与上升沿的变化关系。

VHDL实验报告实验一

实验一:3位比较器一、实验目的1、熟悉Xilinx ISE/ModelSim软件,掌握软件的VHDL程序输入、程序编译和程序仿真操作;2、学习利用VHDL语言设计三位比较器控制电路程序;3、根据三位比较器的原理设计VHDL程序,使得a,b为三位信息的输入端口,若a>b 则c=1。

否则c=0;二、VHDL源程序:●Compare3源代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity compare3 isport (a:in std_logic_vector(2 downto 0);b:in std_logic_vector(2 downto 0);c:out std_logic);end compare3;architecture Behavioral of compare3 isbeginprocess (a,b)beginif(a>=b)thenc<='1';elsec<='0';end if;end process;end Behavioral;●三位比较器testbench代码:LIBRARY ieee;USE ieee.std_logic_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--USE ieee.numeric_std.ALL;ENTITY tbench1 ISEND tbench1;ARCHITECTURE behavior OF tbench1 IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT compare3PORT(a : IN std_logic_vector(2 downto 0);b : IN std_logic_vector(2 downto 0);c : OUT std_logic);END COMPONENT;--Inputssignal a : std_logic_vector(2 downto 0) := "000";signal b : std_logic_vector(2 downto 0) := "000";--Outputssignal c : std_logic;-- No clocks detected in port list. Replace <clock> below with -- appropriate port nameBEGIN-- Instantiate the Unit Under Test (UUT)uut: compare3 PORT MAP (a => a,b => b,c => c);-- Clock process definitions-- Stimulus processstim_proc: processbegin-- hold reset state for 100 ns.wait for 10 ns;a <= "010";b <= "001";wait for 10 ns;a <= "110";b <= "111";wait for 10 ns;a <= "011";b <= "111";wait for 10 ns;a <= "110";b <= "101";wait for 10 ns;a <= "110";b <= "000";wait for 10 ns;a <= "100";b <= "101";wait for 1000 ns;-- insert stimulus herewait;end process;END;三、实验结果与分析●实验仿真波形图●实验结果分析由波形图观察可得该VHDLd代码实现了比较的功能,在输入a,b值大小不同的情况下,成许进行比较均能的出结果并给C赋值,当a>b,c=1, 反之c=0。

VHDL多路波形发生器实验报告

VHDL多路波形发生器实验报告一、基本要求:1、对输入时钟信号进行分频,实现三路互差120°的信号。

2、实现输出信号的占空比控制clk: 输入时钟信号reset: 同步复位信号(低电平有效)div: 输入分频控制信号(注意:6n分频)ctrl: 占空比控制信号ctrl=1时, 占空比为1:1ctrl=2时, 占空比为1:2ctrl=3时, 占空比为2:1A,B,C: 三路输出信号二、设计思路:1.实验为6n分频,用变量s来控制,0~6n-1这六个数,当时钟信号每来一个上升沿时加1,当为6n-1时清零;2.定义N为常量,通过改变N的值改变分频;3.ctrl值不同时,占空比不同,用case语句控制,ctrl分别为01,10,11和其他;4.具体波形的实现用if语句,当占空比为1时,A输出信号在s=0和s=3*n时翻转,B输出信号在s=2*n和s=5*n时翻转,C输出信号在s=4*n和s=n的时候翻转。

当占空比为1:2时,A输出信号在s=0和s=2*n时翻转,B输出信号在s=2*n和s=4*n时翻转,C输出信号在s=4*n和s=0的时候翻转。

当占空比为2:1时,A输出信号在s=0和s=4*n时翻转,B输出信号在s=2*n和s=0时翻转,C输出信号在s=4*n和s=2*n的时候翻转;5.在占空比为1和1:2时,C输出信号应比B慢120度,但是实际输出超前B,所以要对C输出进行反相;同理,在占空比为2:1时,要对B、C分别进行反向。

6.用if语句判断是否复位,若非,则执行case语句。

三、流程图:四、源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity top isport(clk,reset:in std_logic;ctrl:in std_logic_vector(1 downto 0);A,B,C:out std_logic);end top ;architecture rel of top issignal temp1,temp2,temp3,temp4,temp5 : std_logic; constant N: integer:=1;signal s:integer range 0 to 6*N-1 ;beginprocess(clk,reset,ctrl)beginif (reset='0') thentemp1<='0';temp2<='0';temp3<='0';temp4<='0';temp5<='0';s<=0;elsecase ctrl iswhen "01"=>if (clk 'event and clk='1') thenif s=6*N-1 thens<=0;elses <= s+1;end if;if s=0 thentemp1<= not temp1;end if;if s=3*N thentemp1<= not temp1;end if;if s=2*N thentemp2<= not temp2;end if;if s=5*N thentemp2<= not temp2;end if;if s=4*N thentemp4<= not temp4;end if;if s=N thentemp4<= not temp4;end if;end if;temp3<= not temp4;when "10"=>if (clk 'event and clk='1') thenif s=6*N-1 thens<=0;elses <= s+1;end if;if s=0 thentemp1<= not temp1;end if;if s=2*N thentemp1<= not temp1;end if;if s=2*N thentemp2<= not temp2;end if;if s=4*N thentemp2<= not temp2;end if;if s=4*N thentemp4<= not temp4;end if;if s=0 thentemp4<= not temp4;end if;end if;temp3<= not temp4;when "11"=>if (clk 'event and clk='1') thenif s=6*N-1 thens<=0;elses <= s+1;end if;if s=0 thentemp1<= not temp1;end if;if s=4*N thentemp1<= not temp1;end if;if s=2*N thentemp5<= not temp5;end if;if s=0 thentemp5<= not temp5;end if;if s=4*N thentemp4<= not temp4;end if;if s=2*N thentemp4<= not temp4;end if;end if;temp2<= not temp5;temp3<= not temp4;when others=>temp1<='0';temp2<='0';temp3<='0';end case;end if;end process;A<=temp1;B<=temp2;C<=temp3;end rel;五、仿真波形:整体波形:当ctrl=1 当ctrl=2 当ctrl=3复位当ctrl=其他:六、实验过程遇到的问题:在程序设计时,开始不知该怎样使A,B,C互差120度,开始是想通过定义一个变量,每来一个上升沿加1,从0开始,A路信号除3n 取余为0则翻转,B路信号除3n取余为1则翻转,C路信号除3n取余为2则翻转,我觉得这样的想法应该没有错,可是实际却调不出来,可能是某处逻辑有问题,后来就模仿老师给的6分频程序,设计了现在的程序。

VHDL实验报告

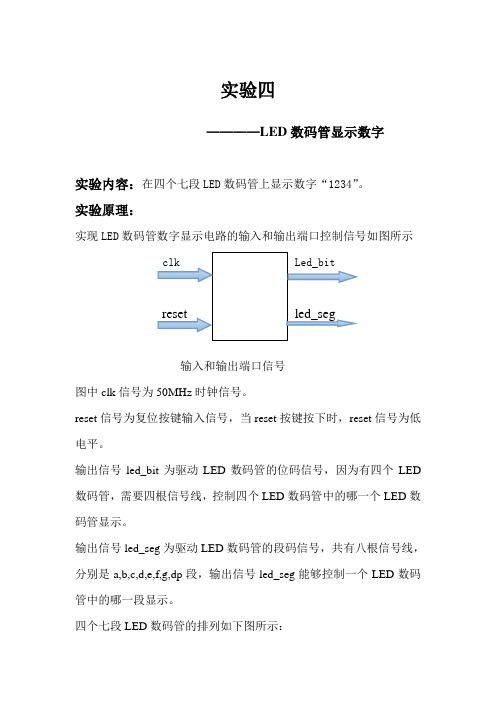

实验四————LED数码管显示数字实验内容:在四个七段LED数码管上显示数字“1234”。

实验原理:实现LED数码管数字显示电路的输入和输出端口控制信号如图所示clkLed_bit reset led_seg输入和输出端口信号图中clk信号为50MHz时钟信号。

reset信号为复位按键输入信号,当reset按键按下时,reset信号为低电平。

输出信号led_bit为驱动LED数码管的位码信号,因为有四个LED 数码管,需要四根信号线,控制四个LED数码管中的哪一个LED数码管显示。

输出信号led_seg为驱动LED数码管的段码信号,共有八根信号线,分别是a,b,c,d,e,f,g,dp段,输出信号led_seg能够控制一个LED数码管中的哪一段显示。

四个七段LED数码管的排列如下图所示:四个LED数码管LED数码管采用共阳极发光二极管,如下图所示,需要点亮数码管中的某一段时,应该在对应段的段码信号输出低电平。

共阳极LED数码管由于每个LED数码管有八个发光二极管,八个发光二极管同时导通时需要提供比较大的电流,需要给共阳极加驱动电路,如下图所示,当需要某一LED数码管显示数字时,就给该行的控制信号led_bit(i)提供一个低电平信号。

共阳极LED数码管的阳极驱动电路原理图实验内容:本次实验采用了两个进程:1.scanclk_get:获取扫描时序控制信号2.led_selest_get:选择数码管并显示数字流程图:Clknum scan_cntr reset led_bit<3:0>源代码:library IEEE;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity EXP4_M isport(clk,rst:in std_logic;led_bit:out std_logic_vector(3 downto 0); led_seg:out std_logic_vector(7 downto 0)); end EXP4_M;进程scanclk_get 产生LED 数码管扫描时序控制电路 Led_select_d isplay 进程选择要显示的数据和对应的数码管 七段译码器architecture Behavioral of EXP4_M issignal scanclk:std_logic_vector(17 downto 0);beginscanclk_get:process(clk,rst)beginif rst='0' thenscanclk<=(others=>'0');elsif rising_edge(clk) thenscanclk<=scanclk+1;end if;end process scanclk_get;led_select_display:process(scanclk)begincase scanclk(17 downto 16) iswhen "00" =>led_bit<="1110";led_seg<="10011111" ;when "01"=>led_bit<="1101";led_seg<="00100101" ;when "10"=>led_bit<="1011";led_seg<="00001101" ;when "11"=>led_bit<="0111";led_seg<="10011001" ;when others =>null;end case;end process led_select_display;end Behavioral;UCF文件:net "clk" loc =Y11;net "rst" loc =J3;net "led_bit(0)" loc =M5;net "led_bit(1)" loc =M4;net "led_bit(2)" loc =M3;net "led_bit(3)" loc =M2;net "led_seg(0)" loc =R4;net "led_seg(1)" loc =T3;net "led_seg(2)" loc =T2;net "led_seg(3)" loc =T1;net "led_seg(4)" loc =N4;net "led_seg(5)" loc =N3;net "led_seg(6)" loc =N2;net "led_seg(7)" loc =N1;实验结果:实验箱数码管依次显示“1234”。

VHDL实验报告汇总

实验一4选一多路选择器一:实验目的及实验环境目的1、熟悉ModelSim SE 6.5c的verilog 的文本设计流程,组合电路的设计、仿真和测试。

2、用verilog语言完成设计4选一多路选择器。

3、熟悉文本输入及仿真步骤。

4、初步了解可编程器件设计的全过程。

环境1、P C 机一台2、M odelSim SE 6.5c二. 实验内容1、用verilog语言完成设计4选一多路选择器,2、用结构建模及数据流建模两种方法实现。

3、对于所设计的程序进行编译,检查纠错。

4、程序完善之后进行程序的仿真并进行波形的记录与分析三.实验步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真四.运行结果五.总结本次实验让我更加的熟悉modelsim使用方法,以及使用时应该注意的问题。

在试验中也学习到了Verilog语法。

在实验中我们应该注意verilog的格式要求,在用编程语言编程的时候,要自习留意语法标准,整理好逻辑思维的同时保证格式的正确。

否则就会浪费大量的时间来完成实验。

试验开始到结束这一过程中,我遇到了很多困难,后来都在同学的提醒和帮助下克服了。

相信有了这次对这个语言和这个软件的接触,我们都有了更加深入的理解。

六.源代码module mux41(a,b,c,d,s1,s0,out);input[1:0] a,b,c,d;input s1,s0;output[1:0] out;reg[1:0] out;always @(a or b or c or d or s1 or s0)begin :mux41case({s1,s0})2'b00: out<=a;2'b01: out<=b;2'b10: out<=c;2'b11: out<=d;default: out=a;endcaseendendmodulemodule sti;reg[1:0] a,b,c,d;reg s0,s1;wire[1:0] out;mux41 dtg(a,b,c,d,s0,s1,out);initialbegina=3'd0;b=3'd1;c=3'd2;d=3'd3;s0=0;s1=0;#100 a=3'd0;b=3'd1;c=3'd2;d=3'd3;s0=0;s1=1;#100 a=3'd0;b=3'd1;c=3'd2;d=3'd3;s0=1;s1=0;#100 a=3'd0;b=3'd1;c=3'd2;d=3'd3;s0=1;s1=1;endendmodule实验二、Verilog HDL设计分频器及计数器一.实验目的及实验环境1)实验目的1、掌握较复杂数字电路或系统的纯Verilog HDL实现方法;2、体会纯Verilog HDL语言输入设计与原理图输入设计的差别;3、更加熟练的使用modelsim软件;2)实验环境计算机一台,使用modelsim软件进行实验仿真3)实验内容1、使用modelsim设计二分频器;2、使用modelsim设计模8计数器;三.测试数据及运行结果1、分频器正常测试数据(3组)及运行结果;2、计数器正常测试数据(3组)及运行结果通过本次实验,进一步熟悉并加深了对verilong语言的认识,初步运用并熟悉了整个程序及操作,加深对分频器的理解。

VHDL实验报告

年月日VHDL实验报告学院专业学号姓名实验1 译码器设计一、实验原理1、译码器是数字系统中常用的组合逻辑电路,常用于地址译码。

74LS138是最常用的一种小规模集成电路,它有3个二进制输入端和8个译码输出端。

表1.1是它的真值表。

表1.1 3-8 译码器真值表2、普通的LED数码管由7段和一个点组成,使用它进行显示,需要译码驱动。

本实验实现一个七段LED显示译码电路。

为了实验方便,在译码之前加入一个4位二进制加法计数器,当低频率的脉冲信号输入计数器后,由7段译码器将计数值译为对应的十进制码,并由数码管显示出来。

图1.1为此电路的原理图。

图1.1 7段LED译码显示电路二、实验内容1、设计一个4-16译码器。

2、设计轮流显示表1.2所示字符的程序。

表1.2 字母显示真值表3、通过仿真,观察设计的正确性。

4、下载、验证设计的正确性。

三、源程序1、4-16译码器。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decode ISPORT( d0, d1, d2,d3, s1 ,s2 ,s3:IN STD_LOGIC;Y : OUT STD_LOGIC_VECTOR ( 15 DOWNTO 0 ) );END decode;ARCHITECTURE rtl OF decode ISSIGNAL indata : STD_LOGIC_VECTOR ( 3 DOWNTO 0 );BEGINIndata <= d3 & d2 & d1 & d0 ;PROCESS ( indata, s1, s2, s3 )BEGINIF (s1 ='1' AND s2='0' AND s3 = '0' ) THENCASE indata ISWHEN "0000" => Y <= "1111111111111110" ;WHEN "0001" => Y <= "1111111111111101" ;WHEN "0010" => Y <= "1111111111111011" ; WHEN "0011" => Y <= "1111111111110111" ;WHEN "0100" => Y <= "1111111111101111" ;WHEN "0101" => Y <= "1111111111011111" ;WHEN "0110" => Y <= "1111111110111111" ;WHEN "0111" => Y <= "1111111101111111" ;WHEN "1000" => Y <= "1111111011111111" ;WHEN "1001" => Y <= "1111110111111111" ;WHEN "1010" => Y <= "1111101111111111" ; WHEN "1011" => Y <= "1111011111111111" ;WHEN "1100" => Y <= "1110111111111111" ;WHEN "1101" => Y <= "1101111111111111" ;WHEN "1110" => Y <= "1011111111111111" ;WHEN "1111" => Y <= "0111111111111111" ;WHEN OTHERS=> NULL;END CASE;ELSEY <= "1111111111111111" ;END IF;END PROCESS;END rtl;2、轮流显示表1.2所示字符的程序。

VHDL实验报告

VHDL实验报告5090309160 庄炜旭实验三. 4位可逆计数器,4位可逆二进制代码-格雷码转换器设计一.实验目的学习时序电路的设计,仿真和硬件测试,进一步熟悉VHDL设计技术1. 学习4位可逆计数器的设计2. 学习4位可逆二进制代码-格雷码转换器设计二.实验内容设计4位可逆计数器,及4位可逆二进制代码-格雷码转换器,并仿真,下载。

[具体要求]1.4位可逆计数器a)使用CLOCK_50作为输入时钟,其频率为50MHz(对于频率大于50Hz的闪烁,人眼会看到连续的光),因而,对其进行225的分频后,再用于时钟控制。

(可利用实验一)b)使用拨码开关SW17作为模式控制,置‘1’时为加法计数器,置‘0’时为减法计数器,同时使用LEDR17显示SW17的值。

c)使用KEY3作为异步复位开关(按下时为0,不按为1),当为加法计数器时,置“0000”,当为减法计数器时,置“1111”。

d)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

2.4位可逆二进制代码――格雷码转换器a)使用拨码开关SW17作为模式控制,置‘1’时为二进制代码―>格雷码转换,置‘0’时为格雷码―>二进制代码,同时使用LEDR17显示SW17的值。

b)使用拨码开关SW3, SW2, SW1, SW0作为输入的被转换数,SW3为高位,SW0为低位。

c)使用LEDR3,LEDR2,LEDR1,LEDR0作为转换后的输出结果显示,LEDR3为高位,LEDR0为低位。

三.管脚设定SW[0]PIN_N25SW[1]PIN_N26SW[2]PIN_P25SW[3] PIN_AE14SW[17] PIN_V2LEDR[0] PIN_AE23LEDR[1] PIN_AF23LEDR[2] PIN_AB21LEDR[3] PIN_AC22LEDR[17] PIN_AD12KEY[3] PIN_W26CLOCK_50 PIN_N2四.相关知识二进制代码与格雷码相互转换格雷码(Gray Code,简称G码)是典型的循环码,它是由二进制码(Binary,简称 B 码)导出的。

数字电路设计实验vhdl语言实验报告

实验一秒表计数器的设计实验目的:本实验通过设计四种频率可选的数字时钟系统, 以达到熟悉VHDL 语言编程语法、设计思路和熟练掌握Quartus II 开发软件的目的。

二、实验内容:该数字时钟的显示格式如下所示: HH: MM: SS, 其中HH表示时计数的两位, MM表示分计数的两位, SS表示秒计数的两位。

本系统输入信号分别为复位信号rst(高有效)、sel(两位信号, 分别可以选择2分频、4分频8分频和16分频)、clk_in(时钟信号)、8位时输出、8位分输出、8位秒输出(其中高4为表示对应的高半字节、低4位表示的低半字节, 譬如当时间为08:59:30时, 时输出为”0000_1000”,分输出为”0101_1001”,秒输出为”0011_0000”)。

该时钟系统可以通过Sel信号时钟运行的快慢。

三、实验流程:通过对实验内容的分析: 可以考虑时钟系统的可由三部分组成: 1.分频器:分频器为时序电路并且通过《数字电路》理论课程的学习可知由计数器来实现, 同学可以回想一下实验1中是如何实现计数器电路的设计), 该模块主要产生2.4.8、16分频的时钟信号;2.多路选择器:在VHDL中多路选择器为组合逻辑, 可以有多种实现方法, 在这里主要选用了case语句来实现。

该模块的作用是从分频器中根据Sel信号选择适当的时钟信号;3.时钟控制器:该模块比较复杂, 主要实现功能是实现一个24小时的计时。

当时间为00:00:59的时候下一个时钟到来时状态的跳变为00:01:00, 计时中多数计数为加1操作, 有几个特殊状态需要重点考虑:当时间产生分进数时, 譬如上例。

当时间产生时进数时, 譬如00:01:59时刻的下一个状态为00:02:00;当时间产生时进数时, 譬如00:59:59是个的下一个状态为01:00:00。

当时间产生天进数时, 譬如23:59:59的下一个状态为00:00:00。

四、仿真要求:1、本次试验的结果全部采用功能仿真分析:在结果图中能够看到让复位信号rst为有效的情况下, 所有的输出为00:00:00;2.当频率选择输出分别为”00”、”01”、”10”、”11”时秒为的进数分别包含2.4.8、16倍clk_in的时钟周期;3.可以看到完整的计时周期00:00:00->23:59:59->00:00:00。

VHDL数字电路课程实验报告

VHDL数字电路课程实验报告实验一8分频器一、实验要求:分别用信号量和变量实现八分频器二、实验过程:1、代码:8分频器vhdlibrary ieee;use ieee.std_logic_1164.all;entity freq_divider isport(clk: in std_logic;out1, out2: buffer bit);end freq_divider;architecture example of freq_divider issignal count1: integer range 0 to 7;beginprocess(clk)variable count2: integer range 0 to 7;beginif(clk'event and clk='1') thencount1<=count1+1;count2:=count2+1;if(count1=3) thenout1<=not out1;count1<=0;end if;if(count2=4) thenout2<=not out2;count2:=0;end if;end if;end process;end example;八分频器tbLIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY fd_tb isEND fd_tb;architecture behavior of fd_tb iscomponent freq_dividerport(clk:IN STD_LOGIC;out1, out2: buffer bit);end component;signal clk:std_logic;signal out1,out2:bit;beginu1: freq_divider port map(clk,out1,out2);processbeginclk<='0';wait for 50 ns;loopclk<=not clk;wait for 25 ns;end loop;end process;end behavior;2、结果图:实验二实现例8.6一、实验要求:电路只有一个输入时钟信号,输出信号在适中的两个边沿都会发生变化二、实验内容:1、代码信号发生器vhdENTITY signal_gen ISPORT (clk: IN BIT;outp: OUT BIT);END signal_gen;ARCHITECTURE fsm OF signal_gen ISTYPE state IS (one, two, three);SIGNAL pr_state1, nx_state1: state;SIGNAL pr_state2, nx_state2: state;SIGNAL out1, out2: BIT;BEGINPROCESS(clk)BEGINIF (clk'EVENT AND clk = '1') THENpr_state1 <= nx_state1;END IF;END PROCESS;PROCESS (clk)BEGINIF (clk'EVENT AND clk = '0') THENpr_state2 <= nx_state2;END IF;END PROCESS;PROCESS (pr_state1)BEGINCASE pr_state1 ISWHEN one =>out1 <= '0';nx_state1 <= two;WHEN two =>out1 <= '1';nx_state1 <= three;WHEN three =>out1 <= '1';nx_state1 <= one;END CASE;END PROCESS;PROCESS (pr_state2)BEGINCASE pr_state2 ISWHEN one =>out2 <= '1';nx_state2 <= two;WHEN two =>out2 <= '0';nx_state2 <= three;WHEN three =>out2 <= '1';nx_state2 <= one;END CASE;END PROCESS;outp <= out1 AND out2;END fsm;信号发生器tbentity tb_fsm isend tb_fsm;architecture behavior of tb_fsm is component signal_gen isport( clk: in bit;outp: out bit);end component;signal clk,outp:bit;beginu1: signal_gen port map(clk,outp); processbeginclk<='0';wait for 20 ns;loopclk<=not clk;wait for 10 ns;end loop;end process;end behavior;2、结果图实验三常数比较器一、实验要求常数比较器,用于比较的变量位宽应大于等于常数二、实验内容1、代码常数比较器vhdLIBRARY ieee;USE ieee.std_logic_1164.all;entity compare isport(b: in integer range 0 to 15;x1,x2,x3: out std_logic);end compare;architecture compare of compare isconstant a: integer:=10;beginx1<='1' when a>b else '0';x2<='1' when a=b else '0';x3<='1' when a<b else '0';end compare;常数比较器tbLIBRARY ieee;USE ieee.std_logic_1164.all;entity tb_compare isend tb_compare;architecture behavior of tb_compare iscomponent compareport(b: in integer range 0 to 15;x1,x2,x3: out std_logic);end component;signal b: integer;signal x1,x2,x3: std_logic;beginu1: compare port map(b, x1,x2,x3);processbeginb<=5; wait for 10 ns;b<=8; wait for 10 ns;b<=10; wait for 10 ns;b<=13; wait for 10 ns; b<=10; wait for 10 ns; b<=3; wait for 10 ns; end process;end behavior;2、结果图实验四序列检测器一、实验要求序列检测’1001’弱检测到,输出‘1‘,否则输出’0‘二、实验内容1、状态图2、代码序列检测器vhdlibrary ieee;use ieee.std_logic_1164.all;entity string_detector isport(datain,clk: in bit;q: out bit);end string_detector;architecture sd of string_detector istype state is (zero, one, two, three, four);signal pr_state, nx_state: state;beginprocess(clk)beginif(clk'event and clk='1') thenpr_state<=nx_state;end if;end process;process(datain, pr_state)begincase pr_state iswhen zero=>q<='0';if(datain='1') then nx_state<=one;else nx_state<=zero;end if;when one=>q<='0';if(datain='0') then nx_state<=two;else nx_state<=zero;end if;when two=>q<='0';if(datain='0') then nx_state<=three;else nx_state<=zero;end if;when three=>q<='0';if(datain='1') then nx_state<=four;else nx_state<=zero;end if;when four=>q<='1';nx_state<=zero;end case;end process;end sd;序列检测器tb------------------------------------------------------------------ library ieee;use ieee.std_logic_1164.all;------------------------------------------------------------------ entity testBench isend testBench;------------------------------------------------------------------architecture test of testBench iscomponent string_detector isport(datain,clk: in bit;q: out bit);end component;signal datain,clk:bit;signal q:bit;beginSD: string_detector port map(datain,clk,q);processbeginfor i in 0 to 100 loopclk<='0';wait for 10 ns;clk<='1';wait for 10 ns;end loop;end process;processbegindin<='1';wait for 20ns;din<='0';wait for 20ns;din<='0';wait for 20ns;din<='0';wait for 20ns;din<='1';wait for 20ns;din<='0';wait for 20ns;din<='0';wait for 20ns;din<='1';wait for 20ns;din<='0';wait for 20ns;din<='1';wait for 20ns;din<='0';wait for 20ns;end process;end test;3、结果图。

(完整word版)2对4译码器VHDL实验报告.doc

通信与信息工程学院2012 /2013学年第二学期软件设计实验报告模块名称二对四译码器专业电子信息工程学生班级B100109学生学号学生姓名指导教师梅中辉、王奇、周晓燕、孔凡坤实验目的:本软件设计的目的和任务: 1.使学生全面了解如何应用该硬件描述语言进行高速集成电路设计; 2.通过软件使用、设计与仿真环节使学生熟悉 EDA-VHDL 开发环境; 3. 通过对基本题、综合题的设计实践,使学生掌握硬件系统设计方法(自底向上或自顶向下),熟悉 VHDL 语言三种设计风格,并且培养学生应用 VHDL 语言解决实际问题的能力。

实验设备: 1:微型计算机2:quartus II 开发软件实验课题: 2 对 4 译码器实验描述:设计一个 2 对 4 译码器(输入: A B 输出: Y3 Y2 Y1 Y0 ),真值表如图:A B Y3 Y2 Y1 Y00 0 1 1 1 00 1 1 1 0 11 0 1 0 1 11 1 0 1 1 1一:实验目的1:能了解组合逻辑中译码器电路的设计原理。

2:能利用 CPLD数字发展实验系统设计一个二对四译码器。

3:能自行验证所设计电路的正确性。

二:实验内容及要求设计一个 2-4 译码器,并验证输出数值的正确性。

三:实验器材1. 软件: Altera公司的Quartus ||软件。

2. 芯片: Altera公司的EP2C8T144C8。

1)、选择 Block Diagran/Schenatic File,单击 OK 按钮,打开图形2)、进入原理图编辑页面如下:导入逻辑门电路符号、输入/输出符号,用导线连接各逻辑单元如下:工程建立与编译建立工程:在 D 盘建立 test 文件夹,进入 quartusII7.2 主界面,新建编辑代码页面,选择 VHDL file ,点击 OK代码输完后存盘,文件名必需为 test8(文件名必须与实体名一致),目录为,按 project 菜单下 set as top-level entity 命令。

VHDL-实验

计算机科学与技术学院实验报告(学年度第学期)课程名称EDA技术实验姓名学号专业计算机班级地点教师实验一:八位二进制补码一.实验目的1.熟悉Max+PlusII和GW48EDA开发系统的使用;2.掌握八位二进制补码的VHDL设计;3.元件例化语句的使用。

二.实验原理若原码为正,则补码等于原码;若原码为负,则补码为(2+原码)mod2。

三.八位二进制补码程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY JACKAN ISPORT(rst:IN STD_LOGIC;din:IN STD_LOGIC_VECTOR(7 DOWNTO 0);dout:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY JACKAN;ARCHITECTURE HAIXIA OF JACKAN ISSIGNAL tmp:STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINPROCESS(din,rst)BEGINIF rst='0' THENdout<=(OTHERS=>'0');ELSIF din(7) ='1' THENFOR i IN 0 TO 6 LOOPtmp(i)<=NOT din(i);END LOOP;dout(6 DOWNTO 0) <= tmp+1;dout(7) <= din(7);ELSEdout<= din;END IF;END PROCESS;END ARCHITECTURE HAIXIA;四.实验结果五.总结8位二进制补码:寄存器主要用来存储8位二进制数据。

高8位为符号位,不进行求反运算。

余下7位根据高8位的数据状态进行相应操作。

实验二.一位全减器的VHDL设计一. 实验目的1.熟悉Max+PlusII和GW48EDA开发系统的使用;2.掌握一位半减器的VHDL设计;3.掌握一位半减器构建一位全减器的方法;二.实验原理由两个半减器和一个或门构成一个全减器。

VHDL实验

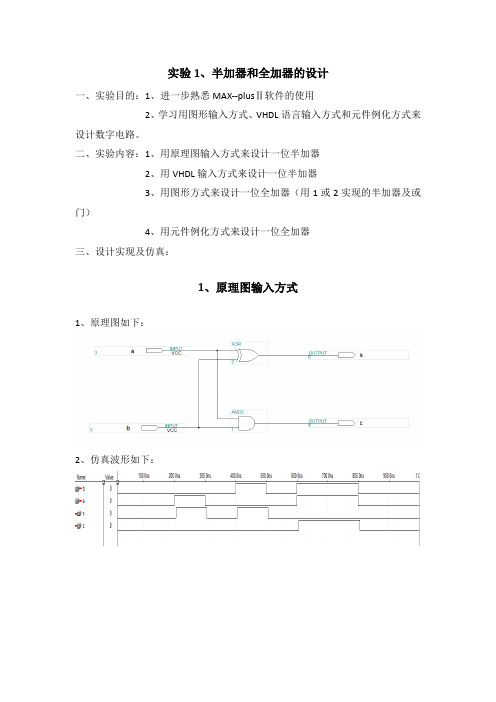

实验1、半加器和全加器的设计一、实验目的:1、进一步熟悉MAX--plusⅡ软件的使用2、学习用图形输入方式、VHDL语言输入方式和元件例化方式来设计数字电路。

二、实验内容:1、用原理图输入方式来设计一位半加器2、用VHDL输入方式来设计一位半加器3、用图形方式来设计一位全加器(用1或2实现的半加器及或门)4、用元件例化方式来设计一位全加器三、设计实现及仿真:1、原理图输入方式1、原理图如下:2、仿真波形如下:2、VHDL输入方式1、源程序如下:library ieee;use ieee.std_logic_1164.all;entity half_adder2 isport (a,b:in std_logic;s,c:out std_logic);end half_adder2;architecture arch of half_adder2 isbegins<=a xor b;c<=a and b;end arch;2、仿真波形如下:3、一位全加器1、原理图如下4、元件例化方式1、源程序如下:实验2、四选一数据选择选择器的设计一、实验目的:1、进一步熟悉MAX--plusⅡ软件的使用2、学习用图形输入方式、VHDL语言输入方式和元件例化方式来设计数字电路。

二、实验内容:1、用if语句实现2、用case语句实现3、用when。

else。

语句实现4、用with。

select。

语句实现三、设计实现及仿真:1、原理图如下:1、源程序如下:四选一library ieee;use ieee.std_logic_1164.all;entity mux41 isport (a,b,c,d:in std_logic_vector(3 downto 0);sel:in std_logic_vector(1 downto 0);y:out std_logic_vector(3 downto 0) );end mux41;architecture arch of mux41 isbeginprocess(a,b,c,d,sel)beginif (sel="00") then y<=a;elsif (sel="01") then y<=b;elsif (sel="10") then y<=c;else y<=d;end if;end process;end arch;2、仿真波形如下:1、源程序如下:2、仿真波形如下:1、源程序如下:2、仿真波形如下:1、源程序如下2、仿真波形如下:实验3、可逆计数器的设计一、实验目的:1、进一步熟悉MAX--plusⅡ软件的使用2、学习用图形输入方式、VHDL语言输入方式和元件例化方式来设计数字电路。

vhdl实验

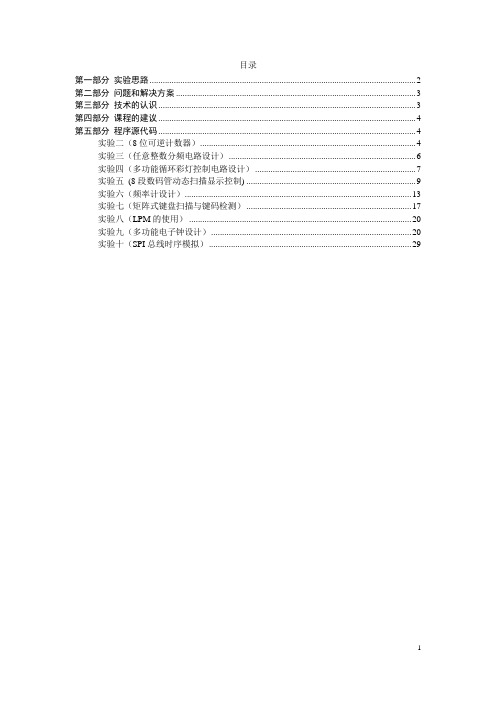

目录第一部分实验思路 (2)第二部分问题和解决方案 (3)第三部分技术的认识 (3)第四部分课程的建议 (4)第五部分程序源代码 (4)--实验二(8位可逆计数器) (4)--实验三(任意整数分频电路设计) (6)--实验四(多功能循环彩灯控制电路设计) (7)--实验五(8段数码管动态扫描显示控制) (9)--实验六(频率计设计) (13)--实验七(矩阵式键盘扫描与键码检测) (17)--实验八(LPM的使用) (20)--实验九(多功能电子钟设计) (20)--实验十(SPI总线时序模拟) (29)第一部分实验思路1.1实验二(8位可逆计数器)分两个进程,一个记录手动脉冲个数,另一个记录脉冲源脉冲个数,最后以方式选择开关决定显示哪个个数。

1.2实验三(任意整数分频电路设计)分两个进程,一个记录上升沿个数,另一个纪录下降沿个数,当计数总和等于预分频数时,两个进程的标识位取反,最后将两个标识位的异或送给输出。

1.3实验四(多功能循环彩灯控制电路设计)确定四种循环方式,分别为1、3、5、7,2、4、6、8,7、5、3、1,8、6、4、2。

用case,when语句,同时计数自动加一。

1.4实验五(8段数码管动态扫描显示控制)设置一个顶层文件,三个模块文件(分频模块,计数模块,显示模块)。

分频是将20Mhz分成周期为1/100s和100us的方波。

计数是记录有多少个1/100s。

显示是以100us为步调扫描数码管以显示计数。

1.5实验六(频率计设计)设置一个顶层文件,三个模块文件(分频模块,计数模块,显示模块)。

分频是将20Mhz分成周期为1s和1ms的方波。

计数是记录在1s内待测脉冲的周期数。

显示是以1ms为步调扫描数码管以显示计数。

1.6实验七(矩阵式键盘扫描与键码检测)设立四个进程,一个完成由20Mhz到周期为10ms,100us的转换(10ms用于扫描键盘,100us 用于扫描数码管以显示键码)。

VHDL实验报告

专用集成电路实验报告13050Z011305024237刘德文实验一开发平台软件安装与认知实验实验内容1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 9.2软件平台上完成设计电路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。

下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。

2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE9.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。

源程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following lines to use the declarations that are-- provided for instantiating Xilinx primitive components.--library UNISIM;--use UNISIM.VComponents.all;entity ls74138 isPort ( g1 : in std_logic;g2 : in std_logic;inp : in std_logic_vector(2 downto 0);y : out std_logic_vector(7 downto 0)); end ls74138;architecture Behavioral of ls74138 isbeginprocess(g1,g2,inp)beginif((g1 and g2)='1') thencase inp iswhen "000"=>y<="00000001";when "001"=>y<="00000010";when "010"=>y<="00000100";when "011"=>y<="00001000";when "100"=>y<="00010000";when "101"=>y<="00100000";when "110"=>y<="01000000";when "111"=>y<="10000000";when others=>y<="00000000";end case;elsey<="00000000";end if;end process;end Behavioral;波形文件:生成元器件及连接电路思考:有程序可以看出,定义了三个输入端,一个输出端。

实验三_VHDL时序逻辑电路设计

实验三实验三 VHDL VHDL VHDL 时序逻辑电路设计时序逻辑电路设计 一、实验目的一、实验目的1. 熟悉用VHDL 语言设计时序逻辑电路的方法语言设计时序逻辑电路的方法 2. 熟悉用Quartus 文本输入法进行电路设计文本输入法进行电路设计 二、实验所用仪器元件及用途二、实验所用仪器元件及用途 1. 计算机:装有Quartus 软件,为VHDL 语言提供操作场所。

语言提供操作场所。

2. 直流稳压电源:通过USB 接口实现,为实验开发板提供稳定电源。

接口实现,为实验开发板提供稳定电源。

3. 数字系统与逻辑设计实验开发板:使试验结果下载到开发板上,实现整个实验的最终结果。

果。

三、实验内容三、实验内容 1. 用VHDL 语言设计实现一个8421码十进制计数器。

码十进制计数器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

2. 用VHDL 语言设计实现一个分频系数为8,分频输出信号占空比为50%的分频器。

的分频器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求。

平台上设计程序和仿真题目要求。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

3. 用VHDL 语言设计实现一个控制8个发光二极管亮灭的电路。

个发光二极管亮灭的电路。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

a. 单点移动模式:一个点在8个发光二极管上来回的亮个发光二极管上来回的亮b. 幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复往复c. 通过拨码开关或按键控制两种模式的转换通过拨码开关或按键控制两种模式的转换 (2) 试验结果:VHDL 代码和仿真结果。

VHDL 实验一组合逻辑电路的设计

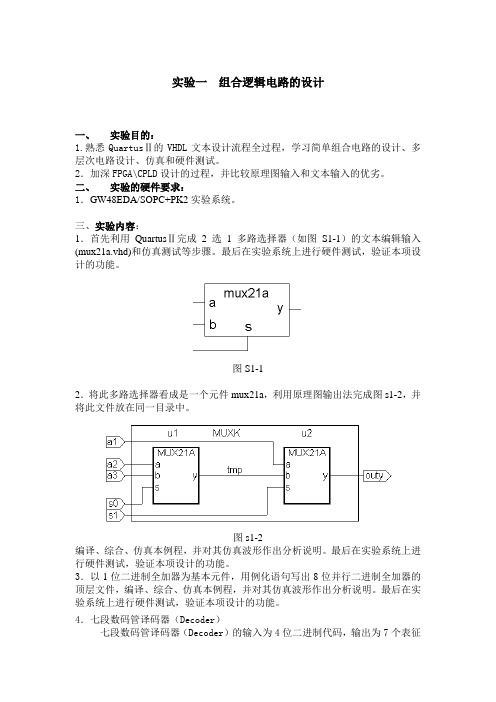

实验一组合逻辑电路的设计一、实验目的:1.熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

2.加深FPGA\CPLD设计的过程,并比较原理图输入和文本输入的优劣。

二、实验的硬件要求:1.GW48EDA/SOPC+PK2实验系统。

三、实验内容:1.首先利用QuartusⅡ完成2选1多路选择器(如图S1-1)的文本编辑输入(mux21a.vhd)和仿真测试等步骤。

最后在实验系统上进行硬件测试,验证本项设计的功能。

图S1-12.将此多路选择器看成是一个元件mux21a,利用原理图输出法完成图s1-2,并将此文件放在同一目录中。

图s1-2编译、综合、仿真本例程,并对其仿真波形作出分析说明。

最后在实验系统上进行硬件测试,验证本项设计的功能。

3.以1位二进制全加器为基本元件,用例化语句写出8位并行二进制全加器的顶层文件,编译、综合、仿真本例程,并对其仿真波形作出分析说明。

最后在实验系统上进行硬件测试,验证本项设计的功能。

4.七段数码管译码器(Decoder)七段数码管译码器(Decoder)的输入为4位二进制代码,输出为7个表征七段数码管代码的状态信号。

下面为一个七段数码管译码器的VHDL源代码模型:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY display ISPORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END;ARCHITECTURE ONE OF display ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000"=>LED7S<="0111111";--X"3F"->0WHEN "0001"=>LED7S<="0000110";--X"06"->1WHEN "0010"=>LED7S<="1011011";--X"5B"->2WHEN "0011"=>LED7S<="1001111";--X"4F"->3WHEN "0100"=>LED7S<="1100110";--X"66"->4WHEN "0101"=>LED7S<="1101101";--X"6D"->5WHEN "0110"=>LED7S<="1111101";--X"7D"->6WHEN "0111"=>LED7S<="0000111";--X"07"->7WHEN "1000"=>LED7S<="1111111";--X"7F"->8WHEN "1001"=>LED7S<="1101111";--X"6F"->9WHEN "1010"=>LED7S<="1110111";--X"77"->10WHEN "1011"=>LED7S<="1111100";--X"7C"->11WHEN "1100"=>LED7S<="0111001";--X"39"->12WHEN "1101"=>LED7S<="1011110";--X"5E"->13WHEN "1110"=>LED7S<="1111001";--X"79"->14WHEN "1111"=>LED7S<="1110001";--X"71"->15WHEN OTHERS=>NULL;END CASE;END PROCESS;END;编译、综合、仿真本例程,并对其仿真波形作出分析说明。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 Quartus II软件使用与十进制计数器一、实验目的熟悉使用Quartus II软件二、实验内容安装Quartus II软件并成功注册、使用Quartus II软件建立工程并完成十进制计数器三、实验仪器、设备计算机、Quartus II软件四、实验步骤1.打开安装文件位于…quartusII6.0\disk1\install.exe,根据提示进行下一步操作,在弹出框中选择第一个选项,install Quartus II and Related Software。

Quartus II的安装步骤1接下来的安装中选择下一步,到下图选择界面。

只勾选安装Quartus II 6.0即可。

Quartus II的安装步骤22.完成安装步骤2后选择下一步至下图所示,选择完全安装complete,再继续点击下一步至安装开始。

完全安装Quartus II软件软件安装途中出现如下图所示情况时,选择安装文件中的…disk2\disk2\quartus,然后选择确定——OK继续安装直到结束。

安装过程中换disk2路径Quartus II软件的安装至此结束,此安装步骤WINXP/WIN 7均有效,WIN8若有问题,请修改兼容权限。

3.软件注册。

软件安装结束后打开Quartus II软件将出现下图所示情况,这是没有注册的提醒,我们必须先进行注册才能建立工程文件,若大家忽略了这个提示窗口,直接进行工程建立等工作,任何仿真图和编译功能都无法正常使用,等于白费功夫浪费时间,还要重新(由于软件注册是绑定MAC物理地址,所以每台机器的license 做,非常影响学习兴趣和情绪。

是完全不一样的,实验室的电脑已经安装好了Quartus II软件,但是没有注册,所以做实验的时候一点要先注册,不然就白做了)Quartus II软件提示未注册弹窗注册方法,打开quiic7.1 lisence 生成器文件夹中的keymaker.exe,在弹出的窗口中点击Make License,在文件夹中就会出现和本台机器相匹配的license.dat。

(注意此license只对应本机,拷贝给其他机器无效)将license.dat复制到C:\altera\quartus60\win文件夹下。

(可以使用快键方式点击Quartus II 6.0右键属性——打开文件夹位置即是需要复制到的文件夹,选择替换该文件),在自己电脑安装时,还有一个sys_cpt.dll文件需要被替换才能完成注册,替换文件的地路径…\quartusII6.0\disk2\disk2\crack6.0\sys_cpt.dll,这一步在实验室电脑无需做,特别是不能复制生成器里面的sys_cpt.dll,不然软件无法打开。

license生成器生成的license复制license.dat到目标文件夹并替换替换license后打开上图即为注册成功到此Quartus II软件安装与注册已经介绍完毕,若安装中还有其他问题请咨询相关老师或网上找寻解决办法。

4. Quartus II软件工程建立。

任何一项设计都是一项工程(project),必须先为此工程建立一个放置与此工程相关的设计文件的文件夹。

一般,不同的设计项目放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

(注意:不要将文件夹设在计算机已有的安装目录中,更不要将工程文件直接放在安装目录中)新建文件夹,在自定的路径建立文件夹,例如:d:\cnt10b(注意:文件夹不能用中文命名,也不要用纯数字)选择主页面的File——New——VHDL File——OK,如下图所示新建VHDL文件将下面源程序复制进去(十进制计数):library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10b isport(clk,rst,en:in std_logic;cq:out std_logic_vector(3 downto 0);cout:out std_logic);end cnt10b;architecture behav of cnt10b isbeginprocess(clk,rst,en)variable cqi:std_logic_vector(3 downto 0);beginif rst = '1' then cqi:=(others =>'0'); --计数器异步复位elsif clk'event and clk='1' thenif en = '1' then --检测是否允许计数if cqi<9 then cqi:=cqi+1; --小于9,计数else cqi:=(others =>'0'); --大于9,计数器清零end if;end if;end if;if cqi=9 then cout<='1'; --大于9,输出进位信号else cout<='0';end if;cq<=cqi; --将计数器值向端口输出end process;end behav;复制完成后将VHDL文件存盘,选择File——Save As,找到已建立的文件夹d:\cnt10b,存盘名称自定,同样不能为中文,我们用文件夹命名cnt10.vhd。

当出现“Do you want to create a new project with this file?”时,选择是,随即进入工程建立流程。

将会出现下图,说明各行的意义,第一行D:/cnt10b/,说明你的工程文件的路径。

第二行cnt10b,是工程的名字。

第三行cnt10b为当前工程文件的实体名,这里即为cnt10b。

此方法所有选项会根据你以上的步骤自动记录,直接选择下一步即可。

工程文件建立点击下一步Next,将设计文件加入工程(如果事先做好的话),我们刚才建立的cnt10b.vhd源程序文件,我们将它加入进来后,选择下一步。

工程文件添加点击下一步Next后,选择具体芯片型号Family类型选择Cyclone,具体型号为EP1C6Q240C8。

芯片型号一定要选择对,不然无法将程序下载至实验箱。

选择下一步Next,第四项选择工具可以全部不选,直接Next完成。

此时,cnt10b的工程已建立好。

cyclone芯片选择工程建立成功图示选择Processing——Start Compilation进行编译,也可点击快捷工具栏中按钮进行编译操作,编译成功如下图所示。

编译成功界面若编译时出现其他问题(warming可忽略),软件会提示出现问题的地方,比如:语句错误等。

根据提示进行修改,若一直跟着此步骤做下来,应该不会有问题。

(注意:未注册的软件是100%无法编译成功的)5.建立波形文件进行仿真。

选择File——new——Other Files——Vector Waveform File——OK,建立波形仿真软件,然后选择View——Utility Windows——Node Found【快捷键(ALT+1)】,然后再弹出的对话框中Filter选择Pins:all——点击list,将出现9个信号源(若未出现说明未编译成功,重新编译一次),框选全部信号源,添加至波形文件的Name下面,然后点击保存,将波形文件命名为cnt10b.vwf。

信号源的添加信号源添加至波形文件进行信号源的属性设置,首先设置仿真的起止时间,Edit——End Time,选择仿真时间10S。

然后将clk时钟源设置为时钟模式Overwrite Clock图标为,点击后选择周期等属性,End time设置时钟周期设置将其他信号源(en,rst)按照仿真图进行设置,然后执行波形仿真,点击进行编译,结果如下图所示。

波形仿真结果图6.引脚设置。

选择assignments——pins进行引脚设置,将引脚设置为同下图一样。

引脚设置完毕后,再进行一次编译(Start Compilation)才能进行下载。

引脚设置界面到此本次实验仿真部分完成,接下来是将程序下载至实验箱的实操部分。

7.源程序下载。

USB下载器驱动安装,将下载器连接到USB口,此时电脑将出现新硬件,Quartus II软件安装时就会将驱动程序一起安装,默认路径C:\altera\quartus60\drivers\usb-blaster,所以我们只要找到驱动路径进行指定就OK了,具体方法见下图(图为WIN7环境下的驱动安装)发现新硬件选择驱动文件路径若出现验证选择始终安装USB驱动安装完毕后,点击Tools——Programmer进行下载步骤,点击Hardware Setup 进行硬件设置,在此选择USB-Blaster,点击close。

若安装了驱动却没出现USB-Blaster,请拔掉下载器重新插入。

然后勾选Program/Configure后点击Start将编译好的程序下载至实验箱。

Progress旁边的蓝色条出现100%,并且页面下部出现绿色字样:Info: Configuration succeeded -- 1 device(s) configured就表示下载成功。

下载页面Hardware Setup页面设置下载成功界面8.功能介绍。

十进制计数器程序已经被我们下载到实验箱,是不是特别想看看实物的结果,我们这个实验的引脚使用的是模式5的电路,所以按模式选择,将指示灯按成5,就是模式5。

按键设置键1为EN端,即使能端,键2为rst,即复位端,LED D1为cout,即进位位。

此时我们需要设置时钟频率,在实验箱右下角,最右边一排有插针,请将插针的跳线帽接在16Hz 及以下就能清楚的看见我们实验的效果。

实验二组合电路的设计一、实验目的熟悉使用Quartus II软件的VHDL文本设计流程全过程二、实验内容学习简单组合电路的设计、多层次电路设计、仿真和硬件测试三、实验仪器、设备计算机、Quartus II软件四、实验步骤1.首先利用QuartusⅡ完成2选1多路选择器(例1-1)的文本编辑输入(mux21a.vhd)。

【例1-1】library ieee;use ieee.std_logic_1164.all;ENTITY mux21a ISPORT ( a, b, s: IN STD_LOGIC;y : OUT STD_LOGIC );END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGINPROCESS (a,b,s) BEGINIF s = '0' THEN y <= a ; ELSE y <= b ;END IF;END PROCESS;END ARCHITECTURE one ;2.将此多路选择器看成是一个元件mux21a,利用元件例化语句描述三选一数据选择器图1-1,并将此文件放在同一目录中。