MIPI--协议详细的介绍

MIPI_协议详细介绍

Protocol IntroductionMIPI Development Team2010-9-2What is MIPI?v MIPI stands for M obile I ndustry P rocessor I nterface §MIPI Alliance is a collaboration of mobile industry leaders.§Objective to promote open standards for interfaces to mobile application processors.§Intends to speed deployment of new services to mobile users by establishing Spec.v Board Members in MIPI Alliance§Intel, Motorola, Nokia, NXP,Samsung, ST, TIWhat is MIPI?v MIPI Alliance Specification for display§DCS (D isplay C ommand S et)•DCS is a standardized command set intended for command modedisplay modules.§DBI, DPI (D isplay B us I nterface, D isplay P ixel I nterface)•DBI:Parallel interfaces to display modules having displaycontrollers and frame buffers.•DPI:Parallel interfaces to display modules without on-paneldisplay controller or frame buffer.§DSI, CSI (D isplay S erial I nterface, C amera S erial I nterface)•DSI specifies a high-speed serial interface between a hostprocessor and display module.•CSI specifies a high-speed serial interface between a hostprocessor and camera module.§D-PHY•D-PHY provides the physical layer definition for DSI and CSI.DSI LayersDCS specDSI specD-PHY specOutlinev D-PHY§Introduction§Lane Module, State and Linelevels§Operating Modes•Escape Mode§System Power States§Electrical Characteristics§SummaryIntroduction for D-PHYv D-PHY describes a source synchronous, high speed, low power, low cost PHY v A PHY configuration contains§ A Clock Lane§One or more Data Lanesv Three main lane types§Unidirectional Clock Lane§Unidirectional Data Lane§Bi-directional Data Lanev Transmission Mode§Low-Power signaling mode for control purpose:10MHz (max)§High-Speed signaling mode for fast-data traffic:80Mbps ~ 1Gbps per Lanev D-PHY low-level protocol specifies a minimum data unit of one byte § A transmitter shall send data LSB first, MSB last.v D-PHY suited for mobile applications§DSI:Display Serial Interface• A clock lane, One to four data lanes.§CSI:Camera Serial InterfaceTwo Data Lane PHY ConfigurationLane Modulev PHY consists of D-PHY (Lane Module)v D-PHY may contain§Low-Power Transmitter (LP-TX)§Low-Power Receiver (LP-RX)§High-Speed Transmitter (HS-TX)§High-Speed Receiver (HS-RX)§Low-Power Contention Detector (LP-CD)v Three main lane types§Unidirectional Clock Lane•Master:HS-TX, LP-TX•Slave:HS-RX, LP-RX§Unidirectional Data Lane•Master:HS-TX, LP-TX•Slave:HS-RX, LP-RX§Bi-directional Data Lane§Master, Slave:HS-TX, HS-RX,LP-TX, LP-RX, LP-CDUniversal Lane Module ArchitectureLane States and Line Levels§The two LP-TX’s drive the two Lines of a Lane independently and single-ended.•Four possible Low-Power Lane states (LP-00, LP-01, LP-10, LP-11)§ A HS-TX drives the Lane differentially.•Two possible High Speed Lane states (HS-0, HS-1)§During HS transmission the LP Receivers observe LP-00 on the Lines §Line Levels (typical)•LP:0~1.2V•HS:100~300mV (Swing:200mV)§Lane States•LP-00, LP-01, LP-10, LP-11•HS-0, HS-1Operating Modes§There are three operating modes in Data Lane•Escape mode, High-Speed (Burst) mode and Control mode§Possible events starting from the Stop State of control mode •Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)•High-Speed mode request (LP-11→LP-01→LP-00)•Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)Escape Modev Escape mode is a special operation for Data Lanes using LP states.§With this mode some additional functionality becomes available:LPDT, ULPS, Trigger§ A Data Lane shall enter Escape mode via LP-11→LP-10→LP-00→LP-01→LP-00§Once Escape mode is entered, the transmitter shall send an 8-bit entry command to§indicate the requested action.§Escape mode uses Spaced-One-Hot Encoding.§means each Mark State is interleaved with a Space State (LP-00).§Send Mark-0/1 followed by a Space to transmit a ‘zero-bit’/ ‘one-bit’§ A Data Lane shall exit Escape mode via LP-10→LP-11v Ultra-Low Power State§During this state, the Lines are in the Space state (LP-00)§Exited by means of a Mark-1 state with a length TWAKEUP(1ms) followed by a Stop state.Escape ModeClock Lane Ultra-Low Power Statev A Clock Lane shall enter ULPS via§LP-11→LP-10→LP-00v exited by means of a Mark-1 with a length TWAKEUP followed bya Stop State§LP-10 →TWAKEUP →LP-11§The minimum value of TWAKEUP is 1msHigh-Speed Data Transmissionv The action of sending high-speed serial data is called HS transmission or burst.v Start-of-Transmission§LP-11→LP-01→LP-00→SoT(0001_1101)§HS Data Transmission Burst§All Lanes will start synchronously§But may end at different times§The clock Lane shall be in High-Speed mode, providing a DDR Clock to the Slave sidev End-of-Transmission§H Toggles differential state immediately after last payload data bitv and keeps that state for a time THS-TRAILHigh-Speed Clock Transmissionv Switching the Clock Lane between Clock Transmission and LP Mode§ A Clock Lane is a unidirectional Lane from Master to Slave§In HS mode, the clock Lane provides a low-swing, differential DDR clock signal.§the Clock Burst always starts and ends with an HS-0 state.§the Clock Burst always contains an even number of transitionsSummary for D-PHYv Lane Module, Lane State and Line Levels§Lane Module:LP-TX, LP-RX, HS-TX, HS-RX, LP-CD§Lane States:LP-00, LP-01, LP-10, LP-11, HS-0, HS-1§Line Levels (typical):LP:0~1.2V, HS:100~300mV (Swing:200mV)v Operating Modes§Escape Mode entry procedure :LP-11→LP-10→LP-00→LP-01→LP-00→Entry Code →LPD (10MHz)§Escape Mode exit procedure:LP-10→LP-11§High Speed Mode entry procedure:LP-11→LP-01→LP-00→SoT(00011101) →HSD (80Mbps ~ 1Gbps)§High Speed Mode exit procedure:EoT→LP-11§Control Mode -BTA transmission procedure:LP-11→LP-10→LP-00→LP-10→LP-00§Control Mode -BTA receive procedure:LP-00→LP-10→LP-11v System Power States§Low-Power mode, High-Speed mode, Ultra-Low Power modev Fault Detection§Contention Detection (LP-CD), Watchdog Timer, Sequence Error Detection (Error Report) v Global Operation Timing Parameter§Clock Lane Timing, Data Lane Timing§Other Timing –Initialization, BTA, Wake-Up from ULPSv Electrical Characteristics§HS-RX, LP-RX, LP-TX, LP-CD, Pin characteristic, Clock signal, Data-Clock timing§DC and AC characteristicOutlinev DSI§Introduction§Lane Distributor/Merger Conceptual§Packet Structure§Data Transmission Way§Processor-Sourced Packets§Peripheral-Sourced Packets§Reverse-Direction LP Transmission§Video Mode§SummaryIntroduction for DSIv DSI is a Lane-scalable interface for increased performance.§One Clock Lane / One to Four Data Lanesv DSI-compliant peripherals support either of two basic modes of operation §Command Mode (Similar to MPU IF)•Data Lane 0:bidirectional–For returning data, ACK or error report to host•Additional Data Lanes:unidirectional.§Video Mode (Similar to RGB IF)•Data Lane 0:bidirectional or unidirectional;•Additional Data Lanes:unidirectional.•Video data should only be transmitted using HS mode.v Transmission Mode§High-Speed signaling mode§Low-Power signaling mode•Forward/Reverse direction LP transmissions shall use Data Lane 0 only•For returning data, DSI-compliant systems shall only use Data Lane 0 in LP Mode v Packet Types§Short Packet:4 bytes (fixed length)§Long Packet:6~65541 bytes (variable length)Two Data Lanes HS Transmission ExampleData Transmission Wayv Separate Transmissionsv Separate Transmissionsv KEY:§LPS –Low Power State SP –Short Packet §SoT–Start of Transmission LgP–Long Packet §EoT–End of TransmissionShort Packet Structurev P acket H eader (4 bytes)§Data Identifier (DI) * 1byte:Contains the Virtual Channel[7:6] and Data Type[5:0].§Packet Data * 2byte:Length is fixed at two bytes§Error Correction Code (ECC) * 1byte:allows single-bit errors to be corrected and 2-bit errors to be detected.v Packet Size§Fixed length 4 bytesv The first byte of any packet is the DI (Data Identifier) byte.§DI[7:6]:These two bits identify the data as directed to one of four virtual channels.§DI[5:0]:These six bits specify the Data Type.Long Packet Structurev P acket H eader (4 bytes)§Data Identifier (DI) * 1byte:Contains the Virtual Channel[7:6] and Data Type[5:0].§Word Count (WC) * 2byte:defines the number of bytes in the Data Payload.§Error Correction Code (ECC) * 1byte:allows single-bit errors to be corrected and 2-bit errors to be detected.v D ata P ayload (0~65535 bytes)§Length = WC ×bytesv P acket F ooter (2 bytes):Checksum§If the payload has length 0, then the Checksum calculation results in FFFFh§If the Checksum isn’t calculated, the Checksum value is 0000hv Packet Size§ 4 + (0~65535) + 2 = 6 ~ 65541 bytesData Types for Processor-sourced PacketsError Correction Codev P7 = 0v P6 = 0v P5 = D10^D11^D12^D13^D14^D15^D16^D17^D18^D19^D21^D22^D23 v P4 = D4^D5^D6^D7^D8^D9^D16^D17^D18^D19^D20^D22^D23v P3 = D1^D2^D3^D7^D8^D9^D13^D14^D15^D19^D20^D21^D23v P2 = D0^D2^D3^D5^D6^D9^D11^D12^D15^D18^D20^D21^D22v P1 = D0^D1^D3^D4^D6^D8^D10^D12^D14^D17^D20^D21^D22^D23 v P0 = D0^D1^D2^D4^D5^D7^D10^D11^D13^D16^D20^D21^D22^D23Checksumvunsigned char xx[] = {0x01,0x5a,0x5a,0x03,0x08,0x2A, 0x00,0x01,0x00,0xF8,0x00,0xF6,0x57,0x00,0X00,0xE5};v typedef unsigned short U16;v typedef unsigned char U8;v U16 CRC_test;v U16 crc16_update(U16 crc, U8 a);v int main()v {v U16 crc,i;v crc = 0xFFFF;v for (i=0; i<1; i++) crc = crc16_update(crc, xx[i]);v CRC_test = crc;v}v U16 crc16_update(U16 crc, U8 a) v {v int i;v crc ^=a;v for (i = 0; i < 8; ++i)v {v if (crc & 1) crc = (crc >> 1) ^ 0x8408;v else crc = (crc >> 1);v }v return crc;v}Peripheral-to-Processor LP Transmissionsv Detailed format description§Packet structure for peripheral-to-processor transactions is the same as for§the processor-to-peripheral directionv For a single-byte read response, valid data shall be returned in the first byte The second byte shall be sent as 00hv If the peripheral does not support Checksum it shall return 0000hPeripheral-to-Processor LP Transmissionsv Peripheral-to-processor transactions are of four basic types §Tearing Effect (TE):trigger message (BAh)§Acknowledge:trigger message (84h)§Acknowledge and Error Report:short packet (Data Type is 02h)§Response to Read Request:short packet or long packet•Generic Read Response、DCS Read Response(1byte, 2byte, multi byte)v Feature§BTA shall take place after every peripheral-to-processor transaction§Multi-Lane systems shall use Lane 0 for all peripheral-to-processor transmissions§Reverse-direction signaling shall only use LP mode of transmissionVideo Modev DSI supports three formats for Video Mode data transmission §Non-Burst Mode with Sync Pulses§Non-Burst Mode with Sync Events§Burst ModeSummary for DSIv DSI is a Lane-scalable interface.§One Clock Lane§One to Four Data Lanesv Transmission Mode§High-Speed signaling mode (differential signal) (100mV~300mV)§Low-Power signaling mode (single-ended signal) (0V~1.2V)•For returning data, only use Data Lane 0 in LP Modev Packet Types§Short Packet:4 bytes (fixed length)•Data ID (1byte) + Data0 (1byte) + Data1 (1byte) + ECC (1byte)§Long Packet:6~65541 bytes (variable length)•Packet Header (4 bytes) + Data Payload (0~65535 bytes) + Packet Footer (2 bytes) v Operation Mode§Command Mode (Similar to MPU IF)§Video Mode (Similar to RGB IF)•Non-Burst Mode with Sync Pulses•Non-Burst Mode with Sync Events•Burst Mode。

mipi协议详细介绍中文版

mipi协议详细介绍中文版Mipi协议详细介绍中文版协议签订双方甲方:(填写名称、法定代表人、地址、联系方式等)乙方:(填写名称、法定代表人、地址、联系方式等)各方身份、权利、义务、履行方式、期限、违约责任一、甲方身份甲方为Mipi协议的版权持有人和所有者,具有该协议相关权利。

二、乙方身份乙方是使用该协议的客户,需要严格遵守该协议的条款和条件。

三、甲方权利(1)对Mipi协议进行全部或部分授权。

(2)对违反Mipi协议的使用者采取追究法律责任的措施。

(3)其他法律规定和合同约定的权利。

四、乙方权利(1)在遵守协议的前提下,使用Mipi协议。

(2)享有协议规定的权利和自由。

(3)其他法律规定和合同约定的权利。

五、甲方义务(1)保护Mipi协议的版权。

(2)及时向乙方提供相关技术支持和帮助。

(3)对乙方在使用Mipi协议过程中提出的问题和反馈信息进行回复和解决。

(4)其他法律规定和合同约定的义务。

六、乙方义务(1)保证使用Mipi协议的合法性。

(2)严格遵守Mipi协议的条款和条件。

(3)不得将Mipi协议进行任何形式的拷贝、修改或衍生。

(4)根据协议进行付款。

(5)其他法律规定和合同约定的义务。

七、履行方式、期限和违约责任(1)Mipi协议的授权方式和期限由双方协商确定,协议期限届满后,协议自动终止。

(2)双方违反该协议的条款和条件,应对其导致的损失承担相应责任。

(3)追究责任方式由协议的合同文本达成一致,并在双方约定的期限内执行。

需遵守中国的相关法律法规八、个人信息保护和隐私保护(1)在涉及个人信息收集、保存、使用和公开等环节中,双方应遵守中国的个人信息保护法律法规和规范。

(2)在涉及隐私保护方面,双方应遵守中国的隐私保护法律法规和规范。

九、国家安全保障(1)双方应遵守中国的国家安全保障法律法规和规范。

(2)如果Mipi协议的使用涉及到国家安全、军事、外交、法律和其他重要利益的,应当获得相关机构、部门的许可和审批。

如何分析mipi协议

如何分析mipi协议MIPI协议是一种用于移动设备的通信协议,它在实现高速数据传输和接口标准化方面发挥着重要作用。

MIPI(Mobile Industry Processor Interface)是一个由移动设备行业联盟(MIPI Alliance)推出的标准化协议,旨在促进移动通信和嵌入式系统的技术发展。

本文将介绍如何分析MIPI协议以及其在移动通信领域的重要性。

首先,MIPI协议涵盖了多个不同的子协议,如MIPI D-PHY、MIPI CSI-2和MIPI DSI等。

其中,MIPI D-PHY是一种物理层协议,用于在芯片之间进行高速数据传输。

它提供了具有低功耗、高带宽和低干扰的特性,适用于移动设备的显示、摄像头和传感器等部件间的通信。

MIPI CSI-2(Camera Serial Interface 2)则是一种用于摄像头模块和图像处理器之间数据传输的协议,主要用于移动设备中的摄像头功能。

类似地,MIPI DSI(Display Serial Interface)是一种用于移动设备显示屏和图形处理器之间数据传输的协议。

在对MIPI协议进行分析时,可以从以下几个方面入手。

首先,了解协议的基本结构和通信原理是非常重要的。

可以查阅相关的技术文档和规范,掌握协议的各个层次以及数据帧的格式和传输方式。

其次,要深入了解协议的特性和特点。

MIPI协议在功耗管理、时序控制和数据处理方面都有一些独特的要求和特性,这些特性对于系统设计和开发至关重要。

此外,还需要了解协议的应用范围和实际场景。

MIPI协议主要应用于移动设备,如智能手机、平板电脑和可穿戴设备等,因此需要对这些设备的硬件和软件架构有一定的了解。

分析MIPI协议还可以从协议的优缺点以及应用案例等方面展开。

MIPI协议在提高数据传输速率、降低功耗、简化系统设计等方面有诸多优点。

首先,它提供了可靠的高速数据传输通道,使得移动设备可以实现更快速和稳定的数据传输。

mipi协议分析仪

mipi协议分析仪MIPI协议分析仪。

MIPI(Mobile Industry Processor Interface)协议是一种用于移动设备的串行接口协议,它被广泛应用于手机、平板电脑、相机、显示器等移动设备中。

MIPI协议分析仪是一种用于分析MIPI协议的工具,它可以帮助工程师们更好地理解和调试MIPI接口,提高产品的稳定性和性能。

本文将对MIPI协议分析仪的原理、功能和应用进行分析。

首先,MIPI协议分析仪的原理是基于MIPI协议的工作原理。

MIPI协议是一种高速、低功耗、低成本的串行接口协议,它采用了差分信号传输和串行通信的方式,能够在保证高速传输的同时降低功耗。

MIPI协议分析仪通过捕获、解码和显示MIPI接口上的数据,帮助工程师们了解数据的传输过程、时序关系、协议格式等信息,从而更好地分析和调试MIPI接口的问题。

其次,MIPI协议分析仪具有多种功能。

首先,它可以捕获MIPI接口上的数据,并对数据进行解码和显示,帮助工程师们直观地了解数据的传输过程和内容。

其次,它可以分析MIPI接口上的时序关系,帮助工程师们找出数据传输中的时序问题,提高接口的稳定性和可靠性。

另外,MIPI协议分析仪还可以对MIPI接口进行性能分析,帮助工程师们优化接口的性能和功耗。

总之,MIPI协议分析仪是工程师们分析和调试MIPI接口问题的重要工具。

最后,MIPI协议分析仪在移动设备领域有着广泛的应用。

随着移动设备的发展,MIPI接口已经成为了移动设备中最常用的接口之一,而MIPI协议分析仪则成为了工程师们分析和调试MIPI接口问题的利器。

它可以帮助工程师们快速定位和解决接口问题,提高产品的稳定性和性能。

因此,MIPI协议分析仪在移动设备的研发、生产和维护中具有非常重要的作用。

综上所述,MIPI协议分析仪是一种用于分析MIPI协议的工具,它通过捕获、解码和显示MIPI接口上的数据,帮助工程师们更好地理解和调试MIPI接口,提高产品的稳定性和性能。

mipi参数

mipi参数

MIPI是一种用于移动设备的串行接口协议。

它的参数包括:

1. 数据传输速度:MIPI协议支持多种传输速度,最高可达4.5 Gbps。

2. 信号传输方式:MIPI协议采用串行传输方式,使用高速差分信号传输数据。

3. 线数:MIPI协议支持多种不同数量的线数配置,包括1、2、3、4、5和8线。

4. 电源电压:MIPI协议的标准电源电压为1.2V和1.8V。

5. 信号格式:MIPI协议通过不同的信号格式传输不同类型的数据,包括视频、音频、命令和控制信号。

6. 协议版本:MIPI协议有多个版本,包括MIPI DSI(显示子系统接口)、MIPI CSI(摄像头子系统接口)和MIPI HSI(高速接口)等。

7. 抗干扰能力:MIPI协议具有较强的抗干扰性能,能够在高速数据传输过程中保持稳定信号传输。

MIPI协议详细介绍

MIPI协议详细介绍MIPI(Mobile Industry Processor Interface)是为移动设备设计的一种接口标准,由移动产业处理器接口工作组(Mobile Industry Processor Interface Working Group)所制定。

MIPI协议旨在提供移动设备所需的高性能、低功耗和低成本的接口解决方案。

MIPI协议的核心是一系列物理层和协议层规范。

在物理层上,MIPI 协议使用低压差分信号(Low Voltage Differential Signaling,LVDS)作为传输介质,以降低功耗和电磁干扰。

同时,MIPI协议还定义了一种叫做DSI(Display Serial Interface)的串行接口,用于连接显示器和处理器。

DSI接口支持传输图像、命令和控制信息,以及具有多种数据格式和分辨率的视频流。

在协议层上,MIPI协议提供了一系列协议规范,包括CSI(Camera Serial Interface)、RFFE(Radio Frequency Front-End)、SLIMbus (Serial Low-power Inter-chip Media Bus)、I3C(Improved Inter Integrated Circuit)等。

CSI接口用于连接摄像头和处理器,支持传输图像和控制信号。

RFFE接口用于连接射频模块和调制解调器芯片,支持传输射频频段切换和天线开关控制等功能。

SLIMbus接口用于连接多媒体芯片和音频处理器,支持音频、命令和控制信号的传输。

I3C接口是一种新兴的接口标准,旨在取代传统的I2C(Inter-Integrated Circuit)接口,提供更高的传输速率和更低的功耗。

除了物理层和协议层规范,MIPI协议还提供了一系列的软件驱动程序和API(Application Programming Interface),用于支持开发者在移动设备上使用MIPI接口的硬件功能。

MIPI协议归纳整理

MIPI DSI协议介绍2015.12.1jcl整理添加一、MIPIMIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。

MIPI(移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准。

二、MIPI联盟的MIPI DSI规范1、名词解释•DCS(DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。

•DSI,CSI(DisplaySerialInterface,CameraSerialInterface•DSI定义了一个位于处理器和显示模组之间的高速串行接口。

•CSI定义了一个位于处理器和摄像模组之间的高速串行接口。

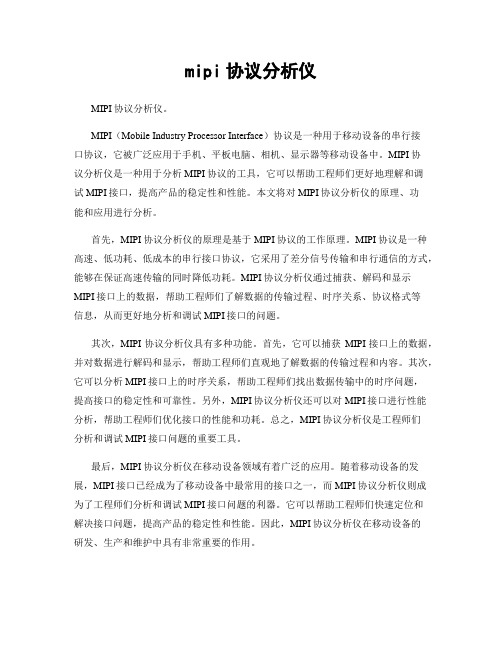

•D-PHY:提供DSI和CSI的物理层定义2、DSI分层结构DSI分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:•PHY定义了传输媒介,输入/输出电路和和时钟和信号机制。

•Lane Management层:发送和收集数据流到每条lane。

•Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

•Application层:描述高层编码和解析数据流。

3、Command和Video模式•DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定•Command模式是指采用发送命令和数据到具有显示缓存的控制器。

主机通过命令间接的控制外设。

Command模式采用双向接口•Video模式是指从主机传输到外设采用时实象素流。

这种模式只能以高速传输。

为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径三、D-PHY介绍1、D-PHY描述了一同步、高速、低功耗、低代价的PHY。

•一个PHY配置包括•一个时钟lane•一个或多个数据lane•两个Lane的PHY配置如下图•三个主要的lane的类型•单向时钟Lane•单向数据Lane•双向数据Lane•D-PHY的传输模式•低功耗(Low-Power)信号模式(用于控制):10MHz(max)•高速(High-Speed)信号模式(用于高速数据传输):80Mbps~1Gbps/Lane•D-PHY低层协议规定最小数据单位是一个字节•发送数据时必须低位在前,高位在后.•D-PHY适用于移动应用•DSI:显示串行接口•一个时钟lane,一个或多个数据lane•CSI:摄像串行接口2、Lane模块•PHY由D-PHY(Lane模块)组成•D-PHY可能包含:•低功耗发送器(LP-TX)•低功耗接收器(LP-RX)•高速发送器(HS-TX)•高速接收器(HS-RX)•低功耗竞争检测器(LP-CD)•三个主要lane类型•单向时钟Lane•Master:HS-TX,LP-TX•Slave:HS-RX,LP-RX•单向数据Lane•Master:HS-TX,LP-TX•Slave:HS-RX,LP-RX•双向数据Lane•Master,Slave:HS-TX,LP-TX,HS-RX,LP-RX,LP-CD3、Lane状态和电压•Lane状态•LP-00,LP-01,LP-10,LP-11(单端)•HS-0,HS-1(差分)•Lane电压(典型)•LP:0-1.2V•HS:100-300mV(200mV)4、操作模式•数据Lane的三种操作模式•Escape mode,High-Speed(Burst)mode,Control mode•从控制模式的停止状态开始的可能事件有:•Escape mode request(LP-11→LP-10→LP-00→LP-01→LP-00)•High-Speed mode request(LP-11→LP-01→LP-00)•Turnaround request(LP-11→LP-10→LP-00→LP-10→LP-00)•Escape mode是数据Lane在LP状态下的一种特殊操作•在这种模式下,可以进入一些额外的功能:LPDT,ULPS,Trigger•数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00•一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作•Escape mode使用Spaced-One-Hot Encoding•超低功耗状态(Ultra-Low Power State)•这个状态下,lines处于空状态(LP-00)•时钟Lane的超低功耗状态•时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态•通过LP-10→TWAKEUP→LP-11退出这种状态,最小TWAKEUP时间为1ms •高速数据传输•发送高速串行数据的行为称为高速数据传输或触发(burst)•全部Lanes门同步开始,结束的时间可能不同。

MIPI传输协议

MIPI传输协议篇一:MIPI接口协议简介MIPI接口简介(Mobile Industry Processor Interface移动行业处理器接口) 对于现代的智能手机来说,其内部要塞入太多各种不同接口的设备,给手机的设计和元器件选择带来很大的难度。

下图是一个智能手机的例子,我们可以看到其内部存储、显示、摄像、声音等内部接口都是各不相同的。

即使以摄像头接口来说,不同的摄像头模组厂商也可能会使用不同的接口形式,这给手机厂商设计手机和选择器件带来了很大的难度。

MIPI 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

MIPI 联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus等。

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

下图是按照 MIPI的规划下一代智能手机的内部架构。

MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。

CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。

以DSI为例,其协议层结构如下:CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。

D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。

数据传输采用DDR 方式,即在时钟的上下边沿都有数据传输。

D- PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。

HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps); LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。

MIPI-中文协议

对于现代的智能手机来说,其内部要塞入太多各种不同接口的设备,给手机的设计和元器件选择带来很大的难度。

下图是一个智能手机的例子,我们可以看到其内部存储、显示、摄像、声音等内部接口都是各不相同的。

即使以摄像头接口来说,不同的摄像头模组厂商也可能会使用不同的接口形式,这给手机厂商设计手机和选择器件带来了很大的难度。

MIPI (Mobile Industry Processor Interface) 是2003年由ARM,Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性. MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus等。

统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。

下图是按照 MIPI的规划下一代智能手机的内部架构.MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。

CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。

以DSI为例,其协议层结构如下:CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。

D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。

数据传输采用DDR方式,即在时钟的上下边沿都有数据传输.D— PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。

HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps); LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低.两种模式的结合保证了MIPI 总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

mipi协议

mipi协议1. 简介MIPI(Mobile Industry Processor Interface)协议是一种用于移动设备的串行接口协议,主要用于传输多媒体数据和控制信息。

它提供了一种高效、低功耗的通信方式,广泛应用于移动设备的摄像头、显示屏和其他传感器等模块之间的数据传输。

2. mipi协议的特点•高带宽:MIPI协议支持高速数据传输,可以满足高分辨率图像和视频的传输需求。

•低功耗:MIPI协议采用差分信号传输和低功耗时钟方案,有效降低了设备的功耗。

•灵活性:MIPI协议可以根据设备的需求进行配置,支持不同数据格式和传输速率的选择。

•可靠性:MIPI协议采用差错校验和流控制等机制,确保数据传输的可靠性。

•简化设计:MIPI协议提供了统一的接口标准,简化了设备的设计和开发过程。

3. mipi协议的应用3.1 摄像头模块MIPI协议被广泛应用于移动设备的摄像头模块。

摄像头模块通常由图像传感器、图像处理器和接口电路组成,其中接口电路使用MIPI协议进行数据传输。

使用MIPI协议可以实现高速、低功耗的图像数据传输,支持实时预览和拍照功能。

同时,MIPI协议还支持控制信息的传输,可以实现对摄像头模块的配置和控制。

3.2 显示屏模块MIPI协议也常用于移动设备的显示屏模块。

显示屏模块通常由显示驱动器、接口电路和显示屏组成,其中接口电路使用MIPI协议进行数据传输。

使用MIPI协议可以实现高分辨率、高帧率的图像显示,支持视频播放和游戏等应用场景。

同时,MIPI协议还支持触摸屏的数据传输,可以实现触摸输入功能。

3.3 其他传感器模块除了摄像头和显示屏模块,MIPI协议还被应用于其他传感器模块,如加速度计、陀螺仪和环境传感器等。

这些传感器模块可以通过MIPI协议与主控芯片进行数据通信,实现对环境、位置和姿态等信息的获取。

通过采集这些信息,可以为移动设备提供更多的功能和服务。

4. mipi协议的未来发展MIPI协议在移动设备领域的应用越来越广泛,随着移动设备的发展和需求的增加,MIPI协议也在不断演进和完善。

MIPI协议详细介绍

• LP:0~1.2V • HS:100~300mV (Swing:200mV)

▪ Lane States

• LP-00, LP-01, LP-10, LP-11 • HS-0, HS-1

❖ Three main lane types

▪ Unidirectional Clock Lane

• Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX

▪ Unidirectional Data Lane

• Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX

❖ Start-of-Transmission

▪ LP-11→LP-01→LP-00→SoT(0001_1101) ▪ HS Data Transmission Burst ▪ All Lanes will start synchronously ▪ But may end at different times ▪ The clock Lane shall be in High-Speed mode, providing a DDR

Clock to the Slave side

❖ End-of-Transmission

▪ H Toggles differential state immediately after last payload data bit

❖ and keeps that state for a time THS-TRAIL

application processors. ▪ Intends to speed deployment of new services to mobile users by

理解mipi协议(含5篇)

理解mipi协议(含5篇)第一篇:理解mipi协议理解mipi协议完成mipi信号通道分配后,需要生成与物理层对接的时序、同步信号:MIPI规定,传输过程中,包内是200mV、包间以及包启动和包结束时是1.2V,两种不同的电压摆幅,需要两组不同的LVDS驱动电路在轮流切换工作;为了传输过程中各数据包之间的安全可靠过渡,从启动到数据开始传输,MIPI定义了比较长的可靠过渡时间,加起来最少也有600多ns;而且规定各个时间参数是可调的,所以需要一定等待时间,需要缓存,我们用寄存器代替FIFO,每通道128Byte。

串行时钟与数据差分传输的过渡时间关系如下:各个时间参数需要满足以下的要求:UI 的值:数据与时钟的相位关系:根据前面文章:mipi差分信号原理介绍。

CLKp是高电平,CLKn是低电平的时候,差分信号表现为高电平。

CLKn是高电平, CLKp是低电平的时候,差分信号表现为低电平。

所以结果就可以等效成红线描述的正弦。

从正弦可以看出,data在clk的高电平和低电平都有传输数据。

数据通道进入和退出SLM(即睡眠模式)的控制:mipi信号传输分为单端和差分传输。

例如: LP-00, LP-01, LP-10, LP-11(单端)HS-0, HS-1(差分)Ultra-Low Power State entry command: 00011110 是差分传输,读取方法和上面提到的clk是一样的,需要注意的是Dp和Dn如果同时是高电平或同时是低电平的时候是无效数据,这个时候大概对应的是clk正弦的峰值,只有其中一个是高一个是低才是有效的差分数据。

总结:对应于同步信号完成并串转换;*HS 状态为高速低压差分信号,传输高速连续串行数据;*LP 状态为低速低功耗信号,传输控制信号和状态信号;*MIPI要求HS 工作在1GHz 的频率下,完成共模信号为0.2v 差模信号为0.2v 的差分信号的传输;*LP 传递控制信号,要求高电平为1.2v 低电平为0的电平信号输出;*HS 及LP 状态下,输出信号的电学特性要求非常苛刻,具体电学性能的要求可见附带文档表格。

MIPI协议详细介绍1

establishing Spec.

❖ Board Members in MIPI Alliance

▪ Intel, Motorola, Nokia, NXP,Samsung, ST, TI

▪ Bi-directional Data Lane ▪ Master, Slave:HS-TX, HS-RX,LP-TX, LP-RX, LP-CD

▪ DBI, DPI (Display Bus Interface, Display Pixel Interface)

• DBI:Parallel interfaces to display modules having display controllers and frame buffers.

• DPI:Parallel interfaces to display modules without on-panel display controller or frame buffer.

▪ DSI:Display Serial Interface

• A clock lane, One to four data lanes.

▪ CSI:Camera Serial Interface

Two Data Lane PHY Configuration

Lane Module

❖ PHY consists of D-PHY (Lane Module) ❖ D-PHY may contain

Introduction for D-PHY

❖ D-PHY describes a source synchronous, high speed, low power, low cost PHY ❖ A PHY configuration contains

MIPI协约详细介绍课件

• LP:0~1.2V • HS:100~300mV (Swing:200mV)

▪ Lane States

• LP-00, LP-01, LP-10, LP-11 • HS-0, HS-1

▪ DBI, DPI (Display Bus Interface, Display Pixel Interface)

• DBI:Parallel interfaces to display modules having display controllers and frame buffers.

• DPI:Parallel interfaces to display modules without on-panel display controller or frame buffer.

❖ Three main lane types

▪ Unidirectional Clock Lane

• Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX

▪ Unidirectional Data Lane

• Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX

application processors. ▪ Intends to speed deployment of new services to mobile users by

establishing Spec.

❖ Board Members in MIPI Alliance

关于MIPI测试!包含来源流程操作步骤等!干货满满

关于 MIPI 测试1,MIPI 协议相关简介1,MIPI 协议和联盟MIPI 协议,即移动产业处理器接口(Mobile Industry Processor Interface 简称 MIPI)。

MIPI 是由诺基亚、ARM、意法半导体、德州仪器、英特尔、飞思卡尔等厂商联盟发起的为移动应用处理器制定的开放标准和一个规范。

随着客户要求手机摄像头像素越来越高同时要求高的传输速度传统的并口传输越来越受到挑战。

提高并口传输的输出时钟是一个办法但会导致系统的 EMC 设计变得越来困难,增加传输线的位数是但是这又不符合小型化的趋势。

采用 MIPI 接口的模组相较于并口具有速度快、传输数据量大、功耗低、抗干扰好的优点越来越受到客户的青睐并在迅速增长。

2,MIPI 协议的主要应用领域2.5G、3G 手机、PDA、PMP、手持多媒体设备3,目前应用最为成熟的两个接口CSI(Camera Serial Interface)一个位于处理器和显示模组之间的高速串行接口DSI(Display Serial Interface)一个位于处理器和摄像模组之间的高速串行接口。

4,DSI 分层结构DSI 分四层,对应 D-PHY、DSI、DCS 规范、分层结构图如下:• PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

• Lane Management 层:发送和收集数据流到每条 lane。

• Low Level Protocol 层:定义了如何组帧和解析以及错误检测等。

• Application 层:描述高层编码和解析数据流。

5,MIPI 应用最广泛的物理层标准是 D-PHYMIPI DPHY 有两种工作模式:HS 和 LPHS:采用低压差分信号,为高速模式,传送速率 80M-1GbpsLP:单端信号,为低功耗模式,传输速率<10Mbps6,MIPI 测试MIPI 接口测试主要分为 D-PHY 物理层测试和逻辑层测试两部分。

MIPI 协议 中文入门

² 通用短写命令是一个通用的数据发送到外设的短数据包类型。这个包的内容,格式和 解释本规范的范围之外。这是系统设计师的责任,以确保主机处理器和外设上同意这些 数据的格式和解释。完整的包可以达到9字节长度包括ECC字节。的字节数的超越页眉 (DI)字节就是由一个3-bit领域明确规定,DT[5:3] 。

34

²

典型应用

30

DCS DSI D-PHY

31

² DSI Display Serial Interface 串行显示界面 ² DT Data Type 数据类型 ² ECC Error-Correcting Code 错误校正码 ² EMI Electro Magnetic interference辐射干扰 ² EoT End of Transmission 传输结束字 ² ESD Electrostatic Discharge 静电干扰 ² Fps Frames per second 帧率 ² HS High Speed 高速传送 ² ISTO Industry Standards and Technology Organization行业标准和技术的组织 ² LLP Low-Level Protocol 底层协议 ² LP Low Power 低功耗 ² LPI Low Power Interval低功耗区间 ² LPS Low Power State 低功耗状态(低功耗串行数据线的状态时,不会传送高速串行数据) ² LSB Least Significant Bit 最低位 ² Mbps Megabits per second 传输速度 ² MIPI Mobile Industry Processor Interface 移动接口协议 ² MSB Most Significant Bit 最高位 ² PE Packet End数据包结束 ² PF Packet Footer数据包尾 ² PH Packet Header 数据包头 ² PHY Physical Layer 物理层

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• DSI specifies a high-speed serial interface between a host processor and display module.

❖ D-PHY low-level protocol specifies a minimum data unit of one byte

▪ A transmitter shall send data LSB first, MSB last.

❖ D-PHY suited for mobile applications

• CSI specifies a high-speed serial interface between a host processor and camera module.

▪ D-PHY

• D-PHY provides the physical layer definition for DSI and CSI.

Introduction for D-PHY

❖ D-PHY describes a source synchronous, high speed, low power, low cost PHY ❖ A PHY configuration contains

▪ A Clock Lane ▪ One or more Data Lanes

What is MIPI?

❖ MIPI Alliance Specification for display

▪ DCS (Display Command Set)

• DCS is a standardized command set intended for command mode display modules.

❖ Three main lane types

▪ Unidirectional Clock Lane ▪ Unidirectional Data Lane ▪ Bi-directional Data Lane

❖ Transmission Mode

▪ Low-Power signaling mode for control purpose:10MHz (max) ▪ High-Speed signaling mode for fast-data traffic:80Mbps ~ 1Gbps per Lane

▪ DSI:Display Serial Interface

• A clock lane, One to four data lanes.

▪ CSI:Camera Serial Interface

Two Data Lane PHY Configuration

Lane Moduleห้องสมุดไป่ตู้

❖ PHY consists of D-PHY (Lane Module) ❖ D-PHY may contain

application processors. ▪ Intends to speed deployment of new services to mobile users by

establishing Spec.

❖ Board Members in MIPI Alliance

▪ Intel, Motorola, Nokia, NXP,Samsung, ST, TI

▪ Bi-directional Data Lane ▪ Master, Slave:HS-TX, HS-RX,LP-TX, LP-RX, LP-CD

MIPI Protocol Introduction

MIPI Development Team 2010-9-2

What is MIPI?

❖ MIPI stands for Mobile Industry Processor Interface ▪ MIPI Alliance is a collaboration of mobile industry leaders. ▪ Objective to promote open standards for interfaces to mobile

▪ Low-Power Transmitter (LP-TX) ▪ Low-Power Receiver (LP-RX) ▪ High-Speed Transmitter (HS-TX) ▪ High-Speed Receiver (HS-RX) ▪ Low-Power Contention Detector (LP-CD)

▪ DBI, DPI (Display Bus Interface, Display Pixel Interface)

• DBI:Parallel interfaces to display modules having display controllers and frame buffers.

• DPI:Parallel interfaces to display modules without on-panel display controller or frame buffer.

❖ Three main lane types

▪ Unidirectional Clock Lane

• Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX

▪ Unidirectional Data Lane

• Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX

DSI Layers

DCS spec DSI spec D-PHY spec

Outline

❖ D-PHY

▪ Introduction ▪ Lane Module, State and Line

levels ▪ Operating Modes

• Escape Mode

▪ System Power States ▪ Electrical Characteristics ▪ Summary