PS2设备通信协议 时序图

PS2鼠标接口协议

PS2鼠标接口协议协议名称:PS2鼠标接口协议一、介绍PS2鼠标接口协议是一种用于连接计算机和鼠标之间的通信协议。

该协议规定了数据传输格式、通信流程以及错误处理等方面的内容,以确保计算机和鼠标之间的稳定通信。

二、数据传输格式1. 数据帧格式PS2鼠标接口协议使用异步串行通信方式传输数据,数据帧由8个bit组成,其中包括1个起始位、1个停止位和6个数据位。

数据帧的格式如下所示:起始位数据位0 数据位1 数据位2 数据位3 数据位4 数据位5 停止位2. 通信速率PS2鼠标接口协议支持的通信速率为1200bps。

三、通信流程1. 初始化计算机在启动时,需要向鼠标发送初始化命令,以建立通信连接。

初始化命令的格式如下所示:发送:0xFF接收:0xFA2. 数据传输一旦通信连接建立成功,计算机可以向鼠标发送指令,鼠标将根据指令执行相应的操作,并将结果返回给计算机。

指令的格式如下所示:发送:0xFX(X为指令码)接收:0xFA(表示指令执行成功)或0xFE(表示指令执行失败)3. 中断当鼠标有新的数据需要传输给计算机时,会发送一个中断信号,以通知计算机接收数据。

计算机在接收到中断信号后,可以通过读取数据寄存器来获取鼠标发送的数据。

四、错误处理1. 通信错误如果在通信过程中发生错误,计算机会发送复位命令给鼠标,以重新建立通信连接。

复位命令的格式如下所示:发送:0xFF接收:0xFA2. 指令错误如果鼠标接收到无法识别的指令,将返回错误码给计算机,表示指令执行失败。

计算机可以根据错误码来判断具体的错误类型,并进行相应的处理。

五、安全性考虑为了保证通信的安全性,PS2鼠标接口协议还提供了数据校验功能。

每个数据帧的最后一个bit是校验位,计算机和鼠标都会对数据进行校验,以确保数据的完整性和准确性。

六、总结PS2鼠标接口协议是一种用于连接计算机和鼠标之间的通信协议,它规定了数据传输格式、通信流程以及错误处理等方面的内容。

PS2设备通信协议 时序图

Ps2设备到主机的通信

• 图中绿色的信号表示由Ps2设备产生的。也就是 说PS2设备在产生时钟的同时向主机送出数据, 主机在PS2CLK信号的下降沿读取每个位 。 • 当PS2CLK频率为15kHz时,从PS2CLK(时钟脚) 的上升沿到数据位转变时间至少要5μs。数据变化 到PS2CLK(时钟脚)下降沿的时间至少也有5 μs, 但不能大于25 μs,这是由PS/2通讯协议的时序规 定的。(一般不用考虑,这由键盘或者鼠标产生)

7

2 3 4 0-7 0-7 0-7

Y overflow

X data (D0-D7) Y data (D0-D7) 高四位是符号扩展位,低四位是滚轮的移动计数值

键盘缺省设置状态

• 在上电或软件复位 (见 Reset 命令) 后 键盘执行诊断自检叫做 BAT( 基本保证测 试)并载入如下的缺省值 : • 击打延迟为 500ms • 击打速率为 10.9cps • *第二套扫描码集 • *置所有按键为机打/通码/断码

Ps2鼠标的工作模式和协议数据包格式

• Ps2鼠标四种工作模式

从主机到PS/2设备的数据的传输时序图

• 绿色信号由ps2设备产生,黄色信号由主机产生 • 由于PS/2设备能提供串行同步时钟,因此,如果主 机发送数据,则主机要先把时钟线和数据线置为请 求发送的状态。主机通过下拉时钟线大于 100μs来 抑制通讯,并且通过下拉数据线发出请求发送数据 的信号,然后释放时钟,PS/2设备检测到需要接收 的数据时,它会产生时钟信号并记录下面8个数据位 和一个停止位。主机此时在时钟线变为低时准备数 据到数据线,并在时钟上升沿锁存数据。

– Reset模式,当鼠标上电或者主机发出reset命 令(ff)时,进入这种模式 – Stream模式:鼠标默认的模式,当鼠标上电或 者复位完成后,自动进入此模式 – Remote模式:和主机交互模式 – Wrap模式,用于测试鼠标和主机连接是否正确

PS_2接口微机键盘协议分析及其应用

福 建 电

脑

20 0 8年第 6期

P / 口微 机键 盘 协 议分 析 及 其应 用 S2接

吕 庭 .吴 正 阳

(常 熟理 工 学 院 信 息与 控 制 工 程 系 江 苏 常 熟 2 5 0 ) 15 0

【 摘

要 】 详细介绍和分析 了 P I : S2键盘 的接 口规范 、 向同步 串4  ̄ i 第二 套键 盘扫描码 集、 双 5 z、 - 通信命令 字和 通信 时

一 . 一 . 一 . 一 一 . 一

维普资讯

20 0 8年第 6期

福

建 电

脑

9 5

上 图 A 部分 . 机拉 低 时 钟 线 到 设 备 产 生 时 钟 的时 问不 得 主

当 A 8 S 1 到 HD 2 9送 来 的按 键 编 码 并转 换 为 键 盘 扫 T9 5 收 77

( 钟 脚 ) 是 集 电极 开 路 的 双 向 信 号线 , 须 接 大 阻值 的上 拉 反 。 时 都 必 电阻 . 阻值 在 1 1k间 。它 们 平 时 处 于 高 电平 状 态 , 要 输 出低 —0 需 当 主 机发 送 完 停 止位 后 .设 备 通过 将 数 据 线 拉 低来 产 生 应 c 电平 时 可 以很 容 易 的 被拉 低 . 之后 仍 旧 回到 高 电平 状 态 。 两 个 答 信 号 A k以表 示接 收 到 一 帧 数据 .同时 时 钟 线产 生 最后 一 个 这 S2设 引脚 主机 和 键 盘 都 可 以控 制 . 在 P / 议 中 主 机 具 有 较 高 的 时 钟 。 图 3为 详 细 的主 机 到 P / 备 通 讯 时 序图 。 但 S2协 控 制权 。 时 22P, . s2通信 协 议 主机 P/ S2通信 协 议 是一 种 双 向同 步 串行 协 议 。 同步 时 钟 总是 由 数 \ j ^ ^ ^ ^ ^ ^ ^ ^ / 据线 ^ ; L 一 一 . . D — . . . . 一 一 P/ 备 产生 . 信 双 方均 可 通 过 数 据线 发 送 数 据 , S2设 通 当时 钟 线 上 ] n 几 n 几 几 n 几 n n 厂 n 产生 一 脉 冲 时 .数 据 线上 发 送 的数 据 被 接 收方 读 入 。传 输 过 程 设备 投 据缱 中 。 机 拥 有 总 线 控 制 权 . 以 随 时把 时钟 线 一 直 拉 低来 抑 制 来 主 可 图 3 主 机 到 P / 备详 细 时 序 图 S2设 自键盘 的通 讯 主 机 和 P / 备间 传 输 数据 的最 大 时 钟频 率 为 S2设

FPGA基础设计_PS2键盘控制及短按、长按

FPGA基础设计_PS2键盘控制及短按、长按

PS2键盘也是一个经典的实验,可能很多人接触如何对通信协议、时序编程就是从这个实验开始学习的。

USB键盘已经很普及,现在市场上还是有一些USB转PS2的转接头,还有一些转换芯片。

这个实验虽然简单,不过不知道您有考虑过单按一次输出一个有效脉冲、短按、长按等这些是如何实现的么?这就涉及到一些时钟、边沿检测等设计问题。

PS2协议实现

我们见到的PS2的接口电路应该都是这样的:

一根时钟线、一根数据线完成通信,PS2通信的帧格式如下所示,时钟的下降沿数据有效:

按键在被按下时,会发送一个字节,这个码就是通码;按键在释放时,会发送两个字节,这个码就做断码(当然也有例外)。

每一个按键都有唯一的通码和断码,据此进行判断按下的是哪个键,从而执行对应的功能。

如一部分按键的通码和断码如下所示:

可以看出断码其实就是在通码前加了一个F0,比如A的通码是1C,则它的断码是F01C。

另外一些特殊功能的按键,在通码和断码前都会加个E0。

PS2解码的代码如下所示:

//-----------------ps2_clk下降沿捕获--------------------

//clk相当于中间采样点的作用,第一个下降沿到来说明起始位开始

reg ps2_clk0,ps2_clk1,ps2_clk2;//缓冲寄存器

wire ps2_clk_neg; //1表示检测到下降沿

reg ps2_state;

always @ (posedge clk or negedge rst_n)

if (!rst_n)

{ps2_clk0,ps2_clk1,ps2_clk2} 《= 3‘d0;

else。

PS2通讯协议

中小系统上位机通讯协议2004-11-2DL451-91(CDT)通讯规约采用RS232通讯接口;波特率支持1200、2400、4800、9600,字符格式10位(1位起始位、8位数据、1位停止位)。

1.帧定义1.1.帧结构1.2.同步字发送:EBH 90H EBH 90H EBH 90H,共6个字节。

1.3.控制字控制字共有B7 – B12 共6个字节,定义如下:1.3.1.控制字节控制字节定义如下:E:扩展位,E=0 表示使用本协议已定义帧类别码,E=1帧类别码可自定义,本协议中总为0L:帧长定义位,E=0 表示本帧无信息字,E=1 表示本帧有信息字,本协议中总为1S:源站地址有效D:目的站地址有效(上行信息中,S=1,D=1,源站地址为直流设备设置地址,目的站地址为上位机地址,固定为01H。

)(下行信息中,D=1, 目的站地址为直流设备设置地址)1.3.2.帧类别码帧类别码定义如下:1.3.3.信息字数信息字数n表示该帧中所含信息字数量;n=0表示本帧无信息。

1.3.4.校验码本协议采用CRC校验,校验多项式为107H,为信息字前5字节构成码流,后面加8个0,得到48位码流,用校验多项式作为除数除以码流,相除时做异或;最后得到8位余数取反后既为校验码。

例如:信息字为;43h E8h 7DH 33H 56H 计算余数为2FH,取反后为D0H,发送序列为:43h E8h 7DH 33H 56H D0H。

1.4.信息字1.4.1.信息字结构每个信息字由6个字节构成:功能码1字节,信息4字节校验码1字节。

功能码定义功能码定义如下:1.4.2.信息字格式遥测:每个信息字传送2路遥测量,每个遥测量包含2字节,先送低字节,后送高字节。

b11 – b0 表示一路模拟量,以2进值表示,b11=0表示正,b11=1表示负,以二进值补码表示负数。

b14=1表示溢出,b15=1表示无效,b12 b13 未使用。

遥信:每个信息字传送32个遥信量。

PS2通信协议说明与接口定义(键盘和鼠标)

PS2键盘与鼠标的接口定义针脚定义:原理PS/2鼠标接口采用一种双向同步串行协议。即每在时钟线上发一个脉冲,就在数据线上发送一位数据。在相互传输中,主机拥有总线控制权,即它可以在任何时候抑制鼠标的发送。方法是把时钟线一直拉低,鼠标就不能产生时钟信号和发送数据。在两个方向的传输中,时钟信号都是由鼠标产生,即主机不产生通信时钟信号。如果主机要发送数据,它必须控制鼠标产生时钟信号。方法如下:主机首先下拉时钟线至少100μs 抑制通信,然后再下拉数据线,最后释放时钟线。通过这一时序控制鼠标产生时钟信号。当鼠标检测到这个时序状态,会在10ms内产生时钟信号。如图3中A 时序段。主机和鼠标之间,传输数据帧的时序如图2、图3所示。2.2 数据包结构在主机程序中,利用每个数据位的时钟脉冲触发中断,在中断例程中实现数据位的判断和接收。在实验过程中,通过合适的编程,能够正确控制并接收鼠标数据。但该方案有一点不足,由于每个CLOCK都要产生一次中断,中断频繁,需要耗用大量的主机资源。PS/2鼠标的四种工作模式是:Reset模式,当鼠标上电或主机发复位命令0xFF给它时进入这种模式;Stream模式鼠标的默认模式,当鼠标上电或复位完成后,自动进入此模式,鼠标基本上以此模式工作;Remote模式,只有在主机发送了模式设置命令0xF0后,鼠标才进入这种模式;Wrap模式,这种模式只用于测试鼠标与主机连接是否正确。PS/2鼠标在工作过程中,会及时把它的状态数据发送给主机。发送的数据包格式如表1所示。Byte1中的Bit0、Bit1、Bit2分别表示左、右、中键的状态,状态值0表示释放,1表示按下。Byte2和Byte3分别表示X轴和Y轴方向的移动计量值,是二进制补码值。Byte4的低四位表示滚轮的移动计量值,也是二进制补码值,高四位作为扩展符号位。这种数据包由带滚轮的三键三维鼠标产生。若是不带滚轮的三键鼠标,产生的数据包没有Byte4 其余的相同。一.PS/2 鼠标键盘协议PC 键盘可以有6 脚的mini-DIN 或5 脚的DIN 连接器如果你的键盘是6 脚的mini-DIN 而你的计算机是5 脚的DIN 或者相反这两类连接器可以用上面提到的适配器来兼容具有6 脚mini-DIN 的键盘通常被叫做PS/2 键盘而那些有5 脚DIN 叫做AT 设备XT 键盘也使用5 脚DIN 但它们非常古老并且多年前就不生产了所有现代的为PC 建造的键盘不是PS/2,AT 就是USB 的这篇文章不适用于USB 设备它们使用了一种完全不同的接口。

PS-2接口原理

PS/2鼠标协议原理(中文)按照PS/2协议,移动时,鼠标会输出一组时钟和数据信号;而在静止时,时钟和数据信号将一直保持为逻辑高电平,表示处于空闲状态。

每次移动时,鼠标会向主机发送3个数据帧,每个数据帧11位,包括1个起始位“0”、8个数据位(低位在前)、1个奇校验位和一个结束位“1”,因此每次移动时,鼠标会向主机发送33位数据,其中第0、11和22位是起始位“0”,第10、21和32位是结束位“1”,如图5.7所示。

图5.7 PS/2鼠标的数据传送在图5.7 中,“Mouse status byte”、“X direction byte”和“Y direction byte”三个字节的数据是鼠标移动产生的相关数据,包括状态、X方向数据和Y方向数据。

按照PS/2协议,鼠标数据在时钟CLK的下降沿有效,而时钟CLK的频率要求在20KHz~30KHz之间。

基于PS/2协议的鼠标采用相对坐标的形式来追踪它的移动轨迹,如图5.8所示。

如果鼠标水平向右移动,则得到一个正的X值;否则,得到一个负的X值。

如果鼠标竖直向上移动,则得到一个正的Y值;否则,得到一个负的Y值。

使用“0”表示正值;而使用“1”表示负值。

在“Mouse status byte”数据字节中,XS和YS就表示了鼠标的移动方向。

图5.8 PS/2鼠标的相对坐标相对坐标中,X值和Y值表示了鼠标的移动速度,值越大表示鼠标的移动速度越大。

“Mouse status byte”数据字节中,XV和YV则标识鼠标的移动是否超出了范围,包括X方向和Y 方向。

如果超出了范围,则XV或YV置位为1。

“Mouse status byte”数据字节中,L和R 则分别表示鼠标的左键和右键,如果有键按下,则相应的L或R置位。

如果鼠标一直移动,则图 5.7所示的33个位的数据不停发送,重复周期约为50ms。

按照PS/2协议,移动时,鼠标会输出一组时钟和数据信号;而在静止时,时钟和数据信号将一直保持为逻辑高电平,表示处于空闲状态。

PS2设备通信协议

电气特性

• PS/2通讯协议是一种双向同步串行通讯协议。通 讯的两端通过Clock(时钟脚)同步,并通过 DATA(数据脚)交换数据。任何一方如果想抑制另 外一方通讯时,只需要把Clock(时钟脚)拉到低电 平。如果是PC机和PS/2键盘间的通讯,则PC机 必须做主机,也就是说,PC机可以抑制PS/2键 盘发送数据,而PS/2键盘则不会抑制PC机发送数 据。一般两设备间传输数据的最大时钟频率是3 3kHz,大多数PS/2设备工作在10~20kHz。推 荐值在15kHz左右,也就是说,Clock(时钟脚)高、 低电平的持续时间都为40μs。每一数据帧包含 11~12个位,具体含义如表1所列。

PS2设备通信协议

时序图

PS2接口和协议

• 接口简介 • 1981年IBM推出了IBM PC/XT键盘及其接 口标准。 经过多年演变成6脚mini-DiN连 接器接口,封装上更小巧,用双向串行通 讯协议并且提供有可选择的第三套键盘扫 描码集,同时支持17个主机到键盘的命令。 现在,市面上的键盘都和PS/2及AT键盘兼 容

主机(即PC)到PS/2设备的传输

• 主机若想影响传输,必须能够控制总线时钟!对于 主机而言,控制PS/2总线有三种状态 状态 PS2D ATA 高 高 低 PS2 Note CLK 高 低 为了传输能够发送串 行数据到一位寄存器 高 输出端,控制器要求 PS2设备产生PTransmission Host Send Request

Ps2键盘

• 如果它发现有键被按下,释放或按住,键盘 将发送 扫描码的信息包到计算机。扫描码有 两种不同的类型 通码 和 断码 。当一个键被 按下或按住就发送通码,当一个键被释放就 发送断码。每个按键被分配了唯一的通码和 断码。这样主机通过查找唯一的扫描码就可 以测定是哪个按键。每个键一整套的通断码 组成了扫描码集,有三套标准的扫描码集分 别是第一套 第二套和第三套。 所有现代的 键盘默认使用第二套扫描码。

PS2接口通信协议解析

11

PS/2 鼠送数据:

标准鼠标在初始化完成后以数据包的格式发送数据 下图为标准鼠标数据包,由三个比特的数据组成,每个比特以一个 上文介绍的数据帧的形式发送(即数据帧中的8个数据位),即一个 数据包由三个数据帧组成 数据包包括鼠标的位移情况,左、中、右键的点击信息

13

PS/2时钟信号的滤波

PS/2时钟信号存在毛刺,应对其进行滤波操作,以免影响接 口电路的稳定性 对时钟的滤波参考代码

该代码使用移位寄存器对时钟进行滤波操作。 设计滤波器时注意时钟接口为双向,只对输入时钟滤波

14

A

B

C

5

主机发送的数据帧结构

主机发送的数据帧结构(A 部分)

主机端:拉低时钟信号超过100us,然后释放时钟线并同时将数 据线拉低 鼠标端:检测到以上变化后开始发送时钟信号,并准备接受来自 主机的数据

A

6

主机发送的数据帧结构

主机发送的数据帧结构(B 部分)

鼠标端:发出时钟信号 主机端:根据鼠标发送的时钟信号发送8位数据位,1位奇 校验位及1位停止位(停止位为”1”)

12

PS/2 鼠标通信流程

标准PS/2鼠标向主机发送的数据包的结构:

X movement为上一个数据包发送后鼠标在X方向上的位置变化绝对值 X sign bit 为上一个发送后鼠标在X方向上的位置变化值的符号 Y方向上的变化类似 Middle Btn、 Right Btn、 Left Btn记录了鼠标中、右、左三键的点击情况。 Y overflow, X overflow记录Y movement 、X movement是否有溢出

基于单片机的PS2键盘设计

PS2键盘在单片机上的应用摘要:在嵌入式PC应用系统中,作为人机交互设备的键盘,往往采用结构简单按键少的矩阵键盘。

标准键盘虽然能直接与嵌入式PC机的PS/2接口相连,但是体积大,按键多,不能满足需求,本文提出用一种AT89C52单片机实现具有标准PS/2接口的矩阵键盘,具有便捷,实用的特点。

关键词:PS/2接口,PS/2键盘,拨号键,AT89C52,LCD1602Abstract:PS/2 interface is one of the most useful mouse interface.It was IBM’s patent named osulum before. It is the dedicate interface of mouse and keyboard. This text implied a plan using PS/2 to make a system. PS/2 tansmit the data which was pressed, and AT89C52 receive it ,disposed it and transmit it to Lcd1602. Lcd1602 discover it to make us know which key has been pressed. PS/2 simulate a phone’s dial keyboard. This system’s feature is the circuit is sample and useful.Keywords:PS/2 keyboard, AT89C52, LCD1602,PS/2 interface,dial keyboard目录1、前言 (1)2、整体方案设计 (2)2.1方案论证 (2)2.2方案比较 (3)3、单元模块设计 (4)3.1PS2键盘模块 (4)3.2单片机模块 (6)3.3LCD显示模块 (7)4、软件设计 (9)5、系统技术指标及精度和误差分析 (10)6、结论 (11)7、设计小结 (12)8、致谢 (14)9、参考文献 (14)附录1:电路总图 (15)附录2:仿真图 (16)附录3:软件代码 (17)1、前言单片机因其性价比高, 处理能力强, 且抗干扰能力好, 在医疗器械、机电液控制、数据传输等各类工控系统和设备仪器中得到广泛应用。

PS2接口通信协议分析

7

用数字示波器记录 键盘时钟及键盘数 据信号

8

松开A键时记录的串行数据波形

键盘时钟

串行数据 低位在前

9

PS/2键盘接口程序模块分析

PS/2键盘接口程序分为两个主要模块: 模块1:键盘数据接收及分析

滤波:键盘产生的数据具有毛刺,需要滤波 接收数据

接收11个串行数据,串并转换。 奇偶校验 提取其中8位扫描码

PS/2接口通信协议分析

1

PS/2 键盘通信原理

PS/2设备履行一种双向同步串行协议 PS/2键盘的通信可分为:

键盘——〉主机 主机——〉键盘 主机可以是计算机、实验板等,这里我们特 指FPGA实验板。

2

键盘各针的定义

1、数据输入、输出 2、未定义 3、地 4、电源(+5V) 5、键盘时钟 6、未定义

5

程产生的数据分析 举例:按下和松开一次“A”键时产生的数据, 注意低位在前

第1组:00011100001(按下,扫描码1C ) 第2组:00000111111(松开前一组,扫描码F0) 第3组:00011100001(松开后一组,扫描码1C )

3

PS/2键盘接口协议分析

每按一个键会产生如下数据

按下产生一组串行数据; 松开产生两组串行数据

每组串行数据11-12位,从低位开始传输; 每组数据包括

1位起始位,低电平; 8位数据位(即扫描码),从低位开始传输; 1位奇偶校验位

如果扫描码中1的个数为奇数,该位取0; 如果扫描码中1的个数为偶数,该位取1。

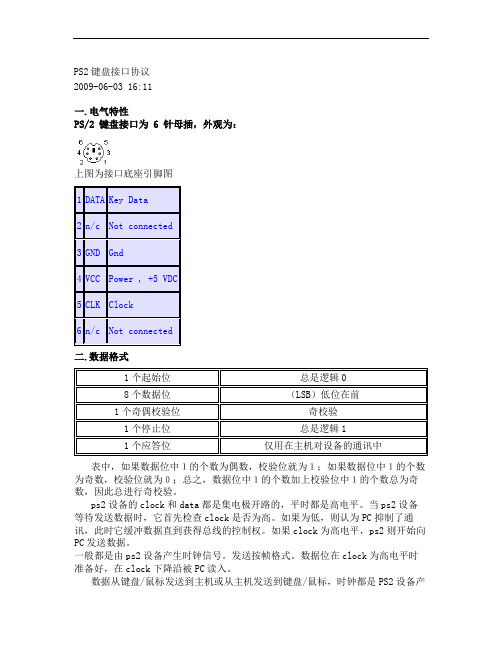

PS2键盘接口协议

PS2键盘接口协议2009-06-03 16:11一.电气特性PS/2 键盘接口为 6 针母插,外观为:上图为接口底座引脚图1DATA Key Data2n/c Not connected3GND Gnd4VCC Power , +5 VDC5CLK Clock6n/c Not connected二.数据格式1个起始位总是逻辑08个数据位(LSB)低位在前1个奇偶校验位奇校验1个停止位总是逻辑11个应答位仅用在主机对设备的通讯中表中,如果数据位中1的个数为偶数,校验位就为1;如果数据位中1的个数为奇数,校验位就为0;总之,数据位中1的个数加上校验位中1的个数总为奇数,因此总进行奇校验。

ps2设备的clock和data都是集电极开路的,平时都是高电平。

当ps2设备等待发送数据时,它首先检查clock是否为高。

如果为低,则认为PC抑制了通讯,此时它缓冲数据直到获得总线的控制权。

如果clock为高电平,ps2则开始向PC发送数据。

一般都是由ps2设备产生时钟信号。

发送按帧格式。

数据位在clock为高电平时准备好,在clock下降沿被PC读入。

数据从键盘/鼠标发送到主机或从主机发送到键盘/鼠标,时钟都是PS2设备产生.主机对时钟控制有优先权,即主机想发送控制指令给PS2设备时,可以拉低时钟线至少100μS,然后再下拉数据线,最后释放时钟线为高。

PS2设备的时钟线和数据线都是集电极开路的,容易实现拉低电平。

PC在时钟的下降沿读取数据.PS: ps2协议是现在大多数鼠标,键盘与PC通讯的标准协议,鼠标的通讯更为简单些,只是传送的数据内容不一样而已。

三.数据发送时序键盘接口时序(a) 键盘发送时序;(b) 键盘接收时序从PS/2向PC机发送一个字节可按照下面的步骤进行:(1)检测时钟线电平,如果时钟线为低,则延时50μs;(2)检测判断时钟信号是否为高,为高,则向下执行,为低,则转到(1);(3)检测数据线是否为高,如果为高则继续执行,如果为低,则放弃发送(此时PC机在向PS/2设备发送数据,所以PS/2设备要转移到接收程序处接收数据);(4)延时20μs(如果此时正在发送起始位,则应延时40μs);(5)输出起始位(0)到数据线上。

ps2键盘协议_资料

键盘接口时序(a) 键盘发送时序;(b) 键盘接收时序从PS/2向PC机发送一个字节可按照下面的步骤进行:(1)检测时钟线电平,如果时钟线为低,则延时50μs;(2)检测判断时钟信号是否为高,为高,则向下执行,为低,则转到(1);(3)检测数据线是否为高,如果为高则继续执行,如果为低,则放弃发送(此时PC机在向PS/2设备发送数据,所以PS/2设备要转移到接收程序处接收数据);(4)延时20μs(如果此时正在发送起始位,则应延时40μs);(5)输出起始位(0)到数据线上。

这里要注意的是:在送出每一位后都要检测时钟线,以确保PC机没有抑制PS/2设备,如果有则中止发送;(6)输出8个数据位到数据线上;(7)输出校验位;(8)输出停止位(1);(9)延时30μs(如果在发送停止位时释放时钟信号则应延时50μs);通过以下步骤可发送单个位:(1)准备数据位(将需要发送的数据位放到数据线上);(2)延时20μs;(3)把时钟线拉低;(4)延时40μs;(5)释放时钟线;(6)延时20μs。

PS/2设备从PC机接收一个字节由于PS/2设备能提供串行同步时钟,因此,如果PC机发送数据,则PC机要先把时钟线和数据线置为请求发送的状态。

PC机通过下拉时钟线大于100μs来抑制通讯,并且通过下拉数据线发出请求发送数据的信号,然后释放时钟。

当PS/2设备检测到需要接收的数据时,它会产生时钟信号并记录下面8个数据位和一个停止位。

主机此时在时钟线变为低时准备数据到数据线,并在时钟上升沿锁存数据。

而PS/2设备则要配合PC机才能读到准确的数据。

具体连接步骤如下:(1)等待时钟线为高电平。

(2)判断数据线是否为低,为高则错误退出,否则继续执行。

(3)读地址线上的数据内容,共8个bit,每读完一个位,都应检测时钟线是否被PC机拉低,如果被拉低则要中止接收。

(4)读地址线上的校验位内容,1个bit。

(5)读停止位。

(6)如果数据线上为0(即还是低电平),PS/2设备继续产生时钟,直到接收到1且产生出错信号为止(因为停止位是1,如果PS/2设备没有读到停止位,则表明此次传输出错)。

ps2接口与通信

一ps2接口(1)母插头母插头引脚定义:(2)公插头公插头引脚定义:二ps2设备数据帧格式1个起始位总是逻辑08个数据位(LSB)低位在前1个奇偶校验位奇校验1个停止位总是逻辑11个应答位仅用在主机对设备的通讯中表中,如果数据位中1的个数为偶数,校验位就为1;如果数据位中1的个数为奇数,校验位就为0;总之,数据位中1的个数加上校验位中1的个数总为奇数,因此总进行奇校验。

三PS/2设备和PC机的通讯PS/2设备的clock(时钟脚)和data(数据脚)都是集电极开路的,平时都是高电平。

当PS/2设备等待发送数据时,它首先检看clock(时钟脚)以确认其是否为高电平。

如果是低电平,则认为是PC机抑制了通讯,此时它必须缓冲需要发送的数据直到重新获得总线的控制权(一般PS/2键盘有16个字节的缓冲区,而PS/2鼠标只有一个缓冲区仅存储最后一个要发送的数据)。

如果clock(时钟脚)为高电平,PS/2设备便开始将数据发送到PC机。

一般都是由PS/2设备产生时钟信号。

发送时一般都是按照数据帧格式顺序发送。

其中数据位在clock(时钟脚)为高电平时准备好,在clock时钟脚的下降沿被PC机读入。

当时钟频率为15kHz时,从clock(时钟脚)的上升沿到数据位转变时间至少要5μs。

数据变化到clock(时钟脚)下降沿的时间至少也有5μs,但不能大于25μs,这是由PS/2通讯协议的时序规定的。

如果时钟频率是其它值,参数的内容应稍作调整。

上述讨论中传输的数据是指对特定键盘的编码或者对特定命令的编码。

一般采用第二套扫描码集所规定的码值来编码。

其中键通码(Make)和断码(Break)。

通码是按键接通时所发送的编码,用两位十六进制数来表示,断码通常是按键断开时所发送的编码,用四位十六进制数来表示。

实例:从键盘/鼠标发送到主机的数据在时钟信号的下降沿(当时钟从高变到低的时候)被读取;从主机发送到键盘/鼠标的数据在上升沿(当时钟从低变到高的时候)被读取。

PS2协议

一,PS2引脚定义1,DATA引脚:数据引脚*集电极开路:空闲高电平2,N/C:没有连接3,GND:电源地4,VCC:电源5,CLK:时钟:一般由PS2设备产生*集电极开路:空闲高电平6,N/C:没有连接二,数据格式1个起始位:逻辑08个数据位:LSB先行1个奇偶位:奇校验1个停止位:逻辑11个应答位:用在主机对设备的通讯中*奇校验:数据位中1的个数+校验位中1的个数=奇数三,数据逻辑PS2发送数据:1,检测CLK电平,如果电平位低->主机抑制通讯如果电平位高->主机正常通讯2,PS2设备产生CLK时钟,数据位在高电平期间准备数据位在下降沿期间被主机读取注意:CLK有PS2从机产生,但是主机对CLK有优先权。

PS2接收数据:拉低CLK至少100us下拉DATA释放时钟为高四,时序逻辑发送时序:a接受时序:b发送一个字节步骤:1,检测CLK电平,如果CLK为低->延时50us2,检测CLK电平,为高执行步骤3,为低执行步骤13,检测DATA电平,为高继续执行,为低放弃操作转为接收4,延时20us5,输出起始位0:每准备发送一次数据,检测一次CLK,确保PC没有抑制发送6,输出数据位(LSB先行)7,输出校验位8,输出停止位19,延时30us单个位发送逻辑:1,准备DATA2,延时20us3,拉低时钟4,延时40us5,释放时钟6,延时20us接收一个字节步骤:1,等待CLK为高2,判断DATA是否为低,为高退出3,读DATA位内容,共8Bit,(每读一位检测CLK是否被主机拉低,拉低中断) 4,读取地址线校验内容5,读停止位内容(非1,继续产生时钟,直到接收到1且产生出错信号)6,输出应答位7,检测奇偶校验位(失败则放弃)8,延时45us,以便PC下次传输接收一个位步骤:1,延时20us2,把CLK拉低3,延时40us4,释放CLK5,延时20us6,读数据应答信号1,延时15us2,把DATA拉低3,延时5us4,把CLK拉低5,延时40us6,释放CLK7,延时5us8,释放DATA五,键码键盘处理器检测到有按键按下or释放时,会发送扫描码信号给主机。

基于51单片机的PS2键盘1602显示24c02存储的密码锁设计(附程序)

基于51单片机的PS2键盘密码锁设计摘要:AT89S52是一种低功耗、高性能CMOS 8位微控制器,具有8K在系统可编程Flash 存储器,被广泛应用于各个领域。

LCD1602液晶显示器以其微功耗、体积小、超薄轻巧等诸多优点而备受人们喜爱。

本作品是以AT89S52作为主控芯片,LCD1602作为显示器,以PS2键盘作为输入设备的密码锁。

PS2键盘与AT89S52通过PS2接口协议进行通信,可以完成密码设置,密码重置及显示等诸多功能。

本作品还使用了24C02存储器来实现密码锁的掉电保存功能。

关键词:AT89S52;LCD1602;24C02;PS2键盘Abstract:AT89S52 is a low power,high performance CMOS 8 bit microcontroller, with 8K flash memory, is widely applied in various fields. LCD1602 liquid crystalDisplay with its low power consumption, small size, thin lightweight and many other advantages, is liked by people.This work is based on the AT89S52 as the main chip, the LCD1602 as display, PS2 keyboard as an input device of the cipher lock. PS2 keyboard and AT89S52 through PS2 interface protocolFor communication, can complete password, password reset and display and other functions. This work we also used the 24C02 memory to realize the password lock the power-down save function.Keywork: A T89C52; LCD1602; 24C02;PS/2 keyboard1 实验目的及意义在单片机系统中,经常使用的键盘都是专用键盘.此类键盘为单独设计制作的,成本高、使用硬件连接线多,且可靠性不高,这一状况在那些要求键盘按键较多的应用系统中更为突出.与此相比,在PC系统中广泛使用PS/2键盘具有价格低、通用可靠,且使用连接线少(仅使用2根信号线)的特点,并可满足多种系统的要求.因此在单片机系统中应用PS/2键盘是一种很好的选择.对于单片机初学者的我而言,AT89S52简单易学,非常适合我学习。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主机到PS/2设备的传输

• PS2控制器必须进入主机发送请求(Host Send Request)的状态。这可以通过以下动作实现: • PS2CLK线首先被拉低至少在一个时钟周期(进 入禁止传输Inhibit Transmission状态) • PS2DATA线随后被拉低(提供的起始位帧传送) • PS2CLK线随后被释放(仍然保持PS2DATA低)。 • PS/2设备定期检查数据和时钟线是否为这种状态, 当检测到,开始产生PS2CLK信号。 • 在从主机向PS/2设备发送数据时,PS2一帧数据由 10个域构成。见时序图

Ps2键盘

• 如果它发现有键被按下,释放或按住,键盘 将发送 扫描码的信息包到计算机。扫描码有 两种不同的类型 通码 和 断码 。当一个键被 按下或按住就发送通码,当一个键被释放就 发送断码。每个按键被分配了唯一的通码和 断码。这样主机通过查找唯一的扫描码就可 以测定是哪个按键。每个键一整套的通断码 组成了扫描码集,有三套标准的扫描码集分 别是第一套 第二套和第三套。 所有现代的 键盘默认使用第二套扫描码。

Description

3

4 5

6

7 2 3 0-7 0-7

Left button status;1=pressed Right button status;1=pressed Middle button status;1=pressed Reserve X data sign; 1=negative Y data sign; 1=negative Reserve Reserve X data (D0-D7) Y data (D0-D7)

Ps2设备到主机的通信

• 图中绿色的信号表示由Ps2设备产生的。也就是 说PS2设备在产生时钟的同时向主机送出数据, 主机在PS2CLK信号的下降沿读取每个位 。 • 当PS2CLK频率为15kHz时,从PS2CLK(时钟脚) 的上升沿到数据位转变时间至少要5μs。数据变化 到PS2CLK(时钟脚)下降沿的时间至少也有5 μs, 但不能大于25 μs,这是由PS/2通讯协议的时序规 定的。(一般不用考虑,这由键盘或者鼠标产生)

电气特性

• PS/2通讯协议是一种双向同步串行通讯协议。通 讯的两端通过Clock(时钟脚)同步,并通过 DATA(数据脚)交换数据。任何一方如果想抑制另 外一方通讯时,只需要把Clock(时钟脚)拉到低电 平。如果是PC机和PS/2键盘间的通讯,则PC机 必须做主机,也就是说,PC机可以抑制PS/2键 盘发送数据,而PS/2键盘则不会抑制PC机发送数 据。一般两设备间传输数据的最大时钟频率是3 3kHz,大多数PS/2设备工作在10~20kHz。推 荐值在15kHz左右,也就是说,Clock(时钟脚)高、 低电平的持续时间都为40μs。每一数据帧包含 11~12个位,具体含义如表1所列。

7

2 3 4 0-7 0-7 0-7

Y overflow

X data (D0-D7) Y data (D0-D7) 高四位是符号扩展位,低四位是滚轮的移动计数值

主机(即PC)到PS/2设备的传输

• 主机若想影响传输,必须能够控制总线时钟!对于 主机而言,控制PS/2总线有三种状态 状态 PS2D ATA 高 高 低 PS2 Note CLK 高 低 为了传输能够发送串 行数据到一位寄存器 高 输出端,控制器要求 PS2设备产生PS2CLK

Idle

Inhibit Transmission Host Send Request

带滚轮的鼠标的数包格式

Byte 1 Bit 0 1 2 3 4 5 6 Description Left button status;1=pressed Right button status;1=pressed Middle button status;1=pressed always 1 X data sign; 1=negative Y data sign; 1=negative X overflow

– Reset模式,当鼠标上电或者主机发出reset命 令(ff)时,进入这种模式 – Stream模式:鼠标默认的模式,当鼠标上电或 者复位完成后,自动进入此模式 – Remote模式:和主机交互模式 – Wrap模式,用于测试鼠标和主机连接是否正确

流模式下数据包格式

Byte Bit

1 0 1 2

PS2设备通信协议

时序图

PS2接口和协议

• 接口简介 • 1981年IBM推出了IBM PC/XT键盘及其接 口标准。 经过多年演变成6脚mini-DiN连 接器接口,封装上更小巧,用双向串行通 讯协议并且提供有可选择的第三套键盘扫 描码集,同时支持17个主机到键盘的命令。 现在,市面上的键盘都和PS/2及AT键盘兼 容

键盘缺省设置状态

• 在上电或软件复位 (见 Reset 命令) 后 键盘执行诊断自检叫做 BAT( 基本保证测 试)并载入如下的缺省值 : • 击打延迟为 500ms • 击打速率为 10.9cps • *第二套扫描码集 • *置所有按键为机打/通码/断码

Ps2鼠标的工作模式和协议数据包格式

• Ps2鼠标四种工作模式

PS/2接口硬件

• 物理连接器 这两种连接器都只有四个脚有意义。 它们分 别是Clock(时钟脚)、DATA数据脚 、+5V (电源脚)和Ground(电源地)。在PS/2键盘与 PC机的物理连接上只要保证这四根线 一一对应 就可以了。PS/2键盘靠PC的PS/2端口提供+5V 电源,另外两个脚Clock(时钟脚)和DATA数据脚 都是集电极开路的,所以必须接大阻值的上拉电 阻。它们平时保持高电平,有输出时才被拉到低 电平,之后自动上浮到高电平。

从主机到PS/2设备的数据的传输时序图

• 绿色信号由ps2设备产生,黄色信号由主机产生 • 由于PS/2设备能提供串行同步时钟,因此,如果主 机发送数据,则主机要先把时钟线和数据线置为请 求发送的状态。主机通过下拉时钟线大于 100μs来 抑制通讯,并且通过下拉数据线发出请求发送数据 的信号,然后释放时钟,PS/2设备检测到需要接收 的数据时,它会产生时钟信号并记录下面8个数据位 和一个停止位。主机此时在时钟线变为低时准备数 据到数据线,并在时钟上升沿锁存数据。

• 表1 数据帧格式说明 1个起始位 总是逻辑0 8个数据位 ,低位在前 1个奇偶校验位(奇校验) 1个停止位 总是逻辑1 1个应答位 仅用在主机对设备的通讯中

奇校验

• 如果数据位中1的个数为偶数,校验位就为 1;如果数据位中1的个数为奇数,校验位 就为0

PS/2设备和PC机的通讯

• PS/2设备的Clock(时钟脚)和DATA数据脚 都是集 电极开路的,平时都是高电平。当PS/2设备等待发 送数据时,它首先检查Clock (时钟脚)以确认其是 否为高电平。如果是低电平,则认为是PC机抑制 了通讯,此时它必须缓冲需要发送的数据直到重新 获得总线的控制权(一般PS/2键盘有 16个字节的 缓冲区,而PS/2鼠标只有一个缓冲区仅存储最后一 个要发送的数据)。如果Clock(时钟脚)为高电平, PS/2设备便开始将数据发送到 PC机。一般都是由 PS/2设备产生时钟信号。发送时一般都是按照数 据帧格式顺序发送。其中数据位在Clock(时钟脚) 为高电平时准备好,在Clock (时钟脚)的下降沿被 PC机读入。PS/2设备到PC机的通讯时序如图2所 示。