开关电源六级能效详解

扬杰科技--美国六级能效标准介绍

49<Pno≤250

扬州扬杰电子科技股份有限公司

追求品质 持续创新 勤简守信 忠诚感恩

美国DoE VI(六级能效)标准介绍

• 美国能源部(DoE)在2013发布了一则建议规则制定的公告 (NOPR),这个标准主要针对:电池充电器与外部电源的节能 标准也就是DoE VI。该标准就电源包括电源适配器,充电器,开 关电源等外置电源(包括电池充电系统(BCS)和/或外部电源 (EPS),在条例限定上,或者是增多限定,或者就是在现有限

扬州扬杰电子科技股份有限公司

追求品质 持续创新 勤简守信 忠诚感恩

欧盟CoC V5标准介绍

•

欧盟正在独立推进外部电源的自愿性和强制性计划,以进一步提高外

部电源(电源适配器、开关电源、充电器等外置电源)的能效要求。目 前欧盟外部电源的强制要求为ErP指令外部电源实施条例EC 278/2009。

欧盟在2013.3月份发布外部电源能源效率行为准则CoC v5的草案进一步

扬州扬杰电子科技股份有限公司

追求品质 持续创新 勤简守信 忠诚感恩

CoC V5草案中对外部电源空载模式下功耗的要求 (不包括低压外部电源)

额定输出功率 (Pno) 主动模式时四个测试点的平均 效率 第一阶段 0<Pno<1 1<Pno≤49 ≥0.50* Pno+0.145 第二阶段 ≥0.50* Pno+0.16 动模式时10%额定输出电流时的 平均效率 第一阶段 第二阶段

特殊规格 最大能源消耗(千瓦时/年)

<20v 对于Ebatt<355.18Wh时,=20.06; 对于Ebatt>355.18Wh时, =0.0219*Ebatt+12.28; 对于Ebatt239.48Wh=30.37; 对于Ebatt≥239.48Wh=0.0495*Ebatt+18.51 =0.502*Ebatt+12.28

六级能效电源适配器到底是什么

六级能效电源适配器到底是什么?随着电源适配器的发展,消费者对它的要求也越来越高,各式各样的标准都需要符合,才能更好的应对当前的市场。

目前电源适配器的标准都是说六级能效,那么六级能效电源适配器到底是什么呢?它这个标准哪里来的?美国能源署(DoE)在2013发布了一则建议规则制定的公告(NOPR),这个标准主要针对:电池充电器与外部电源的节能标准也就是DoE VI。

该标准就电源包括电源适配器,充电器,开关电源等外置电源(包括电池充电系统(BCS)和/或外部电源(EPS),在条例限定上,或者是增多限定,或者就是在现有限定上其要求标准变得更严格。

任何充电产品或有外部电源(EPS)的都将在此条例影响范围之内。

该条例包括:提供产品相应标贴,并极有可能要求在美国能源部(DoE)网站上注册产品。

原来在1998年,美国劳伦斯?伯克利国家实验室(LBNL)的工作人员针对当年美国用电情况提出了一个估算:单就美国,一年的待机功耗就占全部住宅用电的5%,这相当于一年的能源成本为30亿美元。

据美国能源署(DoE)统计,2014年美国住宅用电总量为12.9亿兆瓦时,因此浪费5%就是6400万兆瓦时,这相当于浪费了18个典型电站所生产的电量。

六级能效要求很高,0-50W以下功率电源要求待机功耗小于100mW,而这对于电源IC企业来说既是挑战也是机会。

目前,国内已经有不少的电源管理IC 企业针对六级能效标准推出了相关的产品。

相较于以前的能效标准,六级能效标准主要有三个变化:更低的待机功耗、平均效率的最优化以及10%的负载效率要求。

现在,更严格的标准正准备于2016年生效,以此帮助消费者一年节省650万家庭用电。

目前美国和加拿大都采用六级标准。

OEM厂商需要了解这些新的要求,并且在产品升级时要跟随这些要求,以确保符合标准,以及避免罚款和出货延误。

由于OEM厂商需要有一个通用电源平台,以便他们的产品出口到世界各地,因此大部分外置电源制造商现在需要达到六级要求。

能效六_Level 6_与能效五_Level 5_比较

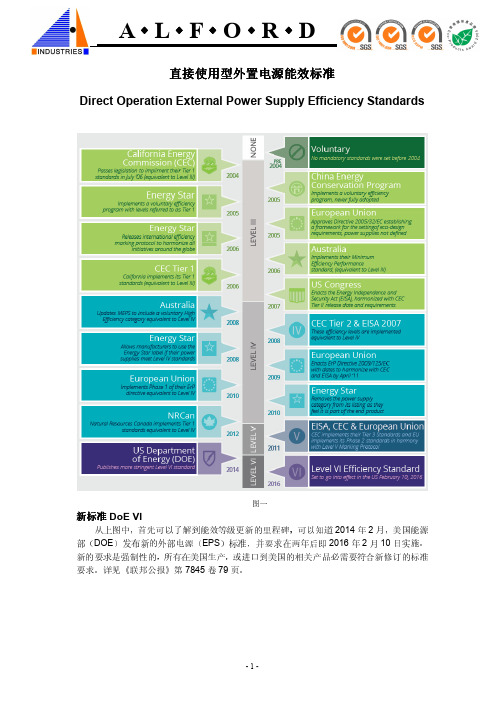

直接使用型外置电源能效标准Direct Operation External Power Supply Efficiency Standards图一新标准DoE VI从上图中,首先可以了解到能效等级更新的里程碑,可以知道2014年2月,美国能源部(DOE)发布新的外部电源(EPS)标准,并要求在两年后即2016年2月10日实施。

新的要求是强制性的,所有在美国生产, 或进口到美国的相关产品必需要符合新修订的标准要求。

详见《联邦公报》第7845卷79页。

图二回顾旧标准限值(PS:AC-AC未列出)图三 能效标准VI 限值增加增加的的外接电源外接电源要求要求对比图二与图三新旧标准,首先发现内容增多。

新增内容为: 1-Multiple-voltage external power supply (多电压输出的EPS )。

2-输出功率大于250W 的EPS 。

提高效率要求1-空载效率要求图四以low-voltage AC-DC EPS 为例,在0-49W 的要求中,Level V 无负载的功耗要求小于0.3W ,而新标准Level VI 要求小于0.1W 。

见图四。

2-负载效率要求图六 单路输出Vo≥6V 为例,系列1为level VI ,系列2为level V从曲线图可以看出,随着功率的增大,新旧版的差异越来小,相差在1%。

但随着输出功率的减小,效率差值越来越大。

图五从图五我们可以发现,在输出功率小于36W以下,则需改善效率需要提高3%以上。

直接与间接使用型外置电源新标准还对“直接工作EPS”和“间接工作EPS”进行了区分。

直接工作EPS是指,无需在电池的协助下即可在其最终应用(非电池充电器)中工作的EPS。

间接工作EPS是指,不在电池的协助下就无法在其最终应用(非电池充电器)中工作的EPS。

在这项法规中还包含一个程序,即确定最终产品是直接工作还是间接工作。

间接工作产品不受更严的新要求影响,它们只须在2016年2月后符合现行的EISA 2007效率限值。

开关电源6级能效标准

开关电源6级能效标准开关电源是一种常见的电子设备,用于将电能转换为适合各种电子设备使用的电源。

随着能源消耗和环保意识的增强,各国对电源能效的要求也越来越高。

为了促进能源节约和减少环境污染,许多国家都制定了一系列的能效标准,其中包括了开关电源的能效标准。

我国《开关电源6级能效标准》是指在实际使用中,开关电源的能效等级达到国家规定的标准,以减少能源浪费,保护环境。

根据标准规定,开关电源的能效等级分为1级至6级,其中1级为最高能效等级,6级为最低能效等级。

各级能效标准对开关电源的能效要求逐级提高,以促进开关电源制造商不断提升产品能效水平,降低能源消耗。

实施《开关电源6级能效标准》有助于推动我国开关电源行业技术进步,提高产品能效水平,减少能源浪费,降低环境污染。

同时,这也有利于消费者选择更节能的产品,降低用电成本,促进可持续发展。

在实际生产中,制造商需要根据标准要求对开关电源进行技术升级和改进,以满足不同能效等级的要求。

通过采用更先进的技术和材料,优化设计结构,提高转换效率,降低待机功耗等手段,制造商可以有效提高产品的能效等级,满足市场需求。

对于消费者来说,了解并选择符合《开关电源6级能效标准》的产品是非常重要的。

在购买开关电源时,消费者可以通过查看产品能效等级标识,了解产品的能效水平,从而选择更节能、环保的产品。

这不仅有利于节约能源,降低用电成本,还可以促进制造商生产更高能效的产品。

另外,政府部门也可以通过加强对开关电源产品的能效监管,推动市场向高能效产品转变。

通过建立健全的能效认证和监督体系,加大对产品的抽检力度,严格执行能效标准,可以有效提高市场上产品的整体能效水平,推动行业向更加环保、节能的方向发展。

总的来说,实施《开关电源6级能效标准》是促进我国开关电源行业可持续发展的重要举措。

这不仅有利于降低能源消耗,减少环境污染,还可以促进技术创新,提高产品质量,满足消费者需求。

因此,各方应共同努力,推动《开关电源6级能效标准》的全面落实,为我国开关电源行业的可持续发展做出贡献。

开关电源6级能效标准与计算.xls

开关电源6级能效标准与计算一、背景介绍1.1 开关电源概述开关电源作为一种电能转换装置,在现代电子设备中应用广泛。

它将电源电压转换为适合设备使用的电压,并且在输出电压稳定的同时具有高效率、小体积和轻便等优点。

开关电源已经成为各种电子产品的核心部件之一。

1.2 能效标准的意义节能减排是当前全球范围内的热门话题,能效标准作为节能减排的一种重要手段,对于推动产品能效水平提升,降低资源消耗,减少环境污染具有十分重要的意义。

其中,开关电源的能效标准更是受到了广泛关注。

二、 6级能效标准介绍2.1 能效标准的等级划分根据国家相关标准,开关电源能效等级分为0级至6级,等级越高说明效率越高,能耗越低。

而随着技术的不断进步,推动了能效标准不断提高,从而更好地适应市场需求。

2.2 6级能效标准的要求6级能效标准是目前国内对于开关电源能效的最高标准,要求在待机模式和工作模式下都能够达到很高的能效水平,从而有效降低能耗,减少资源浪费。

三、 6级能效标准计算3.1 能效标准计算原理开关电源6级能效标准的计算是基于一定的测试条件和方法进行的,主要包括待机模式和工作模式两种情况下的能效计算。

3.2 计算方法6级能效标准的计算方法十分严格,需要按照国家相关标准进行测试,并结合相应的计算公式进行计算。

四、如何提升开关电源能效4.1 技术创新利用先进的技术手段,提升开关电源的转换效率,减少能耗损耗。

4.2 产品设计优化产品结构、布局和材料选择,以提高产品能效水平。

4.3 节能意识加强用户节能意识,提高产品使用效率,从源头上减少能源消耗。

五、结语5.1 发展前景随着能效标准不断提高,开关电源的绿色、高效、节能特点将更加凸显,对于推动节能减排、减少环境污染将发挥越来越重要的作用。

5.2 挑战与机遇开关电源行业将面临更高的能效要求,培育技术创新、产品设计和用户节能意识将成为行业发展的关键。

高标准的能效要求也将为行业带来更多的机遇,促进行业更加健康可持续的发展。

美国电源6级能效标准

美国电源6级能效标准简介能源效率是目前全球关注的一个重要问题,电源设备的能源使用对整个社会和环境都具有重要意义。

为了鼓励和促使电源设备制造商生产和提供更加高效的产品,美国制定了一系列的电源能效标准。

其中,美国电源6级能效标准是其中的一项重要标准。

本文将对美国电源6级能效标准进行介绍和解读。

什么是美国电源6级能效标准美国电源6级能效标准是指电源设备的能耗标准,对于相关电源设备的制造和销售起到了指导和规范作用。

根据美国能源部的定义,电源设备包括了交流-直流电源适配器,开关电源和电池充电器等设备,其额定输出功率范围为15瓦到250瓦。

该标准的目的是限制电源设备的无负载功耗和工作负载的能效。

美国电源6级能效标准的主要内容根据美国电源6级能效标准,电源设备的能效等级从1级到6级,其中6级为最高能效级别。

具体规定如下:1.一级:无要求,为基准能效级别。

2.二级:无要求,为基准能效级别。

3.三级:电源设备在无负载状态下的功耗不得超过0.1瓦。

4.四级:电源设备在工作负载状态下的能效需达到一定程度的要求。

5.五级:电源设备在工作负载状态下的能效需达到一定程度的要求。

6.六级:电源设备在工作负载状态下的能效需达到最高要求。

美国电源6级能效标准强调的是电源设备在工作负载状态下的能效,即设备在实际工作中的能耗效率。

这一标准的出台,对于整个电源设备制造行业有着重要影响。

美国电源6级能效标准对相关产业的影响1.电源设备制造商:为符合美国电源6级能效标准要求,制造商需要改进其产品设计,提高设备的能效水平,以满足更严格的能效要求。

这将推动电源设备制造商加大技术研发的投入,提高产品的竞争力。

2.电源设备使用者:美国电源6级能效标准的实施,将推动市场上更加高效的电源设备产品的出现。

使用者可以选择能效更高的设备,以减少电能的浪费,降低能源消耗。

3.环境保护:电源设备的能效改进将减少能源的消耗,减少化石燃料的燃烧,减少二氧化碳等温室气体的排放,对于环境保护具有积极意义。

开关电源适配器的能效标准

开关电源适配器的能效标准

开关电源适配器的能效标准

开关电源适配器具有其他电源所无法比拟的优势,使开关电源技术的发展非常迅速。

开关电源用途广,所用新原材料、新技术发展之快,是它快速发展的主要动力。

但是,开关电源适配器在体积、重量、工作效率、抗干扰性能、电磁兼容性、待机功耗,以及使用的安全性等方面还有许多待改进之处。

绝大多数的电子产品,用遥控按键关机后,如果不将电源插头从插座上拔下,就会一直消耗功率。

如有线电视机顶盒,电视机、DVD 播放器等始终都在消耗着功率。

所有带LCD显示屏、LED显示屏、触摸板控制的电器,例如电磁炉、冰箱或空调等,它们一直都在通电运行。

手机充电器在不充电时,如果不从插座拔下来,也会不断地消耗功率。

今天,随着越来越多的电子产品出现在我们日常生活中,世界各地的政府机构和行业组织都纷纷制定相应的能耗规范标准,以帮助更好地控制产品的待机功耗和转换效率、节约成本以保护环境和提升市场层次。

比如欧盟的ErP指令,美国CEC,澳洲MEPS等。

国际上开关电源适配器能效的具体要求如下表:

这就是国际上外置电源适配器能效等级标准。

由罗马数字I、II、III、IV、V、VI等表示出外置电源适配器的空载功耗和转换效率。

总的来说,等级越高就表示电源适配器的转换效率越高、空载功耗越低。

开关电源6级能效标准与计算

输入电压

输入功率

输出电压

输出电流 0.25 A 0.50 A

输出功率 0.00 W 0.00 W 0.00 W 0.00 W 0.00 W

转换效率 #DIV/0! #DIV/0! #DIV/0! #DIV/0! #DIV/0!

平均效率

130.00%

115Vac 60Hz

0.75 A 1.00 A 0.10 A

230Vac

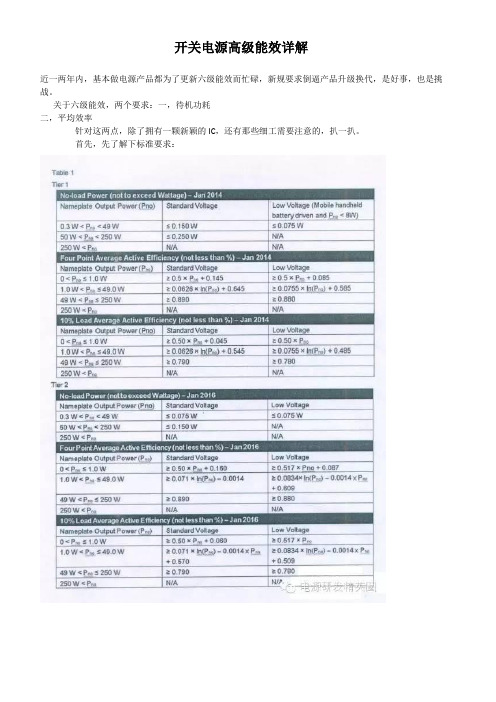

Level VI 能效标准(CoC) AC-DC基本电压外部电源

最低平均效率 ≥0.5*Pout+0.169 ≥0.071*ln(Pout)-0.00115*Pout+0.67 ≥ 0.880 最大待机功耗 ≤ 75mW ≤ 75mW ≤ 150mW

AC-DC低电压(<6V)外部电源

最低平均效率 ≥ 0.517 * Pout + 0.091 ≥0.0834*ln(Pout)-0.0011*Pout+0.609 ≥ 0.870 最大待机功耗 ≤ 75mW ≤ 75mW ≤ 150mW

Level VI 能效标准(CoC) AC-DC基本电压外部电源

最低平均效率 ≥0.5*Pout+0.169

电源六级能效要求

电源六级能效要求电源六级能效要求(Energy Efficient Level VI)是指用于电源适配器、带电池电源以及其他类型的电源的能源效率要达到的标准。

这一标准的制定旨在促进电源产品的节能减排,减少资源消耗和环境污染。

下面将从电源六级能效要求的背景、适用范围、标准规定以及对行业和消费者的影响等方面来深入探讨。

电源六级能效要求的背景是为了满足全球对节能减排的要求。

随着技术的不断进步和对环境保护意识的增强,能源效率已经成为当今社会可持续发展的重要要素。

电源产品是电子设备中的重要组成部分,而电源适配器等电源产品在使用过程中通常会存在一定的能量损耗,因此提高电源产品的能效已经成为一个重要的需求。

电源六级能效要求适用于一系列电源产品,包括但不限于交流(AC)-直流(DC)电源适配器、LED驱动器、充电器、无线充电器、逆变器和UPS电源等。

这些电源产品的能源效率要求根据其功率等级而有所不同。

对于不同功率等级的电源产品来说,其能源效率要求也有所不同。

根据电源六级能效要求的规定,电源产品在待机模式下的能源损耗要小于或等于一定值。

此外,电源产品在额定负载以及低负载、中负载和高负载条件下的能源效率也要符合相应的要求。

同时,电源产品在负载变化时能够保持有效的能源转换效率,以提高其整体能源利用率。

电源六级能效要求的实施对行业和消费者都有一定的影响。

对于电源产品制造商来说,他们需要提升电源产品的设计和制造能力,以满足更严格的能效要求。

这将推动行业技术的创新和发展。

对于消费者来说,购买符合电源六级能效要求的产品,不仅可以降低能源消耗和电费支出,还可以减少环境污染。

总结起来,电源六级能效要求是为了促进电源产品的节能减排而制定的标准。

该标准适用于电源适配器、带电池电源以及其他类型的电源。

电源产品制造商需要提升设计和制造能力以满足更严格的能效要求,消费者也可以通过购买符合标准的产品来降低能源消耗和电费支出。

这一标准的实施将推动电源产品技术的创新和发展,促进社会的可持续发展。

六级能效

12W 以下 AC-DC 应用包括:电源适配器、充电器、电磁炉、空调、DVD、机顶盒等家 电产品。

深圳东科半导体有限公司 Http: TEL:4008-781-212

1

DK1208——12W 高性能准谐振开关电源控制芯片

封装与引脚定义(DIP8)

HV VCC

DK

FB 检测和反馈控制:

Fb 引脚外部连接一只电容,以平滑Fb 电压,外接电容会影响到电路的反馈瞬态特 性及电路的稳定工作,典型应用可在1nF~10nF 之间选择;芯片依据FB电压控制PWM输 出峰值电流和工作频率。

SLEEP 模式:

为实现超低待机功耗,芯片设计了 SLEEP 模式时,当输出功率逐渐下降到 50mW 以 下时,芯片进入 SLEEP 模式。可以实现系统超低的待机功耗(<80mW)。

2:RS计算:

系统PWM输出为准谐振模式,输出电压越低,频率越慢,需要的Ip电流越大。在低 压准谐振时,RS的阻值计算公式如下:

RS = 0.135*Vin _ min*Vor *******(1), Po *(Vin _ min+Vor)

Po:

输出功率

Vin_min: 交流输入电压经过滤波后直流电压平均值,这个电压和输入滤波电容有

自供电:

芯片使用了专利的自供电技术,控制VDD的电压在4.7V左右,提供芯片本身的电流 消耗,无需外部辅助绕组提供。自供电电路只能提供芯片自身的电流消耗,不能为外部 线路提供能量。

过温保护(OTP):

芯片在内部集成了过温保护功能,如果因外部温度过高或者其它异常原因造成芯片 温度过高,检测到芯片温度超过 130℃,立即启动过温保护,停止输出脉冲,关断功率 管并进入异常保护模式,温度异常解除后恢复正常工作。

6级能效标准与计算

平均效率

76.00%

115Vac 60Hz

40.88 W 54.97 W

74.19%

74.00% 72.00%

CoC 10% Load 标准

70.00%

Efficiency

待机功耗 输入电压

45 mW 输入功率 13.91 W 27.42 W 输出电压 12.23 V 12.21 V 12.19 V 12.14 V 输出电流 0.83 A 1.67 A 2.50 A 3.33 A 0.33 A 输出功率 10.18 W 20.33 W 30.44 W 40.43 W 0.00 W 转换效率 73.20% 74.14% 73.57% 72.71% #DIV/0! CoC 10% Load 标准 73.40% 平均效率

AC-DC低电压(<6V)外部电源

额定输出功率 0 to≤1watt >1 to≤49watts >49watts to≤250watts >250watts 最低平均效率 ≥ 0.517 * Pout + 0.087 ≥0.0834*ln(Pout)-0.0014*Pout+0.609 ≥ 0.870 0.875 最大待机功耗 ≤ 0.10 ≤ 0.10 ≤ 0.21 ≤ 0.50

AC-DC低电压(<6V)外部电源

额定输出功率 0 to≤1watt >1 to≤49watts >49watts 最低平均效率 ≥ 0.49பைடு நூலகம் × Pno +0.067 ≥ 0.075 × Ln(Pno) + 0.561 ≥ 0.860 最大待机功耗 ≤ 0.30 ≤ 0.30 ≤ 0.50

68.00% 66.00% 64.00% 62.00% 60.00% 0.00 A 1.00 A 2.00 A 3.00 A 4.00 A

什么是六级能效标准

什么是六级能效标准

六级能效标准是指一种能源效率评价标准,通常用于评估和比较电器、设备或

建筑物的能源利用效率。

这一标准是为了鼓励节能减排、提高能源利用效率,从而降低能源消耗和环境污染而设立的。

六级能效标准通常包括了能源消耗、能源利用效率、环境友好性等方面的要求。

对于不同类型的产品或建筑物,六级能效标准会有所不同,但总的目标都是为了提高能源利用效率,减少能源浪费和环境污染。

在实际应用中,六级能效标准往往会影响到产品的设计、生产和销售。

符合六

级能效标准的产品通常会受到政府的认可和奖励,也更受消费者的青睐。

因此,对于生产企业来说,遵守六级能效标准不仅是一种法律要求,也是一种市场需求和竞争优势。

同时,六级能效标准也对消费者和用户产生了一定的影响。

在购买电器、设备

或建筑材料时,消费者可以通过查看产品的能效标识来选择更节能环保的产品,从而为节能减排做出贡献。

在全球范围内,各国都在积极推动六级能效标准的制定和实施。

通过建立和完

善六级能效标准体系,不仅可以提高产品和建筑物的能源利用效率,也可以推动相关产业的发展和升级,促进经济的可持续发展。

总的来说,六级能效标准是一种重要的能源管理工具,它不仅可以引导企业生

产更节能环保的产品,也可以引导消费者选择更节能环保的产品,从而共同为实现可持续发展和环保目标做出贡献。

希望各界能够共同努力,推动六级能效标准的落实和推广,共同建设一个更加节能环保的社会和环境。

六级能效标准

六级能效标准六级能效标准是指能效等级Ⅰ、Ⅱ、Ⅲ、Ⅳ、Ⅴ,分别对应能效指标≤54%、54% <能效指标≤ 62%、62% <能效指标≤ 70%、70% <能效指标≤ 78%。

以下是关于六级能效标准的相关参考内容。

一、现行六级能效标准的制定背景中国政府高度重视能源效率,为了促进能源的利用效率提高,减少能源消耗和污染物排放,保护环境,提出了一系列能源效率标准,其中包括六级能效标准。

该标准主要适用于家用电器、办公设备、照明设备等产品。

二、六级能效标准的目的1. 降低能源消耗:六级能效标准的推广和实施可以促使制造商不断改进产品能效,在保持产品性能的同时降低能源消耗。

2. 达到国家节能减排目标:通过提高产品能效,减少能源消耗,降低二氧化碳等温室气体的排放量,有助于实现国家节能减排目标。

3. 促进产业升级:六级能效标准的实施将推动相关产业技术创新和产品结构调整,促进产业升级和转型。

三、六级能效标准的实施情况目前,中国已经实施了一系列涉及家用电器、办公设备和照明设备等领域的六级能效标准。

各个领域的能效标准要求不同,但都旨在提高能源利用效率。

1. 家用电器:家用电器是家庭日常生活中能源消耗的主要来源。

根据六级能效标准,在制造商生产的家用电器中,能效等级越高,能源利用效率也就越高。

2. 办公设备:办公设备如电脑、打印机和复印机等在办公场所能源消耗也较大。

根据六级能效标准,办公设备的能效等级越高,其能源利用效率也越高。

3. 照明设备:照明设备如LED灯具的能效也被六级能效标准所规定。

根据标准,能效等级越高的照明设备,能源利用效率也就越高。

四、六级能效标准带来的影响六级能效标准的实施对消费者、制造商和环境都产生了重要影响。

1. 消费者:由于能效等级越高的产品能源利用效率更高,消费者在使用时能够节省更多的能源开支。

同时,高能效产品的推广还可以提高产品的使用寿命,减少因产品损坏而需要更换的频率,为消费者节省维修和更换成本。

开关电源六级能效标准

开关电源六级能效标准随着社会的发展和人们对能源消耗的关注,能效标准成为了各行业关注的焦点之一。

在电源行业中,开关电源的能效标准也备受关注。

本文将就开关电源六级能效标准进行详细介绍,希望能为大家带来更多的了解和启发。

一、能效标准的背景。

随着能源消耗和环境问题日益凸显,各国纷纷出台了相关的能效标准,以限制能源的浪费和环境的污染。

对于开关电源来说,提高能效标准不仅可以减少能源的浪费,还可以降低使用成本,对环境也有积极的作用。

二、开关电源六级能效标准的内容。

开关电源六级能效标准主要包括了待机模式能效、额定输出功率能效和平均效率等要求。

其中,待机模式能效要求开关电源在待机状态下的能耗不得超过一定的标准;额定输出功率能效要求在额定输出功率下的能效达到一定的要求;平均效率则是对整体能效的要求,要求开关电源在各种工作状态下都能够保持较高的能效。

三、六级能效标准的意义。

六级能效标准的实施对于开关电源行业来说意义重大。

首先,能够促进行业技术的升级和创新,推动企业不断提高产品的能效水平。

其次,能够减少能源的浪费,降低用户的使用成本,提高用户体验。

最后,对环境保护也有积极的作用,减少了能源的消耗和环境的污染。

四、企业如何适应六级能效标准。

为了适应六级能效标准的要求,企业需要从多个方面进行调整和改进。

首先,要加大技术研发投入,提升产品的能效水平,不断推出符合标准要求的新产品。

其次,要加强生产管理,提高生产效率,降低生产成本,为产品的能效提升提供保障。

最后,要加强市场监管,确保产品的能效达标,维护市场秩序,保护消费者的利益。

五、消费者如何选择符合六级能效标准的开关电源。

对于消费者来说,如何选择符合六级能效标准的开关电源也是一个重要的问题。

首先,要选择正规渠道购买,避免购买假冒伪劣产品。

其次,要关注产品的能效标识,选择能效等级高的产品。

最后,要结合自身的需求选择合适的产品,避免浪费。

六、结语。

开关电源六级能效标准的实施对于整个行业来说都是一个重要的里程碑,它不仅提高了产品的能效水平,也促进了行业的健康发展。

开关电源六级能效详解(DOC)

开关电源高级能效详解近一两年内,基本做电源产品都为了更新六级能效而忙碌,新规要求倒逼产品升级换代,是好事,也是挑战。

关于六级能效,两个要求:一,待机功耗二,平均效率针对这两点,除了拥有一颗新颖的IC,还有那些细工需要注意的,扒一扒。

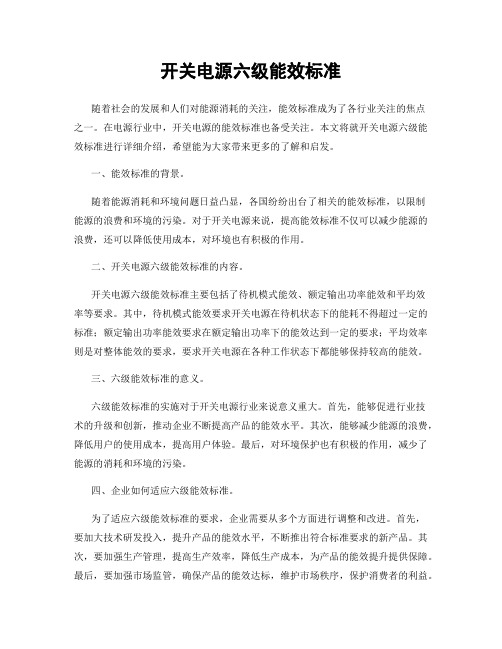

首先,先了解下标准要求:美国能效要求一、待机功耗以美国能效要求为例,要求49W以下空载功耗为0.1W,大于49W空载功耗为0.21W;欧盟49W 以下为75mW,大于49W为150mW。

在设计电源时,相对于75mW的空载功耗,必须要精打细算到每个细节上。

以下几点为显在的固定消耗点:1,Vcc启动回路2,X电容放电回路3,IC Vcc供电回路4,电压(电流)检测环路5,假负载首先,新出的IC大多具有HV启动关断功能,启动后关闭启动电阻回路,避免此回路损耗。

当然,这属于IC原有功能,不在本贴的主旨中,这里一带过,同时后面的一些延伸也会用到此引脚,顺带一说。

如下:当没有HV启动功能的芯片时,Vcc只能尽量大启动电阻,大的启动电阻又需要较快的启动时间时,可以这样做,Vcc两级DC接法,C16用于启动储能,C14用于辅助供电储能,使启动时较大R的情况下C能更快充到IC启动阈值:X电容放电IEC60950要求1S内电压下降到37%IEC60065要求2S内电压下降到35V以下例,按第1条,X电容放电时间常数RC需小于1,设X电容为0.33uF,Rx*Cx<1,那么Rx<3MΩ,由于电容量存在20%误差,那么此电阻选值留足裕量,那应在Rx*0.7内,约2MΩ。

电阻损耗,PR=U2/R,设ACmax=264VPR=2642/2MPR=34.8mWCoC要求49W以下75mW待机或DoE要求49W以下100mW待机,不管那个标准,这部份的损耗都显得巨大。

怎么办,使用更小的X电容(当0.1uF以下,可以不使用放电电阻),或想办法让这个R更灵活一点,如下:1,在断电后,利用IC的HV脚对Cx进行放电2,没有HV启动脚,将启动电阻接到X电容放电电阻中点,断电后,利用IC的Vcc脚帮助放电,可减小X 电容两端电阻的放电功率:3,把EMC元件后移动,AC端不放X电容:Vcc供电用限流电阻,较小的电压标测环流,如图流经R11、R16的静态电流。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

开关电源高级能效详解

近一两年内,基本做电源产品都为了更新六级能效而忙碌,新规要求倒逼产品升级换代,是好事,也是挑战。

关于六级能效,两个要求:一,待机功耗

二,平均效率

针对这两点,除了拥有一颗新颖的IC,还有那些细工需要注意的,扒一扒。

首先,先了解下标准要求:

美国能效要求

一、待机功耗

以美国能效要求为例,要求49W以下空载功耗为0.1W,大于49W空载功耗为0.21W;欧盟49W 以下为75mW,大于49W为150mW。

在设计电源时,相对于75mW的空载功耗,必须要精打细算到每个细节上。

以下几点为显在的固定消耗点:

1 ,Vcc 启动回路

2,X电容放电回路

3,ICVcc供电回路

4,电压(电流)检测环路

5,假负载首先,新出的IC大多具有HV启动关断功能,启动后关闭启动电阻回路,避免此回路损耗。

当然,这属于IC原有功能,不在本贴的主旨中,这里一带过,同时后面的一些延伸也会用到此引脚,顺带一说。

如下:

当没有HV启动功能的芯片时,Vcc只能尽量大启动电阻,大的启动电阻又需要较快的启动时间时,可以这样做,Vcc两级DC接法,C16用于启动储能,C14用于辅助供电储能,使启动时较大R的情况下C能更快充到IC启动阈值:

X电容放电

IEC60950要求1S内电压下降到37%

IEC60065要求2S内电压下降到35V以下

例,

按第1条,X电容放电时间常数RC需小于1,

设X电容为0.33uF,Rx*Cx<1那么Rx<3M Q,由于电容量存在20%误差,那么此电阻选值留足裕量,那应在Rx*0.7内,约2M Q o

电阻损耗,

PR=U2/R 设ACmax=264V

PR=2642/2M

PR=34.8mW

CoC要求49W以下75mW待机或DoE要求49W以下100mW待机,不管那个标准,这部份的损耗都显得巨大。

怎么办,使用更小的X电容(当0.1uF以下,可以不使用放电电阻),或想办法让这个R更灵活一点,如下:

1,在断电后,利用IC的HV脚对Cx进行放电

2,没有HV启动脚,将启动电阻接到X电容放电电阻中点,断电后,利用IC的Vcc脚帮助放电,可减小X电容两端电阻的放电功率:

3,把EMC元件后移动,AC端不放X电容:

Vcc供电

尽量小的Vcc限流电阻,减小损耗。

一般拥有较宽的Vcc的芯片,只要Vcc电压在要求范围内,供电可不用限流电阻,

较小的电压标测环流,如图流经R11、R16 的静态电流。

图中两电阻75K+7.5K回路静态电流约U/R=0.3mA,l2R约7.5mW。

如设为47K+4.7K 贝U U/R=0.49mA,l2R约12.5mW。

所以在环路允许的情况下,建议选取较大值。

假负载一般为了稳定环路在输出预加一定的假负载,在目前 6 级能效来说,几乎不能接受,假设

一个5V1A的电源预加1KR电阻假负载,实际消耗P=U2/R,实际上消耗25mW的功耗,已占COC 待机要求的1/3。

所以要稳定,设整合适的环路才是正道。

待机小结:

1,从功耗上来说,极大一部份来自于高压启动回路,可以从芯片功能选择,启动取电的设计,储能与Vcc的区分来实现较低的消耗。

2,线路中所有元件均存在消耗,所以,对各部份具体核算功耗,再尽可能降低。

3,选用具有突发模式的IC,待机处于突发模式,损耗降低明显。

二、效率

涉及效率,几乎包含了电源的整个系统设计,从整流到变压器转换,再到整流DC输出所有有

电流过的地方都涉及损耗,包括EMI的抑制。

要提升效率就是提升整个系统设计的合理性和平衡。

不再大范围讲解,主要讲述一些重点和我们容易忽略的一些细节。

桥堆

桥堆的损耗是否有注意到,如下同是KBL06有不同的Vf:

下面为ST品牌,同参数下Vf要低0.1V

Pdiode=Vf*Iavginputcurretn 常被忽略的参数,其实一直在侵食我们的效率。

输出整流二极管输出整流D5选用更低Vf的二极管,CCM下需要更快的Trr,如肖特基。

Vf直接影响损耗及发热

较低的Vf会有小的Pd=Vf*lout

如下,同品牌在同等条件下参数对比:

MBRB20100CTV:f 0.95V

MBR20H100CTV:f 0.88V

损耗差Pd=(0.95-0.88)*Iout

当然实际使用电流下的Vf并不一定为上面标称值,但两者的差别对比,在设计效率上应尽量用更低Vf整流二极管。

变压器

对变压器的几点要求:

1,尽量低的漏感,可降低损耗,设漏感为Lkp

Plk=(1/2*Lkp*lp"2)*F

在确定的F情况下,较低的Ipk和Lkp可得到较低的漏感损耗

改善方法: 增加耦合面,用三明治或五明治绕线

副边较粗的线从Bobbin两端出线,不要横跨线包到Pin脚,减少后面绕组的间隙,降低漏感2,

铜损、铁损

平衡两方损耗,监测两方面的温升,调整线匝及气隙,使温升平均尽量绕满绕线窗,最大利用变压器功率密度

合理的EMl

一般60W及以下产品设计合理的情况下,初级一个大感量共模,次级一个小共模可满足一般

IT类同等的EMI要求

从效率和EMI考虑上,变压器线包内屏蔽建议用2个铜箔分隔三明治中的初次级,如再增加屏蔽效用不高

合理处理MOS及二极管上的高频噪声,一般串磁珠是较高效低成本的应用初级大电解并瓷片电容,对噪声有很好滤除作用

PCBLayout

于效率上的影响,PCB上大的环路线路要短,线宽,尽量小的环流面积。

特别次级DC侧,电流要比初级大得多,线宽要控制好。

35um2mm宽1A电流走线(露铜上锡宽度减半),达不到的地方用露铜上锡加粗或在板面上加跳线增大电流。

针对六级能效,目前新IC推出很多特色功能来提升待机和能效,能满足我们应用的IC非常多, 基本有几个特点:

待机方面

1,低启动电流,目前uA级的6Pin。

或具HV独立启动的8Pin

2,轻载突发模式

效率方面

1 ,频率反走

2,低压升频(变压器可用较少规格)。