基于FPGA+DSP的高清视频图像系统设计与实现

基于FPGA的视频处理系统设计与实现

基于FPGA的视频处理系统设计与实现随着数字化技术与高清视频的普及,基于FPGA的视频处理系统的应用也越来越广泛。

它们可以满足人们对于视频质量、速度和响应性能的要求。

FPGA作为一种高度可编程的器件,可根据应用需求任意重构电路结构,使得视频处理系统具有高度的扩展性、灵活性和定制性。

本文将从设计目标、系统结构、视频数据流传输、数字信号处理、硬件开发与软件开发等多个方面来介绍基于FPGA的视频处理系统的设计与实现。

一、设计目标在设计基于FPGA的视频处理系统时,我们需要考虑以下几个方面:1.视频质量:在视频的采集、传输和显示过程中需要确保视频的清晰、流畅和无噪音。

2.速度:视频处理系统需要具备高速的处理能力,可以迅速对视频进行处理,以达到实时性和响应性能。

3.低功耗:由于FPGA系统是基于硬件实现的,所以需要考虑低功耗来满足电源限制和延长电池寿命。

4.设计可重用:这就需要设计出可重用的平台,方便进行软件开发和硬件设计。

二、系统结构基于FPGA的视频处理系统的系统结构如图1所示。

它主要由三个部分组成:视频输入模块、视频处理模块和视频输出模块。

1.视频输入模块视频输入模块主要负责从相机或视频文件中采集视频数据,并将其转换成数字信号传输给FPGA。

该模块包括视频采集和视频解码两个部分。

2.视频处理模块视频处理模块主要是对采集到的视频数据进行处理,包括降噪、滤波、缩放、边缘检测、图像增强等操作。

它往往是FPGA设计的重点。

3.视频输出模块视频输出模块主要把处理好的视频数据输出到显示器、硬盘或网络等外设上,并在此过程中再次进行编码技术,使传输数据量减小,加快传输速度。

该模块还需要实现垂直同步、交错、逆交错等技术来保证视频输出的正确性和质量。

图1:基于FPGA的视频处理系统结构图三、视频数据流传输视频数据流传输是视频处理系统中非常重要的一环,它利用高带宽的总线来传输大量数据。

视频数据流传输主要有以下三种方式:1.像素传输像素传输是最常用的一种方式,它将每个像素的RGB值保存在一个字节中,并采用三根数据线分别传输每个像素的R、G、B值。

基于FPGA_DSP的高清视频图像系统设计与实现_高杨

测试系统与模块化组件 电 子 测 量 技 术 ELEC TRON IC M EAS UREM EN T TECH NO LOGY 第34卷第1期2011年1月 基于FPGA+DSP的高清视频图像系统设计与实现高 杨 刘荣科 胡 伟(北京航空航天大学电子信息工程学院北京100191)摘 要:无人机在侦察、测绘等领域对图像分辨率的要求不断提高,随之带来了数据量的显著增大,其次,视频图像系统与传统遥控遥测系统的融合也是设计中需要考虑的。

针对以上问题,设计并实现了一种基于F PGA+DSP的机载高清视频图像系统,包括机载设备端和地面站端两部分,最高支持分辨率为1280×720,每秒25帧的M PEG-4实时视频编解码,平均码速率在5M bps以下。

图像分辨率和视频码率可通过上行遥控指令动态切换。

视频数据与遥测数据实现了组帧传输。

设备体积小、功耗低、可靠性高,成功完成了挂飞实验。

关键词:M PEG-4;高清视频;遥控;遥测;FPG A;DSP中图分类号:V243.5 文献标识码:ADesign and implementation of high definition videoimage system based on FPGA+DSPG ao Y ang L iu Rong ke H u Wei(Beijing University of Aeronautics and A stronau tics Electronic and Information Engineering Ins tiiu te,Beijing100191)A bstract:T he requirements o f video imag e reso lution is eve r increa sing in the UA V reco nnaissance,mapping and other fields,w hich bring a significant amount of data increa se.In additio n,the integ ratio n of video imaging sy stem and traditio nal telecontr ol and telemetering sy stem is r equired in sy stem design consider atio n.T o solve the pr oblems abo ve, w e de sig n and implement an air bo rne hig h definitio n video image system based on F PG A+DSP,including tw o pa rts: airbo rne equipment end and g round statio n end,it suppor ted the maximum re so lutio n o f1280×720,25fr ame s per second in M PEG-4real-time video encoding and deco ding w ith the ave rage code ra te below5M bps.Imag e re so lutio n a nd video code ra te can be switched up by teleco mma nd dy namically.T he video data and telemetry data are transmitted in the same f rame.T he equipment w ith sma ll size,low pow er consumptio n,hig h re liability,successfully co mpleted flight e xperiments.Keywords:M PEG-4;hig h definition video;telecontro l;telemetering;FPG A;DSP0 引 言无人机广泛应用于军事侦察以及民用测绘等领域,其中的机载视频图像系统是机载电子系统中的重要环节之一。

基于FPGA+DSP的高清视频图像系统的硬件构建

基于FPGA+DSP的高清视频图像系统的硬件构建本文围绕基于FPGA+DSP的高清视频图像系统的硬件系统展开分析,从不同的层面展开对其架构和功能的探讨。

关键字:FPGA;DSP;视频;图像系统在实际的应用环境中,高效的视频编解码技术有着广泛的应用,尤其是当前无人机对于各类工作的广泛深入,更加使得民用测绘以及军用侦测等领域,都对视频图像处理技术提出了更为迫切的要求。

无论何种应用场景,都要求能够将无人机在高空中拍摄的地面图像发送回地面,并且进一步展开处理。

相对于民用系统而言,军用的要求明显更为严格。

从高空中获取到的图像数据,其数据帧内的目标像素都比较小并且目标数量大,这就要求尽可能大的提升图像分辨率,以获取到关于地面的更多情况。

但是与此同时,随着分辨率增加的是需要传输的数据总量,这无疑与当前相对而言比较有限的无线带宽资源形成矛盾。

在这样的背景之下,不仅仅需要发展出更为有效的无线数据传输方式,高效的视频编解码技术更是成为核心重点,直接关系到解析图像本身的效果。

对于需要多路视频传输,并且整体数据率固定的情况下,可以考虑降低单路视频分辨率或者提升单路压缩比来展开工作。

想要实现这种工作方式,系统应当能够实现对于分辨率和压缩比的动态调整和切换,在提升灵活性的同时面向实际需求展开服务。

除此以外,无人机与地面的通信过程中,还需要接收地面传送向无人机的指令并且加以落实,这些数据同样要求比较高的实时性特征。

如果将这些数据与视频数据放在两个独立信道,则传输工作的整体效率就会有所降低。

因此如何构建一个包括传统遥测数据和视频数据的广义遥测系统成为必需。

一、基于FPGA+DSP的高清视频图像系统框架建设在FPGA+DSP两项技术的共同支持之下,整个高清视频图像系统架构可以参见图1。

具体而言,就是大体划分为两个部分,即机载设备端的系统和地面设备端的系统,二者之间通过无线通信网络进行数据的传输和交换。

从图1中可以看到,对于机载设备端而言,经由影像传感器获取到的视频模拟信号数据,将交由AD进行处理,并且转化成为数字信号传递给FPGA,在经过FPGA的预处理之后,生成原始数字视频数据送达DSP进行视频编码。

基于FPGA+DSP的实时图像处理系统设计与实现

万方数据万方数据·110·微处理机2010年(DPRAM)。

虽然C6416片内集成了高达8M位的片内高速缓存,但考虑到图像处理算法必涉及到对前后几帧图像进行处理,为保证系统运行时存储容量不会成为整个系统的性能瓶颈(chokepoint),在DSP模块中额外扩展存储空间。

由于EMIFA口的数据宽度更大,因此系统在EMIFA的CEl空间内扩展了两片总共128M位的同步存储器。

C6416的引导方式有三种,分别是:不加载,CPU直接开始执行地址0处的存储器中的指令;ROM加载,位于EMIFBCEl空间的ROM中的程序首选通过EDMA被搬人地址O处,ROM加载只支持8位的ROM加载;主机加载,外部主机通过主机接口初始化CPU的存储空间,包括片内配置寄存器。

本系统采用的是ROM加载方式。

C6416片内有三个多通道缓冲串口,经DSP处理的最终结果将通过DSP的多通道缓冲串口传送至FPGA。

3.4图像输出模块该模块的功能是将DSP处理后的图像数据进行数模转换,并与字符信号合成后形成VGA格式的视频信号。

这里选用的数模转换芯片为ADV7125。

这是ADI公司生产的一款三通道(每通道8位)视频数模转换器,其最大数据吞吐率330MSPS,输出信图2原始图像图3FPGA图像增强结果5结论实时图像处理系统以DSP和FPGA为基本结构,并在此结构的基础上进行了优化,增加了视频输入通路。

同时所有的数据交换都通过了FPGA,后期的调试过程证明这样做使得调试非常方便,既可以监视数据的交换又方便修正前期设计的错误。

整个系统结构简单,各个模块功能清晰明了。

经后期大量的系统仿真验证:系统稳定性高,处理速度快,能满足设计要求。

号兼容RS一343A/RS一170。

由FPGA产生的数字视频信号分别进入到ADV7125的三个数据通道,经数模转换后输出模拟视频信号并与原来的同步信号、消隐信号叠加后便可以在显示器上显示处理的结果了。

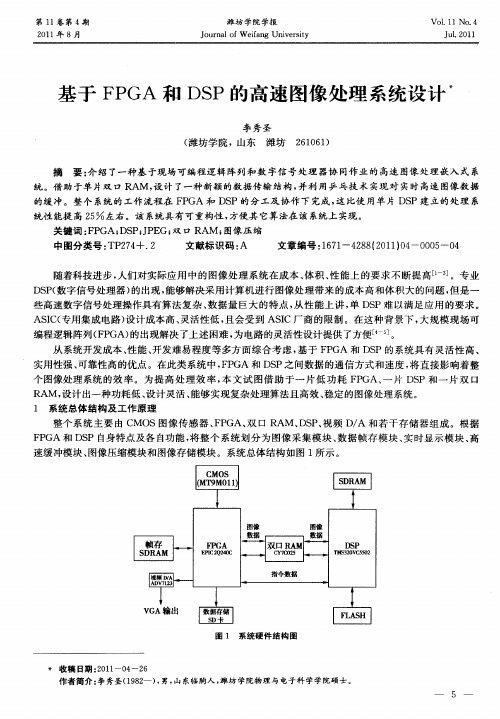

基于FPGA和DSP的高速图像处理系统设计

的缓 冲 。整 个 系统的 工作 流 程 在 F GA 和 D P的分 工 及协 作 下 完成 , 比使 用单 片 DS P S 这 P建 立 的处 理 系

统性 能提 高 2 左右 。该 系统 具 有可重 构性 , 5 方便 其 它算 法在该 系统上 实现 。

关键 词 : P F GA; S J E 双 口 RAM ; D P;P G; 图像 压 缩

第 1 卷 第 4期 1

21 0 1年 8月

潍 坊 学 院 学报

J u n l fW efn ie st o r a ia g Unv r i o y

V0 . 1N0 4 11 .

J 12 1 u. 0 1

基 于 F GA 和 DS P P的 高 速 图 像 处 理 系 统设 计

确 的配置之后 , 就可 以输 出 1 的图像数据 和一些 同步信 号 。在本系统 中采用 I O位 z C实现 传感 器配 置 ,P F— G 管脚通 过模拟 IC时序 , A 。 完成 对 C MOS 感器 的初始 化配置 , 中要 配置 的寄存 器如表 1 传 其 所示 。

表 1 MT M0 9 1寄存 器 设 置

编程逻 辑 阵列 ( P F GA) 出现解 决 了上 述 困难 , 电路 的灵活 性设 计提 供 了方便 [ 。 的 为 4 ]

从 系 统开发 成本 、 能 、 性 开发难 易程 度等 多方 面综 合考 虑 , 基于 F G 和 D P的系 统具 有 灵 活性 高 、 P A S 实用性 强 、 可靠性 高 的优 点 。在此类 系 统 中 ,P F GA和 DS P之 间 数据 的通 信 方式 和速 度 , 直 接影 响着 整 将 个 图像 处理 系统 的效 率 。为 提 高 处 理 效 率 , 文 试 图 借 助 于 一 片 低 功耗 F GA、 片 D P和 一 片 双 口 本 P 一 S

基于FPGA和DSP的高速图像处理系统设计

基于FPGA和DSP的高速图像处理系统设计李秀圣【摘要】A high-efficient image processing embedded system which is based on the field programmable gate array and high-speed digital signal processor was designed in this paper.With a dual-port RAM,a novel data transmission structure was designed,and ping-pong te%介绍了一种基于现场可编程逻辑阵列和数字信号处理器协同作业的高速图像处理嵌入式系统。

借助于单片双口RAM,设计了一种新颖的数据传输结构,并利用乒乓技术实现对实时高速图像数据的缓冲。

整个系统的工作流程在FPGA和DSP的分工及协作下完成,这比使用单片DSP建立的处理系统性能提高25%左右。

该系统具有可重构性,方便其它算法在该系统上实现。

【期刊名称】《潍坊学院学报》【年(卷),期】2011(011)004【总页数】4页(P5-8)【关键词】FPGA;DSP;JPEG;双口RAM;图像压缩【作者】李秀圣【作者单位】潍坊学院,山东潍坊261061【正文语种】中文【中图分类】TP274.2随着科技进步,人们对实际应用中的图像处理系统在成本、体积、性能上的要求不断提高[1-3]。

专业DSP(数字信号处理器)的出现,能够解决采用计算机进行图像处理带来的成本高和体积大的问题,但是一些高速数字信号处理操作具有算法复杂、数据量巨大的特点,从性能上讲,单DSP难以满足应用的要求。

ASIC(专用集成电路)设计成本高、灵活性低,且会受到ASIC厂商的限制。

在这种背景下,大规模现场可编程逻辑阵列(FPGA)的出现解决了上述困难,为电路的灵活性设计提供了方便[4-5]。

基于DSP+FPGA技术的视频图像采集系统的设计

图2

FPGA采集控制部分逻辑原理框图

4.3

DSP中断控制取数部分

数字信号处理是DSP应用的主要方面。DSP所提供的数学运算能力和运算速度远远高于

单片机,具有更为丰富的指令和更大的内存空间,可以实现较为复杂的处理算法。视频信号 经过A/D转换后,形成量化后的数字图像信号,其数据由8位并行接口输出双口RAM,然后 由DSP的中断取数功能在RAM中取数,处理后供主控计算机使用。其工作过程如下:

3.3

DSP核心处理模块 DSP是整个图像处理系统的核心,对采集到的信号进行处理、压缩等过程都由DSP编程

实现。系统由DSP通过芯片上的HPI接口与主机进行通信,接受主机控制命令并向主机传输 采样数据。DSP可对采样所得数据进行实时处理。由于实时性的要求,我们选用,11公司的

DSP处理器TMS320C6202B。 3.4

待下一个HS到来。图2为FPGA采集控制部分逻辑原理框图。

E—

一

舢i

启

#捌

行消臆延时

f6.31Is)

ENAD---DSP发出的AID控制信号 HS--:暖同步信号

cso一组合同步信号—1

AD_CLK—外每时钟信号 AD D限一向DSP发出取敦中断脉冲 ENCA—控喇AD转换信号

l I

ENCA

广

一

■DADL[旺OH]

由于在硬件设计时对实际应用的要求并不能完全了解,设计方案有一定的局限性,因此

・837・

需要使系统具有足够的冗余和灵活性。使用FPGA可以达到这—要求,通过将可能需要的各

种控制和状态信号引入FPGA,利用FPGA的大容量和现场可编程的特性就可根据不同的要求 进行现场修改,增大系统设计的成功率和灵活性。

基于DSP和FPGA的视频图像处理系统设计

技术创新中文核心期刊《微计算机信息》(管控一体化)2008年第24卷第7-3期360元/年邮局订阅号:82-946《现场总线技术应用200例》图像处理基于DSP和FPGA的视频图像处理系统设计DesignofvideoimageprocessingsystembasedonDSPandFPGA(1中国科学院西安光学精密机械研究所;2.中国科学院研究生院)杨露1,2苏秀琴1向静波1,2石磊1,2YANGLuSUXiu-qinXIANGJing-boSHILei摘要:介绍了基于TMS320C6416和EP1C4F400C8的实时视频图像处理系统的设计原理。

系统以DSP为图像处理核心,以FPGA为数据采集和传输的逻辑控制单元,利用乒乓操作实现数据的缓冲和处理。

详细地讨论了视频数据采集部分的结构和FPGA的控制逻辑,以及DSP响应中断后数据的转移和处理。

实验表明,此系统实时性和稳定性均达到了设计要求,具有很大实用价值。

关键词:视频输入处理器;乒乓操作;数字信号处理器;现场可编程门阵列中图分类号:TP311文献标识码:AAbstract:Thispaperdesignedareal-timesystemofvideoimageprocessingbasedonTIDSPofTMS320C6416andAlteraFPGAofEP1C4F400C8.ThesystemusedDSPasamainimageprocessingunit,accomplishedlogiccontrolofdatacatchingandtransmissionwithFPGA,andimplementeddatabufferwithping-pongoperation.Thedesignprinciplewasintroduced.Theconstructionofacquisitionpart,logiccontrolofFPGA,andDSPinterruptrespondofdatatransmissionandprocessingwerealsoexpanded.Theexperimentresultsindicatethathardwarearchitectureiseffectiveandfeasible,theperformancemeetstherequirementofreal-timeprocessing,andthesystemhasasignificantpracticalapplicationvalue.Keywords:Videoinputprocessor;Ping-pongoperation;DSP;FPGA文章编号:1008-0570(2008)07-3-0288-02引言图像处理技术已经被广泛应用于视频图像处理的各个领域,相关的图像处理算法复杂灵活,处理的数据量大,因此实用的图像处理硬件系统要求必须具有运行复杂灵活的算法以及处理大数据量视频图像的能力,以保证系统的实时性,同时系统的体积、功耗、稳定性等也有较严格的要求。

基于FPGA+DSP的实时图像处理系统设计与实现

No 2 . Ap ., 0 0 r 21

微

处

理

机

MI R0PR C OCES ORS S

第 2期 21 0 0年 4月

基 于 FG P A+D P的实 时 图像 处 理 系统设 计 与实现 S

罗戈亮, 鲁新平 , 李吉成

( 防科 学技术 大学 电子 科学 与工程学院 A R国 防科技 重点实 验室 , 沙 4 0 7 ) 国 T 长 10 3 摘 要 : 对 图像 处理 系统计 算量 大 、 时性高和体 积小 的要 求 , 制 了一种 以 D P为 主处理 针 实 研 S

器 FG P A为辅处理 器 的高性 能实 时图像处理 系 统。利 用这 两种 芯 片 的各 自特 点, 算法分 成 两部 将 分分别 交 由 F G P A和 D P处理 , 大提 高 了算法 的效 率。 系统具 有结构 简 单 易于实 现和运 用方便 S 大

灵活 的特 点 , 载上相 应 的程 序之后 能实现对 所获 取 的图像 跟踪 、 别和 匹配等处理 方法。详 细说 加 识

明了系统 的设计 思路 和硬 件结构 , 并在硬 件 系统上进行 了算法仿真及 实验验 证 。实验 结果表 明: 该

系统实 时性高 , 应性好 , 适 能够 满足设 计要求。 关键词 : 时系统 ; 实 图像处 理 ; H L硬件 语言 ; V D 现场 可编程 门阵列

D I O 编码 :0 3 6 / . s .0 2— 2 9 2 1 .2 0 2 1 .9 9 ji n 10 2 7 .0 0 0 .3 s

基于FPGA的视频图像采集处理系统的设计与实现

基于FPGA的视频图像采集处理系统的设计与实现基于FPGA的视频图像采集处理系统的设计与实现摘要:本文针对传统视频图像采集系统在处理速度和资源利用率方面的不足,设计了一种基于FPGA的视频图像采集处理系统。

该系统通过使用FPGA作为硬件平台,结合图像预处理、图像编码和图像解码等核心模块,实现了快速高效的视频图像采集与处理。

实验结果表明,该系统在视频图像采集和处理的功能上具有较好的性能,能够广泛应用于图像处理领域。

1. 引言随着科技的不断发展,视频图像采集与处理在许多领域中得到了广泛应用,如监控系统、医疗影像等。

传统的视频图像采集处理系统通常使用软件实现,但由于软件的运行效率较低,无法满足实时处理的需求。

因此,基于FPGA的硬件实现方案成为了改进的方向。

2. 系统设计基于FPGA的视频图像采集处理系统主要由以下几个模块组成:图像采集模块、图像预处理模块、图像编码模块、图像解码模块和图像显示模块。

图像采集模块主要负责采集外部图像信号,并将其输入到FPGA中。

图像预处理模块对输入的图像进行处理,如去噪、增强等,以提高图像质量。

图像编码模块将处理后的图像进行编码,压缩数据量,并减少传输带宽。

图像解码模块将接收到的编码数据解码成原始图像数据。

图像显示模块将解码后的图像数据进行显示,以供用户观看。

3. 系统实现在系统实现方面,首先需要选择适合的FPGA芯片作为硬件平台。

然后,利用Verilog来描述各个模块的功能,并进行相应的逻辑设计。

最后,通过将Verilog代码综合、布局和布线,生成FPGA配置文件,并烧录到FPGA芯片中。

4. 系统性能评估与实验结果分析为了评估系统的性能,进行了一系列实验。

实验结果表明,该系统在图像采集和处理的速度上优于传统的软件实现方法。

此外,该系统的资源利用效率也较高,能够满足实时处理的需求。

5. 系统应用展望基于FPGA的视频图像采集处理系统具有广泛的应用前景。

不仅可以应用于监控系统,还可以应用于医疗影像、工业检测等领域。

基于DSP和FPGA的图像处理平台的研究和实现

南京航空航天大学硕士学位论文基于DSP和FPGA的图像处理平台的研究和实现姓名:何浩申请学位级别:硕士专业:航空宇航制造工程指导教师:张乐年2011-01南京航空航天大学硕士学位论文摘要实时图像处理技术在现代工业和国防等各个领域得到了越来越广泛的应用,与此相应的是图像处理的数据量不断增加,同时对图像处理系统的实时性要求也越来越高,这对实时图像处理技术提出了更高的要求。

本文研究了一种基于DSP技术和FPGA技术的高速数字信号处理平台,该平台主要针对烟叶异物剔除系统,本课题主要承担系统中硬件部分的研究。

在数字信号处理领域中,“DSP+FPGA”架构被越来越多的设计者所采用,这种架构充分发挥了DSP技术和FPGA技术各自的优势,将两者结合在一起形成了一个最优化的解决方案。

本系统中,通过Camera Link 接口从高性能CCD相机中高速采集图像数据,在FPGA芯片内对其进行必要的预处理和缓存,然后再将其传入DSP芯片进行图像处理,并利用PCI总线将图像数据读入PC机中。

本文首先研究了系统中所涉及的关键技术,包括DSP技术、FPGA技术、Camera Link接口技术和PCI总线技术,并选择了适合本课题的芯片。

然后根据实际需要和硬件设计规则绘制了系统的整体硬件电路原理图,完成PCB印刷电路板设计。

再采用Verilog HDL硬件描述语言完成FPGA内部模块的设计,实现图像数据的高速采集、预处理及缓存功能。

其次根据要求选择WinDriver作为系统驱动程序开发工具,完成系统驱动程序的编写。

最后在Windows环境下成功调试该图像处理卡的图像采集功能,初步达到了目标。

关键词:图像采集,图像处理,DSP,FPGA,Camera Link接口,PCI总线基于DSP的图像处理平台的研究和实现AbstractNowadays, image real time processing technology has been widely applied into modern industry, national defence and other fields. The requirement of image real time processing technology becomes higher because of the increasing amount of image data, better real time property of the image processing system.In this dissertation, hardware of a high-speed digital signal processing platform, which mainly focused on the Tobacco Sundries Eliminating System, is studied based on DSP and FPGA technology. In the digital signal processing field, the model of DSP+FPGA is welcomed by major designer, which combines the respective advantages in DSP and FPGA and gives the optimum solution. In this system, large amount of image data are acquired with high speed from CCD camera by Camera Link Interface, preprocessed and buffered with necessity in FPGA chip, transmitted to DSP chip and processed there, then stored into PC by PCI bus.Firstly, related key technique including DSP, FPGA, Camera Link Interface, PCI bus have been studied and then appropriate chips were chosen based on the requirement of the system. Secondly,the integrated circuit schematics was drew based on practical need and hardware architectural rule, and PCB design was finally finished. Thirdly, FPGA internal module, which realized the function of high speed data acquisition, preprocess, buffer of the image data, was completed using Verilog HDL. Fourthly, according to the practical need, WinDriver was chosen as system dviver developer kits and help program the system driver. Lastly, this image processing card successfully debugged in Windows environment.Keywords:Image Acquisition, Image Processing, DSP, FPGA, Camera Link Interface, PCI Bus南京航空航天大学硕士学位论文图表清单图1.1烟草异物剔除系统 (3)图1.2图像处理系统的构成 (1)图2.1 乘积项逻辑可编程结构原理图 (9)图2.2 C HANNEL L INK工作示意图 (11)图3.1 系统总体结构示意图 (15)图3.2 时钟电路设计 (16)图3.3 DSP的PLL滤波电路 (17)图3.4 FPGA的PLL滤波电路 (18)图3.5 3.3V电源设计 (18)图3.61.4V电源设计 (19)图3.7 1.2V电源设计 (19)图3.8 系统复位电路设计 (20)图3.9 DM642的JTAG接口电路设计 (21)图3.10 FPGA芯片的JTGA接口电路设计 (22)图3.11 FPGA芯片的AS接口电路设计 (22)图3.12 C AMERA L INK接口数据信号电路原理图 (23)图3.13 C AMERA L INK接口控制信号电路原理图 (23)图3.14 RS232接口电路原理图 (24)图3.15 EMIF与双口RAM读时序图 (25)图3.16 DM642与FPGA接口示意图 (26)图3.17 FLASH接口电路 (27)图3.18 SDRAM接口电路 (28)图3.19 DM642芯片EMIFA接口电路图 (29)图3.20 DM642芯片PCI接口电路图 (30)图3.21 PCB板层设计 (31)图4.1 FPGA顶层模块示意图 (33)图4.2 数据接收模块 (34)图4.3 中值滤波模块 (35)图4.4 3×3窗口生成模块 (35)基于DSP的图像处理平台的研究和实现图4.5 标准中值滤波算法流程图 (36)图4.6 快速中值滤波算法流程图 (37)图4.7 计数模块 (38)图4.8 双口RAM模块 (40)图4.9 乒乓结构的双口RAM读写设计 (40)图4.10 WDM驱动程序分层结构 (42)图4.11 驱动程序流程图 (45)图5.1 仿真验证系统框图 (48)图5.2 数据接收模块仿真 (49)图5.3 中值滤波模块仿真 (49)图5.4 SDRAM测试程序流程图 (50)图5.5 SDRAM测试结果 (52)图5.6 SDRAM测试程序中CED ATA变量值 (52)图5.7 FLASH读写测试程序流程图 (53)图5.8 FLASH读写测试程序结果 (54)图5.9 FLASH测试程序中D E D ATA变量值 (54)图5.10 原始测试图片 (55)图5.11 采集到的图像 (56)表2.1 C AMERA L INK控制信号 (12)表2.2 C AMERA L INK接口配置 (12)表3.1 DM642中CLKMODE[1:0]逻辑组合含义 (17)表3.2 DM642中EA20和EA19引脚逻辑组合含义 (17)表3.3 SST39VF040芯片的总线操作 (26)南京航空航天大学硕士学位论文注释表英文缩写英文全称中文全称ASIC Application Specific Integrated Circuit 专用集成电路B Blue 蓝色分量Camera Link Camera Link 相机接口CCD Charge-coupled Device 电荷耦合元件CCS Code Composer Studio 代码调试器CID Charge-coupled Device 电荷注入器件CMOS Complementary Metal Oxide Semiconductor 互补金属氧化物半导体DMA Direct Memory Access 直接内存访问DRC Design Rule Check 设计规则检查DSP Digital Signal Processing 数字信号处理EDA Electronic Design Automation 电子设计自动化EDMA Enhanced Direct Memory Access 增强型直接内存存取EEPROM Electrically Erasable Programmable Read-Only Memory电可擦可编程只读存储EMC Electro Magnetic Compatibility 电磁兼容性FIFO First Input First Output 先入先出队列FPGA Field-Programmable Gate Array 现场可编程门阵列G Green 绿色分量I2C Inter-Integrated Circuit 两线式串行总线I/O Input/Output 输入输出KMD Kernel Mode Driver 内核模式驱动程序模型LVDS Low-V oltage Differential Signaling 低压差分信号PCB Printed Circuit Board 印刷电路板PCI Pedpherd Component Interconnect 外设组件互联标准PLD Programmable Logic Device 逻辑可变程器件PLL Phase Locked Loop 锁相环R Red 红色分量RAM Random Access Memory 随机存储器RGB Red、Green、Blue 红绿蓝色彩模式基于DSP的图像处理平台的研究和实现ROM Read-Only Memory 只读存储器RTDX real-time data exchange 实时数据交换SDRAM Synchronous Dynamic Random Access Memory 同步动态随机存储器SRAM Static RAM 静态存储器VxD Virtual X Driver 虚拟设备驱动程序模型WDM Window Driver Model 视窗驱动程序模型承诺书本人声明所呈交的硕士学位论文是本人在导师指导下进行的研究工作及取得的研究成果。

基于FPGA+DSP的高速视频实时处理系统设计

1310 引言随着经济的快速发展,各个领域对高速视频图像实时处理的速度与精度提出了更高的要求,譬如:机器人导航领域、现场监控领域、安防领域等。

在此背景下,高速视频图像实时处理技术得到了长足的发展[1]。

20世纪70年代,人们开始利用高速摄像机来记录运动的物体,但当时高速摄像机是以胶片的形式作为记录介质,无法实现数据的实时处理[2]。

现如今,高速工业相机的采样频率高达1000FPS (Frame Per Second)[3],由于高速视频图像实时处理系统具有数据量大,数据相关性高,而且对图像的帧、场时间具有严格的限制,因此,高速视频图像实时处理领域对中央处理芯片、外部存储芯片的工作速率以及核心算法的运算复杂度等都提出了极大的挑战[4]。

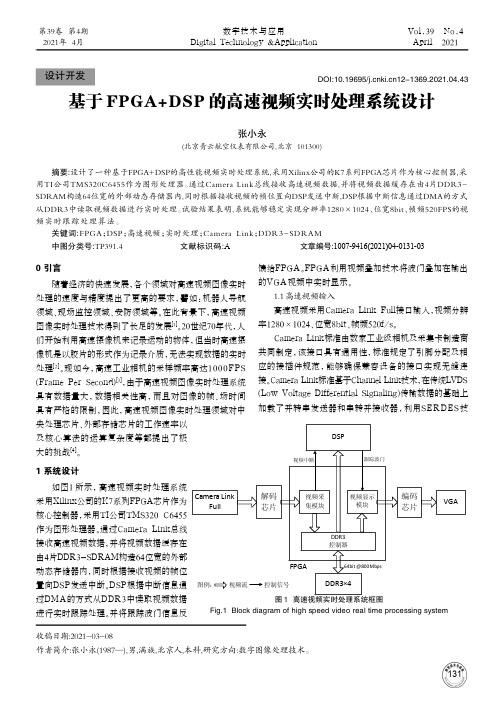

1 系统设计如图1所示,高速视频实时处理系统采用Xilinx公司的K7系列FPGA芯片作为核心控制器,采用TI公司TMS320 C6455作为图形处理器。

通过Camera Link总线接收高速视频数据,并将视频数据缓存在由4片DDR3-SDRAM构造64位宽的外部动态存储器内,同时根据接收视频的帧位置向DSP发送中断。

DSP根据中断信息通过DMA的方式从DDR3中读取视频数据进行实时跟踪处理。

并将跟踪波门信息反馈给FPGA。

FPGA利用视频叠加技术将波门叠加在输出的VGA视频中实时显示。

1.1 高速视频输入高速视频采用Camera Link Full接口输入,视频分辨率1280×1024、位宽8bit、帧频520f/s。

Camera Link标准由数家工业级相机及采集卡制造商共同制定,该接口具有通用性,标准规定了引脚分配及相应的接插件规范,能够确保兼容设备的接口实现无缝连接。

Camera Link标准基于Channel Link技术,在传统LVDS (Low Voltage Differential Signaling)传输数据的基础上加载了并转串发送器和串转并接收器,利用SER DES技收稿日期:2021-03-08作者简介:张小永(1987—),男,满族,北京人,本科,研究方向:数字图像处理技术。

一种基于DSP+FPGA视频图像采集处理系统的设计与实现

一种基于DSP+FPGA视频图像采集处理系统的设计

与实现

1、引言

实时视频图像处理技术的应用十分广泛,在民用领域有机器人视觉、资源探测和医学图像分析等;在军用领域有导弹精确制导、敌方目标侦察与跟踪等。

本设计中采用了DSP+FPGA的硬件结构,DSP采用ADI公司的高性能双核DSP-BF561作为主处理器,负责整个算法的调度和数据流的控制,完成图像数据的采集与显示及核心算法的实现;而FPGA作为DSP的协处理器,依托其高度的并行处理能力,完成图像预处理中大量的累乘加运算。

DSP的2个内核与FPGA通过中断进行通信响应,使系统的各处理器并行工作,提高了DSP内核及FPGA的利用效率,保证了系统采集与显示的实时性。

2、系统原理与结构

图像采集与处理系统主要包括4大模块:图像采集模块、存储模块、处理模块和显示模块。

图1所示为DSP+FPGA的图像采集与处理系统硬件结构框图。

基于FPGA+DSP的高清视频监控系统研究

基于FPGA+DSP的高清视频监控系统探究摘要:随着科技的不息进步和进步,高清视频监控系统在安防领域得到了广泛应用。

本文将详尽探究基于FPGA+DSP的高清视频监控系统,并从硬件设计、软件算法以及系统性能方面进行分析和探讨。

通过试验验证,本文所提出的基于FPGA+DSP的高清视频监控系统在图像质量和处理性能上具有巨大优势,能够有效应对日益复杂的安防需求。

关键词:高清视频;监控系统;FPGA;DSP第一章引言1.1 探究背景随着社会的不息进步和人们对安全的日益重视,高清视频监控系统在城市安防和企事业单位的安全管理中起到了至关重要的作用。

高清视频监控系统通过实时采集和传输高清视频图像,能够对潜在的安全隐患进行准时发现和处理,为各行业提供有效的安全保障。

1.2 探究意义目前市场上的高清视频监控系统主要基于开发板或者成熟的硬件平台,但是这些系统存在着处理速度慢、图像质量差、占用存储空间大等问题。

因此,本文旨在探究并设计一种基于FPGA+DSP的高清视频监控系统,通过硬件和软件的协作,提高系统的处理速度和图像质量,以满足复杂的安防需求。

第二章系统设计方法2.1 硬件设计本系统基于FPGA+DSP实现,接受了高性能的FPGA芯片和DSP 芯片。

FPGA用于图像数据的采集、处理和传输,DSP用于复杂算法的运行和图像质量的优化。

通过硬件设计,实现对高清视频的高速处理和传输,提高系统的实时性和稳定性。

2.2 软件算法本系统接受了图像增强算法、目标检测算法和运动跟踪算法等。

图像增强算法通过增加对比度和锐化处理,提升图像的明晰度和细节;目标检测算法通过特征提取和分类器的运用,实现对目标物体的准确检测;运动跟踪算法通过连续帧的比对和匹配,实现对目标物体的精确跟踪。

第三章系统性能评估为了评估所设计的基于FPGA+DSP的高清视频监控系统的性能,本文进行了多组试验,并从图像质量、处理速度和系统资源占用等方面进行了分析和评估。

基于DSP和FPGA的图像处理系统设计

Abstract

This paper studies the system design principle and composition the of TI high performance DSP core processor for real-time video image processing , and it can achieve video image processingsystem basedon the architecture of DSP and FPGA. The image processing system is composed of image acquisition circuit, image processing circuit, display circuit and system software.

题目:基于DSP和FPGA的图像处理系统设计

外文题目:IMAGE PROCESSING SYSTEM DESIGN BASED ON DSPAND FPGA

摘要

本文研究了以TI高性能DSP为核心处理器的视频实时图像处理系统的设计原理与组成,并基于DSP + FPGA架构实现了视频图像处理系统。本图像处理系统主要由图像采集电路、图像处理电路、显示电路以及系统软件组成。

首先经过CCD图像传感器采集复合视频信号,经过视频A/D处理器(SAA7115)转换成8 bit的数字信号,通过DMA方式存放在双口RAM中,该处理器同时还输出像素时钟信号(PCLK),场同步(CS)、行同步(HS)、奇偶场(OE)、复合消隐信号(BLANK)。

数字信号处理器DSP(TMS320VC5501)是本处理器的核心部分,其功能是完成整个系统的图像预处理以及数据流存储时序控制等功能。经过DSP处理后输出8 bit的数字视频信号以及像素时钟信号(PCLK)、场同步(CS)、行同步(HS),一起送FPGA产生视频信号的时序逻辑,然后送视频D/A处理器(SAA7105H),最后通过VGA视频接口输出。静态双口RAM用于存储图像数据的,图像数据的读写控制时序通过DSP来实现。视频D/A处理器(SAA7105H)将FPGA输出的数字视频信号、像素时钟、行场同步信号合成为彩色全电视信号然后通过VGA输出。该视频图像处理系统可以实现实时的数据视频信号的采集、处理及显示,可以应用于视频处理的相关领域。

基于DSP和FPGA的视频处理系统设计及其实现

第 3 卷 第 1 期 7 2

20 07年 1 2月

激 光 与 红 外

I E AS R & I R NF ARE D

Vo . 7, .1 1 3 No 2

De e e , 0 7 c mb r 2 0

文章编号 :0 15 7 (0 7 1 -380 10 -0 8 20 ) 212 -3

De i n a d Re l a in o d o- o e sn y t m sg n ai to fVi e pr c si g S se z Ba e n DS a d FPGA s d o P n

L U a — i g , AN h , I Xio r n TI u Ya XU ha . i Z o hu

路: 一种是由计算机和视频采集卡组成 , 主要采用以 计算机为核心的集 中式处理 , 图像采集、 视频检测等 工作都在计算机上完成。这种设计方案人机交互方 便、 开发性强 、 操作性强 。但 是 由于通用 C U采用 P 的总线结构和数据处理方式并不适合于高速信号处 理, 导致该类系统实时性差 ; 且系统需要计算机的支 持, 因此 , 在某些有集成度和使用环境要求的应用领 域使用受到限制 , 而且图像 跟踪处理算法的实现受 视频采集卡基本功能的限制 。另一种采用较多的是 分 布式处 理 方 案 , 体 算 法 分 散 在 多 个 D P上 实 主 S 现 , 由 P 14来 完 成 辅 助 的事 务 性 处 理 , 类 系 而 C0 该 统 的优 越性 体现 在 可靠性 、 扩展 性 、 灵活性 这 三个 方 面, 但性价比、 集成度均不高。 今后 视频 处理 的应 用将 越来 越广 泛 , 特殊 领域 、

Ab t a t I ie a k n i r e c iv a g u e s o p r t g p o e sn n afnt i , o a u e sr c :n v d o t c ig, o d rt a h e e lr e n mb r fo e a i rc s i g i i t r n o n i e me s me me s r s f ri r vn p r n p e r e d d o mp o ig o e  ̄i g s e d a e n e e .A a d r y tm e in b s d o MS 2 C 4 6 h g -p e P a d h r wa e s s e d s a e n T 3 0 6 1 ih s e d DS n g F GA i t d c d P si r u e .T e e p r nsd mo sr t a e s se i mu h e i r h n t e fr rDS ny v d op o n o h x e me t e n tae t tt y tm c a e a me P o l i e r — i h h s s t h o c s i g s se frf l l n e r a - me r q i me t i a r i g o t c mp iae g rtm d mu t t g t e ta - e s y t m o u f l g t e lt e u r n ii h i e n n c ryn u o l td a o h a l -a e x r c c l i n ir

基于DSP和FPGA的全景图像处理系统设计与实现

基于DSP和FPGA的全景图像处理系统设计与实现陆军;高乐;刘涛【期刊名称】《电子技术应用》【年(卷),期】2012(38)6【摘要】A scheme of panoramic image processing based on DSP and FPGA.FPGA is designed in this paper. Image acquisition is implemented by using FPGA. DSP completes image processing algorithms. Using of FPGA, the SDRAM controller in ping-paiig buffer mechanism is designed. Communication between DSP and FPGA is implemented based on EDMA mode. Experimental results show that the design of DSP and FPGA panoramic image processing system can implement real-time image acquisition, buffering of 2048x2048 ,15fps per second based on camera link interface. The system can also real-time display panoramic image in 1 024×768.%设计了基于DSP和FPGA的全景图像处理方案,FPGA完成图像采集,DSP完成图像的各种处理算法.利用FPGA设计了基于乒乓缓存机制的SDRAM 控制器;采用EDMA方式,完成了DSP与FPGA的数据交换.测试结果表明,DSP+ FPGA折反射全景图像处理系统完成了对分辨率为2 048×2 048、每秒15帧的Camera Link接口的全景图像的实时采集及缓存解算,并以1024×768的分辨率进行实时显示.【总页数】4页(P24-26,30)【作者】陆军;高乐;刘涛【作者单位】哈尔滨工程大学自动化学院,黑龙江哈尔滨 150001;哈尔滨工程大学自动化学院,黑龙江哈尔滨 150001;中国科学院沈阳自动化研究所,辽宁沈阳110000【正文语种】中文【中图分类】TP274;TN919【相关文献】1.基于FPGA的全景图像处理系统SDRAM控制器设计与实现 [J], 陆军;高乐;刘涛;朱齐丹2.基于VPX的多DSP+FPGA红外图像处理系统设计与实现 [J], 祝树生;李晶;吕殿君;陈冉;仇公望3.基于DSP+FPGA的IRFPA实时图像数字处理系统设计与实现 [J], 何健;胡旭;李勃;洪建堂4.一种基于DSP+FPGA系统架构的雷达实时信号处理系统的设计与实现 [J], 韩涛;孙娟;刘汝猛;裘磊5.基于FPGA+DSP的实时图像处理系统设计与实现 [J], 罗戈亮;鲁新平;李吉成因版权原因,仅展示原文概要,查看原文内容请购买。

FPGA+DSP 架构的 HD-SDI 高清图像处理系统设计

FPGA+DSP 架构的 HD-SDI 高清图像处理系统设计周罡【期刊名称】《单片机与嵌入式系统应用》【年(卷),期】2014(14)8【摘要】随着图像处理技术及传感器技术的不断发展,高清数字图像取代模拟图像成为一种趋势。

设计了一种基于 HD SDI 技术的高清图像处理系统,可通过FPGA+DSP 架构对1080P 全高清图像进行采集和字符叠加,并实时进行目标提取和偏差量计算。

叠加视频可通过 DVI 数字接口或模拟接口实时显示。

利用图像高分辨率特性,系统可实现运动目标精确跟踪。

%The high-definition image replaces analogue image to become a kind of trend with the development of image processing tech-nique and sensor technique.A high-definition image processing system is designed based on HD-SDI technique.The system can acquire 1080P high-definition image and make character composition through the structure of FPGA and DSP,and it can extract target and com-pute deviation in real-time.The composition video is displayed in real-time through DVI digital interface or analogue interface.The sys-tem can track moving target accurately with the high-resolution characteristic of images.【总页数】3页(P49-51)【作者】周罡【作者单位】华中光电技术研究所武汉光电国家实验室,武汉 430223【正文语种】中文【中图分类】TN91【相关文献】1.基于FPGA+DSP的高清视频图像系统设计与实现 [J], 高杨;刘荣科;胡伟2.基于FPGA+DSP的实时图像处理系统设计与实现 [J], 罗戈亮;鲁新平;李吉成3.基于 CPCI 总线的 FPGA+DSP 架构通用视频图像处理系统的设计 [J], 于洪松;韩广良;孙海江;李桂菊;武治国;李赓飞4.基于FPGA的高清HD-SDI视频采集系统设计与实现 [J], 钱宏文;刘会;付强;王毅5.Zynq-7000"FPGA+ARM"架构的数字图像处理系统设计 [J], 王咏星;张国兵;宋俊霞因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.1硬件平台 2.1.1机载端视频采集

高清模拟视频信号为保证信号质量,常采用分量输出 格式,如亮度信号(Y)和色差信号(Cr、Cb)三分量输出,同 时场同步和行同步信号可采取叠加在分量信号上的内同

· 70·

图2 TVP70025I硬件连接

2.1.2机载端DSP+FPGA处理器 机载端处理部分主要完成数字视频信号获取、视频压

机 载 设 备 端

调制一>无线ห้องสมุดไป่ตู้道一>解调

-__-

地 面 站 端

图1系统总体

1)机载设备端 视频AD将影像传感器输出的高清视频模拟信号进行 模数转换传递给FPGA,FPGA将预处理后的原始数字视 频数据传递给DSP进行实时视频编码,DSP完成视频编码 后将压缩码流回传给FPGA,在FPGA中,压缩视频码流 与下行遥测数据组帧后进入调制部分;同时上行遥控指令 进入FPGA,对图像分辨率、视频码率进行控制。 2)地面站端 解调后的数据进入FPGA,FPGA将视频数据与遥测 数据分离,其中遥测数据进入后续的分析处理,视频数据 经PCI9054,通过CPCI接口上传给上位机,上位机完成对 视频压缩码流的实时解码播放以及存储回放。

FPGA

原始码流I l遥控

FIFO

l指令

Y/Cb/Cr I寄存器

压缩 码流

FIF0

l中断产生

儿 儿 11-

EMIFA接口 (CE2)

Jr I

外部中断 处理器

霹I

H

FLASH

I卜 D接D口R2

n

DDR2 SDRAM

;李

视频

ADC

图4 DSP功能设计

DSP部分的设计主要为存储空间的分配,本系统中分 配方式如表2所示。其中CE2空间主要用于与FPGA之 间的数据交互,CE3空间主要用于代码的非易失性存储, CEO空间主要作为程序和数据运行的外部空间。

Gao Yang Liu Rongke Hu Wei

(Beijing University of Aeronautics and Astronautics Electronic and Information Engineering Instiiute,Beijing 100191)

Abstract:The requirements of video image resolution is ever increasing in the UAV reconnaissance,mapping and other fields,which bring a significant amount of data increase.In addition,the integration of video imaging system and traditional telecontrol and telemetering system is required in system design consideration.To solve the problems above, we design and implement an airborne high definition video image system based on FPGA+DSP,including two parts: airborne equipment end and ground station end,it supported the maximum resolution of 1 280×720,25 frames per second in MPEG-4 real-time video encoding and decoding with the average code rate below 5 Mbps.Image resolution and video code rate can be switched up by telecommand dynamically.The video data and telemetry data are transmitted in the same frame.The equipment with small size,low power consumption,high reliability,successfully completed flight experiments. Keywords:MPEG-4;high definition video;telecontrol;telemetering;FPGA;DSP

实现了组帧传输。设备体积小、功耗低、可靠性高,成功完成了挂飞实验。

关键词:MPE昏4;高清视频;遥控;遥测;FPGA;DSP

中图分类号:V243.5

文献标识码:A

Design and implementation of high definition video image system based on FPGA+DSP

表1视频与遥测数据组帧格式

DSP选用TI公司的新一代高性能定点DSP TMS320C6455,它基于C64x+内核结构,片内采用L1/L2 两级缓存结构,主频达1.2 GHz,最大峰值速度9 600 MIPS。 此外,TMS320C6455拥有丰富的外部接口,如总线接口(12C 等)和外部存储器接口(EMIFA、DDR2)等。主要功能设计 如图4所示。

统与传统遥控遥测系统的融合也是设计中需要考虑的。针对以上问题,设计并实现了一种基于FPGA+DSP的机载

高清视频图像系统,包括机载设备端和地面站端两部分,最高支持分辨率为1 280×720,每秒25帧的MPEG-4实时视

频编解码,平均码速率在5 Mbps以下。图像分辨率和视频码率可通过上行遥控指令动态切换。视频数据与遥测数据

本文首先对机载视频图像遥测系统进行概述,提出了 系统的总体实现结构。然后具体给出系统的设计,分为硬

· 69 ·

万方数据

第34卷

电 子 测 量技 术

件平台和程序算法两部分。硬件平台设计包括机载端视 频采集、FPGA+DSP处理器和地面端CPCI总线接口的 设计,程序算法设计包括视频编解码算法、机载端DSP程 序和地面端上位机软件的设计。文章最后给出了系统挂 飞实验的结果并作以总结。

表2 DSP存储空间分配

万方数据

2.1.3地面端CPCI总线接口 CompactPCI是PICMG提出的一种工业接口标准,采

用PCI总线技术嘲,在此基础上改善了机械结构,支持热 插拔,可靠性高。

· 71 ·

第34卷

电 子 测 量技术

地面端采用FPGA+PCI接口芯片的架构实现”],其 中,FPGA主要完成视频与遥测数据分离以及接口时序等 功能,而PCI协议部分由接口芯片来实现,该种方式减小 了FPGA的逻辑设计量。系统中FPGA选用Altera公司 Cyclone系列芯片EPICl2Q240C8,PCI接口芯片选用 PLX公司的PCI9054。PCI9054的PCI总线接口与CPCI 插槽相连,本地总线接口与FPGA相连,EEPROM用于加 载配置数据。 2.2程序算法 2.2.1视频编解码算法

…-礴试 1寨城与挟臻纯瓤件肛El成T舯N。C电M聂s测URE量MEN技T术TECHNOLOGY第203411卷年第1 1期

基于FPGA+DSP的高清 视频图像系统设计与实现

高 杨 刘荣科 胡 伟 (北京航空航天大学电子信息工程学院北京100191)

摘 要:无人机在侦察、测绘等领域对图像分辨率的要求不断提高,随之带来了数据量的显著增大,其次,视频图像系

1 系统概述

机载视频图像系统主要由机载设备端和地面站端两 部分组成,系统总体结构图如图1所示。

步方式输出。本系统中高清视频信号采用720 p(1 280× 720)格式,25帧/秒,选用TI公司的视频ADC芯片 TVP70025I完成该高清模拟视频的模数转换,采样精度及 方式选取为8位,4 z 2:2(Y:Cb:Cr)采样。TVP70025I 与外部器件连接关系如图2所示。TVP70025I输出数字 化视频分量(Y、Cb和Cr)、数据时钟(DATACLK)、场同步 (VSOUT)和行同步(HSOUT)信号给FPGA,DSP通过 12C总线对TVP70025I内部寄存器进行初始化设置,并启 动模数转换过程。

缩编码和遥控遥测接口功能,考虑到DSP强大的数字信号 处理能力和FPGA的大规模逻辑设计能力,系统采用 FPGA+DSP的硬件架构。

FPGA选用Ahera公司StratixII系列芯片 EP2S30F672C5,该芯片有丰富的逻辑资源和嵌入式存储 器,支持LVTTL、LVDS等接口电平标准。主要功能设计 如图3所示。

0引

言

无人机广泛应用于军事侦察以及民用测绘等领域,其 中的机载视频图像系统是机载电子系统中的重要环节之 一。无人机在高空飞行中对地面景物摄像,所得图像帧内 目标像素小且目标数量大[1],这要求增大图像分辨率以提 高目标物体的辨识度。此时数据量随之显著增加,与有限 的无线带宽资源成为矛盾,故要求应用高效的视频编解码 技术。在侦察等特殊应用领域要求视频传输的实时性,此 时需要保证实时的视频编解码以及较小的图像延迟。在 需多路视频传输且总数据率固定的情况下,可通过降低单 路视频分辨率或提高单路压缩比来实现,故系统应可动态 切换分辨率和压缩比,具备较大的灵活性。无人机与地面 的通信中,除了要回传视频数据以外,还要向地面传输飞 行器本身的下行遥测数据01],若采用两个独立信道会导致

EMIF 接口

DSP

外部 中断

+遥测数据一 +遥测时钟一 图3 FPGA功能设计

万方数据

高 杨等:基于FPGA+DSP的高清视频图像系统设计与实现

第1期

包括以下3个方面: 1)数字视频获取 FPGA通过TVP700251输出的场同步和行同步信号 判断一场和一行视频的起始,接收原始视频数据(Y/Cb/ Cr)并存入FPGA内部开辟的FIFO之中,考虑到数据传 输的高效性,需缓存若干行图像并一次性传递至DSP,由 于FPGA内部存储器有限,故外挂SRAM作为数据缓冲。 2)DSP与FPGA间数据传输 DSP与FPGA之间通过DSP的EMIFA接口连接, FPGA内开辟FIFO或者寄存器,DSP通过EMIFA读写 FIFO或寄存器内的数据实现数据传输。本系统中分别开 辟原始视频FIF0(Y/Cb/Cr 3个)、压缩视频FIFO和遥控 指令寄存器,对应于DSP中的5个地址空间,以地址线的 最高3位进行区分。考虑到最大数据吞吐率为原始视频 的传递,EMIFA数据宽度设为32位,数据时钟选取 40 MHz。 3)遥控及遥测 本系统中可接受地面测控站传递的上行遥控指令,通 过改变采样方式,对视频分辨率进行切换,包括QCIF (176×144)、C1F(352×288)、标清(720×576)和高清 (1 280X720)4种模式。同时可根据遥控指令改变编码算 法中的参数,进而实现视频数据的码率控制,分为最高至 最低5个码率等级。 编码后的视频数据与下行遥测数据进行组帧,作为整 体码流进入调制阶段。系统中设计帧格式如表1所示。 每大帧包括64个子帧,以1字节子帧计数标识,大帧计数 以两字节时统信息标识。前63个子帧用于传输视频数 据,考虑到采用变长视频编码算法后每帧压缩图像字节数 不固定,组帧过程中需填充无效字节以保证每子帧中1 022 字节的视频数据,故我们以两字节有效字节数来标识有效 的视频字节数。第64子帧用于传输遥测数据。每个子帧 以3字节同步码作为结束。