基于VHDL的8位除法器的实现

veriloghdl简单计算器设计

V e r i l o g H D L简单计算器设计(总13页)-CAL-FENGHAI.-(YICAI)-Company One1-CAL-本页仅作为文档封面,使用请直接删除目录第一章设计目的及任务要求 (1)1.1 设计目的 (1)1.2 设计任务 (1)1.3 课设要求 (1)第二章设计思路 (2)2.1 设计总体框图 (2)2.2 设计原理 (2)2.2.1 计算其原理 (2)2.2.2 数码显示原理 (2)2.2.3 八位数码管扫描的原理 (3)第三章设计源程序及分析 (4)3.1 计算器模块 (4)3.1.1 计算器源程序 (4)3.1.2 计算器程序分析 (4)3.2 数码管显示部分 (5)3.2.1 数码管显示源程序 (5)3.2.2 数码管显示程序分析 (5)3.3 循环扫描模块 (6)3.3.1 循环扫描程序 (6)3.3.2 循环程序分析 (6)3.4 总程序及其分析 (7)第四章时序仿真和结果验证 (10)4.1 计算器时序仿真及其分析 (10)4.2 数码管时序仿真及分析 (10)4.3 总体时序仿真图 (11)4.4 结果验证 (11)第五章心得体会 (12)第一章设计目的及任务要求1.1 设计目的(1)进一步加强熟练EDA基础知识。

(2)熟练掌握Quartus 6.0软件的使用以及用该软件编程和仿真的全过程。

(3)培养独立思考问题,解决问题的能力以及查阅相关资料和资料的正确使用能力,为明年的毕业设计打下良好的设计基础。

1.2 设计任务设计一个简单计算器,输入为8位二进制数,分别用两位数码管显示,输出的计算结果为16位二进制数,并用四位数码管显示,能够实现+、-、 *、/ 四种运算,其中除法的结果显示分为商和余数两部分,分别用两位数码管显示。

1.3 课设要求(1)说明题目的设计原理和思路、采用方法及设计流程。

(2)系统框图、Verilog语言设计程序或原理图。

(3)对各子模块的功能以及各子模块之间的关系做较详细的描述。

8位CPU的设计-VHDL语言-综合性实验实验报告

综合性实验报告计算机组成原理年级专业班级:10级软工R3班小组号: 5完成日期:2012-06-06【分工包括:、、执行(ALU相关)、通用寄存器组、存储器等】(一)实验类型:验证性+设计性(二)实验类别:综合性专业基础实验(三)实验学时数:8学时(四)实验目的理解和验证参考代码,并在其基础上,通过适当改造,尝试设计一个简单的CPU,并测试其结果。

(五)实验内容设计一个能验证计算机CPU工作原理的实验系统,包括取指部分、指令译码部分、执行部分、通用寄存器组以及存储器,并测试其结果。

(六)实验要求根本目标:缩小到8位的数据通路,也即是4位OP和4位的地址码。

(参考代码是16位数据通路,也即8位OP和8位的地址码)(参见实践报告.doc中的9-11页的指令系统总体说明)学生按照实验要求,在实验平台上实现具有存储与运算功能的计算机系统,并能通过测试,以验证其正确性。

具体要求如下:(1)取指及调试(组长兼任)。

熟悉指令取指过程,并把16位的部分改为8位。

使用DebugController和系统中的调试模块(reg_testa.vhd,reg_test.vhd)。

(2)熟悉电原理图的连接,以通用寄存器组部分为例。

实现上,用实验4所用的简单通用寄存器组(4个寄存器+1个2-4译码器+2个4选1多路开关)设计方法,替代参考代码中的通用寄存器组部分。

(3)学习和掌握控制逻辑。

设计一套指令集(可在原参考代码指令集的基础上做删减,从中选取16条基本的指令),并修改控制器中指令集的译码部分。

(4)执行部件,ALU的改造。

可在原参考代码的基础上,改变某些运算功能的实现方式,比如加、减、增1、减1等算术运算。

实现上,原参考代码采用了最少编码量的“+”、“-”号实现。

可以改用通过port map语句调用系统自带的加法器,也可以进一步自己编写加法器,然后用port map语句调用。

(5)存储器部分的加入。

原参考代码采用的带外部存储器的模式。

高效除法器

一、实验目的及要求用verilog实现一个被除数为8位,除数为4位的高效除法器。

二、实验设备(环境)及要求实验室计算机及modelsim仿真软件,最后用synplify进行综合仿真得到图形。

三、实验内容与步骤1.实验总体设计思路1、先定义被除数为dividend,除数为divisor,商为Rtient,余数为Qainer,举个例子假如被除数与除数分别为1111与0100。

2、将被除数赋给寄存器变量Q=1111,再将除数赋给变量Dr=0100,设置商的变量R 初始值为 4’b0000,则{R,Q}为{00001111}。

3、首先将{R,Q}左移一位,即{00011110},现在R=0001,Q=1110;4、比较R与除数Dr的大小,如果R>Dr,则R=R-Dr,并且{R,Q}再左移一位并且Q[0]=1,反之{R,Q}左移一位Q[0]=0。

5、继续上述过程,循环4次{R,Q}={00111100},{01111000},{01110001},{01100011}。

6、此时商Rtient=Q,而余数Qainer=(R>>1)(即余数等于R向右移一位),所以此例结果为Rtient=0011,Qainer=0011。

检验:对应于十进制,是15除以4,商为3,余数为3.2.系统结构和模块划分,关键子模块之间的接口实现定义。

输入端口:Clk,Rst,dividend,divisor;输出端口:quotient,remainer;寄存器变量:R,Q,Dr;Verilog 代码如下:module chufa(dividend,divisor,Clk,Rst,quotient,remainer); //端口定义input [7:0] dividend; //定义被除数input [7:0] divisor ; //定义除数input Clk; //时钟信号input Rst; //复位信号output [7:0] quotient; //定义商数output [7:0] remainer; //定义余数reg [7:0]Q;reg [7:0]R;reg [7:0]Dr; //定义寄存器变量wire [7:0]quotient;wire [7:0]remainer;integer i;parameter SIZE = 8;always@(posedge Clk or negedge Rst)beginif(!Rst) //复位信号为0时置0。

基于VHDL八位频率计设计

SIGNAL TSTEN:STD_LOGIC; SIGNAL CLR_CNT:STD_LOGIC; SIGNAL LOAD:STD_LOGIC; SIGNAL CARRY1:STD_LOGIC; SIGNAL CARRY2:STD_LOGIC; SIGNAL CARRY3:STD_LOGIC; SIGNAL CARRY4:STD_LOGIC; SIGNAL CARRY5:STD_LOGIC; SIGNAL CARRY6:STD_LOGIC; SIGNAL CARRY7:STD_LOGIC; SIGNAL CARRY8:STD_LOGIC; SIGNAL DIN:STD_LOGIC_VECTOR(31 DOWNTO 0); SIGNAL DOUT:STD_LOGIC_VECTOR(31 DOWNTO 0);

• • • • • • • • • • • • •

ELSIF CLK'EVENT AND CLK= '1' THEN IF ENA= '1' THEN IF CQI<9 THEN CQI<=CQI+1; ELSE CQI<=0;END IF; --大于9,则计数器清零 END IF; END IF; END PROCESS; PROCESS (CQI) BEGIN IF CQI=9 THEN CARRY_OUT<= '1'; --进位输出 ELSE CARRY_OUT<= '0';END IF; END PROCESS; CQ<=CQI;

• 频率测量的基本原理是计算每秒钟内待测信号的 脉冲个数。这就要求TESTCTL的计数使能信号 TSTEN能产生一个1秒脉宽的周期信号,并对频率 计的每一计数器CNT10的ENA使能端进行同步控 制。当TSTEN高电平时,允许计数;低电平时,停止 计数,并保持其所计的数。在停止计数期间,首先需 要一个锁存信号LOAD的上跳沿将计数器在前1秒 钟的计数值锁存进32位锁存器REG32B中,并由外 部的7段译码器译出并稳定显示。锁存信号之后, 必须有一清零信号CLR_CNT对计数器进行清零, 为下1秒钟的计数操作作准备。为了产生这个时序 图,需首先建立一个由D触发器构成的二分频器,在 每次时钟CLK上沿到来时其值翻转。

高效除法器verilog实现

整理文本西北工业大学《 FPGA 技术实验》实验报告二(高效除法器 )学院:软件与微电子学院学号:姓名:专业:微电子学实验时间:2011.10.12实验地点:毅字楼 335指导教师:王少熙西北工业大学2010年 10 月一、实验目的及要求实验目的 : 1.进一步了解熟悉verilog 语句语法掌握条件语句在简单建模中的应用,学会建模仿真综合 .2.熟练运用 modelsim进行调试模拟仿真 .3.初步学会运用综合工具进行综合,熟悉 synplify.实验要求 :用verilog实现一个被除数为8 位,除数为 4 位的高效除法器 .二、实验设备(环境)及要求ModelSim SE 6.2b及 Synplify Pro 9.6.2三、实验内容与步骤1.实验总体设计思路由于只有加法器 ,除法在计算机中是通过部分余数左移加除数补码或 0 实现 ,我们由此可以得到启示 ,也按照如此的思路进行 .整体思路是先将八位 (本来余数是四位的但是我们这里的余数不仅仅充当余数 ,还当中间变量把被除数从最高位一位一位的移到余数里 )余数清零 ,然后把被除数的最高位拼接到余数后面 ,此时余数与除数比较 , 若余数大于除数 ,则把他们俩的差作为新的余数 ,且把对应的商值为记 1; 若余数小于除数 ,则把对应位的商值记 0;进行下一步之前把被除数的第二高位继续拼接到余数后面 ,如此进行 ,循环八次即可 .最后结果是得到商和余数的形式 .其算法流图如下所示 :Start余数 rem=0;商 quo=0; i=7rem={rem[6:0],did[i]}是否rem>disquo[i]=1;i=i-1;quo[i]=0;rem=rem-dis;rem=rem;i=i-1;i<0否是得到 quo,rem.是 4 位,除数 (dis)是 2 位,商(quo)是 4 位 ,余数 (rem)是 4 位,设 did=0110,dis=10,我们来看看是怎么执行的.首先余数和商都清零 ,即 rem=0,quo=0;把被除数的最高位0 拼接到 rem的最低位 ,此时 rem=0000B,由于 rem 小于除数 dis=10,则商 quo[3]=0;下面进行第二次计算,把 did[2]拼接到 rem 最低位 ,此时 rem=0001,dis=10>rem,故 quo[2]=0;继续计算 , 把 did[1]拼接到 rem 最低位 ,此时 rem=0011,dis=10<rem,故quo[1]=1,rem=rem-quo=0011-10=0001;进行最后一轮运算 , 把 did[0]拼接到 rem 最低位 ,此时 rem=0010,dis=10=rem,因此 quo[0]=1,rem=rem-dis=0010-10=0000,至此我们已计算完毕商quo=0011,余数 rem=0000;计算简单快速 .2.测试平台设计模块设计`timescale 1ns/1nsmodule divider_8_4(did,// Divident被除数dis,// Divisor除数quo,// Quotient商rem,// Remainder 余数error//错误,如果除数为0.则error置1);parameter M=7;//被除数,余数,商的位数parameter N=3;//除数的位数input [M:0] did;input [N:0] dis;output [M:0] quo;output [M:0] rem;output error;reg [M:0] quo;reg [M:0] rem;reg error;integer i;//整数,用于计数always @(did or dis)//被除数,除数beginquo=0;rem=0;//开始余数和商清零if(dis==0)error=1;//若除数为0则显示错误else if(did<dis)//为了提高效率,在被除数小于除数时begin//商0,余数为除数rem=dis;quo=0;error=0;endelsebeginerror=0;for (i=8;i>0;i=i-1) //循环8次beginrem={rem[M-1:0],did[i-1]}; //把did[i-1]连接到rem后quo=quo<<1;//商左移一位if(rem>=dis)//若拼接后rem>=除数disbeginquo=quo+1; //商值自加1rem=rem-dis; //新余数变为旧余数减除数endendendend//结束endmoduleTesebench如下 :`timescale 1ns/1nsmodule divider_bench;reg [7:0] did;reg [3:0] dis;wire [7:0] quo;wire [7:0] rem;integer i;//整数,用于控制被除数变化integer j;//整数,用于控制除数变化divider_8_4 d1(did,dis,quo,rem,error); //实例化initialbeginfor(i=0;i<=255;i=i+1)//被除数从0到255begindid=i;for(j=0;j<=15;j=j+1)//除数从0到15变化#1 dis=j;endendinitialbegin$monitor($time,"divident=% divisor=%d quotient=%dremainder=%d",did,dis,quo,rem) ;endinitialbegin#1000 $finish;// 1000ns 时停止仿真endendmodule四、实验结果与数据处理1.Modelsim 仿真结果,波形图,代码覆盖率图等为了严谨 ,把所有的数值都测了一遍 (did 从 0 到 255,dis 从 0 到 15),从modeldim 仿真结果看到程序的正确性 ,鉴于数据较多这里只选择几组数据给予展示 :上图中从上到下一次代表被除数,除数 ,错误 ,商和余数 ,当被除数是 4.除数分别是 9,10,11,12,13,14,15时商为 0,余数分别 9,10,11,12,13,14,15.当被除数为 147,除数分别为 1,2,3,4,5,6,7时 ,商分别为 147,73,49,36,29,24,21,余数分别为 0,1,0,3,2,3,0结.果正确 .由上图可见代码覆盖率已达100%,非常好 .2.综合结果,布局布线结果,关键路径,资源利用率等。

05第6章 VHDL设计应用实例(8位加法器的设计)

第6章 VHDL设计应用实例•6.1 8位加法器的设计实验一:8位加法器的设计• 1. 实验目的• (1) 学习MAX+plus 软件的基本使用方法。

• (2) 学习实验开发系统的基本使用方法。

• (3) 了解VHDL程序的基本结构。

• 2. 实验内容•设计并调试好一个由两个4位二进制并行加法器级联而成的8位二进制并行加法器,并用EDA实验开发系统进行硬件验证。

• 3. 实验要求• (1) 画出系统的原理框图,说明系统中各主要组成部分的功能。

• (2) 编写各个VHDL源程序。

• (3) 根据选用的软件编好用于系统仿真的测试文件。

• (4) 根据选用的软件及EDA实验开发装置编好用于硬件验证的管脚锁定文件。

• (5) 记录系统仿真、硬件验证结果。

• (6) 记录实验过程中出现的问题及解决办法。

实验连线全加器的17个输入所对应的管脚同17位拨码开关相连,16个输入管脚是a0~a7、b0~b7,其中a0~a7、b0~b7代表两个8位二进制数,cin代表低八位来的进位位;9个输出所对应的管脚同9位发光二极管相连,9个输出管脚是sum0~sum7和cout:其中sum0~sum7代表相加结果,cout代表进位位。

000000001111111110000000011111110100000000......00000001 (1)00000000000000001111111111111111101111111011111110000000000......00000001 000000000000000000CoutS8(7..0)A8(7..0)B8(7..0)C in实验结果输入8位加法器的设计过程• 1.设计思路•加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器都可由加法器来构成。

多位加法器的构成有两种方式:并行进位和串行进位。

并行进位加法器设有进位产生逻辑,运算速度较快;串行进位方式是将全加器级联构成多位加法器。

vhdl语言的除法用法

VHDL语言的除法用法1.引言在硬件描述语言(HD L)中,V HD L是一种广泛使用的工业标准。

它提供了一种描述数字电路行为的方法。

V HDL语言强大而灵活,能够很好地支持多种数字逻辑设计需求。

本文将探讨V HD L语言中除法的用法,介绍如何在V HD L代码中实现除法功能。

2.除法的基本概念除法是一种基本的数学运算,用于将一个数(被除数)分成若干等分(除数)。

在数字电路设计中,除法运算常常涉及到位操作和时序控制。

V H DL语言提供了一种方便的方法来描述和实现除法操作。

3. VH DL语言中的除法操作3.1整数除法在V HD L语言中,整数除法可以通过使用`/`操作符来实现。

例如,假设我们要计算被除数A除以除数B的商C:C<=A/B;需要注意的是,这种整数除法会直接截断小数部分,只保留整数部分。

如果想要保留小数部分,可以使用浮点数类型。

3.2浮点数除法V H DL语言也支持浮点数除法。

浮点数除法可以通过使用`rea l`或`r ea lt yp e`类型来实现。

以下是一个示例:s i gn al A,B,C:re al;...C<=A/B;在进行浮点数的除法运算时,VH DL会保留小数部分,并将其存储在指定的信号中。

3.3时序控制在进行除法运算时,特别是在时序控制电路中,需要考虑时钟信号和状态机的操作。

例如,可以使用V HD L中的进程(pr oc es s)语句结合时钟信号和状态机来实现除法运算的时序控制。

p r oc es s(cl k)b e gi ni f ri si ng_e dg e(clk)th eni f re se t='1't he n--复位...e l se--进行除法运算...e n di f;e n di f;e n dp ro ce ss;通过结合时钟信号和状态机,可以实现对除法运算的精确控制和同步操作。

4.除法的应用场景除法运算在数字电路设计中有很多应用场景。

八位运算器实验报告

《组成原理》实验报告姓名:***____________专业:网络工程________学号:**********______日期:2014年11月25日实验一:8位运算器的设计1,设计目的:1)学习并练习verilog语言2)了解8位加法器实现原理2,设计目标:1)使用verilog语言编写8为运算器并进行仿真模拟3,模块设计规格及输入输出端变量说明1)3模块设计规格及输入输出端变量说明:输入:[2:0]s(操作指令), LDA,LDB(输入控制), [7:0]IN(输入数);输出:[7:0]A,B(操作数), ALU(结果寄存器),FZ(判零), FC(进位);2)操作指令表:4,程序原理连接图5,程序代码Module test (T4,s,A,B,LDA,LDB,FZ,FC,IN,ALU);input [2:0] s;input LDA,LDB,T4;input [7:0] IN;output [7:0] A,B,ALU;output FZ,FC;reg [7:0] A,B,ALU;reg FZ,FC;/** 输入模块,当clk上升沿时,如果LDA为1,则把IN的值给A,否则赋给B */always @ (posedge CLK)beginif(LDA==1'b1)beginA<=IN;endelse if(LDB==1'b1)beginB<=IN;endend/**计算模块,根据操作数s的不同值为A和B进行八种不同的计算,其中当A+B *进行加法计算时,把进位值赋给FC*/always @ (s[2] or s[1] or s[0])begincase ({s[2],s[1],s[0]})3'b000:ALU<=A;//直接赋值3'b001:ALU<=A&B;//A与B按位与3'b010:ALU<=A|B;//A与B按位或3'b011:ALU<=~A;//非A3'b100:ALU<=(A<<1);//A左移一位3'b101:{FC,ALU}<=A+B;//ALU=A+B,FC为A+B的进位3'b110:ALU<=A+1;//加一操作3'b111:ALU<=A-1;//减一操作endcaseend/**该模块的作用是判断ALU是否为,若是FZ赋为1*/always @ (negedge T4)beginif(ALU==8'b00000000)FZ<=1'b1;elseFZ<=1'b0;endendmodule6时序仿真图:。

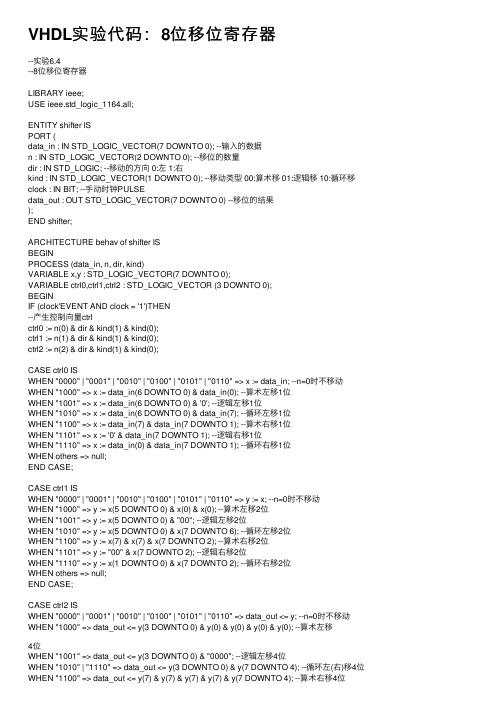

VHDL实验代码:8位移位寄存器

VHDL实验代码:8位移位寄存器--实验6.4--8位移位寄存器LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY shifter ISPORT (data_in : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --输⼊的数据n : IN STD_LOGIC_VECTOR(2 DOWNTO 0); --移位的数量dir : IN STD_LOGIC; --移动的⽅向 0:左 1:右kind : IN STD_LOGIC_VECTOR(1 DOWNTO 0); --移动类型 00:算术移 01:逻辑移 10:循环移clock : IN BIT; --⼿动时钟PULSEdata_out : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --移位的结果);END shifter;ARCHITECTURE behav of shifter ISBEGINPROCESS (data_in, n, dir, kind)VARIABLE x,y : STD_LOGIC_VECTOR(7 DOWNTO 0);VARIABLE ctrl0,ctrl1,ctrl2 : STD_LOGIC_VECTOR (3 DOWNTO 0);BEGINIF (clock'EVENT AND clock = '1')THEN--产⽣控制向量ctrlctrl0 := n(0) & dir & kind(1) & kind(0);ctrl1 := n(1) & dir & kind(1) & kind(0);ctrl2 := n(2) & dir & kind(1) & kind(0);CASE ctrl0 ISWHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => x := data_in; --n=0时不移动WHEN "1000" => x := data_in(6 DOWNTO 0) & data_in(0); --算术左移1位WHEN "1001" => x := data_in(6 DOWNTO 0) & '0'; --逻辑左移1位WHEN "1010" => x := data_in(6 DOWNTO 0) & data_in(7); --循环左移1位WHEN "1100" => x := data_in(7) & data_in(7 DOWNTO 1); --算术右移1位WHEN "1101" => x := '0' & data_in(7 DOWNTO 1); --逻辑右移1位WHEN "1110" => x := data_in(0) & data_in(7 DOWNTO 1); --循环右移1位WHEN others => null;END CASE;CASE ctrl1 ISWHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => y := x; --n=0时不移动WHEN "1000" => y := x(5 DOWNTO 0) & x(0) & x(0); --算术左移2位WHEN "1001" => y := x(5 DOWNTO 0) & "00"; --逻辑左移2位WHEN "1010" => y := x(5 DOWNTO 0) & x(7 DOWNTO 6); --循环左移2位WHEN "1100" => y := x(7) & x(7) & x(7 DOWNTO 2); --算术右移2位WHEN "1101" => y := "00" & x(7 DOWNTO 2); --逻辑右移2位WHEN "1110" => y := x(1 DOWNTO 0) & x(7 DOWNTO 2); --循环右移2位WHEN others => null;END CASE;CASE ctrl2 ISWHEN "0000" | "0001" | "0010" | "0100" | "0101" | "0110" => data_out <= y; --n=0时不移动WHEN "1000" => data_out <= y(3 DOWNTO 0) & y(0) & y(0) & y(0) & y(0); --算术左移4位WHEN "1001" => data_out <= y(3 DOWNTO 0) & "0000"; --逻辑左移4位WHEN "1010" | "1110" => data_out <= y(3 DOWNTO 0) & y(7 DOWNTO 4); --循环左(右)移4位WHEN "1100" => data_out <= y(7) & y(7) & y(7) & y(7) & y(7 DOWNTO 4); --算术右移4位WHEN "1101" => data_out <= "0000" & y(7 DOWNTO 4); --逻辑右移4位WHEN others => null;END CASE;END IF;END PROCESS;END behav;。

verilog hdl除法

verilog hdl除法在Verilog HDL中,除法运算可以通过数学运算符/来实现。

除法运算可以用来实现数字的整除或者小数的精确除法。

在Verilog HDL中,除法运算可以在模块中使用,也可以在操作数级别使用。

1. 在模块中使用除法运算符:可以在模块内部定义一个除法运算的变量,然后使用/运算符计算两个操作数的商。

例如,下面的Verilog代码显示了一个简单的模块,该模块计算两个输入数的除法结果:```verilogmodule divider (input [7:0] a,input [7:0] b,output [7:0] result);assign result = a / b;endmodule```在上面的例子中,输入a和b都是8位宽度的寄存器,而输出result也是8位宽度。

通过使用assign语句,我们将输入a除以b的结果赋值给输出result。

2. 在操作数级别使用除法运算符:除了在模块中使用除法运算符外,我们还可以在操作数级别使用除法运算符。

这意味着可以直接将除法运算的结果赋值给一个变量,而无需在模块内部进行计算。

```verilogreg [7:0] a;reg [7:0] b;reg [7:0] result;initial begina = 16;b = 4;result = a / b;$display("Result: %d", result);end```在上面的例子中,我们定义了三个8位宽度的寄存器a、b和result。

使用initial块,我们对寄存器a和b进行赋值,然后将a除以b的结果赋值给result。

最后,我们使用$display函数打印结果。

3. 除法运算的注意事项:在Verilog HDL中,除法运算有一些特殊的情况需要注意:- 如果除数为0,则会产生除以零的错误。

在除数可能为零的情况下,应该在代码中添加适当的检查机制。

- 如果被除数和除数的位宽不同,则除法运算将截断除法结果的小数部分。

基于VHDL语言的8位RISC-CPU的设计 终稿

毕业设计说明书基于VHDL语言的8位RISC-CPU的设计学院:专业:学生姓名:学号:指导教师:201 年月中文摘要摘要RISC即精简指令集计算机(Reduced Instruction Set Computer)的缩写。

RISC-CPU与一般的CPU相比,通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。

本文对RISC-CPU的架构进行了分析,并使用VHDL 语言设计了8位RISC-CPU IP软核。

RISC-CPU由八大基本模块构成:时钟发生器、指令寄存器、累加器、算术逻辑单元、数据输出控制器、地址多路器、程序计数器、状态控制器。

本设计中借助MAX+PLUSⅡ软件平台对各模块进行时序仿真,并最终给出了指令执行的仿真波形,验证了CPU的功能。

设计仿真结果表明,该8位RISC-CPU能够完成既定的任务指标,而且在运行效率上有一定程度改善。

关键词:RISC-CPU、VHDL、MAX+PLUSⅡ、IP软核、时序仿真AbstractRISC reduced instruction set computer that (Reduced Instruction Set Computer) acronym. RISC-CPU and CPU in general compared to instruction by simplifying the structure of the computer is more simple and reasonable, thereby increasing processing speed. In this paper, RISC-CPU architecture is analyzed, and by using the VHDL language, I designed an 8-bit RISC-CPU IP soft core.RISC-CPU is based on 8 modules: clock generator, instruction register, accumulator, arithmetic logic unit, data output controller, address multiplexer, program counter, state controller. In the design, each module are timing simulated on MAX+PLUSⅡ software platform, and finally the simulated waveform of instruction execution that verifies the CPU features is given.Design and simulation results show that the 8-bit RISC-CPU can complete the tasks, and also has a certain degree of improvement on operational efficiency. Keywords: RISC-CPU, VHDL, MAX+PLUSⅡ, IP soft core, Timing Simulation目录摘要 (I)ABSTRACT(英文摘要) (II)目录 ............................................................................................................................................. I II 第一章引言 .. (1)1.1课题背景与发展现状 (1)1.1.1课题背景 (1)1.1.2RISC-CPU的发展现状 (1)1.2RISC-CPU优势与现实意义 (1)1.2.1RISC-CPU具备的优势 (1)1.2.2本课题的现实意义 (2)1.3本设计的主要内容 (2)第二章RISC-CPU的架构设计 (3)2.1RISC-CPU基本架构 (3)2.2RISC-CPU模块的划分 (4)第三章八位RISC-CPU各模块设计与仿真 (6)3.1时钟发生器 (6)3.2指令寄存器 (7)3.3累加器 (10)3.4算术逻辑单元 (11)3.5数据输出控制器 (13)3.6地址多路器 (14)3.7程序计数器 (15)3.8状态控制器 (17)第四章RISC-CPU的综合及操作时序 (25)4.1RISC-CPU各模块综合 (25)4.2CPU复位启动操作时序 (29)结论 (30)参考文献 (31)致谢 (32)第一章引言1.1 题背景与发展现状1.1.1 课题背景CPU是Central Processing Unit——中央处理器的缩写,它是计算机中最重要的一个部分。

基于VHDL语言的8位CPU的设计(quartus仿真)

假设指令地址为0、1、2、3…,为便于显示,设置地址指令和程序计数器输出为数制十进制, 仿真波形如下图:

图2.14 程序计数电路仿真波形

第二部分:RISC-CPU各模块设计与仿真

8. 状态控制器

是CPU的控制核心, 用于产生一系列的控 制信号,启动或停止 某些部件,由状态机 和状态机控制器组成, 如图。

图2.9 数据输出控制器

假设累加器输出值由00000000递增,验证当data_ena为1时,data输出alu_out的值,当 data_ena为0时,data输出"ZZZZZZZZ"。波形如下:

图2.10 数据输出控制器仿真波形

第二部分:RISC-CPU各模块设计与仿真

6. 地址多路器

用于选择输出的地址是PC地址还是数据/ 端口地址,如图2.11所示。每个指令周期的 前4个时钟周期用于从ROM中读取指令,输 出PC地址。后4个时钟周期用于对RAM或 端口的读写,输出数据或端口地址。

图2.7算术逻辑单元

在仿真过程中,假设操作码依次为上述8种操作码。数据值为5,累加器值为由3变0,以此来 验证zero作用。仿真波形下图所示:

图2.8 算术逻辑运算单元仿真波形

第二部分:RISC-CPU各模块设计与仿真

5.数据输出控制器

控制累加器数据输出,如图2.9由于数据总 线是各种操作时传送数据的公共通道,不同 的情况下传送不同的内容。有时要传输指令, 有时要传送RAM区或接口的数据。

图3.2 RISC-CPU各模块连接图

谢谢!!

WPS Office

Make Presentation much more fun

@WPS官方微博 @kingsoftwps

基于VHDL语言的8位 RISC-CPU的设计

VHDL_8位CPU设计_包含程序

实用文档Computer Organization and ArchitectureCourse DesignThe Experiment ReportOfCPUI . PurposeThe purpose of this project is to design a simple CPU (Central Processing Unit). This CPU has basic instruction set, and we will utilize its instruction set to generate a very simple program to verify its performance. For simplicity, we will only consider the relationship among the CPU, registers, memory and instruction set. That is to say we only need consider the following items: Read/Write Registers, Read/Write Memory and Execute the instructions.At least four parts constitute a simple CPU: the control unit, the internal registers, the ALU and instruction set, which are the main aspects of our project design and will be studied.II . Instruction SetSingle-address instruction format is used in our simple CPU design. The instruction word contains two sections: the operation code (opcode), which defines the function of instructions (addition, subtraction, logic operations, etc.); the address part, in most instructions, the address part contains the memory location of the datum to be operated, we called it direct addressing. In some instructions, the address part is the operand, which is called immediate addressing.For simplicity, the size of memory is 256× 16 in the computer. The instruction word has 16 bits. The opcode part has 8 bits and address part has 8 bits. The instructionFigure 1 the instruction formatThe opcode of the relevant instructions are listed in Table 1.In Table 1, the notation [x] represents the contents of the location x in the memory. For example, the instruction word (03B916) means that the CPU adds word at location B916 in memory into the accumulator (ACC); the instruction word (050716) means if the sign bit of the ACC (ACC [15]) is 0, the CPU will use the address part of the instruction as the address of next instruction, if the sign bit is 1, the CPU will increase the program counter (PC) and use its content as the address of the next instruction.Table 1 List ofCalculate the sum of all integers from 1 to 100.(1), programming with C language:sum=0;temp=100;loop :sum=sum+temp;temp=temp-1;if temp>=0 goto loop;end(2), Assume in the RAM_DQ:sum is stored at location A4,temp is stored at location A3,the contents of location A0 is 0,the contents of location A1 is 1,the contents of location A2 is 10010=6416.We can translate the above C language program with the instructions listed in Table 1 into the instruction program as shown in Table 2.Table 2 Example of a program to sum from 1 to 100III. Internal Registers and MemoryMAR (Memory Address Register)MAR contains the memory location of the word to be read from the memory or written into the memory. Here, READ operation is denoted as the CPU reads from memory, and WRITE operation is denoted as the CPU writes to memory. In our design, MAR has 8 bits to access one of 256 addresses of the memory.MBR (Memory Buffer Register)MBR contains the value to be stored in memory or the last value read from memory. MBR is connected to the address lines of the system bus. In our design, MBR has 16 Bits.PC (Program Counter)PC keeps track of the instructions to be used in the program. In our design, PC has 8 bits.IR (Instruction Register)IR contains the opcode part of an instruction. In our design, IR has 8 bits.BR (Buffer Register)BR is used as an input of ALU, it holds other operand for ALU. In our design, BR has16 bits.LPM_RAM_DQLPM_RAM_DQ is a RAM with separate input and output ports. It works as a memory, and its size is 256×16. Although it’s not an internal register of CPU, we need it to simulate and test the performance of CPU.LPM_ROMLPM_ROM is a ROM with one address input port and one data output port, and its size of data is 32bits which contains control signals to execute micro-operations.IV.ALUALU (Arithmetic Logic Unit) is a calculation unit which accomplishes basic arithmetic and logic operations. In our design, some operations must be supported which are listed as follows:Table 3 ALU OperationsV. Micro-programmed Control UnitIn the Microprogrammed control, the microprogram consists of some microinstruction and the microprogram is stored in control memory that generates all the control signals required to execute the instruction set correctly. The microinstruction contains some micro-operations which are executed at the same time.Figure 2 shows the key elements of such an implementation.The set of microinstructions is stored in the control memory. The control address register contains the address of the next microinstructions to be read. When a microinstruction is read from the control memory, it is transferred to a control buffer register. The register connects to the control lines emanating from the control unit. Thus, reading a microinstruction from the control memory is the same as executing that microinstruction. The third element shown in the figure is a sequencing unit that loads the control address register and issues a read command.Figure 2 Control Unit Micro-architecture(I)Total control signals for instructions are listed as follows:Table 4 Control signals for the micro-operationsfollows:0 : 00810000; R←1, CAR←CAR+11 : 00A00000; OP←MBR[15..8],CAR←CAR+12 : 02000000; CAR←CAR+OP3 : 01000014; CAR←14H4 : 01000019; CAR←19H5 : 0100001E; CAR←1EH6 : 01000023; CAR←23H7 : 01000041; CAR←41H8 : 01000028; CAR←28H9 : 0100002D; CAR←2DHa : 01000032; CAR←32Hb : 01000037; CAR←37Hc : 0100003C; CAR←3CHd : 01000046; CAR←46He : 0100004B; CAR←4Hf : 00000000;………14 : 00840000; MAR←MBR[7..0], CAR←CAR+1 ------STORE15 : 00920200; MBR←ACC, PC←PC+1,W←1,CAR←CAR+116 : 04080000; CAR←019 : 00840000; MAR←MBR[7..0], CAR←CAR+1 ------LOAD1a : 00810A00; PC←PC+1,R←1,ACC←0,CAR←CAR+11b : 00C03000; BR←MBR,ACC←ACC+BR, CAR←CAR+11c : 04080000; CAR←01d : 00000000;1e : 00840000; MAR←MBR[7..0], CAR←CAR+1 ----------ADD1f : 00810200; PC←PC+1,R←1,CAR←CAR+120 : 00C03000; BR←MBR,ACC←ACC+BR, CAR←CAR+121 : 04080000; CAR←022 : 00000000;23 : 00840000; MAR←MBR[7..0], CAR←CAR+1 ----------SUB24 : 00810200; PC←PC+1,R←1,CAR←CAR+125 : 00C04000; BR←MBR,ACC←ACC-BR, CAR←CAR+126 : 04080000; CAR←027 : 00000000;28 : 00840000; MAR←MBR[7..0], CAR←CAR+1 ---------AND29 : 00810200; PC←PC+1,R←1,CAR←CAR+12a : 00C06000; BR←MBR,ACC←ACC AND BR,CAR←CAR+12b : 04080000; CAR←02c : 00000000;2d : 00840000; MAR←MBR[7..0], CAR←CAR+1 ---------OR2e : 00810200; PC←PC+1,R←1,CAR←CAR+12f : 00C07000; BR←MBR,ACC←ACC OR BR, CAR←CAR+130 : 04080000; CAR←031 : 00000000;32 : 00840000; MAR←MBR[7..0], CAR←CAR+1 ----------NOT33 : 00808200; PC←PC+1, ACC←NOT ACC,CAR←CAR+134 : 04080000; CAR←035 : 00000000;36 : 00000000;37 : 00840000; MAR←MBR[7..0], CAR←CAR+1 ----------SHIFTR38 : 08092000; PC←PC+1, ACC←SHIFT ACC to Right 1 bit,CAR←CAR+139 : 04080000; CAR←03a : 00000000;3b : 00000000;3c : 00840000; MAR←MBR[7..0], CAR←CAR+1 -----------SHIFTL3d : 0080A200; PC←PC+1, ACC←SHIFT ACC to Left 1 bit,CAR←CAR+1 3e : 04080000; CAR←03f : 00000000;40 : 00000000;41 : 00840000; MAR←MBR[7..0], CAR←CAR+1 -----------JMPGEZ42 : 00805000; CAR←CAR+1,43 : 04080000; CAR←046 : 00840000; MAR←MBR[7..0], CAR←CAR+1 ------------MPY47 : 00810200; PC←PC+1,R←1,CAR←CAR+148 : 00C0B000; BR←MBR,ACC←ACC*BR, CAR←CAR+149 : 04080000; CAR←04a : 00000000;4b : 0100004B; CAR←4BH ------------------------------HALT 4c : 00000000;(III)The simulation waveforms of some operates1, load, add, store, halt (22+10)The contents in RAM:0 : 022A; Load 2A1 : 032B; ADD 2B2 : 012C; Store 2C3 : 0C00; Halt2a : 0016;2b : 000A;The content in RAM addressed of 2b is 0020(H).The waveform of the operate:2, load, SUB, store, halt (22-10)The contents in RAM:0 : 022A; Load 2A1 : 042B; SUB 2B2 : 012C; Store 2C3 : 0C00; Halt2a : 0016;2b : 000A;The content in RAM addressed of 2c is 000C(H).The waveform of the operate:3, load, mpy, add, store, halt (13*10+22)The contents in RAM:0 : 022A; Load 2A1 : 0B2B; MPY 2B2 : 032C; ADD 2C3 : 012D; Store 2D4 : 0C00; Halt2a : 000D;2b : 000A;2c : 0016;The content in RAM addressed of 2d is 0098(H). The waveform of the operate:4, S um from 1 to 100The contents in RAM are shown in table2.The content in RAM addressed of A4 is 13BA(H).The waveform of the operate:The clock cycle of CAR is 400 ns.From the waveform, it takes 2.314ms to execute the operate. So the number of the executing cycles is 2.134/0.0004=5335.VI. Appendix:(I)The GDF of CPU:(II) The code of the CPU program:1, MBR (Memory Buffer Register)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MBR isport( clk, reset, MBR_OPc, ACC_MBRc,R,W:in std_logic;ACC_MBR :in std_logic_vector(15 downto 0);RAM_MBR :in std_logic_vector(15 downto 0);MBR_RAM :out std_logic_vector(15 downto 0);MBR_BR :out std_logic_vector(15 downto 0);MBR_OP :out std_logic_vector(7 downto 0);MBR_MAR :out std_logic_vector(7 downto 0);MBR_PC :out std_logic_vector(7 downto 0));end MBR;architecture behave of MBR isbeginprocess(clk)variable temp:std_logic_vector(15 downto 0);beginif(clk'event and clk='0')thenif reset='1' thenif ACC_MBRc='1' then temp:=ACC_MBR; end if;if R='1' then MBR_BR<=RAM_MBR; end if;if W='1' then MBR_RAM<=temp; end if;MBR_MAR<=RAM_MBR(7 downto 0);MBR_PC<=RAM_MBR(7 downto 0);if MBR_OPc='1' then MBR_OP<=RAM_MBR(15 downto 8); end if; else MBR_BR<=x"0000";MBR_MAR<="00000000";MBR_OP<="00000000";MBR_PC<="00000000";end if;end if;end process;end behave;2, BR (Buffer Register)library ieee;use ieee.std_logic_1164.all;entity BR isport( MBR_BRc:in std_logic;MBR_BR:in std_logic_vector(15 downto 0);BRout:out std_logic_vector(15 downto 0));end BR;architecture behave of BR isbeginprocessbeginif MBR_BRc='1' then BRout<=MBR_BR; end if;end process;end behave;3, MAR (Memory Address Register)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MAR isport( clk,PC_MARc,MBR_MARc:in std_logic;PC,MBR_MAR:in std_logic_vector(7 downto 0);MARout:out std_logic_vector(7 downto 0));end MAR;architecture behave of MAR isbeginprocess(clk)beginif(clk'event and clk='1')thenif PC_MARc='1' then MARout<=PC; end if; if MBR_MARc='1' then MARout<=MBR_MAR; end if;end if;end process;end behave;4, PC (Program Counter)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity PC isport( clk,PCjmp,PCc1,PCinc,PCc3,reset:in std_logic;CONTRalu :in std_logic_vector(3 downto 0);MBR_PC :in std_logic_vector(7 downto 0);PCout :buffer std_logic_vector(7 downto 0));end PC;architecture behave of PC isbeginprocess(clk)beginif(clk'event and clk='0')thenif reset='1' thenif CONTRalu="0101" thenif PCjmp='1' then PCout<=MBR_PC;elsif PCjmp='0' then PCout<=PCout+1;end if;end if;if PCc1='1' then PCout<="00000000"; end if; if PCinc='1' then PCout<=PCout+1; end if; if PCc3='1' then PCout<=MBR_PC; end if; else PCout<="00000000";end if;end if;end process;end behave;5, IR (Instruction Register)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity IR isport( opcode :in std_logic_vector(7 downto 0);IRout :out std_logic_vector(7 downto 0));end IR;architecture behave of IR isbeginIRout<=opcode;end behave;6, CAR (Control Address Register)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CAR isport( clk,reset :in std_logic;CARc :in std_logic_vector(3 downto 0);CAR,OP :in std_logic_vector(7 downto 0);CARout:buffer std_logic_vector(7 downto 0));end CAR;architecture behave of CAR isbeginprocess(clk)beginif(clk'event and clk='1')thenif reset='1' thenif CARc="1000" then CARout<="00000000"; end if; if CARc="0100" then CARout<=OP+CARout; end if; if CARc="0010" then CARout<=CAR; end if; if CARc="0001" then CARout<=CARout+1; end if; else CARout<="00000000";end if;end if;end process;end behave;7, CONTRALR (Control Buffer Register)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CONTROLR isport(control :in std_logic_vector(31 downto 0); R,W, RW, PCc1,PCinc,PCc3:out std_logic;ACCclear,MBR_MARc,PC_MARc:out std_logic; ACC_MBRc,MBR_OPc,MBR_BRc:out std_logic;CONTRout:out std_logic_vector(3 downto 0); CARc :out std_logic_vector(3 downto 0); CAR :out std_logic_vector(7 downto 0)); end CONTROLR;architecture behave of CONTROLR isbeginprocessbeginCAR<=control(7 downto 0);PCc1<=control(8);PCinc<=control(9);PCc3<=control(10);ACCclear<=control(11);CONTRout<=control(15 downto 12);R<=control(16);W<=control(17);MBR_MARc<=control(18);PC_MARc<=control(19);ACC_MBRc<=control(20);MBR_OPc<=control(21);MBR_BRc<=control(22);CARc<=control(26 downto 23);RW<=control(17);end process;end behave;8, ALU (Arithmetic Logic Unit)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ALU isport( clk,reset,ACCclear:in std_logic;aluCONTR :in std_logic_vector(3 downto 0);BR :in std_logic_vector(15 downto 0);PCjmp :out std_logic;ACC :buffer std_logic_vector(15 downto 0));end ALU;architecture behave of ALU isbeginprocess(clk)beginif(clk'event and clk='0')thenif reset='0' then ACC<=x"0000";elseif ACCclear='1' then ACC<=x"0000"; end if;if aluCONTR="0011" then ACC<=BR+ACC; end if; --ADD if aluCONTR="0100" then ACC<=ACC-BR; end if; --SUB if aluCONTR="0110" then ACC<=ACC and BR; end if; --AND if aluCONTR="0111" then ACC<=ACC or BR; end if; --OR if aluCONTR="1000" then ACC<=not ACC; end if; --NOT if aluCONTR="1001" then --SRR ACC(14 downto 0)<=ACC(15 downto 1); ACC(15)<='0';end if;if aluCONTR="1010" then --SRL ACC(15 downto 1)<=ACC(14 downto 0); ACC(0)<='0';end if;if aluCONTR="1011" then ACC<=ACC*BR; end if; --MPY end if;end if;if ACC>0 then PCjmp<='1';else PCjmp<='0';end if;end process;end behave;。

VHDL实现简单的8位CPU

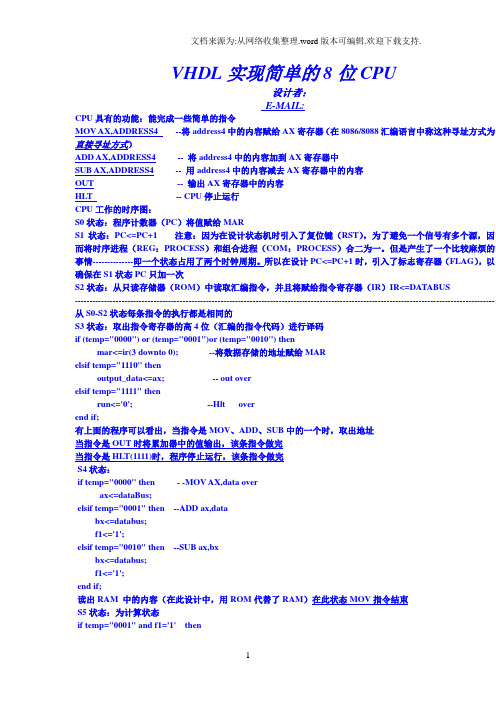

VHDL实现简单的8位CPU设计者:E-MAIL:CPU具有的功能:能完成一些简单的指令MOV AX,ADDRESS4 --将address4中的内容赋给AX寄存器(在8086/8088汇编语言中称这种寻址方式为直接寻址方式)ADD AX,ADDRESS4 -- 将address4中的内容加到AX寄存器中SUB AX,ADDRESS4 -- 用address4中的内容减去AX寄存器中的内容OUT -- 输出AX寄存器中的内容HLT -- CPU停止运行CPU工作的时序图:S0状态:程序计数器(PC)将值赋给MARS1状态:PC<=PC+1 注意:因为在设计状态机时引入了复位键(RST),为了避免一个信号有多个源,因而将时序进程(REG:PROCESS)和组合进程(COM:PROCESS)合二为一。

但是产生了一个比较麻烦的事情--------------即一个状态占用了两个时钟周期。

所以在设计PC<=PC+1时,引入了标志寄存器(FLAG),以确保在S1状态PC只加一次S2状态:从只读存储器(ROM)中读取汇编指令,并且将赋给指令寄存器(IR)IR<=DATABUS------------------------------------------------------------------------------------------------------------------------------------------------ 从S0-S2状态每条指令的执行都是相同的S3状态:取出指令寄存器的高4位(汇编的指令代码)进行译码if (temp="0000") or (temp="0001")or (temp="0010") thenmar<=ir(3 downto 0); --将数据存储的地址赋给MARelsif temp="1110" thenoutput_data<=ax; -- out overelsif temp="1111" thenrun<='0'; --Hlt overend if;有上面的程序可以看出,当指令是MOV、ADD、SUB中的一个时,取出地址当指令是OUT时将累加器中的值输出,该条指令做完当指令是HLT(1111)时,程序停止运行,该条指令做完S4状态:if temp="0000" then - -MOV AX,data overax<=dataBus;elsif temp="0001" then --ADD ax,databx<=databus;f1<='1';elsif temp="0010" then --SUB ax,bxbx<=databus;f1<='1';end if;读出RAM 中的内容(在此设计中,用ROM代替了RAM)在此状态MOV指令结束S5状态:为计算状态if temp="0001" and f1='1' thenax<=ax+bx;f1<='0';elsif temp="0010" and f1='1' thenax<=ax-bx;f1<='0';end if;当指令是ADD(0001)时,AX<=AX+BX当指令是SUB(0010)时,AX<=AX-BX此图为Modelsim se6.0的功能仿真图(结果为62 =(10+20+1)×2 注:×2用SHL指令实现因为其目的寄存器为Ax所以实现方法同OUT、HLT请读者自己实现)源程序:ROM16_4.VHD--//////////////////////////////////////////////////////////--16*8ROM--CE=0时允许读--huyugui--2005,1,28--//////////////////////////////////////////////////////////library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity rom16_8 isport( addr:in std_logic_vector(3 downto 0);ce:in std_logic;dataout:out std_logic_vector(7 downto 0));end entity rom16_8;architecture behave of rom16_8 isbegin--10+20+60-10=80hdataout<="00001001" when addr="0000" and ce='0' else --mov ax,9h"00011010" when addr="0001" and ce='0' else --add ax,ah"00011011" when addr="0010" and ce='0' else --add ax,bh"00101100" when addr="0011" and ce='0' else --sub ax,ch"" when addr="0100" and ce='0' else --out"" when addr="0101" and ce='0' else --hlt"00000000" when addr="0110" and ce='0' else"00000000" when addr="0111" and ce='0' else"00000000" when addr="1000" and ce='0' else"00010000" when addr="1001" and ce='0' else --10h"00100000" when addr="1010" and ce='0' else --20h"01100000" when addr="1011" and ce='0' else --60h"00010000" when addr="1100" and ce='0' else --10h"00000000" when addr="1101" and ce='0' else"00000000" when addr="1110" and ce='0' else"00000000" when addr="1111" and ce='0' else"";end architecture behave;CPU_CONTROL.VHD--/////////////////////////////////////////////////////////////////////////////--8_CPU--mov ax,address /add ax,address/sub ax,address/out /hlt--说明:address为4位的地址(9H-fH)--完善:每个状态为一个时钟周期,这样的话PC<=PC+1在S1状态将只做一次,时钟将--得到很大的改善--设计者:胡玉贵--时间:2005,1,29A--/////////////////////////////////////////////////////////////////////////////library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity cpu_control isport(clk:in std_logic;rst:in std_logic;output_data,databus_out:out std_logic_vector(7 downto 0));end entity cpu_control;architecture behave of cpu_control iscomponent rom16_8 isport( addr:in std_logic_vector(3 downto 0);ce:in std_logic;dataout:out std_logic_vector(7 downto 0));end component rom16_8;type states is (s0,s1,s2,s3,s4,s5);signal current_state,next_state:states;signal flag:std_logic;signal pc,addrbus:std_logic_vector(3 downto 0);signal ax,bx:std_logic_vector(7 downto 0);--Ax,Bxsignal cs:std_logic;signal databus:std_logic_vector(7 downto 0);signal run:std_logic;signal mar:std_logic_vector(3 downto 0);signal ir:std_logic_vector(7 downto 0);signal f1:std_logic;beginreg:processvariable temp:std_logic_vector(3 downto 0);beginif rst='1' then --系统复位pc<="0000";ax<="00000000";bx<="00000000";run<='1';flag<='1'; --PC可以加1f1<='1';current_state<=s0;--databus<="00000000";elsif rising_edge(clk) thenif run='1' thencase current_state iswhen s0=>next_state<=s1; --Address State&Fetchmar<=pc; --将PC的值赋给MAR,在S2状态时从ROM中读出指令(IR<=databus)when s1=>next_state<=s2;if flag='1' thenpc<=pc+1; --地址加1flag<='0';end if;when s2=>next_state<=s3;flag<='1' ;ir<=databus; --将ROM中的指令赋给IR(指令寄存器)when s3=>next_state<=s4;temp:=ir(7 downto 4); --取指令寄存器的高4位(指令代码MOV 0000,ADD 0001,SUB 0010)-- Mov Add Subif (temp="0000") or (temp="0001")or (temp="0010") thenmar<=ir(3 downto 0); --将数据存储的地址赋给MARelsif temp="1110" thenoutput_data<=ax; -- out overelsif temp="1111" thenrun<='0'; --Hlt overend if;when s4=>next_state<=s5; --在S4状态,将从数据总线上读取数据if temp="0000" then --MOV AX,data overax<=dataBus;elsif temp="0001" then --ADD ax,databx<=databus;f1<='1';elsif temp="0010" then --SUB ax,bxbx<=databus;f1<='1';end if;when s5=>next_state<=s0;if temp="0001" and f1='1' thenax<=ax+bx;f1<='0';elsif temp="0010" and f1='1' thenax<=ax-bx;f1<='0';end if;end case;current_state<=next_state; --此设计使每个状态为两个时钟周期(Attention) end if;end if;end process reg;u1:rom16_8 port map(addrbus,cs,databus);addrbus<=mar when (current_state=s2) or (current_state=s4) else"0000";cs<='0' when (current_state=s2) or (current_state=s4) else'1';databus_out<=databus;end architecture behave;参考书目:微机原理及应用第3章:清华大学出版社VHDL和数字电路设计:科学出版社VHDL实用教程:电子科技大出版社。

基于VHDL的8位除法器的实现

基于VHDL的8位除法器的实现The Design of 8 Division With VHDL摘要:介绍了利用VHDL实现八位除法,采用层次化设计,给出了实现除法的子模块程序。

使用Altera公司的MAX+PLUSII10.2开发软件进行功能仿真并给出仿真波形。

关键词:二进制除法 VHDL MAX+PLUS2Abstract:The design of division(8/8) by hierarchy technique is proposed. Schematic documents and submodule program with VHDL language are also given. At the end of the article, using MAX+PLUS2, the flow char is given and the simulation result is attached.Keywords: division VHDL MAX+PLUS2引言除法是数值计算和数据分析中最常用的运算之一,许多高级运算如平方根、指数、三角函数等都与其有关。

在FPGA中,有加、减、乘、除的算法指令,但除法中除数必须是2的幂,因此无法实现除数为任意数的除法。

本文用VHDL编写了除法运算,可实现任意八位数的除法。

除法器的设计本文所采用的除法原理是:对于八位无符号被除数A,先对A转换成高八位是0低八位是A的数C,在时钟脉冲的每个上升沿C向左移动一位,最后一位补零,同时判断C的高八位是否大于除数B,如是则C的高八位减去B,同时进行移位操作,将C的第二位置1。

否则,继续移位操作。

经过八个周期后,所得到的C的高八位为余数,第八位为商。

从图(1)可清楚地看出此除法器的工作原理。

此除法器主要包括比较器、减法器、移位器、控制器等模块。

1、比较模块设计中所用的八位比较器是由两个四位比较器级联而成的。

基于VHDL的8位除法器的实现

基于VHDL的8位除法器的实现

陈玉丹;齐京礼;陈建泗

【期刊名称】《微计算机信息》

【年(卷),期】2006(022)036

【摘要】介绍了利用VHDL实现八位除法,采用层次化设计,给出了实现除法的子模块程序.使用Altera公司的MAX+PLUSI-I10.2开发软件进行功能仿真并给出仿真波形.

【总页数】3页(P277-278,292)

【作者】陈玉丹;齐京礼;陈建泗

【作者单位】050003,石家庄市军械工程学院训练部;050003,石家庄市军械工程学院训练部;050003,石家庄市军械工程学院训练部

【正文语种】中文

【中图分类】TP312

【相关文献】

1.VHDL除法运算可综合性分析与除法器设计 [J], 曾鑫;熊波;于德海;邢永强

2.基于FPGA的浮点除法器的研究与实现 [J], 钟强;刘鹏飞;刘宝军;胡宗进;秦绪栋

3.一种基于SRT-8算法的SIMD浮点除法器的设计与实现 [J], 邓子椰;陈书明;彭元喜;雷元武

4.基于VHDL的8位除法器的实现 [J], 陈玉丹;齐京礼;陈建泗

5.可任意设定计算精度的整数除法器的VHDL设计 [J], 朱卫华;郑留平

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于VHDL的8位除法器的实现

The Design of 8 Division With VHDL

摘要:介绍了利用VHDL实现八位除法,采用层次化设计,给出了实现除法的子模块程序。

使用Altera公司的MAX+PLUSII10.2开发软件进行功能仿真并给出仿真波形。

关键词:二进制除法 VHDL MAX+PLUS2

Abstract:The design of division(8/8) by hierarchy technique is proposed. Schematic documents and submodule program with VHDL language are also given. At the end of the article, using MAX+PLUS2, the flow char is given and the simulation result is attached.

Keywords: division VHDL MAX+PLUS2

引言

除法是数值计算和数据分析中最常用的运算之一,许多高级运算如平方根、指数、三角函数等都与其有关。

在FPGA中,有加、减、乘、除的算法指令,但除法中除数必须是2的幂,因此无法实现除数为任意数的除法。

本文用VHDL编写了除法运算,可实现任意八位数的除法。

除法器的设计

本文所采用的除法原理是:

对于八位无符号被除数A,先对A转换成高八位是0低八位是A的数C,在时钟脉冲的每个上升沿C向左移动一位,最后一位补零,同时判断C的高八位是否大于除数B,如是则C的高八位减去B,同时进行移位操作,将C的第二位置1。

否则,继续移位操作。

经过八个周期后,所得到的C的高八位为余数,第八位为商。

从图(1)可清楚地看出此除法器的工作原理。

此除法器主要包括比较器、减法器、移位器、控制器等模块。

1、比较模块

设计中所用的八位比较器是由两个四位比较器级联而成的。

比较器的原理是先对高位进行比较,如果不相等,则得出结论,否则,再对下一位进行比较。

设计的四位比较器可以级联成任意位的比较器。

比较器输出信号决定减法器是否进行减法运算。

2、运算控制模块

控制模块的主要在外部运算时钟和起始信号的作用下,产生控制其他模块所需的数据调用、运算同步时钟以及乘法运算结束标志信号等。

其VHDL语言描述如下: LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ARICTL IS ——除法运算控制器

PORT(CLK,START:IN STD_LOGIC;

CLKOUT,RSTALL,ARIEND:OUT STD_LOGIC);

END ARICTL;

ARCHITECTURE BEHAV OF ARICTL IS

SIGNAL SIGN:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

RSTALL<=START;

CLKOUT<=CLK;

PROCESS(CLK,START)

BEGIN

IF START='1'THEN ——高电平清零计数器

SIGN<="0000";

ELSIF CLK'EVENT AND CLK='1'THEN

IF SIGN<8 THEN ——小于八则计数,等于八则表

明运算已经结束

SIGN<=SIGN+1;

END IF;

END IF;

END PROCESS;

PROCESS(CLK,SIGN,START)

BEGIN

IF START='0' THEN

IF SIGN<8 THEN ——除法运算正在进行

ARIEND<='0';

ELSE

ARIEND<='1'; ——如果余数小于除数则运算结束,否

则,再进行一个周期的运算

END IF;

ELSE ARIEND<='0';

END IF;

END PROCESS;

END BEHAV;

图(1)

3、减法器

减法器接收比较器所输出的信号,如果A B,则进行减法,输出A-B,否则输出A,减法器的输出到移位器中进行循环。

4、移位器

这是除法器实现中的核心部分,主要实现数据的移位和最后结果的输出,其VHDL程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY REG16B IS

PORT(CLK,CIN,LOAD,ARIEND:IN STD_LOGIC;

A:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

QL,QH:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END REG16B;

ARCHITECTURE BEHAV OF REG16B IS

SIGNAL R16S:STD_LOGIC_VECTOR(15 DOWNTO 0);

BEGIN

PROCESS(CLK,LOAD,ARIEND)

BEGIN

IF(CLK'EVENT AND CLK='1') THEN

IF(ARIEND='0')THEN

IF LOAD='1'THEN ——装载新数据

R16S(15 DOWNTO 0)<="00000000"&A(7 DOWNTO 0);

ELSIF(LOAD='0')THEN

R16S(15 DOWNTO 9)<=D(6 DOWNTO 0);

R16S(8 DOWNTO 1)<=R16S(7 DOWNTO 0); ——数据左移

R16S(0)<='0'; ——最后一位补0

IF(CIN='1')THEN ——如果比较器的输出为1,

则第二位值为1

R16S(1)<='1';

END IF;

END IF;

ELSE

IF(CIN='1')THEN ——最后余数如果大于除数则

再进行一次减法

R16S(15 DOWNTO 8)<=D(7 DOWNTO 0);

R16S(7 DOWNTO 0)<=R16S(7 DOWNTO 0)+1;——商加1

END IF;

END IF;

END IF;

END PROCESS;

QH<=R16S(15 DOWNTO 8); ——余数的输出

QL<=R16S(7 DOWNTO 0); ——商的输出

END BEHAV;

MAX+PLUS2仿真

采用ALTERA公司的MAX+PLUS2 对除法器进行仿真,图(2)为仿真波形图。

结论 由于除法运算包含了减法、试商、移位等多种操作过程,因此运算比较复杂,在现有的参考资料中,主要都基于乘法器的设计,除法器设计资料较少。

本文作者的创新点是:参考文献[3]的乘法器设计,利用VHDL 语言实现了八位数的除法器设计,该除法器采用了VHDL 的混合输入方式,将除法器分成若干个子模块后,对各个子模块分别设计,各自生成功能模块,最后用一个图形文件调用这些子模块的功能模块,完成整体设计,实现了任意八位无符 号数的除法。

参考文献:

[1]赵岩岭,刘春,曹源等.在MAX+PLUS2 平台下用VHDL 进行数字电路设计[J].微计算机信息,2004,20(4):9-11

[2] 陈耀和. VHDL 语言设计技术[M].北京:电子工业出版社,2004.

[3] 于敦山,田 泽. 32⨯8 乘法器完成32⨯32 乘加器的算法及实现[J].微电子学与计算机,2002,3:21-23.

[4]冯涛,王程.可编程逻辑器件开发技术—MAX+PLUS2入门与提高[M].北京:人民邮电出版社,2002

图(2)。