Candence课程设计——2位数值比较器

数值比较器的应用

数值比较器的应用数值比较器电路的仿真分析及应用程勇陈素陈淑平(机电信息工程系实训中心 450008)摘要:数值比较器是数字电路中经常用到的典型电路,传统的教学模式中,对数值比较器的学习及应用设计,离不开在实验室中的电路调试,学习方式较为枯燥抽象,又耗时费力,学习效果也不尽理想。

现代电子设计中,由于仿真软件的出现,变抽象的知识为直观的展示,既可以通过仿真学习数值比较器的工作原理,又可以通过仿真进行数值比较器的应用设计,学习及应用效果事半功倍。

关键词:数值比较器、仿真分析、应用在各种数字系统尤其是在数字电子计算机中,经常需要对两个二进制数进行大小判别,然后根据判别结果转向执行某种操作。

用来完成两个二进制数的大小比较的逻辑电路称为数值比较器,简称比较器。

在数字电路中,数值比较器的输入是要进行比较的两个二进制数,输出是比较的结果。

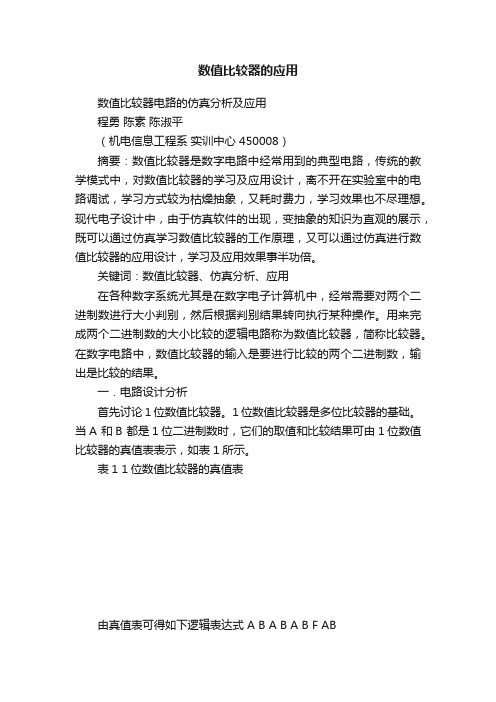

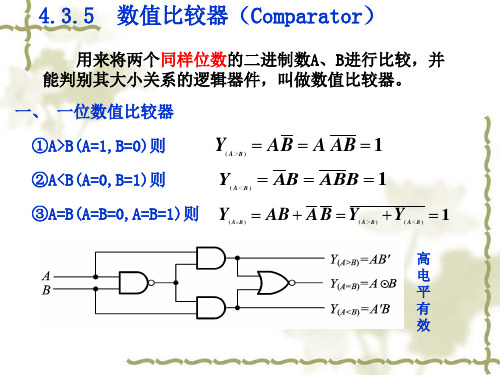

一.电路设计分析首先讨论1位数值比较器。

1位数值比较器是多位比较器的基础。

当A 和B 都是1位二进制数时,它们的取值和比较结果可由1位数值比较器的真值表表示,如表1所示。

表1 1位数值比较器的真值表由真值表可得如下逻辑表达式 A B A B A B F ABF ABF AB AB A B ><====+=⊕由逻辑表达式可以画出如图1所示的逻辑图。

图1 1位数值比较器逻辑图二.比较器电路的仿真分析(一)元件选取及电路组成打开仿真软件Multisim 10,根据图1所示的1位数值比较器逻辑图,可以在仿真软件Multisim 10中构建仿真电路,如图3所示。

1.元件选取(1)指示灯的选取1位数值比较器逻辑运算完后,输出结果处接一指示灯作为指示,灯亮表示运算结果成立,灯灭表示运算结果不成立。

单击元件栏的PlaceIndicator→PROBE,选取PROBE_RED指示灯。

为了观察清晰明白,将指示灯PROBE连击打开其图2 指示灯的Label设置设置对话框,在其Label中的标号由默认的X1改为“A等于B”、“A大于B”、“A 小于B”等。

cadence课程设计

模拟CMOS集成电路课程设计学院:机械与电子工程学院专业:电子科学与技术班级:080631姓名:刘颖华学号:08063131指导老师:蔡志民老师2011.12一、实验目的1.熟悉candence软件的使用2.了解运算放大器的基本原理3.能够对带宽、增益等参数进行调节达到指标二、设计任务及指标要求基于CMOS 0.18um工艺,设计一个运算放大器电路。

要求:(1)能够实现对两路差分输入信号进行放大,并且以单端形式输出;(2)在电路正常工作下,计算运放的功耗;(3)负载电容为15pF,负载电阻为100k情况下,运算交流小信号增益>20Db,单位增益带宽>10M Hz,相位裕度>60度;(4)完成电路前仿及版图后仿。

三、实验操作打开终端,进入文件夹目录,输入icfb &启动软件,主要中间有个空格。

启动后出现下图:(一)、运算放大器的原理图设计1、创建库和视图单元点击CIW窗口的file—new—library,由此可创建库,用来存放单元视图的文件夹,将库文件的路径设置在cadence目录下,Name栏输入库文件名last,右侧Technology File 栏中选择Attach to an existing teachfile,点击OK。

然后再点击file—new—cellview,创建一个单元视图,不同的单元视图存放不同的文件夹,Library Name 选取为last,添加库名,点击OK,此时便会弹出Schematic Edit的空白窗口。

2、运算放大器原理图图13.原理图的连接3.1 元器件参数设置PMOS P1 8u P2,P3,P4 16uNMOS N1,N2 400nR r 10kVDD vdc 1.8v负载电容:15pF负载电阻:100k差分输入端都加入900mv的直流电压,同相输入端加入1v的交流电压(在vdc的AC magnitude 栏设置)。

3.2 添加元件在Schematic Edit的窗口中,选择Add—Instance窗口,点击Browse按钮,弹出Library Browser窗口。

比较器指令操作方法

比较器指令操作方法比较器指令是计算机指令的一种类型,用于实现比较操作。

比较操作是计算机处理中常见且重要的操作之一,常用于判断条件、排序和查找等算法中。

比较器指令可用于比较两个数据的大小、相等性和关系,并根据比较结果设置相应的标志位或执行相应的分支操作。

下面是关于比较器指令的一些常见操作方法。

1. 比较数值大小:比较器指令可用于比较两个数值的大小。

常见的比较器指令包括CMP (Compare)、CMPS(Compare String)和CMPXCHG(Compare and Exchange)等。

使用这些指令时,需要将要比较的两个数值加载到寄存器中,然后执行比较操作,并根据比较结果设置相应的标志位。

2. 比较字符串:比较器指令还可用于比较两个字符串的大小。

CMPS指令可以用于比较两个字符串在内存中的内容。

它将比较源字符串和目标字符串中相同位置的字符,并根据比较结果设置标志位。

3. 比较条件跳转:比较器指令常用于实现条件跳转操作。

根据比较结果,可以使用JMP(Jump)、JE(Jump if Equal)、JNE(Jump if Not Equal)、JG(Jump if Greater)、JGE (Jump if Greater or Equal)、JL(Jump if Less)、JLE(Jump if Less or Equal)等指令实现条件跳转。

这些指令可以根据标志位的值来判断是否满足条件,并执行相应的跳转操作。

4. 比较并交换:比较器指令还可以实现比较并交换操作。

CMPXCHG指令可以用于比较寄存器中的值和内存中的值,并根据比较结果进行交换操作。

使用CMPXCHG指令时,可以设置标志位来表示比较结果,然后根据标志位的值决定是否进行交换。

5. 比较多个数值:在某些情况下,需要比较多个数值的大小。

这时可以使用多个比较器指令来实现。

比如可以使用多个CMP指令,将要比较的数值加载到不同的寄存器中,然后依次进行比较操作。

第10讲数值比较器

2.正确理解组合器件的工作原理。

3..熟练掌握常用组合逻辑器件的逻辑功能及使用方法。 4..了解组合逻辑电路中的竞争与冒险。

1. 代数识别法 一个变量以原变量和反变量出现在逻辑函数F中时,则

该变量是具有竞争条件的变量。如果消去其他变量(令其

他变量为0或1),留下具有竞争条件的变量, ①若函数出现

F A A

则产生负的尖峰脉冲的冒险现象,--“0”型冒险; ②若函数出现

F A A

则产生正的尖峰脉冲的冒险现象,--“1”型冒险。

最高位

IA <B IA=B A8 B8

最低位

IA<B IA=B

„

A4 B4

A3 B3

„

A0 B0

4.5 组合逻辑电路中的竞争与冒险

一、什么是竞争与冒险现象

1、竞争:我们把门电路两个输 入信号同时向相反的 电平跳变的现象叫做 竞争。 2、竞争—冒险:由于竞争而在 输出端可能产生不应 有的尖峰脉冲的现象 叫做竞争—冒险。

2. 引入选通脉冲法 毛刺仅发生在输入信号变化的瞬间,因此在这段时间 内先将门封锁,待电路进入稳态后,再加选通脉冲使输出 门电路开门。这样可以抑制尖峰脉冲的输出。该方法简单 易行,但选通信号的作用时间和极性等一定要合适。

4.5 组合逻辑电路中的竞争与冒险

3. 修改逻辑设计法--增加冗余项 只要在其卡诺图上两卡诺圈相切处加一个卡诺圈,即

增加了一个冗余项,就可消除逻辑冒险。

Y AB AC

Y

BC A 00 0

1

01 1

11 1 1

10

1

Y AB AC BC

第3章 小结

组合逻辑电路的特点是,电路任一时刻的输出状态只决定于 该时刻各输入状态的组合,而与电路的原状态无关。组合电路就 是由门电路组合而成,电路中没有记忆单元,没有反馈通路。 1.熟练掌握组合逻辑电路的设计和分析方法。

兰州交通大学电子专业课程设计,4位与非门的电路设计,2位数值比较器设计

兰州交通大学电子与信息工程学院课程设计报告课题一:4位与非门的电路设计课题二:2位数值比较器设计专业电子科学与技术班级电子1001班学号姓名一、Hspice简介Hspice线路模拟软件在早期是美国Meta-Software公司根据Berkeley SPICE26G .6、SPICE3及其他线路模拟软件所发展的工业级线路分析软件。

Hspice 在基本功能部分和其他SPICE软件相似,可应用于下列领域的电子电路研究,即稳态(直流分析)。

暂态(时间分析)及频率(交流分析)等领域。

由于Meta-Software公司在集成电路制程技术持续进步与元件尺寸缩小下,对于MOSFET模型的适用性与精确性的不断耕耘,以及该公司对元件与电路最优化、罗特卡罗与最坏状况分析等进阶段的应用亦有自我突破,使得Hspice逐渐脱颖而出,超过PSPICE、IsSPICE等软件,成为在集成电路设计上最普遍及最佳的晶体管层次线路模拟软件。

1997年,计算机辅助设计软件大厂Avant!公司购并了Meta-Software公司,Hspice也成为Avant!公司众多设计软件之一,并改称为STAR-Hspice。

2002年,计算机辅助设计软件大厂Synopsys公司并购了Avant!公司。

SPICE是“Simulation Program with Integrated Circuit Emphasisl”之意,原先的目的是为电子系统中集成电路的模拟与设计而发展的软件。

然而,随着电子领域应用面的扩大,Hspice也因为Synopsys公司的持续研发,而具有其特色与功能。

因此,Hspice已成功地用在直流到高频操作的电子电路设计。

二、Tanner Tools Pro简介Tanner Tools Pro是一套集成电路设计软件,包括S-Edit、T-Spice、W-Edit、L-Edit与LVS,各软件的主要功能整理如表1.1所示:编辑出电路图,再将该电路图输出成SPICE文件。

数值比较器

输 出 FA>BFA<BFA = B > < 1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 0 1 0 0 0 1 0 0 1

× × × × × × × × × × × × × × × × × × × × × × × × 1 0 0 0 1 0 0 0 1 × × 1

实验题

设计一个对两个两位无符号的二进制数进 行比较的电路;根据第一个数是否大于、 等于、小于第二个数,使相应的三个输出 端中的一个输出为“1”,要求用与门、与非 门及或非门实现。

4、设计一个对两个两位无符号的二进制数进行 比较的电路;根据第一个数是否大于、等于、 小于第二个数,使相应的三个输出端中的一个 输出为“1”,要求用与门、与非门及或非门实 现。 实验过程提示: 根据题意,第一个设为A1A0,第二个数设为 B1B0,列真值表如下

74LS85的功能表(187) 74LS85的功能表(187)

输 A3,B3 1 0 0 1 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A2,B2 × × 1 0 0 1 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 入 A1,B1 × × × × 1 0 0 1 A1 = B1 A1 = B1 A1 = B1 A1 = B1 A1 = B1 A1 = B1 A0,B0 × × × × × × 1 0 0 1 A0 = B0 A0 = B0 A0 = B0 A0 = B0 级联输入 IA>BIA<B IA > <

( A < B) = A3B3 + A3 ⊕ B3 ⋅ A2B2 + A3 ⊕ B3 ⋅ A2 ⊕ B2 ⋅ A B1 1 + A3 ⊕ B3 ⋅ A2 ⊕ B2 ⋅ A ⊕ B1 ⋅ A B0 1 0 + A3 ⊕ B3 ⋅ A2 ⊕ B2 ⋅ A ⊕ B1 ⋅ A ⊕ B0 ⋅ (a < b) 1 0

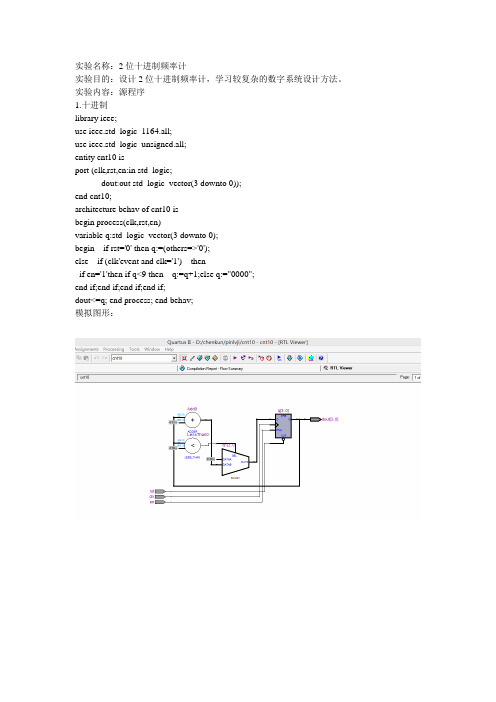

eda实验 2位十进制

实验名称:2位十进制频率计实验目的:设计2位十进制频率计,学习较复杂的数字系统设计方法。

实验内容:源程序1.十进制library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport (clk,rst,en:in std_logic;dout:out std_logic_vector(3 downto 0));end cnt10;architecture behav of cnt10 isbegin process(clk,rst,en)variable q:std_logic_vector(3 downto 0);begin if rst='0' then q:=(others=>'0');else if (clk'event and clk='1') thenif en='1'then if q<9 then q:=q+1;else q:="0000";end if;end if;end if;end if;dout<=q; end process; end behav;模拟图形:2.测控计library IEEE ;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chekong isport (CLK : in std_logic;EN,RST,Load :out std_logic );end chekong;architecture behav of chekong issignal CLK2 : std_logic;begin process(clk)begin if clk'event and clk ='1' thenCLK2 <= not clk2;end if;end process;process(clk,clk2)begin if clk='0'and clk2='0' then rst<='1';else rst<='0';end if;end process;Load <= not CLK2;EN <=CLK2;end behav;模拟图:3.寄存器library ieee;use ieee.std_logic_1164.all;entity jicunqi isport(clk : in std_logic;din: in std_logic_vector(3 downto 0);dout : out std_logic_vector(3 downto 0) );end jicunqi;architecture behav of jicunqi is beginprocess(clk,din)beginif clk'event and clk='1'then dout<=din;end if;end process;end behav;模拟图频率计框图:分析:根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的输入信号脉冲计数允许的信号;1秒计数结束后,计数值被锁入锁存器,计数器清0,为下一测频计数周期作好准备。

数字电路二位数值比较器

数字电子技术基础课程设计报告书题目:2位数值比较器姓名:班级:指导教师:设计时间:2011年3月— 7月民族大学数学与计算机学院一、背景和编写目的随着时代的进步,社会的发展,科学技术的进步,我们会在很多地方用到比较器,比如,在体育竞技场地对一些选手的成绩进行比较,选出他们中的成绩优异者;我们为了比较一下不同物品的参数,我们可以利用一些科学技术来实现这些功能,使得我们的工作效率得以提高,减少了我们认为的工作量。

本次设计的目的就是通过实践掌握数字电路的分析方法和设计方法,了解了解EDA技术和maxplus2软件并掌握VHDL硬件描述语言的设计方法和思想。

以数字电子技术基础为指导,通过学习的VHDL语言结合电子电路的设计知识理论联系实际,掌握所学的课程知识和基本单元电路的综合设计应用。

通过对比较器的设计,巩固和综合运用所学知识,提高分析、解决计算机技术实际问题的独立工作能力。

比较器有2位数比较器,4位数比较器,8位数比较器等多种。

本课程设计就是两位数比较器,可以实现2位二进制数值的比较。

二、EDA和VHDL的介绍EDA技术EDA技术的概念EDA是电子设计自动化(E1echonics Des5p AM•toM60n)的缩写。

由于它是一门刚刚发展起来的新技术,涉及面广,内容丰富,理解各异。

从EDA技术的几个主要方面的内容来看,可以理解为:EDA技术是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件的方式设计电子系统到硬件系统的一门新技术。

EDA技术的特点采用可编程器件,通过设计芯片来实现系统功能。

采用硬件描述语言作为设计输入和库(LibraLy)的引入,由设计者定义器件的内部逻辑和管脚,将原来由电路板设计完成的大部分工作故在芯片的设计中进行。

由于管脚定义的灵活性,大大减轻了电路图设计和电路板设计的工作量和难度,有效增强了设计的灵活性,提高了工作效率。

Candence课程设计——2位数值比较器

集成电路设计论文论文题目:2位数值比较器*名:***学号:**********学院:机械与电子工程学院专业:电子科学与技术班级:10206301指导教师:***一、课程实验设计目的本次课程设计把重点放在电路的设计、制作和仿真上,熟悉在UNIX系统下Candencce软件的使用,掌握电路原理图的输入和编辑及电路的仿真。

在数字系统中,特别是在计算机中都需具有运算功能,一种简单的运算就是比较两个数A和B的大小。

用以对两数A、B的大小或是否相等进行比较的逻辑电路称为数值比较器。

比较结果有A>B、A<B以及A=B三种情况。

二、实验原理1.数值比较器分类1位数值比较器:比较输入的两个1位二进制数A、B的大小多为数值比较器:比较输入的两个多位二进制数A、B 的大小,比较时需从高位到低位逐位进行比较。

2. 1位数值比较器设输入的两个二进制数位A、B,输出比较的结果为Y(A>B)、Y(A<B)、Y(A=B)三种情况。

输出时为1,否则为0。

逻辑符号示意框图:Y(A>B)Y(A=B)Y(A<B)2.1 真值表如下:输入输出A B Y(A>B)Y(A=B)Y(A<B)0 0 0 1 00 1 0 0 11 0 1 0 01 1 0 1 02.2根据真值表可写出逻辑函数表达式为2.3 逻辑图如下所示:3. 2位数值比较器3.1 定义:比较两个2 位二进制数的大小的电路3.2 基础:2位数值比较器是在一位数值比较器上,加上3个与门和2个或门构成的。

3.3 输入:两个2位二进制数A=A1 A0 、B=B1 B03.4 原理:当高位(A1、B1)不相等时,无需比较低位(A0、B0),高位比较的结果就是两个数的比较结果。

当高位相等时,两数的比较结果由低位比较的结果决定。

3.5 真值表3.6 根据真值表可写出逻辑函数表达式为FA>B = (A1>B1) + ( A1=B1)(A0>B0)FA<B = (A1<B1) + ( A1=B1)(A0<B0)0 0 10 1 01 0 0A0 > B0 A0 < B0 A0 = B0A1 = B1 A1 = B1 A1 = B1 0 1 0 × A1 < B1 01×A1 > B1 FA=B FA<B FA>B A0 B0 A1 B1 输 出输 入FA=B=(A1=B1)(A0=B0) 3.7两位数值比较器逻辑图三、实验步骤1. 画原理图及创建符号1.1 调用cadence软件进入UNIX系统后,输入icfb 命令调用cadence软件。

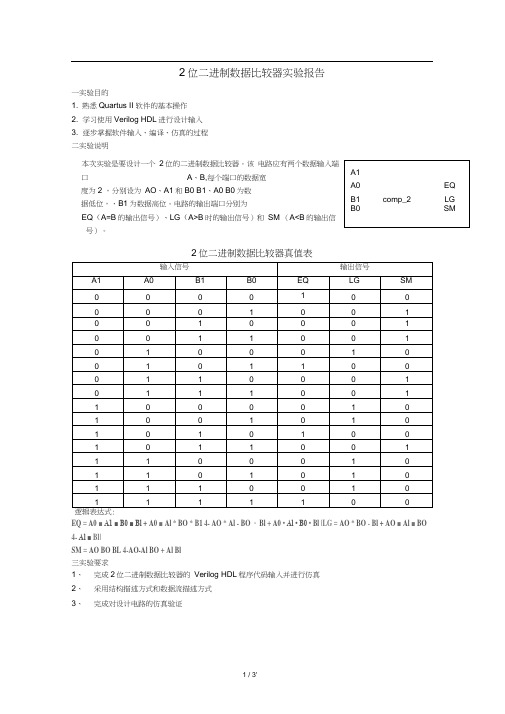

2位二进制数据比较器实验报告

2位二进制数据比较器实验报告一实验目的1. 熟悉Quartus II 软件的基本操作2. 学习使用Verilog HDL进行设计输入3. 逐步掌握软件输入、编译、仿真的过程二实验说明口A、B,每个端口的数据宽度为2 ,分别设为AO、A1和B0 B1、A0 B0为数据低位,、B1为数据高位。

电路的输出端口分别为EQ(A=B的输出信号)、LG(A>B时的输出信号)和SM (A<B的输出信号)。

2位二进制数据比较器真值表EQ = A0 ■ A1 ■ B0 ■ Bl + A0 ■ Al * BO * B1 4- AO * Al - BO ・Bl + A0 • Al • B0 • Bl |LG = AO * BO - Bl + AO ■ Al ■ BO 4- Al ■ Bl|SM = AO BO BL 4-AO-Al BO + Al Bl三实验要求1、完成2位二进制数据比较器的Verilog HDL程序代码输入并进行仿真2、采用结构描述方式和数据流描述方式3、完成对设计电路的仿真验证四、实验过程1程序代码⑴module yan gyi ng(A,B,EQ, LG,SM); in put [1:0]A,B; output EQ,LG,SM;assig n EQ=(A==B)?1'b1:1'bO;assign LG=(A>B)?1'b1:1'bO;assign SM=(A<B)?1'b1:1'bO;en dmodule⑵module yan gyi ng(A,B,EQ, LG,SM); in put [1:0]A,B; output EQ,LG,SM; reg EQ,L G,SM;always@(A or B)beginif(A==B)beginEQ<=1'b1;LG<=1'b1;SM<=1'b1;endelse if(A>B) beginEQ<=1'b1;LG<=1'b0;SM<=1'b0;endelsebeginEQ<=1'b0;LG<=1'b0;SM<=1'b1;endend en dmodule2仿真结果五、实验体会通过2位二进制数据比较器的设计,使我们更加熟悉Quartus软件进行数字系统设计的步骤,以及运用Verilog HDL进行设计输入,并掌握2位二进制数据比较器的逻辑功能和设计原理,逐步理解功能仿真和时序仿真波形。

数电13(比较器,加法器)

74HC283引脚图

S1 1 B1 2 A1 3 S0 4 A0 5 B0 6 C–1 7 GND 8

16 VCC 15 B2 14 A2 13 S2 12 A3 11 B3 10 S3 9 CO

另外,中间变量 Gi被称为产生变量 , Pi被称为传输变量。 WHY?

根据

Gi = Ai Bi Pi = Ai Bi

FA>B = (A1>B1) + ( A1=B1)(A0>B0) FA<B = (A1<B1) + ( A1=B1)(A0<B0) FA=B=(A1=B1)(A0=B0)

FA>B = (A1>B1) + ( A1=B1)(A0>B0)

FA=B=(A1=B1)(A0=B0)

FA<B = (A1<B1) + ( A1=B1)(A0<B0)

<

FA

B

>

FA=B

FA

B

<

FA

B

>

输出

用74HC85组成16位数值比较器的并联扩展方式。

B15A15~B12A12

B15 A15 B12 A12

B11A11~B8A8

B 8 A8 B 3 A3 B 2 A2 B 1 A 1 B 0 A0 IA>B C2 FA

B

<

B7A7~B4A4

B 4 A4 B 3 A3 B 2 A2 B 1 A1 B 0 A0 IA>B C1 FA

1 ≥ & 1 & & B3 & & CO (C3)

4位超前进位加法器74LS283逻辑图

A3

≥ 1

& P3 1 ≥ & 1 & & & P2 =1 1 ≥ & 1 & & P1 =1 1 ≥ & 1 & P0 =1 1 S0 S1 S2 =1 S3

EDA实验报告

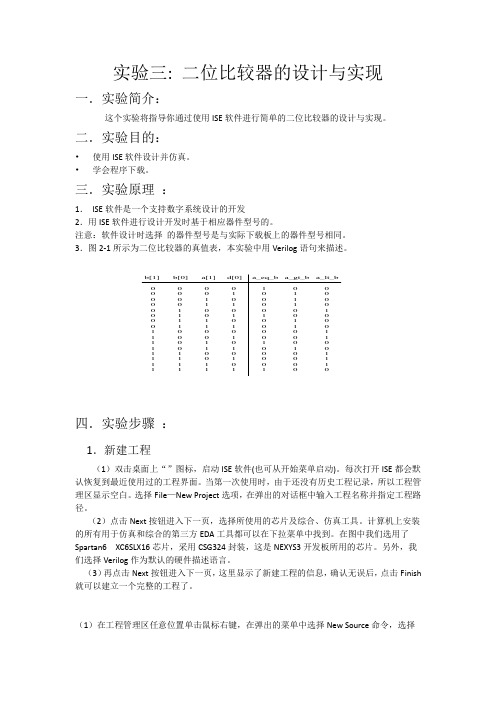

实验三: 二位比较器的设计与实现一.实验简介:这个实验将指导你通过使用ISE软件进行简单的二位比较器的设计与实现。

二.实验目的:•使用ISE软件设计并仿真。

•学会程序下载。

三.实验原理:1.ISE软件是一个支持数字系统设计的开发2.用ISE软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。

3.图2-1所示为二位比较器的真值表,本实验中用Verilog语句来描述。

b[1] b[0] a[1] d[0]0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1a_eq_b a_gt_b a_lt_b1 0 00 1 00 1 00 1 00 0 11 0 00 1 00 1 00 0 10 0 11 0 00 1 00 0 10 0 10 0 11 0 0四.实验步骤:1.新建工程(1)双击桌面上“”图标,启动ISE软件(也可从开始菜单启动)。

每次打开ISE都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。

选择File—New Project选项,在弹出的对话框中输入工程名称并指定工程路径。

(2)点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到。

在图中我们选用了Spartan6 XC6SLX16芯片,采用CSG324封装,这是NEXYS3开发板所用的芯片。

另外,我们选择Verilog作为默认的硬件描述语言。

(3)再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish 就可以建立一个完整的工程了。

(1)在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,选择Verilog Module输入,并输入Verilog文件名。

数值比较器

数值比较器

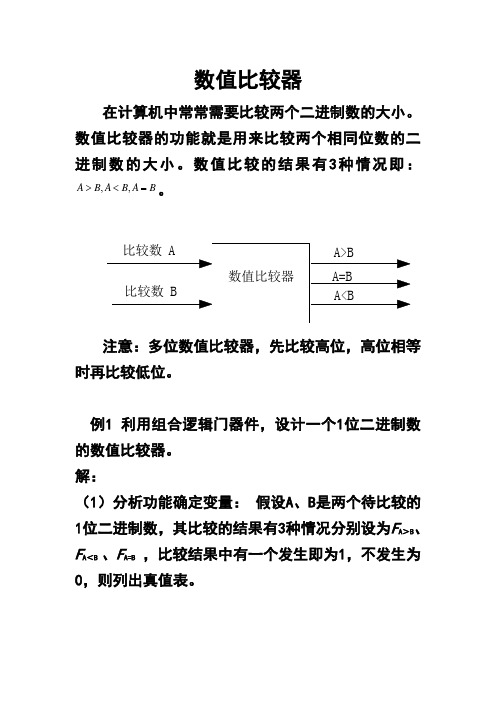

在计算机中常常需要比较两个二进制数的大小。

数值比较器的功能就是用来比较两个相同位数的二进制数的大小。

数值比较的结果有3种情况即:A=

<

B

,。

>,

B

A

A

B

注意:多位数值比较器,先比较高位,高位相等时再比较低位。

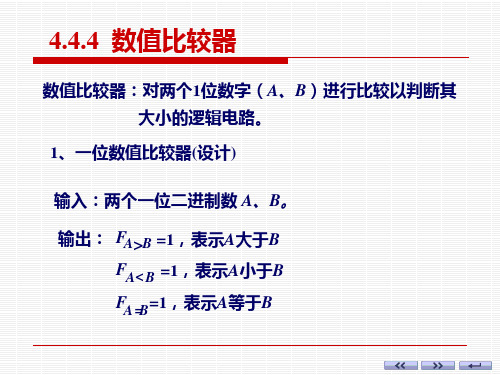

例1 利用组合逻辑门器件,设计一个1位二进制数的数值比较器。

解:

(1)分析功能确定变量:假设A、B是两个待比较的1位二进制数,其比较的结果有3种情况分别设为F A>B、F A<B 、F A=B,比较结果中有一个发生即为1,不发生为0,则列出真值表。

两一位二进制数数值比较器真值表

(2)由真值表列出逻辑表达式: B A F B A =>

F A <B B A =

B A B A AB B A F B A +=+==

(3)由逻辑表达式画出逻辑电路图。

A B A>B

F A<B F A=B

F。

13数值比较器,算术运算电路

A1 B1

A 2 B2 C1

A 3 B3

A 0 B0 IA> B IA< B

A 1 B1

A2 B2 C2

A3 B3

A 0 B0 IA> B IA< B

A1 B1

A2 B2

3

A3 B 3

低位片

F A< B F A >B

C 高位片 F A< B FA> B

I A=B F A=B

I A=B F A=B

FA <B

(2)集成数值比较器的位数扩展 (2)集成数值比较器的位数扩展

用两片 组成8位数值比较器 扩展方式)。 用两片74LS85组成 位数值比较器(串联扩展方式)。 组成 位数值比较器(串联扩展方式 输入: A=A7 A6A5A4A3 A2A1A0 输入 输出: 输出 F A> B F A< B F A= B < = B3A3~B0A0

F A=B F A< B F A> B

F A< B 7 GND 8

B0

74LS85的逻辑符号 的逻辑符号

74LS85的引脚图 的引脚图

的功能表 4位数值比较器74LS85的功能表 位数值比较器 的功能

输 A3 B3 A3 > B3 A3 < B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A3 = B3 A2 B2 × × A2 > B2 A2 < B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A2 = B2 A1 B1 × × × × A1 > B1 A1 < B1 A1 = B1 A1 = B1 A1 = B1 A1 = B1 A1 = B1 A1 = B1 A1 = B1 入 A0 B0 × × × × × × A0 > B0 A0 < B0 A0 = B0 A0 = B0 A0 = B0 A0 = B0 A0 = B0 IA>B IA<B IA=B × × × × × × × × H L × H L × × × × × × × × L H × H L × × × × × × × × L L H L L 输 出 FA>B FA<B FA=B H L H L H L H L H L L L H L H L H L H L H L H L L H L L L L L L L L L L H L L

Candence课程设计——2位数值比较器解析

集成电路设计论文论文题目:2位数值比较器姓名:陈英文学号:1020630126学院:机械与电子工程学院专业:电子科学与技术班级:10206301指导教师:蔡老师一、课程实验设计目的本次课程设计把重点放在电路的设计、制作和仿真上,熟悉在UNIX系统下Candencce软件的使用,掌握电路原理图的输入和编辑及电路的仿真。

在数字系统中,特别是在计算机中都需具有运算功能,一种简单的运算就是比较两个数A和B的大小。

用以对两数A、B的大小或是否相等进行比较的逻辑电路称为数值比较器。

比较结果有A>B、A<B以及A=B三种情况。

二、实验原理1.数值比较器分类1位数值比较器:比较输入的两个1位二进制数A、B的大小多为数值比较器:比较输入的两个多位二进制数A、B 的大小,比较时需从高位到低位逐位进行比较。

2. 1位数值比较器设输入的两个二进制数位A、B,输出比较的结果为Y(A>B)、Y(A<B)、Y(A=B)三种情况。

输出时为1,否则为0。

逻辑符号示意框图:Y(A>B)Y(A=B)Y(A<B)2.1 真值表如下:输入输出A B Y(A>B)Y(A=B)Y(A<B)0 0 0 1 00 1 0 0 11 0 1 0 01 1 0 1 02.2根据真值表可写出逻辑函数表达式为2.3 逻辑图如下所示:3. 2位数值比较器3.1 定义:比较两个2 位二进制数的大小的电路3.2 基础:2位数值比较器是在一位数值比较器上,加上3个与门和2个或门构成的。

3.3 输入:两个2位二进制数A=A1 A0 、B=B1 B03.4 原理:当高位(A1、B1)不相等时,无需比较低位(A0、B0),高位比较的结果就是两个数的比较结果。

当高位相等时,两数的比较结果由低位比较的结果决定。

3.5 真值表3.6 根据真值表可写出逻辑函数表达式为FA>B = (A1>B1) + ( A1=B1)(A0>B0)FA<B = (A1<B1) + ( A1=B1)(A0<B0)0 0 10 1 01 0 0A0 > B0 A0 < B0 A0 = B0A1 = B1 A1 = B1 A1 = B1 0 1 0 × A1 < B1 01×A1 > B1 FA=B FA<B FA>B A0 B0 A1 B1 输 出输 入FA=B=(A1=B1)(A0=B0)3.7两位数值比较器逻辑图3.7 两位数值比较器逻辑图A 1B 1A 0B 01位数值比较器1位数值比较器A 1>B 1A 1=B 1 A 1<B 1 A 0>B 0A 0=B 0 A 0<B 0G 1 G 2 &&G 3 & ≥1≥1F A >BF A=BF A <B三、实验步骤1. 画原理图及创建符号1.1 调用cadence软件进入UNIX系统后,输入icfb 命令调用cadence软件。

2位数据比较器迭代单元

2位数据比较器迭代单元什么是两位数据比较器迭代单元?两位数据比较器迭代单元是一种在数字电路中用来比较两个二进制数的元件。

它可以判断两个输入数的大小关系,并输出相应的比较结果。

这个元件通常由逻辑门电路组成,能够实现在计算机和其他数字系统中进行数字比较的功能。

在计算机和数字系统中,比较操作是一项极为重要的功能。

在任何时候,都会有需要比较两个数的大小关系的情况。

比如,在排序算法中,需要判断两个数的大小来确定它们的相对位置;在控制流程中,需要比较两个数的大小来确定程序的执行顺序;在输入输出处理中,需要比较两个数的大小来进行条件判断等等。

两位数据比较器迭代单元的设计思路来源于简单的比较器电路。

一个简单的比较器电路可以将两个输入数进行比较,并输出它们的大小关系。

然而,对于比较更多位的二进制数,我们需要一种更加高效的设计方法。

其中之一就是使用迭代单元的方式。

迭代单元的基本思想是将比较操作分解为逐位比较的子任务,并通过递归地使用相同的比较器电路来完成整个比较过程。

这种分解的方式使得我们能够通过重复使用同一种电路元件来实现较长位数的比较,从而简化设计,提高效率。

两位数据比较器迭代单元的具体实现方式可以使用多个比较器电路来完成。

比如,对于两个8位的二进制数,可以使用8个1位比较器电路来完成每一位的比较。

然后,对于每一位的比较结果,我们可以通过逻辑门电路来进一步处理,从而得到最终的比较结果。

在实际的设计过程中,我们可以使用逻辑门电路和触发器电路来实现两位数据比较器迭代单元。

逻辑门电路可以用来进行每一位的比较操作,而触发器电路可以用来存储和传输比较结果。

通过将多个逻辑门电路和触发器电路组合在一起,我们可以构建出一个完整的两位数据比较器迭代单元。

两位数据比较器迭代单元的应用非常广泛。

它可以作为计算机和其他数字系统中的基本元件,用于实现各种比较操作。

在现代计算机系统中,比较操作被广泛应用于算术运算、逻辑运算、条件判断等各个方面。

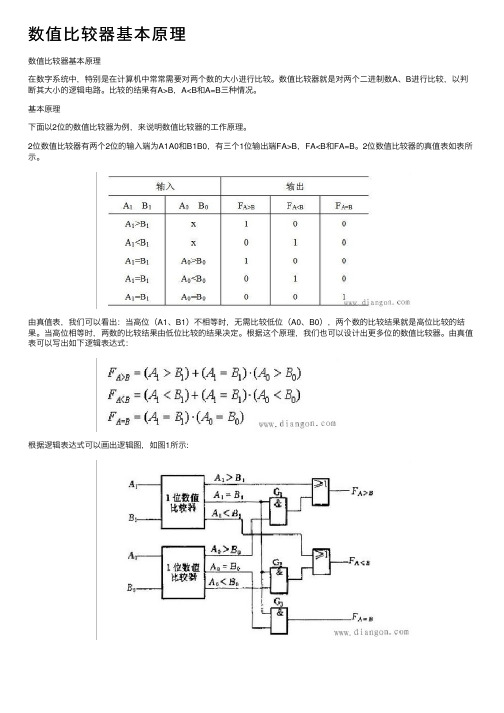

数值比较器基本原理

数值⽐较器基本原理

数值⽐较器基本原理

在数字系统中,特别是在计算机中常常需要对两个数的⼤⼩进⾏⽐较。

数值⽐较器就是对两个⼆进制数A、B进⾏⽐较,以判断其⼤⼩的逻辑电路。

⽐较的结果有A>B,A<B和A=B三种情况。

基本原理

下⾯以2位的数值⽐较器为例,来说明数值⽐较器的⼯作原理。

2位数值⽐较器有两个2位的输⼊端为A1A0和B1B0,有三个1位输出端FA>B,FA<B和FA=B。

2位数值⽐较器的真值表如表所⽰。

由真值表,我们可以看出:当⾼位(A1、B1)不相等时,⽆需⽐较低位(A0、B0),两个数的⽐较结果就是⾼位⽐较的结果。

当⾼位相等时,两数的⽐较结果由低位⽐较的结果决定。

根据这个原理,我们也可以设计出更多位的数值⽐较器。

由真值表可以写出如下逻辑表达式:

根据逻辑表达式可以画出逻辑图,如图1所⽰:。

基本门电路和数值比较器的设计

苏州大学《电子信息科学与技术》课程设计报告智力竞赛抢答答器种子和大树相遇学院————————专业————————班级XXXXXXX 学号XXXXXXXX学生姓名种子和大树相遇指导教师XXX课程成绩完成日期20xx年x月xx日课程设计任务书XXX学院XX专业课程设计成绩评定学院XXXXXXXXXXX 专业XX班级 XX学号 XX学生姓名 XXX 指导教师 XXX课程成绩完成日期指导教师对学生在课程设计中的评价指导教师对课程设计的评定意见基本门电路和数值比较器的设计学生姓名:XXX 指导老师:XXX摘要系统采用EDA技术设计基本门电路和数值比较器中的两个部分,基本门电路模块中包含与门、或门、异或门等6个基本电路。

数值比较器模块用来实现两个数值比较,结果用特定的二进制编码来表示。

系统采用硬件描述语言VHDL把电路按模块化方式进行设计,然后进行编程、时序仿真等。

各个模块的结构简单,使用方便,具有一定的应用价值。

关键字门电路;EDA;VHDL;数值比较目录1 引言 (1)1.1 设计的目的 (1)1.2 设计的基本内容 (1)2 EDA、VHDL简介 (1)2.1 EDA技术 (1)2.2 硬件描述语言——VHDL (2)3 设计规划过程 (3)3.1基本门电路工作原理 (4)3.2数值比较器的工作原理 (4)3.3课程设计中各个模块的设计 (5)结束语 (8)参考文献 (10)附录 (11)1 引言20世纪60年代初,美国德克萨斯仪器公司TI(Texas Instruments)将各种基本逻辑电路以及连线制作在一片体积很小的硅片上,经过封装后提供给用户使用,这就是集成电路。

从先前的采用半导体技术实现的计算机到现在广泛应用的采用高集成度芯片实现的计算机。

基本门电路和数值比较器作为计算机原理中的一个元件,因而成为深入研究和了解基本逻辑电路的基石。

本设计主要介绍的是一个基于超高速硬件描述语言VHDL 对基本门电路和数值比较器电路进行编程实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路设计论文

论文题目:2位数值比较器

*名:***

学号:**********

学院:机械与电子工程学院专业:电子科学与技术

班级:10206301

指导教师:***

一、课程实验设计目的

本次课程设计把重点放在电路的设计、制作和仿真上,熟悉在UNIX系统下Candencce软件的使用,掌握电路原理图的输入和编辑及电路的仿真。

在数字系统中,特别是在计算机中都需具有运算功能,一种简单的运算就是比较两个数A和B的大小。

用以对两数A、B的大小或是否相等进行比较的逻辑电路称为数值比较器。

比较结果有A>B、A<B以及A=B三种情况。

二、实验原理

1.数值比较器分类

1位数值比较器:比较输入的两个1位二进制数A、B的大小

多为数值比较器:比较输入的两个多位二进制数A、B 的大小,比较时需从高位到低位逐位进行比较。

2. 1位数值比较器

设输入的两个二进制数位A、B,输出比较的结果为Y(A>B)、Y(A<B)、Y(A=B)三种情况。

输出时为1,否则为0。

逻辑符号示意框图:

Y(A>B)

Y(A=B)

Y(A<B)

2.1 真值表如下:

输入输出

A B Y(A>B)Y(A=B)Y(A<B)

0 0 0 1 0

0 1 0 0 1

1 0 1 0 0

1 1 0 1 0

2.2根据真值表可写出逻辑函数表达式为

2.3 逻辑图如下所示:

3. 2位数值比较器

3.1 定义:比较两个2 位二进制数的大小的电路

3.2 基础:2位数值比较器是在一位数值比较器上,加上3个与门和2个或门构成的。

3.3 输入:两个2位二进制数A=A1 A0 、B=B1 B0

3.4 原理:

当高位(A1、B1)不相等时,无需比较低位(A0、B0),高位比较的结果就是两个数的比较结果。

当高位相等时,两数的比较结果由低位比较的结果决定。

3.5 真值表

3.6 根据真值表可写出逻辑函数表达式为

FA>B = (A1>B1) + ( A1=B1)(A0>B0)

FA<B = (A1<B1) + ( A1=B1)(A0<B0)

0 0 1

0 1 0

1 0 0

A0 > B0 A0 < B0 A0 = B0

A1 = B1 A1 = B1 A1 = B1 0 1 0 × A1 < B1 0

1

×

A1 > B1 FA=B FA<B FA>B A0 B0 A1 B1 输 出

输 入

FA=B=(A1=B1)(A0=B0) 3.7两位数值比较器逻辑图

三、实验步骤

1. 画原理图及创建符号

1.1 调用cadence软件

进入UNIX系统后,输入icfb 命令调用cadence软件。

此时会弹出CIW 窗口(命令解释窗口),如下图所示:

1.2 创建模型库与单元视图

进入cadence后,点击CIW 窗口的file—》new—》library,将库文件的路径设置在cadence目录下,Name栏输入库文件名为wen。

点击file—》new—》cellview,生成单元视图Libray Name选取为wen,Cell Name分别命名为text1、text2、text3、text4、text5、text6、text7,对应的原理图为非门电路、与门电路、或门电路、或非门电路、1位数值比较器电路、2位数值比较器、总电路。

设置view name为shcemetic,设置tool 为composer schematic。

1.3 画原理图

1.3.1 非门电路图

1.3.2 与门电路图

1.3.3或门电路图

1.3.4 或非门电路图

1.3.5 1位数值比较器电路图

1.3.6 2位数值比较器电路图

1.3.7 总封装电路图

1.3.8 画原理图的几个常用的快捷键:

①i ——Add Instance

②w ——Add Wire

③p ——Add Pin

④q ——Edit Properties

⑤ f ——Fit Window

⑥ c ——Copy

⑦u ——Undo(在CIW 窗口点击option—>User Preferences —>Undo Limit 可修改撤消次

数。

)

⑧m ——Stretch 的快捷键

⑨del ——Delete 的快捷键

1.4 创建符号(封装)

在需要建立Symbol 的原理图中,点击Design—》Create Cellview —》From Cellview弹出Cell From Cellview窗口,如下图所示:

图中Library Name和Cell Name会自动填写为我们所要创建符号的原理图名。

点击OK,弹出Symbol Generation Option 窗口,如下图所示:

电路中各个管脚会分别出现在对话框Pin Specifications 所规定的Left Pins、RightPins、Top Pins 和Bottom Pins 中。

设置完成后单击OK,系统会生成并显示一个长方形的Symbol 符号,通过修改,我们可以

创建非门、与门、或门、或非门、1位数值比较器、2位数值比较器的符号。

1.5 前仿

1.5.1 设置分析环境

在原理图编辑窗口下,仿真之前必须先对分析环境进行设置。

点击Tools——AnalogEnvironment,首先我们要设置模型库文件的路径,点击Setup—>Model librarie将库路径设为/mnt/hgfs/D/lib/csmoc/csmcof/models/s05mixddst02v23.scs,将Section 设为tt,如下图所示:

1.5.2 外加激励

在4个输入端外加4个5v的激励,并都接地

1.5.3 选择分析类型

点击Analyses—>Choose,可以选择分析类型,这里我们选择Tran(暂态)分析,参数设置如下图所示,我们同样也可以选择dc(直流)、ac(交流)、noise(噪声)等作为我们的分析对象。

1.5.4 选择输出信号保存

点击Outputs—》Save All,可选择输出,输出信号选择allpub,器件电流选择all。

这样我们可以有选择性的得到我们需要最后看到的信号。

1.5.5 产生列表

点击Simulation—》Netlist and Run 可进行仿真,点击后会

弹出Welcome to Spectre窗口,点击OK就开始仿真了,如果提示有错误,就需要修改原理图。

通常这样我们无法看到网络表,此时我们可以点击Netlist—>create产生网络表,我们在这里可以看到各个元器件及参数。

注意:每次修改原理图都必须检查并保存、产生Netlist,然后再运行。

1.5.6 查看结果

点击Results—》Direct Plot—》Transient Signal 可查看想看的信号,如点击输入端和输出端,再按下Esc,我们就可看到输入与输出的信号了。

如下图所示:

四、实验小结

在实验室呆了1天半左右的时间,由于平时Candence实验没怎么认真做,所以开始那一天,做的很辛苦,很多东西都不懂,上午基本就学会了建工程和文件,然后画原理图,画的原理图也经常编译时出错,原理图画了又画,当时就觉得很烦;下午,开始仿真,由于对仿真也不熟悉,就不断的问同学、老师,但效果还是不怎么好,自己理解到才能真正做好;晚上继续做,发现了下午没仿真出来的原因,原来是或门电路图画错,于是重新修改,时间关系,没做完;第二天上午继续前一天的图,终于成功仿真出波形。

通过这次实验,让我认识到坚持的重要性,第一天看着别人都做出了几个仿真图,而我的还没出结果时,心里很急,一天都没出结果,真有想放弃的冲动,幸好坚持下来了,第二天轻松出结果。

这次实验让我学习并掌握国际流行的EDA 仿真软件Cadence的使用方法,完成了2位数值比较器集成电路的设计,并进行了前仿,得出了正确的仿真波形。