VHDL语言设计七段示波译码器

EDA实验三-七段译码显示

河北科技大学实验报告2013级电信专业132 班学号130701213 2016年6月7日姓名田继辉同组人指导教师于国庆实验名称实验三七段译码显示成绩实验类型设计型批阅教师一、实验目的(1)掌握VHDL语言的行为描述设计时序电路。

(2)掌握FPGA动态扫描显示电路设计方法。

(3)熟悉进程(process)和顺序语句的应用。

二、实验原理:用4个开关作为加法器的一组输入变量,共4组输入变量;对每组变量进行译码,变换成0~F标准段码,段码中“1”表示段亮,“0”表示段灭。

一位时钟输入作为扫描显示位扫时钟,四位位扫输出,依次输出高电平。

8位段码输出,根据位选状态选择输出四组输入变量的相应译码结果。

四组输入采用试验箱K1~K16,时钟输入选择试验箱CP1或CP2;试验箱LED显示选择动态显示方式(CZ1开关ST选择OFF),段码、位码分别扫描输出,某个管的位码有效期间,将其对应的段码输出,各位码依次有效,实现循环扫描显示,将输入的16位二进制数,每4位一组,分别显示到4个数码管上(0~F)。

三、实验内容及步骤1.打开MUXPLUS II VHDL编辑器,完成七段译码显示的设计。

包括VHDL程序输入、编译、综合。

实验程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY alpher ISPORT(1 / 6clk : IN STD_LOGIC;choice : OUT STD_LOGIC_VECTOR(7 downto 0);data : OUT STD_LOGIC_VECTOR(7 downto 0)); END alpher;ARCHITECTURE a OF alpher ISSIGNAL count : STD_LOGIC_VECTOR(3 downto 0); SIGNAL temp : STD_LOGIC_VECTOR(3 downto 0);BEGINchoice<="10000000";clk1_label:PROCESS (clk)BEGINIF clk'event and clk='1' THENcount<=count+1;END IF;END PROCESS clk1_label;WITH count selectdata <= "11111100" WHEN "0000","01100000" WHEN "0001","11011010" WHEN "0010","11110010" WHEN "0011","01100110" WHEN "0100","10110110" WHEN "0101","10111110" WHEN "0110","11100000" WHEN "0111","11111110" WHEN "1000","11110110" WHEN "1001","11101110" WHEN "1010","00111110" WHEN "1011","10011100" WHEN "1100","01111010" WHEN "1101","10011110" WHEN "1110","10001110" WHEN OTHERS;END a;2、建立仿真波形文件,使用MAXPLUS II Simulator功能进行功能仿真。

7段数码显示译码器设计

7段数码显示译码器设计

设计一个7段数码显示译码器,主要功能是将4位二进制编码转换为用7段LED显示的十进制数。

具体设计过程如下:

1.确定电路的输入和输出:输入为4位二进制编码,输出为7段LED 显示的十进制数。

2.确定译码器类型:由于需要将二进制编码转换为十进制数,可以选用BCD-7段译码器或者十进制译码器作为基本器件。

3.确定电路原理图:根据所选的译码器类型,画出电路原理图。

在原理图中,需要连接一个4位二进制编码器到译码器的输入端,同时将译码器的输出连接到7段LED显示器的相应段。

4.电路连接和布线:将译码器和7段LED显示器连接到电源和接地线上,并将4位二进制编码器的输出连接到译码器的输入端。

5.电源和接地线:将电源和接地线正确连接到电路中,确保电路能够正确工作。

6.电路调试和测试:通过输入不同的4位二进制编码来测试电路的译码功能,确保译码器能够正确地将二进制编码转换为十进制数,并且在7段LED显示器上显示。

7.电路性能优化和改进:根据测试结果,对电路进行进一步的优化和改进。

可以考虑是否需要增加输入的保护电路,或者改进电源和接地线的布线方式来提高电路的性能。

总结:

以上是设计一个7段数码显示译码器的基本步骤,通过选择合适的译码器类型,正确连接电路和调试测试,可以实现4位二进制编码到十进制数的转换,并在7段LED显示器上显示。

在设计过程中,需要注意电路连接的正确性和稳定性,以及对电路的性能进行优化和改进。

七段显示译码器设计

电子科技大学光电信息学院课程设计论文课程名称《数字逻辑设计及应用》题目名称七段显示译码器设计学号2010072010024姓名王殷洁指导老师陈德军起止时间2012/5/20-2012/6/232012年6 月 20日电子科技大学光电信息学院课程设计任务书一、课程名称《数字逻辑设计及应用》二、课程设计题目七段显示译码器器设计三、课程设计目的1、熟练数字逻辑设计的基本方法。

应用课程所学的基本逻辑设计思想完成简单的逻辑设计过程;2、提高学生利用软件完善设计的基本能力。

要求学生自学HDL语言或者其他仿真工具对所完成的设计进行验证和仿真。

3、提高学生对所设计内容的文本描述能力。

要求学生对设计思想、设计过程以及结果进行描述。

四、课程设计要求1、要求有一定的组合逻辑和时序逻辑的设计能力;2、要求对未用编码1010~1111进行讨论;五、课程设计任务和内容设计一个2421BCD计数器。

基本要求如下:无启动风险。

该课程设计的应包括如下的内容:a)设计过程的文字描述。

设计过程应该包括设计思路的简单描述、系统子模块的定义以及功能描述、逻辑变量的定义、逻辑状态的定义等。

必要的真值表、功能表和状态表等;该部分要求提供word文本。

b)电路原理图或者verilog HDL语言描述。

该部分要求提供所选择仿真软件的编译文件。

c)仿真结果。

该部分要求提供所选择仿真软件的编译结果或者word文档。

d)团队分工情况说明,团队课包括1~3人。

请描述个人在设计中所承担的任务,以word文档提交。

六、参考文献1、《数字设计——原理及实践》John F. Wakerly编机械工业出版社 2003年8月第四版2、《数字电子技术基础》阎石主编高等教育出版社第五版指导教师签名:陈德军日期:2012年5月12日七段显示译码器设计摘要:本课程设计的七段译码器主要以BCD译码器或LED显示器为主要部件,应用集成门电路的一个具有译码和显示的装置。

其中七段显示器就是使用发光二极管或液晶显示器元件,在手表、计算器和仪器中显示十进制数码,通过点亮7个线段的子集就可以显示数码。

实验一七段数码显示译码器设计

《EDA技术实用教程》实验报告实验一七段数码显示译码器班级学号姓名日期2010.9.29一、实验目的1、了解显示译码器的结构和理解其工作原理。

2、学习7段数码显示译码器设计。

3、学习VHDL的多层次设计方法。

二、实验仪器PC机,Quartus II 8.0设计平台。

EDA实验开发系统。

三、实验原理7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

但为了简化过程,首先完成7段BCD码译码器的设计。

如图3-1作为7段BCD码译码器,输出信号LED7S的7位分别接如图3-1数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

四、实验步骤及结果1破解软件2、新建工程前两个实验到这里直接点击“Finish”完成一个工程的建立,现在点击“Next”来调用芯片。

点击“Next”选择芯片类型,这次选择“ACEX1K”点击“Finish”完成工程建立。

这里在工程的建立中同时确定了要用到的芯片型号及一些参数。

3、程序输入及编译新建文件并输入程序并进行编译。

LIBRARY IEEE;USE IEEE.std_logic_1164.ALL;ENTITY ex4 ISPORT (A : IN STD_LOGIC_VECTOR(3 DOWNTO 0); -- IO43..IO40 (P121, P120, P119, P118)LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0) -- IO14..IO08 (P63, P62, P60, P59, P51, P49, P48));END ex4;ARCHITECTURE behv OF ex4 ISBEGINPROCESS(A)BEGINCASE A(3 DOWNTO 0) ISWHEN "0000" => LED7S <= "0111111"; WHEN "0001" => LED7S <= "0000110"; WHEN "0010" => LED7S <= "1011011"; WHEN "0011" => LED7S <= "1001111"; WHEN "0100" => LED7S <= "1100110"; WHEN "0101" => LED7S <= "1101101"; WHEN "0110" => LED7S <= "1111101"; WHEN "0111" => LED7S <= "0000111"; WHEN "1000" => LED7S <= "1111111"; WHEN "1001" => LED7S <= "1101111"; WHEN "1010" => LED7S <= "1110111"; WHEN "1011" => LED7S <= "1111100"; WHEN "1100" => LED7S <= "0111001"; WHEN "1101" => LED7S <= "1011110"; WHEN "1110" => LED7S <= "1111001"; WHEN "1111" => LED7S <= "1110001";WHEN OTHERS => NULL;END CASE;END PROCESS;END behv;选择Processing菜单中的Start Compilation项,启动全程编译。

实验二 7段数码显示译码器

实验二7段数码显示译码器【实验目的】1.设计七段显示译码器,并在实验板上验证2.学习Verilog HDL文本文件进行逻辑设计输入;3.学习设计仿真工具的使用方法;【实验内容】1. 实现BCD/七段显示译码器的“Verilog ”语言设计。

说明:7段显示译码器的输入为:IN0…IN3共5根,7段译码器的逻辑表同学自行设计,要求实现功能为:输入“0…15 ”(二进制),输出“0…9…F ”(显示数码),输出结果应在数码管(共阴)上显示出来。

2. 使用工具为译码器建立一个元件符号3. 设计仿真文件,进行验证。

4.编程下载并在实验箱上进行验证。

【实验原理】7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的。

为了满足16进制数的译码显示,利用Verilog译码程序在FPGA/CPLD中来实现。

首先要设计一段程序,该程序可用case语句表述方法,根据真值表写出程序。

设输入的4位码为IN[3:0],输出控制7段共阴数码管的七位数据为led7[6:0]。

首先完成7段BCD码译码器的设计。

本实验中的7段译码管输出信号led7的7位分别接数码管的7个段,高位在左,低位在右。

如当LED7输出为“1101111”时,数码管的7个段:a,b,c,d,e,f,g分别接1、1、1、1、0、1、1;接有高电平的段发亮,于是数码管显示“9”。

【共阴数码管】【程序源代码】(加注释)module LED7(IN,led7);input [3:0] IN; //定义LED7的4位数据输入端口output [6:0] led7;// 定义LED7的7位数据输出端口reg[6:0] led7; //定义一个模块内部的暂存变量led7[6:0]always @(IN) begin //主块开始case(IN)4'b0000: led7<=7'b0111111;//输入为“0”时,数码管显示“0”4'b0001: led7<=7'b0000110;//以下同理4'b0010: led7<=7'b1011011;4'b0011: led7<=7'b1001111;4'b0100: led7<=7'b1100110;4'b0101: led7<=7'b1101101;4'b0110: led7<=7'b1111101;4'b0111: led7<=7'b0000111;4'b1000: led7<=7'b1111111;4'b1001: led7<=7'b1101111;default: led7<=0; //输入不在“0—9”时,数码管显示“0”endcaseend //主块结束endmodule【RLT电路】【仿真和测试结果】功能分析:在仿真结果中,输入IN采用十进制形式,输出led7采用二进制形式。

七段译码器设计(5)未完成

EDA技术与VHDL实验报告一实验题目:七段数码显示译码器二实验目的:学习7段数码显示译码器设计;学习VHDL的CASE语句应用及多层次设计方法。

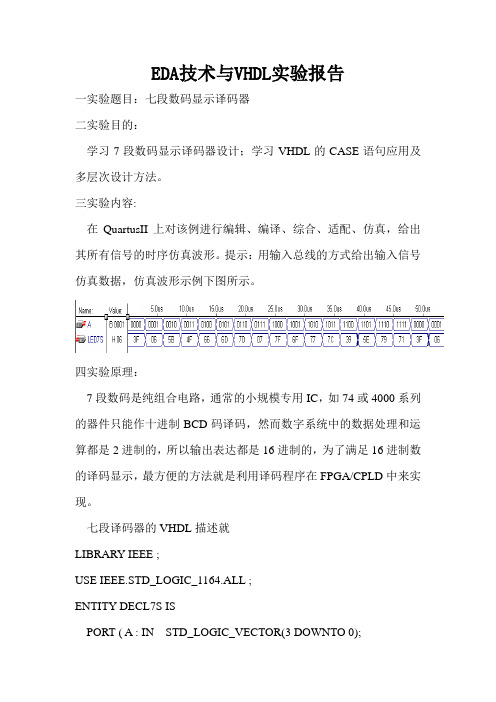

三实验内容:在QuartusII上对该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

提示:用输入总线的方式给出输入信号仿真数据,仿真波形示例下图所示。

四实验原理:7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

七段译码器的VHDL描述就LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DECL7S ISPORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ; END ;ARCHITECTURE one OF DECL7S ISBEGINPROCESS( A )BEGINCASE A ISWHEN "0000" => LED7S<= "0111111" ;WHEN "0001" => LED7S<= "0000110" ;WHEN "0010" => LED7S<= "1011011" ;WHEN "0011" => LED7S<= "1001111" ;WHEN "0100" => LED7S<= "1100110" ;WHEN "0101" => LED7S<= "1101101" ;WHEN "0110" => LED7S<= "1111101" ;WHEN "0111" => LED7S<= "0000111" ;WHEN "1000" => LED7S<= "1111111" ;WHEN "1001" => LED7S<= "1101111" ;WHEN "1010" => LED7S<= "1110111" ;WHEN "1011" => LED7S<= "1111100" ;WHEN "1100" => LED7S<= "0111001" ;WHEN "1101" => LED7S<= "1011110" ;WHEN "1110" => LED7S<= "1111001" ;WHEN "1111" => LED7S<= "1110001" ;WHEN OTHERS => NULL ;END CASE ;END PROCESS ;END ;引脚分配:五实验过程:引脚设定六实验结果:输出波形图。

eda实验7段数码显示译码器

《EDA技术实用教程》实验报告实验一、7段数码显示译码器一、实验目的(1) 熟悉QuartusⅡ软件应用环境,了解实验流程。

(2) 编写简单的VHDL代码,并在QuartusⅡ中进行调试和验证,并在EDA6000中下载代码和验证。

(3) 学习7段数码显示译码器的设计。

二、实验原理7段数码管是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能做十进制BCD译码,然而数字系统中的处理和运算都是二进制,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

本实验中的7段译码管输出信号LED7S 的7位分别接数码管的7个段,高位在左,低位在右。

三、实验仪器南京伟福实业有限公司生产EDA2000/6000试验仪EDA6000相关软件和试验仪连接线和ByteBlaster[MV]连接线四、实验步骤与结果1、创建文件夹并编辑设计文件在D盘中创建文件夹取名ex4。

打开QuartusⅡ,选择菜单File中New。

在New窗口中的Device Design File中选择语言类型VHDL File。

在该编译窗口中键入本实验程序。

将其保存在D盘的ex4文件夹里。

文件名与实体名一致,类型为vhd。

程序如下LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DecL7S ISPORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ;LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ;END ;ARCHITECTURE one OF DecL7S ISBEGINPROCESS( A )BEGINCASE A(3 DOWNTO 0) ISWHEN "0000" => LED7S <= "0111111" ; -- X"3F"'0WHEN "0001" => LED7S <= "0000110" ; -- X"06"'1WHEN "0010" => LED7S <= "1011011" ; -- X"5B"'2WHEN "0011" => LED7S <= "1001111" ; -- X"4F"'3WHEN "0100" => LED7S <= "1100110" ; -- X"66"'4WHEN "0101" => LED7S <= "1101101" ; -- X"6D"'5WHEN "0110" => LED7S <= "1111101" ; -- X"7D"'6WHEN "0111" => LED7S <= "0000111" ; -- X"07"'7WHEN "1000" => LED7S <= "1111111" ; -- X"7F"'8WHEN "1001" => LED7S <= "1101111" ; -- X"6F"'9WHEN OTHERS => NULL ;END CASE ;END PROCESS ;END ;2、创建工程(1)选择菜单File中New Project Wizard命令,在如下“工程设置”对话框中单击右侧“…”按钮,找到文件夹D:\ex4,选中已存盘的ex4.vhd的文件。

EDA实验二_VHDL七段数码管显示译码

EDA实验二七段数码管显示译码的设计一、实验目的1、掌握七段数码管译码器的工作原理;2、学会运用波形仿真测试检验程序的正确性;3、学会运用波形仿真测试检验程序的正确性。

二、实验设备ZYE1502C型实验箱三、内容要求1、用拨位开关输入8421BCD码,七段数码管显示“0-F”16个16进制的数字。

2、观察字符亮度和显示刷新的效果:(1)在8个七段数码管上同时显示某一数字;(2)在8个七段数码管上动态显示某一数字。

3、扩展内容:(1)动态显示时,能即时改变显示的顺序;(2)动态显示时,实现显示数字从0~F的循环显示。

四、实验步骤1、输入:设计部分采用VHDL语言完成;2、编译;3、仿真;4、下载;5、连线。

(1)四个拨位开关(在P1、P2处选择)连接D3、D2、D1、D0信号所对应的管脚。

时钟CLK所对应的管脚同实验箱上的时钟源相连。

(2)扫描片选信号DIG(0 TO 3)的管脚同七段数码管(共阴)相连;(3)七段数码管驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入PCLK处的连接线孔A,B,C,D,E,F,G相连。

五、实验报告1、论述实验过程和步骤;2、填写正确的实验结果。

(1)通过两种显示效果分析:字符显示亮度同扫描频率的关系,且让人眼感觉不出光闪烁现象的最低扫描频率是多少?答:扫描频率越高,显示亮度越低。

人眼看是否闪烁与所用的时钟和分频方式有关,在频率稳定和分频均匀的情况下,最低扫描频率为256Hz,若分频不均匀或频率不稳定,则需更高频率。

(2)字形编码的种类,即一个7段数码管可产生多少种字符,产生所有字符需要多少根被译码信号线?答:一个7段数码管可产生2^7=128种字符,产生所有字符至少需要7根被译码信号线。

但假如只编译0-F,16个字符,则至少只需要4根被译码信号线。

六、实验小结。

答:1、不同控制端需要预先分配控制优先级,否则编写的时候会出现很多问题。

优先级分为普通和特殊,一般错误情况可以跨越权限显示出来。

【实验二】7段数码显示译码器设计

实验内容

WHEN "1101" => LED7S<="1011110"; WHEN "1110" => LED7S<="1111001"; WHEN "1111" => LED7S<="1110001"; WHEN OTHERS => NULL; END CASE; END PROCESS; END ONE;

实验原理 PROCESS语句的执行由敏感信号的变化启动,引 导语句被执行一遍,然后返回进程的起始端,进 入等待状态,直到下一次任意敏感信号的变化。

实验原理 3. 7段数码显示译码器设计 7段数码显示器是纯组合电路。为了满足十六进制 数的译码显示,最方便的方法就是利用译码程序 在FPGA/CPLD中实现。7段译码器的VHDL的程 序,A[3..0]是二进制码输入端,LED7S是7段输 出信号。

实验内容

PROCESS(A) BEGIN CASE A IS WHEN "0000" => LED7S<="0111111"; WHEN "0001" => LED7S<="0000110"; WHEN "0010" => LED7S<="1011011"; WHEN "0011" => LED7S<="1001111"; WHEN "0100" => LED7S<="1100110";

实验三七段数码显示译码器设计

实验三七段数码显示译码器设计一、实验目的1、了解显示译码器的结构和理解其工作原理。

2、学习7段数码显示译码器设计。

3、学习VHDL的多层次设计方法。

二、实验仪器PC机,操作系统为Windows2000/XP,本课程所用系统均为WindowsXP(下同),Quartus II 5.1设计平台。

GW48系列SOPC/EDA实验开发系统。

三、实验原理1、七段字符显示器为了能以十进制数码直观地显示数字系统的运行数据,符显示器有七段可发光的线段拼合而成。

常见的七段字符显示器有半导体数码管和液晶显示器两种。

图3-1是半导体数码管BS201A外形图,这种数码管的每个线段都是一个发光二极管(Light Emitting Diode,简称LED),因而把它叫做LED数码管或LED七段显示器。

图3-1 发光二极管使用的材料与普通的硅二极管和锗二极管不同,有磷砷化镓,磷化镓,砷化镓等几种,而且半导体中的杂质浓度高。

当外加正电压时,大量的电子和空穴在扩散过程中复合,其中一部分电子从导带跃迁到价带,把多余的能量以光的形式释放出来,便发出一定波长的可见光。

磷砷化镓发光二极管发出光线的波长与磷和砷的比例有关,含磷的比例越高波长越短,同时效率也随之降低。

目前生产的磷砷化镓发光二极管发出的光线波长在6500ā左右,呈橙红色。

另外一种常用的七段字符显示器是液晶显示器(Liquid Crystal Display,简称LCD)。

液晶是一种即具有液体的流动性有具有光学特性的有机化合物。

它的透明度和呈现的颜色手外加电场的影响,利用这一特点边可作成字符显示器。

在没有外加电场的情况下,液晶分子按一定取向整齐地排列着,这时液晶为透明状态,射入的光线大部分由反射电极反射回来,显示器呈白色。

在电极上加上电压后,液晶分子因电离而产生正离子,这些正离子在电场的作用下运动并碰撞其他液晶分子,破坏了液晶分子的整齐排列,使液晶呈现混浊状态。

这时射入的光线散射后仅有善良反射回来,故显示器呈暗灰色。

7段数码显示译码器的VHDL设计

xxxxxx大学实验报告课程名称:EDA技术试验实验名称:7段数码显示译码器的VHDL设计学号:xxxxxxxx 姓名:xxx指导教师评定:__________________ 签名:____________________________一、实验目的1、学习7段数码显示译码器的设计;2、学习多层次设计方法。

3、了解使用VHDL表达和设计电路的方法和学习多层次设计方法.二、实验仪器:计算机一台,Quartus 2软件三、实验步骤:1、新建一个文件夹,打开Quartus 2软件,选择FILE->NEW菜单,在弹出的NEW对话框中选择DEVICE DESGIN FILE页的原理图文件编辑器输入项VHDL FILE,按确定键打开VHDL编辑器窗口;2、在VHDL编辑器窗口输入2选1多路选择器的VHDL描述;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DecL7S ISPORT(A :IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );END;ARCHITECTURE one OF DecL7S ISBEGINPROCESS(A)BEGINCASE A(3 DOWNTO 0) ISWHEN “0000”=>LED7S<=”0111111”;WHEN “0001”=>LED7S<=”0000110”;WHEN “0010”=>LED7S<=”1011011”;WHEN “0011”=>LED7S<=”1001111”;WHEN “0100”=>LED7S<=”1100110”;WHEN “0101”=>LED7S<=”1101101”;WHEN “0110”=>LED7S<=”1111101”;WHEN “0111”=>LED7S<=”0000111”;WHEN “1000”=>LED7S<=”1111111”;WHEN “1001”=>LED7S<=”1101111”;WHEN “1010”=>LED7S<=”1110111”;WHEN “1011”=>LED7S<=”1111100”;WHEN “1100”=>LED7S<=”0111001”;WHEN “1101”=>LED7S<=”1011110”;WHEN “1110”=>LED7S<=”1111001”;WHEN “1111”=>LED7S<=”1110001”;WHEN OTHERS=> NULL;END CASE;END PROCESS;END;3、打开波形编辑器,分别运行2选1多路选择器,观察他们的输出波形:4、调出VHDL描述产生的2选1多路选择器的原理图.点击TOOLS->NELIST VIEWERS->RTL VIEWERS,即调出VHDL描述产生的2选1多路选择器的RTL电路图,如下所示:四、实验小结通过本次实验,基本上掌握了7段数码显示译码器的设计,了解了使用VHDL表达和设计电路的方法和学习多层次设计方法。

实验三 用VHDL输入法设计七段译码器电路

实验三用VHDL输入法设计七段译码器电路一、实验目的:熟悉VHDL程序的一般结构以及用VHDL语言设计组合逻辑电路的一般方法。

要求用VHDL语言设计一个7段译码器,能实现四位二进制数到对应的十六进制数的译码功能,并完成设计输入、编译、仿真、硬件测试等过程。

二、实验原理:VHDL程序通常包含库、程序包、实体、结构体、配置5个组成部分,其中实体和结构体是VHDL程序中不可缺少的最基本的两个组成部分。

组合电路的特点是电路任一时刻的输出仅与当时的输入有关,而与当前的状态无关。

组合电路的设计只须注意如果采用条件语句,一定要采用完整的条件语句。

三、实验内容与步骤:1、打开VHDL编辑器,完成七段译码器的设计。

实验程序如下(CASE语句实现):LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DECODER ISPORT(INP:IN STD_LOGIC_VECTOR(3 DOWNTO 0);OUTP:OUT BIT_VECTOR (6 DOWNTO 0);SELIN:IN BIT_VECTOR(2 DOWNTO 0);SELOUT:OUT BIT_VECTOR(2 DOWNTO 0));END DECODER;ARCHITECTURE ART4 OF DECODER ISBEGINprocess(inp)beginCASE INP ISWHEN "0000"=>OUTP<= "0111111";WHEN "0001"=>OUTP<= "0000110";WHEN "0010"=>OUTP<= "1011011";WHEN "0011"=>OUTP<= "1001111";WHEN "0100"=>OUTP<= "1100110";WHEN "0101"=>OUTP<= "1101101";WHEN "0110"=>OUTP<= "1111101";WHEN "0111"=>OUTP<= "0000111";WHEN "1000"=>OUTP<= "1111111";WHEN "1001"=>OUTP<= "1101111";WHEN "1010"=>OUTP<= "1110111";WHEN "1011"=>OUTP<= "1111100";WHEN "1100"=>OUTP<= "0111001";WHEN "1101"=>OUTP<= "1011110";WHEN "1110"=>OUTP<= "1111001";WHEN "1111"=>OUTP<= "1110001";WHEN OTHERS=>NULL;END CASE;end process;SELOUT<=SELIN;END ART4;2、读懂以上程序,然后改用WHEN-ELSE语句完成本实验,VHDL程序输入完成后保存,并进行全编译。

7段数码显示译码器

7段数码显示译码器一、实验目的1.掌握QuartusII的使用使用方法,基本操作。

2.熟练掌握Verilog语言的语法,能够写出基本程序3.学习7段数码显示译码器的Verilog硬件设计,并在试验箱上验证。

二、实验环境1.计算机2.EDA试验箱二、实验原理7段数码是纯组合电路,通常的小规模专用IC,如74或6000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

可设输入4位码位A[3:0],输出控制7段共阴数码管的7位数据位LED7S[6:0].输出信号LED7S的7位分别接图2数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h。

三、实验内容将设计好的Verilog程序在Quartus II上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形,并在硬件平台上进行测试。

四、实验步骤1.新建一个Verilog HDL文件。

2.创建工程,并将文件添加进去。

3.设置并进行全程编译,修改出错的地方,直到程序正确编译。

4.设置芯片相应的管脚。

5.进行时序和功能仿真。

6.选择试验箱模式4。

7.配置下载。

module seg7(IN,led7);input [3:0] IN;output [6:0] led7;reg[6:0] led7;always @(IN)begincase(IN)4'b0000: led7<=7'b0111111;4'b0001: led7<=7'b0000110;4'b0010: led7<=7'b1011011;4'b0011: led7<=7'b1001111;4'b0100: led7<=7'b1100110;4'b0101: led7<=7'b1101101;4'b0110: led7<=7'b1111101;4'b0111: led7<=7'b0000111;4'b1000: led7<=7'b1111111;4'b1001: led7<=7'b1101111;4'b1010: led7<=7'b1110111;4'b1011: led7<=7'b1111100;4'b1100: led7<=7'b0111001;4'b1101: led7<=7'b1011110;4'b1110: led7<=7'b1111001;4'b1111: led7<=7'b1110001;default: led7<=0;endcaseendendmodule六、实验心得通过本次试验,熟悉了Quartus ii的基本操作,能够熟练的使用Verilog语言设计电路,对EDA软硬件平台有了更深的理解。

实验四七段数码管显示译码电路设计

实验四七段数码管显示译码电路设计一、实验目的1.学习7段数码显示译码器设计;2.学习VHDL的CASE语句应用及多层次设计方法;二、实验原理7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能做十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

作为7段译码器,输出信号LED7S的7位分别接如图1数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h。

图1 共阴数码管及其电路七段数码管显示译码电路真值表三、实验内容1、在QuartusII上用VHDL文本方式设计七段数码管显示译码电路;2;对该设计进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

提示:用输入总线的方式给出输入信号仿真数据,仿真波形示例图如图2所示。

3、将经过仿真的设计下载到硬件实验箱进行验证。

图2 7段译码器仿真波形[引脚锁定]用键8~键5控制输入D3~D0,用第8位数码管输出(引脚号167,166,165,164,163,162,161)。

四、实验要求1用VHDL语言实现电路设计2设计仿真文件,进行软件验证3通过下载线下载到实验板上进行验证五、实验报告要求1写出VHDL程序并加以详细注释2给出软件仿真结果及波形图3通过下载线下载到实验板上进行验证并给出硬件测试结果4写出学习总结。

EDA基于VHDL语言的7段LED显示译码器的设计

《EDA技术》课程实验报告一、实验名称实验5: 7段LED显示译码器的设计二、任务及要求【基本部分】4分1、在QuartusII平台上,采用文本输入设讣方法,通过编写VHDL语言程序,完成7段LED显示译码器的设计并进行时序仿真。

2、设计完成后生成一个元件,以供更高层次的设计调用。

3、实验箱上选择恰当的模式进行验证,目标芯片为ACEX1K系列EP1K30TC144-3。

【发挥部分】1分新建一原理图文件,调用一个实验一的24进制计•数器元件和2个本次的LED 显示译码器元件,组成带LED显示译码器的24进制计数器电路,选择一个不带译码器的模式,在实验箱上进行验证。

三、实验程序源程序:library ieee;use ieee・std_logic_1164. all:use ieee・ std_logic_unsigned・ all;use ieee・ std_logic_arith・ all;entity LEDXIAXSHI isport(din:in std_logic_vector(3 downto 0); led:out std_logic_vector(6 downto0)); end entity LEDXIAXSHI:architecture art 1 of LEDXIAXSHI isbeginprocess(din)begincase(din) iswhen "0000"二〉ledU" 1111110"; —0 when "0001〃二>led〈二〃0110000〃;--1 when "0010〃二>ledU〃1101101";—2 when "0011 "二〉1 edU" 1111001"; —3 when "0100"二>led〈="0110011";—4 when "0101〃二〉led〈二"1011011";--5 when "0110"二>led〈="1011111";--6 when "0111 "二>ledU" 1110000"; —7 when " 1000"二〉ledU" 1111111"; —8 when " 1001〃二>led〈二〃1111011"; —9 when others二>led〈二"1111110";--0 end case;end process;end architecture art_l;四、仿真及结果分析当A="0000〃时LED7S二"0111111";即显示十进制0当A=,,ooor,时1^)75二"0000110";即显示十进制 1当A=〃0010〃时LED7S二"1011011";即显示十进制 2当A二"0011"时LED7S二"1001111";即显示十进制 3当A二"0100"时LED7S二"1101100";即显示十进制 4当A二"0101"时LED7S二"1101101";即显示十进制 5当A二〃0110"时LED7S二"1111101";即显示十进制 6当A二〃0111"时LED7S二"0001111";即显示十进制7当A二〃1000〃时LED7S二"1111111";即显示十进制8当A="100r时LED7S二"1101111";即显示十进制9当A二其他时LED7S二"0000000"不显示。

实验六 BCD七段显示译码器的设计

浙江大学城市学院实验报告纸一.实验目的(1)学习利用VHDL语言设计BCD七段显示译码器的方法,掌握BCD 七段显示译码器的设计思路;(2)掌握软件工具的使用方法。

二.实验原理根据BCD七段显示译码器的真值表原理进行实验,如表2—3所示。

三.实验内容用VHDL语言设计BCD七段显示译码器,进行编译、波形仿真及器件编程,并自行用VHDL语言设计3线-8线译码器。

四.源程序清单library ieee;use ieee.std_logic_1164.all;entity gaoqianyi isport (a:in std_logic_vector (3 downto 0);y:out std_logic_vector (6 downto 0));end gaoqianyi;architecture zhang of gaoqianyi isbeginprocess(a)begincase a iswhen"0000"=>y<="0111111"; --0的BCD七段码when"0001"=>y<="0000110"; --1的BCD七段码when"0010"=>y<="1011011"; --2的BCD七段码when"0011"=>y<="1001111"; --3的BCD七段码when"0100"=>y<="1100110"; --4的BCD七段码when"0101"=>y<="1101101"; --5的BCD七段码when"0110"=>y<="1111101"; --6的BCD七段码when"0111"=>y<="0100111"; --7的BCD七段码when"1000"=>y<="1111111"; --8的BCD七段码when"1001"=>y<="1101111"; --9的BCD七段码when"1010"=>y<="1110111"; --A的BCD七段码when"1011"=>y<="1111100"; --B的BCD七段码when"1100"=>y<="0111001"; --C的BCD七段码when"1101"=>y<="1011110"; --D的BCD七段码when"1110"=>y<="1111001"; --E的BCD七段码when others=>y<="1110001"; --F的BCD七段码end case; end process; end zhang;附加:3线-8线译码器表2-4 3线-8线译码器真值表不带使能端library ieee;use ieee.std_logic_1164.all;entity gaoqianyi11 isport (a:in std_logic_vector (2 downto 0);y:out std_logic_vector (7 downto 0)); end gaoqianyi11;architecture zhang of gaoqianyi11 isbeginwith a selecty<="11111110"when"000","11111101"when"001","11111011"when"010","11110111"when"011","11101111"when"100","11011111"when"101","10111111"when"110","01111111"when"111","11111111"when others;end zhang;带使能端library IEEE;use IEEE.std_logic_1164.all;entity gaoqianyi111 isport (A : in std_logic_vector (2 downto 0);S1,S2,S3 : in std_logic;Y : out std_logic_vector (7 downto 0));end entity;architecture gaoqianyi111_arch of gaoqianyi111 is signal s : std_logic_vector(2 downto 0);beginS <= S1&S2&S3;process(A, S)beginY <= (others => '1');if S="100" thencase A iswhen "000" =>y<= "11111110";when "001" =>y<= "11111101";when "010" =>y<= "11111011";when "011" =>y<= "11110111";when "100" =>y<= "11101111";when "101" =>y<= "11011111";when "110" =>y<= "10111111";when "111" =>y<= "01111111";when others => NULL;end case;end if;end process;end architecture;五.实验总结我学会了利用VHDL 语言设计BCD 七段显示译码器的方法和自己编写类似的程序。

VHDL语言设计七段示波译码器

课程: 数字逻辑与数字系统BCD-七段译码示波器实验报告系:电子信息与计算机科学系专业:自动化班级:文自112—2班姓名:桑*超学号: 2011905192**指导教师:徐红霞学年学期:2012-2013学年(第一学期)2012年12月19日姓名: 桑*超班级: 文自112-2班学号: 2011905192**试验: VHDL语言设计日期:2012.12.19 指导老师: 徐洪霞一、实验报告的名称: VHDL语言设计BCD-七段译码示波器二、本次实验的目的:1.掌握VHDL 语言的设计技巧2.用VHDL语言设计BCD-七段译码示波器三、设计过程:1.工程编译源:用VHDL语言编程。

2.功能仿真:将功能编译后的结果进行仿真。

3.引脚锁定:将个信号按要求分配到相应引脚.4.物理实现:将结果下载到所悬着的器件中四、写出源程序,画出防真波形图.例化后: 显示器:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity v_deco74 isport( num : in std_logic_vector(3 downto 0);b : out std_logic_vector(6 downto 0));end v_deco74;architecture one of v_deco74 isbeginprocess(num)begincase a iswhen "0000"=>b<="1111110";when "0001"=>b<="0110000";when "0010"=>b<="1101101";when "0011"=>b<="1111001";when "0100"=>b<="0110011";when "0101"=>b<="1011011";when "0110"=>b<="1011111";when "0111"=>b<="1110000";when "1000"=>b<="1111111";when "1001"=>b<="1111011";when others =>b<="XXXXXXX";end case;end process;end one;五、实验总结,主要包括实验中所犯错误,怎样改正等1.在文件名必须与VHDL文件中的设计实体名保持一致。

用VHDL语言设计BCD-七段译码

简单电路的VHDL语言描述一、实验内容1.用VHDL语言设计BCD-七段译码驱动芯片,编译、下载,并进行电路功能验证。

(1) 程序源代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DELED ISPORT(NUM:IN STD_LOGIC_VECTOR(3 DOWNTO 0);A,B,C,D,E,F,G: OUT STD_LOGIC);END ENTITY DELED;ARCHITECTURE ART OF DELED ISSIGNAL LED:STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINPROCESS(NUM)BEGINCASE NUM ISWHEN "0000"=>LED<="1111110";WHEN "0001"=>LED<="0110000";WHEN "0010"=>LED<="1101101";WHEN "0011"=>LED<="1111001";WHEN "0100"=>LED<="0110011";WHEN "0101"=>LED<="1011011";WHEN "0110"=>LED<="1011111";WHEN "0111"=>LED<="1110000";WHEN "1000"=>LED<="1111111";WHEN "1001"=>LED<="1111011";WHEN "1010"=>LED<="1110111";WHEN "1011"=>LED<="0011111";WHEN "1100"=>LED<="1001110";WHEN "1101"=>LED<="0111101";WHEN "1110"=>LED<="1001111";WHEN OTHERS=>LED<="1000111";END CASE;END PROCESS;A<=LED(6);B<=LED(5);C<=LED(4);D<=LED(3);E<=LED(2);F<=LED(1);G<=LED(0);END ART;(2) 程序的编译和电路功能的仿真结果电路的编译电路功能的仿真(3) 电路的引脚分配电路引脚分配图2.用VHDL语言设计一个分频器,输出100Hz方波的电路,编译、仿真、下载,并进行电路功能的验证。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程: 数字逻辑与数字系统BCD-七段译码示波器实验报告

系:电子信息与计算机科学系

专业:自动化

班级:文自112—2班

姓名:桑*超

学号: 2011905192**

指导教师:徐红霞

学年学期:2012-2013学年(第一学期)

2012年12月19日

姓名: 桑*超班级: 文自112-2班学号: 2011905192**

试验: VHDL语言设计日期:2012.12.19 指导老师: 徐洪霞

一、实验报告的名称: VHDL语言设计BCD-七段译码示波器

二、本次实验的目的:

1.掌握VHDL 语言的设计技巧

2.用VHDL语言设计BCD-七段译码示波器

三、设计过程:

1.工程编译源:用VHDL语言编程。

2.功能仿真:将功能编译后的结果进行仿真。

3.引脚锁定:将个信号按要求分配到相应引脚.

4.物理实现:将结果下载到所悬着的器件中

四、写出源程序,画出防真波形图.

例化后: 显示器:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity v_deco74 is

port( num : in std_logic_vector(3 downto 0);

b : out std_logic_vector(6 downto 0));

end v_deco74;

architecture one of v_deco74 is

begin

process(num)

begin

case a is

when "0000"=>b<="1111110";

when "0001"=>b<="0110000";

when "0010"=>b<="1101101";

when "0011"=>b<="1111001";

when "0100"=>b<="0110011";

when "0101"=>b<="1011011";

when "0110"=>b<="1011111";

when "0111"=>b<="1110000";

when "1000"=>b<="1111111";

when "1001"=>b<="1111011";

when others =>b<="XXXXXXX";

end case;

end process;

end one;

五、实验总结,主要包括实验中所犯错误,怎样改正等

1.在文件名必须与VHDL文件中的设计实体名保持一致。

2.要记住七段示波译码器是共阴极的.

3.要知道七段示波译码器的a、b、c、d、e、f段分别所对应的位置。