典型半导体案例失效分析

半导体器件失效分析的研究

半导体器件失效分析的研究Research on Semiconductor Device Failure Analysis中文摘要半导体失效分析在提高集成电路的可靠性方面有着至关重要的作用。

随着集成度的提高,工艺尺寸的缩小,失效分析所面临的困难也逐步增大。

因此,失效分析必须配备相应的先进、准确的设备和技术,配以具有专业半导体知识的分析人员,精确定位失效位置。

在本文当中,着重介绍多种方法运用Photoemission显微镜配合IR-OBIRCH精确定位失效位置,并辅以多项案例。

Photoemission是半导体元器件在不同状态下(二极管反向击穿、短路产生的电流、MOS管的饱和发光,等等),所产生的不同波长的光被捕获,从而在图像上产生相应的发光点。

Photoemission在失效分析中有着不可或缺的作用,通过对好坏品所产生的发光点的对比,可以为后面的电路分析打下坚实的基础,而且在某些情况下,异常的发光点就是最后我们想要找到的defect的位置。

IR-OBIRCH(Infrared Optical beam Induced Resistance Change)主要是由两部分组成:激光加热器和电阻改变侦测器。

电阻的改变是通过激光加热电流流经的路径时电流或者电压的变化来表现的,因此,在使用IR-OBIRCH时,前提是必须保证所加电压两端产生的电流路径要流过defect的位置,这样,在激光加热到defect位置时,由于电阻的改变才能产生电流的变化,从而在图像上显现出相应位置的热点。

虽然Photoemission和IR-OBIRCH可以很好的帮助我们找到defect的位置,但良好的电路分析以及微探针(microprobe)的使用在寻找失效路径方面是十分重要的,只有通过Photoemission的结果分析,加上电路分析以及微探针(mi croprobe)测量内部信号的波形以及I-V曲线,寻找出失效路径后,IR-OBIRCH 才能更好的派上用场。

半导体器件失效原因分析

半导体器件失效原因分析发信站: 紫金飞鸿 (Mon Oct 2 12:02:48 2000)多年来,用户要求有更可靠的电子设备,而与此同时,电子设备发展得越来越复杂。

这两个因素的结合,促使人们更加关注电子设备在长期运行中确保无故障的能力。

通过失效分析可以深入理解失效机理和原因,引导元器件和产品设计的改进,有助于提高电子设备(系统)的可靠性。

半导体器件的失效通常是因为产生的应力超过了它们的最大额定值。

电气应力、热应力、化学应力、辐射应力、机械应力及其他因素都会造成器件失效。

半导体器件的失效机理主要划分成以下6种:一、包封失效。

这类失效发生在用于封装器件的包封出现缺陷,通常是开裂。

机械应力或热应力以及包封材料与金属引线之间热膨胀系数的不同都会引起包封开裂,当环境湿度很高或器件暴露在溶剂、清洗剂等中时,这些裂缝会使湿气浸入,产生的化学反应会使器件性能恶化,使它们失效。

二、导线连接失效。

由于通过大电流造成过量的热应力、或由于连接不当使连接线中产生机械应力、连接线与裸芯之间界面的开裂、硅中的电致迁移、以及过量的连接压力,都会引起导线连接失效。

三、裸芯粘接故障。

裸芯与衬底之间粘接不当时,就会恶化两者之间的导热性,结果会使裸芯过热,产生热应力和开裂,使器件失效。

四、本征硅的缺陷。

由晶体瑕疵或本征硅材料中的杂质和污染物造成的缺陷使器件失效,在器件制造期间扩散工艺产生的工艺瑕疵也会造成器件失效。

五、氧化层缺陷。

静电放电和通过器件引线的高压瞬时传送,可能会使氧化层(即绝缘体)断开,造成器件功能失常。

氧化层中的开裂、划伤、或杂质也会导致器件失效。

六、铝金属缺陷。

这类缺陷往往由下列几种情况造成:由于大电场导致在电流流动方向上发生铝的电迁移;由于大电流造成过量电气应力,导致铝导体断裂;铝被腐蚀;焊接引起铝金属耗损;接触孔被不适当地淀积上金属;有小丘和裂缝。

半导体器件应该工作在由生产厂确定的电压、电流和功耗限定范围内,当器件工作在这个“安全工作范围(SOA)”之外时,电气应力过度(EOS)就会引起内部电压中断,导致器件内部损伤。

浅谈IGBT失效分析

浅谈 IGBT失效分析摘要:绝缘栅双极晶体管(IGBT)是由功率MOSFET和双极晶体管(BJT)复合而成的一种新型的电力半导体器件,它集两者的优点于一体,具有输入阻抗大、驱动功率小、控制电路简单、开关损耗小、速度快及工作频率高等特点,成为目前最有应用前景的电力半导体器件之一。

在轨道交通、航空航天、新能源、智能电网、智能家电这些朝阳产业中,IGBT作为自动控制和功率变换的关键核心部件,是必不可少的功率“核芯”。

采用IGBT进行功率变换,能够提高用电效率,提升用电质量,实现节能效果,在绿色经济中发挥着无可替代的作用。

关键词:IGBT;电力半导体;频率;功率本文研究大功率交流传动电力机车技术平台及大功率交流传动内燃机车技术平台,参考了国内外文献,通过对试验和应用数据的搜集、统计、整理,发现了一些典型的IGBT模块失效案例,并对其进行了失效特征分析,具体如下:1 过压失效1.1集-射极过压失效失效位置发生在有源区的边缘处,如图1(a)所示。

可见,芯片表面靠近内侧保护环处有小面积轻微烧损。

发生失效的条件:一是芯片击穿电压不满足要求,或者芯片的击穿电压发生退化;二是IGBT工作时发生异常,导致芯片承受的电压超过其可以承受的额定击穿电压。

1.2栅-射极过压失效失效位置发生在栅极与发射极隔离区,如图1(b)所示。

失效特征表现为芯片表面栅极与发射极隔离区上有熔点。

发生失效的条件:一是芯片栅极氧化层质量差,耐压不满足要求,或者芯片的栅极氧化层耐压发生退化;二是工况导致栅极过电压或电路产生栅极震荡。

2 过流失效2.1短路失效失效位置发生在IGBT有源区(不含栅极),如图2所示。

失效表现为模块中多个IGBT 芯片同时严重烧毁。

发生失效的条件:一是芯片短路安全工作区不能满足系统设计要求,或者短路安全工作区发生退化;二是工况发生异常,IGBT回路出现短路且IGBT未能及时被保护;三是半桥臂出现短路(IGBT或续流二极管),导致另一半桥臂IGBT被短路,发生短路失效;四是工作环境温度升高,导致芯片结温升高,短路安全工作区范围变小;五是控制信号问题,导致IGBT误开关,引起(桥臂)短路失效。

死灯-LED半导体封装失效典型案例原因分析及预防措施

死灯,不亮属于灾难性失效.下面列举常见的失效案例及预防措施供大家参考

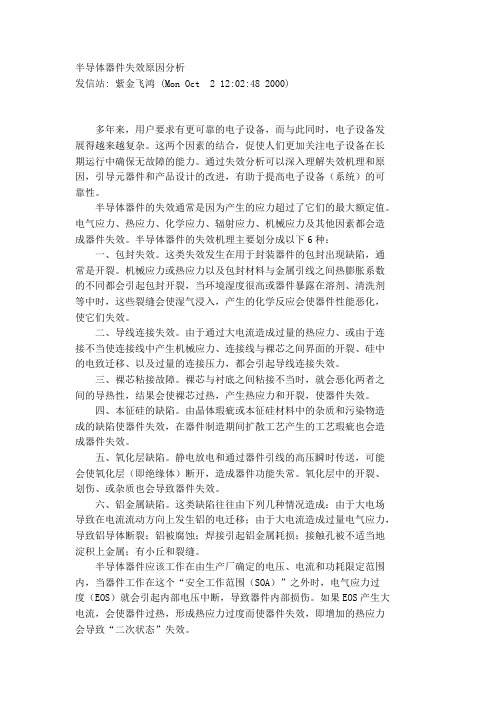

1)LED散热不佳,固晶胶老化,层脱,芯片脱落

预防措施:做好LED散热工作,保证LED的散热通道顺畅(焊接时防止LED 悬浮,倾斜)

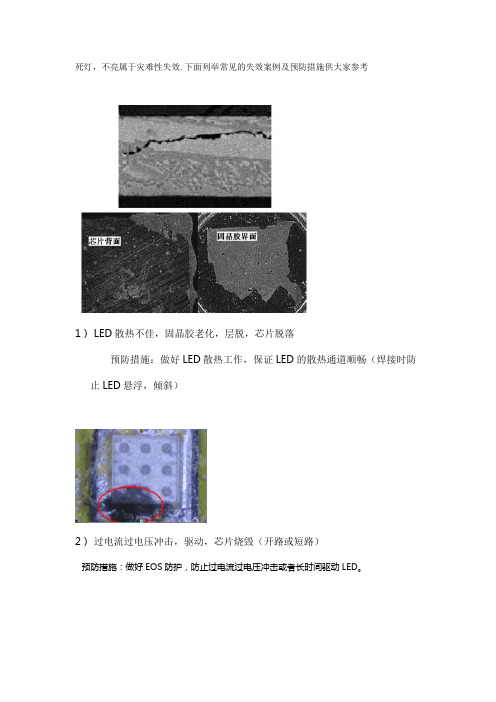

2)过电流过电压冲击,驱动,芯片烧毁(开路或短路)

预防措施:做好EOS防护,防止过电流过电压冲击或者长时间驱动LED。

3)过电流冲击,金线烧断4)使用过程中,未做好ESD防静电防护,导致LED PN结被击穿。

预防措施:防止过电流过电压冲击LED。

4)使用过程未做好防静电防护,导致LED PN结被击穿。

预防措施:做好ESD防护工作

5)焊接温度过高,胶体膨胀剧烈扯断金线或者外力冲击碰撞封装胶体,扯断金

线。

预防措施:按照推荐的焊接条件焊接使用,装配过程中注意保护封装结构部分不受损坏。

6)LED受潮未除湿,回流焊过程中胶裂,金线断。

预防措施:按照条件除湿,可利用防潮箱或者烘箱进行干燥除湿。

应按照推荐的回流参

数过回流焊。

7)回流焊温度曲线设置不合理,造成回流过程胶体剧烈膨胀导致金线断。

预防措施:按照推荐的回流参数过回流焊。

8)齐纳被击穿,装配时LED正负极被短接或者PCB板短路,LED被击穿。

预防措施:做好ESD防静电保护工作,避免正负极短路,PCB要做仔细排查。

功率半导体IGBT失效分析与可靠性

功率半导体IGBT失效分析与可靠性摘要:目前,IGBT是绿色经济领域的核心技术之一,应用于航空航天、新能源、轨道交通、工业变频、智能电网等领域。

作为自动控制和功率转换的关键核心部件,IGBT是不可或缺的功率核心。

利用IGBT进行电能转换,可以提高电能效率和质量,达到30%~40%的节能效果。

即使用IGBT技术改造传统设备,平均节电率仍可提高20%。

此外,IGBT也是实现能源转换的关键部件,光伏发电、风力发电、太阳能发电等新能源都需要使用IGBT产品向电网输送电能。

关键词:主动式PFC升压电路;IGBT;SOA;闩锁效应;ESD;结合大量失效品分析与电路设计分析,对IGBT失效原因及失效机理分析,分析结果表明:经过对IGBT失效分析及IGBT工作电路失效分析及整机相关波形检测、热设计分析、IGBT极限参数检测对比发现IGBT失效由多种原因导致,IGBT在器件选型、器件可靠性、闩锁效应、驱动控制、ESD能力等方面存在不足,逐一分析论证后从IGBT本身及电路设计方面全部提升IGBT工作可靠性。

一、分析及生效机理1.失效器件无损检测分析。

(1)X-ray透射分析。

失效IGBT表面无损伤,万用表测试1、2、3脚互相短路,X光透射内部IGBT芯片金线焊接等无异常,芯片表面有烧毁点,分析内部过电损伤导致失效。

(2)开封解析。

对主板失效IGBT进行开封解析,内部芯片表面有击穿烧痕迹,IGBT失效均为有源区(active area)受到高能量损坏,分析主要为过电击穿失效。

IGBT等效电路如图1所示。

图1 IGBT结构描述(3)失效IGBT应用电路。

如图2,红框部分为PFC电路整流滤波部分,C401电容具有滤波和抑制EMI作用,PFC主电路部分由PFC电感L3、IGBT及快恢复二极管D901组成。

当IGBT闭合时电感L3充能,IGBT断开时电感L3释放电能。

IGBT应用电路结构图如图2所示。

图2 IGBT应用电路二、失效原因及失效机理分析经过对失效IGBT器件ESD能力检测、极限参数测试分析(极限耐压、SOA安全工作区、开关损耗、)、应用环境、驱动电路设计、整机工作波形分析、热设计分析发现其存在众多不足,总结归纳如下。

半导体器件失效分析

半导体器件失效分析半导体器件失效分析就是通过对失效器件进行各种测试和物理、化学、金相试验,确定器件失效的形式(失效模式),分析造成器件失效的物理和化学过程(失效机理),寻找器件失效原因,制订纠正和改进措施。

加强半导体器件的失效分析,提高它的固有可靠性和使用可靠性,是改进电子产品质量最积极、最根本的办法,对提高整机可靠性有着十分重要的作用。

半导体器件与使用有关的失效十分突出,占全部失效器件的绝大部分。

进口器件与国产器件相比,器件固有缺陷引起器件失效的比例明显较低,说明进口器件工艺控制得较好,固有可靠性水平较高。

1. 与使用有关的失效与使用有关的失效原因主要有:过电应力损伤、静电损伤、器件选型不当、使用线路设计不当、机械过应力、操作失误等。

①过电应力损伤。

过电应力引起的烧毁失效占使用中失效器件的绝大部分,它发生在器件测试、筛选、安装、调试、运行等各个阶段,其具体原因多种多样,常见的有多余物引起的桥接短路、地线及电源系统产生的电浪涌、烙铁漏电、仪器或测试台接地不当产生的感应电浪涌等。

按电应力的类型区分,有金属桥接短路后形成的持续大电流型电应力,还有线圈反冲电动势产生的瞬间大电流型电应力以及漏电、感应等引起的高压小电流电应力;按器件的损伤机理区分,有外来过电应力直接造成的PN结、金属化烧毁失效,还有外来过电应力损伤PN结触发CMOS电路闩锁后引起电源电流增大而造成的烧毁失效。

②静电损伤。

严格来说,器件静电损伤也属于过电应力损伤,但是由于静电型过电应力的特殊性以及静电敏感器件的广泛使用,该问题日渐突出。

静电型过电应力的特点是:电压较高(几百伏至几万伏),能量较小,瞬间电流较大,但持续时间极短。

与一般的过电应力相比,静电型损伤经常发生在器件运输、传送、安装等非加电过程中,它对器件的损伤过程是不知不觉的,危害性很大。

从静电对器件损伤后的失效模式来看,不仅有PN结劣化击穿、表面击穿等高压小电流型的失效模式,也有金属化、多晶硅烧毁等大电流失效模式。

半导体器件可靠性与失效分析微电子

可靠性影响因素

制造工艺

制造过程中的缺陷、杂质和结构变化等会影 响器件的可靠性。

环境因素

温度、湿度、压力、电磁场等环境因素对器 件的可靠性产生影响。

物理特性

器件的物理特性如尺寸、材料、结构等对可 靠性有重要影响。

电源和信号条件

电源电压、电流、信号频率和幅度等对器件 的可靠性有一定影响。

02

失效分析

失效定义与类型

失效定义

在规定条件下,半导体器件不能维持其特性或功能,称为失 效。

失效类型

分为硬失效和软失效。硬失效是指器件物理损坏,如断路、 短路或芯片脱落等;软失效是指器件性能下降,如参数漂移 、噪声增大或信号丢失等。

失效分析方法

外观检查

电路测试

通过肉眼观察或使用显微镜来检查器件的 外观是否有异常,如机械损伤、腐蚀或金 属化迁移等。

半导体器件的失效案例 分析

热失效案例

01

02

03

失效描述

半导体器件在高温下运行 时,其性能会受到影响, 导致其参数漂移或功能失 效。

原因分析

热失效通常由于热量积聚 、散热不良或热膨胀等因 素导致。

解决方案

优化器件设计、改善散热 条件或采用耐高温材料等 。

机械失效案例

失效描述

半导体器件在机械应力或 振动条件下运行时,可能 会出现裂纹、断裂或脱落 等现象。

THANKS FOR WATCHING

感谢您的观看

扫描电子显微镜(SEM)分析

通过测试电路性能来检查器件是否正常工 作,如电压、电流和电阻等参数的测量。

能谱分析(EDS)

利用SEM观察器件表面的微观结构,以确 定是否存在缺陷或污染物。

通过EDS检测器件表面的化学成分,以确定 是否存在金属污染或氧化等化学问题。

2-_失效分析案例2

爆米花效应引起塑封器件 内引线开路

4

MOS输入保护电路静电放电损伤

高温试验后引线键合失效

输入保护二极管烧毁

二极管保护电路漏电烧毁

二极管保护电路漏电烧毁

树脂暴裂拉断金丝,双基极二 极管BT33EJ开路

装机前进行过

-40℃~85℃高低温循 环和冲击 , 树脂内涂 料在温度和机械应力 下产生裂纹,拉断金 丝引线使二极管开路 失效

5

内涂胶裂纹拉断发射极引线

开关管高 低温试验和振 动试验后开路

三端稳压器失效

化学开封 后发现,输入 电源电压过 高,芯片表面 输入端引线键 合点周边金属 化连线烧毁

时钟电路静电放电损伤

瞬变电压引起的器件内部互联 线间击穿短路

去除芯片表面钝化层、金属化层后,SEM观察发现有微小击穿点

金属化铝-硅接触窗过合金

开关二极管 芯片粘接不良

电极分离面光滑且严重氧化 分离界面焊料光滑

6

芯片破裂三极管参数漂移

封装和键合应 力造成三极管芯 片破裂

基极键合区

封装和键合应力造成塑封三极管 芯片破裂

基极键合 区损伤 和芯 片裂纹

三态缓冲器 244F性能不稳定

整机做55℃高温环境 试验时,整机工作不 正常,表现为所驱动 总线的时序出现异 常,用相同厂家和型 号的另一电路更换 后,整机工作恢复正 常。 水汽含量 好品1266ppM 失效品6724ppM

时间:2分钟

过电证据:下层金属严重损伤

49% HF 1.5 分钟

结论

• 与静电放电(ESD)相比,过电应力(EOS) 持续时间长,电流大

• 过热是EOS的主要特点 • 电-热共同引起:金属电迁移、金-铝键合点

形成金-铝化合物 • 热-机械应力引起:塑封器件的塑封材料和管

FA process instruction (半导体器件失效分析)

表2、X射线透视技术和反射式扫描声学显微术(C-SAM)的 比较

名称

应用优势

X射线透视 以低密度区为背景, 技术(X-Ray) 观察材料的高密度区

的密度异常点(主要 用来判定引线断裂)

反射式扫描 以高密度区为背景, 声学显微术 观察材料内部空隙或 (C-SAM)低密度区(主要用来

1.7.1打开封装

机械开封(磨,撬,加热等方法) 主要针对金属封装的器件。

化学开封(磨,钻,发烟硝酸、发烟硫酸腐 蚀法等) 主要针对塑料封装的器件。

去除塑料封装机器(decapsulator)

1.7.2 去钝化层技术

1为什么要去除钝化层?

2去除钝化层的方法: 化学腐蚀(各向同性) 等离子腐蚀PIE (各向同性) 反应离子刻蚀RIE(各向异性)

一般步骤: 固定器件(石蜡、松香和环氧树脂Epoxy) 研磨(毛玻璃、粗砂纸) 粗抛光(金相砂纸) 细抛光(抛光垫加抛光膏) 染色 金相观察

测量结深的抛光染色图片

1.8显微形貌像技术

光学显微镜和扫描电子显微镜的比较

仪器名称 真空条件 样品要求 理论空间 最大放 景深 分辨率 大倍数

光学显微 无 镜

开封

360nm

1200 小

扫描电子 高真空 开封、去 5nm

显微镜

钝化层

50万 大

光学照片与SEM照片对比

1.9基于测量电压效应的失效定位技术

1.9.1、扫描电子显微镜的电压衬度像 工作原理 :电子束在处于工作状态下的被测芯片表

面扫描,仪器的二次电子探头接收到的电子数量与 芯片表面的电位分布有关。从而得到包含器件中电 极的电势信息的SEM图象(IFA Image-based Failure Analysis)。 判定内容:芯片的金属化层开路或短路失效。

半导体三极管的失效分析与可靠性研究

图1 开封芯片表面表1 三极管性能测试数据图2 焊接不良示意图鱼尾也出现过断线,如图3所示,CT扫描发现管脚鱼尾不良,出现断点。

断点处与焊盘有轻微接触,导致故障不稳定,在使用中长期通电出现开路。

图3 鱼尾断线CT扫描图如图4所示,底板不平,底板四周出现高度差,导图4 鱼尾断线示意图鱼尾断线的不良原因为底板有硅碎,或在拆卸重新安装后未做水平高度差检测,导致底板不平,劈刀切线时,管脚呈悬空状态,管脚上下摆动,拉扯铜线,最终导致鱼尾断线。

1.1.4 虚焊故障模拟验证制作一颗硅碎,如图5所示,大概整颗芯片的1/3大小放在底板对应的基岛位置下面,将已上芯的产品拉到底板下,开始焊接,共计实验5颗。

当焊接到此颗芯图5 焊接故障模拟图综合以上分析,确认此次不良的根本原因为生产期间偶然有硅碎随着机器的振动移动到底板下,造成基岛不平,铜线焊接时焊接能量损失,导致产品焊球焊接不图6 X光透视图图8 塌丝故障分析鱼骨图3.2.2 出料盒改善焊线机料盒出料口处加装挡块,具体见图9,防止机器振动使框架从料盒振出压塌已焊线产品造成塌线。

图9 增加挡板3.2.3 包封台优化改善针对包封工序人为调整料片方法不规范,造成产品塌线的现象,将原来的凸台设计改为凹台设计,见图10,在四周增加挡边定位,防止料片移动,无需手动对料片位置进行调整,避免人为调整料片造成塌线。

图10 料片定位改为凹台3.2.4 检验方法优化针对产品检验时易受干扰导致塌线的情况更改检验方法,见图11,由之前取下料片在放大镜下检查改为在设备显示器上检查焊球和鱼尾,用设备显微镜检查线弧形状,减少人为干涉产品,预防塌丝。

QC检验频率:图11 显微镜检查3.2.5 人为调整专项打包针对产品包封前受人为干扰产品存在塌线风险的可能,将焊线工序、包封工位所有人为干预过的料片统一装入蓝色料盒,包封后再对其进行X-ray全检确认,将异常品剔除。

4 失效整改总结及意义三极管失效是厂家本身产品生产过程及筛选不良导致实际应用中出现故障。

半导体失效分析报告案例范文

半导体失效分析报告案例范文英文回答:Semiconductor failure analysis is a crucial process in identifying and resolving issues with semiconductor devices. It involves the investigation and examination of failed semiconductors to determine the root cause of the failure.In this report, I will provide a case study on a semiconductor failure analysis.The first step in the analysis is to gather information about the failed device and its operating conditions. This includes details such as the device type, application, and any relevant specifications. For example, let's say we are analyzing a failed power MOSFET that was used in a motor control application. The device was rated for a maximum voltage of 600V and a maximum current of 20A.Next, I would perform a visual inspection of the failed device. This involves examining the external features ofthe device for any signs of damage or anomalies. In our case, I might observe that the device has burn marks on the surface, indicating a potential thermal issue.After the visual inspection, I would proceed with electrical testing. This involves measuring various electrical parameters of the device, such as voltage, current, resistance, and capacitance. By comparing the measured values to the device's specifications, I can identify any deviations that may have contributed to the failure. For example, I might find that the resistance between the drain and source terminals of the MOSFET is higher than the specified value, suggesting a possible short circuit.In addition to electrical testing, I would also conduct a thermal analysis. This involves measuring the temperature of the device during operation and comparing it to the device's thermal specifications. In our case, I might use a thermal camera to observe the temperature distribution on the surface of the MOSFET. If I find that certain areas of the device are significantly hotter than others, it couldindicate a localized overheating issue.To further investigate the root cause of the failure, I would perform a failure mode and effects analysis (FMEA). This involves analyzing the potential failure modes of the device and their effects on its performance. By considering factors such as material defects, manufacturing processes, and environmental conditions, I can narrow down the possible causes of the failure. For example, I might determine that the burn marks on the MOSFET were caused by excessive current flowing through the device, leading to thermal runaway.Based on the findings from the analysis, I would then propose recommendations for resolving the issue and preventing future failures. This could include suggesting design improvements, changes in manufacturing processes, or modifications to the device's operating conditions. For example, I might recommend using a MOSFET with a higher current rating or implementing better thermal management techniques in the motor control system.In conclusion, semiconductor failure analysis is a systematic process that involves gathering information, performing visual and electrical testing, conducting thermal analysis, and using failure mode and effects analysis to identify the root cause of a failure. By understanding the failure mechanism, appropriate recommendations can be made to prevent future failures and improve the reliability of semiconductor devices.中文回答:半导体失效分析是识别和解决半导体器件问题的关键过程。

PCB失效分析技术与典型案例

在 PCB 或焊点的失效分析方面,SEM 主要用来作失效机理的分析, 具体说来就是用来观察焊 盘表明的形貌结构、焊点金相组织、测量金属间化物、可焊性镀层分析以及做锡须分析测量等。与 光学显微镜不同, 扫描电镜所成的是电子像, 因此, 只有黑白两色, 并且扫描电镜的试样要求导,电 对非导体和部分半导体需要喷金或碳处理,否则电荷聚集在样品表面就影响样品的观察。此外,扫 描电镜图象景深远远大于光学显微镜,是金相结构、显微断口以及锡须等不平整的样品的重要分析 方法。

Abstract Due to the trend of PCB developing toward high density and the environmental requirements of lead free and halogen free for PCB,all kinds of failure issues including bad wetting, blast, delamination and CAF are apt to take place more and more oftenly. In this paper analysis technologies for these failures will be firstly introduced,which includes SEM/EDS,XPS, microsection,t hermal analysis(TGA/DSC/TMA),FTIR , wetting balance test and so on. Followingly, the applications of these analysis technologies are presented in some typical failure cases. To discover the mechanism and rooted causes for PCB failure will make for the quality control of PCB and free of re-happening of similar cases in the coming days. Keywords:PCB Failure Analysis Analysis Technology

(整理)半导体器件芯片焊接失效模式分析与解决探讨.

半导体器件芯片焊接失效模式分析与解决探讨半导体器件芯片焊接失效模式分析与解决探讨芯片到封装体的焊接(粘贴)方法很多,可概括为金属合金焊接法(或称为低熔点焊接法)和树脂粘贴两大类。

它们连接芯片的机理大不相同,必须根据器件的种类和要求进行合理选择。

要获得理想的连接质量,还需要有针对性地分析各种焊接(粘贴)方法机理和特点,分析影响其可靠性的诸多因素,并在工艺中不断地加以改进。

本文对两大类半导体器件焊接(粘贴)方法的机理进行了简单阐述,对几种常用方法的特点和适用性进行了比较,并讨论了在半导体器件中应用最为广泛的金-硅合金焊接失效模式及其解决办法。

1、芯片焊接(粘贴)方法及机理芯片的焊接是指半导体芯片与载体(封装壳体或基片)形成牢固的、传导性或绝缘性连接的方法。

焊接层除了为器件提供机械连接和电连接外,还须为器件提供良好的散热通道。

其方法可分为树脂粘接法和金属合金焊接法。

树脂粘贴法是采用树脂粘合剂在芯片和封装体之间形成一层绝缘层或是在其中掺杂金属(如金或银)形成电和热的良导体。

粘合剂大多采用环氧树脂。

环氧树脂是稳定的线性聚合物,在加入固化剂后,环氧基打开形成羟基并交链,从而由线性聚合物交链成网状结构而固化成热固性塑料。

其过程由液体或粘稠液→凝胶化→固体。

固化的条件主要由固化剂种类的选择来决定。

而其中掺杂的金属含量决定了其导电、导热性能的好坏。

掺银环氧粘贴法是当前最流行的芯片粘贴方法之一,它所需的固化温度低,这可以避免热应力,但有银迁移的缺点。

近年来应用于中小功率晶体管的金导电胶优于银导电胶。

非导电性填料包括氧化铝、氧化铍和氧化镁,可以用来改善热导率。

树脂粘贴法因其操作过程中载体不须加热,设备简单,易于实现工艺自动化操作且经济实惠而得到广泛应用,尤其在集成电路和小功率器件中应用更为广泛。

树脂粘贴的器件热阻和电阻都很高。

树脂在高温下容易分解,有可能发生填料的析出,在粘贴面上只留下一层树脂使该处电阻增大。

因此它不适于要求在高温下工作或需低粘贴电阻的器件。

半导体失效分析及案例分享2022-1-5

要非常熟悉你的分析仪器,不仅要玩转的很6,还要很了 解它的精度及性能;

要懂得利用可靠性试验来验证产品的某项性能;

Typical Case Sharing

死灯案例一

1、背景描述: ※Note: A客户反馈我司EMC3030产品做成灯具后,终端客户使用3个月出 现死灯现象,客户安装300个灯发现50个灯失效。

……………

失效信息的收集

How much 多少? 耗费成本

What 是什么? 事件主体

How 怎么样? 如何达成

5W2H

Where 何处? 何处进行

When 何时? 起止时间

Why 为什么? 原因目的

Who 谁? 参与人员

01 What:客户客诉3030死灯 02 Why:需要确认3030失效的原因 03 Who:客户名称? 04 When:什么时间?客户使用多久? 05 Where:什么地方发现的? 06 How:做什么试验发现的? 07 How much:有多少不良?不良率?

失效模式是什么?

失效原因

失效机理是什么?

有哪些失效模式?

有哪些失效机理?

失效样品

如何理解失效模式

什么是失效模式?

Failure Modes:

➢ 是指由失效机理所引起的可观察到的物理或化学变化;

比如:开路、短路、漏电;参数变化;颜色变化;

通俗的讲就是失效的表现形式。

外观失效

✓缺损 ✓异物 ✓裂纹 ✓变色

息么

做

的

分析的依据

失效品

失效分析的开始

失效样品的确认

样品的准确性

01

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

典型半导体案例失效分析

Author:朱秋高

光宝电子(东莞)有限公司

E-mial: Collins.zhu@

摘要:

开关电源与地之间走线的电感对主开关Mosfet 驱动影响和失效案例

关键词:

PWM 驱动信号的布线要点:

在开关转换期间,某些走线 (PCB上的敷铜线路) 电流会瞬间停止,而另外一些走线电流同时瞬间导通(均在开关转换时间100ns 之内发生). 这些走线被认为是开关调整器PCB布线的”关键走线”. 每个开关转换瞬时,这些走线中都产生很高的Di/dt .如图1-1所示,整个线路混杂着细小但不低的电压尖峰.由经验可知,不难理解这是方程V=L*Di/dt 在走线中起作用,L是PCB走线的寄生电感.根据经验,每英寸走线的寄生电感约为20nH

图1-1 确定三种拓扑中的关键走线

噪声尖峰一旦产生,不仅传递到输入/输出(影响电源性能),而且渗透到IC控制单元,使控制功能失稳失常,甚至使控制的限流功能失效,导致灾难性后果.

199

引言:

设计开关调整器PCB时,需知最终产品的好坏完全取决于它的布线,当然,有些开关IC可能会比其他开关IC对干扰更敏感.有时,从不同供应商购得的 “ 同类” 产品也可能有完全不同的噪声敏感度,.此外,某些开关IC结构本身也会比其他IC对噪声更敏感(如电流模式控制芯片比电压模式控制芯片”布线敏感度”高很多). 事实上,用户必须面对这样的现实: 半导体器件生产商不会提供其产品噪声敏感度的资料. 而作为设计人员,往往对布线不够重视,结果将似乎可稳定工作的IC弄得波形震荡,易受干扰,以致误动作,甚至导致灾难性的后果(开关烧掉). 另外,这些问题在调试后期往往很难纠正或补救,因此开始阶段就正确布线非常重要.

试验方法:

1. MOSFET 的驱动信号通常由IC内的驱动级产生,故MOSFET的源极应接至IC接地端.但MOSFET的实际表现并不由施加在栅极与参考间的电压所决定, 而是取决于栅极与源极间的电压,即完全取决于实际的V GS.

实例1,如果源极与地之间的走线有点长的话,在开关转换瞬间它上面会出现很大的电感反冲, 不严重的话只是降低开关转换的速度,严重时会使MOSFET错误地开通或关断,导致管子毁坏.

图1-2 是在关断瞬间可能发生的相当安全的情形.栅极控制MOSFET关断,但源极的PCB走线阻抗刚才也流过了电流,并产生小电压源(尖峰) 以阻止电流减小,电流持续流动直到能量消耗光.这使V GS波形发生改变从而使开关转换速度降低.然而,这种降低转换速度的方法并不值得推荐,根据我所知其结果不可预知,因为它本质上是基于寄生参数的.

图 1-2 关断时源极寄生电感的影响

2. 实例2, 图1-3 是一款使用在网络产品上的电源布线图,我们不难发现驱动信号到MOSFET的栅极之间的走线过长,(约为63mm) .且高频电感离驱动信号非常近,而导致在系统使用时,不时发生MOSFET 烧毁和PCB板大面积烧黑的现象,

200

图1-3 PCB红线为驱动信号到栅极的走线图1-4红线部分为高频电感R016为栅极限流电阻此电源在正常工作时测得其V GS的波形如下图1-5

图1-5 Vg-s

对于高频谐波电流来说,几毫米长的PCB走线会成为名副其实的阻抗壁,从而导致走线一端的电压上升(相对于另一端), 造成电路某处出现意外的结果.当阻抗呈感性时,由基本公式V=LdI/dt 可知,走线上会产生严重的电压反冲,其中dI/dt 为电流跳变沿的斜率,L是这段走线的电感.所以在设计开关调节器或排除开

201

关调节器故障时,PCB的设计显得如此重要.

结论:

1.对所有拓扑, 通常认为最重要的信号走线是反馈走线,若这条走线吸收了噪音(容性的或感性的),就会

使输出电压产生些许偏移------极端情况(较少见) 甚至造成不稳定或器件损坏.应使反馈走线尽量短,并远离噪声或磁场源(开关,二极管和电感)干扰.绝不能将反馈走线置于电感,开关或二极管下方(即使是PCB的另外一面的下方),也不能让它靠近或平行噪声走线超过2mm~~3mm,即使PCB的临近层也要这样考虑..有地处于中间层时,应在层间提供足够的屏蔽保护.

2.有时使反馈走线很短是不现实的,应认识到使走线尽量短并非第一位的要求.事实上,经常会有意识地

将它布得长一些,以便使这些走线避开潜在的噪声源.也可小心设计使部分反馈走线穿过地没有返回电流流过的部分,这将使得它被地包围着,免受干扰,如果这样还会有噪音干扰,就上像上面这个例子,也有一些补救措施,通过实验,在MOSFET管的栅极引脚上穿入一个小铁氧体磁珠可以减缓和吸收此类高频噪音,同时显著减少EMI.事实证明这个做是行之有效的,之后MOSFET没有因此噪音而损坏, 注意: 有时磁珠也与MOSFET串联,但是不能将这种磁珠放在源极上,如果放在源极上的话,那么交导通时源极引脚(带磁珠)会产生尖峰.因为栅极的参考点是源极而不是漏极,所以这会造成假导通,从而导致可靠性问题.因此,如果需要使用磁珠的话,磁珠的位置应该而且只能是在MOSFET的栅极或漏极.的确,这一额外的非耦合电感原理上会引起小尖峰,但实际上这很少会有问题..

致谢:

感谢Lite-on公司的资深电源主管SD.Deng, 也感谢Lite-on公司为我提供这样的平台和参考,测量仪器,当我写这个论文的时候我的同事:Norton.yin, Otto.Wang, Amir.ouYang, 设法为我提供不可估量的建议和数据.

202。