cpu控制器的设计

CPU设计实践教程6-Minisys-1单周期CPU控制器的设计

指令操作码 ori

addiu

lw

sw

beq jump

RegDst

0

0

0

000000 R-format

1

RegDST = R-format

wire R_format;

assign R_format = (Opcode==6'b000000)? 1'b1:1'b0; assign RegDST = R_format; //说明目标是rd,否则是rt

output Sftmd; output[1:0] ALUOp;

// 他I-类型指令 // 为1表明是移位指令 // 是R-类型或I_format=1时位1为1, beq、bne指令则 // 位0为1

2021/9/5 P.22

单周期控制器设计

RegDST的控制电路

op 001101 001001 100011 101011 000100 000010

output nBranch; // 为1表明是Bne指令

output Jmp;

// 为1表明是J指令

output Sftmd; // 为1表明是移位指令

2021/9/5 P.25

单周期控制器设计

练习2

请给出下列控制信号电路的Verilog描述

assign Sw = ????? assign ALUSrc = ????? assign Branch = ????? assign nBranch = ????? assign Jmp = ?????

2021/9/5 P.10

创建一个项目

在打开的Default Port对话框中选择的FPGA器件为 xc7a100tfgg484-1,如图所示,点击Next。

六章CPU设计

下地址控制编码方式

一般情况下后继微指令旳地址有下列几种给出方式:顺序递增法:将µPC设置成可实现自动加1旳功能,每当完毕目前指令旳执行,就以µPC +1后旳值为地址在控制存储器中取下一条微指令。直接给出法:下一条微指令旳地址直接取自微指令中旳下地址字段。分支转移法:在包括分支转移旳微指令中常设置一种条件选择子区域,用于指出哪些鉴定条件被测试,与此同步转移地址被存储在下地址字段。当转移条件满足时,将下地址字段旳内容读入到µPC中,取下一条微指令,实现微程序转移。若转移条件不满足,微程序则顺序执行。微程序入口地址旳形成:每条机器指令所相应旳微程序旳入口地址(首地址),一般由指令旳操作码所决定。在机器加电后,第一条微指令旳地址一般是由专门旳逻辑电路生成,也能够采用由外部直接输入旳形式取得。

操作控制编码方式

在操作控制字段一般涉及一种或多种操作控制域,每个控制域可控制一种或一组控制信号旳生成,根据控制信号是直接生成于控制域还是译码生成控制信号旳不同可分为下列几种形式。直接控制法:操作控制字段旳每一位都与一种独立控制信号相相应。若目前微指令旳某一位ki=1,则与之相应ci控制信号有效,不然ci控制信号无效。分段编码控制法:在微程序级别,许多微操作是能够并行执行。一般采用将微指令旳操作控制字段提成k个相互独立旳控制域,每一种控制域存储一组微操作,每一种编码相应一种微操作,每一种微操作都能够与其他控制域所存储旳任意一种微操作并行执行,但在组内旳微操作之间是互斥旳,不允许在同一时间段内发生或有效。分段间接编码控制法:在微指令格式里,假如一种字段旳含义不只决定本字段编码,还兼由其他字段决定,则可采用分段间接编码控制法。此时一种字段兼有两层或两层以上旳含义。其他方式:在实际微指令中操作控制编码并不是只单独采用上述三种编码方式中旳一种,而是将上述三种混合使用,以确保能综合考虑指令旳字长、灵活性和执行微程序旳速度等方面旳要求。

32位MIPS CPU设计

实验四32位MIPS CPU设计实验

1设计要求

使用Logisim 软件依次完成4 个子电路的设计,如下:

1. 指令译码器

2. 时序发生器状态机(定长指令周期)

3. 时序发生器输出函数(定长指令周期)

4. 硬布线控制器

在此基础上完成对“单总线CPU(3 级时序)”的联合调试,使之可以运行

简单的冒泡排序算法MIPS 汇编程序,实现排序功能。

2方案设计

2.1 指令译码器

原理:

根据MIPS指令格式表中各个指令的op字段,和IR送来的指令op字段比较,若相同则是该指令,注意SLT 指令还需要判断funct字段为101010,用异或门判断OtherInstr

电路:

图1指令译码器

2.2 时序发生器状态机(定长指令周期)

原理:

由于是定长指令周期,所以次态只和现态有关,Si->Si+1 (0<=i<=10),S11->S0

电路:

图2状态机

2.3 时序发生器输出函数(定长指令周期)

原理:

定长指令周期分为3个机器周期(取指,计算,执行)每个机器周期分为4个节拍S0~S3取指周期,S4~S7计算周期,S8~S11执行周期

每个机器周期内节拍递增

电路:

图3输出函数

2.4 硬布线控制器

原理:

状态暂存器输出到状态机计算出次态再返回状态寄存器,同时现态送到输出函数电路:

图4硬布线控制器

3实验步骤

按照设计连接电路,在电路图中“单总线CPU(3 级时序)”子电路中进行调试,测试CPU 是否可以正确执行冒泡排序程序

4测试与分析

发现数据6,5,4,3,2,1,-1按递减排序

实验结果符合预期。

PLC的双CPU冗余控制实现

PLC的双CPU冗余控制实现PLC(可编程逻辑控制器)的双CPU冗余控制是一种高可靠性的控制系统设计,它通过备用的CPU来实现系统的冗余保护,以提高系统的可用性和可靠性。

在双CPU冗余控制系统中,主CPU和备CPU同时运行,并且通过互相监控对方的状态和运行情况,实现故障检测、切换和恢复。

双CPU冗余控制的工作原理如下:1.主CPU和备CPU同时运行并执行相同的控制任务,输出信号也同时送至执行机构进行实际的控制操作。

2.主CPU和备CPU通过心跳信号相互监控对方的状态。

心跳信号由CPU定时产生,并发送至对方。

如果其中一方长时间未收到对方的心跳信号,则判断另一方发生了故障。

3.当主CPU发生故障时,备CPU会立即接管控制任务,并输出相同的控制信号。

这个切换的过程一般需要在几个周期内完成,以保证控制的连续性和稳定性。

4.当故障修复后,主CPU会重新与备CPU进行同步,并恢复正常的工作状态。

为了实现双CPU冗余控制,需要满足一些关键技术要求:1.心跳信号:主CPU和备CPU需要通过心跳信号相互监控。

心跳信号的产生和检测一般是基于硬件电路实现的,可以使用定时器和计数器控制心跳信号的周期和频率。

2.数据同步:主CPU和备CPU需要实时同步控制数据和状态信息,以保证在切换过程中不引入错误。

这一般需要通过专门的通信模块或总线进行数据传输和同步。

3.切换策略:在主CPU发生故障时,备CPU需要能够及时接管控制任务,并保证控制的连续性。

切换策略可以采用热备份、冷备份或温备份等不同的方案,具体选择需要根据实际应用需求和性能要求进行评估。

4.故障检测和恢复:在主CPU发生故障后,需要能够及时检测故障原因,并进行相应的故障处理和恢复。

这一般需要通过专门的故障检测算法和自动化处理程序来实现。

双CPU冗余控制的优点是可以提高系统的可用性和可靠性,降低因单点故障引起的停机时间和生产损失。

但也存在一些挑战和限制,如成本较高、对系统运行时的性能要求较高等。

基于多CPU的智能电动执行机构控制器设计

上 、该控制 器设 计 方案 可提 高 系统 的 可靠性 和 可维护性 ,对进 一步设 计新 型智 能 电动执 行机

构具 有指 导意 义 . 关 键 词 :电动执 行机 构 ;多 C PU;控 制 器

中 图 分 类 号 :TM 7 51

文 献 标 识 码 :A

文 章 编 号 :1 7 —7 7 ( 0 7 0 —3 50 , 39 8 2 0 ) 30 1 —3 6

收 稿 日期 :2 0 — 30 0 70 — 1 基 金项 目:河 南 省 科 技 攻 关 项 目 ( 3 4 5 0 5 ;河南 理 工大 学 青 年 基 金 项 目 ( 4 1 8 0 2 20 0 ) 660 )

作 者 简 介 :王 莉 (9 6 ) 17 一 。女 ,河 南 温 县 人 ,讲 师 ,从 事 工 业 过 程 计 算 控 制 和 智 能 仪 器 仪 表 方 面 的研 究

V o . No. 126 3

J n. 0 7 u 20

基 于多 C U 的智 能 电动 执 行 机 构 控 制 器设 计 P

王 莉 ,苏 波

( 南 理 工 大 学 电气 学 院 ,河 南 焦 作 河 44 0 ) 50 3

摘 要 :在对 目前 电动执 行机 构存 在 的 问题进 行 分析 的基 础上 ,提 出了一 种新 型智 能 电动执 行

个特定 的任务分 割成 较小 的任 务 由 多个 处 理器 并 行 地 执行 ,因 而具 有 速 度优 势 .采 用 嵌 入 式 多 C U P 系统使 得信 息处 理模块 化 ,各 个 C U 采 集分 配 的数据 量并 独 立处理 信 息 ,从 而 可 以减 轻 单个 C U 的 P P

负担 ,提 高系统 的信 息处 理速 度 和 处 理能 力 [ .因此 ,为 了 克服 电动 执 行 机 构控 制 器 现 有 结 构 形 式 存在 的 弊端 ,可 以在控制 器设计 中采用 多 C U 系统结 构 . P

多合一控制器CPU模块组成及功能解析

多合一控制器CPU模块组成及功能解析多合一控制器是一种集成了多种功能的电子控制设备。

它通过集成多个控制模块,在一个设备中提供了多种不同的功能。

本文将对多合一控制器的CPU模块的组成和功能进行解析。

一、多合一控制器CPU模块的组成多合一控制器的CPU模块是整个设备的核心部件,负责处理和控制各个功能模块之间的协调工作。

CPU模块通常由以下几个核心组成部分构成:1. 中央处理器(Central Processing Unit,CPU):CPU是多合一控制器的核心处理器,负责执行各种运算和控制指令。

它是多合一控制器的大脑,决定了整个设备的运行效率和性能。

2. 存储器(Memory):存储器是CPU模块中的重要组成部分,用于存储程序、数据和临时结果。

存储器通常包括高速缓存、内存和外部存储等。

3. 输入/输出接口(Input/Output Interface):输入/输出接口是CPU 模块与其他功能模块进行数据交换的纽带。

它负责管理和控制设备的输入和输出动作,以及进行数据的传输和转换。

4. 时钟发生器(Clock Generator):时钟发生器是CPU模块的一个重要组成部分,用于提供稳定的时钟信号。

时钟信号是整个设备的运行节奏,能够保证各个功能模块之间的同步性。

5. 总线(Bus):总线是CPU模块中的数据传输通道,用于连接各个功能模块。

总线通常包括地址总线、数据总线和控制总线,负责传输数据、地址和控制信号。

二、多合一控制器CPU模块的功能解析多合一控制器的CPU模块承担着多种重要功能,下面将对其功能进行解析:1. 运算功能:CPU模块通过内部的算术逻辑单元(Arithmetic Logic Unit,ALU)执行各种数学和逻辑运算,包括加法、减法、乘法、除法和比较等。

这些运算功能使得多合一控制器能够进行各种复杂的计算和处理任务。

2. 控制功能:CPU模块通过指令寄存器(Instruction Register)和程序计数器(Program Counter)等组成部分,解析和执行指令,控制各个功能模块的运行。

CPU设计

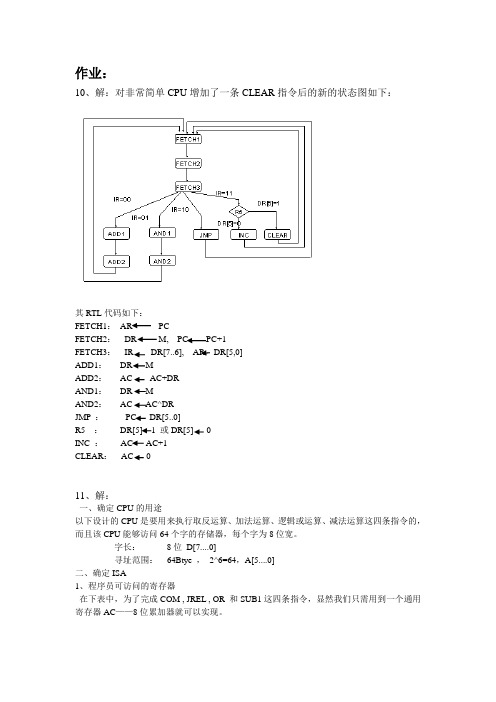

作业:10、解:对非常简单CPU增加了一条CLEAR指令后的新的状态图如下:其RTL代码如下:FETCH1:AR PCFETCH2:DR M, PC PC+1FETCH3:IR DR[7..6], AR DR[5,0]ADD1:DR MADD2:AC AC+DRAND1:DR MAND2:AC AC^DRJMP :PC DR[5..0]R5 :DR[5] 1 或DR[5] 0INC :AC AC+1CLEAR:AC 011、解:一、确定CPU的用途以下设计的CPU是要用来执行取反运算、加法运算、逻辑或运算、减法运算这四条指令的,而且该CPU能够访问64个字的存储器,每个字为8位宽。

字长:8位D[7....0]寻址范围:64Btye ,2^6=64,A[5....0]二、确定ISA1、程序员可访问的寄存器在下表中,为了完成COM , JREL , OR 和SUB1这四条指令,显然我们只需用到一个通用寄存器AC——8位累加器就可以实现。

指令操作码操作COM 00XX XXXX AC AC' (取反)JRET 01AA AAAA PC PC+00AA AAAAOR 10AA AAAA AC AC^M[00AA AAAA]SUB1 11AA AAAA AC AC—M[00AA AAAA]—12、CPU还需要一些其他的寄存器以便完成取指令(或数据)、译码和执行指令所必须的内部操作,最基本的寄存器有:AR(地址寄存器)——6位,由A[5.....0]向存贮提供地址PC (程序计数器)——6位,指出下一条指令的地址DR(数据寄存器)——8位,通过D[7....0]从存贮器接受指令和数据IR(指令寄存器)——2位,存放从存贮器中取回的指令的操作码部分。

三、为CPU设计状态图为了确定CPU的状态图,需对每条指令作如下分析:1、从存贮器取出指令(所有指令都相同)2、指令译码3、指令执行从存贮器中取出指令:1、原理:根据冯. 诺依曼型机的原理(指令在存贮器中按顺序存放.......), 在CPU能执行指令之前,它必须将这条指令从存贮中取出,CPU通过执行如下的操作序列完成这个任务的:【1】选择存贮单元由A[5... 0]确定【2】对A[5... 0]译码、延迟、并向存贮器发一个信号(如READ或R/W'=1),使存贮器将此指令输出到它的输出引脚。

单总线CPU设计(定长指令周期3级时序)

单总线CPU设计(定长指令周期3级时序)1. 引言本文档将介绍一种基于单总线的CPU设计,采用定长指令周期和3级时序。

单总线CPU是一种较为简单且常见的计算机处理器设计,其内部结构相对简单,适合于一些资源受限的嵌入式系统或低功耗应用。

定长指令周期意味着每条指令的执行时间是固定的,而3级时序则指的是CPU的时序由三个阶段组成。

2. 设计概述2.1 总体结构单总线CPU设计采用冯·诺依曼结构,主要包含以下几个核心组件:•控制器(Controller):负责控制指令的执行流程和时序控制。

•运算器(ALU):负责执行算术、逻辑和位操作指令。

•寄存器组(Register File):用于暂存数据和地址等信息。

•存储器(Memory):包括指令存储器和数据存储器。

•输入/输出接口(I/O Interface):负责与外部设备进行通信。

2.2 指令格式单总线CPU设计采用定长指令格式,每条指令由固定长度的几个字段组成。

常见的指令格式包括操作码(Opcode)、目标寄存器(Destination Register)、源操作数1(Source Operand 1)和源操作数2(Source Operand 2)等。

例如,对于一条简单的加法指令,其指令格式如下:| Opcode (6 bits) | Destination Register (4 bi ts) | Source Operand 1 (4 bits) | Source Operand 2 (4 bits) |2.3 时序控制单总线CPU设计采用3级时序,将指令执行过程划分为三个阶段:取指(Fetch)、译码(Decode)和执行(Execute)。

每个阶段占据一个时钟周期,遵循时序控制的规则。

取指阶段:从指令存储器中读取指令,存放到指令寄存器中。

译码阶段:解析当前指令的操作码和操作数,并从寄存器组中读取相关数据。

执行阶段:根据操作码和操作数执行相应的操作,将结果存储到寄存器组中。

计算机组成原理CPU设计

计算机组成原理CPU设计计算机组成原理是研究计算机内部结构和工作原理的一门学科。

而CPU(中央处理器)作为计算机的核心部件,负责执行计算机中所有的指令和运算操作。

CPU的设计有很多不同的方法和架构,本文将介绍一种常见的CPU设计,冯·诺依曼结构和指令周期。

冯·诺依曼结构是由冯·诺依曼在20世纪40年代提出的,并成为了现代计算机的基本结构。

它包含了五个主要的组成部分:控制器、算术逻辑单元(ALU)、寄存器、存储器和输入/输出(I/O)接口。

首先是控制器,它负责控制整个计算过程。

它将输入的指令解码并发送给相应的部件执行。

控制器通常是通过微指令来实现的,每个微指令对应着一条机器指令的执行过程。

其次是算术逻辑单元(ALU),它是负责实现加法、减法、乘法和逻辑运算等基本操作的核心部件。

它可以对数据进行运算,并将计算结果存储到寄存器中。

然后是寄存器,它是一种用于暂时存储数据的硬件设备。

计算机中有多种寄存器,如程序计数器(PC)、指令寄存器(IR)和通用寄存器等。

它们可以暂时存储计算过程中使用的数据和指令。

存储器是用来存储数据和指令的地方。

计算机中有多种存储器,如主存储器(RAM)、高速缓存(Cache)和硬盘等。

存储器按照地址访问,可以读取和写入数据。

最后是输入/输出(I/O)接口,它负责计算机与外部设备的数据交换。

输入接口接收来自外部设备的数据,输出接口将计算机处理的结果发送给外部设备。

这样计算机就可以实现与外界的通信。

指令周期是CPU执行一条机器指令的时间周期。

它通常包括取指令、译码、执行、访存和写回这五个阶段。

在取指令阶段,控制器从存储器中读取指令并保存到指令寄存器中;在译码阶段,控制器对指令进行解码,并根据指令的类型决定下一步的操作;在执行阶段,ALU根据控制器的指令进行运算操作;在访存阶段,控制器根据指令的要求将数据从存储器中读取或写入;最后在写回阶段,将计算结果写回到寄存器中或存储器中。

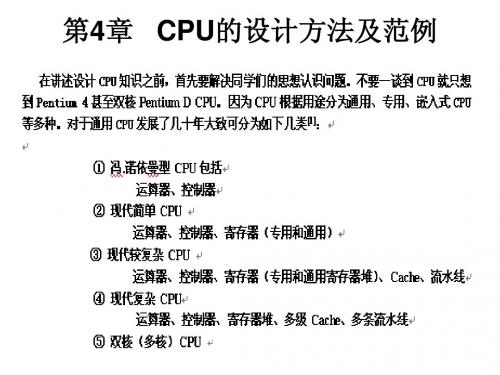

第4章 CPU的设计方法及范例

非常简单CPU不具有应用价值,仅用来说明 设计过程。不过,只要我们能正确设计出只有4条 指令的CPU,就可以设计出拥有40条指令的CPU, 甚至更多·· ·。难道这样还有怀疑吗?当然不能期 望马上就有创新,但这个CPU是拥有自主知识产 权的。或者有些同学会这样想,我以后并非从事 硬件的工作,更不可能从事设计CPU的专业,我 也相信这是事实。但是,这绝对有利于我们掌握 计算机的工作原理,也有利于从事各种软、硬件 开发和计算机科学等领域的研究、教学工作。

图4.9 通用CPU的状态图

其实CPU就是一个复杂的有限状态机 【冯· 诺依曼机的理论是基于图灵(Turing) 机理论的,而图灵机就是一个有限状态 机】。通过确定状态及其对应的微操作, 就可明确CPU为了取数据(或指令),指 令译码和执行指令集中每一条指令所必须 要完成的步骤。 问题:什么是图灵机理论?

1966年美国计算机协会设立“图灵奖”,被视为计算机科学界的最高荣誉

它的“纸带”相当于作业薄,读写头相当于人的眼 睛、手、笔,对于输入集{x1,x2,…xn},r(i, 0)= xi,i= 1,2,..n相当于“抄题”,而映射f 的读写变换相当于人脑判断确定下一步的行为且 指挥手和笔如何去动作和书写。它高度概括地回 答了什么是运算,不但为计算复杂度理论提供了 研究工具,而且为20世纪50年代计算机的设计提 供了思想基础,即Moore机和Mealy机。【注:当 出现状态Sy或Sn时,即得到了Turing 机的运算结 论Yes或No,这时即S(t)∈{ Sy,Sn }时停机】

二、建立数据通路的原理和方法

1.存贮器数据通路的原理

2.CPU内部的数据通路(两种不同的方案)

三、CPU内部寄存器控制信号的定义和确定方法

2.决定每个部件应完成的功能(详见图4.14)

简单CPU系统设计与实现

数字电路综合实验报告简单CPU系统设计与实现1设计课题的任务要求设计一个简单的CPU及其外部模块,能够完成机器代码的输入、存储、执行和结果显示。

基本要求:指令要求至少有空指令,跳转指令,加法指令,存取数据指令。

利用自己设计的指令系统编写一段机器语言,可以完成求两个小于256的数的最大公约数.机器语言通过拨码开关和按键逐条输入,通过程序执行开关控制程序执行,最后在数码管或LED灯上显示结果。

提高要求:设计并实现其它指令。

2系统设计2.1 设计思路设计的简易CPU系统主要由指令存储器(可以通过拨码和按键读入指令)、控制器、内部寄存器、内存以及ALU构成。

设计过程重点考虑如下事项:读/写寄存器,读/写存储器以及执行指令。

通过执行读入的指令以及编写好的求两个数的最大公约数的程序来测试该系统的功能。

2。

2总体框图2。

2.1系统总体框图由设计思路,可绘制如下的简单CPU系统总体框图:最终在quartusII中连接好的CPU系统图如下所示(其中的AC C属于ALU部件):2.2。

2 系统状态转移图如上图,系统共有3个状态:S0、S1、S2.分别为S0:在这一状态,通过拨码和按键录入要执行的指令.S1:在这一状态,CPU执行程序,即S0录入的指令.S2:在这一状态,CPU执行完全部程序,等待再次执行或等待录入指令.2。

2。

3 求解最大公约数的程序框图设a,b为给定的两个整数,用辗转相减法求解他们的最大公约数:2。

3 分块设计2.3。

1 DIV(分频器)DIV将电路板所提供的时钟分频,产生CPU工作所需要的时钟以及数码管扫描所需要的时钟.2.3。

2MCU (控制器)MCU用来产生系统内部所有寄存器、运算单元所需的控制信号,以及执行各条指令所需要的微操作。

它是整个系统设计的核心所在。

2。

3.3 ALU(算术逻辑运算单元)ALU完成数据的算术和逻辑运算.ALU有5个输入端和2个输出端,其中一个操作数固定来自累加器acc(具体编程时可用变量或信号表示),另一个操作数来自端口mbr_in(通过数据总线接到寄存器MBR)。

8位CPU的设计

8位CPU的设计一、设计的任务与要求计算机的核心部件CPU通常包含运算器和控制器两大部分。

组成CPU的基本部件有运算部件,寄存器组,微命令产生部件和时序系统等。

这些部件通过CPU内部的总线连接起来,实现它们之间的信息交换。

1.设计目的(1).深入理解基本模型计算机的功能、组成知识;(2).深入学习计算机各类典型指令的执行流程;(3).学习微程序控制器的设计过程和相关技术,掌握LPM_ROM的配置方法。

(4).在掌握部件单元电路实验的基础上,进一步将单元电路组成系统,构造一台基本模型计算机。

(5).定义五条机器指令,并编写相应的微程序,上机调试,掌握计算机整机概念。

掌握微程序的设计方法,学会编写二进制微指令代码表。

(6).通过熟悉较完整的计算机的设计,全面了解并掌握微程序控制方式计算机的设计方法。

2.设计原理在部件实验过程中,各部件单元的控制信号是人为模拟产生的,而本实验将能在微过程控制下自动产生各部件单元控制信号,实现特定的功能。

实验中,计算机数据通路的控制将由微过程控制器来完成,CPU从内存中取出一条机器指令到指令执行结束的一个指令周期,全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。

11该CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器R0~R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。

图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。

虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。

二、单元电路设计1、运算部件运算部件的任务是对操作数进行加工处理。

主要由三部分组成:(1) 输入逻辑。

简单的CPU设计

CPU 设计10 计算机科学与技术姓名:谢xx学号:201040200xx一.非常简单的CPU设计规范:1.确定CPU的用途:该CPU的字长为8位,寻址范围为64个字节,并且要求能实现4条简单的指令。

2.确定ISA:要实现的指令集如下:要实现该CPU的功能,还需要一些寄存器完成取指,译码和执行的步骤:AR(地址寄存器)—6位,由A[7..0]向存贮器提供地址PC (程序计数器) —6位,指出下一条指令的地址DR (数据寄存器) —8位,通过D[7..0]从存贮器接收指令和数据IR (指令寄存器) —2位,存放从存贮器中取回的指令的操作码部分3.为CPU设计状态图:为了确定CPU的状态图,需对每条指令作如下分析:①从存贮器中取指令②指令译码③指令执行二.从存贮器中取指令:⑴原理:根据冯•诺依曼型的原理(指令在存贮器中顺序存放••••••),在CPU能执行指令之前,它必须将这条指令从存贮器中取出,CPU通过执行如下的操作序列完成这个任务:①选择存贮单元由A[5..0]确定②对A[5..0]译码、延迟并向存贮器中发一个信号,使存贮器将此指令输出到它的输出引脚。

这些引脚与CPU的D[7..0]相连接。

CPU从这些引脚读入数据。

⑵具体的操作①要取的指令的地址存放在程序计数器(PC)中。

由于A[5..0]从地址寄存器AR中。

这样,取指令周期的第一个状态就是:FETCH1:AR←PC这一状态的意义是当FETCH为真时,把PC的值送到AR,执行微操作AR←PC,以下同理。

②CPU必须存贮器中读取指令。

为此CPU必须发一个READ信号到存贮器的RD端使存贮器将数据送到D[7..0]上。

同时,CPU读进该数据并放到DR 中,因为DR是用来访问存贮器的唯一寄存器。

同时还实现微操作PC←PC+1,为取下一条指令作准备。

FETCH2:DR←M,PC←PC+1③作为取指令的一部分,CPU还必须完成两件事。

•DR的高2位拷贝到IR,母的是确定指令的功能(即将指令的操作码读入IR)·DR的第六位拷贝到AR。

中山大学计算机组成原理实验单周期CPU设计

中⼭⼤学计算机组成原理实验单周期CPU设计《计算机组成原理实验》实验报告(实验三)学院名称:数据科学与计算机学院专业(班级):学⽣姓名:学号:时间:2019 年11 ⽉8 ⽇成绩:实验三:单周期CPU设计与实现⼀.实验⽬的(1) 掌握单周期CPU数据通路图的构成、原理及其设计⽅法;(2) 掌握单周期CPU的实现⽅法,代码实现⽅法;(3) 认识和掌握指令与CPU的关系;(4) 掌握测试单周期CPU的⽅法。

⼆.实验内容设计⼀个单周期CPU,该CPU⾄少能实现以下指令功能操作。

指令与格式如下:==> 算术运算指令加“加”运算。

加“加”运算。

==> 逻辑运算指令加“与”运算。

功能:GPR[rt] ←GPR[rs] or zero_extend(immediate)。

==>移位指令==>⽐较指令==> 存储器读/写指令==> 分⽀指令else pc ←pc + 4特别说明:offset是从PC+4地址开始和转移到的指令之间指令条数。

offset符号扩展之后左移2位再相加。

为什么要左移2位?由于跳转到的指令地址肯定是4的倍数(每条指令占4个字节),最低两位是“00”,因此将offset放进指令码中的时候,是右移了2位的,也就是以上说的“指令之间指令条数”。

else pc ←pc + 4(16)bltz rs, offsetelse pc ←pc + 4。

==>跳转指令(17)j addr说明:由于MIPS32的指令代码长度占4个字节,所以指令地址⼆进制数最低2位均为0,将指令地址放进指令代码中时,可省掉!这样,除了最⾼6位操作码外,还有26位可⽤于存放地址,事实上,可存放28位地址,剩下最⾼4位由pc+4最⾼4位拼接上。

==> 停机指令功能:停机;不改变PC的值,PC保持不变。

三.实验原理单周期CPU指的是⼀条指令的执⾏在⼀个时钟周期内完成,然后开始下⼀条指令的执⾏,即⼀条指令⽤⼀个时钟周期完成。

MIPS指令单周期CPU设计

rd rs rt imm

sw rt rs imm Addr = R[rs] + SignExt(imm) MEM[Addr] = R[rt]

PC

Register File

ALU

+4

Data memory

4. MIPS指令——BEQ

比较指令BEQ

– beq rs rt imm

Phase 5: Register Write (WB for “write back”)

– Write the instruction result back into the Register File – Those that don’t (e.g. sw, j, beq) remain idle or skip this phase

– if R[rs] = R[rt] – then PC (PC +4)+ SignExt(imm) – Else PC PC+4

instruction memory rd rs rt imm MUX

PC

Register File

ALU

+4

Data memory

5. MIPS指令——Jump

Data memory

rd rs rt

Register File

PC

单周期CPU设计思路

指令的行

– 显然要设计一个时序逻辑电路 – 一条指令用一个CPU周期完成

执行步骤的实现

– 取指:从指令存储器中读指令(地址:PC)

– 读出一或两个源寄存器的值(寄存器组)

– 进行指令规定的运算(ALU) – 读/写数据存储器

– Zero extend imm16? – Pass imm16 to input of ALU? – Write result to rt?

计算机组成原理课程设计(中央处理器--微程序控制器设计)

“计算机组成原理”课程设计报告微程序控制器的设计一、设计思路按照要求设计指令系统,该指令系统能够实现数据传送,进行加、减运算和无条件转移,具有累加器寻址、寄存器寻址、寄存器间接寻址、存储器直接寻址、立即数寻址等五种寻址方式。

从而可以想到如下指令: (1)24位控制位分别介绍如下:位控制位分别介绍如下: XRD XRD :: 外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

定外设读数据。

EMWR EMWR:: 程序存储器EM 写信号。

写信号。

EMRD EMRD:: 程序存储器EM 读信号。

读信号。

PCOE PCOE:: 将程序计数器PC 的值送到地址总线ABUS 上。

上。

EMEN EMEN:: 将程序存储器EM 与数据总线DBUS 接通,由EMWR 和EMRD 决定是将DBUS 数据写到EM 中,还是从EM 读出数据送到DBUS DBUS。

IREN IREN:: 将程序存储器EM 读出的数据打入指令寄存器IR 和微指令计数器uPC uPC。

EINT EINT:: 中断返回时清除中断响应和中断请求标志,便于下次中断。

中断返回时清除中断响应和中断请求标志,便于下次中断。

ELP ELP:: PC 打入允许,与指令寄存器的IR3IR3、、IR2位结合,控制程序跳转。

转。

MAREN MAREN:将数据总线:将数据总线DBUS 上数据打入地址寄存器MAR MAR。

MAROE MAROE:将地址寄存器:将地址寄存器MAR 的值送到地址总线ABUS 上。

上。

OUTEN OUTEN:将数据总线:将数据总线DBUS 上数据送到输出端口寄存器OUT 里。

里。

STEN STEN:: 将数据总线DBUS 上数据存入堆栈寄存器ST 中。

中。

RRD RRD:: 读寄存器组读寄存器组R0-R3R0-R3,寄存器,寄存器R?R?的选择由指令的最低两位决定。

的选择由指令的最低两位决定。

的选择由指令的最低两位决定。

简单CPU设计

程序计数器用于提供指令地址,以便读取指令,指令按地址顺序存放在存储器中。有两种途径

可形成指令地址:其一是顺序执行的情况,其二是遇到要改变顺序执行程序的情况,例如执行 JMP

指令后,需要形成新的指令地址。

复位后,指令指针为零,即每次 CPU 重新启动将从 ROM 的零地址开始读取指令并执行。每条指

令执行完需 1 个时钟,这时 pc_addr 已被增 1,指向下一条指令。如果正执行的指令是跳转语句,这

load_ir 信号控制。load_ir 信号通过 ena 口输入到指令寄存器。复位后,指令寄存器被清为零。

Verilog 代码:

module

register(opcode,ir_addr,data,ena,clk,rst);

4

output [2:0] opcode; output [4:0] ir_addr; input [7:0] data; input ena, clk, rst; reg [2:0] opcode; reg [4:0] ir_addr;

end

LDA =3'b101,

LDA: alu_out<=data;

STO =3'b110,

STO: alu_out<=accum;

JA =3'b111;

JA: alu_out<=accum;

default: alu_out<=8'bxxxx_xxxx;

assign zero=!accum;

endcase

output [7:0]alu_out;

SUB: alu_out<=accum-data;

output zero,bz;

MUL:begin

《计算机组成原理》6-CPU设计

6.1.2 CPU组成——CPU内部数据通路

CPU 运算器

寄存器

中断

系统

CU

时序系统

数

地

控

据

址

制

线

线

线

在确定一台计算机的总体结构的时候,主要考 虑这样以下问题:

设置哪些部件; 各部件间如何传递信息(即数据通路); 主机与外围设备之间如何实现信息传送; 如何形成微操作命令序列。 前三个问题于机器指令系统设计有密切的关系; 后一个问题涉及到设计策略,其中,数据通路结构 是总体结构设计的核心。

但这种寄存器结构使所需单元器件与连接线增多, 不利于集成度的提高。

6.1.2 CPU组成——CPU典型内部数据通路

M

移位器

D R

ALU

RN

...

锁存器

锁存器

R2

M A

R1

R

IR

PC

状

CU

…

态 信

时钟

…

息

控制信号

3)单组内总线、集成寄存器结构。为了提高寄存 器的集成度,常将寄存器组制作成为小型半导体存储 器结构,一个存储单元就相当于一个寄存器。

6.1.2 CPU组成——CPU典型内部数据通路

2)单组内总线、分立寄存器结构。它的特点是 寄存器分别独立设置,采用一组单向的数据总线, 以ALU为内部数据传送通路的中枢。由于各寄存器在 物理上彼此分立,它们的输出端均与ALU输入端的多 路选择器相连(MAR除外因为它的特殊作用使得它 只能接收地址,传送给主存),多路选择器可以采 用与或逻辑,在同一时刻最多可以选择两路输入, 送入ALU进行相应运算处理。寄存器的数据输入来自 CPU内部总线,由于寄存器彼此分离,只要发出相 应的同步打入脉冲,即可使内总线同时将数据打入 一个或多个寄存器。

实验六_CPU_微程序控制器实验

CPU__微程序控制器实验实验目的1.理解微程序控制器的控制原理2.进一步掌握指令流程和功能3.了解掌握微程序控制器的设计思路和方法实验原理微程序控制器的设计思想是由英国剑桥大学的威尔克斯(Wilkes)教授于1951年提出来的, 即将机器指令的操作(从取指令到执行)分解成若干个更基本的微操作序列, 并将有关的控制信号(微命令)按照一定的格式编成微指令, 存放到一个只读存储器中, 当机器运行时, 一条一条地读出这些微指令, 从而产生全机所需要的各种操作控制信号, 使相应部件执行所规定的操作。

微指令格式:N _µA 0N _µA 1N _µA 2N _µA 3N _µA 4P 0P 1P 2P C _i n cl j _i n s t r u c tc _z _j _f l a gl d _I Ro p _c o d e 0o p _c o d e 1o p _c o d e 2c h a n g e _zc h a n g e _cD R W rs e l _m e m d a t aM e m _W r i t e1234567891011121314151617181920D W _i n s t r u c t实验步骤(1)实验台设置成FPGA-CPU 独立调试模式, REGSEL=0、CLKSEL=1.FDSEL=0.使用实验台上的单脉冲, 即STEP_CLK 短路子短接, 短路子RUN_CLK 断开;(2)将设计在Quartus II 下输入, 编译后下载到TEC-CA 上的FPGA 中;(3)按复位键后, 拨动实验台上的开关SD5~SD0, 改变IR[15…12]、进位标志C 和结果为0标志Z, 观察指示灯R15~R0、A4~A0、A12~A8、A14和A15显示的信号, 追踪每条指令的执行过程并把相应数据填在表6-1中。

(4)观察每条指令的执行过程, 每个节拍进行的微操作和微操作控制信号。

中央处理器CPU——控制器

中央处理器CPU——控制器控制器是计算机系统的指挥中⼼,控制器的主要功能有:1)从主存中取出⼀条指令,并指出下⼀条指令在主存中的位置。

2)对指令进⾏译码或测试,产⽣相应的操作控制信号,以便启动规定的动作。

3)指挥并控制CPU、主存、输⼊和输出设备之间的数据流动⽅向。

控制单元的输⼊与输出:输⼊:(1)指令寄存器:OP(IR)⼀>CU控制信号的产⽣与操作码有关(2)时钟:⼀个时钟脉冲发⼀个操作命令或⼀组需要同时执⾏的操作命令(3)标志:如条件转移指令,根据相应的标志位决定下⼀步操作(4)外来信号:如:中断请求信号INTR 总线请求信号HRQ输出:(1)CPU内部的控制信号寄存器之间的数据传输、pc的修改、控制ALU进⾏相应的运算(2)到控制总线的控制信号到存储器:访存控制信号、读命令、写命令到I/O设备:访问I/O设备的控制信号中断响应信号INTA、总线响应信号HLDACPU的控制⽅式:产⽣不同微操作命令序列所⽤的时序控制⽅式。

1.同步控制⽅式整个系统所有的控制信号均来⾃⼀个统⼀的时钟信号。

同步控制万式的优点是控制电路简单,缺点是运⾏速度慢。

2.异步控制⽅式异步控制⽅式不存在基准时标信号。

各部件按⾃⾝固有的速度⼯作,通过应答⽅式进⾏联络。

异步控制⽅式的优点是运⾏速度快,缺点是控制电路⽐较复杂。

3·联合控制⽅式对各种不同的指令的微操作实⾏⼤部分采⽤同步控制、⼩部分采⽤异步控制的办法。

安排微操作时序的原则原则⼀:微操作的先后顺序不得随意更改原则⼆:被控对象不同的微操作尽量安排在⼀个节拍内完成原则三:占⽤时间较短的微操作尽量安排在⼀个节拍内完成并允许有先后顺序微命令<微指令<微程序=⼀条机器指令微命令:控制部件通过控制线向执⾏部件发出各种控制命令,是最⼩单位相容性微命令互斥性微命令微操作:执⾏部件接受微命令后所执⾏的操作微指令:在机器的⼀个CPU周期中,⼀组实现⼀定操作功能的微命令的组合微操作码+微地址码 00010000微程序:⼀条机器指令的功能是由许多条微指令组成的序列来实现的例如:取指微指令(操作相同)硬布线原理:微操作控制信号由组合逻辑电路根据当前指令码,状态和时序,即时产⽣微程序原理:将控制器所需的微命令以代码形式编成微指令,存⼊⼀个由ROM构成的控制存储器(CM)中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《计算机组成与结构》课程设计报告题目:CPU控制器设计院(系):信息科学与工程专业班级:学生姓名:学号:指导教师:顾兵20 15 年 06 月 15 日至20 15 年 06 月 26 日华中科技大学武昌分校制计算机组成与结构课程设计任务书目录目录 (i)1需求与总体设计 (1)1.1设计任务及功能要求 (1)1.1.1设计任务 (1)1.1.2功能要求 (1)1.2总体设计 (1)1.2.1总体设计原理 (1)1.2.2总体设计说明 (1)1.3总体框图 (2)2详细设计与实现 (3)2.1方案设计与实现 (3)2.1.1输入与输出逻辑图 (3)2.1.2指令与控制信号真值表 (3)2.1.3控制器设计思路流程图 (4)2.2指令分析及逻辑电路图 (4)2.2.1 R-type型指令 (4)2.2.2 Ori指令 (5)2.2.3 lw指令 (6)2.2.4 sw指令 (7)2.2.5 branch指令 (7)2.2.6 Jump指令 (8)2.2.7逻辑电路图 (9)2.3 VHDL代码分析及实现 (10)2.3.1代码分析 (10)2.3.2代码实现 (11)3电路仿真调试 (14)3.1代码仿真 (14)3.2功能仿真及调试 (14)总结 (17)参考文献 (18)1需求与总体设计1.1设计任务及功能要求1.1.1设计任务通过对CPU的工作原理和逻辑功能的理解,运用VHDL硬件描述语言实现能支持基本指令的单时钟控制器设计,采用QUARTUS II软件设计仿真和调试完成。

1.1.2功能要求1.运用VHDL实现能支持基本指令的单时钟控制器设计与调试。

1>实现能够执行R类型、ori、addiu、lw、sw、beg以及jump指令的单时钟控制器使其能够支持基本的指令。

2>实现cpu的控制。

2.采用QUARTUS II软件设计仿真和调试完成。

1.2总体设计1.2.1总体设计原理CPU每次从存储器读取一条指令后,PC指针指向正在取值的指令并存放到指令寄存器IR中,IR将指令送到控制器,控制器对指令进行译码,判断指令类型,从而生成相应指令对应的的数据通路控制信号,指挥整个CPU的运转。

控制单元主要包含一个指令译码器,输入的是指令操作码op(R-型指令还包括功能码func),输出的是控制信号。

所以,控制单元的设计过程如下。

1>根据每条指令的功能,分析控制信号的取值,并在表中列出。

2>根据列出的指令和控制信号的关系,写出每个控制信号的逻辑表达式。

1.2.2总体设计说明1)指令格式如下:MIPS指令分为三种指令:R_Type,I_Type,J_TypeR_Type 如:加法ADD 减法SUBSTRACT加法指令的汇编格式add rd, rs, rt加法指令的汇编格式sub rd, rs, rt图1.1 指令格式2)设计步骤:第一步:确定每个元件所需控制信号的取值。

第二步:汇总所有指令所涉及到的控制信号,生成一张反映指令与控制信号之间关系的表。

第三步:根据表得到每个控制信号的逻辑表达式,据此设计控制器电路。

1.3总体框图总体设计框图如图1.1:图1.2 控制器总体框图2详细设计与实现2.1方案设计与实现2.1.1输入与输出逻辑图由cpu控制器的功能原理得出输入与输出逻辑图如下:图2.1 输入与输出逻辑图2.1.2指令与控制信号真值表查阅得到指令与控制信号真值表如下:表2.1指令与控制信号真值表2.1.3控制器设计思路流程图根据各指令控制信号真值表可得主控制器设计思路流程图如图2.2所示。

图2.2 设计思路流程图2.2指令分析及逻辑电路图2.2.1 R-type型指令图2.3是R-型指令的执行过程示意图,其中粗线描述了R-型指令的数据在数据通中的执行路径:Register File(Rs,Rt)→busA,busB→ALU→Register File(Rd)。

图2.3 R-型指令执行过程控制信号的取值分析如下。

Branch=Jump=0:因为是非分支指令、非无条件跳转指令。

RegDst=1:因为R-型指令的目的寄存器为Rd。

ALUSrc=0:保证选择busB作为ALU的B口操作数。

MemtoReg=0:保证选择ALU结果送到目的寄存器。

RegWr=1:保证在下个时钟到来时,在不发生溢出的情况下结果被写到目的寄存器。

MemWr=0:保证下一个时钟到来时,不会有信息写到数据存储器。

ExtOp=x:因为ALUSrc=0,所以扩展器Extender的值不会影响执行结果,故ExtOp 取0或1都无所谓。

2.2.2 Ori指令指令完成的功能:R[rt] ←R[rs] op ZeroExt[imm16]]图2.4 Ori的控制信号控制信号的取值分析如下。

分支指令和跳转指令都为零Branch=jump=0因为是非分之指令,非跳转指令。

RegDst=1:因为Ori指令的目的寄存器为Rt。

ALUSrc=1:保证选择busB作为ALU的A口操作数。

ALUctr=or。

MemtoReg=0:保证选择ALU结果送到目的寄存器。

RegWr=1:保证在下个时钟到来时,在不发生溢出的情况下结果被写到目的寄存器。

MemWr=0:保证在下个时钟到来时,不会有信息写到数据存储器。

ExpOp=x:因为ALUSrc=0,所以扩展器Extender的值不会影响执行结果,故ExtOP 取0或1都无所谓。

2.2.3 lw指令指令完成的功能:R[rt] ←M[ R[rs] + SignExt[imm16] ]图2.5 lw的控制信号控制信号的取值分析如下。

分支指令和跳转指令都为零Branch=jump=0因为是非分之指令,非跳转指令。

RegDst=1:因为lw指令的目的寄存器为Rt。

ALUSrc=1:保证选择busA作为ALU的A口操作数。

ALUctr=add。

MemtoReg=1:保证选择存储器结果送到目的寄存器。

RegWr=1:保证在下个时钟到来时,在不发生溢出的情况下结果被写到目的寄存器。

MemWr=0:保证在下个时钟到来时,不会有信息写到数据存储器。

ExpOp=1:因为要利用扩展器Extender进行扩展。

2.2.4 sw指令指令完成的功能:rt, rs, imm16图2.6 sw的控制信号控制信号的取值分析如下。

分支指令和跳转指令都为零Branch=jump=0因为是非分之指令,非跳转指令。

RegDst=x:因为不会写到寄存器。

ALUSrc=1:保证选择busA作为ALU的A口操作数。

ALUctr=add。

MemtoReg=x:有没有结果送到目的寄存器无所谓。

RegWr=0:不会有结果被写到目的寄存器。

MemWr=1:保证在下个时钟到来时,会有信息写到数据存储器。

ExpOp=1:因为要利用扩展器Extender进行扩展。

2.2.5 branch指令指令完成的功能:rs, rt, imm16图2.7 branch的控制信号控制信号的取值分析如下。

分支指令置位,跳转指令清零Branch=1,jump=0因为是分之指令,非跳转指令。

寄存器写信号RegDst=x:因为不会写到寄存器。

算术逻辑单元选择信号ALUSrc=0:保证选择busB作为ALU的B口操作数。

算术逻辑单元控制信号ALUctr=sub。

存储器写寄存器信号MemtoReg=x:有没有结果送到目的寄存器无所谓。

寄存器写信号RegWr=0:不会有结果被写到目的寄存器。

存储器写信号MemWr=0:保证在下个时钟到来时,不会有信息写到数据存储器。

符号扩展信号ExpOp=x:因为不需要利用扩展器Extender进行扩展。

2.2.6 Jump指令指令完成的功能:j target图2.8 jump指令的控制信号控制信号的取值分析如下。

分支指令清零,跳转指令置位Branch=0,jump=1因为是非分之指令,跳转指令。

目的寄存器RegDst=x:因为不会写到寄存器。

算术逻辑单元ALUSrc=x:保证选择busB作为ALU的A口操作数。

算术逻辑单元控制信号ALUctr=x。

存储器到寄存器信号MemtoReg=x:有没有结果送到目的寄存器无所谓。

寄存器写信号RegWr=0:不会有结果被写到目的寄存器,避免寄存器在指令执行过程时被写入任何结果。

存储器写信号MemWr=0:保证在下个时钟到来时,不会有信息写到数据存储器。

符号扩展信号ExpOp=x:因为要利用扩展器Extender进行扩展。

2.2.7逻辑电路图图2.9控制器逻辑电路图2.3 VHDL代码分析及实现2.3.1代码分析1)实体一个VHDL实体指定了实体的名称,实体的端口和实体所关联的信息。

所有的设计都是用一个或多个实体创建起来的。

实体是设计的最基本模块。

设计的最高层次是顶层设计。

如果设计是分等级的,那么顶层的描述将包含较低层次的描述。

这些较低层次的描述将是被包含在顶层实体描述中的较低层次的实体。

关键字ENTITY表示这是一个实体语句的开始。

它指定了端口数量,端口方向和端口类型。

实体是描述VHDL模型的接口。

entity main_controller isport(op: in std_logic_vector(5 downto 0);RegWr,ALUSrc,RegDst,MemtoReg,MemWr,Branch,Jump,ExtOp,ALUOP0,ALUOP1,ALUOP2,RType: out std_logic);end main_controller;2)结构结构体描述实体的基本功能,并有对实体的行为进行建模的语句。

所有的能被仿真的实体都有一个结构体描述,这个结构体描述了实体的行为。

一个单一的实体可以有多个结构体,一个结构体可能是一种行为,而令一个结构体可能是一个设计的结构描述。

一个结构体总是与一个实体和描述这个实体的行为相关联。

关键字ARCHITECTURE表示这条语句描述了一个实体的结构体。

这个结构体的名称是behav,所描述的实体称为main_controller。

architecture behav of main_controller issignal iRtype, ori,addiu,lw,sw,beq,jump1: std_logic;beginprocess(op)beginend process;process(iRtype, ori,addiu,lw,sw,beq,jump1)end process;end behav;2.3.2代码实现library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity main_controller isport(op: in std_logic_vector(5 downto 0);RegWr,ALUSrc,RegDst,MemtoReg,MemWr,Branch,Jump,ExtOp,ALUOP0,ALUOP1,ALUOP2,RType: out std_logic);end main_controller;architecture behav of main_controller issignal iRtype, ori,addiu,lw,sw,beq,jump1: std_logic;beginprocess(op)begincase op iswhen "000000" =>iRtype <= '1';ori<='0' ; addiu <= '0'; lw <= '0'; sw <= '0'; beq <= '0'; jump1 <= '0';when "001101" =>iRtype <= '0';ori<='1' ; addiu <= '0'; lw <= '0'; sw <= '0'; beq <= '0'; jump1 <= '0';when "001001" =>iRtype <= '0';ori<='0' ; addiu <= '1'; lw <= '0'; sw <= '0'; beq <= '0'; jump1 <= '0';when "100011" =>iRtype <= '0';ori<='0' ; addiu <= '0'; lw <= '1'; sw <= '0'; beq <= '0'; jump1 <= '0';when "101011" =>iRtype <= '0';ori<='0' ; addiu <= '0'; lw <= '0'; sw <= '1'; beq <='0'; jump1 <= '0';when "000100" =>iRtype <= '0';ori<='0' ; addiu <= '0'; lw <= '0'; sw <= '0'; beq <= '1'; jump1 <= '0';when "000010" =>iRtype <= '0';ori<='0' ; addiu <= '0'; lw <= '0'; sw <= '0'; beq <= '0'; jump1 <= '1';when others=>end case;end process;process(iRtype, ori,addiu,lw,sw,beq,jump1)beginif(iRtype = '1' )thenRegDst<= '1' ; ALUOP0<= '1' ; ALUOP2<= '0'; RType<= '1' ;RegWr <= '1';ALUSrc <= '0';MemtoReg<= '0';MemWr<= '0';Jump<= '0';Branch<= '0';ExtOp<= '0';ALUOP1<= '0';elsif(ori='1')thenALUOP1<= '1';RegWr <= '1';ALUSrc <= '1';RegDst<= '0' ; ALUOP0<= '0' ; ALUOP2<= '0'; RType<= '0' ;MemtoReg<= '0';MemWr<= '0';Jump<= '0';Branch<= '0';ExtOp<= '0';elsif(addiu ='1')thenRegWr <= '1';ALUSrc <= '1';ExtOp<= '1';ALUOP1<= '0';RegDst<= '0' ; ALUOP0<= '0' ; ALUOP2<= '0'; RType<= '0' ;MemtoReg<= '0';MemWr<= '0';Jump<= '0';Branch<= '0';elsif( lw ='1' )thenRegWr <= '1';ALUSrc <= '1';MemtoReg<= '1';ExtOp<= '1';ALUOP1<= '0';RegDst<= '0' ; ALUOP0<= '0' ; ALUOP2<= '0'; RType<= '0' ;MemWr<= '0';Jump<= '0';Branch<= '0';elsif(sw ='1')thenMemWr<= '1';ALUSrc <= '1';ExtOp<= '1';ALUOP1<= '0';RegWr <= '0';RegDst<= '0' ; ALUOP0<= '0' ; ALUOP2<= '0'; RType<= '0' ;MemtoReg<= '0';Jump<= '0';Branch<= '0';elsif(beq ='1')thenBranch<= '1'; ALUOP2<= '1';ALUOP1<= '0';RegWr <= '0';ALUSrc <= '0';RegDst<= '0' ; ALUOP0<= '0' ; RType<= '0' ;MemtoReg<= '0';MemWr<= '0';Jump<= '0';ExtOp<= '0';elsif(jump1='1')thenJump<= '1';ALUOP1<= '0';RegWr <= '0';ALUSrc <= '0';RegDst<= '0' ; ALUOP0<= '0' ;ALUOP2<= '0'; RType<= '0' ;MemtoReg<= '0';MemWr<= '0';Branch<= '0';ExtOp<= '0';end if;end process;end behav;3电路仿真调试3.1代码仿真将VHDL语言编写的代码在quartus5.0上进行仿真,如图3.1所示。