F28335BOOTROM引导模式和程序

TMS320F28335核心板:Core28335软件调试指南

如果出现下图所示,则表示仿真器和开发板已连接成功。

第三步: 新建一个工程,如下图

第四步: 选择路径,输入工程项目名,并确定,则如下图所示

第五步: 添加源文件,添加 CMD 文件,如下图所示: 注意:源文件有*.c 文件,也有*.asm 文件

添加 CMD 文件跟添加源文件的方法相似,在这里不在赘述。添加完成后整个工程如下所示:

版权© 2013,株洲市索思达电子有限公司

前言

阅前必读

简介:

本 用 户指 南是 TMS320F28335 DSP 处 理 模板 硬 件使 用说 明书 ,详 细描 述 了

28335实用版 的硬件构成、原理,以及它的使用方法和编程指导。

保修:

所有由株洲市索思达电子有限公司生产制造的硬件和软件产品, 保修期为从发货 之日起一 年。 在保修期内由于产品质量原因引起的损坏, 株洲市索思达电子有限公司负责免费维修。当在 保修期内软件进行了升级, 株洲市索思达电子有限公司将免费提供。

参考资料:

TMS320F28x DSP CPU and Instruction Set Reference Guide (文献号 SPRU430) : 介 绍 TMS320F28x 系列 DSP 的 CPU 结构、指令组、流水线及中断。 TMS320C28x Floating Point Unit and Instruction Set Reference Guide (文献号 SPRUEO2)介绍浮点单元和FPU指令集。 TMS320x28xx, 28xxx Peripheral Reference Guide(文献号 绍 TMS320F28x 系列 DSP 的外设。 TMS320x2833x 献 号 System Control and Interrupts Reference Guide ( 文 SPRU566):介

F28335各个程序代码简单描述

mcbsp_loopback_interrupts

McBSP通信实验(通过中断方法自发自收)

mcbsp_spi_loopback

McBSP作为SPI通信实验

sci_autobaud

SCI通信实验1(自动波特率)

sci_echoback

SCI通信实验2

scia_loopback

CAN通信实验(自发自收)

ecap_apwm

CAP实验(APWM)

ecap_capture_pwm

CAP实验

epwm_deadband

PWM实验(带死区)

epwm_dma

PWM实验(通过DMA传输数据)

epwm_timer_interrupts

PWM实验(定时中断)

epwm_trip_zone

PWM跳闸保护实验

epwm_up_aq

PWM向上计数实验

epwm_updown_aq

PWM中心对称计数实验

eqep_freqcal

QEP脉冲频率测量实验

eqep_pos_speed

QEP位置速度脉冲测量实验

external_interrupt

外部中断实验

external_interrupt_hanyuan

外部中断实验

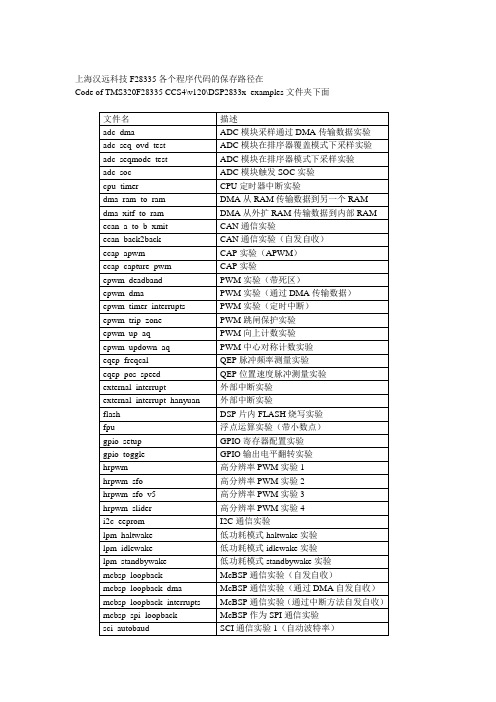

上海汉远科技F28335各个程序代码的保存路径在

Code of TMS320F28335 CCS4\v120\DSP2833x_examples文件夹下面

文件名

描述

adc_dma

ADC模块采样通过DMA传输数据实验

adc_seq_ovd_test

ADC模块在排序器覆盖模式下采样实验

adc_seqmode_test

dsp tms320f28335 在线升级资料4(参考论坛博客)

TMS320C6701(以下简称C6701)是一款浮点运算DSP,适用于需要大量运算且实时性要求高的场合,如导航解算等。

在浮点DSP芯片中,C6701是一款可应用于恶劣环境并具有高可靠性的产品,因此该型DSP芯片虽然推出较早,却依然在某些领域具有重要应用价值。

DSP应用程序需脱离开发系统独立工作,在实时DSP应用系统中,通常将应用程序存储在外部非易失性存储器(如FLASH、E EPROM、PROM等)中。

系统上电后,DSP将外部程序存储器的程序代码加载到可高速存取的RAM中,加载完成后自动跳转到零地址开始运行。

因此DSP程序烧写及自动加载是实时DSP系统设计的重要部分。

本文采用的烧写方法不需要格式转换到外部辅助设备,同时DSP程序不再进行二次加载,简化了烧写及程序自动加载的过程。

1 加载方案及电路设计1.1 外围电路设计C6701有三种加载模式:不加载(No Boot)、ROM加载(Rom Boot)、主机加载(Host Boot)。

这三种加载模式由C6701的BOOTMODE[4:0]引脚电平设定,由这5个引脚的设置共同决定使用何种存储空间映射模式。

在恶劣环境及高可靠应用场合中,可使用不加载方式,也可使用程序从ROM中加载到DSP片外高可靠RAM存储器中的运行方式。

FLASH、EEPROM、PROM等程序存储芯片多为8位或16位,在高可靠应用环境中8位比较常见。

本文中设置BOOTMODE[4:0]为01010B,即程序由外部8位程序存储器加载到外部32位SRAM中,LENDIAN引脚接高电平。

外部程序存储器选用FLASH芯片AM29LV160,32位SRAM芯片选用ACT—S512K32V。

FLASH和SRAM芯片与C6701的硬件连接如图1和图2所示。

1.2 加载方案设计在BOOTMODE[4:0]为01010B的设置下,程序由外部8位程序存储器加载到外部32位SRAM中。

C6701具体加载过程为:DMA按默认时序从CE1地址(0x01000000)复制64 KB到零起始地址外部SRAM芯片中,加载完成后,从零地址处开始执行。

F28335手册

2 通道

CAN

2 通道

SPI

1 通道

IIC

1 通道

DMA

6 通道

看门狗电路

1个

Copyright 2009 © yanxu. All rights recerved 3

2 产品说明

YXDSP-F28335 实用开发板采用核心板与底板分拆模式。 产品图示如下:

南京研旭电气科技有限公司

BOOT ROM

8K ×16 位

OPT ROM

1K ×16 位

其中 FLASH、OPT ROM 受口令保护,可以保护用户程序。

片上外设

PWM

12 路

HRPWM

6路

QEP

2 通道

ADC

2×8 通道,12 位,80ns 转换时间,0—3V 输入量程

SCI

3 通道

MCBPS

脉冲宽度调制pwm是一种对模拟信号电平进行数字编码的方法其根据相应载荷的变化来调制晶体管栅极或基极的偏置来实现开关稳压电源输出晶体管或晶体管导通时间的改变这种方式能使电源的输出电压在工作条件变化时保持恒定是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术广泛应用在从测量通信到功率控制与变换的许多领域中

YXDSP-F28335 实用开发板 用户指南 V1.00

南京研旭电气科技有限公司

声明

南京研旭电气科技有限公司保留随时对其产品进行修改、改进和完善的权利,同时也 保留在不作任何通告的情况下,终止其任何一款产品的供应和服务的权利。用户在下订单 前应获取相关信息的最新版本,并验证这些信息是当前的和完整的。

版权©2009,南京研旭电气科技有限公司

Copyright 2009 © yanxu. All rights recerved 1

F28335BOOTROM引导模式和程序

在此模式下,引导ROM软件将针对28x操作配置器件,然后直接分支至闪存的0x33FFF6位置。此位置刚好是128位代码安全模块(CSM)密码位置之前。您需要预先在0x33FFF6位置处编写分支指令,以将代码执行重定向至定制的boot-loader或应用代码。

在仅有RAM的器件上,“引导至闪存”将跳转到保留存储器,因此不应当使用此选项。

对CSM密码读取完成后,初始化例程调用模式选择功能函数(SelectBoot),该函数根据GPIO的状态确定处理器引导的方式。一旦完成SelectMode将会把入口地址返回给初始化引导。然后初始化引导函数调用回复CPU寄存器的退出例程(ExitBoot)并退出到由引导模式确定的程序入口地址。

因此我们在使用SCI升级程序时可以分两个步骤,第一个步骤是我们需要一个Bootloader程序,第二个就是我们要升级的程序,BootLoader程序就是我们在选择引导SCI模式之后,SelectBoot之后通过串口加载的第一个程序,待ExitBoot之后会跳转到我们这个bootloader指定的地址开始执行(即将控制权交给我们的这个BootLoader程序),因此我们的BootLoader程序就肩负着串口接收我们的应用程序并将应用程序烧写到FLASH的任务。第二个就是我们的应用程序,这个跟平常的应用程序一样,没有任何区别。

{

//表示的是extended地址高位和低位

data[0] = fgetc(myFile);

data[1] = fgetc(myFile);

CharToByte(data,&addresslinearhigh);

data[0] = fgetc(myFile);

data[1] = fgetc(myFile);

F28335_DSP_烧写程序的方法

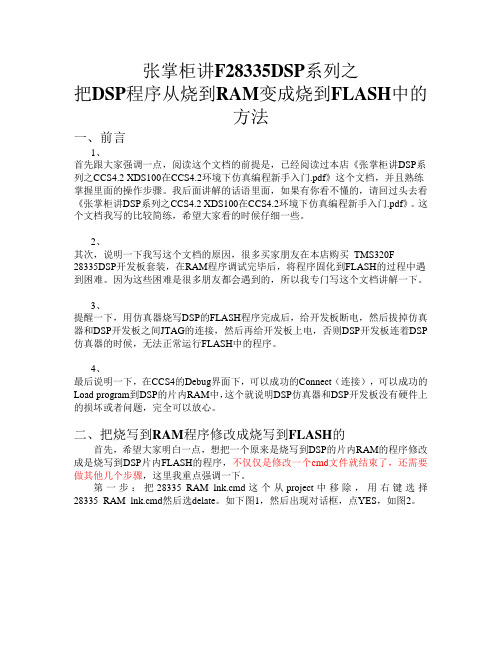

张掌柜讲F28335DSP系列之把DSP程序从烧到RAM变成烧到FLASH中的方法一、前言1、首先跟大家强调一点,阅读这个文档的前提是,已经阅读过本店《张掌柜讲DSP系列之CCS4.2 XDS100在CCS4.2环境下仿真编程新手入门.pdf》这个文档,并且熟练掌握里面的操作步骤。

我后面讲解的话语里面,如果有你看不懂的,请回过头去看《张掌柜讲DSP系列之CCS4.2 XDS100在CCS4.2环境下仿真编程新手入门.pdf》。

这个文档我写的比较简练,希望大家看的时候仔细一些。

2、其次,说明一下我写这个文档的原因,很多买家朋友在本店购买TMS320F 28335DSP开发板套装,在RAM程序调试完毕后,将程序固化到FLASH的过程中遇到困难。

因为这些困难是很多朋友都会遇到的,所以我专门写这个文档讲解一下。

3、提醒一下,用仿真器烧写DSP的FLASH程序完成后,给开发板断电,然后拔掉仿真器和DSP开发板之间JTAG的连接,然后再给开发板上电,否则DSP开发板连着DSP 仿真器的时候,无法正常运行FLASH中的程序。

4、最后说明一下,在CCS4的Debug界面下,可以成功的Connect(连接),可以成功的Load program到DSP的片内RAM中,这个就说明DSP仿真器和DSP开发板没有硬件上的损坏或者问题,完全可以放心。

二、把烧写到RAM程序修改成烧写到FLASH的首先,希望大家明白一点,想把一个原来是烧写到DSP的片内RAM的程序修改成是烧写到DSP片内FLASH的程序,不仅仅是修改一个cmd文件就结束了,还需要做其他几个步骤,这里我重点强调一下。

第一步:把28335_RAM_lnk.cmd这个从project中移除,用右键选择28335_RAM_lnk.cmd然后选delate。

如下图1,然后出现对话框,点YES,如图2。

图1图2第二步:右键选择project名称,然后选add file to project,如下图3,然后出现浏览框,在\Code of TMS320F28335 CCS4\v120\DSP2833x_common\cmd这个子文件夹下,选择F28335.cmd,点OK,至此可以在project的文件列表内看到F28335.cmd被添加到project中。

TMS320F28335经验若干要点

TMS320F28335经验若干要点TMS320F28335开发过程中常见问题总结1.SPI驱动TLE7241E出现返回值不对的问题。

主要是由于时序的不对,导致TLE7241E输入采样时数据还没有建立,所以TLE7241E 收到的命令不正确,所以返回值不正确。

2.SPI驱动EEPROM时,如果用金属物触到clock pin时,能正确运行,否则不能正确运行。

出现次问题也是由于时序的问题,金属物触到clock导致clock出现微小幅度的偏移,导致正好和eeprom 的时序对上,而不用金属物触碰时时序不正常,当使dsp MOSIpin数据发送提前半个周期后,eeprom工作正常。

3.示波器有时会导致显示的波形被消尖,所以用示波器测量时周期不能太大。

TMS320F28335笔记-I2C1.响应和非响应的区别是什么?关于i2c的响应问题:对于每一个接收设备(从设备,slaver),当它被寻址后,都要求在接收到每一个字节后产生一个响应。

因此,the master device 必须产生一个额外的时钟脉冲(第九个脉冲)用以和这个响应位相关联。

在这个脉冲期间,发出响应的从设备必须将SDA拉低并在时钟脉冲的高电平期间保持住。

这表示该设备给出了一个ACK。

如果它不拉低SDA 线,就表示不响应(NACK)。

另外,在从机(发送方)发送完最后一个字节后主设备(接收方)必须产生一个不响应位,用以通知从机(发送方)不要再发送信息了,这样从机就知道该将SDA释放了,而后,主机发出一个停止位给slaver。

总结下,i2c通讯中,SDA 和SCL 都是有主机控制的,从设备只是能够将SDA线拉低而已。

对于SCL线,从机是没有任何能力去控制的。

从机只能被动跟随SCL再说的清楚些:主机发送数据到从机的状态下:主机控制SCL信号线和SDA信号线,从机只是在SCL线为高的时候去被动读取SDA 线。

主机读取从机的数据:主机来发出时钟信号,从机只是保证在时钟信号为高电平的时候的SDA的状态而已。

绝密,DSPF28335实用板使用教程

绝密,DSPF28335实⽤板使⽤教程官⽅声明YXDSP-F28335系列开发板是南京研旭开发⽣产并直接进⾏销售及提供技术服务的产品,暂时未设置任何代理商。

如有其它任何⼚商或代理使⽤“YXDSP-F28335开发套件”的名义进⾏销售,均属于假冒产品。

南京研旭对您购买及使⽤此假冒产品过程中造成的所有损失均不承担任何责任。

官⽅指定销售⽹站:/doc/98ddcdb369dc5022aaea002f.html 中⽂名称:研旭商城官⽅指定销售⽹站:/doc/98ddcdb369dc5022aaea002f.html 中⽂名称:研旭淘宝商城YXDSP-F28335开发板是研旭电⽓科技有限公司⾃主研发的,针对⾼校、研究所和中⼩企业⼩批量设计的需求⽽研发的。

该开发板可以满⾜基于所有F28335开发时的所有应⽤。

YXDSP-F28335开发套件功能强⼤,代码丰富,⽅便使⽤。

在国内,我们的产品已经成为众多的国家级科研院所、⼤学、国家重点实验室、电⼒、通讯、⼯业、医疗类公司指定的开发⼯具。

TMS320F28335型数字信号处理器是TI公司的⼀款TMS320C28X系列浮点DSP控制器。

与以往的定点DSP相⽐,该器件的精度⾼,成本低,功耗⼩,性能⾼,外设集成度⾼,数据以及程序存储量⼤,A/D转换更精确快速等。

TMS320F28335具有150MHz的⾼速处理能⼒,具备32位浮点处理单元,6个DMA通道⽀持ADC、McBSP和EMIF,有多达18路的PWM输出,其中有6路为TI特有的更⾼精度的PWM输出(HRPWM),12位16通道ADC。

得益于其浮点运算单元,⽤户可快速编写控制算法⽽⽆需在处理⼩数操作上耗费过多的时间和精⼒,从⽽简化软件开发,缩短开发周期,降低开发成本。

采⽤六层核⼼板与底板的分拆形式,在听取⼴⼤DSP⼯程师意见的基础上,以保证DSP 能稳定独⽴运⾏、外设资源充分扩展为原则,优化结构设计,注重EMC处理,⽆论在设计还是在⼯艺上,均⽤⼼完成。

F28335BOOTROM引导模式和程序

28335使用串口烧写程序串口烧写是一种相对较方便的烧写方式,相对于仿真器或是CAN烧写,相对于仿真器或是USB转CAN的设备,串口是一种非常廉价的烧写方式,而且也不需要安装专业的集成开发环境CCS等,但是不能实现在线调试,因此也只适用于程序基本不用再调整或大批量的场合。

F28335的存储器映射图如下:BOOTROM 是一块8K X 16的只读存储器,位于地址空间0x3FE000~0x3FFFFF,片内BOOTROM在出厂时固化了引导加载程序以及定点和浮点数据表,片上BOOTROM的存储映射如下图所示:1.内BOOT ROM数学表:在BOOT ROM中保留了4K X 16位空间,用以存放浮点和IQ数据公式表,这些数据公式表有助于改善性能和节省SARAM空间。

向量表:CPU向量表位于ROM存储器0x3FE000~0x3FFFFF段内,如下图所示。

复位后,当VMAP=1,ENPIE=0(PIE向量表禁止)时,该向量表激活。

在内部BOOT ROM引导区中能够调用的唯一向量就是位于0x3FFFC0的复位向量。

复位向量在出厂时被烧录为直接指向存储在BOOT ROM 空间中的InitBoot函数,该函数用于开启引导过程。

然后通过通用I/O引脚上的检验判断,决定具体引导模式。

引导模式与控制引脚之间的关系如下图所示:Bootloader特性:Bootloader是位于片上引导ROM中的在复位后执行的程序,用于在上电复位后,将程序代码从外部源转移到内部存储器。

这允许代码暂时存储在掉电不丢失数据的外部存储器内,然后被转移到高速存储器中执行。

引导ROM中的复位向量将程序执行重定向至InitBoot函数。

执行器件初始化之后,bootloader将检查GPIO引脚的状态以确定您需要执行哪种引导模式。

这些选项包括:跳转至闪存、跳转至SARAM、跳转至OTP或调用其中一个片上引导加载例程。

完成选择进程后,如果已完成所需的引导加载,处理器将在所选引导模式确定的应用起点继续执行。

F28335BootROM笔记

SCI-A启动:

SCI启动将会被调用。但是,根据请求的波特率,该设备可能无法自动波特锁定。这种情况下bootROM软件将在自动波特锁定函数里无限循环下去。SCI-A启动完成后,用户应该检查丢失时钟状态并采取适当行动

eCAN-A启动:

eCAN bootloader狗模块

当直接执行:FLash、OTP memory、M0 single-access RAM(SARAM),或扩展接口XINTF时,看门狗不会被触发。

在其他启动模式,看门狗在启动之前被disable,在执行最后的目标地址之前再enable和clear。

解释:由代码可以看出,如果是其他启动模式,那么获取入口地址的操作就会进入另一个函数文件,时间很长,所以需要disable看门狗。

该函数还检查PLLSTS寄存器里面的时钟丢失探测bit(MCLKSTS),以确定PLL是否工作在limp模式。如果PLL工作在limp模式,启动模式选择函数依赖于启动模式选择来采用适当的行动:

boot to Flash、OTP、SARAM、I2C-A、SPI-A、XINTF和并口I/O:

这些模式行为正常。如果MCLKSTS位被置位,用户软件必须检查丢失时钟状态并采取适当行动。

OTP:one time programmable

DSP的寄存器详细信息包含在每个模块的独立PDF里面

IQ 数学表:

1,sin cos表。2,标准反转表。3,标准平方根表。 4,标准反正切表。5,舍入饱和表。6,指数最大最小表。7,指数系数表。

1.3 CPU向量表:0x3F FFC0 - 0x3F FFFF

bootloader的sourcecode入口地址定义:

Flash入口地址:0x33 FFF6。

dspf28335启动过程

dspf28335启动过程1.DSP reset后运行的起始地址是多少?0x3FFFC02.仿真器烧写程序的步骤是?根据cmd文件把程序烧到指定位置,然后执行。

3.DSP的Flash启动过程是什么?首先硬件配置GPIO84~87上拉为1,即处于Flash启动过程。

当DSP复位后,会从复位向量0x3FFFC0处取得复位向量,并跳转到InitBoot处开始执行,InitBoot会读GPIO84~87的值发现全为1判断为Flash启动方式。

然后会跳到0x33FFF6处执行。

在CCS5.2工程的cmd文件中有如下代码:MEMORY{PAGE 0 :BEGIN : origin = 0x33FFF6, length = 0x000002 /* Boot to M0 will go here */...}SECTIONS{...codestart : > BEGIN PAGE = 0...}即表示把codestart段放到0x33FFF6位置处,文件“DSP2833x_CodeStartBranch.asm”中有codestart段的定义,实际上codestart段只是包含了一个跳转指令,是程序跳转到_c_int00处,_c_int00在boot.asm in RTS library中有定义,_c_int00的代码最终会调用c的main 函数,之后就是main函数的执行。

总的就是:Reset(0x3fffc0)—>initBoot()—>判断启动方式—>codestart(0x33fff6)—>_c_int00—>main函数4.F28335如何烧写代码到flash中并运行?首先使用添加C:\ti\controlSUITE\device_support\f2833x\v133\DSP2833x_com mon\cmd\F28335.cmd。

此文件即为配置代码到flash中的TI官方配置文件。

TMS320F28335学习笔记-启动过程

TMS320F28335学习笔记-启动过程分类:DSP TMS320F28335项目研发笔记(11)版权声明:本文为博主原创文章,未经博主允许不得转载。

1.DSP reset后运行的起始地址是多少?0x3FFFC02.仿真器烧写程序的步骤是?根据cmd文件把程序烧到指定位置,然后执行。

3.DSP的Flash启动过程是什么?首先硬件配置GPIO84~87上拉为1,即处于Flash启动过程。

当DSP复位后,会从复位向量0x3FFFC0处取得复位向量,并跳转到InitBoot处开始执行,InitBoot会读GPIO84~87的值发现全为1判断为Flash启动方式。

然后会跳到0x33FFF6处执行。

在CCS5.2工程的cmd文件中有如下代码:MEMORY{PAGE 0 :BEGIN : origin = 0x33FFF6, length = 0x000002 /* Boot to M0 will gohere */...}SECTIONS{...codestart : > BEGIN PAGE = 0...}即表示把codestart段放到0x33FFF6位置处,文件“DSP2833x_CodeStartBranch.asm”中有codestart段的定义,实际上codestart段只是包含了一个跳转指令,是程序跳转到_c_int00处,_c_int00在boot.asm in RTS library中有定义,_c_int00的代码最终会调用c的main 函数,之后就是main函数的执行。

4.F28335如何烧写代码到flash中并运行?首先使用添加C:\ti\controlSUITE\device_support\f2833x\v133\DSP2833x_common\cmd\F28335.cmd。

此文件即为配置代码到flash中的TI官方配置文件。

然后参考C:\ti\controlSUITE\device_support\f2833x\v133\DSP2833x_examples_ccsv4\flash_f2833 5。

TMS320F28335教程

低功耗模式和省电模式

支持IDLE,STANDBY,HALT模式

禁止外设独立时钟

179引脚BGA封装或176引脚LQFP封装

DSP技术应用

DSP技术应用

SEED-DEC28335

DSP技术应用

原理框图

片上存储器: FLASH:256K x 16 SRAM:34K x 18 Boot ROM:8K x 16 OTP ROM:1K x 16 片上外设 PWM脉冲输出 GAP/QEP输入 A/D模拟输入 RS232/RS485 CAN总线 RTC+EEPROM EPWM输出:12通道 HRPWM:6通道

简化软件开发,加快上手速度

无需再将程序转换为定点,节省开发时间 提供完善的用户手册和源程序,缩短新芯片的学习时间

DSP技术应用

处理器性能

300 MFLOPS at 150MHz Single-cycle 32-bit MAC 6-channel DMA support for EMIF, ADC, McBSP Code security 68 存储器 512 KB KB Flash 512KB flash and 68KB RAM RAM Configurable 16- or 32-bit EMIF Memory Bus 控制外设 DMA PWM outputs interfaces for three

使用

• 最佳的代码密度 • 兼容C54x™ DSP软件

• 兼容C62x™ DSP软件

DSP技术应用

C2000系列DSP

子系列

C2xx子系列:16位定点DSP、20MIPS

代表器件:TMS320F206PZ C24x子系列:16位定点DSP、20MIPS

F28335存储器功能概述

F28335存储器功能概述班级:姓名:学号:F28335芯片整体功能框图存储器映射1、F28335使用32位数据地址线和22位程序地址线。

2、32位数据地址线可访问4GB的数据空间, 16位/32位3、22位程序地址线可访问4MB的程序空间。

16位/32位。

4、存储器模块采用统一编址方式映射到程序空间和数据空间。

F28335的存储器分为以下几部分:1. 单周期访问RAM(SARAM)2. Flash存储器3. OTP存储器4. Boot ROM(装载了引导程序)5. 安全模块6. 外设存储器(片内的外设)7. 片外存储器一、单周期访问RAM(SARAM)共分10部分:(1)M0和M1,可映射到数据空间或程序空间(2)L0~L3、 L4~L7,可映射到数据空间或程序空间二、flash存储器闪存的英文名称是"Flash Memory",一般简称为"Flash",它属于内存器件的一种,是一种不挥发性( Non-Volatile )内存。

闪存的物理特性与常见的内存有根本性的差异:目前各类 DDR 、 SDRAM 或者 RDRAM 都属于挥发性内存,只要停止电流供应内存中的数据便无法保持,因此每次电脑开机都需要把数据重新载入内存;闪存在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。

是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。

任何flash器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。

F28335的Flash存储器一般可以把程序烧写到Flash中,以避免带着仿真器试调。

F28335器件包含256K*16位的嵌入式闪存存储器,被分别放置在8个32k*16位扇区内。

三、OTP存储器OTPROM(One Time Programmable Read-Only Memory),可以进行片内编程操作,而且可以增强加密功能。

DSP2-F28335的结构基本知识

XINTF

D(31-0)

实时JTAG 仿真逻辑

Atomic ALU

(R-M-W)

乘法器

(32x32 bit)

辅助 寄存器组

(32 bit)

FPU

CPU

寄存器总线

Data Bus(数据总线)

系统控制

时钟管理 Watchdog 定时器*3

PIE

(96个中断)

2017/3/1 Wednesday

4

ePWM eCAP eQEP 12- bit ADC 片上外设 CAN2.0B

2017/3/1 Wednesday

8

二、F28335的ALU

1、ALU

•输入 •输出

程序总线 数据总线

32 16

2、ACC

•AH:AH.MSB,AH.LSB •AL:AL.MSB,AL.LSB

32

Shift R/L (0-16)

32 32

32

XT (32) or T/TL

MULTIPLIER

32 x 32 or Dual 16 x 16

(一)、 F28335的内部结构

一、F28335的基本组成 二、F28335的总线结构

一、F28335的基本组成

Program Bus(程序总线)

A(19-0)

Sectored Flash

(256KW)

SARAM

(34KW)

BootROM OTPROM

(8KW)

(1KW)

存储器

DMA

6 CH.

DMA总线

I 2C SCI SPI McBSP

88*GPIO

Program Bus(程序总线)

一、F28335的基本组成(续) Sectored Flash

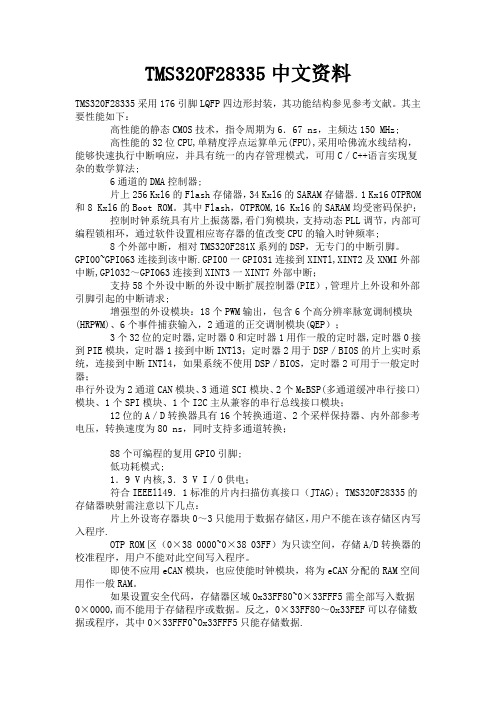

TMS320F28335中文资料

TMS320F28335中文资料TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM 和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断.GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序.OTP ROM区(0×38 0000~0×38 03FF)为只读空间,存储A/D转换器的校准程序,用户不能对此空间写入程序。

DSP第5章-F28335-概述

5.1 F28335的性能

高性能静态CMOS技术:主频150MHZ,指令周期6.67ns; 低功

耗设计,1.9V/1.8V内核电压,3.3VI/O引脚电压;Flash编 程电压为3.3V

高性能32位CPU:IEEE-754单精度浮点运算单元(FPU) ;

534存储器存储空间映射如右图534存储器resetsleepstate芯片复位后的状态standbystate耗能比sleep状态多但转为下个状态时间短activereadstatecpu在flash和otp读取访问由fbankwait寄存器和fotpwait寄存器控制534flash和otp存储器的低功耗模式可提高flash中线性代码的执行效率对fopt寄存器中的enpipe置位来使能流水线模式独立于cpu的流水线模式535flash的流水线模式536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器536flash和otp的寄存器54代码安全模块csm541csm的功能阻止对片内存储器未授权访问防止代码被复制或反解两级保护

5.5 总结

外设帧的寄存器映射如下图所示。

5.5 总结

外设帧的寄存器映射如下图所示。

5.6 F28335与F2812的比 较

5.6 F28335与F2812的比 较

5.4 代码安全模块(CSM)

5.4.2 CSM对其它片内资源的影响

5.4 代码安全模块(CSM)

5.4.3 CSM的使用

工程开发阶段,一般不使用CSM 开发出可靠代码后,才使用CSM 在Flash中烧写代码前,采用密码对芯片进行保护 之后,通过JTAG或运行片内外存储器对安全存储器调试,需输入正 确密码

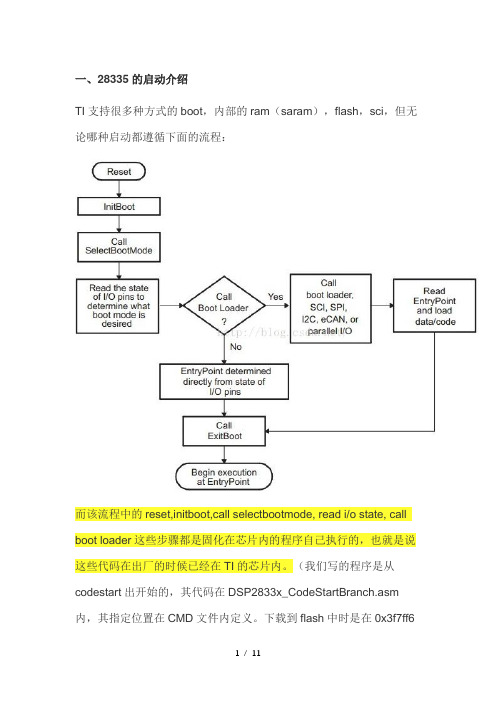

dsp28335-的bootloder过程

一、28335的启动介绍TI支持很多种方式的boot,内部的ram(saram),flash,sci,但无论哪种启动都遵循下面的流程:而该流程中的reset,initboot,call selectbootmode, read i/o state, call boot loader这些步骤都是固化在芯片内的程序自己执行的,也就是说这些代码在出厂的时候已经在TI的芯片内。

(我们写的程序是从codestart出开始的,其代码在DSP2833x_CodeStartBranch.asm 内,其指定位置在CMD文件内定义。

下载到flash中时是在0x3f7ff6处,因为复位的时候指向的0x3fffc0,先执行固化的bootloader再跳转到0x3f7ff6。

下载到RAM中时是在0处。

因为不需执行bootloader。

)在28335中是一段的8k*16的read-only的memory,地址位于0x3fe000-0x3fffff,见下图:根据上面的流程图,详细的解释一下流程:1.在3fffc0到3fffff其实是放了中断向量表的地方:系统一开机当然是处于reset中断,因此直接跳至reset的地方执行(0x3fffc0)。

而这个地方的两个字节只是放了一条指令,就是跳至initboot函数,也就是3ff34c的地址执行bootloader。

.reset 与reset是不同的,一个在memory,一个在sections中。

.reset只包含一个32位的中断矢量,指向实时支持库rts2800_ml.lib 中的C编译器导引函数,即_c_int00子程序。

通常我们不用此块,而是另外创建分支指令指向开始代码。

如4中介绍。

2.在3ff34c的bootloader的程序,这里主要有initboot, 和SelectBootMode, 以及一些外设引导的函数。

SeleteBootMode根据芯片的硬件或软件设置来判断芯片该去哪里寻找程序入口,直接目的是如何找到main,然后执行应用程序。

F28335BOOTROM引导模式和程序

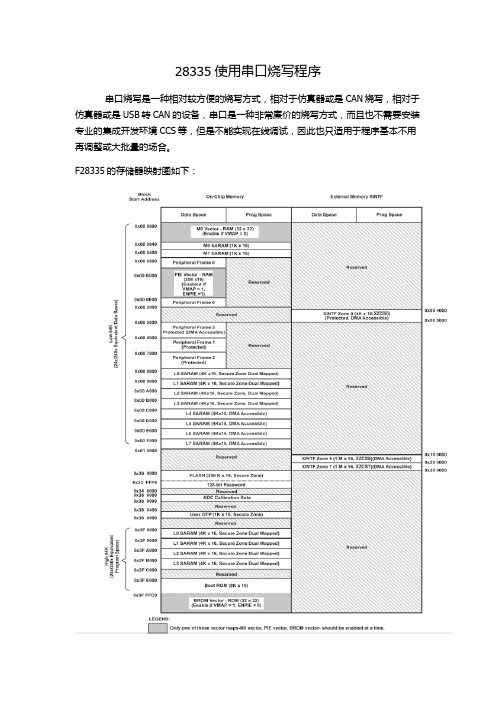

28335使用串口烧写程序串口烧写是一种相对较方便的烧写方式,相对于仿真器或是CAN烧写,相对于仿真器或是USB转CAN的设备,串口是一种非常廉价的烧写方式,而且也不需要安装专业的集成开发环境CCS等,但是不能实现在线调试,因此也只适用于程序基本不用再调整或大批量的场合。

F28335的存储器映射图如下:BOOTROM 是一块8K X 16的只读存储器,位于地址空间0x3FE000~0x3FFFFF,片内BOOTROM在出厂时固化了引导加载程序以及定点和浮点数据表,片上BOOTROM的存储映射如下图所示:1.内BOOT ROM数学表:在BOOT ROM中保留了4K X 16位空间,用以存放浮点和IQ数据公式表,这些数据公式表有助于改善性能和节省SARAM空间。

2.CPU向量表:CPU向量表位于ROM存储器0x3FE000~0x3FFFFF段内,如下图所示。

复位后,当VMAP=1,ENPIE=0(PIE向量表禁止)时,该向量表激活。

在内部BOOT ROM引导区中能够调用的唯一向量就是位于0x3FFFC0的复位向量。

复位向量在出厂时被烧录为直接指向存储在BOOT ROM空间中的InitBoot函数,该函数用于开启引导过程。

然后通过通用I/O引脚上的检验判断,决定具体引导模式。

引导模式与控制引脚之间的关系如下图所示:Bootloader特性:Bootloader是位于片上引导ROM中的在复位后执行的程序,用于在上电复位后,将程序代码从外部源转移到内部存储器。

这允许代码暂时存储在掉电不丢失数据的外部存储器内,然后被转移到高速存储器中执行。

引导ROM中的复位向量将程序执行重定向至InitBoot函数。

执行器件初始化之后,bootloader将检查GPIO引脚的状态以确定您需要执行哪种引导模式。

这些选项包括:跳转至闪存、跳转至SARAM、跳转至OTP或调用其中一个片上引导加载例程。

完成选择进程后,如果已完成所需的引导加载,处理器将在所选引导模式确定的应用起点继续执行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

28335使用串口烧写程序

串口烧写是一种相对较方便的烧写方式,相对于仿真器或是

CAN烧写,相对于仿真器或是USB转CAN的设备,串口是一种非常廉价的烧写方式,而且也不需要安装专业的集成开发环境CCS等,但是不能实现在线调试,因此也只适用于程序基本不用再调整或大

批量的场合。

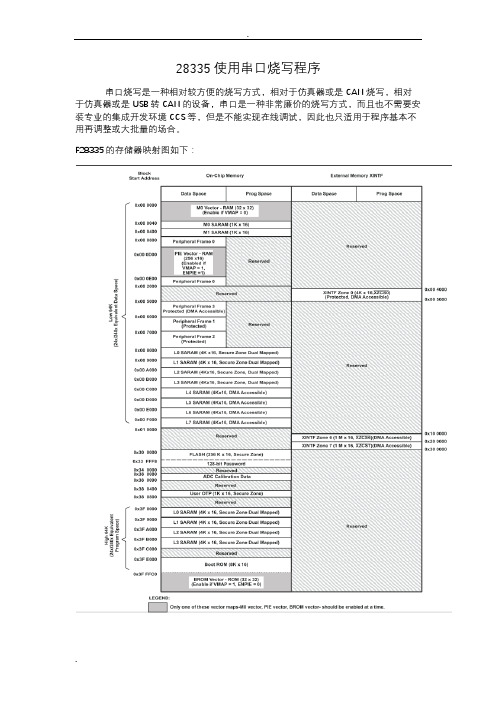

F28335的存储器映射图如下:

BOOTROM 是一块8K X 16的只读存储器,位于地址空间0x3FE000~0x3FFFFF,片内BOOTROM在出厂时固化了引导加载程序以

的存储映射如下图所示:

及定点和浮点数据表,片上BOOTROM

1.内BOOT ROM数学表:

在BOOT ROM中保留了4K X 16位空间,用以存放浮点和IQ数据公式表,这些数据公式表有助于改善性能和节省SARAM空间。

向量表:

CPU向量表位于ROM存储器0x3FE000~0x3FFFFF段内,如下图所示。

复位后,当VMAP=1,ENPIE=0(PIE向量表禁止)时,该向量表激活。

在内部BOOT ROM引导区中能够调用的唯一向量就是位于0x3FFFC0的复位向量。

复位向量在出厂时被烧录为直接指向存储在BOOT ROM 空间中的InitBoot函数,该函数用于开启引导过程。

然后通过通用

I/O引脚上的检验判断,决定具体引导模式。

引导模式与控制引脚

之间的关系如下图所示:

Bootloader特性:

Bootloader是位于片上引导ROM中的在复位后执行的程序,

用于在上电复位后,将程序代码从外部源转移到内部存储器。

这允

许代码暂时存储在掉电不丢失数据的外部存储器内,然后被转移到

高速存储器中执行。

引导ROM中的复位向量将程序执行重定向至InitBoot函数。

执行器件初始化之后,bootloader将检查GPIO引脚的状态以确定您需要执行哪种引导模式。

这些选项包括:跳转至闪存、跳转至SARAM、跳转至OTP或调用其中一个片上引导加载例程。

完成选择进程后,如果已完成所需的引导加载,处理器将在所

选引导模式确定的应用起点继续执行。

如果调用了bootloader,则由外设加载的输入流确定此应用起点地址。

然而,如果选择直接引

导至闪存、OTP或SARAM,这些存储器块中每一个存储器块的应用起

点均已预定义。

上图显示了引导进程的概述。

以下引导模式不掉用bootloader,他们会跳转至存储器中的预定义位置:

1.跳转至闪存中的分支指令:

在此模式下,引导ROM软件将针对28x操作配置器件,然后直接分支至闪存的0x33FFF6位置。

此位置刚好是128位代码安全模块(CSM)密码位置之前。

您需要预先在0x33FFF6位置处编写分支指令,以将代码执行重定向至定制的boot-loader或应用代码。

在仅有RAM的器件上,“引导至闪存”将跳转到保留存储器,因此不应当使用此选项。

2.跳转至M0 SARAM

在此模式下,BOOT ROM将针对28x操作配置器件,然后直接分支至0x000000,即M0 SARAM存储器块中的第一个地址。

3.跳转至OTP存储器

在此模式下直接分支至0x380400,即OTP存储器块中的第一个地址

以下引导模式将调用一个用于将数据流从外设加载至存储器的引导

加载例程:

SCI-A(注意此处的SCI-A对应的是GPIO28和GPIO29)

SPI-A

I2C-A

eCAN-A

GPIO0-GPIO15并行引导。

如果使用SCI或者其他引导的话,首先需要将启动模式选择相

关的引脚配置成对应的模式,然后器件退出复位状态之后,首先从

复位向量处开始运行,即从0x3FFFC0处,该地址存放着BOOT ROM 中的第一个汇编初始引导程序InitBoot程序的入口地址,程序跳转

至0x3FFC00执行InitBoot程序。

该程序主要初始化F28335器件工

作的目标模式。

然后读取安全保护模块的密码,如果CSM密码被擦

除(全部等于0xFFFF)则自动解锁,否则CSM仍被锁定。

对CSM密码读取完成后,初始化例程调用模式选择功能函数(SelectBoot),该函数根据GPIO的状态确定处理器引导的方式。

一旦完成SelectMode将会把入口地址返回给初始化引导。

然后初始

化引导函数调用回复CPU寄存器的退出例程(ExitBoot)并退出到

由引导模式确定的程序入口地址。

因此我们在使用SCI升级程序时可以分两个步骤,第一个步骤

是我们需要一个Bootloader程序,第二个就是我们要升级的程序,BootLoader程序就是我们在选择引导SCI模式之后,SelectBoot之后通过串口加载的第一个程序,待ExitBoot之后会跳转到我们这个bootloader指定的地址开始执行(即将控制权交给我们的这个BootLoader程序),因此我们的BootLoader程序就肩负着串口接

收我们的应用程序并将应用程序烧写到FLASH的任务。

第二个就是

我们的应用程序,这个跟平常的应用程序一样,没有任何区别。

1.BootLoader程序

由上面的介绍明显知道我们的Bootloader程序是运行在RAM 里面的,所以使用CCS在编写该程序的时候使用的是RAM_Link的CMD,而且该程序除了串口的处理还有包括FLASH操作的API函数,

而这些函数必须要运行在RAM里面,而且在进行FLASH操作的时候

要将中断全部都关掉,FLASH的API有相关的例程是烧进FLASH的还要拷贝到RAM,我们这里正好还免去了拷贝的过程,因为我们整

个程序都是运行在RAM中的。

Bootloader数据流的结构:

上图就是BootLoader数据流的结构,数据流的第一个16位字称为键值,该键值用来指向Bootloader指示流入的数据流的宽度:8位或16位(在这里SCI就是8位),对于8位数据流,键值为0x08AA,如果bootloader收到一个无效的键值,加载则中止。

则直接跳转到FLASH开始执行。

接下来的8个字(2-9)用于初始化寄存器直,如果bootloader不使用这些值,则将这些值留作将来使用。

第10个和第11个字组成了22位应用起点地址,此地址用于在完成引导加载后初始化PC,也就是我们程序的起点。

第12个字表示传输的第一个数据块的大小。

对于8位和16位数据流格式,该数据块的大小均定义为块中的16位字个数,例如,

要从8位数据流中传输一个包含20个8位数据值的数据块,该块大

小将为0x000A,表示有10个16位字。

第13和14个字表示程序的目的地址,后面跟的就是程序的字,直到遇到数据块长度为0的则传输结束。

上图为BOOTLoader传输流程,如果不相等会自动退出引导程序,系统会从内部FLASH存储器执行程序。

这里需要讲一下,我们的Bootloader数据流如何得到,我们

正常的使用CCS编译链接得到了文件,然后使用–boot

–sci8 --map= -o -i (详细解释可参考TMS320C28x-Assembly-Language-Tools-User',当然你可以将这些命令参数写成

脚本,然后直接执行即可。

这就会生成Intel格式的hex文件,我们需要自己对这个hex文件解析,对于生成的Hex文件都是以冒号

开始,后面一个字节是数据长度,2-3字节是地址,第4字节是数据类型(00表示数据记录,01表示文件结束记录,02表示扩展段地址记录,04表示扩展线性地址记录)

首先需要一个将两个字符转换为一个字节量函数:

Void CharToByte(char *pChar,BYTE *pByte)

{

char h,l;

h=pChar[0];

l=pChar[1];

if(l>=’0’ && l<=’9’)

l=l-‘0’;

else if(l>=’a’ && l<=’f’)

l=l-‘a’+0xa;

else if(l>=’A’ && l<=’F’)

l=l-‘A’+0xa;

if(h>=’0’ && h<=’9’)

h=h-‘0’;

else if(h>=’a’ && h<=’f’)

h=h-‘a’+0xa;

else if(h>=’A’ && h<=’F’)

h=h-‘A’+0xa;

*pByte=(BYTE)h*16 + 1;

}

解析的关键代码:

If(fopen_s(&myFile,filename,”r”) != 0)

{

Printf(“打开文件%s失败!”,filename);

}

while(!feof(myFile))

{

++len;

fgetc(myFile);

}ut文件生成hex文件的目录下,通过命令行执行如下命令:即可生成hex文件。

在按照上图所示根据自己实际情况配置完成后,我们要将我们板子DSP的启动方式更改为SCI-A启动方式,然后才能进行烧写。

烧写成功如上图所示。

在烧写完成之后,将拨码开关重新切换

至FLASH启动方式,重新启动DSP,这时可以观察程序的运行情况。