高效除法器verilog实现

verilog参数除法

verilog参数除法在Verilog中,如果你想要实现参数化的除法,可以使用/运算符,并将除数和被除数作为参数传递给模块。

下面是一个简单的例子:module Divider #(parameter WIDTH = 8) (input logic signed [WIDTH-1:0] numerator,input logic signed [WIDTH-1:0] denominator,output logic signed [WIDTH-1:0] quotient);assign quotient = numerator / denominator;endmodule在这个例子中,WIDTH是一个参数,用于指定被除数、除数和商的位宽。

这个模块执行带符号整数除法,并将结果赋给输出端口quotient。

你可以实例化这个模块并通过参数传递被除数和除数,如下所示:module TestDivider;logic signed [7:0] numerator;logic signed [7:0] denominator;logic signed [7:0] result;// Instantiate Divider module with WIDTH = 8Divider #(8) uut (.numerator(numerator),.denominator(denominator),.quotient(result));// Rest of your testbench code goes here...endmodule在这个例子中,我们使用Divider #(8)来实例化Divider模块,将numerator、denominator和result作为输入和输出端口连接。

请注意,实例化时通过#(8)指定了参数WIDTH的值。

这只是一个简单的例子,具体实现取决于你的需求和设计规模。

如果有其他特定的要求,请提供更多细节,我将尽力提供更具体的帮助。

Verilog除法器设计(包含单步设计和流水线设计)

Verilog除法器设计(包含单步设计和流水线设计)1.单步设计:单步设计是最简单的一种除法器设计,其原理是将被除数和除数逐位进行比较和计算,直到得到商和余数。

首先,需要定义Verilog模块的输入和输出端口。

输入包括被除数(dividend)和除数(divisor),输出包括商(quotient)和余数(remainder)。

同时,还需要定义一些辅助信号,如计数器和比较器。

```verilogmodule Dividerinput [N-1:0] dividend,input [N-1:0] divisor,output [N-1:0] quotient,output [N-1:0] remainder```在单步设计中,使用一个循环进行逐位比较和计算,直到得到商和余数。

在每一步循环中,被除数向左移动一位,并与除数进行比较。

如果被除数大于或等于除数,则商的对应位为1,否则为0。

然后,将商的对应位赋值给商,并从被除数中减去除数的相应部分。

最后,余数更新为被除数。

```verilogreg [N-1:0] temp_dividend;reg [N-1:0] temp_remainder;reg [N-1:0] temp_quotient;integer i;temp_dividend = dividend;temp_remainder = {N{1'b0}};temp_quotient = {N{1'b0}};for (i = 0; i < N; i = i+1) begintemp_remainder = temp_dividend;if (temp_remainder >= divisor) begin temp_quotient[i] = 1'b1;temp_dividend = temp_remainder - divisor; endtemp_dividend = temp_dividend << 1;endquotient = temp_quotient;remainder = temp_dividend;endendmodule```以上就是单步设计的Verilog除法器代码。

verilog代码乘法除法编写

Verilog代码乘法除法1. 引言Verilog是一种硬件描述语言,用于设计和建模数字电路。

在数字电路中,乘法和除法是常见的运算操作。

本文将介绍如何使用Verilog编写乘法和除法的代码,并提供一些示例来帮助读者更好地理解。

2. 乘法2.1 基本原理乘法是一种基本的算术运算,用于计算两个数的积。

在数字电路中,我们可以使用逻辑门和触发器来实现乘法运算。

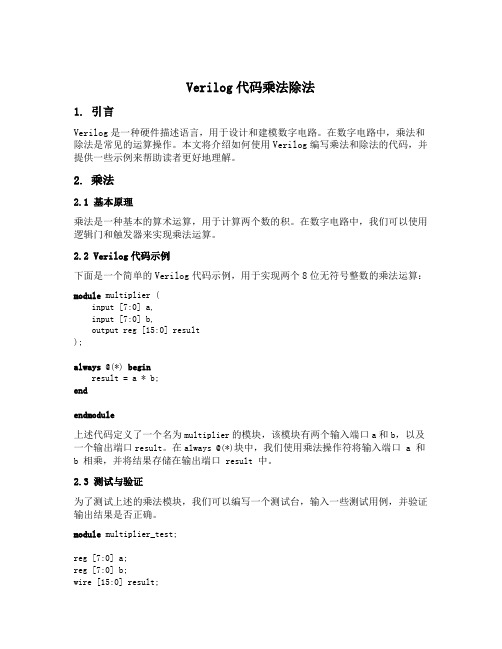

2.2 Verilog代码示例下面是一个简单的Verilog代码示例,用于实现两个8位无符号整数的乘法运算:module multiplier (input [7:0] a,input [7:0] b,output reg [15:0] result);always @(*) beginresult = a * b;endendmodule上述代码定义了一个名为multiplier的模块,该模块有两个输入端口a和b,以及一个输出端口result。

在always @(*)块中,我们使用乘法操作符将输入端口a和b相乘,并将结果存储在输出端口result中。

2.3 测试与验证为了测试上述的乘法模块,我们可以编写一个测试台,输入一些测试用例,并验证输出结果是否正确。

module multiplier_test;reg [7:0] a;reg [7:0] b;wire [15:0] result;multiplier dut(.a(a),.b(b),.result(result));initial begin// Test case 1: a = 5, b = 3a = 5;b = 3;#10; // Wait for 10 time unitsif (result !== 15)$display("Test case 1 failed");// Test case 2: a = 10, b = 0a = 10;b = 0;#10; // Wait for 10 time unitsif (result !== 0)$display("Test case 2 failed");// Add more test cases here...endendmodule上述代码定义了一个名为multiplier_test的测试台模块。

基于Verilog计算精度可调的整数除法器的设计

基于Verilog计算精度可调的整数除法器的设计除法器是技术领域的基础模块,在电子设计中得到广泛应用。

目前,实现除法器的办法有硬件实现和软件实现两种办法。

硬件实现的办法主要是以硬件的消耗为代价,从而有实现速度快的特点。

用硬件的办法来实现除法器的讨论无数,如利用微处理器实现迅速乘除法运算,实现二进制除法运算,模拟除法器等;而通过软件实现的除法器算法,可以大大提高器件的工作频率和设计的灵便性,可以从总体上提高设计性能,而设计高效有用的算法是除法器的关键,故除法器的算法讨论成为现今热点。

目前,软件方面主要是通过减法算法来实现除法运算,把被除数作为被减数,除数作为减数,作减法,直到被减数小于减数为止,记录能够相减的次数即得到商的整数部分。

将所得的余数乘以10作为被减数,除数作为减数,作减法,差重新置入被减数,反复相减,直到被减数小于减数为止,记录能够相减的次数即得到商的非常位数值。

依此继续下去,可得到商的百分位数值,千分位数值,……,要精确到哪一位,就依次做到哪一位。

此办法的缺点是速度慢,而且最后一位的精度不高,为了克服以上的缺点,这里设计一种算法在软件上改进了除法器运算的精确性和处理速度。

1 设计办法对于随意给定的两个整数fenzi和fenmu,设fenzi为被除数,fenmu 为除数。

为了得到两个数相除的十进制结果,本设计主要通过下面的算法来实现,如果要保留小数点后面的n位有效数字,首先把fenzi 乘以10的n次方,赋值给寄存器变量dataO;接着把fenmu分离乘以10的(n+m),(n+m一1),(n+m一2),…,1,O次方分离赋值给(n+m+1)个不同的变量data(n+m+1),data(n+m),…,datal,其中m是fenzi 和fenmu的位数之差(当fenzi的位数多于fenmu时,m为正,否则为负);先求出商的最高位的值,假如dataO大于data(n+m+1),则计数器自动加1,再把dataO和data(n+m+1)的差值赋给data0,再相减直到data0的值小于data(n+m+1),此时计数器的计数值就是最高位的值;依此用同样的办法继续下去,就可得到各个位上的值。

verilog 乘法 除法

verilog 乘法除法摘要:一、引言二、Verilog 简介三、Verilog 乘法模块设计1.点乘法2.阵列乘法四、Verilog 除法模块设计1.循环除法2.快速除法五、Verilog 乘除法模块的应用六、总结正文:一、引言Verilog 是一种硬件描述语言,广泛应用于数字电路设计领域。

在数字电路设计中,乘法和除法是基本的运算操作。

本文将详细介绍如何使用Verilog 实现乘法和除法功能。

二、Verilog 简介Verilog 是一种基于文本的硬件描述语言,用于描述数字电路和模拟混合信号电路。

Verilog 具有简洁、清晰的语法结构,易于学习和使用。

通过Verilog 描述的电路可以被仿真和验证,确保设计正确性。

1.点乘法点乘法是两个数相乘的简单运算。

在Verilog 中,可以使用assign 语句实现点乘法。

例如:```verilogmodule multiplier(input [15:0] a, b, output [31:0] result);assign result = a * b;endmodule```2.阵列乘法阵列乘法是实现多个数相乘的操作。

在Verilog 中,可以使用for 循环和循环阵列实现阵列乘法。

例如:```verilogmodule multiplier_array(input [15:0] a, b, output [31:0] result);reg [15:0] temp_result [15:0];integer i;for (i = 0; i < 16; i = i + 1)temp_result[i] = a * b[i];assign result = temp_result[15] + temp_result[14] + ...+temp_result[0];endmodule```1.循环除法循环除法是一种简单的除法实现方法,通过不断减去除数和更新商来实现。

verilog 乘法 除法

verilog 乘法除法Verilog是一种硬件描述语言,广泛应用于数字电路设计和验证。

本文将介绍Verilog中的乘法和除法原理及其在实际应用中的实现。

一、Verilog乘法器原理与实现1.原理Verilog乘法器的原理是基于位级运算。

输入的两个二进制数按位进行与运算,得到乘积的位级表示。

然后通过移位和加法运算,将位级乘积转换为最终的整数乘积。

2.实现Verilog乘法器的实现主要分为三个部分:全加器、位级乘法器和移位器。

全加器用于处理乘数和被乘数的各位与运算结果;位级乘法器用于计算乘数和被乘数的各位与运算;移位器用于调整位级乘积的位数。

3.实例以下是一个简单的Verilog乘法器实例:```module multiplier(input [7:0] a, b [7:0], output [15:0] result);wire [15:0] partial_product;wire [15:0] temp_result;// 位级乘法器wire [15:0] product [7:0];genvar i;generatefor (i = 0; i < 8; i = i + 1) beginassign product[i] = a * b[i];endendgenerate// 移位器assign partial_product = {product[7], product[6:0]};// 全加器assign temp_result = partial_product + result;assign result = temp_result;endmodule```二、Verilog除法器原理与实现1.原理Verilog除法器的原理是采用迭代算法,将除法问题转化为加法和减法问题。

除数和被除数按位进行与运算,得到余数的位级表示。

然后通过循环移位和加法运算,将余级表示转换为最终的整数商和余数。

verilog 乘法 除法

verilog 乘法除法摘要:一、引言1.介绍Verilog 语言2.Verilog 中的乘法和除法运算二、Verilog 乘法运算1.语法和规则2.举例说明3.注意事项三、Verilog 除法运算1.语法和规则2.举例说明3.注意事项四、乘法和除法运算的比较1.运算速度2.资源消耗3.适用场景五、结论1.Verilog 乘法和除法运算的应用领域2.选择乘法或除法运算的依据正文:一、引言Verilog 是一种硬件描述语言,广泛应用于数字电路设计、验证和仿真。

在Verilog 中,乘法和除法运算是非常基本的操作,对于构建复杂数字电路具有重要意义。

本文将详细介绍Verilog 中的乘法和除法运算。

二、Verilog 乘法运算1.语法和规则在Verilog 中,乘法运算使用“*”符号表示。

乘法操作数可以是数字、变量或者表达式。

例如:```wire [7:0] a, b;a = 8"h12 * 8"h34; // 8 位乘法```2.举例说明以下是一个8 位乘法器的Verilog 代码示例:```module multiplier_8bit(input [7:0] a,input [7:0] b,output [15:0] result);wire [15:0] partial_products [15:0];// 生成partial_productsgen_partial_products: for (genvar i = 0; i < 16; i++) beginassign partial_products[i] = a * b[i];end// 求和wire [15:0] sum0, sum1, sum2, sum3, sum4, sum5, sum6, sum7;wire [15:0] sum8, sum9, sum10, sum11, sum12, sum13, sum14, sum15;assign sum0 = {16"h0, partial_products[0]};assign sum1 = {partial_products[1], 16"h0} + sum0;assign sum2 = {partial_products[2], 16"h0} + sum1;assign sum3 = {partial_products[3], 16"h0} + sum2;assign sum4 = {partial_products[4], 16"h0} + sum3;assign sum5 = {partial_products[5], 16"h0} + sum4;assign sum6 = {partial_products[6], 16"h0} + sum5;assign sum7 = {partial_products[7], 16"h0} + sum6;assign sum8 = {partial_products[8], 16"h0} + sum7;assign sum9 = {partial_products[9], 16"h0} + sum8;assign sum10 = {partial_products[10], 16"h0} + sum9;assign sum11 = {partial_products[11], 16"h0} + sum10;assign sum12 = {partial_products[12], 16"h0} + sum11;assign sum13 = {partial_products[13], 16"h0} + sum12;assign sum14 = {partial_products[14], 16"h0} + sum13;assign sum15 = {partial_products[15], 16"h0} + sum14;assign result = sum15;endmodule```3.注意事项(1)Verilog 中的乘法运算不支持直接对变量或表达式进行溢出处理,需要通过其他方法实现溢出控制。

verilog参数除法

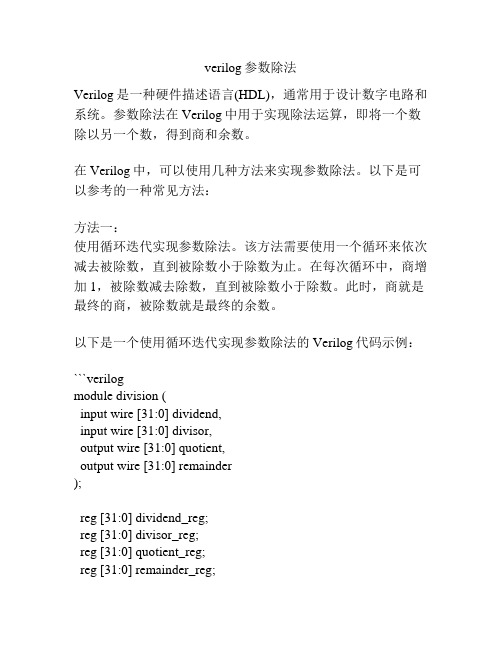

verilog参数除法Verilog是一种硬件描述语言(HDL),通常用于设计数字电路和系统。

参数除法在Verilog中用于实现除法运算,即将一个数除以另一个数,得到商和余数。

在Verilog中,可以使用几种方法来实现参数除法。

以下是可以参考的一种常见方法:方法一:使用循环迭代实现参数除法。

该方法需要使用一个循环来依次减去被除数,直到被除数小于除数为止。

在每次循环中,商增加1,被除数减去除数,直到被除数小于除数。

此时,商就是最终的商,被除数就是最终的余数。

以下是一个使用循环迭代实现参数除法的Verilog代码示例:```verilogmodule division (input wire [31:0] dividend,input wire [31:0] divisor,output wire [31:0] quotient,output wire [31:0] remainder);reg [31:0] dividend_reg;reg [31:0] divisor_reg;reg [31:0] quotient_reg;reg [31:0] remainder_reg;always @(dividend, divisor) begindividend_reg <= dividend;divisor_reg <= divisor;quotient_reg <= 0;remainder_reg <= 0;while (dividend_reg >= divisor_reg) begindividend_reg <= dividend_reg - divisor_reg;quotient_reg <= quotient_reg + 1;endremainder_reg <= dividend_reg;endassign quotient = quotient_reg;assign remainder = remainder_reg;endmodule```在上述代码中,输入参数dividend和divisor分别表示被除数和除数。

verilog 补码定点数除法

verilog 补码定点数除法

Verilog是一种硬件描述语言,用于描述数字电路。

补码定点

数除法是数字电路中常见的运算,可以通过Verilog来实现。

在Verilog中,补码定点数除法可以通过多种方法来实现,其

中一种常见的方法是使用移位和减法来模拟除法运算。

下面我将从

多个角度来讨论如何在Verilog中实现补码定点数除法。

首先,补码定点数除法的基本原理是将被除数和除数转换为补

码表示,然后进行除法运算,最后根据需要进行舍入或截断操作。

在Verilog中,我们可以使用模块化的方式来实现补码定点数除法,将整个除法过程分解为多个子模块,分别实现补码转换、除法运算、舍入和截断等操作。

其次,补码定点数除法的关键在于如何进行除法运算。

在

Verilog中,我们可以使用循环或者递归的方式来实现除法运算,

通过多次减法和移位来逼近商。

同时,我们还需要考虑除数为0的

情况,需要在Verilog代码中添加相应的异常处理逻辑。

另外,在Verilog中实现补码定点数除法时,还需要考虑到数

据宽度、符号位处理、溢出和舍入等问题。

我们需要根据具体的需求来设计合适的Verilog代码,确保实现的除法运算能够满足设计要求。

总的来说,补码定点数除法在Verilog中的实现涉及到补码转换、除法运算、舍入和截断等多个方面,需要综合考虑数据表示、运算精度和性能等因素。

在实际设计中,需要根据具体的应用场景和需求来选择合适的实现方法,保证Verilog代码能够正确、高效地实现补码定点数除法运算。

verilog的取余和除法

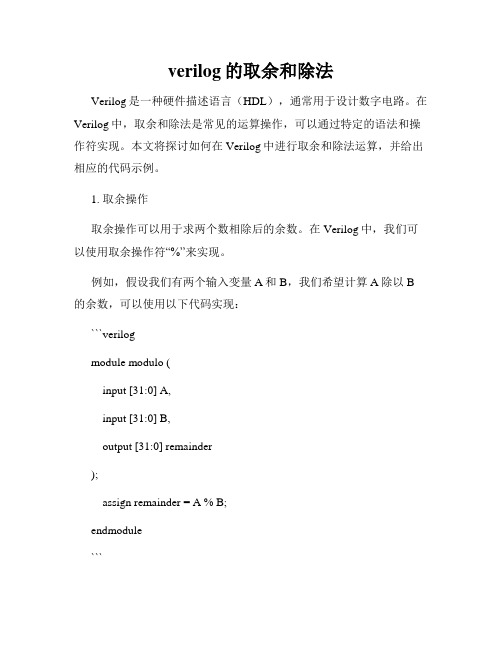

verilog的取余和除法Verilog是一种硬件描述语言(HDL),通常用于设计数字电路。

在Verilog中,取余和除法是常见的运算操作,可以通过特定的语法和操作符实现。

本文将探讨如何在Verilog中进行取余和除法运算,并给出相应的代码示例。

1. 取余操作取余操作可以用于求两个数相除后的余数。

在Verilog中,我们可以使用取余操作符“%”来实现。

例如,假设我们有两个输入变量A和B,我们希望计算A除以B 的余数,可以使用以下代码实现:```verilogmodule modulo (input [31:0] A,input [31:0] B,output [31:0] remainder);assign remainder = A % B;endmodule```上述代码定义了一个名为"modulo"的模块,该模块有三个端口:输入变量A和B,以及输出变量remainder。

在assign语句中,我们使用取余操作符将输入变量A除以B,并将结果赋值给输出变量remainder。

2. 除法操作除法操作可以用于求两个数相除后的商。

在Verilog中,我们可以使用除法操作符“/”来实现。

例如,假设我们有两个输入变量A和B,我们希望计算A除以B的商,可以使用以下代码实现:```verilogmodule division (input [31:0] A,input [31:0] B,output [31:0] quotient);assign quotient = A / B;endmodule```上述代码定义了一个名为"division"的模块,该模块有三个端口:输入变量A和B,以及输出变量quotient。

在assign语句中,我们使用除法操作符将输入变量A除以B,并将结果赋值给输出变量quotient。

需要注意的是,Verilog中的除法操作是按照整数除法规则进行计算的,即结果只保留整数部分。

高效除法器verilog实现

西北工业大学《FPGA技术实验》实验报告二(高效除法器)学院:软件与微电子学院学号:姓名:专业:微电子学实验时间: 2011.10.12 实验地点:毅字楼335 指导教师:王少熙西北工业大学2010年10月endinitialbegin$monitor($time,"divident=% divisor=%d quotient=%d remainder=%d",did,dis,quo,rem) ;endinitialbegin#1000 $finish; // 1000ns时停止仿真endendmodule四、实验结果与数据处理1.Modelsim仿真结果,波形图,代码覆盖率图等为了严谨,把所有的数值都测了一遍(did从0到255,dis从0到15),从modeldim仿真结果看到程序的正确性,鉴于数据较多这里只选择几组数据给予展示:上图中从上到下一次代表被除数,除数,错误,商和余数,当被除数是4.除数分别是9,10,11,12,13,14,15时商为0,余数分别9,10,11,12,13,14,15.当被除数为147,除数分别为1,2,3,4,5,6,7时,商分别为147,73,49,36,29,24,21,余数分别为0,1,0,3,2,3,0.结果正确.由上图可见代码覆盖率已达100%,非常好.2.综合结果,布局布线结果,关键路径,资源利用率等。

用Synplify Pro 9.6.2进行综合得到结果如下图:由于过程简单,布局和布线基本用到很少,,关键路径主要在testbench中开始赋初值的时间和除数被除数的正确输入,程序简单明了资源利用率较高。

五、分析与讨论1.电路的功能是否正确,仿真是否充分,如何进一步提高代码覆盖率。

verilog 乘法 除法

Verilog乘法和除法引言Verilog是一种硬件描述语言(HDL),用于描述数字电路的结构和行为。

它广泛用于设计和验证集成电路(IC)和其他数字系统。

Verilog的一个重要应用是实现乘法和除法运算。

在本文中,我们将详细介绍Verilog中的乘法和除法的实现原理和方法。

我们将讨论乘法和除法的基本概念、Verilog中的乘法和除法操作符、乘法和除法的实现技术等内容。

乘法乘法的基本概念乘法是一种基本的数学运算,用于计算两个数的乘积。

在Verilog中,乘法可以使用乘法操作符*来实现。

乘法操作符的语法如下:<result> = <operand1> * <operand2>;其中,<operand1>和<operand2>是要相乘的操作数,<result>是乘法的结果。

Verilog中的乘法操作符Verilog中的乘法操作符*可以用于乘法运算。

它可以用于任何大小的整数、浮点数和向量。

以下是一些使用乘法操作符的示例:// 乘法示例reg a = 5;reg b = 3;reg c;always @(*) beginc = a * b;end上述示例中,c的值将被计算为5 * 3,即15。

乘法的实现技术在硬件实现中,乘法通常使用乘法器来完成。

乘法器是一种特殊的电路,用于将两个数字相乘。

乘法器的实现方式有很多种,包括布斯算法、Wallace树算法、Dadda树算法等等。

这些算法都有各自的特点和适用范围。

在Verilog中,可以使用内置的乘法操作符*来实现乘法。

这些内置操作符会根据操作数的类型和位宽自动选择合适的乘法器。

除法除法的基本概念除法是一种基本的数学运算,用于计算两个数的商。

在Verilog中,除法可以使用除法操作符/来实现。

除法操作符的语法如下:<result> = <operand1> / <operand2>;其中,<operand1>和<operand2>是要相除的操作数,<result>是除法的结果。

verilog 乘法 除法

verilog 乘法除法(实用版)目录1.引言2.Verilog 乘法和除法的基本概念3.Verilog 乘法和除法的实现方法4.Verilog 乘法和除法的应用实例5.总结正文【引言】Verilog 是一种硬件描述语言,常用于数字电路和模拟混合信号电路的描述。

在 Verilog 中,乘法和除法是数字电路设计中常见的运算。

本文将介绍 Verilog 中乘法和除法的基本概念、实现方法以及应用实例。

【Verilog 乘法和除法的基本概念】在 Verilog 中,乘法和除法运算是基于寄存器的。

乘法和除法运算的结果需要经过一定的时钟周期后才能得到。

乘法和除法的操作数可以是整数或者实数。

其中,整数乘法和除法通常使用位运算实现,实数乘法和除法则需要使用特殊的运算符和函数。

【Verilog 乘法和除法的实现方法】Verilog 中乘法和除法的实现方法主要有两种:一种是使用位运算实现,另一种是使用乘法和除法运算符实现。

1.使用位运算实现乘法和除法在 Verilog 中,可以使用位运算实现乘法和除法。

例如,可以使用“&”运算符实现乘法,使用“~”和“&”运算符实现除法。

2.使用乘法和除法运算符实现乘法和除法Verilog 中提供了专门的乘法和除法运算符:“*”和“/”。

使用这些运算符可以方便地实现乘法和除法运算。

【Verilog 乘法和除法的应用实例】下面是一个 Verilog 代码实例,演示了如何使用 Verilog 实现一个4 位整数乘法器和除法器:```verilogmodule multiplier_divider(input [3:0] a,input [3:0] b,output [7:0] product,output [7:0] quotient);reg [7:0] temp_product;reg [7:0] temp_quotient;always @(*) begintemp_product = a * b;temp_quotient = a / b;product = temp_product;quotient = temp_quotient;endendmodule```【总结】Verilog 中的乘法和除法运算是数字电路设计中常见的运算。

verilog除法

verilog除法

Verilog除法:

1.什么是Verilog除法?

Verilog除法是一种把整数和实数的除法运算用Verilog语言表示的,它允许用户进行不同类型的数据之间的除法运算。

它具有简单易用,快速高效的特点,可以满足让用户的众多应用和需求。

2.Verilog除法的优势

(1)Verilog除法把整数和实数的除法运算用Verilog语言表示,可以针对不同计

算用途给出非常有效的实现。

(2)Verilog除法支持几乎所有类型的数据,包括整数和实数,因此可以通过比较精确的方式进行计算。

(3)Verilog除法的运行性能可以满足资源受限的系统级设计。

它可以使用在嵌入式处理器上,有效减少了设计时间,增加了系统性能。

3.Verilog除法的应用

(1)Verilog除法可以用于数字信号处理(DSP),例如音视频技术、图像压缩技术、信号检测等多媒体应用。

(2)在微控制器和摄像系统中,Verilog除法可以用于实现复杂的算法,并快速准确得出结果。

(3)Verilog除法可以用于调制解调技术,例如数字无线电技术和宽带接入技术等。

4.总结

Verilog除法允许用户进行不同类型的数据之间的除法运算,具有简单易用,快速

高效的特点。

它广泛应用于各种复杂的数据处理算法,如多媒体应用、微控制器系统、调制解调系统等,为设计者提供了性能最优,最佳系统方案。

verilog hdl除法

verilog hdl除法在Verilog HDL中,除法运算可以通过数学运算符/来实现。

除法运算可以用来实现数字的整除或者小数的精确除法。

在Verilog HDL中,除法运算可以在模块中使用,也可以在操作数级别使用。

1. 在模块中使用除法运算符:可以在模块内部定义一个除法运算的变量,然后使用/运算符计算两个操作数的商。

例如,下面的Verilog代码显示了一个简单的模块,该模块计算两个输入数的除法结果:```verilogmodule divider (input [7:0] a,input [7:0] b,output [7:0] result);assign result = a / b;endmodule```在上面的例子中,输入a和b都是8位宽度的寄存器,而输出result也是8位宽度。

通过使用assign语句,我们将输入a除以b的结果赋值给输出result。

2. 在操作数级别使用除法运算符:除了在模块中使用除法运算符外,我们还可以在操作数级别使用除法运算符。

这意味着可以直接将除法运算的结果赋值给一个变量,而无需在模块内部进行计算。

```verilogreg [7:0] a;reg [7:0] b;reg [7:0] result;initial begina = 16;b = 4;result = a / b;$display("Result: %d", result);end```在上面的例子中,我们定义了三个8位宽度的寄存器a、b和result。

使用initial块,我们对寄存器a和b进行赋值,然后将a除以b的结果赋值给result。

最后,我们使用$display函数打印结果。

3. 除法运算的注意事项:在Verilog HDL中,除法运算有一些特殊的情况需要注意:- 如果除数为0,则会产生除以零的错误。

在除数可能为零的情况下,应该在代码中添加适当的检查机制。

- 如果被除数和除数的位宽不同,则除法运算将截断除法结果的小数部分。

高效除法器的Verilog实现

高效除法器的Verilog实现module divider(clock,reset,word1,word2,Start,quotient,remainder,Ready,Error);//---------------------------input [L_divn-1:0]word1;input [L_divr-1:0]word2;input Start,clock,reset;output [L_divn-1:0]quotient;output [L_divn-1:0]remainder;output Ready,Error;//-----------参数---------------------------------------- parameter L_divn=8;parameter L_divr=4;parameter S_idle=0,S_Adivr=1,S_Adivn=2,S_div=3,S_Err=4;parameter L_state=3,L_cnt=4,Max_cnt=L_divn-L_divr;//-----------reg && wire--------------------------------reg [L_state-1:0]state,next_state;reg Load_words,Subtract,Shift_dividend,Shift_divisor; reg[L_divn-1:0]quotient;reg [L_divn:0]dividend;reg [L_divr-1:0]divisor;reg [L_cnt-1:0]num_shift_dividend,num_shift_divisor; reg [L_divr:0]comparison;wire MSB_divr=divisor[L_divr-1];wire Ready=((state==S_idle)&&!reset);wire Error=(state==S_Err);wireMax=(num_shift_dividend==Max_cnt+num_shift_divisor); wire sign_bit=comparison[L_divr];//---------------------主状态机--------------------------always @ (*)begincase(state)S_Adivr:if(MSB_divr==0)comparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~(divisor<<1)}+1'b1;elsecomparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~divisor[L_divr-1:0]}+1'b1;default:comparison=dividend[L_divn:L_divn-L_divr]+{1'b1,~divisor[L_divr-1:0]}+1'b1;endcaseendassign remainder=(dividend[L_divn-1:L_divn-L_divr])-num_shift_divisor;always @(posedge clock)beginif(reset)state<=S_idle;elsestate<=next_state;end//---------------------------------------------------------------------always @(*)beginLoad_words=0;Shift_dividend=0;Shift_divisor=0;Subtract=0;case(state)S_idle:case(Start)0:next_state=S_idle;1:if(word2==0)next_state=S_Err;else if(word1)beginnext_state=S_Adivr;Load_words=1;endelsenext_state=S_idle;endcaseS_Adivr:case(MSB_divr)0:if(sign_bit==0)beginnext_state=S_Adivr;Shift_divisor=1;end1:next_state=S_div;endcaseS_Adivn:case({Max,sign_bit}) 2'b00:next_state=S_div;2'b01:beginnext_state=S_Adivn;Shift_dividend=1;end2'b10:beginnext_state=S_idle; Subtract=1;end2'b11:next_state=S_idle; endcaseS_div:case({Max,sign_bit})2'b00:beginnext_state=S_div; Subtract=1;end2'b01:next_state=S_Adivn; 2'b10:beginnext_state=S_div; Subtract=1;end2'b11:beginnext_state=S_div;Shift_dividend=1;endendcasedefault:next_state=S_Err; endcaseendalways @(posedge clock)beginif(reset)begindivisor<=0;dividend<=0;quotient<=0;num_shift_dividend<=0;num_shift_divisor<=0;endelse if(Load_words==1)begindividend<=word1;divisor<=word2;quotient<=0;num_shift_dividend<=0;num_shift_divisor<=0;endelse if(Shift_divisor)begindivisor<=divisor<<1;num_shift_divisor<=num_shift_divisor+1; endelse if(Shift_dividend)begindividend<=dividend<<1;quotient<=quotient<<1;num_shift_dividend<=num_shift_dividend+1; endelse if(Subtract)begindividend[L_divn:L_divn-L_divr]<=comparison; quotient[0]<=1;endendendmodule测试:module dividertest;reg clock;reg reset;reg [7:0]word1;reg [3:0]word2;reg Start;wire [7:0]quotient;wire [7:0]remainder;wire Ready;wire Error;divider uut(.clock(clock),.reset(reset),.word1(word1),.word2(word2),.Start(Start),.quotient(quotient),.remainder(remainder),.Ready(Ready),.Error(Error)); always #5 clock=~clock; always #10 word1=word1+4; always #10 word2=word2+2;initial beginclock=0;reset=1;Start=0;word1=0;word2=1;#100;reset=0; Start=1; end endmodule。

verilog参数除法

Verilog参数除法1. 引言Verilog是一种硬件描述语言,用于设计和验证数字电路。

它广泛应用于FPGA和ASIC设计中。

本文将讨论在Verilog中实现参数除法的方法。

2. 参数除法的需求在数字电路设计中,除法运算是非常常见的操作。

然而,由于除法运算的复杂性,Verilog中并没有内置的除法运算符。

因此,需要使用其他方法来实现参数除法。

3. 方法一:利用乘法和移位运算一种实现参数除法的方法是利用乘法和移位运算。

该方法基于以下原理:除法可以通过连续减法来实现,而连续减法可以通过乘法和移位运算来实现。

3.1 算法描述以下是参数除法的算法描述:1.将被除数和除数加载到两个寄存器中。

2.判断被除数是否为0,如果是,则结果为0。

3.通过乘法和移位运算将除数左移,直到它大于被除数。

4.将除数右移一位,并将结果累加到商中。

5.重复步骤3和4,直到除数小于被除数。

6.返回商作为结果。

3.2 Verilog实现以下是使用Verilog实现参数除法的代码示例:module param_divider (input [31:0] dividend,input [31:0] divisor,output [31:0] quotient);reg [31:0] dividend_reg;reg [31:0] divisor_reg;reg [31:0] quotient_reg;reg [31:0] remainder_reg;reg [31:0] shift_reg;always @(*) begindividend_reg = dividend;divisor_reg = divisor;quotient_reg = 0;remainder_reg = 0;shift_reg = 0;if (dividend_reg == 0) beginquotient_reg = 0;end else if (divisor_reg == 0) beginquotient_reg = 0;end else beginwhile (divisor_reg >= dividend_reg) begindivisor_reg = divisor_reg >> 1;shift_reg = shift_reg + 1;endwhile (shift_reg > 0) beginif (dividend_reg >= divisor_reg) begindividend_reg = dividend_reg - divisor_reg;quotient_reg = quotient_reg + (1 << (shift_reg - 1));enddivisor_reg = divisor_reg >> 1;shift_reg = shift_reg - 1;endendquotient = quotient_reg;endendmodule4. 方法二:利用查找表另一种实现参数除法的方法是利用查找表。

verilog除法代码

Verilog 中的除法操作可以通过内置的`/` 操作符完成,它用于整数除法。

例如,以下是一个简单的模块,它接受两个输入`a` 和`b`,并输出结果`quotient` 和`remainder`:```verilogmodule div_mod #(parameter WIDTH=32) (input [WIDTH-1:0] a,input [WIDTH-1:0] b,output [WIDTH-1:0] quotient,output [WIDTH-1:0] remainder);assign quotient = a / b;assign remainder = a % b;endmodule```注意:这个代码示例假设了输入`a` 和`b` 都是非负的,并且`b` 不为零。

在实际设计中,你可能需要添加更多的错误检查和处理代码以防止除数为零或其他错误。

另外,Verilog 2001标准引入了`$signed()`函数,可以将一个无符号的整数转化为有符号的整数。

这个函数在处理负数除法时非常有用。

例如:```verilogmodule div_mod #(parameter WIDTH=32) (input [WIDTH-1:0] a,input [WIDTH-1:0] b,output [WIDTH-1:0] quotient,output [WIDTH-1:0] remainder);assign quotient = $signed(a) / $signed(b);assign remainder = a % b;endmodule```在这个例子中,`$signed(a)`将输入`a`转化为有符号整数,然后进行除法。

如果`a`或`b`为负,这个方法可以正确处理。

然而,需要注意的是,如果`b`为零,这个代码将产生一个运行时错误。

高效除法器

一、实验目的及要求用verilog实现一个被除数为8位,除数为4位的高效除法器。

二、实验设备(环境)及要求实验室计算机及modelsim仿真软件,最后用synplify进行综合仿真得到图形。

三、实验内容与步骤1.实验总体设计思路1、先定义被除数为dividend,除数为divisor,商为Rtient,余数为Qainer,举个例子假如被除数与除数分别为1111与0100。

2、将被除数赋给寄存器变量Q=1111,再将除数赋给变量Dr=0100,设置商的变量R 初始值为 4’b0000,则{R,Q}为{00001111}。

3、首先将{R,Q}左移一位,即{00011110},现在R=0001,Q=1110;4、比较R与除数Dr的大小,如果R>Dr,则R=R-Dr,并且{R,Q}再左移一位并且Q[0]=1,反之{R,Q}左移一位Q[0]=0。

5、继续上述过程,循环4次{R,Q}={00111100},{01111000},{01110001},{01100011}。

6、此时商Rtient=Q,而余数Qainer=(R>>1)(即余数等于R向右移一位),所以此例结果为Rtient=0011,Qainer=0011。

检验:对应于十进制,是15除以4,商为3,余数为3.2.系统结构和模块划分,关键子模块之间的接口实现定义。

输入端口:Clk,Rst,dividend,divisor;输出端口:quotient,remainer;寄存器变量:R,Q,Dr;Verilog 代码如下:module chufa(dividend,divisor,Clk,Rst,quotient,remainer); //端口定义input [7:0] dividend; //定义被除数input [7:0] divisor ; //定义除数input Clk; //时钟信号input Rst; //复位信号output [7:0] quotient; //定义商数output [7:0] remainer; //定义余数reg [7:0]Q;reg [7:0]R;reg [7:0]Dr; //定义寄存器变量wire [7:0]quotient;wire [7:0]remainer;integer i;parameter SIZE = 8;always@(posedge Clk or negedge Rst)beginif(!Rst) //复位信号为0时置0。

verilog除法运算符

verilog除法运算符Verilog是一种硬件描述语言,常用于数字电路设计和FPGA编程。

在Verilog中,除法运算符是用于执行除法操作的重要运算符之一。

本文将详细介绍Verilog中的除法运算符及其相关知识。

在Verilog中,除法运算符使用“/”表示,它用于计算两个操作数的商。

除法运算符需要两个操作数,即被除数和除数。

被除数是要被除以的数,而除数是用来除以被除数的数。

除法运算符返回的结果是两个操作数的商。

除法运算符在Verilog中使用的语法如下所示:result = dividend / divisor;其中,result是存储计算结果的变量,dividend是被除数,divisor 是除数。

除法运算符的使用需要注意一些特殊情况。

首先,除数不能为零,否则会导致除零错误。

其次,除法运算符在Verilog中是一个整数除法运算符,它执行整数除法并返回一个整数结果。

如果被除数或除数是浮点数,那么除法运算符将截断小数部分并返回一个整数结果。

除法运算符在数字电路设计中有着广泛的应用。

例如,在时钟频率分频的设计中,除法运算符可以用来将一个高频时钟信号分频为一个较低频率的信号。

此外,在数字信号处理中,除法运算符可以用来执行数字滤波器的设计和实现。

除法运算符还可以用于计算器、浮点数运算单元和通信系统等领域的设计中。

除法运算符在硬件电路中的实现通常使用迭代除法算法或者查找表方法。

迭代除法算法是一种基于减法和移位操作的算法,它通过多次重复减去除数并移位得到商和余数。

查找表方法是一种基于查找表的算法,它通过预先计算并存储除法的结果,并通过查表得到商和余数。

除法运算符的性能取决于硬件的实现方式和操作数的位宽。

在Verilog中,可以根据具体的需求选择适当的实现方式和位宽,以优化除法运算的性能和资源占用。

除法运算符在Verilog中是一个重要的运算符,它可以用于执行除法操作。

本文详细介绍了Verilog中除法运算符的语法和使用注意事项,并介绍了除法运算符在数字电路设计中的应用和硬件实现方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

v1.0可编辑可修改

西北工业大学

《FPGA技术实验》

实验报告二

(高效除法

器)

可编辑可修改

学院: 学号: 姓名: 专业: 实验时间: 实验地点: 软件与微电子学院微电子学

毅字楼335

指导教师:王少熙

西北工业大学

2010年10月

为了能清楚的展示以上算法我们看下面例子:为了简单期间我们假设被除数

(did)是4位,除数(dis)是2位,商(quo)是4位,余数(rem)是4位,设did=0110,dis=10,我们来看看是怎么执行的•首先余数和商都清零,即rem=0,quo=0;把被除数的最高位0拼接到rem的最低位,此时rem=0000B,由于rem小于除数dis=10,则商quo[3]=0;下面进行第二次计算,把did[2]拼接到rem 最低位,此时rem=0001,dis=10>rem,故quo[2]=0;继续计算,把

did[1]拼接到rem 最低位,此时rem=0011,dis=10<rem,故quo[1]=1,rem=rem-quo=0011-10=0001;

进行最后一轮运算,把did[O]拼接到rem最低位,此时rem=0010,dis=10=rem, 因此

quo[0]=1,rem=rem-dis=0010-10=0000,至此我们已计算完毕商quo=0011, 余数rem=0000;计算简单快速.

2.测试平台设计

模块设计

'timescale 1ns/1ns

module divider_8_4(did, error 置 1

);

parameter M=7;

数分别是9,10,11,12,13,14,15 时商为0,余数分别9,10,11,12,13,14,15.

当被除数为147,除数分别为1,2,3,4,5,6,7 时,商分别为

147,73,49,36,29,24,21, 余数分别为0,1,0,3,2,3,0. 结果正确.

由上图可见代码覆盖率已达100%,非常好.

1.综合结果,布局布线结果,关键路径,资源利用率等。

由于过程简单,布局和布线基本用到很少,,关键路径主要在testbench中开始赋初值的时间和除数被除数的正确输入,程序简单明了资源利用率较高。

五、分析与讨论

1.电路的功能是否正确,仿真是否充分,如何进一步提高代码覆盖率

电路功能正确,仿真很充分,代码覆盖率已经达到了很高.

2.电路的关键路径在哪里,如何对关键路径进行优化。

关键是移位相减法,然后考虑在不同情况下,商和余数的结果.

六、教师评语成绩

签名:

日期:。