模拟版图设计最新版

最新模拟集成电路设计流程课件

Session菜单

Schematic Window Save State Load State Options Reset Quit

回到电路图

2021/1/15

保存当前 所设定的 模拟所用 到的各种

参数

加载已 经保存 的状态

共88页

一些显 示选项 的设置

重置

analog artist。 相当于 重新打 开一个 模拟窗

ac(交流分析)是 分析电路性能随着 运行频率变化而变

化的仿真。

既可以对频率进行 扫描也可以在某个 频率下进行对其它

变量的扫描。

2021/1/15

共88页

22

其它有关的菜单项

Outputs/Setup

当然我们需要输出的有时不仅仅是电流、电压,还有一 些更高级的。比如说:带宽、增益等需要计算的值,这时 我们可以在Outputs/setup中设定其名称和表达式。在运行 模拟之后,这些输出将会很直观的显示出来。

2021/1/15

共88页

11

编辑完成的电路图

2021/1/15

共88页

12

一些快捷键

以下是一些常用的快捷键: i 添加元件,即打开添加元件的窗口; [ 缩小两倍; ] 扩大两倍; w 连线(细线); f 全图显示; p 查看元件属性; m 整体移动(带连接关系); shift+m 移动(不带连接关系)。

2021/1/15

共88页

13

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

模拟电路版图设计试题

模拟电路版图设计试题模拟电路设计是电子工程中非常重要的一个环节,通过合理的版图设计可以确保电路的稳定性与性能。

下面给出一个模拟电路版图设计的试题,以检验您的设计能力。

题目描述:设计一个差分放大器电路,输入端为正反馈结构,要求增益为100倍,输入阻抗大于10kΩ,输出阻抗小于100Ω,带宽在500kHz以上。

使用CMOS工艺,电源电压为3.3V。

设计要求:1. 设计电路的整体结构,包括差分输入端、放大器部分和输出端。

2. 根据要求计算电路的具体参数,如电阻、电容值等。

3. 画出电路的布局图和连线图,确保版图布局合理,连线短小。

4. 模拟电路的仿真验证,分析电路的性能,调整参数使得符合设计要求。

设计思路:1. 差分放大器电路的设计是差分放大器和共模反馈电路的结合,可以实现对输入信号的放大,同时抑制共模干扰。

2. 选择合适的晶体管作为放大器,保证增益和带宽的要求。

3. 输入端的正反馈结构可以提高输入阻抗,减小输入信号的失真。

4. 输出端加入缓冲电路,使得输出阻抗小于100Ω,能够驱动负载。

电路参数计算:1. 根据增益要求和电源电压确定放大器的工作点电压。

2. 计算输入端电阻的大小,保证输入阻抗大于10kΩ。

3. 根据放大器的带宽要求确定放大器的频率特性,选择合适的电容值。

布局设计和仿真验证:1. 将电路分块布局,实现电路模块化设计。

2. 优化布局,减小布线长度,降低互感和互容影响。

3. 打开仿真软件,验证电路的性能,调整参数使得输出符合设计要求。

4. 进行交叉仿真,保证电路的稳定性和可靠性。

通过以上步骤,可以完成差分放大器电路的设计与验证,达到题目所要求的性能指标。

设计模拟电路需要仔细思考每一个环节,严格按照设计要求进行实施,方可完成高质量的电路设计。

祝您顺利完成设计任务!。

学习了解cadencevirtuoso版图设计

学习了解cadence virtuoso版图设计Virtuoso 设计平台,可以为设计师实现平均达10倍的全平台性能和容量的提升。

那么下面小编给大家整理了关于学习cadence virtuoso版图设计的方法,希望大家喜欢。

学习cadence virtuoso版图设计知识:Virtuoso 设计平台,可以为设计师实现平均达10倍的全平台性能和容量的提升。

该平台包括采用多项新技术的Cadence Virtuoso 模拟设计环境(ADE)工具,和进一步提高性能的Cadence Virtuoso 版图工具,来全面地应对汽车安全、医疗器械及物联网(IoT)应用的需求。

介绍:新一代Virtuoso ADE产品套件自1991年伊始,Virtuoso 技术与工具平台就已在定制化IC和模拟设计的前端中被广泛采用,25年中,Virtuoso平台帮助无以数计的工程师和IC设计制造商将创新的设计在产品中实现并投放市场。

现在,不断涌现的全新行业标准、先进工艺节点设计及更高的系统设计要求带来了一系列挑战,新一代 Cadence Virtuoso ADE 产品套件应运而生,助力工程师充分探索、分析并验证其设计,确保全周期内设计目标的一致性。

数据处理能力的增强表现在加载数据库超过 1 GB 的波形文件时速度最快可提高20 倍;同时其版本管理和设置文件的加载性能最高可提升 50 倍。

套件的关键技术包括:●Virtuoso ADE探索工具(Virtuoso ADE Explorer):快速、精确的实现设计参数实时调节;自动生成合格/不合格设计的数据列表;提供了完整的工艺角及蒙特卡罗随机抽样统计环境用于检测并修复工艺随机变化问题●Virtuoso ADE 组装工具(Virtuoso ADE Assembler):助力工程师分析不同工艺-电压-温度(PVT)参数组合下的设计性能,并提供基于图形用户界面(GUI)的验证方案,帮助设计师更方便的进行条件性和相关性的仿真●Virtuoso ADE验证工具(Virtuoso ADE Verifier):模拟验证技术的重大进步。

集成电路版图设计基础第五章:模拟IC版图

电源分布是版图设计中非常重要 的一个环节,它涉及到如何合理 地分布电源网络,以保证电路的

稳定性和性能。

常用的电源分布技术包括电源网 格、电源岛和电源总线等,这些 技术可以有效减小电源网络的阻

抗和减小电压降。

热设计

在模拟IC版图设计中,热设计 是一个不可忽视的环节,它涉 及到如何有效地散热和防止热 失效。

验证与测试

功能验证

通过仿真测试或实际测试,验证版图实现的电路功能是 否正确。

时序验证

检查电路时序是否满足设计要求,确保电路正常工作。

ABCD

性能测试

对版图实现的电路进行性能测试,包括参数、频率、功 耗等方面的测试。

可测性、可维护性和可靠性测试

对版图进行测试,验证其在测试、维修和可靠性方面的 表现是否符合要求。

02

模拟IC版图设计流程

电路设计

确定设计目标

根据项目需求,明确电路 的功能、性能指标和限制 条件。

选择合适的工艺

根据电路需求,选择合适 的工艺制程,确保电路性 能和可靠性。

电路原理图设计

使用电路设计软件,根据 电路功能和性能要求,设 计电路原理图。

参数提取与仿真验证

对电路原理图进行仿真验 证,提取关键参数,确保 电路性能满足设计要求。

版图布局

确定版图布局方案

模块划分与放置

根据电路原理图和工艺制程要求,确定合 理的版图布局方案。

将电路原理图划分为若干个模块,合理放 置在版图上,确保模块间的连接关系清晰 、简洁。

电源与地线设计

考虑可测性、可维护性和可靠性

合理规划电源和地线的分布,降低电源和 地线阻抗,提高电路性能。

在版图布局时,应考虑测试、维修和可靠 性等方面的需求。

CMOS模拟集成电路版图设计

相差一个有源 区。所 以源极 与漏极 的总面积不 相 值 。但实际中,有时这种原则会和降低栅噪声 比等

同,则对应的电容也不相同 ,在版图设计时就必须考 矛盾 ,需要根据实际应用采用相应的方法。

虑 哪一极对 电容 比较 敏感 ,进 而减 小相应 极 的面积 , 面积越 小 电容 越小 。

由以上分析可知 ,在设计叉指晶体管时,一般应 尽 可 能采用奇 数叉 指 。

作者简介 :解放 (1980一),女 ,辽宁辽阳人 ,工程 师 ,主研方 向:集成电路设计 。 收稿 13期 :2012—02—23

3期

解 放等 :CMOS模拟集成电路版图设计

·5·

要 求 和工 艺离 散性 的影 响 。

影响不同,下面以 3叉指和 4叉指器件结构为例说

当采用叉指结构时,不同叉指数对电路的性能 明奇偶数个叉指的异同点。如图 2所示。 ‘

No.3 Jun.,2012

微 处 理 机

MICROPROCESSORS

第 3期 2012年 6月

CMOS模 拟集 成 电路 版 图设 计

解 放 ,罗 闯 (中国电子科技集团公 司第四十七研究所,沈阳 110032)

摘 要 :由于模 拟集 成 电路 的性能 与版 图设 计 密切 相 关 ,着 重介 绍 了 CMOS模 拟 电路版 图设 计 的 一般思路 ,优 化器件 结构 和平 面布 局使 寄 生效应对 电路 性能 的影 响 降至最低 。

面 。 建立模拟电路版图单元 ,有两个原则 :使芯片面

积 减 至最小 和将 寄生 器件 对 电路性 能 的影 响降至最 低 。文 中主要 介 绍 模 拟 电路 版 图 布 局 中叉 指 晶 体

Cdb/ 工 丁 Cdb/2

版图设计规则(最新版).ppt

版图概述

设计者只能根据厂家提供的设计规则进行 版图设计。严格遵守设计规则可以极大地 避免由于短路、断路造成的电路失效和容 差以及寄生效应引起的性能劣化。

版图在设计的过程中要进行定期的检查, 避免错误的积累而导致难以修改。

举例:工艺结构

以TSMC(台积电)的0.35μm CMOS工艺为例

TSMC的0.35μm沟道尺寸和对应的电源电压、 电路布局图中金属布线层及其性能参数

顶点 octagon

图形

Layer Processing(层处理命令)

•Selection Commands(选择命令)

gate = geomAnd(poly diff) sd = geomAndNot(diff poly)

Layer Processing(层处理命令)

•Selection Commands(选择命令)

如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension),

如图 (b)

TSMC_0.35μm CMOS工艺版图 各层图形之间最小交叠

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

设计规则(design rule)

•TSMC_0.35μm CMOS工艺中各版图层的线条最小宽 度

设计规则(design rule)

2、最小间距(minSep) 间距指各几何图形外边界之间的距离。

TSMC_0.35μm CMOS工艺版图 各层图形之间的最小间距

设计规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

模拟版图设计工程师实习周记

模拟版图设计工程师实习周记

第一周7.15-7.20

这一周我刚来到公司主要练习了一下CAD,用CAD作图,画一些已经完成CAD图。

主要就是熟悉CAD作图软件。

反复练习CAD软件快捷键。

在这一周,主要练习了CAD画图,因为不算太熟练CAD,所以画图不算很快。

几天的时间,主要学习那一下CAD操作,包括文字样式,图层框选,放大,缩小,拖动命令,确认,和取消,保存,画直线,圆,多边形文字的快捷键的命令操作,我发现如果能交费的快捷键背下来,并且在画图的时候使用真的是非常的快。

比如说框选从上到下拖拉和从下到上拖拉的操作是有区别的;在画图和保存文件时,要将内部设置相对应设置好;在选项设置时,须细心并确认是否应用在当前设置等等。

看来CAD,还真是个大学问,我要勤奋一点联系才好。

第二周7.21-7.27

这一周学习并绘制了公司的主要图例,对公司的业务有了一定的了解。

我画了一些香坊区的街道地图和街道上的井具模型。

在这一周,我的工作内容是对公司的图例进行了解,并且学习、绘制,公司让我对公司所用的图例进行深入地了解。

其中包括图框的大小。

图框的大小包括A3和A4两个图例,以及绘图的比例,其中绘图的比例是1:2000,还有一些常用的图例,这些常用图例都有统一的规格型号,我把他们画了出来,作为自己的素材库,以备后面所需时提取应用,通过这些天的绘图,我发现自己的制图速度又加快了一些,比以前更加的快。

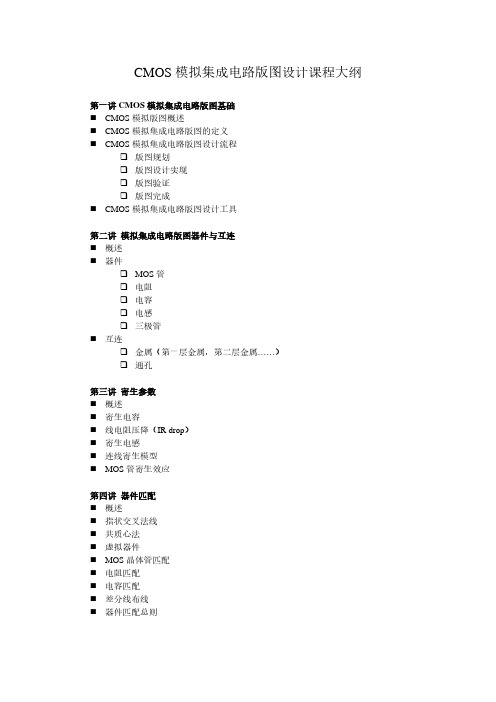

CMOS模拟集成电路版图设计课程大纲

CMOS模拟集成电路版图设计课程大纲第一讲CMOS模拟集成电路版图基础⏹CMOS模拟版图概述⏹CMOS模拟集成电路版图的定义⏹CMOS模拟集成电路版图设计流程❑版图规划❑版图设计实现❑版图验证❑版图完成⏹CMOS模拟集成电路版图设计工具第二讲模拟集成电路版图器件与互连⏹概述⏹器件❑MOS管❑电阻❑电容❑电感❑三极管⏹互连❑金属(第一层金属,第二层金属……)❑通孔第三讲寄生参数⏹概述⏹寄生电容⏹线电阻压降(IR drop)⏹寄生电感⏹连线寄生模型⏹MOS管寄生效应第四讲器件匹配⏹概述⏹指状交叉法线⏹共质心法⏹虚拟器件⏹MOS晶体管匹配⏹电阻匹配⏹电容匹配⏹差分线布线⏹器件匹配总则第五讲设计规则⏹概述⏹工艺库中各类器件的层信息⏹设计规则细则⏹工业标准的基本数据格式第六讲验证⏹设计规则检查(DRC)Design Rule Check⏹版图与电路图的对照(LVS)Layout Versus Schematic⏹电气规则检查(ERC)Electrical Rule Check⏹天线规则检查(ANT)⏹静电放电检查(ESD)第七讲可靠性设计⏹天线效应⏹闩锁效应⏹静电放电保护(Electro-Static Discharge ,ESD)⏹数模混合集成电路版图设计第八讲工艺设计工具包(PDK)⏹ 1.PDK名称的涵义⏹ 2.PDK中包含的内容● 2.1 IO lib2.1.1 GDS文件的导入操作2.1.2 网表导入2.1.3 IO使用文档介绍● 2.2 SMIC_13_PDK_v2.6_20142.2.1 Smic13mmrf_1233文件夹2.2.2 model 文件夹2.2.3 Calibre 文件夹● 2.3 SMIC_13_TF_LG_LIST_2014122.3.1 Standard cell Timing lib2.3.2 Calview.cellmap2.3.3 Standard cell netlist及网表导入操作2.3.4 Ant rule (天线规则)第九讲Cadence spectre概述与操作界面⏹Cadence spectre 概述⏹Cadence spectre的特点⏹Cadence spectre的仿真设计方法⏹Cadence spectre与其他EDA软件的连接⏹Cadence spectre的基本操作第十讲Spectre窗口和库元件⏹模拟设计环境(Analog Design Environment)⏹波形显示窗口(Waveform)⏹波形计算器(Waveform Calculator)⏹Spectre库中的基本器件第十讲Cadence Virtuoso版图设计工具⏹Cadence Virtuoso概述⏹Virtuoso 界面介绍⏹Virtuoso 基本操作第十一讲Mentor Calibre版图验证工具⏹Mentor Calibre版图验证工具概述⏹Mentor Calibre版图验证工具调用⏹Mentor Calibre DRC验证⏹Mentor Calibre LVS验证⏹Mentor Calibre寄生参数提取(PEX)第十二讲版图设计与验证流程实例⏹设计环境准备⏹反相器链电路的建立和前仿真⏹反相器链版图设计⏹反相器链版图验证与参数提取⏹反相器链电路后仿真⏹输入输出单元环设计⏹主体电路版图与输入输出单元环的连接⏹导出GDSII文件。

MultiSim简介

Multisim本是加拿大图像交互技术公司(Interactive Image Technoligics简称IIT公司)推出的以Windows为基础的仿真工具,被美国NI公司收购后,更名为NI Multisim ,而V10.0是其(即NI,National Instruments)最新推出的Multisim最新版本。

目前美国NI公司的EWB的包含有电路仿真设计的模块Multisim、PCB设计软件Ultiboard、布线引擎Ultiroute及通信电路分析与设计模块Commsim 4个部分,能完成从电路的仿真设计到电路版图生成的全过程。

Multisim、Ultiboard、Ultiroute及Commsim 4个部分相互独立,可以分别使用。

Multisim、Ultiboard、Ultiroute及Commsim 4个部分有增强专业版(Power Professional)、专业版(Professional)、个人版(Personal)、教育版(Education)、学生版(Student)和演示版(Demo)等多个版本,各版本的功能和价格有着明显的差异。

NI Multisim 10用软件的方法虚拟电子与电工元器件,虚拟电子与电工仪器和仪表,实现了“软件即元器件”、“软件即仪器”。

NI Multisim 10是一个原理电路设计、电路功能测试的虚拟仿真软件。

NI Multisim 10的元器件库提供数千种电路元器件供实验选用,同时也可以新建或扩充已有的元器件库,而且建库所需的元器件参数可以从生产厂商的产品使用手册中查到,因此也很方便的在工程设计中使用。

NI Multisim 10的虚拟测试仪器仪表种类齐全,有一般实验用的通用仪器,如万用表、函数信号发生器、双踪示波器、直流电源;而且还有一般实验室少有或没有的仪器,如波特图仪、字信号发生器、逻辑分析仪、逻辑转换器、失真仪、频谱分析仪和网络分析仪等。

NI Multisim 10具有较为详细的电路分析功能,可以完成电路的瞬态分析和稳态分析、时域和频域分析、器件的线性和非线性分析、电路的噪声分析和失真分析、离散傅里叶分析、电路零极点分析、交直流灵敏度分析等电路分析方法,以帮助设计人员分析电路的性能。

半导体-芯片模拟版图设计工程师述职报告

尊敬的领导:我是半导体/芯片模拟版图设计工程师,现向您汇报过去一段时间的工作情况和成果。

一、工作内容及完成情况:1. 参与项目需求分析和芯片设计:根据项目需求和规格书,与团队成员一起进行芯片功能分析和设计,制定详细的设计方案。

在项目中,我负责了模拟电路部分的设计工作,并与其他模块的设计工程师密切合作,确保整个设计的一致性和完整性。

2. 进行模拟电路版图设计:根据设计方案,使用专业的版图设计工具进行模拟电路版图的设计。

在设计过程中,我注重细节,确保电路的匹配性和稳定性,并尽量减少功耗和面积。

同时,我也积极与其他设计工程师进行交流和讨论,解决设计中的问题和难题。

3. 进行版图验证和仿真:在版图设计完成后,我进行了版图的验证和仿真工作。

通过使用仿真工具,我对电路的性能进行了评估和优化,并解决了一些潜在的问题。

同时,我也与测试工程师合作,进行实际的测试和验证,确保电路的可靠性和稳定性。

4. 参与团队协作和项目管理:作为团队的一员,我积极参与团队的协作和项目管理工作。

我与其他设计工程师密切合作,及时沟通和解决问题,确保项目的进度和质量。

同时,我也参与了项目的评审和会议,提出了一些建设性的意见和建议。

二、工作成果和亮点:1. 完成了多个项目的模拟电路版图设计工作,并按时交付了设计文件。

这些项目涵盖了不同的应用领域,包括通信、汽车电子等。

通过我的努力,这些项目的电路性能得到了有效提升,满足了客户的需求。

2. 在版图设计和仿真过程中,我发现并解决了一些潜在的问题。

通过对电路的优化和改进,我成功提高了电路的稳定性和可靠性,并减少了功耗和面积。

这些改进得到了团队的认可和赞赏。

3. 在团队协作和项目管理方面,我积极参与了团队的工作,并与团队成员保持良好的沟通和合作。

我提出了一些改进工作流程的建议,并得到了团队的支持和采纳。

通过我的努力,团队的工作效率得到了提高,项目的进度得到了保障。

三、存在的问题和改进措施:1. 在工作中,我发现自己在版图设计和仿真方面还有一些不足之处。

版图模拟集成电路版图设计工作流程

版图模拟集成电路版图设计工作流程

一、设计准备阶段

1.收集设计需求和规格

2.确定版图设计工具

(1)选择合适的版图设计软件

(2)熟悉工具操作方法

二、布局设计

1.绘制整体版图布局

(1)放置主要功能模块

(2)确定连线路径和间距

2.设计外围器件布局

(1)放置电容、电阻等器件

(2)保证布局紧凑和良好连接

三、器件布线

1.连接器件引脚

(1)确定引脚连接顺序

(2)绘制连线路径

2.优化布线

(1)考虑信号传输和功耗(2)调整布线路径提高性能

四、特殊器件设计

1.设计特殊功能模块

(1)绘制模拟电路部分(2)完成数字逻辑设计

2.验证特殊器件功能

(1)模拟仿真验证

(2)数字仿真测试

五、验证与调试

1.进行版图验证

(1)检查器件连接和间距(2)确保布局符合设计规范2.仿真验证

(1)电气仿真测试

(2)时序分析和功耗测试

六、提交版图

1.准备版图文件

(1)导出版图文件格式

(2)打包必要设计文件2.提交给布局工程师(1)交流设计细节和要求(2)确认后提交版图。

模拟版图设计2019最新版

第四部分:版图设计艺术

3. 匹配 3.2 匹配问题

3.2.1 差分对、电流镜…… 3.2.2 误差 3.2.3 工艺导致不匹配

1)不统一的扩散 2)不统一的注入 3)CMP后的不完美平面

3.2.4 片上变化导致不匹配

1)温度梯度 2)电压变化

第四部分:版图设计艺术

3. 匹配 3.3 如何匹配

1)需要匹配的器件尽量彼此挨近

电路图

Symbol 图

第二部分:版图设计基础

4. 电路图编辑器

5) virtuoso编辑器--建立SYMBOL 操作

第二部分:版图设计基础

4. 电路图编辑器 6) virtuoso编辑器--CDL输出操作

第二部分:版图设计基础

4. 电路图编辑器

7) virtuoso编辑器--CDL输出

第二部分:版图设计基础

2.1器件

2.1.2 电阻 选择合适的类型,由电阻阻值、方块电阻值,确

定 W、L;R=L/W*R0

电阻类型

电阻版图

第二部分:版图设计基础

2.1器件 2.1.3 电容

1) 电容值计算C=L*W*C0 2) 电容分类:

poly电容 MIM电容

基于单位面积电容值 MOS电容

源漏接地,基于栅电容, C=W*L*Cox

3. DRC文件

3.3 举例说 明 nwell 的 DRC文 件

NW DRC

第三部分:版图的准备

4. LVS文件

4.1 LVS: layout versus schematic, 版图与电路图对照。

4.2 LVS工具不仅能检 查器件和布线,而 且还能确认器件的 值和类型是否正确。

第三部分:版图的准备

最新模拟版图述职报告范本

最新模拟版图述职报告范本尊敬的领导及同事们:今天,我有幸在此向大家汇报过去一年中我在模拟版图领域的工作成果与心得体会。

我的述职报告将分为三个部分:工作回顾、问题与挑战、未来规划。

一、工作回顾1. 项目完成情况在过去一年中,我主要参与了三个关键的模拟版图项目。

第一个项目是针对5G通信技术的射频模拟版图设计,我们成功实现了高频信号的低损耗传输。

第二个项目是为一款高性能计算芯片设计模拟版图,通过优化布局和电源管理,显著提升了芯片的能效比。

第三个项目则是为一款医疗设备开发高精度模拟信号处理版图,确保了设备的稳定性和可靠性。

2. 技术创新与应用在技术创新方面,我引入了一种新型的电流镜设计,有效降低了版图中的噪声干扰。

同时,我还参与开发了一套自动化版图设计工具,提高了设计效率和精度。

3. 团队协作与知识分享我积极参与团队协作,与同事共同解决技术难题,并定期组织知识分享会,促进团队成员间的技术交流。

二、问题与挑战1. 技术难题在模拟版图设计过程中,我们遇到了一些技术难题,如高频信号的串扰问题和电源噪声抑制问题。

通过不断试验和优化,我们逐步找到了解决方案。

2. 时间管理面对紧张的项目进度,时间管理成为了一大挑战。

我通过合理规划工作流程和优先级,确保了项目的按时交付。

3. 持续学习模拟版图领域的技术更新迅速,持续学习成为了我工作的一部分。

我通过阅读最新的技术文献、参加行业会议和在线课程,不断提升自己的专业能力。

三、未来规划1. 技术深化我计划深入研究模拟版图设计中的高级技术,如毫米波频段的信号完整性问题。

2. 团队建设我将致力于团队建设,通过招聘和培训,提升团队的整体技术水平。

3. 项目管理我希望能够承担更多的项目管理职责,通过优化流程和资源配置,提高团队的工作效率。

总结过去,展望未来,我相信通过不断的努力和创新,我们能够在模拟版图领域取得更多的突破。

感谢大家的聆听,我愿意接受任何问题和建议。

谢谢!。

IC模拟版图课程设计

IC模拟版图课程设计一、课程目标知识目标:1. 学生能理解IC版图的基本概念,掌握版图设计的基本原理。

2. 学生能够运用所学知识,进行简单的IC模拟版图设计。

3. 学生了解版图中常见的电路元件及其符号,掌握其连接方式和布局规则。

技能目标:1. 学生能够运用专业软件进行IC模拟版图的设计与绘制。

2. 学生掌握版图设计中常见的调试方法,具备分析和解决问题的能力。

3. 学生通过实际操作,提高团队协作能力和沟通能力。

情感态度价值观目标:1. 学生培养对电子科技的兴趣,增强对IC行业的认知。

2. 学生在实践过程中,树立正确的工程观念,注重细节,追求精益求精。

3. 学生通过课程学习,培养良好的学习习惯和团队合作精神。

课程性质:本课程为实践性较强的课程,结合理论教学,使学生能够将所学知识应用于实际操作中。

学生特点:学生具备一定的电子基础知识,对IC设计有一定了解,但对版图设计较为陌生。

教学要求:教师应注重理论与实践相结合,以学生为中心,引导他们主动探究、积极实践,提高学生的动手能力和创新能力。

在教学过程中,关注学生的个体差异,提供有针对性的指导。

通过课程学习,使学生达到上述设定的知识、技能和情感态度价值观目标。

二、教学内容1. 版图设计基础理论:- 版图基本概念、版图设计流程及规范。

- 版图中常见的电路元件、符号及其连接方式。

- 版图布局规则及注意事项。

2. 版图设计实践操作:- 使用专业软件进行版图设计的基本操作。

- 简单IC模拟版图的设计与绘制。

- 版图设计中常见问题的调试与解决。

3. 教学案例分析:- 分析典型IC模拟版图案例,了解版图设计的实际应用。

- 学习优秀版图设计技巧,提高自身设计水平。

教学内容安排与进度:第一周:版图设计基础理论、软件操作介绍。

第二周:版图中常见电路元件及其连接方式、布局规则。

第三周:实际操作练习,进行简单IC模拟版图设计。

第四周:版图设计案例分析,总结经验,提高设计能力。

教材章节及内容:第一章:版图设计基础1.1 版图基本概念1.2 版图设计流程及规范1.3 版图中常见的电路元件及符号第二章:版图设计实践2.1 专业软件操作2.2 简单IC模拟版图设计2.3 版图调试与问题解决第三章:教学案例分析3.1 典型IC模拟版图案例3.2 优秀版图设计技巧教学内容确保科学性和系统性,结合实际教学需求,注重理论与实践相结合,使学生能够循序渐进地掌握版图设计相关知识。

实验38 模拟集成电路的版图设计

实验38 模拟集成电路的版图设计模拟集成电路设计是现代集成电路设计的重要组成部分。

模拟集成电路的版图设计是模拟集成电路设计环节中的重要关键环节。

模拟集成电路版图设计的优劣直接影响着整个集成电路的性能和设计的成败。

本实验要求学生在系统地学习了《半导体物理》、《场效应器件物理》、《模拟集成电路设计》和《集成电路制造技术》等专业知识的基础上,使用Tanner公司设计开发的集成电路版图设计工具Ledit软件,独立完成CMOS模拟集成电路单元的版图设计和布局工作,提高模拟集成电路版图设计和布局能力,强化对模拟集成电路制造技术的理解和知识运用能力,培养学生初步的模拟集成电路版图设计能力。

一、实验原理1. 模拟集成电路版图中的器件与设计规则在模拟集成电路中,主要器件有NMOS、PMOS、NPN和PNP晶体管,二极管、电阻和电容等。

这些器件在Ledit软件中,实现的方法存在较大差异,但都是遵循器件的定义实现的。

器件的定义存储在以.ext为后缀的器件萃取文件中。

在Ledit软件环境下,P型衬底N阱CMOS 2P2M工艺下(两层多晶两层金属),模拟集成电路版图中器件的设计规则,除去与数字集成电路版图设计中通用的规则外,主要还有:NPN、PNP晶体管设计规则、电容设计规则和电阻设计规则等,表38.1中摘录了这些规则中的部分内容。

使用这些设计规则可以实现NPN、PNP、MOS电容和电阻等器件版图。

=1.0μm部分设计规则表38.1 P型衬底N阱CMOS工艺下,182在绘制模拟集成电路版图时,所绘制的各种基本图形尺寸不能小于这些设计规则要求的尺寸,否则将导致设计规则错误。

在Ledit软件环境下,完成设计规则检查的功能称为设计规则检查(Design Rule Check,DRC)。

在集成电路版图绘制过程中,需要经常性地使用DRC功能来检查版图是否存在错误,这样做可以避免同时有太多违反设计规则的错误产生,决定着版图的完成效率和完成质量。

模拟电路版图设计方法与框架结构毕业论文【范本模板】

上海城市管理职业技术学院毕业设计(论文)分院人文与信息技术学院专业应用电子班级 11应用电子(1)姓名胡穆学号 110502003指导教师崔玉美设计(论文)题目模拟电路版图设计方法与框架结构二○一三年三摘要集成电路的出现与发展彻底改变了人类的文明和人们的日常生活面目,比如:手机、U盘、麦克风、等等。

集成电路是电子电路,它不不同于一般意义上的电子电路,它是把成千上万的电子元件包括晶体管,电阻,电容甚至电感集成在微小的芯片上面,正是这种奇妙的设计和制造方式使它为人类社会的进步创造了空前绝后的奇迹,而使这种奇迹变为现实的是集成电路掩膜版图设计。

集成电路或称微电路(microcircuit)、微芯片(microchip)、芯片(chip)在电子学中是一种把电路(主要包括半导体装置,也包括被动元件等)小型化的方式,并通常制造在半导体晶圆表面上。

集成电路是相对分立器件组成的电路而言、把组成电路的元件、器件以及相互间的连线放在单个芯片上,整个电路就在这个芯片上,把这个芯片放到管壳中进行封装,电路与外部的连接靠引脚完成。

根据电路功能和性能的要求,在正确选择系统配置、电路形式、器件结构、工艺方案和设计规则的情况下,尽量减小芯片面积,降低设计成本,缩短设计周期,以保证全局优化,设计出满足要求的集成电路。

关键词:版图设计;设计规则;版图验证;电阻,电容,二极管;目录摘要------------------------------------------------------------ 2前言-------------------------------------------------------------- 4 第一章了解版图-------------------------------------------------- 5 1。

1 版图意义----------------------------------------------------- 5 1.2 版图定义-------------------------------------------------------- 5 1。

模拟版图中的顶层设计

模拟版图中的顶层设计在模拟版图的顶层设计中,你需要考虑整个系统的需求和功能,并设计出一个适当的架构来实现这些需求和功能。

这通常包括对系统的功能进行划分,并设计出适当的接口来使这些功能能够交互。

在进行顶层设计时,你还需要考虑系统的性能、可靠性、安全性等因素,并设计出适当的措施来保证这些因素。

为了帮助你更好地进行顶层设计,你可以使用一些工具和方法,比如流程图、系统架构图、用例图、状态图等。

这些工具和方法可以帮助你更清晰地表示出系统的功能和交互,并更好地理解系统的工作流程。

在进行顶层设计时,你还需要考虑到系统的可维护性和扩展性。

这意味着,你需要设计出一个架构,使得系统在未来的变化和扩展中能够保持稳定,并且能够方便地进行维护和升级。

总之,在进行模拟版图的顶层设计时,你需要考虑整个系统的需求和功能,并设计出一个适当的架构来实现这些需求和功能。

你还需要考虑系统的性能、可靠性、安全性等因素,并设计出适当的措施来保证这些因素。

同时,你还要注意系统的可维护性和扩展性,以便使系统在未来的变化和扩展中能够保持稳定,并方便进行维护和升级。

在完成顶层设计后,你还需要进行低层设计,具体地设计出每个模块或子系统的具体实现细节。

在低层设计中,你可能需要使用一些工具和方法,比如类图、顺序图、活动图等,来帮助你更清晰地表示出每个模块或子系统的功能和交互。

在完成低层设计后,你就可以开始编写代码了。

你需要按照设计的架构和低层设计来实现每个模块或子系统。

在编写代码时,你还需要注意代码的质量,比如避免出现常见的错误、使用良好的编码风格、编写有效的单元测试等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.2.1金属(第一层金属,第二层金属……) 2.2.2通孔

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管

NMOS

PMOS

MOS管剖面图

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管

NMOS工艺层立体图

NMOS版图

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管 1) NMOS管

✓ 以TSMC,CMOS,N单阱 工艺为例

✓ NMOS管,做在P衬底上, 沟道为P型,源漏为N型

2) 包括层次:

✓ NIMP,N+注入 ✓ DIFF,有源区 ✓ Poly,栅 ✓ M1,金属 ✓ CONT,过孔

3) MOS管的宽长确定 4) 当有PCELL时;当无 PCELL时

NMOS版图

第二部分:版图设计基础

– Mentor

✓calibre

– Spring soft

✓laker

第4.一版部图的分设:计了流解程 版图

熟悉所需文件 对电路的了解 版图布局布线

DRC/LVS GDSII to FAB

工艺厂商提供:.tf .display Design rule 、 DRC LVS 文件、PDK、 ESD文件、金属阻值文件

IC模拟版图设计

目录

• 第一部分:了解版图

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

• 第二部分:版图设计基础

1. 认识版图 2. 版图组成两大部件 3. 版图编辑器 4. 电路图编辑器 5. 了解工艺厂商

目录

• 第三部分:版图的准备

1. 必要文件 2. 设计规则 3. DRC文件 4. LVS文件

MIM电容版图

MOS电容版图

第二部分:版图设计基础

2.2互连

2.2.1金属(第一层金属,第二层金属……)

1) 金属连线 ✓ M1,M2,M3,M4……

2.2.2 通孔 2)过孔

✓ Via1,Via2,Via3……

第二部分:版图设计基础

2.2互连 1) 典型工艺

✓CMOS N阱 1P4M工艺剖面图

2.1器件

2.1.2 电阻 选择合适的类型,由电阻阻值、方块电阻值,

确定 W、L;R=L/W*R0

电阻类型

电阻版图

第二部分:版图设计基础

2.1器件

2.1.3 电容

1) 电容值计算C=L*W*C0 2) 电容分类:

✓ poly电容 ✓ MIM电容

» 基于单位面积电容值 ✓ MOS电容

» 源漏接地,基于栅电 容,C=W*L*Cox

第二部分:版图设计基础

3. 版图编辑器

7) virtuoso编辑器 --显示窗口

第二部分:版图设计基础

3. 版图编辑器 8) virtuoso编辑器 --版图显示

第二部分:版图设计基础

3. 版图编辑器

9) virtuoso编辑器--数据流格式版图输出

第二部分:版图设计基础

4. 电路图编辑器

1) virtuoso编辑器--电路图显示

IC模拟版图设计

• 第二部分:版图设计基础

1. 认识版图 2. 版图组成两大部件

2.1 器件 2.2 互连 3. 版图编辑器 4. 电路图编辑器 5. 了解工艺厂商

第二部分:版图设计基础

1. 认识版图

Poly

M1

CT

M2

第二部分:版图设计基础

2. 版图是电路图的反映,有两大组成部分

2.1器件

2.1.1 MOS管 2.1.2 电阻 2.1.3 电容 2.1.4 三极管(省略) 2.1.5 二极管(省略) 2.1.6 电感(省略)

PMOS版图

第二部分:版图设计基础

2.1 器件 • 反向器

器件剖面图及俯视图

器件版 图

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管 1)反向器

VDD

3u/0.18u

IN

OUT

1u/0.18u

2)NMOS,PMOS

GND

3)金属连线

4)关于Butting Contact部分

第二部分:首要目标 2. 首先考虑的三个问题 3. 匹配 4. 寄生效应 5. 噪声 6. 布局规划 7. ESD 8. 封装

IC模拟版图设计

• 第一部分:了解版图

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

第一部分:了解版图

2)它需要设计者具有电路系统原理与工艺制造 方面的基本知识,设计出一套符合设计规则 的“正确”版图也许并不困难,但是设计出 最大程度体现高性能、低功耗、低成本、能 实际可靠工作的芯片版图缺不是一朝一夕能 学会的本事。

第一部分:了解版图

3. 版图的工具:

– Cadence

✓Virtuoso ✓Dracula ✓Assura ✓Diva

CIW窗口

第二部分:版图设计基础

3. 版图编辑器

4) virtuoso编辑器--工作区和层次显示器

LSW

工作区域

第二部分:版图设计基础

3. 版图编辑器 5) virtuoso编辑器 --版图层次显示(LSW)

第二部分:版图设计基础

3. 版图编辑器 6) virtuoso编辑器 --版图编辑菜单

第二部分:版图设计基础

4. 电路图编辑器 2) virtuoso编辑器 --电路器件及属性

1. 版图的定义:版图是在掩膜制造产品上实现 电路功能且满足电路功耗、性能等,从版图上 减少工艺制造对电路的偏差,提高芯片的精准 性。

VDD

3u/0.18u

IN

OUT

1u/0.18u

GND

电路图

版图

第一部分:了解版图

2. 版图的意义:

1)集成电路掩膜版图设计师实现集成电路制造 所必不可少的设计环节,它不仅关系到集成 电路的功能是否正确,而且也会极大程度地 影响集成电路的性能、成本与功耗。

2.1 器件

2.1.1 MOS管 1) NMOS管

✓ 以TSMC,CMOS,N单 阱工艺为例

✓ PMOS管,做在N阱中, 沟道为N型,源漏为P型

2) 包括层次:

✓ NWELL,N阱 ✓ PIMP,P+注入 ✓ DIFF,有源区 ✓ Poly,栅 ✓ M1,金属 ✓ CONT,过孔

3) MOS管的宽长确 定

连线与孔之间的连接

第二部分:版图设计基础

3. 版图编辑器

1) virtuoso编辑器

• 建立LIBRARY

CIW窗口

第二部分:版图设计基础

3. 版图编辑器

2) virtuoso编辑器--Library manager

第二部分:版图设计基础

3. 版图编辑器

3) virtuoso编辑器-- 建立

cell