I2C总线协议规范 v2.1

i2c电平转换电路,高压为0

I2C电平转换电路,是一种用于在I2C通信中将高电平转换为低电平的电路。

在某些情况下,需要将I2C总线的电平从高压转换为0,以便与其他设备进行通信。

本文将从以下几个方面介绍I2C电平转换电路。

I2C电平转换电路的基本原理I2C是一种串行通信协议,使用两根线进行数据传输:一个是时钟线(SCL),另一个是数据线(SDA)。

在I2C通信中,高电平通常被定义为电压范围(2.1V-5.5V),低电平被定义为电压范围(0V-0.9V)。

如果需要将I2C通信中的高电平转换为低电平,就需要使用I2C电平转换电路。

I2C电平转换电路的工作原理通常基于场效应晶体管(FET)或双向电平转换器。

当输入信号为高电平时,I2C电平转换电路将其转换为低电平输出,以满足其他设备的输入要求。

具体工作原理可以分为以下几个步骤:1. 将高电平信号输入到I2C电平转换电路的输入端。

2. 电路内部的FET或双向电平转换器将高电平信号转换为低电平信号。

3. 低电平信号输出到外部设备进行通信。

I2C电平转换电路的应用领域I2C电平转换电路广泛应用于各种需要I2C通信的场合,如电子设备、工业控制系统和通信领域。

具体应用领域包括但不限于:1. 电子设备:智能手机、平板电脑、数字相框等电子产品中的各个模块之间的通信。

2. 工业控制系统:传感器、执行器和控制器之间的数据交换和控制信号传输。

3. 通信领域:基站设备、射频前端模块等通信设备中的各个模块之间的通信。

I2C电平转换电路的特点和优势I2C电平转换电路具有以下特点和优势:1. 低功耗:采用场效应晶体管或双向电平转换器作为核心元件,具有低功耗特性。

2. 快速转换:能够快速将高电平转换为低电平,满足I2C通信的时序要求。

3. 低成本:采用常见的电子元件和材料制造,成本较低。

4. 坚固可靠:经过严格的设计和测试,具有良好的稳定性和可靠性。

总结I2C电平转换电路是一种用于在I2C通信中将高电平转换为低电平的电路。

I2C通讯协议

I2C通讯协议协议名称:I2C通讯协议1. 引言I2C(Inter-Integrated Circuit)是一种串行通信协议,用于在集成电路芯片之间进行数据传输。

本协议旨在规范I2C通信的各个方面,包括物理层连接、数据传输格式、设备地址分配、时序要求等。

2. 物理层连接2.1 I2C总线拓扑I2C总线采用多主机、多从机的拓扑结构。

总线由两根信号线组成,分别是串行数据线(SDA)和串行时钟线(SCL)。

2.2 电气特性I2C总线采用开漏输出方式,需要外部上拉电阻。

SDA和SCL线上的电平由总线上的主机或从机设备控制。

2.3 总线速率I2C总线支持多种速率,常见的有标准模式(100 kbit/s)、快速模式(400 kbit/s)和高速模式(3.4 Mbit/s)。

3. 数据传输格式3.1 帧结构I2C通信采用帧结构,每个帧包含一个起始位、8位数据位、一个应答位和一个停止位。

3.2 数据传输方向I2C通信支持主机向从机的写操作(主机发送数据)和主机从从机的读操作(主机接收数据)。

3.3 起始和停止条件I2C通信的起始条件是SDA线由高电平跳变到低电平,同时SCL线保持高电平。

停止条件是SDA线由低电平跳变到高电平,同时SCL线保持高电平。

4. 设备地址分配4.1 7位地址模式I2C总线使用7位设备地址进行设备识别。

地址的最高位为0,表示写操作;最高位为1,表示读操作。

4.2 10位地址模式I2C总线还支持10位设备地址模式,用于解决设备数量过多的情况。

5. 时序要求5.1 数据传输时序I2C通信的时序要求严格,包括起始条件、停止条件、数据传输、应答等。

具体的时序图可参考相关文档。

5.2 时钟同步I2C总线上的时钟由主机设备产生,所有从机设备都同步于主机设备的时钟信号。

5.3 延时要求I2C通信需要保证一定的延时要求,以确保数据的稳定传输。

6. 错误处理6.1 应答错误主机设备在发送地址或数据后,会等待从机设备的应答信号。

I2C总线连接规范

I2C总线连接规范力泰电子开发部 朱文锋 2008-3-31I2C(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。

1.I2C总线特点I2C总线最主要的优点是其简单性和有效性。

由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。

总线的长度可高达7.6米,并且能够以10Kbps的最大传输速率支持40个组件。

目前我司的I2C总线只有一个主控,即S3C9228/R5R0C02;其余每个器件都有一个唯一的地址识别,作为一个发送器或接收器由器件的功能决定。

2. I/O 级和总线线路的电气规范2.1 I2C 总线器件SDA 和SCL I/O 级的特性:参数 最小值 最大值低电平输入电压 -0.5V 0.3VDD高电平输入电压 0.7VDD Vmax+0.5V低电平输出电压 0 0.4V表一2.2 I2C 总线器件到总线线路的电气连接上拉电阻必须连接到一个5V 10%的电源,输入电平连接到V DD 的I2C 总线器件必须有一条公共的电源线连接到上拉电阻。

如图一所示。

图一输入电平定义:低电平噪声容限是0.1V DD高电平噪声容限是0.2V DD串连电阻R S 可以用于防止SDA 和SCL 线的高电压毛刺波,如图二所示:图二2.3 I2C 总线器件电阻R p 和R S 的最大和最小值对于标准模式I2C 总线系统电阻R p 和R S的值由下面的参数决定:¾电源电压¾总线电容¾连接器件数量噪声容限:在前一极输出为最坏的情况下,为保证后一极正常工作.所允许的最大噪声幅度。

电源电压限制了电阻R p 的最小值因为输出级在V OLmax=0.4V 时指定的最小下拉电流是3mA。

低电平要求的0.1V DD 噪声容限限制了R S 的最大值。

图三V DD 与R pmin 的函数曲线从图三V DD 与R pmin 的函数曲线知,R pmin > 1.8KΩ。

I2C通讯协议

I2C通讯协议协议名称:I2C通讯协议1. 引言I2C通讯协议是一种用于集成电路(Integrated Circuit,简称IC)之间进行通信的串行通信协议。

本协议旨在规范I2C通信的格式、电气特性、数据传输速率以及设备地址分配等方面的要求,以确保不同厂商生产的IC能够在I2C总线上进行可靠的通信。

2. 范围本协议适合于使用I2C通信协议的所有设备和系统,包括但不限于集成电路、传感器、存储器等。

3. 术语和定义以下术语和定义适合于本协议:- 主设备(Master Device):发起I2C通信的设备。

- 从设备(Slave Device):响应I2C通信的设备。

- 总线(Bus):用于连接主设备和从设备的物理通信路线。

- 传输速率(Transfer Rate):主设备和从设备之间传输数据的速度。

- 设备地址(Device Address):用于识别从设备的惟一地址。

4. 电气特性4.1 电压I2C总线上的电压应符合以下要求:- 逻辑高电平(V_H):2.1V至5.5V。

- 逻辑低电平(V_L):0V至0.7V。

- 上拉电阻(R_PU):主设备和从设备上的上拉电阻应保证逻辑高电平的稳定。

4.2 时钟速率I2C通信的时钟速率应符合以下要求:- 标准模式(Standard Mode):时钟速率不超过100kHz。

- 快速模式(Fast Mode):时钟速率不超过400kHz。

- 高速模式(High-Speed Mode):时钟速率不超过3.4MHz。

- 超高速模式(Ultra Fast Mode):时钟速率不超过5MHz。

5. 数据传输格式5.1 帧结构I2C通信使用帧结构进行数据传输,一个帧包含以下要素:- 起始位(Start Bit):逻辑低电平表示传输开始。

- 设备地址(Device Address):用于识别从设备的惟一地址。

- 读/写位(R/W Bit):逻辑低电平表示主设备发送数据,逻辑高电平表示主设备接收数据。

IIC总线协议

IIC总线协议协议名称:IIC总线协议一、引言IIC总线协议是一种串行通信协议,用于在集成电路之间进行数据传输。

本协议旨在规定IIC总线的物理层和数据链路层的规范,以确保不同设备之间的互操作性和数据传输的可靠性。

二、术语和定义1. IIC总线:Inter-Integrated Circuit总线的简称,也被称为I2C总线,是一种用于短距离通信的串行总线。

2. 主设备:在IIC总线上发起通信的设备。

3. 从设备:响应主设备通信的设备。

4. 数据帧:在IIC总线上传输的数据单元,包括起始位、地址位、数据位和校验位。

三、物理层规范1. 电气特性1.1 电压:IIC总线使用双向开漏或双向三态的器件进行通信,通信线上的电平为0V或高阻态。

1.2 电流:通信线上的电流应在设备规格范围内,以保证通信的可靠性。

1.3 电阻:总线上的上拉电阻和下拉电阻应根据总线长度和设备数量进行合理选择,以确保信号的稳定性。

2. 时序要求2.1 起始条件:主设备发送起始信号,即将总线上的数据线(SDA)从高电平拉低,时钟线(SCL)保持高电平。

2.2 结束条件:主设备发送结束信号,即将总线上的数据线从低电平拉高,时钟线保持高电平。

2.3 数据传输时序:数据传输的时钟由主设备提供,每个数据位在时钟的下降沿进行传输,数据线上的数据保持稳定直到下一个时钟周期的下降沿。

四、数据链路层规范1. 寻址方式1.1 主设备发送起始信号后,发送从设备地址和读写位。

地址由7位或10位组成,用于唯一标识从设备。

1.2 读写位为0表示主设备向从设备发送数据,为1表示主设备从从设备读取数据。

2. 数据传输2.1 数据帧格式:数据帧由起始位、地址位、数据位和校验位组成。

2.2 起始位:数据线上的高电平信号,表示数据传输的开始。

2.3 地址位:由主设备发送,用于指定通信的从设备。

2.4 数据位:数据线上的数据传输,每个数据位在时钟的下降沿进行传输。

2.5 校验位:用于验证数据的完整性和正确性,由主设备发送。

IIC总线协议

iic总线协议I2C协议是单片机与其它芯片常用的通讯协议,由于只需要两根线,所以很好使用。

1. I2C总线的特点(1)只要求两条总线线路一条串行数据线SDA 一条串行时钟线SCL(2) 每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机/从机关系软件设定地址;主机可以作为主发送器或主机接收器(3)它是一个真正的多主机总线,如果两个或更多主机同时初始化数据传输可以通过冲突检测和仲裁防止数据被破坏(4)串行的8 位双向数据传输位速率在标准模式下可达100kbit/s 快速模式下可达400kbit/s 高速模式下可达.4Mbit/s(5)片上的滤波器可以滤去总线数据线上的毛刺波保证数据完整(6) 连接到相同总线的IC数量只受到总线的最大电容400pF 限制I2C协议总线信号时序分析1 .数据的有效性:SDA 线上的数据必须在时钟的高电平周期保持稳定数据线的高或低电平状态只有在SCL 线的时钟信号是低电平时才能改变。

如图3.1 I2C总线的位传输所示。

图1. I2C总线的位传输2 .起始和停止条件当SCL线是高电平时,SDA线从高电平向低电平切换,这个情况表示起始条件。

当SCL线是高电平时,SDA线由低电平向高电平切换表示停止条件。

如图3.2 I2C起始和停止条件所示。

图3.2 起始和停止条件3. 总线空闲状态SDA和SCL两条信号线都处于高电平,即总线上所有的器件都释放总线,两条信号线各自的上拉电阻把电平拉高;4 .数据传输与应答信号ACK发送到SDA线上的数据必须是8位的。

每次传输可以发送的数据不受限制。

每个字节后必须在时钟的第9个脉冲期间释放数据总线(SDA为高),由接收器发送一个ACK(把数据总线的电平拉低)来表示数据成功接收。

如图3.3 I2C总线响应。

图3.3 I2C总线响应首先传输的是数据的最高位(MSB)。

如果从机要完成一些其他功能后(例如一个内部中断服务程序)才能接收或发送下一个完整的数据字节,可以使时钟SCL保持低电平迫使主机进入等待状态。

IIC总线协议

IIC总线协议协议名称:IIC总线协议1. 引言IIC(Inter-Integrated Circuit)总线协议是一种用于在集成电路之间进行通信的串行通信协议。

本协议旨在规定IIC总线通信的物理层电气特性、数据传输格式以及通信协议的规则,以确保不同设备之间的互操作性和数据的可靠传输。

2. 术语和定义2.1 主设备(Master Device):通过IIC总线控制和发起通信的设备。

2.2 从设备(Slave Device):通过IIC总线接收和响应通信的设备。

2.3 时钟线(SCL):用于同步数据传输的时钟信号线。

2.4 数据线(SDA):用于传输数据的双向数据线。

2.5 起始条件(Start Condition):在通信开始时,主设备将SCL保持高电平,然后将SDA从高电平转为低电平。

2.6 停止条件(Stop Condition):在通信结束时,主设备将SCL保持高电平,然后将SDA从低电平转为高电平。

3. 物理层电气特性3.1 电压电平:3.1.1 高电平:大于等于0.7 * VDD,VDD为供电电压。

3.1.2 低电平:小于等于0.3 * VDD。

3.2 电平状态转换:3.2.1 所有电平状态的转换都必须在SCL为低电平时进行。

3.2.2 数据线(SDA)上的电平状态只能在SCL为低电平时发生改变。

3.3 上拉电阻:3.3.1 SCL线和SDA线上需要连接上拉电阻,以确保在无通信时线路保持高电平状态。

3.3.2 上拉电阻的阻值应根据系统设计和总线负载进行合理选择。

4. 数据传输格式4.1 数据帧:4.1.1 所有数据传输都以数据帧为单位进行。

4.1.2 数据帧由起始位、数据位、应答位和停止位组成。

4.2 传输顺序:4.2.1 数据位从高位到低位进行传输。

4.2.2 主设备发送数据帧时,从设备必须在每个数据位的传输结束后进行应答。

4.3 起始位和停止位:4.3.1 起始位由主设备发送,标志着数据传输的开始。

英语,I2C总线规范2.1部分

THE I2C-BUS SPECIFICATION VERSION 2.1JANUARY 200011 EXTENSIONS TO THE STANDARD-MODE I2C-BUS SPECIFICATIONThe Standard-mode I2C-bus specification, with its data transfer rate of up to 100 kbit/s and 7-bit addressing, has been in existence since the begin ning of the 1980’s. This concept rapidly grew in popularity and is today accepted worldwide as a de facto standard with several hundred different compatible ICs on offer from Philips Semiconductors and other suppliers. To meet the demands for higher speeds, as well as make available more slave address for the growing number of new devices, the Standard-mode I2C-bus specification was upgraded over the years and today is available with the following extensions:-mode, with a bit rate up to 400 kbit/s.-speed mode (Hs-mode), with a bit rate up to 3.4 Mbit/s.-bit addressing, which allows the use of up to 1024 additional slave addresses.There are two main reasons for extending the regular I2C-bus specification:d to transfer large amounts of serial data and require bit rates far in excess of 100 kbit/s (Standard-mode), or even 400 kbit/s (Fast-mode). As a result of continuing improvements in semiconductor technologies, I2C-bus devices are now available with bit rates of up to 3.4 Mbit/s (Hs-mode) without any noticeable increases in the manufacturingcost of the interface circuitry.-bit addressing scheme were soon allocated, it became apparent that more address combinations were required to prevent problems with the allocation of slave addresses for new devices. This problem was resolved with the new 10-bit addressing scheme, which allowed about a tenfold increase in available addresses.New slave devices with a Fast- or Hs-mode I2C-bus interface can have a 7- or a 10-bit slave address. If possible, a 7-bit address is preferred as it is the cheapesthardware solution and results in the shortest message length. Devices with 7- and10-bit addresses can be mixed in the same I2C-bus system regardless of whether it is an F/S- or Hs-mode system. Both existing and future masters can generate either 7- or 10-bit addresses.12 FAST-MODEWith the Fast-mode I2C-bus specification, the protocol,format, logic levels and maximum capacitive load for the SDA and SCL lines quoted in the Standard-modeI2C-bus specification are unchanged. New devices with an I2C-bus interface must meet at least the minimum requirements of the Fast- or Hs-mode specification (see Section 13).Fast-mode devices can receive and transmit at up to 400 kbit/s. The minimum requirement is that they can synchronize with a 400 kbit/s transfer; they can then prolong the LOW period of the SCL signal to slow down the transfer. Fast-mode devices are downward-compatible and can communicate with Standard-mode devices in a 0 to 100 kbit/s I2C-bus system. As Standard-mode devices, however, are not upward compatible, they should not be incorporated in a Fast-mode I2C-bus system as they cannot follow the higher transfer rate andunpredictable states would occur.The Fast-mode I2C-bus specification has the following additional features compared with the Standard-mode:signals has been adapted. There is no need for compatibility with other bus systems such as CBUS because they cannot operate at the increased bit rate.-mode devices incorporate spike suppression and a Schmitt trigger at the SDA and SCL inputs.-mode devices incorporate slope control of the falling edges of the SDA and SCL signals.-mode device is switched off, the SDA and SCL I/O pins must be floating so that they don’t obstruct the bus lines.-up devices connected to the bus lines must be adapted to accommodate the shorter maximum permissible rise time for the Fast-mode I2C-bus. For bus loads up to 200 pF, the pull-up device for each bus line can be a resistor; for bus loads between 200 pF and 400 pF, the pull-up device can be a current source (3 mA max.) or a switched resistor circuit (see Fig.43).13 Hs-MODEHigh-speed mode (Hs-mode) devices offer a quantum leap in I2C-bus transfer speeds. Hs-mode devices can transfer information at bit rates of up to 3.4 Mbit/s, yet they remain fully downward compatible with Fast- or Standard-mode (F/S-mode) devices for bi-directional communication in a mixed-speed bus system. With the exception that arbitration and clock synchronization is not performed during theHs-mode transfer, the same serial bus protocol and data format is maintained as with the F/S-mode system. Depending on the application, new devices may have a Fast or Hs-mode I2C-bus interface,although Hs-mode devices are preferred as they can be designed-in to a greater number of applications.13.1 High speed transferTo achieve a bit transfer of up to 3.4 Mbit/s the following improvements have been made to the regular I2C-bus specification:-mode master devices have an open-drain output buffer for the SDAH signal and a combination of an open-drain pull-down and current-source pull-up circuit on the SCLH output(1). This current-source circuit shortens the rise time of the SCLH signal. Only the current-source of one master is enabled at any one time,and only during Hs-mode.during Hs-mode transfer in multi-master systems, which speeds-up bit handling capabilities. The arbitration procedure always finishes after a preceding master code transmission inF/S-mode.-mode master devices generate a serial clock signal with a HIGH to LOW ratio of 1 to 2. This relieves the timing requirements for set-up and hold times.-mode master devices can have a built-in bridge(1). DuringHs-mode transfer, the high speed data (SDAH) and high-speed serial clock (SCLH) lines of Hs-mode devices are separated by this bridge from the SDA and SCL lines of F/S-mode devices. This reduces the capacitive load of the SDAH and SCLH lines resulting in faster rise and fall times.-mode slave devices and F/S-mode slave devices is the speed at which they operate. Hs-mode slaves have open-drain output buffers on the SCLH and SDAH outputs. Optional pull-down transistors on the SCLH pin can be used to stretch the LOW level of the SCLH signal, although this is only allowed after the acknowledge bit in Hs-mode transfers.-mode devices incorporate spike suppression and a Schmitt trigger at the SDAH and SCLH inputs.-mode devices incorporate slope control of the falling edges of the SDAH and SCLH signals.Figure 20 shows the physical I2C-bus configuration in a system with onlyHs-mode devices. Pins SDA and SCL on the master devices are only used inmixed-speed bus systems and are not connected in an Hs-mode only system. In such cases, these pins can be used for otherfunctions.Optional series resistors Rs protect the I/O stages of the I2C-bus devices from high-voltage spikes on the bus lines and minimize ringing and interference.Pull-up resistors Rp maintain the SDAH and SCLH lines at a HIGH level when the bus is free and ensure the signals are pulled up from a LOW to a HIGH level within the required rise time. For higher capacitive bus-line loads (>100 pF), the resistor Rp can be replaced by external current source pull-ups to meet the rise time requirements. Unless proceeded by an acknowledge bit, the rise time of the SCLH clock pulses in Hs-mode transfers is shortened by the internal current-source pull-up circuit MCS of the active master.Fig.20 I2C-bus configuration with Hs-mode devices only(1) SDA and SCL are not used here but may be used for other functions.(2) To input filter.(3) Only the active master can enable its current-source pull-up circuit(4) Dotted transistors are optional open-drain outputs which can stretch the serial clock signal SCLH.13.2 Serial data transfer format in Hs-modeSerial data transfer format in Hs-mode meets the Standard-mode I2C-bus specification. Hs-mode can only commence after the following conditions (all of which are in F/S-mode):1. START condition (S)2. 8-bit master code (00001XXX)3. not-acknowledge bit (A)Figures 21 and 22 show this in more detail. This master code has two main functions:It allows arbitration and synchronization between competing masters atF/S-mode speeds, resulting in one winning master.It indicates the beginning of an Hs-mode transfer.Hs-mode master codes are reserved 8-bit codes, which are not used for slave addressing or other purposes. Furthermore, as each master has its own unique master code, up to eight Hs-mode masters can be present on the one I2C-bus system (although master code 0000 1000 should be reserved for test and diagnostic purposes).The master code for an Hs-mode master device is software programmable and is chosen by the System Designer.Arbitration and clock synchronization only take place during the transmission of the master code and not-acknowledge bit (A), after which one winning master remains active. The master code indicates to other devices that an Hs-mode transfer is to begin and the connected devices must meet the Hs-mode specification. As no device is allowed to acknowledge the master code, the master code is followed by a not-acknowledge (A).After the not-acknowledge bit (A), and the SCLH line has been pulled-up to a HIGH level, the active master switches to Hs-mode and enables (at time tH, seeFig.22) the current-source pull-up circuit for the SCLH signal. As other devices can delay the serial transfer before tH by stretching the LOW period of the SCLH signal, the active master will enable its current-source pull-up circuit when all devices have released the SCLH line and the SCLH signal has reached a HIGH level, thus speeding up the last part of the rise time of the SCLH signal.The active master then sends a repeated START condition (Sr) followed by a7-bit slave address (or 10-bit slave address, see Section 14) with a R/W bit address, and receives an acknowledge bit (A) from the selected slave.After a repeated START condition and after each acknowledge bit (A) ornot-acknowledge bit (A), the active master disables its current-source pull-up circuit. This enables other devices to delay the serial transfer by stretching the LOW period of the SCLH signal. The active master re-enables its current-source pull-up circuit again when all devices have released and the SCLH signal reaches a HIGH level, and so speeds up the last part of the SCLH signal’s rise time.Data transfer continues in Hs-mode after the next repeated START (Sr), and only switches back toF/S-mode after a STOP condition (P). To reduce the overhead of the master code, it’s possible that a master links a number of Hs-mode transfers, separated by repeated START conditions (Sr).Fig.21 Data transfer format in Hs-mode.Fig.22 A complete Hs-mode transfer.13.3 Switching from F/S- to Hs-mode and backAfter reset and initialization, Hs-mode devices must be in Fast-mode (which is in effect F/S-mode as Fast-mode is downward compatible with Standard-mode). Each Hs-mode device can switch from Fast- to Hs-mode and back and is controlled by the serial transfer on the I2C-bus.Before time t1 in Fig.22, each connected device operates in Fast-mode. Between times t1 and tH (this time interval can be stretched by any device) each connected device must recognize the “S 00001XXX A” sequence and has to switch its internal circuit from the Fast-mode setting to the Hs-mode setting. Between times t1 and tH the connected master and slave devices perform this switching by the followingactions.The active (winning) master:1. Adapts its SDAH and SCLH input filters according to the spike suppression requirement in Hs-mode.2. Adapts the set-up and hold times according to the Hs-mode requirements.3. Adapts the slope control of its SDAH and SCLH output stages according to the Hs-mode requirement.4. Switches to the Hs-mode bit-rate, which is required after time tH.5. Enables the current source pull-up circuit of its SCLH output stage at time tH.The non-active, or losing masters:1. Adapt their SDAH and SCLH input filters according to the spike suppression requirement in Hs-mode.2. Wait for a STOP condition to detect when the bus is free again.All slaves:1. Adapt their SDAH and SCLH input filters according to the spike suppression requirement in Hs-mode.2. Adapt the set-up and hold times according to the Hs-mode requirements. This requirement may already be fulfilled by the adaptation of the input filters.3. Adapt the slope control of their SDAH output stages, if necessary. For slave devices, slope control is applicable for the SDAH output stage only and, depending on circuit tolerances, both the Fast- and Hs-mode requirements may be fulfilled without switching its internal circuit.At time tFS in Fig.22, each connected device must recognize the STOP condition (P) and switch its internal circuit from the Hs-mode setting back to the Fast-mode setting as present before time t1. This must be completed within the minimum bus free time as specified in Table 5 according to the Fast-mode specification.13.4 Hs-mode devices at lower speed modesHs-mode devices are fully downwards compatible, and can be connected to anF/S-mode I2C-bus system (see Fig.23). As no master code will be transmitted in such a configuration, all Hs-mode master devices stay in F/S-mode and communicate atF/S-mode speeds with their current-source disabled. The SDAH and SCLH pins are used to connect to the F/S-mode bus system, allowing the SDA and SCL pins (if present) on the Hs-mode master device to be used for other functions.Fig.23 Hs-mode devices at F/S-mode speed(1) Bridge not used. SDA and SCL may have an alternative function.(2) To input filter.(3) The current-source pull-up circuit stays disabled.(4) Dotted transistors are optional open-drain outputs which can stretch the serial clock signal SCL.13.5 Mixed speed modes on one serial bus systemIf a system has a combination of Hs-, Fast- and/or Standard-mode devices, it’s possible, by using an interconnection bridge, to have different bit rates between different devices (see Figs 24 and 25).One bridge is required to connect/disconnect an Hs-mode section to/from anF/S-mode section at the appropriate time. This bridge includes a level shift function that allows devices with different supply voltages to be connected. For exampleF/S-mode devices with a VDD2 of 5 V can be connected to Hs-mode devices with a VDD1 of 3 V or less5 V tolerant. This bridge is incorporated in Hs-mode master devices and is completely controlled by the serial signals SDAH, SCLH, SDA and SCL. Such a bridge can be implemented in any IC as an autonomous circuit.TR1, TR2 and TR3 are N-channel transistors. TR1 and TR2 have a transfer gatefunction, and TR3 is an opendrain pull-down stage. If TR1 or TR2 are switched on they transfer a LOW level in both directions, otherwise when both the drain and source rise to a HIGH level there will be a high impedance between the drain and source of each switched on transistor. In the latter case, the transistors will act as a level shifter as SDAH and SCLH will be pulled-up to VDD1 and SDA and SCL will be pulled-up to VDD2During F/S-mode speed, a bridge on one of the Hs-mode masters connects the SDAH and SCLH lines to the corresponding SDA and SCL lines thus permittingHs-mode devices to communicate with F/S-mode devices at slower speeds. Arbitration and synchronization is possible during the total F/S-mode transfer between all connected devices as described in Section 8. During Hs-mode transfer, however, the bridge opens to separate the two bus sections and allows Hs-mode devices to communicate with each other at 3.4 Mbit/s. Arbitration between Hs-mode devices and F/S-mode devices is only performed during the master code (00001XXX), and normally won by one Hs-mode master as no slave address has four leading zeros. Other masters can win the arbitration only if they send a reserved 8-bit code (00000XXX). In such cases, the bridge remains closed and the transfer proceeds inF/S-mode. Table 3 gives the possible communication speeds in such a system.Fig.24 Bus system with transfer at Hs- and F/S-mode speeds(1) Bridge not used. SDA and SCL may have an alternative function.(2) To input filter.(3) Only the active master can enable its current-source pull-up circuit.(4) Dotted transistors are optional open-drain outputs which can stretch the serial clock signal SCLor SCLH.Table 3Communication bit-rates in a mixed speed bus system13.5.1 F/S-MODE TRANSFER IN A MIXED-SPEED BUS SYSTEMThe bridge shown in Fig.24 interconnects corresponding serial bus lines, forming one serial bus system. As no master code (00001XXX) is transmitted, thecurrent-source pull-up circuits stay disabled and all output stages are open-drain. All devices, including Hs-mode devices, communicate with each other according the protocol, format and speed of the F/S-mode I2C-busspecification.13.5.2 HS-MODE TRANSFER IN A MIXED-SPEED BUS SYSTEMFigure 25 shows the timing diagram of a complete Hs-mode transfer, which is invoked by a START condition, a master code, and a not-acknowledge A (atF/S-mode speed). Although this timing diagram is split in two parts, it should be viewed as one timing diagram were time point tH is a common point for both parts.Fig.25 A complete Hs-mode transfer in a mixed-speed bus system.The master code is recognized by the bridge in the active or non-active master (see Fig.24). The bridge performs the following actions:1. Between t1 and tH (see Fig.25), transistor TR1 opens to separate the SDAH and SDA lines, after which transistor TR3 closes to pull-down the SDA line to VSS.2. When both SCLH and SCL become HIGH (tH in Fig.25), transistor TR2 opens to separate the SCLH and SCL lines. TR2 must be opened before SCLH goes LOW after Sr.Hs-mode transfer starts after tH with a repeated START condition (Sr). During Hs-mode transfer, the SCL line stays at a HIGH and the SDA line at a LOW steady-state level, and so is prepared for the transfer of a STOP condition (P).After each acknowledge (A) or not-acknowledge bit (A) the active masterdisables its current-source pull-up circuit. This enables other devices to delay theserial transfer by stretching the LOW period of the SCLH signal. The active masterre-enables its current-source pull-up circuit again when all devices are released and the SCLH signal reaches a HIGH level, and so speeds up the last part of the SCLH signal’s rise time. In irregular situations, F/S-mode devices can close the bridge (TR1 and TR2 closed, TR3 open) at any time by pulling down the SCL line for at least 1 ms, e.g. to recover from a bus hang-up.Hs-mode finishes with a STOP condition and brings the bus system back into the F/S-mode. The active master disables its current-source MCS when the STOP condition (P) at SDAH is detected (tFS in Fig.25). The bridge also recognizes this STOP condition and takes the followingactions:1. Transistor TR2 closes after tFS to connect SCLH with SCL; both of which are HIGH at this time. Transistor TR3 opens after tFS, which releases the SDA line and allows it to be pulled HIGH by the pull-up resister Rp. This is the STOP condition for the F/S-mode devices. TR3 must open fast enough to ensure the bus free time between the STOP condition and the earliest nextSTART condition is according to the Fast-mode specification (see tBUF in Table 5).2. When SDA reaches a HIGH (t2 in Fig.25) transistor TR1 closes to connect SDAH with SDA. (Note:interconnections are made when all lines are HIGH, thus preventing spikes on the bus lines). TR1 and TR2 must be closed within the minimum bus free time according to the Fast-mode specification (see tBUF in Table 5).13.5.3 TIMING REQUIREMENTS FOR THE BRIDGE IN AMIXED-SPEED BUS SYSTEMIt can be seen from Fig.25 that the actions of the bridge at t1, tH and tFS must be so fast that it does not affect the SDAH and SCLH lines. Furthermore the bridge must meet the related timing requirements of the Fast-mode specification for the SDA and SCL lines.。

中文译文,I2C总线规范2.1

I2C总线规范2.12000年1月11.标准模式I2C总线规范的扩展标准模式I2C总线规范在80年代的初期已经存在,它规定数据传输速率可高达100kbit/s而且7位寻址。

这个概念在普及中迅速成长,今天它已经作为一个标准被全世界接受,而且Philips Semiconductors和其他供应商提供了几百种不同的兼容IC电路。

为了符合更高速度的要求以及制造更多可使用的从机地址给数量不断增长的新器件,标准模式I2C总线规范不断升级,到今天它提供了以下的扩展:快速模式速率高达400kbit/s。

高速模式Hs模式速率高达3.4Mbit/s。

10位寻址允许使用高达1024个额外的从机地址。

扩展I2C总线规范主要有两个原因:现在很多应用需要传输大量的串行数据,要求的速率远远超过100kbit/s (标准模式),甚至是400kbit/s快速模式。

半导体技术持续改进的结果使I2C 总线器件现在可以使用高达3.4Mbit/s(Hs模式)的速率,而且接口电路的生产成本没有任何明显的提高。

由于使用7位寻址策略的大多数地址能被立即分配,很显然要求更多地址结合来防止为新器件分配从机地址的问题。

这个问题可以用新的10位寻址策略解决,它允许可使用的地址成10倍增长。

带有快速或Hs模式I2C总线接口的新从机器件可以有7位或10位的从机地址。

如果可能的话,首选7位地址,因为它是最便宜的硬件解决方案,而且报文长度最短。

有7位和10位地址的器件可以在相同的I2C总线系统中混合使用,不需要考虑它是F/S模式还是Hs模式的系统。

现有的和未来的主机都能产生7位或10位地址。

12.快速模式已经在标准模式I2C总线规范提出的协议、格式、逻辑电平和SDA以及SCL 线的最大电容负载,在快速模式I2C总线规范都没有修改。

带I2C总线接口的新器件必须至少符合快速模式或Hs模式规范的最小要求(见第13章)。

快速模式器件可以在400kbit/s下接收和发送。

I2c总线协议

1.I2C协议2条双向串行线,一条数据线SDA,一条时钟线SCL。

SDA传输数据是大端传输,每次传输8bit,即一字节。

支持多主控(multimastering),任何时间点只能有一个主控。

总线上每个设备都有自己的一个addr,共7个bit,广播地址全0.系统中可能有多个同种芯片,为此addr分为固定部分和可编程部份,细节视芯片而定,看datasheet。

1.1 I2C位传输数据传输:SCL为高电平时,SDA线若保持稳定,那么SDA上是在传输数据bit;若SDA发生跳变,则用来表示一个会话的开始或结束(后面讲)数据改变:SCL为低电平时,SDA线才能改变传输的bit1.2 I2C开始和结束信号开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

1.3 I2C应答信号Master每发送完8bit数据后等待Slave的ACK。

即在第9个clock,若从IC发ACK,SDA会被拉低。

若没有ACK,SDA会被置高,这会引起Master发生RESTART或STOP流程,如下所示:1.4 I2C写流程写寄存器的标准流程为:1. Master发起START2. Master发送I2C addr(7bit)和w操作0(1bit),等待ACK3. Slave发送ACK4. Master发送reg addr(8bit),等待ACK5. Slave发送ACK6. Master发送data(8bit),即要写入寄存器中的数据,等待ACK7. Slave发送ACK8.第6步和第7步可以重复多次,即顺序写多个寄存器9. Master发起STOP写一个寄存器写多个寄存器1.5 I2C读流程读寄存器的标准流程为:1. Master发送I2C addr(7bit)和w操作1(1bit),等待ACK2. Slave发送ACK3. Master发送reg addr(8bit),等待ACK4. Slave发送ACK5. Master发起START6. Master发送I2C addr(7bit)和r操作1(1bit),等待ACK7. Slave发送ACK8. Slave发送data(8bit),即寄存器里的值9. Master发送ACK10.第8步和第9步可以重复多次,即顺序读多个寄存器读一个寄存器读多个寄存器2. PowerPC的I2C实现Mpc8560的CCSR中控制I2C的寄存器共有6个。

IIC_讲解

27

当所有有关的器件数完了它们的低电平周 期后,时钟线被释放并变成高电平。之后, 器件时钟和SCL 线的状态没有差别。而且 所有器件会开始数它们的高电平周期。首 先完成高电平周期的器件会再次将SCL 线 拉低。 这样,产生的同步SCL时钟的低电平周期由 低电平时钟周期最长的器件决定,而高电 平周期由高电平时钟周期最短的器件决定。

8

9

I2C 总线是一个多主机的总线。这就是说可以连接多于一 个能控制总线的器件到总线。由于主机通常是 微控制器, 让我们考虑以下数据在两个连接到 I2C 总线的微控制器 之间传输的情况(见图 2)

10

这突出了 I2C总线的主机—从机和接收器—发送器的关系。 应当注意的是:这些关系不是持久的,只由当时数据传输 的方向决定。传输数据的过程如下: 1)假如微控制器A要向B发送信息: 微控制器A(主控器)寻址微控制器B(被控器) 微控制器A(主发送器)发送数据到微控制器B 微控制器A结束传输 2)如果微控制器A要从B接收信息: 微控制器A(主控器)寻址微控制器B(被控器) 微控制器A(主接收器)从微控制器B(从发送器)接收数据 微控制器A结束传输 在此情况下,主控器(微控制器A)产生定时信号并终止 传输。

IIC总线概念

I2C总线支持任何IC生产过程(NMOS、CMOS、 双极性)。两线――串行数据(SDA)和串行时钟 (SCL)线在连接到总线的器件间传递信息。每个 器件都有一个唯一的地址识别(无论是微控制器、 LCD 驱动器、存储器或键盘接口),而且都可以 作为一个发送器或接收器(由器件的功能决定)。 很明显,LCD 驱动器只是一个接收器,而存储器 则既可以接收又可以发送数据。除了发送器和接 收器外,器件在执行数据传输时也可以被看作是 主机或从机(见表 1)。主机是初始化总线的数 据传输并产生允许传输的时钟信号的器件。此时, 任何被寻址的器件都被认为是从机。

I2C协议V2.1_中文版

11 标准模式 I2C 总线规范的扩展 ............................................................................. 16 12 快速模式 ............................................................................................................. 17 13 Hs 模式 ............................................................................................................... 17

8 仲裁和时钟发生 .................................................................................................... 10

IIC总线协议

IIC总线协议IIC总线协议是一种串行通信协议,也被称为I2C(Inter-Integrated Circuit)总线协议。

它是由飞利浦公司(现在的恩智浦半导体公司)于1982年开发的,旨在提供一种简单、高效的通信方式,用于连接微控制器、传感器、存储器以及其他外设。

1. 引言IIC总线协议旨在实现多个设备之间的通信,通过两根线(SDA和SCL)进行数据传输。

该协议具有以下特点:简单、灵活、可扩展、多主机支持、多从机支持等。

2. 协议规范2.1 物理层规范IIC总线协议使用开漏输出,即总线上的设备只能拉低总线,而不能将总线拉高。

SDA线上的数据传输是双向的,而SCL线上的时钟信号是单向的。

2.2 逻辑层规范IIC总线协议使用起始位、地址位、数据位、应答位和停止位来组成数据帧。

起始位用于指示数据传输的开始,停止位用于指示数据传输的结束。

地址位用于指定设备的地址,数据位用于传输实际的数据。

应答位用于确认数据的接收情况。

2.3 时序规范IIC总线协议的时序由主机设备控制。

主机设备发送时钟信号,根据时钟信号的上升沿和下降沿来进行数据的传输和接收。

每个数据位都在时钟信号的下降沿进行传输。

3. 数据传输3.1 主机模式在主机模式下,主机设备负责发起通信,并控制总线上的数据传输。

主机设备首先发送起始位,然后发送设备地址,接着发送数据位,并等待从机设备的应答。

主机设备可以在传输过程中发送多个数据帧,并在最后发送停止位。

3.2 从机模式在从机模式下,从机设备等待主机设备的指令,并根据指令进行数据的接收或发送。

从机设备接收到起始位和地址位后,会检查地址是否匹配,如果匹配则进行数据的接收或发送,并发送应答位。

4. 错误处理IIC总线协议提供了多种错误处理机制,以确保数据的可靠传输。

例如,如果主机设备在发送数据位后没有接收到从机设备的应答位,则可以进行重试操作。

此外,总线上还可以使用时钟拉伸机制,即从机设备可以拉低时钟信号,以便主机设备有足够的时间处理数据。

I2C总线规范

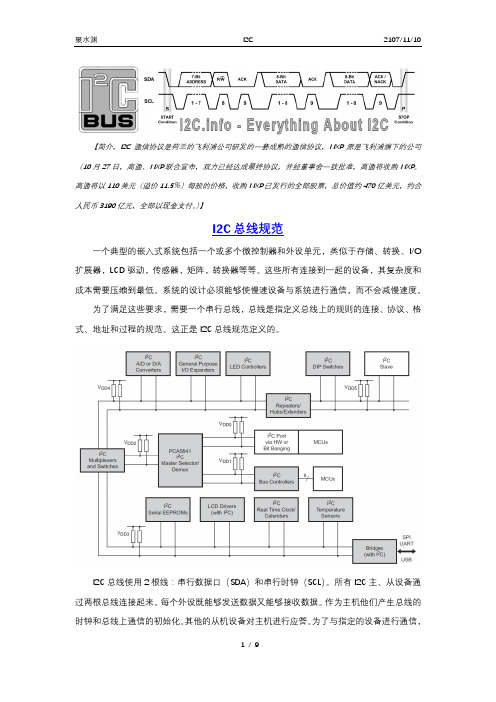

【简介,I2C通信协议是荷兰的飞利浦公司研发的一套成熟的通信协议,NXP原是飞利浦旗下的公司(10月27日,高通、NXP联合宣布,双方已经达成最终协议,并经董事会一致批准,高通将收购NXP。

高通将以110美元(溢价11.5%)每股的价格,收购NXP已发行的全部股票,总价值约470亿美元,约合人民币3190亿元,全部以现金支付。

)】I2C总线规范一个典型的嵌入式系统包括一个或多个微控制器和外设单元,类似于存储、转换、I/O 扩展器,LCD驱动,传感器,矩阵,转换器等等。

这些所有连接到一起的设备,其复杂度和成本需要压缩到最低。

系统的设计必须能够使慢速设备与系统进行通信,而不会减慢速度。

为了满足这些要求,需要一个串行总线,总线是指定义总线上的规则的连接、协议、格式、地址和过程的规范。

这正是I2C总线规范定义的。

I2C总线使用2根线:串行数据口(SDA)和串行时钟(SCL)。

所有I2C主、从设备通过两根总线连接起来。

每个外设既能够发送数据又能够接收数据。

作为主机他们产生总线的时钟和总线上通信的初始化。

其他的从机设备对主机进行应答。

为了与指定的设备进行通信,每个在总线上的从机设备必须拥有唯一的设备地址。

主设备可以没有主机地址,因为主机不需要其他设备对其发送命令,然后产生应答。

I2C时序发送者这是传输数据到总线的设备接受者这是从总线接收数据的设备主机:这是一个产生时钟信号,开始通信指令,和发送I2C指令,和停止通信的指令。

从机:这是一个监听总线信号,回信息给主机的设备多主机:I2C可以有跟多的主机每个主机都可以发送命令给从机仲裁:当更多的主设备需要占用总线时,一个确定总线上的主机可以使用它同步:在一个或者多个设备上处理同步时钟信号总线信号SCL和SDA信号都是双向的。

他们通过连接正电极的两个电阻进行供电。

这意味着当总线空闲时,两根线都是高电平,总线上的所有设备都必须有开槽或开漏针。

激活这条线意味着把它拉下来(有线和)。

I2C通讯协议

I2C通讯协议协议名称:I2C通讯协议一、引言I2C通讯协议是一种串行通信协议,用于在集成电路(IC)之间进行数据传输。

本协议旨在规范I2C通讯的格式、电气特性和传输速率,以确保不同设备之间的互操作性和数据的可靠传输。

二、定义1. I2C总线:由两根双向线(SDA和SCL)组成的串行总线,用于设备之间的通信。

2. 主设备(Master):发起I2C通讯的设备,负责控制总线的时序和数据传输。

3. 从设备(Slave):响应主设备的指令并提供数据的设备。

三、电气特性1. 电压级别:I2C总线使用标准逻辑电平,高电平为V_H,低电平为V_L,其中V_H > 2.1V,V_L < 0.9V。

2. 上拉电阻:SDA和SCL线上需连接上拉电阻,以确保线路空闲时为高电平状态。

四、物理连接1. SDA线:用于数据传输的双向线。

2. SCL线:用于时钟同步的线。

3. 地线:用于连接设备的共地。

五、通讯流程1. 总线空闲状态:SDA和SCL线均为高电平。

2. 起始信号:主设备将SDA线由高电平拉低,然后将SCL线拉低,表示通讯开始。

3. 地址传输:主设备发送从设备的地址和读/写位到SDA线上。

4. 从设备应答:从设备接收到地址后,根据自身地址是否匹配,发送应答信号(ACK/NACK)到SDA线上。

5. 数据传输:主设备和从设备通过SDA线传输数据,每传输8位数据后,接收方发送应答信号。

6. 停止信号:主设备将SCL线拉高,然后将SDA线由低电平拉高,表示通讯结束。

六、数据传输格式1. 起始信号:SDA线由高电平拉低,然后将SCL线拉低。

2. 7位从设备地址:主设备发送从设备的7位地址到SDA线上,最高位为读/写位。

3. 应答信号:从设备接收到地址后,发送应答信号(ACK/NACK)到SDA线上。

4. 数据传输:主设备和从设备通过SDA线传输数据,每传输8位数据后,接收方发送应答信号。

5. 停止信号:主设备将SCL线拉高,然后将SDA线由低电平拉高。

I2C总线协议讲述

I2C总线详细介绍FC是一种串行•总线的外设接口•它采用同步方式串行接收或发送信息,两个设备任同一个时钟卜•工作。

PC总线只用两根线:串行数拯SDA (Serial Data).串行时钟SCL (Serial Clock)。

由于Fc只有-•根数据线.因此其发送信息和接收信息不能同时进行。

信息的发送和接收只能分时进行。

I2C 串行总线工作时传输速率址高町达400K bit/so卩C总线上的所有器件的SDA线并接在一起.所有器件的SCL线并接在一起.且SDA线和SCL线必须通过上拉电阻连接到正电源。

Fc总线的数拯传输协议要比SPI总线复杂一些,因为Fc总线器件没有片选控制线.所以卩c总线数抑:传输的开始必须由主器件产生通信的开始条件(SCL高电平时.SDA产生负跳变):通信结束时,由主器件产生通信的结束条件(SCL高电平时.SDA产生正跳变》。

SDA线上的数拥任SCL高电平期间必须保持稳定,否则会被误认为开始条件或结束*件,只有在SCL低电平期间才能改变SDA线上的数抑;。

FC总线的数据传输波形图如卜图所示。

I2C应用实例AT24C系列为美IB ATMEL公司推出的帘行COMS型E2PROM.具有功耗小.宽电压范国等优点。

卜图为AT24C 系列E2PROM的引脚图。

图中AO、AK A2为器件地址引脚,Vss为地,Vcc为正电源.WP为写保护.SCL为串行时钟线.SDA为串行数据线。

AT24C系列E2PROM采用FC总线• FC总线上可挂接多个接口器件•在PC 总线上的每个器件应有唯一的器件地址.按I,C总线规则,器件地址为7位二进制数•它与一位数据方向位构成一个器件寻址字节。

器件寻址字节的最低位(D0)为方向位(i卖/写),最高4位(D7、D4)为器件型号地址(不同的FC总线接口器件的型号地址由厂家给定■ AT24C系列E2PROM的型号地址都为1010):其余3位(D3~D1)与器件引脚地址A2A1A0相对应。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

THE I2C-BUS SPECIFICATIONVERSION 2.1JANUARY 2000CONTENTS1PREFACE. . . . . . . . . . . . . . . . . . . . . . . . . . .3 1.1Version 1.0 - 1992. . . . . . . . . . . . . . . . . . . . 3 1.2Version 2.0 - 198. . . . . . . . . . . . . . . . . . . . . 3 1.3Version 2.1 - 1999. . . . . . . . . . . . . . . . . . . . 3 1.4Purchase of Philips I2C-bus components . . 3 2THE I2C-BUS BENEFITS DESIGNERSAND MANUFACTURERS. . . . . . . . . . . . . . .4 2.1Designer benefits . . . . . . . . . . . . . . . . . . . . 4 2.2Manufacturer benefits. . . . . . . . . . . . . . . . . 6 3INTRODUCTION TO THE I2C-BUSSPECIFICATION . . . . . . . . . . . . . . . . . . . . .6 4THE I2C-BUS CONCEPT . . . . . . . . . . . . . . .6 5GENERAL CHARACTERISTICS . . . . . . . . .8 6BIT TRANSFER . . . . . . . . . . . . . . . . . . . . . .8 6.1Data validity . . . . . . . . . . . . . . . . . . . . . . . . 8 6.2START and STOP conditions. . . . . . . . . . . 9 7TRANSFERRING DATA. . . . . . . . . . . . . . .10 7.1Byte format . . . . . . . . . . . . . . . . . . . . . . . . 10 7.2Acknowledge. . . . . . . . . . . . . . . . . . . . . . . 10 8ARBITRATION AND CLOCKGENERATION . . . . . . . . . . . . . . . . . . . . . .11 8.1Synchronization . . . . . . . . . . . . . . . . . . . . 11 8.2Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . 12 8.3Use of the clock synchronizingmechanism as a handshake. . . . . . . . . . . 13 9FORMATS WITH 7-BIT ADDRESSES. . . .13 107-BIT ADDRESSING . . . . . . . . . . . . . . . . .15 10.1Definition of bits in the first byte . . . . . . . . 15 10.1.1General call address. . . . . . . . . . . . . . . . . 16 10.1.2START byte . . . . . . . . . . . . . . . . . . . . . . . 17 10.1.3CBUS compatibility. . . . . . . . . . . . . . . . . . 18 11EXTENSIONS TO THE STANDARD-MODE I2C-BUS SPECIFICATION . . . . . . .19 12FAST-MODE. . . . . . . . . . . . . . . . . . . . . . . .19 13Hs-MODE . . . . . . . . . . . . . . . . . . . . . . . . . .20 13.1High speed transfer. . . . . . . . . . . . . . . . . . 20 13.2Serial data transfer format in Hs-mode. . . 21 13.3Switching from F/S- to Hs-mode andback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2313.4Hs-mode devices at lower speed modes. . 24 13.5Mixed speed modes on one serial bussystem. . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 13.5.1F/S-mode transfer in a mixed-speed bussystem. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 13.5.2Hs-mode transfer in a mixed-speed bussystem. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 13.5.3Timing requirements for the bridge in amixed-speed bus system. . . . . . . . . . . . . . 27 1410-BIT ADDRESSING. . . . . . . . . . . . . . . . 27 14.1Definition of bits in the first two bytes. . . . . 27 14.2Formats with 10-bit addresses. . . . . . . . . . 27 14.3General call address and start byte with10-bit addressing. . . . . . . . . . . . . . . . . . . . 30 15ELECTRICAL SPECIFICATIONSAND TIMING FOR I/O STAGESAND BUS LINES. . . . . . . . . . . . . . . . . . . . 30 15.1Standard- and Fast-mode devices. . . . . . . 30 15.2Hs-mode devices. . . . . . . . . . . . . . . . . . . . 34 16ELECTRICAL CONNECTIONS OFI2C-BUS DEVICES TO THE BUS LINES . 37 16.1Maximum and minimum values ofresistors R p and R s for Standard-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 39 17APPLICATION INFORMATION. . . . . . . . . 41 17.1Slope-controlled output stages ofFast-mode I2C-bus devices. . . . . . . . . . . . 41 17.2Switched pull-up circuit for Fast-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 41 17.3Wiring pattern of the bus lines. . . . . . . . . . 42 17.4Maximum and minimum values ofresistors R p and R s for Fast-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 42 17.5Maximum and minimum values ofresistors R p and R s for Hs-modeI2C-bus devices . . . . . . . . . . . . . . . . . . . . . 42 18BI-DIRECTIONAL LEVEL SHIFTERFOR F/S-MODE I2C-BUS SYSTEMS . . . . 42 18.1Connecting devices with differentlogic levels. . . . . . . . . . . . . . . . . . . . . . . . . 43 18.1.1Operation of the level shifter . . . . . . . . . . . 44 19DEVELOPMENT TOOLS AVAILABLEFROM PHILIPS. . . . . . . . . . . . . . . . . . . . . 45 20SUPPORT LITERATURE . . . . . . . . . . . . . 461PREFACE1.1Version 1.0 - 1992This version of the 1992 I2C-bus specification includes the following modifications:•Programming of a slave address by software has been omitted. The realization of this feature is rather complicated and has not been used.•The “low-speed mode” has been omitted. This mode is, in fact, a subset of the total I2C-bus specification and need not be specified explicitly.•The Fast-mode is added. This allows a fourfold increase of the bit rate up to 400kbit/s. Fast-mode devices are downwards compatible i.e. they can be used in a 0 to 100kbit/s I2C-bus system.•10-bit addressing is added. This allows 1024 additional slave addresses.•Slope control and input filtering for Fast-mode devices is specified to improve the EMC behaviour.NOTE: Neither the 100kbit/s I2C-bus system nor the 100kbit/s devices have been changed.1.2Version2.0 - 1998The I2C-bus has become a de facto world standard that is now implemented in over 1000 different ICs and licensed to more than 50 companies. Many of today’s applications, however, require higher bus speeds and lower supply voltages. This updated version of the I2C-bus specification meets those requirements and includes the following modifications:•The High-speed mode (Hs-mode) is added. This allows an increase in the bit rate up to 3.4Mbit/s. Hs-mode devices can be mixed with Fast- and Standard-mode devices on the one I2C-bus system with bit rates from 0 to 3.4Mbit/s.•The low output level and hysteresis of devices with a supply voltage of 2V and below has been adapted to meet the required noise margins and to remain compatible with higher supply voltage devices.•The 0.6V at 6mA requirement for the output stages of Fast-mode devices has been omitted.•The fixed input levels for new devices are replaced by bus voltage-related levels.•Application information for bi-directional level shifter is added.1.3Version2.1 - 2000Version 2.1 of the I2C-bus specification includes the following minor modifications:•After a repeated START condition in Hs-mode, it is possible to stretch the clock signal SCLH (see Section13.2 and Figs22, 25 and 32).•Some timing parameters in Hs-mode have been relaxed (see Tables6 and 7).1.4Purchase of Philips I2C-bus componentsPurchase of Philips I2C components conveys a license under the Philips’ I2C patent to use thecomponents in the I2C system provided the system conforms to the I2C specification defined byPhilips.2THE I2C-BUS BENEFITS DESIGNERS AND MANUFACTURERSIn consumer electronics, telecommunications and industrial electronics, there are often many similarities between seemingly unrelated designs. For example, nearly every system includes:•Some intelligent control, usually a single-chip microcontroller•General-purpose circuits like LCD drivers, remote I/O ports, RAM, EEPROM, or data converters•Application-oriented circuits such as digital tuning and signal processing circuits for radio and video systems, or DTMF generators for telephones with tone dialling.To exploit these similarities to the benefit of both systems designers and equipment manufacturers, as well as to maximize hardware efficiency and circuit simplicity, Philips developed a simple bi-directional 2-wire bus for efficient inter-IC control. This bus is called the Inter IC or I2C-bus. At present, Philips’ IC range includes more than 150 CMOS and bipolar I2C-bus compatible types for performing functions in all three of the previously mentioned categories. All I2C-bus compatible devices incorporate an on-chip interface which allows them to communicate directly with each other via the I2C-bus. This design concept solves the many interfacing problems encountered when designing digital control circuits.Here are some of the features of the I2C-bus:•Only two bus lines are required; a serial data line (SDA) and a serial clock line (SCL)•Each device connected to the bus is software addressable by a unique address and simplemaster/slave relationships exist at all times; masters can operate as master-transmitters or as master-receivers•It’s a true multi-master bus including collision detection and arbitration to prevent data corruption if two or more masters simultaneously initiate data transfer•Serial, 8-bit oriented, bi-directional data transfers can be made at up to 100kbit/s in the Standard-mode, up to 400kbit/s in the Fast-mode, or up to 3.4Mbit/s in the High-speed mode•On-chip filtering rejects spikes on the bus data line to preserve data integrity •The number of ICs that can be connected to the same bus is limited only by a maximum bus capacitance of 400pF.Figure1 shows two examples of I2C-bus applications. 2.1Designer benefitsI2C-bus compatible ICs allow a system design to rapidly progress directly from a functional block diagram to a prototype. Moreover, since they ‘clip’ directly onto theI2C-bus without any additional external interfacing, they allow a prototype system to be modified or upgraded simply by ‘clipping’ or ‘unclipping’ ICs to or from the bus. Here are some of the features of I2C-bus compatible ICs which are particularly attractive to designers:•Functional blocks on the block diagram correspond with the actual ICs; designs proceed rapidly from block diagram to final schematic.•No need to design bus interfaces because the I2C-bus interface is already integrated on-chip.•Integrated addressing and data-transfer protocol allow systems to be completely software-defined•The same IC types can often be used in many different applications•Design-time reduces as designers quickly become familiar with the frequently used functional blocks represented by I2C-bus compatible ICs•ICs can be added to or removed from a system without affecting any other circuits on the bus•Fault diagnosis and debugging are simple; malfunctions can be immediately traced•Software development time can be reduced by assembling a library of reusable software modules.In addition to these advantages, the CMOS ICs in theI2C-bus compatible range offer designers special features which are particularly attractive for portable equipment and battery-backed systems.They all have:•Extremely low current consumption•High noise immunity•Wide supply voltage range•Wide operating temperature range.Fig.1 Two examples of I 2C-bus applications: (a) a high performance highly-integrated TV set(b) DECT cordless phone base-station.handbook, full pagewidthSDA SCLMICRO-CONTROLLER PCB83C528PLLSYNTHESIZERTSA5512NON-VOLATILE MEMORY PCF8582ESTEREO / DUAL SOUND DECODER TDA9840HI-FI AUDIOPROCESSOR TDA9860SINGLE-CHIP TEXT SAA52XXM/S COLOUR DECODER TDA9160APICTURE SIGNALIMPROVEMENTTDA4670VIDEOPROCESSORTDA4685ON-SCREENDISPLAYPCA8510(a)MSB575SDASCLLINEINTERFACEPCA1070BURST MODE CONTROLLERPCD5042ADPCMPCD5032(b)DTMFGENERATOR PCD3311MICRO-CONTROLLER P80CLXXX2.2Manufacturer benefitsI2C-bus compatible ICs don’t only assist designers, they also give a wide range of benefits to equipment manufacturers because:•The simple 2-wire serial I2C-bus minimizes interconnections so ICs have fewer pins and there are not so many PCB tracks; result - smaller and less expensive PCBs•The completely integrated I2C-bus protocol eliminates the need for address decoders and other ‘glue logic’•The multi-master capability of the I2C-bus allows rapid testing and alignment of end-user equipment via external connections to an assembly-line•The availability of I2C-bus compatible ICs in SO (small outline), VSO (very small outline) as well as DIL packages reduces space requirements even more. These are just some of the benefits. In addition, I2C-bus compatible ICs increase system design flexibility by allowing simple construction of equipment variants and easy upgrading to keep designs up-to-date. In this way, an entire family of equipment can be developed around a basic model. Upgrades for new equipment, or enhanced-feature models (i.e. extended memory, remote control, etc.) can then be produced simply by clipping the appropriate ICs onto the bus. If a larger ROM is needed, it’s simply a matter of selecting a micro-controller with a larger ROM from our comprehensive range. As new ICs supersede older ones, it’s easy to add new features to equipment or to increase its performance by simply unclipping the outdated IC from the bus and clipping on its successor.3INTRODUCTION TO THE I2C-BUS SPECIFICATION For 8-bit oriented digital control applications, such as those requiring microcontrollers, certain design criteria can be established:•A complete system usually consists of at least one microcontroller and other peripheral devices such as memories and I/O expanders•The cost of connecting the various devices within the system must be minimized •A system that performs a control function doesn’t require high-speed data transfer•Overall efficiency depends on the devices chosen and the nature of the interconnecting bus structure.To produce a system to satisfy these criteria, a serial bus structure is needed. Although serial buses don’t have the throughput capability of parallel buses, they do require less wiring and fewer IC connecting pins. However, a bus is not merely an interconnecting wire, it embodies all the formats and procedures for communication within the system.Devices communicating with each other on a serial bus must have some form of protocol which avoids all possibilities of confusion, data loss and blockage of information. Fast devices must be able to communicate with slow devices. The system must not be dependent on the devices connected to it, otherwise modifications or improvements would be impossible. A procedure has also to be devised to decide which device will be in control of the bus and when. And, if different devices with different clock speeds are connected to the bus, the bus clock source must be defined. All these criteria are involved in the specification of the I2C-bus.4THE I2C-BUS CONCEPTThe I2C-bus supports any IC fabrication process (NMOS, CMOS, bipolar). Two wires, serial data (SDA) and serial clock (SCL), carry information between the devices connected to the bus. Each device is recognized by a unique address (whether it’s a microcontroller, LCD driver, memory or keyboard interface) and can operate as either a transmitter or receiver, depending on the function of the device. Obviously an LCD driver is only a receiver, whereas a memory can both receive and transmit data. In addition to transmitters and receivers, devices can also be considered as masters or slaves when performing data transfers (see Table 1). A master is the device which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave.Table 1Definition of I 2C-bus terminologyThe I 2C-bus is a multi-master bus. This means that more than one device capable of controlling the bus can be connected to it. As masters are usually micro-controllers, let’s consider the case of a data transfer between two microcontrollers connected to the I 2C-bus (see Fig.2). This highlights the master-slave and receiver-transmitter relationships to be found on the I 2C-bus. It should be noted that these relationships are not permanent, but onlydepend on the direction of data transfer at that time. The transfer of data would proceed as follows:1) Suppose microcontroller A wants to send information to microcontroller B:•microcontroller A (master), addresses microcontroller B (slave)•microcontroller A (master-transmitter), sends data to microcontroller B (slave- receiver)•microcontroller A terminates the transfer2) If microcontroller A wants to receive information from microcontroller B:•microcontroller A (master) addresses microcontroller B (slave)•microcontroller A (master- receiver) receives data from microcontroller B (slave- transmitter)•microcontroller A terminates the transfer.Even in this case, the master (microcontroller A) generates the timing and terminates the transfer.The possibility of connecting more than onemicrocontroller to the I 2C-bus means that more than one master could try to initiate a data transfer at the same time. To avoid the chaos that might ensue from such an event - an arbitration procedure has been developed. Thisprocedure relies on the wired-AND connection of all I 2C interfaces to the I 2C-bus.If two or more masters try to put information onto the bus, the first to produce a ‘one’ when the other produces a ‘zero’ will lose the arbitration. The clock signals during arbitration are a synchronized combination of the clocks generated by the masters using the wired-AND connection to the SCL line (for more detailed information concerning arbitration see Section 8).TERM DESCRIPTIONT ransmitter The device which sends data to the busReceiver The device which receives data from the busMasterThe device which initiates a transfer, generates clock signals and terminates a transferSlave The device addressed by a master Multi-masterMore than one master can attempt to control the bus at the same time without corrupting the message ArbitrationProcedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to do so and the winning message is not corruptedSynchronizationProcedure to synchronize the clock signals of two or more devicesFig.2 Example of an I 2C-bus configuration using two microcontrollers.MBC645SDA SCLMICRO -CONTROLLER ASTATIC RAM OR EEPROMLCD DRIVERGATE ARRAYADCMICRO -CONTROLLER BGeneration of clock signals on the I 2C-bus is always the responsibility of master devices; each master generates its own clock signals when transferring data on the bus. Bus clock signals from a master can only be altered when they are stretched by a slow-slave device holding-down the clock line, or by another master when arbitration occurs.5GENERAL CHARACTERISTICSBoth SDA and SCL are bi-directional lines, connected to a positive supply voltage via a current-source or pull-up resistor (see Fig.3). When the bus is free, both lines are HIGH. The output stages of devices connected to the bus must have an open-drain or open-collector to perform the wired-AND function. Data on the I 2C-bus can be transferred at rates of up to 100kbit/s in theStandard-mode, up to 400kbit/s in the Fast-mode, or up to 3.4Mbit/s in the High-speed mode. The number ofinterfaces connected to the bus is solely dependent on the bus capacitance limit of 400pF. For information on High-speed mode master devices, see Section 13.6BIT TRANSFERDue to the variety of different technology devices (CMOS, NMOS, bipolar) which can be connected to the I 2C-bus, the levels of the logical ‘0’ (LOW) and ‘1’ (HIGH) are not fixed and depend on the associated level of V DD (see Section 15 for electrical specifications). One clock pulse is generated for each data bit transferred.6.1Data validityThe data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (see Fig.4).Fig.3 Connection of Standard- and Fast-mode devices to the I 2C-bus.MBC631SCLKN1OUT SCLK INSCLKDATAN1OUT DATA IN DEVICE 1SDA (Serial Data Line)SCL (Serial Clock Line)SCLKN2OUT SCLK INSCLK DATAN2OUT DATA IN DEVICE 2V DDR pR ppull-up resistorsFig.4 Bit transfer on the I 2C-bus.handbook, full pagewidthMBC621data line stable;data validchange of data allowedSDASCL6.2START and STOP conditionsWithin the procedure of the I 2C-bus, unique situations arise which are defined as START (S) and STOP (P) conditions (see Fig.5).A HIGH to LOW transition on the SDA line while SCL is HIGH is one such unique case. This situation indicates a START condition.A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition. This bus free situation is specified in Section 15.The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. In this respect, the START (S) and repeated START (Sr) conditions are functionally identical (see Fig. 10). For the remainder of this document, therefore, the S symbol will be used as a generic term to represent both the START and repeated START conditions, unless Sr is particularly relevant.Detection of START and STOP conditions by devices connected to the bus is easy if they incorporate the necessary interfacing hardware. However,microcontrollers with no such interface have to sample the SDA line at least twice per clock period to sense the transition.Fig.5 START and STOP conditions.handbook, full pagewidthMBC622SDA SCLPSTOP conditionSDASCLSSTART condition7TRANSFERRING DATA 7.1Byte formatEvery byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first (see Fig.6). If a slave can’t receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer thencontinues when the slave is ready for another byte of data and releases clock line SCL.In some cases, it’s permitted to use a different format from the I 2C-bus format (for CBUS compatible devices for example). A message which starts with such an address can be terminated by generation of a STOP condition, even during the transmission of a byte. In this case, no acknowledge is generated (see Section 10.1.3).7.2AcknowledgeData transfer with acknowledge is obligatory. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse.The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOWduring the HIGH period of this clock pulse (see Fig.7). Of course, set-up and hold times (specified in Section 15) must also be taken into account.Usually, a receiver which has been addressed is obliged to generate an acknowledge after each byte has been received, except when the message starts with a CBUS address (see Section 10.1.3).When a slave doesn’t acknowledge the slave address (for example, it’s unable to receive or transmit because it’s performing some real-time function), the data line must be left HIGH by the slave. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.If a slave-receiver does acknowledge the slave address but, some time later in the transfer cannot receive any more data bytes, the master must again abort the transfer. This is indicated by the slave generating thenot-acknowledge on the first byte to follow. The slave leaves the data line HIGH and the master generates a STOP or a repeated START condition.If a master-receiver is involved in a transfer, it must signal the end of data to the slave- transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave-transmitter must release the data line to allow the master to generate a STOP or repeated START condition.Fig.6 Data transfer on the I 2C-bus.handbook, full pagewidthMSC608Sr or PSDASrPSCLSTOP or repeated STARTconditionS or SrSTART or repeated STARTcondition12 3 - 89ACK9ACK7812MSBacknowledgement signal from slavebyte complete,interrupt within slaveclock line held low while interrupts are servicedacknowledgement signal from receiverFig.7 Acknowledge on the I 2C-bus.handbook, full pagewidthMBC602S START condition9821clock pulse for acknowledgementnot acknowledgeacknowledgeDATA OUTPUT BY TRANSMITTERDATA OUTPUT BY RECEIVERSCL FROM MASTER8ARBITRATION AND CLOCK GENERATION 8.1SynchronizationAll masters generate their own clock on the SCL line to transfer messages on the I 2C-bus. Data is only valid during the HIGH period of the clock. A defined clock is therefore needed for the bit-by-bit arbitration procedure to take place.Clock synchronization is performed using the wired-AND connection of I 2C interfaces to the SCL line. This meansthat a HIGH to LOW transition on the SCL line will cause the devices concerned to start counting off their LOW period and, once a device clock has gone LOW, it will hold the SCL line in that state until the clock HIGH state is reached (see Fig.8). However, the LOW to HIGH transition of this clock may not change the state of the SCL line if another clock is still within its LOW period. The SCL line will therefore be held LOW by the device with the longest LOW period. Devices with shorter LOW periods enter a HIGH wait-state during this time.Fig.8 Clock synchronization during the arbitration procedure.CLK 1CLK 2SCLcounter resetwait statestart counting HIGH periodMBC632When all devices concerned have counted off their LOW period, the clock line will be released and go HIGH. There will then be no difference between the device clocks and the state of the SCL line, and all the devices will start counting their HIGH periods. The first device to complete its HIGH period will again pull the SCL line LOW.In this way, a synchronized SCL clock is generated with its LOW period determined by the device with the longest clock LOW period, and its HIGH period determined by the one with the shortest clock HIGH period.8.2ArbitrationA master may start a transfer only if the bus is free. Two or more masters may generate a START condition within the minimum hold time (t HD;STA ) of the START condition which results in a defined START condition to the bus.Arbitration takes place on the SDA line, while the SCL line is at the HIGH level, in such a way that the master which transmits a HIGH level, while another master istransmitting a LOW level will switch off its DATA output stage because the level on the bus doesn’t correspond to its own level.Arbitration can continue for many bits. Its first stage is comparison of the address bits (addressing information is given in Sections 10 and 14). If the masters are each tryingto address the same device, arbitration continues with comparison of the data-bits if they are master-transmitter, or acknowledge-bits if they are master-receiver. Because address and data information on the I 2C-bus is determined by the winning master, no information is lost during the arbitration process.A master that loses the arbitration can generate clock pulses until the end of the byte in which it loses the arbitration.As an Hs-mode master has a unique 8-bit master code, it will always finish the arbitration during the first byte (see Section 13).If a master also incorporates a slave function and it loses arbitration during the addressing stage, it’s possible that the winning master is trying to address it. The losingmaster must therefore switch over immediately to its slave mode.Figure 9 shows the arbitration procedure for two masters. Of course, more may be involved (depending on how many masters are connected to the bus). The moment there is a difference between the internal data level of the master generating DATA 1 and the actual level on the SDA line, its data output is switched off, which means that a HIGH output level is then connected to the bus. This will not affect the data transfer initiated by the winning master.Fig.9 Arbitration procedure of two masters.handbook, full pagewidthMSC609DATA 1DATA 2SDASCLSmaster 1 loses arbitrationDATA 1 SDA。