按键消抖

按键消除抖动的措施

按键消除抖动的措施

按键消除抖动是指在使用电子设备中,当按下按键后可能会出

现的多次触发信号的问题。

为了解决这个问题,可以采取以下措施:

1. 软件滤波,在程序设计中,可以采用软件滤波的方法来消除

按键抖动。

软件滤波可以通过延时、状态机等方式来确保只有真正

的按键按下才会触发相应的操作,而忽略短暂的抖动信号。

2. 硬件滤波,在电路设计中,可以加入电容、电阻等元件来实

现硬件滤波,通过延长按键信号的上升沿或下降沿时间,从而消除

按键抖动带来的干扰。

3. 使用稳定的按键元件,选择质量好、稳定性高的按键元件,

可以减少按键抖动的发生。

4. 金属片设计,在按键设计中,可以添加金属片来增加按键的

稳定性,减少抖动。

5. 硬件消抖器,使用专门的硬件消抖器芯片,这些芯片可以自

动检测和消除按键抖动,提高按键的稳定性。

综上所述,消除按键抖动可以通过软件滤波、硬件滤波、选择稳定的按键元件、金属片设计以及使用硬件消抖器等多种措施来实现。

在实际应用中,可以根据具体情况选择合适的方法或者结合多种方法来解决按键抖动问题。

按键开关去抖动问题

目录

• 引言 • 按键开关抖动的常见解决方法 • 按键开关去抖动的原理 • 去抖动效果的评估和测试 • 实际应用中的按键开关去抖动案例

01

引言

按键开关去抖动的背景和重要性

按键开关在电子设备中广泛应用,但在实际使用中,由 于机械或电气噪声的影响,按键开关可能会出现抖动现 象,即开关状态在短时间内的快速切换。

结合硬件去抖和软件去抖的优点,先通过硬件电路对按键信号进行初步处理,再通过软件算法 进一步去除抖动。

互补滤波法

采用硬件滤波和软件滤波两种方法对按键信号进行互补处理,提高去抖效果。

04

去抖动效果的评估和测试

去抖动效果的评估方法

实际使用评估

在实际使用场景中,观察 按键开关去抖动的表现, 评估其稳定性和可靠性。

在智能家居领域,按键开关被广泛应用于各种智 能设备的控制面板上。由于用户操作频繁,按键 开关容易出现机械疲劳和抖动现象,影响设备的 正常使用。

通过采用去抖动技术,可以有效消除按键开关的 抖动现象,提高设备的响应速度和稳定性,提升 用户的使用体验。

汽车电子中的按键开关去抖动应用

在汽车电子领域,按键开关广泛应用于车载信息娱乐系统、空调控制、车窗升降 等系统中。由于汽车环境的复杂性和使用频率高,按键开关的抖动问题尤为突出 。

实验过程

在实验中模拟按键开关的 抖动情况,记录去抖动电 路的表现和性能数据。

数据处理

对实验数据进行处理和分 析,提取关键性能指标, 如抖动抑制时间、抑制率 等。

结果分析

根据实验结果,分析去抖 动电路的性能表现,评估 其优缺点和适用场景。

实际应用中的按键开关去抖

05

动案例

工业控制中的按键开关去抖动应用

vivado按键消抖原理

vivado按键消抖原理按键消抖是指在数字电路中,当按键按下或释放时,由于按键机械开关的特性,会导致电路出现不稳定的信号状态。

这种不稳定状态可能会导致错误的触发,例如出现多次触发或漏触发。

因此,为了确保按键信号的稳定性和可靠性,需要进行按键消抖处理。

按键消抖的原因主要有两个方面。

首先,按键机械开关的接触面存在微小的弹跳现象,当按键按下或释放时,接触面会在短时间内反复接触和分离,导致电路信号出现多次变化。

其次,由于电路中存在的噪声干扰,也会使得按键信号产生抖动。

为了解决按键消抖问题,可以采用硬件和软件两种方法。

硬件方法主要通过添加滤波电路或使用稳定的按键开关来消除按键弹跳现象。

滤波电路可以通过RC电路或者使用专用的按键消抖芯片来实现。

而软件方法主要通过在数字电路中添加按键消抖算法来处理按键信号。

在Vivado中,按键消抖可以通过使用状态机来实现。

状态机是一种用于描述系统行为的模型,可以根据输入信号的状态变化来改变系统的状态和输出。

在按键消抖中,可以使用状态机来检测按键信号的变化,并根据一定的状态转换规则来消除按键弹跳现象。

具体实现时,可以将按键信号作为输入,将按键状态和输出作为状态机的状态和输出。

当按键信号发生变化时,状态机会根据一定的状态转换规则进行状态转换,并输出消抖后的按键信号。

常用的状态转换规则包括按键按下时状态转换为按下状态,按键释放时状态转换为释放状态,以及连续按键时状态不变。

在Vivado中,可以使用Verilog或VHDL等硬件描述语言来编写状态机代码。

首先,需要定义状态机的输入、输出和状态变量,并初始化各个变量的初始值。

然后,需要编写状态转换规则和输出逻辑,根据输入信号的状态变化来改变状态和输出。

最后,需要将状态机代码综合生成对应的逻辑电路,并进行仿真和验证。

总结起来,按键消抖是数字电路设计中常见的问题,为了确保按键信号的稳定性和可靠性,需要进行按键消抖处理。

在Vivado中,可以使用状态机来实现按键消抖,通过定义状态转换规则和输出逻辑,消除按键弹跳现象。

按键消抖的原理

按键消抖的原理一、引言在电子设备中,按键是常见的输入方式。

然而,由于按键的机械结构,当按下或松开按键时,会产生机械弹跳现象,导致信号出现多次跳变,这就是所谓的“按键抖动”现象。

为了避免这种现象对电路造成干扰,需要进行按键消抖处理。

二、什么是按键消抖?按键消抖是指在接收到按键信号后,在一定时间内只处理一次信号,并且保证该信号为有效信号。

其目的是消除因机械结构引起的多次跳变信号。

三、按键消抖的原理1. 机械弹跳原理在了解按键消抖原理之前,需要先了解机械弹跳原理。

当按下或松开一个开关时,由于接触面积有限和金属表面不完全平整等因素影响,开关触点会发生不稳定震荡,并在短时间内反复接通和断开。

这种现象称为“机械弹跳”。

2. 软件处理原理软件处理原理是通过程序来实现对按键状态进行检测和判断的方式。

具体实现方法包括:轮询法、中断法、计时法等。

(1)轮询法轮询法是指通过循环检测按键状态的方式来实现按键消抖。

具体实现方法为:在主程序中设置一个循环,不断检测按键状态,当检测到按键被按下时,进行一定的延时后再次检测按键状态,如果依然是按下状态,则判断为有效信号。

(2)中断法中断法是指通过外部中断来实现对按键状态进行检测和判断的方式。

具体实现方法为:将按键连接到微控制器的外部中断引脚上,在程序中设置好相应的中断服务程序,当检测到外部中断信号时,进入相应的中断服务程序进行处理。

(3)计时法计时法是指通过定时器来实现对按键状态进行检测和判断的方式。

具体实现方法为:当检测到按键被按下时,启动定时器并开始计数,在一定时间内只处理一次信号,并保证该信号为有效信号。

四、硬件处理原理硬件处理原理是通过使用电路元件来实现对按键消抖的方式。

具体包括RC滤波器、Schmitt触发器、反相器等。

1. RC滤波器RC滤波器是将电容和电阻组合在一起,利用电容的充放电特性实现对信号的滤波。

当按键被按下时,由于电容的充放电时间常数较长,可以使机械弹跳信号被滤除。

键盘抖动消除方法

键盘抖动消除方法

键盘抖动是指在敲击键盘时手部或手臂的微小颤动,导致输入的文字不清晰或出现错别字等问题。

因此,很多用户都希望能够消除键盘抖动,提升打字的准确性和效率。

下面介绍几种实用的键盘抖动消除方法。

1. 改变坐姿和姿势

键盘抖动主要是由于手部和手臂的颤动引起的,因此改变打字时的坐姿和姿势可以有效减少颤动。

建议调整座椅和桌面的高度,使得手臂可以在自然状态下平放在桌面上,手腕和手臂之间的角度约为90度。

此外,保持良好的体姿和放松肌肉也有助于减少键盘抖动。

2. 练习手部稳定性

练习手部稳定性可以提高手部肌肉的控制力和协调性,从而减少键盘抖动。

可以通过一些简单的活动来锻炼手部稳定性,比如按摩手掌和手腕、做手部放松练习、在手心放一支笔并保持平衡等。

3. 使用键盘垫或鼠标垫

键盘垫和鼠标垫可以提供稳定的支撑,降低手部和手臂的抖动。

一些键盘垫还具有防滑和缓冲的功能,可以减少打字时的噪音和疲劳感。

4. 调整键盘反馈力度

键盘反馈力度较大时,敲击按键需要更大的力量,会增加手部和手臂的抖动。

因此,可以调整键盘反馈力度为轻按键。

这样不仅可以减少键盘抖动,还可以提高打字的速度和舒适度。

5. 使用语音输入

如果键盘抖动比较严重,可以尝试使用语音输入来代替打字。

语音输入可以通过输入语音指令来进行操作,不需要使用键盘进行输入,可以有效减少键盘抖动的问题。

总结起来,减少键盘抖动需要综合考虑多个方面,包括改变姿势、练习手部稳定性、使用适当的支撑工具、调整键盘反馈力度和使用语音输入等。

只要掌握了正确的方法,就可以提高打字的准确性和效率,避免键盘抖动的问题。

c语言按键消抖常用方法

在C语言中,按键消抖是指处理物理按键在按下或释放时可能产生的抖动或不稳定信号的问题。

常用的方法包括软件延时消抖和状态机消抖。

1. 软件延时消抖:- 当检测到按键按下或释放时,可以通过在代码中添加一个短暂的延时来过滤掉按键可能产生的抖动信号。

例如,在按键检测到变化后,延时几毫秒以确保按键信号稳定后再进行状态读取。

```cvoid delay(unsigned int ms) {unsigned int i, j;for (i = 0; i < ms; i++)for (j = 0; j < 300; j++);}// 在按键检测中使用延时if (button_pressed && !last_button_state) {delay(10); // 等待10毫秒if (button_pressed) {// 执行按键按下后的操作last_button_state = button_pressed;}}```这种方法简单易行,但需要根据具体硬件和按键特性调整延时时间,且可能会造成按键响应速度变慢。

2. 状态机消抖:- 利用状态机来跟踪按键状态变化,并在一定持续时间内保持一致的状态才认定为有效按键按下或释放。

这可以通过一个状态变量和定时器结合实现。

```cenum ButtonState {IDLE, PRESSED, RELEASED};enum ButtonState current_state = IDLE;unsigned int debounce_timer = 0;// 在按键检测中使用状态机void button_check() {switch (current_state) {case IDLE:if (button_pressed) {current_state = PRESSED;debounce_timer = 10; // 设定10毫秒的延时}break;case PRESSED:if (!button_pressed) {current_state = RELEASED;debounce_timer = 10; // 设定10毫秒的延时}break;case RELEASED:if (button_pressed) {current_state = PRESSED;debounce_timer = 10; // 设定10毫秒的延时}break;}if (debounce_timer > 0) {debounce_timer--;} else {if (current_state == PRESSED) {// 执行按键按下后的操作} else if (current_state == RELEASED) {// 执行按键释放后的操作}current_state = IDLE; // 处理完毕后返回IDLE状态 }}```这种方法相对于延时消抖更加灵活,可以根据具体需求设置不同的延时时间,并且不会影响整体的按键响应速度。

按键消抖原理

按键消抖原理

按键消抖原理是指通过某种方法在按键被按下或松开时,消除或减少按键的抖动现象,使输入信号得到稳定的识别和处理。

在实际应用中,按键在被按下或松开时,由于机械结构的原因,往往会引起按键的不稳定状态,表现为按键在短时间内多次触发开关。

这种按键抖动不仅会导致输入信号的波动,还可能对系统造成误操作或不良影响。

为了解决按键抖动问题,常用的按键消抖原理主要有以下几种:

1. 软件延时消抖:通过在程序中设定一个适当的延时时间,当按键被按下或松开后,延时一段时间再读取按键状态,以判断按键是否稳定。

如果经过延时后按键状态仍然相同,则可以认为按键已经稳定按下或松开,从而减少抖动的影响。

2. 硬件滤波消抖:通过在按键电路上设计滤波器或添加电容元件,可以对按键信号进行滤波处理,去除短时间内的干扰信号,使输入信号更加稳定。

常用的滤波电路包括RC滤波电路、OTA滤波电路等。

3. 状态改变检测消抖:在按键电路中,通过检测按键的状态变化来判断按键是否按下或松开。

当按键在短时间内发生多次状态变化时,只会认为按键状态发生了一次改变,从而忽略了抖动现象。

这种方式适用于按键状态改变的速度较慢的情况。

通过以上的按键消抖原理,可以有效地减少按键抖动现象,提

高按键输入的可靠性和稳定性。

在实际应用中,可以根据具体情况选择适合的原理和方法来实现按键消抖,以满足不同的需求。

verilog按键消抖原理

verilog按键消抖原理(原创版)目录1.Verilog 简介2.按键消抖的概念3.按键消抖的实现原理4.实际应用中的按键消抖设计5.总结正文【1.Verilog 简介】Verilog 是一种硬件描述语言,主要用于数字系统硬件的描述、模拟和验证。

在数字电路设计和 FPGA 开发领域,Verilog 被广泛应用。

通过Verilog,设计人员可以对硬件电路进行建模、模拟和验证,以确保设计满足性能要求。

【2.按键消抖的概念】按键消抖,又称按键去抖,是一种在按键输入过程中消除误触发的技术。

在实际应用中,按键输入可能会受到噪声、抖动等因素的影响,导致误触发。

按键消抖的目的就是消除这些干扰,确保按键输入的准确性。

【3.按键消抖的实现原理】按键消抖的实现原理主要有两种:软件消抖和硬件消抖。

(1)软件消抖:软件消抖是通过程序算法实现的。

在按键触发时,程序会检测按键触发信号是否满足一定的条件,例如连续触发次数、触发时间间隔等。

如果满足条件,则认为这是一个有效的按键触发,否则不予响应。

(2)硬件消抖:硬件消抖是通过硬件电路实现的。

硬件消抖电路通常包括滤波器、延迟器等组件。

当按键触发信号输入时,滤波器会滤除噪声,延迟器会消除触发信号的抖动,从而保证输出信号的稳定性。

【4.实际应用中的按键消抖设计】在实际应用中,按键消抖设计需要考虑多种因素,如按键触发信号的噪声、抖动特性,系统的响应速度等。

为了实现高效、可靠的按键消抖,设计人员需要对这些因素进行综合考虑,选择合适的消抖方案。

【5.总结】按键消抖是一种重要的技术,可以有效消除按键输入中的误触发,提高系统的稳定性和可靠性。

键盘的消抖原理

键盘的消抖原理键盘消抖是指在通过键盘输入时,对于一个按键在被按下到最终确认的过程中,可能会出现多次触发的情况,这样会导致输入数据错误,给使用者带来很大的困扰。

消抖技术旨在解决这一问题,通过特定的电路设计或编程算法,将输入信号进行抑制或过滤,以保证输入数据的准确性。

一、消抖技术的原理1. 机械式按键的消抖机械式按键的消抖主要是通过按键的物理特性来实现的。

当按键被按下时,按键头与底座之间会产生一定的位移或压缩,导致弹簧被压缩或弯曲,使得电路闭合,从而产生按键信号。

为了避免按键震动在电路中产生的反复触发问题,通常会在按键电路中加入一个RC电路或短暂延时电路。

在按键按下后,通过加电、蓄电和放电等过程,使得输入信号稳定下来,从而消除了多余的触发信号。

触摸式按键的消抖主要是通过电容值的变化来识别按键信号的。

当手指接触到触摸板时,会引起电容量的变化,从而识别出按下的位置和时间。

在识别过程中,通常利用滤波器或计数器进行信号的稳定化处理,消除不稳定的噪声输入。

还可以利用防误触算法,对快速按下和抬起的操作进行识别和排除。

矩阵式按键是由多个按键交错排列而成的,通过多个行列连接交叉的方式来实现按键的输入。

在输入时,需要依次扫描每个按键的状态,并将状态从矩阵输出到处理器或控制器中。

为了防止按键的反复触发,通常可以采用“按下即认为有效,抬起则认为无效”的算法,以保证输入数据的准确性。

还可以利用短暂延时电路或状态寄存器等技术来消除抖动干扰,从而有效地提高按键输入的精度和可靠性。

1. 电子游戏电子游戏是一种需要快速响应、高精度的应用场景,玩家需要在短时间内完成复杂的操作,并保证输入的准确性和流畅度。

此时,键盘消抖技术就显得尤为重要,可以有效消除按键的抖动和误触干扰,提高玩家的游戏体验和胜率。

2. 工控设备工控设备是一种需要高可靠性、稳定性和安全性的系统。

在工控设备中,键盘消抖技术可以保证输入的精度和可靠性,减少系统的故障率和维护成本。

按键消抖原理

按键消抖原理

按键消抖是指在按下按键后,由于机械原因或者信号干扰等因素导致按键在短时间内出现多次开关状态变化的现象,这种现象会给电子系统带来干扰和误判。

为了避免这种情况的发生,常常采用按键消抖技术。

按键消抖的原理是在按键输入电路中添加一个延时电路和滤波电路,可以在按键按下后延迟一段时间后再检测按键状态,同时通过滤波电路去除掉抖动信号,从而保证按键的稳定性和可靠性。

延时电路可以采用RC延时电路或者数字延时电路,其作用是在按键按下后,延迟一段时间再检测按键状态,这段时间一般为几毫秒至几十毫秒不等。

这样可以保证按键状态稳定后再进行后续处理,避免了抖动信号的影响。

滤波电路可以采用RC滤波电路或者数字滤波电路,其作用是去除掉按键抖动信号,只保留按键真实的状态信号。

这样可以保证按键状态的准确性和可靠性。

总之,按键消抖技术是保证电子系统稳定和可靠运行的重要技术手段。

- 1 -。

按键消抖原理

按键消抖原理

按键消抖原理是指在按下按键后,由于机械特性引起的按键跳动现象被过滤掉,保证按键信号的稳定性和可靠性。

按键消抖的实现原理通常是通过软件技术来实现。

下面将介绍两种常见的按键消抖原理。

1. 软件延时消抖原理:

在按键按下时,通过软件延时一段时间,然后再读取按键状态。

软件延时的作用是等待机械抖动的结束,只有当一段时间内按键状态保持不变时,才认为按键真正被按下。

这种方法简单易行,但缺点是消抖时间较长,响应速度较慢。

2. 状态扫描消抖原理:

在按键按下时,通过不断扫描按键状态来判断按键是否真正被按下。

状态扫描的过程是周期性地读取按键状态,如果发现连续几次读取到的按键状态相同,则认为按键稳定,即按键被按下。

这种方法比延时消抖的响应速度更快,但需要一个额外的线程或中断服务程序来执行状态扫描。

以上是两种常见的按键消抖原理,它们都能有效解决按键抖动问题,提高按键信号的稳定性和可靠性。

在具体应用中,可以根据需要选择适合的消抖原理来实现按键的稳定响应。

51单片机按键消抖程序原理

51单片机按键消抖程序原理一、引言按键消抖是嵌入式系统编程中常见的问题之一,尤其是在使用51单片机时。

51单片机是一款常用的微控制器,广泛应用于各种嵌入式系统中。

按键作为常见的输入设备,在51单片机应用中经常被使用。

由于按键的机械特性,当按键按下或释放时,会产生机械抖动,给系统带来误操作。

因此,了解并编写按键消抖程序对于保证系统的正常运行至关重要。

二、消抖原理按键消抖,简单来说,就是通过一定的算法,消除按键产生的机械抖动,从而准确识别按键的状态。

其原理主要基于以下两点:1.机械抖动的特点:按键的机械抖动主要表现为按键触点之间的快速开关,产生一系列微小的电信号。

这些信号通常包含真实的按键输入信号和噪声信号。

2.消抖算法:通过分析这些信号,识别出真实的按键输入信号,并忽略噪声信号,从而达到消除机械抖动的目的。

常用的消抖算法有阈值比较法、防抖延时法、防抖滤波法等。

三、消抖程序实现下面以51单片机为例,介绍一种简单的阈值比较法消抖程序实现:```cvoidkey_debounce(intkey_pin){//定义按键引脚intdebounce_time=50;//消抖时间,单位毫秒intthreshold=5;//阈值,可以根据实际情况调整intkey_state=0;//按键状态,初始化为0(未按下)intlast_key_state=0;//上一次的按键状态while(1){//读取按键状态key_state=digitalRead(key_pin);last_key_state=key_state;//判断按键是否按下if(key_state==LOW){//按键按下,开始消抖if(millis()-last_key_state>=debounce_time){//经过一定时间,确定按键状态if(key_state==digitalRead(key_pin)){//检测到真实的按键输入信号//这里可以进行相应的操作,例如点亮LED灯等}else{//检测到噪声信号或其他干扰,忽略}}else{//消抖时间不足,忽略当前状态}}else{//按键释放,忽略当前状态}}}```上述程序中,通过设置一个阈值和消抖时间,来判断按键状态是否发生变化。

详解MCU独立按键消抖,原因、方法统统都有

简单的说,进入了电子,不管是学纯模拟,还是学单片机,DSP、ARM等处理器,或者是我们的FPGA,一般没有不用到按键的地方。

按键:人机交互控制,主要用于对系统的控制,信号的释放等。

因此在这里,FPGA上应用的按键消抖动,也不得不讲!一、为什么要消抖动在按键被按下的短暂一瞬间,由于硬件上的抖动,往往会产生几毫秒的抖动,在这时候若采集信号,势必导致误操作,甚至系统崩溃;同样,在释放按键的那一刻,硬件上会相应的产生抖动,会产生同样的后果。

因此,在模拟或者数字电路中,我们要避免在最不稳定的时候采集信号,进行操作。

对此一般产用消抖动的原理。

一般可分为以下几种:(1)延时(2)N次低电平计数(3)低通滤波在数字电路中,一般产用(1)(2)种方法。

后文中将详细介绍。

二、各种消抖动1. 模拟电路按键消抖动对于模拟电路中,一般消抖动用的是电容消抖动或者施密特触发等电路,再次不做具体介绍。

2. 单片机中按键消抖动对于单片机中的按键消抖动,本节Bingo根据自己当年写过的单片机其中的一个代码来讲解,代码如下所示:针对以上代码,消抖动的顺序如下所示:(1)检测到信号(2)延时5ms,消抖动(3)继续检测信号,确认是否被按下a) 是,则开始等待释放b) 否,则返回0,退出(4)延时5ms,消抖动(5)确认,返回按下信号,退出当然在单片机中也可以循环计数来确认是否被按下。

Bingo认为如此,太耗MCU 资源,因此再次不做讲述。

3. FPGA中的按键消抖动对于FPGA中的消抖动,很多教科书上都没有讲述。

但Bingo觉得这个很有必要。

对于信号稳定性以及准确性分析,按键信号必须有一个稳定的脉冲,不然对系统稳定性有很大的干扰。

按键的硬件消抖电路原理

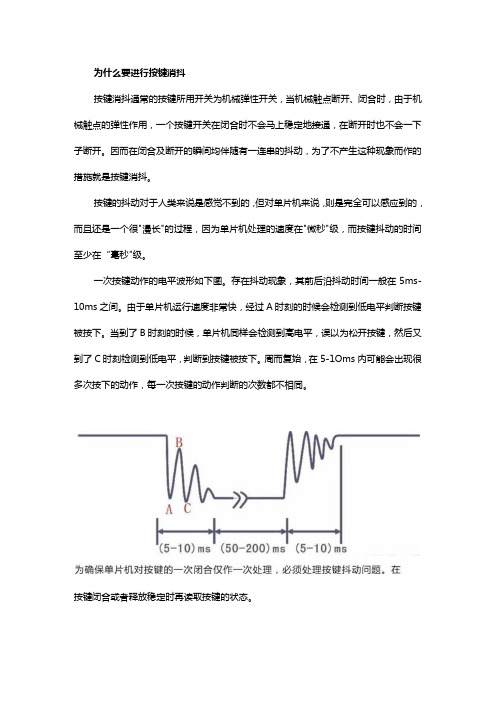

为什么要进行按键消抖按键消抖通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。

因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是按键消抖。

按键的抖动对于人类来说是感觉不到的,但对单片机来说,则是完全可以感应到的,而且还是一个很"漫长"的过程,因为单片机处理的速度在"微秒"级,而按键抖动的时间至少在“毫秒"级。

一次按键动作的电平波形如下图。

存在抖动现象,其前后沿抖动时间一般在5ms-10ms之间。

由于单片机运行速度非常快,经过A时刻的时候会检测到低电平判断按键被按下。

当到了B时刻的时候,单片机同样会检测到高电平,误以为松开按键,然后又到了C时刻检测到低电平,判断到按键被按下。

周而复始,在5-1Oms内可能会出现很多次按下的动作,每一次按键的动作判断的次数都不相同。

按键闭合或者释放稳定时再读取按键的状态。

硬件消抖电路硬件消抖一般有两种实现方式:ORS触发器O电谷滤波RS触发器利用RS触发器来吸收按键的抖动。

一旦有键按下,触发器立即翻转,触电的抖动便不会再对输出产生影响,按键释放时也一样。

RS触发电路消抖电路图如下。

电容滤波将电容并联在按键的两端,利用电容的放电的延时特性。

将产生抖动的电平通过电容吸收掉。

从而达到消抖的作用,电容消抖电路图如下图所示。

3V3Keyl6Slsw-PBzzLcι'O.IuFGND总结实际上,在没有MCU的情况下,对按键进行消抖通常是通过硬件消抖电路来实现。

而在嵌入式开发中,大多数情况下都是通过程序来实现按键消抖。

简单说就是加合适的延迟,显然这实现成本要比硬件电路方式低得多。

按键消抖原理

按键消抖原理

按键消抖通俗来说就是在按下或松开按键时,由于机械性能的限制,会出现短时间内多次开关状态的变化,这种现象称为按键抖动。

对于需要按键精准响应的电子设备而言,按键抖动会给正常使用带来很大的干扰。

按键消抖的原理是通过软件算法实现。

一般来说,消抖分为两个阶段:第一阶段叫做消除抖动,第二阶段叫做确认有效。

具体做法是在按键按下时,先等待一段时间(一般为几毫秒),然后读取按键的状态。

如果读取到的状态与第一次读取到的状态相同,就确认按键是有效的;如果读取到的状态与第一次不同,则重新进行第一阶段的消抖处理。

按键消抖的实现方法有多种,其中比较常见的是基于中断处理的方法和基于定时器的方法。

基于中断处理的方法是指在按键按下时,通过中断函数来响应按键事件,并进行消抖处理;基于定时器的方法是指通过定时器设定一定时间,在这段时间内进行按键状态的检测和消抖处理。

无论采用哪种方法,按键消抖的原理都是一样的。

综上所述,按键消抖是通过软件算法实现的,可以有效地消除按键抖动对电子设备的干扰。

在实际应用中,需要根据实际情况选择合适的消抖方法和参数,以达到最佳的按键响应效果。

- 1 -。

实验05按键消抖

实验5 按键消抖1. 实验目的1. 掌握QuartusII的硬件描述语言设计方法2. 了解同步计数器的原理及应用3. 设计一个带使能输入、进位输出及同步清零的增1四位N (N<16)进制同步计数器2. 准备知识在按键使用的过程中,常常遇到按键抖动的问题,开关在闭合(断开)的瞬间,不能一接触就一直保持导通(断开),因为开关的机械特性,重要经历接触-断开-再接触-再断开,最终稳定在接触位置,这就是开关的抖动,即虽然只是按下按键一次然后放掉,结果在按键信号稳定前后,竟出现了一些不该存在的噪声,这样就会引起电路的误动作。

在很多应用按键的场合,要求具有消抖措施。

按键抖动与开关的机械特性有关,其抖动期一般为5-10ms。

图5.1 按键电平抖动示意图按键的消除抖动分为硬件消除抖动和软件消除抖动。

硬件消除抖动一般采用滤波的方法,通常在按键两端并联一个1~10u左右的电容,有时这样也不能完全消除按键的抖动。

软件消除抖动的方法有多种,常用的是延时扫描和定时器扫描。

延时扫描其原理为:检测到按键操作后延时一端时间(如10ms)后,再检测是否为仍然为同样的按键操作状态,如果相同,就认为是进行了按键操作,然后对该操作进行相应的处理。

定时器扫描的原理是:每隔一端时间(几毫秒)扫描一次键盘,如果连续两次(或3次)的所获得的按键状态相同,就输出按键状态,然后再对这种按键状态进行处理,这里的扫描时间间隔和连续判断按键状态的次数是有关系的,一般总时间要大于按键的抖动期。

如果总时间太长,则感觉按键迟钝,太短可能不能完全消除抖动,要根据实际的情况合适的选择。

在实际电路设计中,经常采用的是软硬件相结合对按键进行消除抖动的处理方法。

本实验采用的方法:实验箱按键的硬件电路是共阳极电路,按下按键时输出到FPGA管脚的电平为低电平,松开按键时为高电平。

我们采用5ms的定时器扫描FPGA管脚电平,如果连续3次为低电平时,存储连续按键状态的次数CNT的值加1,直到该计数值等于10(或再大一些),就不再累加(防止长按该值溢出而重新计数),此时认为按键已稳定,输出按键操作标志;在该过程中,一旦FPGA管脚电平为低电平就对CNT复位清零并同时对按键操作标志位复位,即一个异步复位。

按键消抖的原理

按键消抖的原理引言按键消抖是电子设备中常见的一种技术处理方式,用于解决按键在按下或松开时可能出现的多次触发的问题。

本文将介绍按键消抖的原理、常见的实现方法以及应用场景。

什么是按键消抖?当我们按下或松开一个物理按键时,由于按键弹性或机械性能的原因,按键可能会在短时间内多次切换状态。

这种多次切换状态的现象被称为按键抖动。

按键消抖的目的是通过软件或硬件的方式,保证在按下或松开一个按键时,系统只识别一次按键操作,而不是多次。

按键消抖的原理按键消抖的原理是通过延时和状态稳定来处理按键信号。

通常情况下,按键的信号变化是非常快速的,因此需要通过延时来等待按键信号稳定。

延时的时间设置要根据按键的特性及使用环境而定,一般情况下,10毫秒的延时已经足够。

具体的按键消抖原理如下: 1. 监测按键状态:通过采集按键的电压信号或连接处的电流变化,检测按键的状态。

2. 检测按键抖动:将检测到的按键状态与先前的状态进行比较,判断是否出现按键抖动。

3. 延时处理:当检测到按键状态发生变化时,延时一段时间,等待按键信号稳定。

这段时间的长短要根据按键的特性和使用环境来决定。

4. 状态稳定判断:在延时过后,再次检测按键的状态,如果按键状态仍然保持稳定,则判断为有效的按键操作。

常见的按键消抖实现方法为了实现按键消抖,有多种方法可供选择,下面介绍几种常见的实现方式:软件消抖软件消抖是通过编程的方式来实现按键消抖的。

具体步骤如下: 1. 监测按键状态:在软件中定时采集按键状态。

2. 判断按键状态变化:将采集到的按键状态与先前的状态进行比较,判断是否出现按键抖动。

3. 延时处理:在检测到按键状态变化后,延时一段时间,等待按键信号稳定。

这段时间的长短要根据按键的特性和使用环境来决定。

4. 状态稳定判断:在延时过后,再次检测按键的状态,如果按键状态仍然保持稳定,则判断为有效的按键操作。

硬件消抖硬件消抖是通过电路设计来实现按键消抖的。

按键消抖的原理

按键消抖的原理按键消抖是指在按键被按下或松开时,因按键触点的弹性以及机械结构原因,导致按键信号在短时间内频繁抖动,从而产生多次触发信号的现象。

为了有效避免按键抖动对系统带来的干扰和误操作,需要进行按键消抖处理。

按键消抖的原理主要包括硬件消抖和软件消抖两种方式。

硬件消抖是通过在按键电路中添加外部元件实现的。

常见的硬件消抖方式包括使用电容、电感或者滤波器等元件,通过延迟、滤波或者稳定电平等方式来消除按键抖动信号。

电容消抖的原理是利用电容的充放电特性,将抖动的信号通过电容进行延时处理,从而产生稳定的按键触发信号。

电感消抖则是利用电感的滤波特性,通过电感对抖动信号进行滤波处理,从而获得稳定的按键信号。

而滤波器消抖则是通过在电路中加入滤波器元件,对抖动信号进行滤波处理,使得按键信号变得稳定可靠。

硬件消抖的优点是简单可靠,但缺点在于需要占用额外的电路资源和成本,且对于信号干扰抑制能力有一定的限制。

软件消抖是通过程序算法来实现的,常见的软件消抖方式包括延时消抖、状态机消抖和计数器消抖等。

延时消抖的原理是在按键按下后通过一个设定的延时时间来判断按键的有效触发,若在延时时间内未出现抖动信号,则判定为有效触发信号。

状态机消抖是通过设定按键的状态机来判断有效触发信号,只有在按键状态经过一定的稳定转换后才判断为有效触发。

计数器消抖则是通过设定一个计数器,在计数器计数达到一定次数后才判断为有效触发信号。

软件消抖的优点是不需要额外的硬件资源,可灵活性高,但缺点在于需要占用系统的处理器资源和对于时间精度的要求较高。

在实际应用中,通常会结合硬件消抖和软件消抖来实现按键的稳定触发。

例如在按键电路中加入电容滤波器来消除抖动信号,同时在系统程序中采用延时消抖或状态机消抖算法来进一步确保按键信号的稳定可靠。

这样既能保证按键信号的稳定触发,又能兼顾系统的资源和成本。

综上所述,按键消抖是通过硬件或者软件手段对按键信号进行处理,消除由按键触点的弹性抖动引起的干扰信号,从而获得稳定的按键触发信号。

verilog按键消抖原理

verilog按键消抖原理

摘要:

1.按键消抖的原理

2.按键消抖的方法

3.基于Verilog 的按键消抖设计

4.结论

正文:

一、按键消抖的原理

按键消抖是指在按键输入过程中,由于按键机械特性和电路特性的影响,导致按键在按下或松开时,信号电平会在一段时间内发生抖动。

为了消除这种抖动,需要采用一定的方法来确认按键输入的稳定性,这就是按键消抖。

二、按键消抖的方法

常见的按键消抖方法有以下几种:

1.硬件消抖:通过硬件电路实现消抖,如使用滤波器、RC 电路等。

2.软件消抖:通过软件算法实现消抖,如使用计数器、计时器等。

3.结合硬件和软件消抖:既使用硬件电路,也使用软件算法来实现消抖。

三、基于Verilog 的按键消抖设计

基于Verilog 的按键消抖设计可以分为以下几个步骤:

1.输入信号处理:对输入的按键信号进行采样,并转化为数字信号。

2.计数器:使用计数器来统计按键信号的持续时间,以判断按键是否稳定。

3.状态判断:根据计数器的计数值来判断按键是按下还是松开。

4.输出信号处理:将判断结果输出,以控制其他电路或设备。

四、结论

按键消抖是电子设备中常见的一种技术,它可以有效地消除按键输入过程中的抖动,提高系统的稳定性和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、按键消抖1.1 计数器型消抖电路(一)计数器型消抖电路(一)是设置一个模值为(N+1)的控制计数器,clk在上升沿时,如果按键开关key_in='1',计数器加1,key_in='0' 时,计数器清零。

当计数器值为2时,key_out 输出才为1,其他值为0时。

计数器值为N时处于保持状态。

因此按键key_in持续时间大于N个clk时钟周期时,计数器输出一个单脉冲,否则没有脉冲输出。

如果按键开关抖动产生的毛刺宽度小于N个时钟周期,因而毛刺作用不可能使计数器有输出,防抖动目的得以实现。

clk的时钟周期与N的值可以根据按键抖动时间由设计者自行设定。

主要程序结构如下:图1是N为3的波形仿真图,当按键持续时间大于3个时钟周期,计数器输出一个单脉冲,其宽度为1个时钟周期,小于3个时钟周期的窄脉冲用作模拟抖动干扰,从图1可以看出,抖动不能干扰正常的单脉冲输出。

1 按键抖动产生原因分析绝大多数按键都是机械式开关结构,由于机械式开关的核心部件为弹性金属簧片,因而在开关切换的瞬间会在接触点出现来回弹跳的现象。

虽然只是进行了一次按键,结果在按键信号稳定的前后出现了多个脉冲,如图1所示。

如果将这样的信号直接送给微处理器扫描采集的话,将可能把按键稳定前后出现的脉冲信号当作按键信号,这就出现人为的一次按键但微处理器以为多次按键现象。

为了确保按键识别的准确性,在按键信号抖动的情况下不能进入状态输入,为此就必须对按键进行消抖处理,消除抖动时不稳定、随机的电压信号。

机械式按键的抖动次数、抖动时间、抖动波形都是随机的。

不同类型的按键其最长抖动时间也有差别,抖动时间的长短和按键的机械特性有关,一般为5~10 ms,但是,有些按键的抖动时间可达到20 ms,甚至更长。

所以,在具体设计中要具体分析,根据实际情况来调整设计。

2 按键消抖电路的设计按键消抖一般采用硬件和软件消抖两种方法。

硬件消抖是利用电路滤波的原理实现,软件消抖是通过按键延时来实现。

在微机系统中一般都采用软件延时的消抖方法。

在用可编程逻辑器件FPGA/CPLD设计数字系统中,也可以用VHDL语言设计相应的时序和逻辑电路,对按键信号进行处理,同样可以达到消抖目的。

本文利用Altera公司的可编程逻辑器件CPLD和QuartusⅡ,设计性能可靠的按键消抖电路。

2.1 按键消抖电路设计原理按键消抖的关键是提取稳定的低电平(或高电平)状态,滤除按键稳定前后的抖动脉冲。

在用基于VHDL 语言的时序逻辑电路设计按键消抖电路时,可以用一个时钟脉冲信号对按键状态进行取样,当第一次采样到低电平时,启动延时电路,延时结束后,再对按键信号进行连续三次取样,如果三次取样都为低电平,则可以认为按键已经处在稳定状态,这时输出一个低电平的按键确认信号,如果连续三次的取样中,至少有一次是高电平,则认为按键仍处在抖动状态,此时不进行按键确认,按键输出信号为高电平。

2.2 按键消抖电路设计该控制电路采用VHDL语言的有限状态机的设计方法来描述和实现,其状态转换图如图2所示。

电路的复位信号Reset有效时,电路进入复位状态S0,在S0状态下时钟信号CLK以一定的频率采样按键输入信号Key_in,如果采样到Key_in=‘1’则停留在S0状态,并继续采样按键输入信号的状态,一旦采样到输入信号是低电平,即Key_in=‘0’,则转入S1延时状态,进行消抖延时,当延时结束时Delay_end=‘1’,则转入在S2状态,在此状态下时钟信号CLK以一定频率采样按键输入Key_in的状态,如果采样到Key_in为高电平即Key_in=‘1’则转回状态S0,表示按键仍处在抖动状态,如果采样到Key_in=‘O’,则转入状态S3;状态S3,S4的转换过程和条件跟S2相同,在S4状态下,如果Key_in=‘0’则转入S5状态,当到达状态S5时.表示经过S2,S3,S4三个连续状态检测按键输入Key_in的状态都为‘0’,则认为按键处在稳定状态,并在S5输出按键确认信号Key_confirm=‘1’。

同时在状态S5下时钟信号CLK检测按键输入状态,当检测到按键输入Key_in=‘0’,表示按键仍未释放,则停留在S5继续检测按键输入信号状态,如果检测到Key_in=‘1’,表示按键已经释放,则转回状态S0,等待下一次按键操作。

3 按键消抖电路的仿真分析消抖电路的仿真图如图3所示。

当复位信号Reset=‘0’时,状态机Key处在S0状态,同时以CLK的时钟频率采样按键输入信号Din的状态,当CLK第一次采样到Din为低电平时,此时可能发生了按键操作,随即状态机Key进入S1消抖延时状态,当延时结束时delay_end=‘1’(延时结束信号),跟接着状态机KEY 的S2,S3,S4连续三个状态对按键输入信号Din进行采样,当三个状态下采样到Din信号都是低电平,则转入S5状态,并产生按键确认信号Key_confirm=‘1’,同时在S5状态下等待按键释放,在此状态下当CLK时钟信号检测到Din为高电平时转回状态S0。

因按键释放瞬间也会发生抖动,所以由波形图可以看出,当按键释放瞬间由状态S5转回状态S0,在S0状态下,因按键抖动CLK时钟又检测到Din为低电平,随即转入S1进行消抖延时,经过S1的消抖延时后,按键已经稳定,Din为稳定的高电平,所以在状态S2检测到Din为高电平,则转入S0状态,到此时完成一次按键的操作,等待下一次按键操作,如果没有按键操作,即按键没按下,则一直保持在状态S0。

4 结语采用有限状态机方法设计按键消抖电路,再根据按键的特性设定合适的延时时间(一般10 ms)后,通过仿真分析及实验验证,能够起到很好的消抖效果,而且性能稳定,能确保每一次按键操作,产生一次按键确认,可广泛应用于可编程逻辑器件的键盘扫描设计中。

基于CPLD 的VHDL 语言数字钟设计基于CPLD 的VHDL 语言数字钟()设计利用一块芯片完成除时钟源、按键、扬声器和显示器(数码管)之外的所有数字电路功能。

所有数字逻辑功能都在CPLD 器件上用VHDL 语言实现。

这样设计具有体积小、设计周期短(设计过程中即可实现时序仿真)、调试方便、故障率低、修改升级容易等特点。

本设计采用自顶向下、混合输入方式(原理图输入—顶层文件连接和VHDL 语言输入—各模块程序设计)实现数字钟的设计、下载和调试。

一、功能说明已完成功能1. 完成秒/分/时的依次显示并正确计数;2. 秒/分/时各段个位满10 正确进位,秒/分能做到满60 向前进位;3. 定时闹钟:实现整点报时,又扬声器发出报时声音;4. 时间设置,也就是手动调时功能:当认为时钟不准确时,可以分别对分/时钟进行调整;5. 利用多余两位数码管完成秒表显示:A、精度达10ms;B、可以清零;C、完成暂停可以随时记时、暂停后记录数据。

待改进功能:1.闹钟只是整点报时,不能手动设置报时时间,遗憾之一;2.秒表不能向秒进位,也就是最多只能记时100ms;3.秒表暂停记录数据后不能在原有基础上继续计时,而是复位重新开始。

【注意】秒表为后来添加功能,所以有很多功能不成熟!二、设计方案1. 数字钟顶层设计外部输入要求:输入信号有1kHz/1Hz 时钟信号、低电平有效的秒/微秒清零信号CLR、低电平有效的调分信号SETmin、低电平有效的调时信号SEThour;外部输出要求:整点报时信号SOUND(59 分51/3/5/7 秒时未500Hz 低频声,59 分59 秒时为1kHz 高频声)、时十位显示信号h1(a,b,c,d,e,f,g)、时个位显示信号h0(a ,b,c,d,e,f,g)、分十位显示信号m1 及分个位m0、秒十位s1 及秒个位s0、微秒十位ms1 及微秒个位ms0;数码管显示位选信号SEL0/1/2 等三个信号。

2. 内部功能模块主要有:Fenp 分频模块:主要是整点报时用的1kH 与500Hz 的脉冲信号,这里的输入信号是1KHz 信号,所以只要一个二分频即可;时间基准采用1Hz 输入信号直接提供(当然也可以分频取得,这里先用的是分频取得的信号,后考虑到精度问题而采用硬件频率信号。

实现带有100 进制进位和清零功能,暂定等功能的微秒模块MINSECONDB 输入为1Hz 脉冲和低电平的清零信号CLR 与暂定信号STOP,输出微秒个位、十位及进位信号CO(虽然没有实现进位功能,但还是编写了这个端口,只是在连线时悬空)。

实现60 进制带有进位和清零功能的秒计数模块SECOND,输入为1Hz 脉冲和低电平有效的清零信号CLR,输出秒个位、时位及进位信号CO。

实现60 进制带有进位和置数功能的分计数模块MINUTE,输入为1Hz 脉冲和高 1 基于CPLD 的VHDL 语言数字钟设计电平有效的使能信号EN,输出分个位、时位及进位信号CO。

实现24 进制的时计数模块HOUR,输入为1Hz 脉冲和高电平有效的使能信号EN,输出分个位、时位。

实现分时复用功能模块SELTIME,输入为秒(含个/十位)、分、时、扫描时钟CLK1K,输出为D 和显示控制信号SEL。

实现整点报时功能模块ALERT,输入为分/秒信号,输出为高频声控Q1K 和Q500。

实现译码显示功能模块DISPLAY,输入为D,输出为Q三、设计框图高/低电平频率信号输入分频进进进微秒模块位秒模块位分模块位时模块置数/位选显示模块四、模块说明(含程序代码)1. 分频模块 2 基于CPLD 的VHDL 语言数字钟设计采用原理图输入方式实现 2 分频与1000 分频,但这里并没有用到1000 分频,因为后来考虑到精度问题,将千分频用直接输入了。

程序如图:利用三个7490 进行硬件分频!2. 微秒模块采用VHDL 语言输入方式,以时钟clk,清零信号clr 以及暂停信号STOP 为进程敏感变量,程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MINSECONDb isport(clk,clrm,stop:in std_logic;----时钟/清零信号secm1,secm0:out std_logic_vector(3 downto 0);----秒高位/低位co:out std_logic);-------输出/进位信号end MINSECONDb;architecture SEC of MINSECONDb issignal clk1,DOUT2:std_logic;beginprocess(clk,clrm)variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数V ARIABLE COUNT2 :INTEGER RANGE 0 TO 10 ;beginIF CLK'EVENT AND CLK='1'THENIF COUNT2>=0 AND COUNT2<10 THENCOUNT2:=COUNT2+1;ELSE COUNT2:=0;DOUT2<= NOT DOUT2;END IF; 3 基于CPLD 的VHDL 语言数字钟END IF;if clrm='1' then----当clr 为1 时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'event and clk='1' thenif stop='1' thencnt0:=cnt0;cnt1:=cnt1;end if;if cnt1="1001" and cnt0="1000" then----当记数为98(实际是经过59 个记时脉冲)co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9 时cnt0:=cnt0+1;----计数--elsif cnt0="1001" then--clk1<=not clk1;Elsecnt0:="0000";if cnt1<"1001" then----高位小于9 时cnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;secm1<=cnt1;secm0<=cnt0;end process;end SEC;3. 秒模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity SECOND is port(clk,clr:in std_logic;----时钟/清零信号sec1,sec0:out std_logic_vector(3 downto 0);----秒高位/低位co:out std_logic);-------输出/进位信号4 基于CPLD 的VHDL 语言数字钟end SECOND;architecture SEC of SECOND isbeginprocess(clk,clr)variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数beginif clr='1' then----当ckr 为1 时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'event and clk='1' thenif cnt1="0101" and cnt0="1000" then----当记数为58(实际是经过59 个记时脉冲)co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9 时cnt0:=cnt0+1;----计数elsecnt0:="0000";if cnt1<"0101" then----高位小于5 时cnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;sec1<=cnt1;sec0<=cnt0;end process;end SEC;4. 分模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MINUTE isport(clk,en:in std_logic; min1,min0:out std_logic_vector(3 downto 0); co:out std_logic); end MINUTE; 5 基于CPLD 的VHDL 语言数字钟architecture MIN of MINUTE isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0);beginif clk'event and clk='1' thenif en='1' thenif cnt1="0101" and cnt0="1000" thenco<='1';cnt0:="1001";elsif cnt0<"1001" thencnt0:=cnt0+1;elsecnt0:="0000";if cnt1<"0101" thencnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;end if;min1<=cnt1;min0<=cnt0;end process;end MIN;5. 时模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity HOUR isport(clk,en:in std_logic;----输入时钟/高电平有效的使能信号h1,h0:out std_logic_vector(3 downto 0));----时高位/低位end HOUR;architecture hour_arc of HOUR isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0);----记数6 基于CPLD 的VHDL 语言数字钟beginif clk'event and clk='1' then---上升沿触发if en='1' then---同时“使能”为1if cnt1="0010" and cnt0="0011" thencnt1:="0000";----高位/低位同时为0 时cnt0:="0000";elsif cnt0<"1001" then----低位小于9 时,低位记数累加cnt0:=cnt0+1;elsecnt0:="0000";cnt1:=cnt1+1;-----高位记数累加end if;end if;end if;h1<=cnt1;h0<=cnt0;end process;end hour_arc;6. 动态扫描模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity SELTIME isport( clk:in std_logic;------扫描时钟secm1,secm0,sec1,sec0,min1,min0,h1,h0:in std_logic_vector(3 downto 0);-----分别为秒个位/时位;分个位/ daout:out std_logic_vector(3 downto 0);----------------输出sel:out std_logic_vector(2 downto 0));-----位选信号end SELTIME;architecture fun of SELTIME issignal count:std_logic_vector(2 downto 0);----计数信号beginsel<=count;process(clk)beginif(clk'event and clk='1') thenif(count>="111") thencount<="000";elsecount<=count+1;end if; 7 基于CPLD 的VHDL 语言数字钟end if;case count iswhen"111"=>daout<= secm0;----秒个位when"110"=>daout<= secm1;----秒十位when"101"=>daout<= sec0;----分个位when"100"=>daout<= sec1;----分十位when"011"=>daout<=min0; ----时个位when"010"=>daout<=min1;----时十位when"001"=>daout<=h0;when others =>daout<=h1; end case;end process;end fun;7. 报时模块library ieee;use ieee.std_logic_1164.all;entity ALERT isport(m1,m0,s1,s0:in std_logic_vector(3 downto 0);------输入秒、分高/低位信号clk:in std_logic;------高频声控制q500,qlk:out std_logic);----低频声控制end ALERT;architecture sss_arc of ALERT isbeginprocess(clk)beginif clk'event and clk='1' thenif m1="0101" and m0="1001" and s1="0101" then----当秒高位为5,低位为9 时且分高位为5if s0="0001" or s0="0011" or s0="0101" or s0="0111" then---当分的低位为1 或3 或5或7时q500<='1';----低频输出为1else q500<='0';----否则输出为0end if;end if;if m1="0101" and m0="1001" and s1="0101" and s0="1001" then---当秒高位为5,低位为9 时且分高位为5,----分低位为9 时,也就是“59 分59 秒”的时候“报时” qlk<='1';-----高频输出为1elseqlk<='0'; 8 基于CPLD 的VHDL 语言数字钟end if;end if;end process;end sss_arc;8. 显示模块library ieee;use ieee.std_logic_1164.all;entity DISPLAY isport(d:in std_logic_vector(3 downto 0);----连接seltime 扫描部分 d 信号q:out std_logic_vector(6 downto 0));----输出段选信号(电平)end DISPLAY;architecture disp_are of DISPLAY isbeginprocess(d)begincase d iswhen"0000" =>q<="0111111";--显示0when"0001" =>q<="0000110";--显示1when"0010" =>q<="1011011";--显示2when"0011" =>q<="1001111";--显示3when"0100" =>q<="1100110";--显示4when"0101" =>q<="1101101";--显示5when"0110" =>q<="1111101";--显示6when"0111" =>q<="0100111";--显示7when"1000" =>q<="1111111";--显示8when others =>q<="1101111";--显示9end case; end process; end disp_are;9. 顶层文件(原理图输入)9 基于CPLD 的VHDL 语言数字钟******************************************************************** 数字钟模块与程序(不)*********************************************************************。