微机原理与接口技术(楼顺天第二版)第二章习题解答

微机原理与接口技术(第2版张颖超)第2章答案

练习题12.2-18086CPU在结构上由两个独立的处理单元和构成。

【解答】总线接口单元(BIU)执行单元(EU)2.2-2将62A0H和4321H相加,则AF=,SF=,ZF=,CF=,OF=,PF=。

【解答】AF=0;SF=1;ZF=0;CF=0;OF=0⊕1=1,PF=02.2-3设某台微处理器有20根地址总线,16根数据总线,若存储器寻址空间和I/O地址的寻址空间是分开的,则存储器空间大小为,经数据线一次可传送的带符号数的范围是。

【解答】1MB,-215~+215-12.2-4已知CS=1800H,IP=1500H,则指令所处的物理地址为,给定一个数据的有效地址是2359H,且DS=49B0H,该数据在内存中的实际物理地址为H。

【解答】19500H,19500H2.2-58086/8088段寄存器的功能是()。

A.用于计算有效地址B.执行各种数据传送操作C.用于存放段起始地址及计算物理地址【解答】C2.2-6微机的地址总线功能是()。

A.只用于选择存储器单元B.只用于选择进行信息传输的设备C.用于传送要访问的存储器单元或I/O端口的地址D.只用于选择I/O端口【解答】C2.2-7在堆栈段中,存放栈顶地址的寄存器是()。

A.IPB.SPC.BXD.BP【解答】B练习题22.3-18086中地址/数据线分时复用,为保证总线周期内地址稳定,应配置___________,为提高总线驱动能力,应配置__________。

【解答】地址锁存器(如74LS373)、数据收发器(如74LS245)2.3-28086最小组态下的总线控制信号由产生,最大组态下由产生。

【解答】CPU,总线控制器82882.3-38086有两种工作方式,当8086处于最小方式时,MN/MX接()。

A.+12VB.-12VC.+5VD.地【解答】C2.3-48086/8088CPU上INTR信号为()有效。

A.上升沿 B.下降沿 C.高电平 D.低电平【解答】C2.3-5下列说法中属于8086CPU最小工作模式特点的是()。

微机原理与接口技术_楼顺天版_课后题答案

微机原理与接口技术_楼顺天版_课后题答案本页仅作为文档封面,使用时可以删除This document is for reference only-rar21year.March微机原理与接口技术楼顺天周佳社编著科学出版社找了好久,终于在期末从老师那儿弄了一份,希望对大家有用!5章习题1.微处理器的外部结构表现为数量有限的输入输出引脚,它们构成了微处理器级总线。

2.微处理器级总线经过形成电路之后形成了系统级总线。

3.简述总线的定义及在计算机系统中采用标准化总线的优点。

答:总线是计算机系统中模块(或子系统)之间传输数据、地址和控制信号的公共通道,它是一组公用导线,是计算机系统的重要组成部分。

采用标准化总线的优点是:1)简化软、硬件设计。

2)简化系统结构。

3)易于系统扩展。

4)便于系统更新。

5)便于调试和维修。

4.在微型计算机应用系统中,按功能层次可以把总线分成哪几类。

答:在微型计算机应用系统中,按功能层次可以把总线分成:片内总线、元件级总线、系统总线和通信总线。

5.简述RESET信号的有效形式和系统复位后的启动地址。

答:RESET为系统复位信号,高电平有效,其有效信号至少要保持四个时钟周期,且复位信号上升沿要与CLK下降沿同步。

系统复位后的启动地址为0FFFF0H。

即:(CS)=0FFFFH,(IP)=0000H。

M/信号在访问存储器时为高电平,访问I/O端口时为低电6.8086 CPU的IO平。

7.在8086系统总线结构中,为什么要有地址锁存器?答:8086CPU有20条地址线和16条数据线,为了减少引脚,采用了分时复用,共占了20条引脚。

这20条引脚在总线周期的T1状态输出地址。

为了使地址信息在总线周期的其他T状态仍保持有效,总线控制逻辑必须有一个地址锁存器,把T1状态输出的20位地址信息进行锁存。

8. 根据传送信息的种类不同,系统总线分为 数据总线 、 地址总线 和 控制总线 。

9. 三态逻辑电路输出信号的三个状态是 高电平 、 低电平 和 高阻态 。

微机原理与接口技术_楼顺天版_课后题答案

微机原理与接口技术_楼顺天版_课后题答案微机原理与接口技术楼顺天周佳社编著科学出版社微机原理与接口技术楼顺天周佳社编著科学出版社2006年习题解答因时间紧,习题解答由部分老师提供,还没有经过仔细校对,肯定有不少错误,请各位指正。

另外,习题有多种解法,答案不唯一,仅供参考。

1第1 章数制与码制1.将下列十进制数转换成二进制数:(1)58;(2)67.625;(3)5721;解:(1)58D = 0011 1010B(2)67.625D = 0100 0011.1010B(3)5721D = 0001 0110 0101 1001B2.将二进制数变换成十六进制数:(1)1001 0101B;(2)11 0100 1011B;(3)1111 1111 1111 1101B;(4)0100 0000 10101B;(5)0111 1111B;(6)0100 0000 0001B解:(1)1001 0101B = 95H(2)11 0100 1011B = 34BH(3)1111 1111 1111 1101B = FFFDH(4)0 1000 0001 0101B = 815H(5)0111 1111B = 7FH(6)0100 0000 0001B = 401H3.将十六进制数变换成二进制数和十进制数:(1)78H;(2)0A6H;(3)1000H;(4)0FFFFH解:(1)78H = 120D = 0111 1000B(2)0A6H = 166D = 1010 0110B(3)1000H = 4096D = 0001 0000 0000 0000H(4)0FFFFH = 65535D = 1111 1111 1111 1111B4.将下列十进制数转换成十六进制数:(1)39;(2)299.34375;(3)54.5625解:(1)39D = 27H(2)299.34375D = 12B.58H(3)54.5625D = 36.9H5.将下列二进制数转换成十进制数:(1)10110.101B;(2)10010010.001B;(3)11010.1101B解:(1)10110.101B = 22.625D2(2)10010010.001B = 146.125D(3)11010.1101B = 26.8125D6.计算(按原进制运算):(1)10001101B+11010B;(2)10111B+11100101B;(3)1011110B-1110B;(4)124AH+78FH;(5)5673H+123H;(6)1000H-F5CH;解:(1)10100111B(2)11111100B(3)1010000B(4)19D9H(5)5796H(6)A4H7.已知 a=1011B, b=11001B, c=100110B, 按二进制完成下列运算,并用十进制运算检查计算结果:(1)a+b; (2)c-a-b; (3)a×b;(4)c÷b解:a=1011B=11D b=11001B=25D c=100110B =38D (1)100100B = 36D(2)10B= 2D(3)1 0001 0011B=275D(4)1B余1101B= 13D8.已知 a=00111000B, b=11000111B, 计算下列逻辑运算:(1)a AND b; (2)a OR b; (3)a XOR b; (4)NOT a 解:(1)00000000B(2)11111111B(3)11111111B(4)11000111B9. 设机器字长为 8 位,写出下列各数的原码和补码:(1)+1010101B;(2)-1010101B;(3)+1111111B;(4)-1111111B;(5)+1000000B;(6)-1000000B解:(1)原01010101B补01010101B(2)原11010101B补10101011B3(3)原01111111B 补01111111B(4)原11111111B 补10000001B(5)原01000000B 补01000000B(6)原11000000B 补11000000B10. 写出下列十进制数的二进制补码表示(设机器字长为8位):(1)15;(2)-1;(3)117;(4)0;(4)-15;(5)127;(6)-128;(7)80解:(1)(00001111B)补(2)(11111111B)补(3)(01110101B)补(4)(00000000B)补(5)(11110001B)补(6)(01111111B)补(7)(10000000B)补(8)(01010000B)补11.设机器字长为8位,先将下列各数表示成二进制补码,然后按补码进行运算,并用十进制数运算进行检验:(1)87-73;(2)87+(-73);(3)87-(-73);(4)(-87)+73;(5)(-87)-73;(6)(-87)-(-73);解:(1)1110B=14D(2)00001110B 进位舍弃(3)10100000B=-96D溢出(4)11110010B=-14D(5)01100000B=96D 溢出(6)11110010B=-14D12.已知a,b,c,d 为二进制补码:a=00110010B, b=01001010B, c=11101001B, d=10111010B,计算:(1)a+b;(2)a+c;(3)c+b;(4)c+d;(5)a-b;(6)c-a;(7)d-c;(8)a+d-c解:(1)01111100B4(2)00011011B(3)00110011B(4)10100011B(5)11101000B(6)10110111B(7)11010001B(8)11B13.设下列四组为8 位二进制补码表示的十六进制数,计算a+b和 a-b,并判断其结果是否溢出:(1)a=37H, b=57H;(2)a=0B7H, b=0D7H;(3)a=0F7H, b=0D7H; (4)a=37H, b=0C7H解:(1)a+b=8EH溢出,a-b=E0H未溢出(2)8EH未溢出,E0H未溢出(3)CEH未溢出,20H未溢出(4)FEH未溢出70H未溢出14. 求下列组合 BCD 数的二进制和十六进制表示形式:(1)3251(2)12907(3)2006解:(1)0011 0010 0101 0001B = 3251H(2)0001 0010 1001 0111B = 12907H(3)0010 0000 0000 0110B = 2006H15. 将下列算式中的十进制数表示成组合BCD 码进行运算,并用加 6/减 6 修正其结果:(1)38+42;(2)56+77;(3)99+88;(4)34+69;(5)38-42;(6)77-56;(7)15-76;(8)89-23解:(1) 0011 1000B + 0100 0010B = 0111 1010B 低 BCD 码位需要加6 修正0111 1010B + 0000 0110B = 1000 0000B = 80BCD(2) 0101 0110B + 0111 0111B = 1100 1101B 高、低 BCD 码位都需要加6 修正1100 1101B + 0110 0110B = 0001 0011 0011B=133BCD(3) 1001 1001B+1000 1000B = 0001 0010 0001B 高、低BCD 码位都需要加 6 修正0001 0010 0001B +0110 0110B = 0001 1000 0111B=187BCD(4) 0011 0100B + 0110 1001B = 1001 1101B 低 BCD 码位需要加 6 修正5。

微型计算机原理与接口技术(第二版)习题参考解答

mov al , ah

adc al , bl

mov result , cx

adc al , bh

daa

mov ax , [x1+1]

daa

mov cl , al

mov bx , [x2+1]

mov ch , al

mov al , ah 【解】(6)

adc al , bl

mov [result+1] , cx

; 基址变址相对寻址

寄存器寻址

(9) in al , 05

; 寄存器寻址

立即数

(10) mov ds , ax

; 寄存器寻址

寄存器寻址

2. 已知:DS=1000H,BX=0200H,SI=02H,内存 10200H~10205H 单元的内容分别为 10H,2AH,3CH,46H,59H,6BH。

下列每条指令执行完后 AX 寄存器内容各为什么?

(1) MOV AX , 0200

; 执行后,AX=0200H

(2) MOV AX , [200H]

; 执行后,AX=2A10H

(3) MOV AX , BX

; 执行后,AX=0200H

(4) MOV AX , 3[BX]

; 执行后,AX=5946H

(5) MOV AX , [BX+SI]

; 执行后,AX=463CH

题 5. 假设程序中的数据定义如下:

par

dw ?

pname db 16 dup(?)

count dd ?

plenth dw $-par 求 plenth 的值为多少?表示什么意义?

(1) mov ax , [100h]

; 直接寻址,

《微机原理及接口技术》(第2版)―习题解答

《微机原理及接口技术》(第2版)―习题解答《16/32位微机原理、汇编语言及接口技术・第2版》习题解答1第1章微处理器指令系统〔习题1.1〕微型计算机到目前为止已发展了几代?给出各代微机的特点和典型的微处理器。

〔解答〕〔习题1.2〕什么是微型计算机?PC机、单片机和数字信号处理器的含义各是什么?〔解答〕?微型计算机:以大规模、超大规模集成电路为主要部件,以集成了计算机主要部件――控制器和运算器的微处理器为核心,所构造出的计算机系统?PC机:PC(Personal Computer)机就是面向个人单独使用的一类微机?单片机:用于控制的微处理器芯片,内部除CPU外还集成了计算机的其他一些主要部件,如:ROM、RAM、定时器、并行接口、串行接口,有的芯片还集成了A/D、D/A转换电路等。

?数字信号处理器DSP:主要面向大流量数字信号的实时处理,在宿主系统中充当数据处理中心,在网络通信、多媒体应用等领域正得到越来越多的应用〔习题1.3〕微型计算机主要由哪些基本部件组成?各部件的主要功能是什么?〔解答〕CPU:存储器:外部设备:〔习题1.4〕什么是微机的系统总线?微机的总线结构为它带来了哪些好处?除电源和地线外,一般将总线分为哪3组信号?总线的使用特点是什么?〔解答〕?系统总线:传递信息的一组公用导线,CPU通过它们与存储器和I/O设备进行信息交换?好处:组态灵活、扩展方便?三组信号线:数据总线、地址总线和控制总线?其使用特点是:在某一时刻,只能由一个总线主控设备来控制系统总线,只能有一个发送者向总线发送信号;但可以有多个设备从总线上同时获得信号。

2〔习题1.5〕简述微型计算机的两个主要应用方向及其应用特点。

〔解答〕?用于数值计算、数据处理及信息管理方向?采用通用微机,要求有较快的工作速度、较高的运算精度、较大的内存容量和较完备的输入输出设备,为用户提供方便友好的操作界面和简便快捷的维护、扩充手段。

?用于过程控制及嵌人应用方向?采用控制类微机,要求能抵抗各种干扰、适应现场的恶劣环境、确保长时间稳定地工作,要求其实时性要好、强调其体积要小、便携式应用强调其省电。

微机原理与接口技术(第二版)课后习题答案

微机原理与接口技术(第二版)课后习题答案微机原理与接口技术(第二版)课后题答案第1章作业答案1.1 微处理器、微型计算机和微型计算机系统的区别是什么?微处理器是将CPU集成在一个芯片上,微型计算机是由微处理器、存储器和外部设备构成,而微型计算机系统则是微型计算机与管理、维护计算机硬件以及支持应用的软件相结合的系统。

1.2 CPU的内部结构由哪些部分组成?它应该具备哪些主要功能?CPU主要由算术逻辑单元、指令寄存器、指令译码器、可编程逻辑阵列和标志寄存器等寄存器组成。

它的主要功能是进行算术和逻辑运算以及控制计算机按照程序的规定自动运行。

1.3 采用总线结构的微型计算机有哪些优点?采用总线结构可以扩大数据传送的灵活性,减少连线。

此外,总线可以标准化,易于兼容和工业化生产。

1.4 数据总线和地址总线在结构上有什么不同?如果一个系统的数据和地址合用一套总线或者合用部分总线,那么要靠什么来区分地址和数据?数据总线是双向的,而地址总线是单向的。

如果一个系统的数据和地址合用一套总线或者部分总线,就要靠信号的时序来区分。

通常在读写数据时,总是先输出地址,过一段时间再读或写数据。

1.8 给定一个模型,如何用累加器实现15×15的程序?LD A。

15LD H。

15LOOP: ADD A。

15DEC HJP NZ。

LOOPHALT第2章作业答案2.1 IA-32结构微处理器直至Pentium 4,有哪几种?IA-32结构微处理器有、、Pentium、Pentium Pro、Pentium II、Pentium III和Pentium 4.2.6 IA-32结构微处理器有哪几种操作模式?IA-32结构支持保护模式、实地址模式和系统管理模式三种操作模式。

操作模式决定了哪些指令和结构特性可以访问。

2.8 IA-32结构微处理器的地址空间是如何形成的?由段寄存器确定的段基地址与各种寻址方式确定的有效地址相加形成了线性地址。

微机原理与接口技术课后习题答案

微机原理与接口技术习题解答第1章微型计算机系统〔习题〕简答题(1)计算机字长(Word)指的是什么(2)总线信号分成哪三组信号(3)PC机主存采用DRAM组成还是SRAM组成(4)Cache是什么意思(5)ROM-BIOS是什么(6)中断是什么(7)32位PC机主板的芯片组是什么(8)教材中MASM是指什么(9)处理器的“取指-译码-执行周期”是指什么(10)本课程的主要内容属于计算机系统层次结构中哪个层次〔解答〕①处理器每个单位时间可以处理的二进制数据位数称计算机字长。

②总线信号分成三组,分别是数据总线、地址总线和控制总线。

③ PC机主存采用DRAM组成。

④高速缓冲存储器Cache是处理器与主存之间速度很快但容量较小的存储器。

⑤ ROM-BIOS是“基本输入输出系统”,操作系统通过对BIOS的调用驱动各硬件设备,用户也可以在应用程序中调用BIOS中的许多功能。

⑥中断是CPU正常执行程序的流程被某种原因打断、并暂时停止,转向执行事先安排好的一段处理程序,待该处理程序结束后仍返回被中断的指令继续执行的过程。

⑦主板芯片组是主板的核心部件,它提供主板上的关键逻辑电路。

⑧ MASM是微软开发的宏汇编程序。

⑨指令的处理过程。

处理器的“取指—译码—执行周期”是指处理器从主存储器读取指令(简称取指),翻译指令代码的功能(简称译码),然后执行指令所规定的操作(简称执行)的过程。

⑩机器语言层,即指令集结构。

(学生很多认为是:汇编语言层。

前4章主要涉及汇编语言,但本书还有很多处理器原理等内容)〔习题〕判断题(1)软件与硬件的等价性原理说明软硬件在功能、性能和成本等方面是等价的。

(2)IA-64结构是IA-32结构的64位扩展,也就是Intel 64结构。

(3)8086的数据总线为16位,也就是说8086的数据总线的个数、或说条数、位数是16。

(4)微机主存只要使用RAM芯片就可以了。

(5)处理器并不直接连接外设,而是通过I/O接口电路与外设连接。

微机原理与接口技术(楼顺天第二版)第二章习题解答

微机原理与接口技术(楼顺天第二版)习题解答第2章 8086CPU 的结构与功能2.1 答:微处理器内部结构由四部分组成:(1)算术逻辑运算单元ALU :完成所有的运算操作; (2)工作寄存器:暂存寻址信息和计算过程中的中间结果;(3)控制器:完成指令的读入、寄存和译码,并产生控制信号序列使ALU 完成指定操作; (4)I/O 控制逻辑:处理I/O 操作。

2.2 答:微处理器级总线有三类:(1)数据总线:传送信息;(2)地址总线:传送地址码;(3)控制总线 传送控制信号。

2.3 答:地址码只能由CPU 生成。

而数据需要在CPU 和存储器之间传输。

2.4 答:8086CPU 对存储器按20位地址编址,从00000H~FFFFFH ;IO 端口按16位编址,从0000H~FFFFH 。

为独立编址方式。

统一编址优点为存储器与I/O 端口访问指令一致,寻址方式多,缺点是I/O 端口地址占用了一定范围的存储器地址;独立编址的优点是存储器与I/O 端口有各自的地址,缺点是需要有专门的指令,使得指令系统复杂。

2.5 8086CPU 按内部功能可分为BIU 和EU 两部分。

BIU 主要完成取指令、存储数据操作;EU 的功能是执行指令规定的操作。

EU 和BIU 可以独立、并行执行,但相互之间会有协作。

当指令队列中还没有指令时,EU 处于等待状态,当EU 执行指令需要访问存储器或I/O 端口时,BIU 应尽快完成存取数据的操作。

2.6 答:8086CPU 内部有14个16位寄存器,其中8个通用寄存器(4数据寄存器AX 、BX 、CX 、DX ,4地址指针/变址寄存器SI 、DI 、SP 、BP ),4个段寄存器(CS 、DS 、ES 、SS ),2个控制寄存器(指令指针IP ,微处理器状态字PSW )。

应该注意的是:可以在指令中用作为地址指针的寄存器有:SI 、DI 、BP 和BX ;在微处理器状态字PSW 中,一共设定了9个标志位,其中6个标志位用于反映ALU 前一次操作的结果状态(CF ,PF ,AF ,ZF ,SF ,OF ),另3个标志位用于控制CPU 操作(DF ,IF ,TF )。

微机原理与接口技术(第二版)课后习的题目问题解释完整版

微机原理与接口技术(第二版)课后习的题目问题解释完整版习题11.什么是汇编语言,汇编程序,和机器语言答:机器语言是用二进制代码表示的计算机能直接识别和执行的一种机器指令的集合。

汇编语言是面向及其的程序设计语言。

在汇编语言中,用助记符代替操作码,用地址符号或标号代替地址码。

这种用符号代替机器语言的二进制码,就把机器语言编程了汇编语言。

使用汇编语言编写的程序,机器不能直接识别,要由一种程序将汇编语言翻译成机器语言,这种起翻译作用的程序叫汇编程序。

2.微型计算机系统有哪些特点具有这些特点的根本原因是什么答:微型计算机的特点:功能强,可靠性高,价格低廉,适应性强、系统设计灵活,周期短、见效快,体积小、重量轻、耗电省,维护方便。

这些特点是由于微型计算机广泛采用了集成度相当高的器件和部件,建立在微细加工工艺基础之上。

3.微型计算机系统由哪些功能部件组成试说明“存储程序控制”的概念。

答:微型计算机系统的硬件主要由运算器、控制器、存储器、输入设备和输出设备组成。

“存储程序控制”的概念可简要地概括为以下几点:①计算机(指硬件)应由运算器、存储器、控制器和输入/输出设备五大基本部件组成。

②在计算机内部采用二进制来表示程序和数据。

③将编好的程序和原始数据事先存入存储器中,然后再启动计算机工作,使计算机在不需要人工干预的情况下,自动、高速的从存储器中取出指令加以执行,这就是存储程序的基本含义。

④五大部件以运算器为中心进行组织。

4.请说明微型计算机系统的工作过程。

答:微型计算机的基本工作过程是执行程序的过程,也就是CPU 自动从程序存放的第1个存储单元起,逐步取出指令、分析指令,并根据指令规定的操作类型和操作对象,执行指令规定的相关操作。

如此重复,周而复始,直至执行完程序的所有指令,从而实现程序的基本功能。

5.试说明微处理器字长的意义。

答:微型机的字长是指由微处理器内部一次可以并行处理二进制代码的位数。

它决定着计算机内部寄存器、ALU和数据总线的位数,反映了一台计算机的计算精度,直接影响着机器的硬件规模和造价。

《汇编语言 微机原理及接口技术》(第2版)课后习题答案

《汇编语言微机原理及接口技术》(第2版)课后习题答案第1章进制及码元1.进制转换129= 81H= 10000001B=201Q 298= 12AH= 100101010B=452Q 1000= 3E8H= 1111101000B= 1750Q 5DH= 1011101 B= 135 Q= 93 D 3E8H= 1111101000 B= 1750Q= 1000 D 357Q=11101111 B= 0EF H= 239 D 3.数据表示范围:一字节的无符号数表示范围为0~255,有符号数(补码)表示范围为-l28—+127。

一个字的无符号数表示范围为0~65535,有符号数(补码)表示范围为—32768~+32767。

N位二进制数的无符号数表示范围为0~(2N-1),有符号数(补码)表示范围为-2N-1~(2N-1-1). 4.35H代表的ASCII字符为’5’,代表十六进制数时等价的十进制值为53 ,代表压缩8421BCD码等价的十进制值为35 ,代表非压缩8421BCD码等价的十进制值为5。

5.FFH代表无符号数时等价的十进制值为255 ,代表补码有符号数时等价的十进制值为一1 ,代表反码有符号数时等价的十进制值为一0 ,代表原码有符号数时等价的十进制值为一l27。

6.--20的8位二进制补码为ECH ,原码为94H ,反码为EBH 。

158的16位二进制补码为009EH,原码为009EH ,反码为009EH 。

第2章微机硬件基础1.计算机系统硬件的五大功能部件及其主要功能? 答:硬件系统按功能模块分为运算器、控制器、存储器、输入设备、输出设备。

运算器主要完成算术运算、逻辑运算及移位运算,其中主要包括算术逻辑运算单元Arithmetic Logic Unit,ALU)和暂存数据(原始、中间、结果)的寄存器(Register,R)。

控制器实现对计算机部件的协调调度完成指令的分析执行,其中主要有程序计数器Program Counter,PC)或叫指令指针(Instruction Pointer,IP)、指令寄存器(Instruction register,IR)、指令译码器(Instruction Decoder,ID)、微操作命令发生器、时序发生器等。

微机原理与接口技术(第二版)课后习题答案完整版

微机原理与接口技术(第二版)课后习题答案完整版标准化文件发布号:(9312-EUATWW-MWUB-WUNN-INNUL-DQQTY-习题11.什么是汇编语言,汇编程序,和机器语言答:机器语言是用二进制代码表示的计算机能直接识别和执行的一种机器指令的集合。

汇编语言是面向及其的程序设计语言。

在汇编语言中,用助记符代替操作码,用地址符号或标号代替地址码。

这种用符号代替机器语言的二进制码,就把机器语言编程了汇编语言。

使用汇编语言编写的程序,机器不能直接识别,要由一种程序将汇编语言翻译成机器语言,这种起翻译作用的程序叫汇编程序。

2.微型计算机系统有哪些特点具有这些特点的根本原因是什么答:微型计算机的特点:功能强,可靠性高,价格低廉,适应性强、系统设计灵活,周期短、见效快,体积小、重量轻、耗电省,维护方便。

这些特点是由于微型计算机广泛采用了集成度相当高的器件和部件,建立在微细加工工艺基础之上。

3.微型计算机系统由哪些功能部件组成试说明“存储程序控制”的概念。

答:微型计算机系统的硬件主要由运算器、控制器、存储器、输入设备和输出设备组成。

“存储程序控制”的概念可简要地概括为以下几点:①计算机(指硬件)应由运算器、存储器、控制器和输入/输出设备五大基本部件组成。

②在计算机内部采用二进制来表示程序和数据。

③将编好的程序和原始数据事先存入存储器中,然后再启动计算机工作,使计算机在不需要人工干预的情况下,自动、高速的从存储器中取出指令加以执行,这就是存储程序的基本含义。

④五大部件以运算器为中心进行组织。

4.请说明微型计算机系统的工作过程。

答:微型计算机的基本工作过程是执行程序的过程,也就是CPU自动从程序存放的第1个存储单元起,逐步取出指令、分析指令,并根据指令规定的操作类型和操作对象,执行指令规定的相关操作。

如此重复,周而复始,直至执行完程序的所有指令,从而实现程序的基本功能。

5.试说明微处理器字长的意义。

答:微型机的字长是指由微处理器内部一次可以并行处理二进制代码的位数。

微机原理与接口技术第二章试题及答案[最终版]

![微机原理与接口技术第二章试题及答案[最终版]](https://img.taocdn.com/s3/m/177cb0cc67ec102de3bd891f.png)

第二章2-1 填空1..微处器由存放器、控制器和运算器三局部组成 ..2.当 MCS-51 引脚 ALE 信号有效时 ,暗示从 Po 口不变地送出了低 8 位地址 .3.MCS-51 的仓库是软件填写仓库指针临时在_片内数据存储器内斥地的区域4.MCS-51 中凡字节地址能被 _8 整除的特殊功能存放器均能寻址5.MCS-51 有 4 组工作存放器,它们的地址范围是00H~1FH...6.MCS-51 片内 20H~2FH 范围内的数据存储器 ,既可以字节寻址又可以位寻址7.计算机的系统总线有地址总线、控制总线和数据总线。

8.80C51 含 4KB 掩膜 ROM 。

.9.80C51 在物理有 4 个独立的存储空间。

10.一个机器周期等于 6 个状态周期,振荡脉冲 2 分频后发生的时钏信号的周期定义为状态周期。

2-2 判断1.我们所说的计算机本色上是计算机的硬件系统与软件系统的总称。

2.MCS-51 的相对转移指令最大负跳距是 127B 。

〔 √ 〕 〔 × 〕3.MCS-51 的程序存储器只是用来存放程序的。

〔 × 〕 存放程序和表格常数。

4.MCS-51 的时钟最高频率是 18MHz.5.使用可编程接口必需处始化。

(×).12MHz 。

〔 √ 〕。

6.当 MCS-51 上电复位时,仓库指针SP=00H 。

〔 ×〕。

SP=07H 7.MCS-51 外扩 I/O 口与外 RAM 是统一编址的。

〔 √〕。

8.使用 8751 且 =1 时,仍可外扩 64KB 的程序存储器。

〔 × 〕60KB 。

9.8155 的复位引脚可与 89C51 的复位引脚直接相连。

〔 √ 10.MCS-51 是微处置器。

〔× 〕不是。

〕11.MCS-51 的串行接口是全双工的。

〔 √ 〕12.PC 存放的是当前执行的指令。

〔 × 〕是将要执行的下一条指令的地址。

微机接口原理与接口技术第二章答案马维华

微机接⼝原理与接⼝技术第⼆章答案马维华第2章思考与习题参考答案2-1简述微处理器的主要性能指标,性能公式(2-1)说明了什么?公式(2-1): 性能=核⼼频率×每个周期执⾏指令的条数说明,微处理器的性能的提⾼不仅取决于⼯作频率,还依赖每周期执⾏指令的条数。

新的处理器代替⽼的处理器,就是根据这⼀性能公式来提⾼它的性能的。

即或单独提⾼频率,或单独增加每周期执⾏指令的条数,或既提⾼频率⼜增加每周期执⾏指令的条数。

由于核⼼频率的提⾼是有限制的,因此从Cure系列开始注重提⾼每个周期指令执⾏的条数来提⾼性能。

2-2简述微处理器的⼯作⽅式、各⼯作⽅式的含义和区别是什么?它们之间是如何切换的?答:1.五种⼯作⽅式:实地址⽅式、保护虚地址⽅式、虚拟86⽅式、系统管理⽅式以及IA-32E ⽅式。

2.含义:(1)实地址⽅式是指处理器⼯作在8086/8088编程环境下的⼯作⽅式。

(2)保护地址⽅式,⼜称保护虚地址⽅式,简称保护⽅式,是真正发挥处理器潜能的⼀种⼯作⽅式。

所谓保护是指在执⾏多任务操作时,对不同任务使⽤的不同存储空间进⾏完全隔离,保护每个任务顺利执⾏。

(3)虚拟86⽅式是指⼀个多任务的环境,即模拟多个8086的⼯作⽅式。

在这个⽅式之下,处理器被模拟成多个8086微处理器同时⼯作。

(4) 系统管理⽅式(SMM)是为实现特定功能及系统安全提供的⼀种⼯作⽅式,SMM 的功能主要包括电源管理以及为操作系统和正在运⾏的程序提供安全性。

SMM最显著的应⽤就是电源管理。

以上四种⽅式是IA-32所有处理器所具有的⼯作⽅式。

(5)从后期的P4到以Core为核⼼的处理器开始⽀持64位扩展技术,引⼊了IA-32E⼯作⽅式。

在这种⽅式下,处理器⽀持两种模式即兼容的⼯作⽅式(兼容IA-32处理器的⽅式)和64位⼯作⽅式。

在兼容模式下,允许在64位操作系统下运⾏原来的16位和32位应⽤程序,可使⽤前缘REX访问64位数据,最⼤⽀持的32位地址空间,⽽在64位⽅式下,采⽤EM64T技术,⽀持64位操作,同时⽀持36位的地址(从Pentium Pro开始处理器的外部地址线就提供36条),⽀持64位线性地址,默认的地址空间为64位,默认的数据宽度为32位,指令允许32/64地址和32/64数据的混合使⽤,因此⼜把Core为核⼼的处理器称为32/64处理器,与真正64位处理器有区别,可称之为具有64位功能的32位处理器。

微型计算机原理与接口技术第二章课后答案

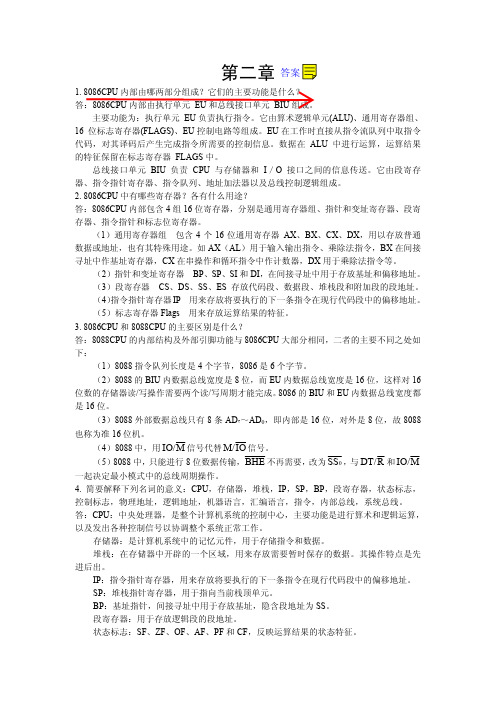

第二章 1. 8086CPU内部由哪两部分组成?它们的主要功能是什么?答:8086CPU 内部由执行单元 EU 和总线接口单元 BIU 组成。

主要功能为:执行单元 EU 负责执行指令。

它由算术逻辑单元(ALU)、通用寄存器组、16 位标志寄存器(FLAGS)、EU 控制电路等组成。

EU 在工作时直接从指令流队列中取指令代码,对其译码后产生完成指令所需要的控制信息。

数据在 ALU 中进行运算,运算结果的特征保留在标志寄存器 FLAGS 中。

总线接口单元 BIU 负责 CPU 与存储器和 I /O 接口之间的信息传送。

它由段寄存器、指令指针寄存器、指令队列、地址加法器以及总线控制逻辑组成。

2. 8086CPU 中有哪些寄存器?各有什么用途?答:8086CPU 内部包含4组16位寄存器,分别是通用寄存器组、指针和变址寄存器、段寄存器、指令指针和标志位寄存器。

(1)通用寄存器组 包含4个16位通用寄存器 AX 、BX 、CX 、DX ,用以存放普通数据或地址,也有其特殊用途。

如AX (AL )用于输入输出指令、乘除法指令,BX 在间接寻址中作基址寄存器,CX 在串操作和循环指令中作计数器,DX 用于乘除法指令等。

(2)指针和变址寄存器 BP 、SP 、SI 和DI ,在间接寻址中用于存放基址和偏移地址。

(3)段寄存器 CS 、DS 、SS 、ES 存放代码段、数据段、堆栈段和附加段的段地址。

(4)指令指针寄存器IP 用来存放将要执行的下一条指令在现行代码段中的偏移地址。

(5)标志寄存器Flags 用来存放运算结果的特征。

3. 8086CPU 和8088CPU 的主要区别是什么?答:8088CPU 的内部结构及外部引脚功能与8086CPU 大部分相同,二者的主要不同之处如下:(1)8088指令队列长度是4个字节,8086是6个字节。

(2)8088的BIU 内数据总线宽度是8位,而EU 内数据总线宽度是16位,这样对16位数的存储器读/写操作需要两个读/写周期才能完成。

微机原理与接口技术(第二版)课后习题答案完整版

习题11.什么就是汇编语言,汇编程序,与机器语言?答:机器语言就是用二进制代码表示得计算机能直接识别与执行得一种机器指令得集合。

汇编语言就是面向及其得程序设计语言。

在汇编语言中,用助记符代替操作码,用地址符号或标号代替地址码。

这种用符号代替机器语言得二进制码,就把机器语言编程了汇编语言。

使用汇编语言编写得程序,机器不能直接识别,要由一种程序将汇编语言翻译成机器语言,这种起翻译作用得程序叫汇编程序。

2.微型计算机系统有哪些特点?具有这些特点得根本原因就是什么?答:微型计算机得特点:功能强,可靠性高,价格低廉,适应性强、系统设计灵活,周期短、见效快,体积小、重量轻、耗电省,维护方便。

这些特点就是由于微型计算机广泛采用了集成度相当高得器件与部件,建立在微细加工工艺基础之上。

3.微型计算机系统由哪些功能部件组成?试说明“存储程序控制”得概念。

答:微型计算机系统得硬件主要由运算器、控制器、存储器、输入设备与输出设备组成。

“存储程序控制”得概念可简要地概括为以下几点:①计算机(指硬件)应由运算器、存储器、控制器与输入/输出设备五大基本部件组成。

②在计算机内部采用二进制来表示程序与数据。

③将编好得程序与原始数据事先存入存储器中,然后再启动计算机工作,使计算机在不需要人工干预得情况下,自动、高速得从存储器中取出指令加以执行,这就就是存储程序得基本含义。

④五大部件以运算器为中心进行组织。

4.请说明微型计算机系统得工作过程。

答:微型计算机得基本工作过程就是执行程序得过程,也就就是CPU自动从程序存放得第1个存储单元起,逐步取出指令、分析指令,并根据指令规定得操作类型与操作对象,执行指令规定得相关操作。

如此重复,周而复始,直至执行完程序得所有指令,从而实现程序得基本功能。

5.试说明微处理器字长得意义。

答:微型机得字长就是指由微处理器内部一次可以并行处理二进制代码得位数。

它决定着计算机内部寄存器、ALU与数据总线得位数,反映了一台计算机得计算精度,直接影响着机器得硬件规模与造价。

微机原理与接口技术课后答案第二版

微机原理与接口技术课后答案第二版微机原理与接口技术课后答案第二版【篇一:《微机原理与接口技术》(第二版)龚尚福-习题解析和实验指导】xt>2.2 8086微处理器由哪几部分组成?各部分的功能是什么?16355【解】:按功能可分为两部分:总线接口单元biu(bus interface unit)和执行单元eu(execution unit)。

总线接口单元biu是8086 cpu在存储器和i/o设备之间的接口部件,负责对全部引脚的操作,即8086对存储器和i/o设备的所有操作都是由biu完成的。

所有对外部总线的操作都必须有正确的地址和适当的控制信号,biu中的各部件主要是围绕这个目标设计的。

它提供了16位双向数据总线、20位地址总线和若干条控制总线。

其具体任务是:负责从内存单元中预取指令,并将它们送到指令队列缓冲器暂存。

cpu执行指令时,总线接口单元要配合执行单元,从指定的内存单元或i/o端口中取出数据传送给执行单元,或者把执行单元的处理结果传送到指定的内存单元或i/o端口中。

执行单元eu中包含1个16位的运算器alu、8个16位的寄存器、1个16位标志寄存器fr、1个运算暂存器和执行单元的控制电路。

这个单元进行所有指令的解释和执行,同时管理上述有关的寄存器。

eu对指令的执行是从取指令操作码开始的,它从总线接口单元的指令队列缓冲器中每次取一个字节。

如果指令队列缓冲器中是空的,那么eu就要等待biu通过外部总线从存储器中取得指令并送到eu,通过译码电路分析,发出相应控制命令,控制alu数据总线中数据的流向。

2.3 简述8086 cpu的寄存器组织。

【解】:(1)通用寄存器:通用寄存器又称数据寄存器,既可作为16位数据寄存器使用,也可作为两个8位数据寄存器使用。

当用作16位时,称为ax、bx、cx、dx。

当用作8位时,ah、bh、ch、dh 存放高字节,al、bl、cl、dl存放低字节,并且可独立寻址。

微机原理与接口技术答案

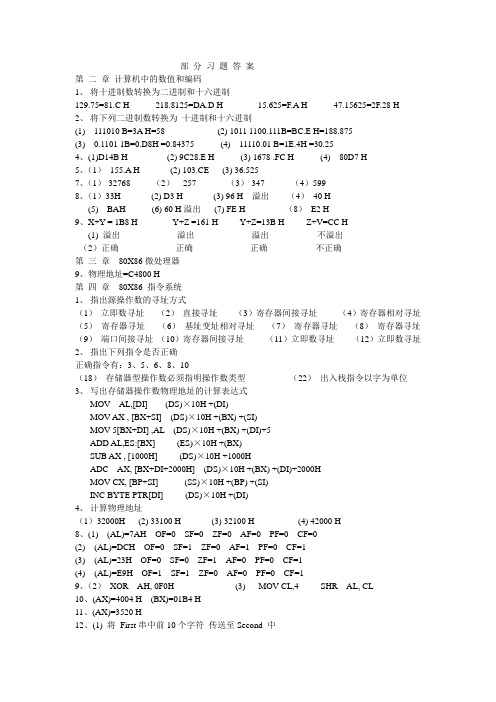

部分习题答案第二章计算机中的数值和编码1、将十进制数转换为二进制和十六进制129.75=81.C H 218.8125=DA.D H 15.625=F.A H 47.15625=2F.28 H2、将下列二进制数转换为十进制和十六进制(1) 111010 B=3A H=58 (2) 1011 1100.111B=BC.E H=188.875(3) 0.1101 1B=0.D8H =0.84375 (4) 11110.01 B=1E.4H =30.254、(1)D14B H (2) 9C28.E H (3) 1678 .FC H (4) 80D7 H5、(1)155.A H (2) 103.CE (3) 36.5257、(1)-32768 (2)257 (3)-347 (4)5998、(1)33H (2) D3 H (3) 96 H 溢出(4)40 H(5) BAH (6) 60 H溢出(7) FE H (8)E2 H9、X+Y = 1B8 H Y+Z =161 H Y+Z=13B H Z+V=CC H(1) 溢出溢出溢出不溢出(2)正确正确正确不正确第三章80X86微处理器9、物理地址=C4800 H第四章80X86 指令系统1、指出源操作数的寻址方式(1)立即数寻址(2)直接寻址(3)寄存器间接寻址(4)寄存器相对寻址(5)寄存器寻址(6)基址变址相对寻址(7)寄存器寻址(8)寄存器寻址(9)端口间接寻址(10)寄存器间接寻址(11)立即数寻址(12)立即数寻址2、指出下列指令是否正确正确指令有:3、5、6、8、10(18)存储器型操作数必须指明操作数类型(22)出入栈指令以字为单位3、写出存储器操作数物理地址的计算表达式MOV AL,[DI] (DS)×10H +(DI)MOV AX , [BX+SI] (DS)×10H +(BX) +(SI)MOV 5[BX+DI] ,AL (DS)×10H +(BX) +(DI)+5ADD AL,ES:[BX] (ES)×10H +(BX)SUB AX , [1000H] (DS)×10H +1000HADC AX, [BX+DI+2000H] (DS)×10H +(BX) +(DI)+2000HMOV CX, [BP+SI] (SS)×10H +(BP) +(SI)INC BYTE PTR[DI] (DS)×10H +(DI)4、计算物理地址(1)32000H (2) 33100 H (3) 32100 H (4) 42000 H8、(1) (AL)=7AH OF=0 SF=0 ZF=0 AF=0 PF=0 CF=0(2)(AL)=DCH OF=0 SF=1 ZF=0 AF=1 PF=0 CF=1(3)(AL)=23H OF=0 SF=0 ZF=1 AF=0 PF=0 CF=1(4)(AL)=E9H OF=1 SF=1 ZF=0 AF=0 PF=0 CF=19、(2)XOR AH, 0F0H (3) MOV CL,4 SHR AL, CL10、(AX)=4004 H (BX)=01B4 H11、(AX)=3520 H12、(1) 将First串中前10个字符传送至Second 中(2)存80 H 个0至0404 H 为起始地址的单元14、(BX)=139E H15、(SI)=0180 H(DS)=2000 H16、(1) (CL)=F6 H (2) (1ECF6 H)=5678 H(3)(BX)=0056H (AX)=1E40 H(4)((SI))=0024H (5) (AX)=5678 H (09226H)=1234 H 17、(1)(IP)=1256H (2) (IP)=3280 H (3) (IP)=2450 H 第五章汇编语言程序设计2.PLENTH的值为0022,它表示当前已分配单元空间;3.L的值为6;5.(AX)=000AH;(BL)=0AH;(CL)=01H;9.MOV AX,BXXCHG AL,CLMOV BX,ALMOV AX,BLXCHG AL,CHMOV BL,AL10. MOV DL,AHAND DL,0F0HMOV CL,4SHR DL,CLPUSH AXAND AH,0FHMOV BH,AHAND AL,0F0HMOV BL,ALMOV CL,4SHR BL,CLMOV CL,BHPOP AXAND AL,0FH11.DA TA SEGMENTSTRMA TCH DB ‘MA TCH’,0AH,0DH,’$’STRNMA TCH DB ‘NOMATCH,0AH,0DH,’$’STRING1 DB ‘GOOD MORNING!’LENG1 EQU $-STRING1STRING2 DB ‘GOOD MOING!’LENG1 EQU $-STRIGN2DATA ENDSCODE SEGMENTASSUME CS : CODE , DS : DA TASTART : MOV AX,DA TAMOV DS,AXMOV CX,LENG1CMP CX,LENG2JNZ NMATCHLEA SI,STRING1LEA DI,STRING2CLDREPE CMPSBJCXZ MATCHNMATCH : MOV DX,OFFSET STRNMA TCHMOV AH,09HINT 21HJMP EXITMATCH : MOV DX,OFFSET STRMA TCHMOV AH,09HINT 21HEXIT: MOV AH,4CHINT 21HCODE ENDSEND START13、DA TA SEGMENTM DB ……;已知的二十个数据DA TA ENDSCODE SEGMENTASSUME CS:CODE , DS:DA TASTART : MOV AX,DA TAMOV DS,AXLEA BP,MMOV SI,0MOV DI,19COMPARE : CMP DI,SIJC COMPLETEMOV AH,[BP][SI]OR AH,AHJS NEGA TIVEINC SIJMP COMPARENEGATIVE : CMP DI,SIJC COMPLETEMOV AL,[BP][ DI]OR AL,ALJNS CHANGEDEC DIJMP NEGATIVECHANGE: MOV [BP][SI],ALMOV [BP][DI],AHINC SIDEC DIJMP COMPARECOMPLETE :MOV AX,SICALL DISPMOV BX,20SUB BX,SIMOV AX,BXCALL DISPMOV AH,4CHINT 21HDISP PROC NEARMOV AH,ALAND AL,0F0HMOV CL,4SHR AL,CLMOV CH,2CONVERSE : ADD AL,30HCMP AL,3AHJL NUMBERADD AL,07HNUMBER : MOV DL,ALMOV AH,2INT 21HDEC CHJZ EXITMOV AL,AHAND AL,0FHJMP CONVERSEEXIT : RETDISP ENDPCODE ENDSEND START20、DA TA SEGMENTBVAR DB 54HDA TA ENDSCODE SEGMENTASSUME CS:CODE , DS:DATA START: MOV AX,DATAMOV DS,AXMOV CL,4MOV BL,BV ARROR BL,CLMOV AL,BLMOV CH,10MUL CH ;求十位数MOV BL,BVARAND BL, 0FHADD AL,BL ;十位与个位相加MOV BV AR,ALMOV AH,4CHINT 21HCODE ENDSEND START另解:MOV CL,4MOV AL,BV ARMOV AH,ALAND AL,0FHSHR AH,CLAADMOV BV AR,AL23.DATA SEGMENTBV AR DB ? ;已知待转化的数据RESULT DB 3 DUP(?)DA TA ENDSCODE SEGMENTASSUME CS: CODE, DS: DA TASTART : MOV AX,DA TAMOV DS,AXLEA BP,RESULTMOV SI,2MOV AL,BV ARCONVERSE : CBWMOV CH,10DIV CHMOV [BP][SI],AHDEC SIJS COMPLETEJMP CONVERSECOMPLETE : INC SICMP SI,3JG EXITMOV DL,[BP][SI]ADD DL,30HNUMBER : MOV AH,2INT 21HJMP COMPLETEEXIT : MOV AH,4CHINT 21HCODE ENDSEND START24.DATA SEGENTRESULT DW ? ;存放结果X DW ? ;已知数据Y DW ?DATA ENDSCODE SEGMENTASSUME CS : CODE, DS : DA TASTART : MOV AX,DA TAMOV DS,AXMOV AX,XCMP AX,YJL NEGATIVESUB AX,YJMP COMPLETENEGATIVE : MOV AX,YSUB AX,XCOMPLETE : MOV RESULT,AXMOV AH , 4CHINT 21HCODE ENDSEND START26、DA TA SEGMENTBUF3 DB ……BUF1 DB ……;定义已知数据BUF2 DB ……N1 DB ……N2 DB ……DA TA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATASTART: MOV AX,DATAMOV DS,AXLEA DX,BUF3LEA BX,BUF1LEA BP,BUF2MOV SI,0MOV DI,0COMPARE : CMP SI,N1JGE FULL1CMP DI,N2JGE FULL2MOV AL,[BX][SI]CMP AL,[BP][DI]JL LITTLEJE EQUALMOV CX,[BP][DI]MOV [DX] , CXINC DIINC DXJMP COMPARELITTLE : MOV [DX],ALINC SIINC DXJMP COMPAREEQUAL : MOV [DX],ALINC SIINC DIINC DXJMP COMPAREFULL1 : CMP DI,N2JGE EXITMOV CX,[BP][DI]MOV [DX] , CXINC DXINC DIJMP FULL1FULL2 : CMP SI,N1JGE EXITMOV CX,[BX][SI]MOV [DX] , CXINC DXINC SIJMP FULL2EXIT : MOV AH, 4CHINT 21HCODE ENDSEND START第六章半导体存储器2、(1)64片片内寻址线10根,片间寻址线6根(2)128片片内寻址线11根,片间寻址线5根(3)16片片内寻址线11根,片间寻址线5根(4)2片片内寻址线14根,片间寻址线2根3、1024×8的RAM芯片,地址线11根。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微机原理与接口技术(楼顺天第二版)习题解答

第2章 8086CPU 的结构与功能

2.1 答:微处理器内部结构由四部分组成:

(1)算术逻辑运算单元ALU :完成所有的运算操作; (2)工作寄存器:暂存寻址信息和计算过程中的中间结果;

(3)控制器:完成指令的读入、寄存和译码,并产生控制信号序列使ALU 完成指定操作; (4)I/O 控制逻辑:处理I/O 操作。

2.2 答:微处理器级总线有三类:(1)数据总线:传送信息;(2)地址总线:传送地址码;(3)控制总线 传送控制信号。

2.3 答:地址码只能由CPU 生成。

而数据需要在CPU 和存储器之间传输。

2.4 答:8086CPU 对存储器按20位地址编址,从00000H~FFFFFH ;IO 端口按16位编址,从0000H~FFFFH 。

为独立编址方式。

统一编址优点为存储器与I/O 端口访问指令一致,寻址方式多,缺点是I/O 端口地址占用了一定范围的存储器地址;独立编址的优点是存储器与I/O 端口有各自的地址,缺点是需要有专门的指令,使得指令系统复杂。

2.5 8086CPU 按内部功能可分为BIU 和EU 两部分。

BIU 主要完成取指令、存储数据操作;EU 的功能是执行指令规定的操作。

EU 和BIU 可以独立、并行执行,但相互之间会有协作。

当指令队列中还没有指令时,EU 处于等待状态,当EU 执行指令需要访问存储器或I/O 端口时,BIU 应尽快完成存取数据的操作。

2.6 答:8086CPU 内部有14个16位寄存器,其中8个通用寄存器(4数据寄存器AX 、BX 、

CX 、DX ,4地址指针/变址寄存器SI 、DI 、SP 、BP ),4个段寄存器(CS 、DS 、ES 、SS ),2个控制寄存器(指令指针IP ,微处理器状态字PSW )。

应该注意的是:可以在指令中用作为地址指针的寄存器有:SI 、DI 、BP 和BX ;在微处理器状态字PSW 中,一共设定了9个标志位,其中6个标志位用于反映ALU 前一次操作的结果状态(CF ,PF ,AF ,ZF ,SF ,OF ),另3个标志位用于控制CPU 操作(DF ,IF ,TF )。

2.7 答:IBM PC 有段地址寄存器(CS, DS, ES,SS)和基址、变址寄存器(BX, BP, SI, DI)来指示存储器地址。

2.8 答:(1)若为有符号数,则0FEH 为负数,02H 为正数,相加无溢出; (2)若为无符号数,则相加有溢出;

(3)有符号数相加根据OF 标志,无符号数相加,根据CF 标志判断。

2.9 答:(1)存储器地址空间为:20

2

1MB

(2)有符号数范围为: 15152~21--, 即 -32768~32767

2.10 答:字型数据低位字节存低地址,高位字节存高地址;由于8086有16为数据总线,一次可以读写16位数据,即2个字节,8086的存储器组织分奇地址存储体和偶地址存储体,若在存储器访问中,一次读写一个字(2个字节),且存储器的地址为偶地址,则认为是对准的,否则,是为对准的。

8086对对准的字操作通过一个总线周期完成,对未对准的字操作需要通过两个总线周期完成。

2.13 答:逻辑地址是由段地址和偏移地址表示的存储器地址,均用16位二进制表示。

物理地址是用20位二进制表示的存储器地址。

由逻辑地址的段地址左移4位和偏移地址相加可以得到唯一的20位物理地址。

2.14 答:(1)223E0H (2)2041FH (3)32016H

2.15 答:逻辑地址为:490BH:2359H ,物理地址为4B409H

2.16 答:末单元的逻辑地址为1412H:F2BCH ,则物理地址为14120H+F2BCH=233DCH ,首单元的物理地址为233DCH-254+1=233DCH-0FDH=232DFH

2.17 答:程序第一个字节的物理地址为A7F00H+2B40H=0AAA40H ,第一个字的物理地址为0AAA40H 和0AAA41H 。

2.18 答:(1)O (2)D (3)C (4)B (5)A (6)E (7)F (8)Q (9)N (10)M (11)L (12)H (13)J (14)I (15)G (16)K (17)R (18)P。