DSPI串行外设接口-主_从

Kinetis_DSPI模块详解

_ __ _____

PCSSE=0:PCS[5]/PCSS 作为一般片选信号;

_ __ _____

PCSSE=0:PCS[5]/ PCSS 低电平有效的选通信号。

ROOE:接收缓冲区溢出覆盖使能。即设置当接收缓冲区满时,新的数据如何处理。 ROOE=0:接收缓冲区满时,新到数据被丢弃; ROOE=1:接收缓冲区满时,新到数据存入移位寄存器。

PCSIS[5:0]:选择外设片选信号 5:0,工作时的有效电平。 PCSIS[x]=0:片选信号 x 高电平有效; PCSIS[x]=1:片选信号 x 低电平有效。

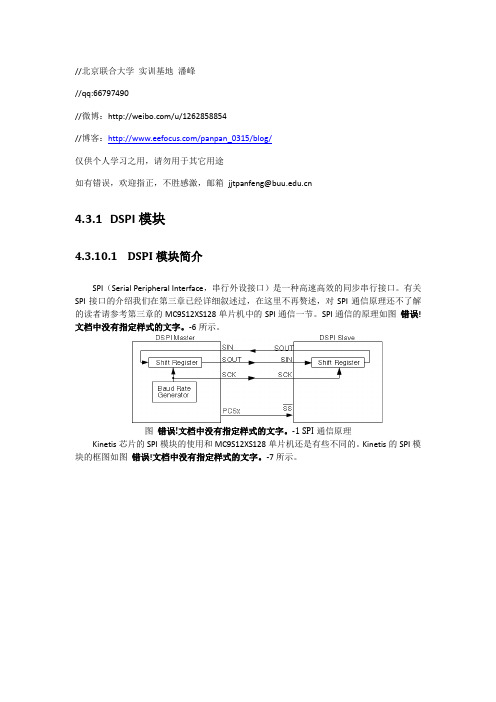

//北京联合大学 实训基地 潘峰 //qq:66797490 //微博:/u/1262858854 //博客:/panpan_0315/blog/ 仅供个人学习之用,请勿用于其它用途 如有错误,欢迎指正,不胜感激,邮箱 jjtpanfeng@

图 错误!文档中没有指定样式的文字。-4 SPI 时钟产生示意图 公式 错误!文档中没有指定样式的文字。-1 SCK baud rate = (fSYS/Prescaler) x

[(1+DBR)/Scaler] 注意:图中的 System Clock 实际为总线时钟 Bus clock。 4. DSPI 时钟和传输属性寄存器(从机模式)(SPIx_CTAR_SLAVE)

CPOL=1:时钟高电平空闲。

CPHA:时钟相位。

CPHA=0:数据在 SCK 的第一个边沿被捕捉,第二个边沿变化;

CPHA=1:数据在 :设置传输时是低位在前还是高位在前。

电子系统设计中常用串行接口及其应用

电子系统设计中常用串行接口及其应用在电子系统设计中,串行接口是一种常用的通信协议,用于在多个设备之间传输数据。

与并行接口相比,串行接口只需使用一条信号线来传输数据,因此可以减少硬件复杂度、节省成本,并且具有更好的扩展性和可靠性。

下面将介绍一些常见的串行接口及其应用。

1. 串行通用总线(Serial General Purpose Interface,SGPI):SGPI是一种开放标准的串行总线接口,可以在各种应用中使用,包括计算机、通信设备、工业自动化等。

它支持高速的全双工数据传输,可以连接多个设备,并提供了可靠的错误检测和纠正机制。

SGPI还支持热插拔功能,方便设备的添加和移除。

2. 串行外设接口(Serial Peripheral Interface,SPI):SPI是一种常用的串行通信接口,常用于连接微控制器和外设设备,如存储器、传感器、显示器等。

SPI接口使用4条信号线实现全双工的数据传输:主设备输出SCLK时钟信号,从设备接收数据(MISO)、主设备发送数据(MOSI)和主设备选择从设备(SS)。

SPI接口具有高速传输、简单灵活、可靠性高等特点,适用于多种应用场景。

3. 串行高速接口(Serial Advanced Technology Attachment,SATA):SATA是一种用于连接计算机硬盘驱动器和光盘驱动器的串行接口,取代了传统的并行接口(IDE)。

SATA接口使用7条信号线进行数据传输,支持高达6 Gbps的传输速度。

SATA接口具有高速传输、抗干扰能力强、线缆长度灵活等特点,广泛应用于个人电脑、服务器等领域。

4. 通用串行总线(Universal Serial Bus,USB):USB是一种广泛应用于计算机和消费电子产品中的串行接口标准。

USB接口可以连接各种外部设备,如键盘、鼠标、打印机、摄像头等。

USB接口提供了简单易用的插拔功能,支持高速数据传输和供电能力。

USB接口还定义了各种协议和设备类别,方便不同设备的互联互通。

DSP外设端口

预定标模块包括TCR中的TDDR和PSC位,由CPU 时钟定时,每来一个CPU时钟,PSC值减1。

当PSC减至0、设备复位或定时器复位时, TDDR的内容复制到PSC中。

4位预定标计数器PSC和16位定时计数器TIM组成 一个20位计数器,定时器每接收一个CPU时钟减1,当 计数器减到0时,产生定时中断(TINT),同时PSC和 TIM重新装入预设的值。

’C54x的定时器

1.定时器结构

2.定时器工作原理 3.定时器的初始化

1.定时器结构

定时器主要由定时寄存器TIM、定时周期寄存 器PRD、定时控制寄存器TCR及相应的逻辑控制电路

组成。

寄存器TIM、PRD和TCR是存储器映像寄存器,

地址分别为0024H、0025H和0026H。

1 3

1 2 预定标分频系数 TDDR 预定标计数器 PSC

;不插等待时间 ;TSS=1关闭定时器 ;加载周期寄存器(PRD) ;装入定时器控制字,启动定时器 ;消除尚未处理完的定时器中断 ;开放定时器中断 ;开放中断

’C54x的串行口

多通道带缓冲串行口McBSP

’C54x的多通道缓冲串行口McBSP是在缓冲串 行口的基础上发展起来的。在外部通道选择电路的 控制下,采用分时方式实现多路缓冲串行通信。 McBSP串行口可以与其他’C54x器件、编程器 或其他串口器件通信。

0

1

1

0

1

1

主机可以读/写HPID寄存器。 HPIA寄存器不受影响

HDS1、HDS2:数据选通信号,与主机读选通和写 选通或数据选通线连接,用于在主机寻址HPI 周期内,控制HPI数据的传送。

HDS1和HDS2信号与HCS一道产生内部选通信号。 HINT: HPI中断输出信号,与主机中断输入相连。受 HPIC寄存器中的HINT位控制。

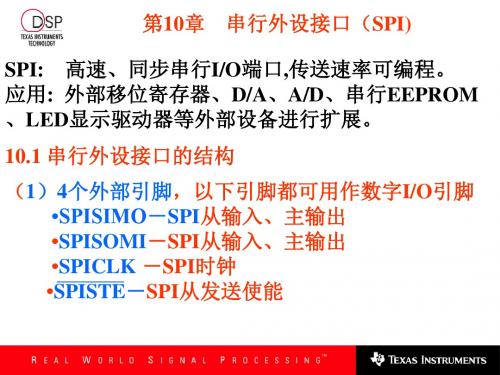

DSP第十章

SPI: 高速、同步串行I/O端口,传送速率可编程。 应用: 外部移位寄存器、D/A、A/D、串行EEPROM 、LED显示驱动器等外部设备进行扩展。

10.1 串行外设接口的结构

(1)4个外部引脚,以下引脚都可用作数字I/O引脚 •SPISIMO-SPI从输入、主输出 •SPISOMI-SPI从输入、主输出 •SPICLK -SPI时钟 •SPISTE-SPI从发送使能

10.5 波特率和时钟配置

SPI模块支持125种不同的波特率和4种不同的时钟 模式。SPI最大波特率为CLKOUT频率的四分之一 。

10.5.1 SPI波特率的确定

SPI波特率取决于CLKOUT和SPIBRR的值。

(1)对于SPIBRR=3~127 SPI波特率=CLKOUT/(SPIBRR+1)

(2)主控制器发送数据,从控制器发送数据; (3)主控制器发送伪数据,从控制器发送数据。

•主控制器控制SPICLK信号,通过发出SPICLK信号启动 数据发送,从控制器则通过检测SPICLK信号接收数据。

•一个主控制器可以连接多个从控制器,但是一次只允许 一个从控制器给主控制器发送数据

10.3 串行外设接口中断

MAX5121与DSP的SPI软件实现

以下用DAC输出一个三角波来说明SPI总线的软件编 程,由于MAX5121为SCLK的上升沿时接收SPI线上的数 据,因此DSP用无延时的下降沿时钟方式来发送SPI数据 ,这样才能配合MAX5121的SPI时序。用软件查询的发式 来发送数据。

程序

MAX512l与TMS320LF2407的硬件接口

在设计TMS320LF2407与MAX5121的硬件接口电路时 ,可将TMS320LF2407作为SPI主机,MAX512l作为从机 。MAX5121只接受来自主机的数据,然后进行D/A转换 并从OUT引脚输出模拟电压。由于MAX5121是在SCLK 的上升沿接收SPI线上的数据,因此,DSP应采用无延时 的下降沿来发送SPI数据,这样才能配合MAX5121的工作 时序。

SPI读书笔记

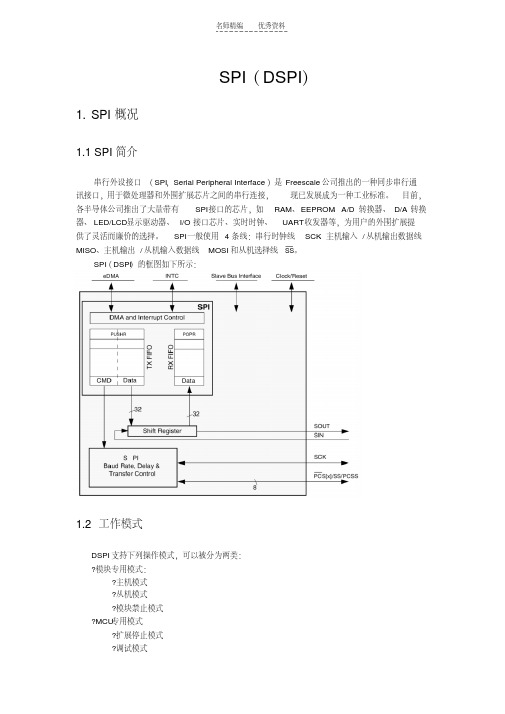

SPI(DSPI)1.SPI概况1.1 SPI简介串行外设接口(SPI,Serial Peripheral Interface)是Freescale公司推出的一种同步串行通讯接口,用于微处理器和外围扩展芯片之间的串行连接,现已发展成为一种工业标准。

目前,各半导体公司推出了大量带有SPI接口的芯片,如RAM、EEPROM、A/D转换器、D/A转换器、LED/LCD显示驱动器、I/O接口芯片、实时时钟、UART收发器等,为用户的外围扩展提供了灵活而廉价的选择。

SPI一般使用4条线:串行时钟线SCK、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和从机选择线SS。

SPI(DSPI)的框图如下所示:1.2 工作模式DSPI支持下列操作模式,可以被分为两类:?模块专用模式:?主机模式?从机模式?模块禁止模式?MCU专用模式?扩展停止模式?调试模式当主机写一个SDPI寄存器时,DSPI进入模块专用模式。

MCU专用模式由引脚控制,并可扩展到SDPI。

MCU专用模式就是一个MCU可以进入与DSPI模块专用模式不同的模式。

1.3引脚说明这部分提供了DSPI的引脚说明。

下表罗列了一些引脚,它们可以根据需要进行相应地连接。

DSPI引脚描述引脚描述IOI/OPCS0//SS 主机模式:外设芯片选择0输出从机模式:从机选择输入OPCS1-PCS3 主机模式:外设芯片选择1-3从机模式:无用OPCS4 主机模式:外设芯片选择 4从机模式:无用PCS4//PCSS 主机模式:外设芯片选择5,外设芯片选中脉冲OSIN 串行数据输入ISOUT 串行数据输出OI/OSCK 主机模式:串行时钟(输出)从机模式:串行时钟(输入)2.功能描述串行外设接口(DSPI)提供了一种全双工、同步串行通信用来连接MCU机器外设。

所有的通信都是工作于类SPI协议。

DSPI具有以下的配置:1.SPI可以配置为处于基本SPI或者队列SPI模式;DSPI模块配置寄存器(MCR)的DCONF字段用来决定DSPI的配置。

DSP之外部设备连接接口之HPI

通过主机借口HPI,外部主机可以直接访问DSP内部的双访问RAM(DARAM).HPI可以让外部的主处理器直接访问DSP内存映射中的部分内存,而无需DSP 干预。

通过主机接口还可以完成DSP的程序引导,DSP向主机发出中断信号要求主机响应中断等功能。

HPI提供了一个16位宽的并口,使用14位地址,每个地址装一个16位的字。

HPI不能直接访问其他的外设寄存器,如果主机需要从其他外设获取数据,则必须通过CPU或6个DMA通道中的一个,先将数据搬到DARAM 中,反之依然。

主机在HPI外部地址线上的地址,当成字地址,而不是字节地址来对待。

HPI的14根地址线,使主机可以访问到内部的地址为000060H~003FFFH的双访问RAM(DARAM)。

0~00005Fh为MMR保留,HPI不能访问。

在所有的C5509上,HPI和EMIF共享一个并口。

EBSR(外部总线选择寄存器)中的并行端口位决定这个端口用于数据EMIF模式(00b),完全 EMIF(01b),非复用HPI(10b)或者HPI模式(11b)。

并口模式位的复位值由复位时GPIO 0引脚的状态决定。

复位是GPIO 0引脚为高,是完全EMIF模式,低,复用HPI模式。

HPI信号简介信号名称类型说明HD[15:0]输入/输出/高阻主机数据总线在非复用模式下,只传输数据信号;复用模式下传输数据和地址信号HA[19:0]输入主机地址总线复用模式下传输主机到HPI口的地址信号;复用模式下HA[1]变成HCNTL1,HA[2]变为HAS_,其他引脚没有使用HBE[1:0]输入主机字节选择信号,但在TMS320VC5510的2.0版本之后不再支持该信号HCS_输入片选信号,低有效HR/W_输入读写信号HDS1_,HDS2_输入数据选通信号,HPI接口的数据选通信号是这两个信号的同或结果。

选通信号至少应持续2个CPU周期,HDS1_和HDS2_信号的连接根据主机选通信号而对应不同的接法。

基于DSP串行外设接口的通信

文章编号:1006-1576(2003)05-0039-02基于DSP串行外设接口的通信徐朝阳,朱春光,孙海洋(国防科技大学机电工程与自动化学院,湖南长沙410073)摘要:基于DSP串行外设接口(SPI)的通信,以TMS320LF2407为主机,DAC7614为从机。

主从机数据均在SPICLK的一个边沿移出移位寄存器,在另一个边沿锁存到移位寄存器。

由系统软件决定主机对从机的检测,通过I/O口设置控制数据的发送。

以一路模拟电压输出设计为例,其DSP采用无延时下降沿时钟方式发送数据以配合DAC7614上升沿接收数据的时序,通过查询方式来控制数据的发送。

关键词:DSP控制器;串行外设接口;通信中图分类号:TP393.03 文献标识码:ACommunication of Serial Peripheral Interface Based on DSPXU Zhao-yang, ZHU Chun-guang, SUN Hai-yang(College of Electromechanical Engineering & Automation, National University of Defence Technology,Changsha 410073, China)Abstract: In the communication of serial peripheral interface (SPI) based on DSP, TMS320LF2407 is used as the host controller and DAC7614 used as the obedient controller. The data is sent out from the shift register on one edge of the SPICLK and received on another. How the host controller check up the obedient controller is decided with system software, and TXD controlled by setting I/O. Taking design of simulation voltage output as example, the data is sent out with the timing mode for the descend edge without delay to suit to suit the timing sequence for receiving data on ascend edge of DAC7614, sending and receiving data is controlled with inquiring mode in DSP.Key words: DSP Controller; Serial peripheral interface (SPI); Communication1 引言DSP的串行外设接口(SPI)是一个高速、同步串行输入/输出端口,允许长度可编程的串行位流(1~16位)以可编程的位传输速率从设备移入或移出。

DSP串行外设接口SPI

(8).SPI串行数据寄存器SPIDAT—地址7049h

位15~0 (SDAT15~SDAT0 ):用于存 放发送/接收到的串行数据。发送的数据左 对齐,在SPICLK的合适边沿从最高位 (MSB)逐位移出;接收到的数据右对齐, 在SPICLK的合适边沿从SPIDAT的最低位 (LSB)逐位移入。向SPIDAT寄存器中写 入数据将启动数据传输。

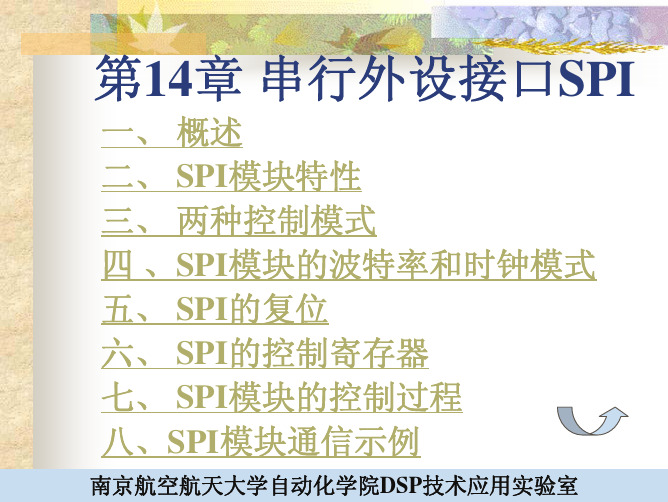

三、 两种控制模式

(1)主模式

在 主 模 式 下 , SPI 为 整 个 串 行 通 信 网 络 在 SPICLK 引脚上提供串行时钟,按照SPIBRR寄存 器规定的位传输速率把主控制器的串行数据传输 到从控制器。如下图所示,其工作过程如下。

南京航空航天大学自动化学院DSP技术应用实验室

主动控制具体过程

南京航空航天大学自动化学院DSP技术应用实验室

注意:

A ) 主 控 制 器 可 以 在 任 意时刻起动数据发 送,因为它控制着SPICLK信号;而在从模 式下,从控制器要发送数据,必须要用软 件设置SPICTL.1以确保使能 SPISTE输入 引脚。 B)串行数据长度可以由SPICCR.3~0编程, 且当传输数据长度小于16位的,数据写入 SPIDAT或者SPITXBUF时,必须左对齐;数 据从SPIRXBUF读回时是右对齐的。

六、 SPI的控制寄存器

(1).SPI配置控制寄存器 SPICCR—地址7040h

位 7 6 3 2 1 0

名称

SPI SW RESET

CLOCK POLARITY

说明 SPI软件复位

移位时钟极性

动作

0-SPI复位;1-SPI准备好接收发送

0-时钟上开沿有效;1-时钟下降沿有效 0000-1 0100-5 1000-9 1100-13 0001-2 0101-6 1001-10 1101-14 0010-3 0110-7 1010-11 1110-15 0011-4 0111-8 1011-12 1111-16

SPI接口简介0x0001

SPI接口简介0x0001本文介绍spi接口与串行spi接口应用。

SPI(Serial Peripheral Interface,串行外设接口)是Motorola 公司提出的一种同步串行数据传输标准,在很多器件中被广泛应用。

1. 接口SPI接口经常被称为4线串行总线,以主/从方式工作,数据传输过程由主机初始化。

如图1所示,其使用的4条信号线分别为:1)SCLK:串行时钟,用来同步数据传输,由主机输出;2)MOSI:主机输出从机输入数据线;3)MISO:主机输入从机输出数据线;4)SS:片选线,低电平有效,由主机输出。

在SPI总线上,某一时刻可以出现多个从机,但只能存在一个主机,主机通过片选线来确定要通信的从机。

这就要求从机的MISO口具有三态特性,使得该口线在器件未被选通时表现为高阻抗。

2. 数据传输在一个SPI时钟周期内,会完成如下操作:1)主机通过MOSI线发送1位数据,从机通过该线读取这1位数据;2)从机通过MISO线发送1位数据,主机通过该线读取这1位数据。

这是通过移位寄存器来实现的。

如图2所示,主机和从机各有一个移位寄存器,且二者连接成环。

随着时钟脉冲,数据按照从高位到低位的方式依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。

当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

3. 时钟极性和时钟相位在SPI操作中,最重要的两项设置就是时钟极性(CPOL或UCCKPL)和时钟相位(CPHA 或UCCKPH)。

时钟极性设置时钟空闲时的电平,时钟相位设置读取数据和发送数据的时钟沿。

主机和从机的发送数据是同时完成的,两者的接收数据也是同时完成的。

所以为了保证主从机正确通信,应使得它们的SPI具有相同的时钟极性和时钟相位。

举例来说,分别选取MSP430控制器和OLED驱动SH1101A为主从机,图3和图4为它们的SPI时序。

由图4可知,SH1101A的SPI时钟空闲时为高电平,并且在后时钟沿接收数据,则MSP430控制器SPI的设置应与此保持一致。

一文读懂SPI串行外设接口

一文读懂SPI串行外设接口

SPI 总线系统是一种同步串行外设接口,它可以使MCU 与各种外围设备

以串行方式进行通信以交换信息。

正是由于有了通信方式,我们才能够通过芯

片控制各种各样的外围器件,实现很多“不可思议”的现代科技。

这里将以SPI

为题,从编程角度来介绍SPI 总线。

下面就随网络通信小编一起来了解一下相

关内容吧。

1、SPI 协议简介

图1 SPI 接口

SPI 是英语Serial Peripheral interface 的缩写,顾名思义就是串行外围设备接口。

是Motorola 首先在其MC68HCXX 系列处理器上定义的。

SPI 是一种高速的,全双工,同步的通信总线,由于其简单易用的特性,现在很多的nor

flash 和nandflash 芯片集成了这种通信协议,也就是我们说的SPI flash。

2、应用及现状

图2 SPI 应用

SPI flash 芯片应用十分广泛,在很多电子产品上面或多或少都有它的踪影,如手机、数码、液晶显示器、机顶盒、电脑主板等。

最近,有消息透露,苹果

新手机iPhone 8 将导入采用编码型快闪存储(NOR Flash),让已经处于缺货状态的NOR 芯片更为恼火,另外据存储业者透露,今年NOR 芯片供给缺口将可能

扩大至20%。

3、解剖SPI 总线

SPI 接口一般使用4 条线通信,MISO 主设备数据输入,从设备数据输出。

MOSI 主设备数据输出,从设备数据输入。

SCLK 时钟信号,由主设备产生。

CS 从设备片选信号,由主设备控制。

DSP第三章4节

SPICTL

7041h 操作控制 寄存器

7

6

保留

5

4

3

2

1

0

RW-0 SPISTS 状态 寄存器 7 6 5 4

RW-0 3

RW-0 2

RW-0 1

RW-0 0

7042h

保留

RW-0 RW-0 保留 7 保留 6 5 4 3 2 1 0

7043h 7044h

—— SPIBRR 波特率 寄存器 ——

SPI主机(主/从=1) SPIRXBUF.15~0 SPI接收缓冲数据寄存器 SPIRXBUF SPISIMO

从:接收 主:发送 SPISIMO

SPI从机(主/从=0) SPIRXBUF.15~0 SPI接收缓冲数据寄存器 SPIRXBUF

SPI SPISTE SPI发送数据寄存器 SPISOMI MSB SPIDAT LSB SPIDAT15~0 SPICLK 选通 从:发送 主:接收 串行时钟 SPISTE SPISOMI SPI发送数据寄存器 MSB SPIDAT LSB

SPI配置控制寄存器和操作控制寄存器的地址各位定义与说明 如表3.26~3.34所示:

表3.26 串行外设(SPI)模块寄存器

地 址 7040h 寄存器 SPICCR 外设接口 配置控制 寄存器 7 SPISW RW-0 6 CLOCK 保留 RW-0 5 4 位 数 3 SPI CHAR3 RW-0 2 SPI CHAR2 RW-0 1 SPI CHAR1 RW-0 0 SPI CHAR0 RW-0

在同步时钟SPICLK的节拍下把SPIDAT的内容一位一位地移到 图 引脚SPISIMO。 移位完毕,将置一个中断标志SPIINT FLAG,通知主机这个信 息块已发送完毕。 对于从机,同样在同步时钟SPICLK的节拍下把出现在引脚 SPISIMO上的数据一位一位地移到从机的移位寄存器。 当一个完整的信息块接收完成后,将置一个中断标志SPIINT FLAG,通知从机这个信息块已接收完毕,同时将移位寄存器接收 到的内容复制到从机的SPI接收缓冲数据寄存器SPIBUF。 对于用户编程只需关注在发送数据时写SPI发送数据寄存器 SPIDAT;在接收数据时读SPI接收缓冲数据寄存器SPIBUF。其余的 移位、同步、置收发标志等工作都由内置的SPI模块自动完成。 DSP控制器SPI接口模块的结构示意图如图3.27所示: 应注意:引脚SPISET、SPISIMO、SPISOMI和SPICLK都是与 I/O复用的,引脚功能的选择由SPI端口控制寄存器来设置。图

spi

SPI总线简介SPI总线基本概念SPI ( Serial Peripheral Interface ———串行外设接口) 总线是Motorola公司推出的一种同步串行接口技术。

SPI总线系统是一种同步串行外设接口,允许MCU 与各种外围设备以串行方式进行通信、数据交换。

外围设备包括FLASHRAM、A/ D 转换器、网络控制器、MCU 等。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

其工作模式有两种:主模式和从模式。

SPI是一种允许一个主设备启动一个从设备的同步通讯的协议,从而完成数据的交换。

也就是SPI是一种规定好的通讯方式。

这种通信方式的优点是占用端口较少,一般4根就够基本通讯了(不算电源线)。

同时传输速度也很高。

一般来说要求主设备要有SPI控制器(也可用模拟方式),就可以与基于SPI的芯片通讯了。

SPI总线系统结构SPI 系统可直接与各个厂家生产的多种标准外围器件直接接口,一般使用4 条线:串行时钟线(SCK) 、主机输入/ 从机输出数据线MISO(DO)、主机输出/ 从机输入数据线MOSI (DI)和低电平有效的从机选择线CS。

MISO和MOSI用于串行接收和发送数据,先为MSB(高位),后为LSB(低位)。

在SPI设置为主机方式时,MISO是主机数据输入给,MOSI 是主机数据输出线。

SCK用于提供时钟脉冲将数据一位位地传送。

SPI总线器件间传送数据框图如图3所示:图3 SPI总线器件间传送数据框图SPI总线的接口特性利用SPI总线可在软件的控制下构成各种系统。

如1个主MCU和几个从MCU、几个从MCU相互连接构成多主机系统(分布式系统)、1个主MCU和1个或几个从I/O设备所构成的各种系统等。

在大多数应用场合,可使用1个MCU作为主控机来控制数据,并向1个或几个从外围器件传送该数据。

DSP课件 第九章 串行外设接口(SPI)

12

9.2.4 数据格式

13

ห้องสมุดไป่ตู้

9.2.5 波特率设置和时钟方式

SPI支持125种不同的波特率和4种不同的时钟方式。 1.波特率的计算

对于SPIBRR=3~127时

4

接口结构框图(从机方式)

5

§9.2 串行外设接口操作

串行外设接口的操作包括:操作方式、中断、数据格 式、时钟源和初始化。 9.2.1 操作介绍

两机之间的连接。 主机输出SPICLK信号启动数据传送。主机和从机数据 在SPICLK的一个边沿移出,在另一个边沿锁存。

6

返回

图9.2 SPI主机/从机的连接

之前接收的数据已被覆盖。如果OVERRUN INT ENA置位,则SPI就发生一次中

断请求。 该位可由以下三种操作来清除:

写1到该位;写0 到SPI SW RESET位;系统复位。

0 无中断请求

1 中断请求

位6

SPI INT FLAG。SPI中断标志位。

0 无中断请求

1 中断请求

位5

TX BUF FULL FLAG。SPI发送缓冲器满标志位。向SPITXBUF写入数据,该位置

9

9.2.2 SPI的主机和从机方式

2.从机方式

数据从SPISOMI引脚移出, SPISIMO引脚移入,SPICLK引脚输入串 行时钟。

发送数据:当主机SPICLK边沿合适时,从机中SPIDAT数据移出。 全部数据移出后,SPITXBUF数据传送到SPIDAT中。

接收数据:来自主机的SPICLK信号,将SPISIMO引脚上的数据移入 到SPIDAT。如果从机同时发送数据,则在SPICLK信号开始之前把数据 写入到SPITXBUF或SPIDAT中。

DSP课件-SPI串行外设接口

传输速率较很高,可达75M×16=1200Mbps 信号线多(DB8/16,AB等) 限用于板级扩展外设的输入/输出接口。

4

SPI模块的特点与信号

F281x包含一个四线制SPI接口,可工作于全双工模式 数据长度:1~16位可编程 波特率:126种可编程 可同时进行发送和接收操作

SPI中断使能位(SPICTL.0):1-使能中断,0-禁止中断 当中断使能置位,且满足中断条件时,产生相应的中断。 SPI中断标志位(SPISTS.6):只读,由硬件设置。 指示SPI接收器中已经存放字符可以被读取或已完成指定长度的数据发送。 该位置位时已接收数据送入SPIRXBUF,当DSP读SPIRXBUF中的数据后 自动清除中断标志。

SPICCR.3~SPICCR.0确定了字符的位数(1~16); 当数据写入SPIDAT和SPITXBUF寄存器时必须左对齐; 当数据从SPIRXBUF读取时,必须是右对齐; SPIRXBUF中包含最新接收的字符,以及上次接收且已移位到左边的位。 例1:发送数据长度为1,SPIDAT当前值为737BH,数据格式见下图。

讲授人:奚伯齐 Email: 2015dsp@ 密码:2015dsp

SPI串行外设接口

Serial Peripheral Interface(SPI) 1 SPI模块概述 2 SPI的工作原理 3 通过SPI接口扩展外设 4 软件编程举例

2

1 SPI模块概述

SPI与SCI有什么区别?

两种工作方式:主/从工作方式 4种时钟模式:由极性和相位控制 接口方式:中断或查询

4个外部引脚 只能以 16位方 式访问

12个寄存器

同步时钟

5

模 块 框 图

ISP接口定义

ISP接⼝定义ISP接⼝定义2011-03-15 19:55:32| 分类:通信技术|字号⼤中⼩订阅1.标准SPI接⼝(串⾏外围设备接⼝SPI(serial peripheral interface)总线技术)是以主从⽅式⼯作的,这种模式通常有⼀个主器件和⼀个或多个从器件,其接⼝包括以下四种信号:(1)MOSI –主器件数据输出,从器件数据输⼊(2)MISO –主器件数据输⼊,从器件数据输出(3)SCLK –时钟信号,由主器件产⽣(4)/SS –从器件使能信号,由主器件控制MOSI (SPI Bus Master Output/Slave Input)SPI 总线主输出/ 从输⼊MISO (SPI Bus Master Input/Slave Output) SPI 总线主机输⼊/ 从机输出2.AVR的ISP接⼝的定义:⼤部分AVR MCU的ISP数据端⼝亦为SCK、MOSI、MISO引脚(如Attiny13/24/2313,Atmega48/88/168,Atmega16/32/162,Atmega8515/8535等),如下:ISP下载器端AVR端⼝备注⼝MISO MISOVCC VCCSCK SCKMOSI MOSIRESET RESETGND GND少部分AVRMCU的ISP数据端⼝则不是使⽤这些接⼝,⽽是:SCK、PDI、PDO引脚(如ATmega64/128/1281等),如下:ISP下载器端AVR端⼝备注⼝MISO PDOVCC VCCSCK SCKMOSI PDIRESET RESETGND GND下⾯是标准的接⼝排列:ATMEL指定的ISP_10PIN标准接⼝ATMEL指定的ISP_6PIN标准接⼝转⾃:/doc/db86f503cc1755270722087a.html注意MEGA64和MEGA128的ISP与其它AVR不同,使⽤了PDI和PDO,⽽不是MOSI 和MISO。

SPI接口详细讲解

10101011

0101011X 01010110 1010110X 10101101 0101101X 01011010 1011010X 10110101 0110101X 01101010

0

1 1 0 0 1 1 0 0 1 1

1

0 0 1 1 0 0 1 1 0 0

7↑

7↓ 8↑0ຫໍສະໝຸດ 10101X二 SPI相关的寄存器

(1) SCPR:控制寄存器:(SPI的大部分设置都在该寄存器) Bit3:CPOL (时钟极性);Bit2:CPHA(时钟相位) (2)SPSR:标志寄存器:(查看一些标志和设置SPI速度, 主要是用到SPIF这个标志位,接收完成和发送完成都会 置位这个标志,进入中断服务程序或访问SPDR寄存器都 可以清零这个标志) 。 (3)SPDR:数据寄存器:

00101010 0101010X

1101010X

11010101 1010101X

0

0 1

1

1 0

五SPI时序图分析

(1)CPOL=0, SCLK为低时总线空闲: • CPHA=0 数据在SCLK的上升沿(rising edge)被读取;数据在下降沿(f alling edge)写入;

• CPHA=1 数据在SCLK的下降沿(falling edge)被读取;数据在上升沿(r ising edge)写入;

(2)CPOL=1, SCLK为高时总线空闲:

• CPHA=0 数据在SCLK的下降沿(falling edge)被读取;数据在上升沿( falling edge)写入;

• CPHA=1 数据在SCLK的上升沿(falling edge)被读取;数据在下降沿(r ising edge)写入;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

● Fully synthesizable, static synchronous design with no internal tri-states

DELIVERABLES

♦ Source code: ◊ VHDL Source Code or/and ◊ VERILOG Source Code or/and ◊ Encrypted, or plain text EDIF netlist

● Single Design license for

○ VHDL, Verilog source code called HDL Source

○ Encrypted, or plain text EDIF called Netlist

● One Year license for

○ Encrypted Netlist only

♦ VHDL & VERILOG test bench environment ◊ Active-HDL automatic simulation macros ◊ ModelSim automatic simulation macros ◊ Tests with reference responses

In all cases number of IP Core instantiations within a design, and number of manufactured chips are unlimited. There is no time restriction except One Year license where time of use is limited to 12 months.

APPLICATIONS

● Embedded microprocessor boards

● Consumer and professional audio/video

● Home and automotive radio

● Digital multimeters

KEY FEATURES

● SPI Master

All trademarks mentioned in this document are trademarks of their respective owners.

http://www.dcd.pl

Copyright 1999-2007 DCD – Digital Core Design. All Rights Reserved.

○ Bit rates generated 1/4 - 1/512 of system clock.

○ Four transfer formats supported

○ Simple interface allows easy connection to microcontrollers

● SPI Slave

○ Master and Multi-master operations

○ 8 SPI slave select lines

○ System error detection

○ Mode fault error○ WrΒιβλιοθήκη te collision error

○ Interrupt generation

○ Supports speeds up ¼ of system clock

The DSPI automatically drive selected by SSCR (Slave Select Control Register) slave select outputs (SS7O – SS0O), and address SPI slave device to exchange serially shifted data. Error-detection logic is included to support interprocessor communications. A writecollision detector indicates when an attempt is

scki

mi si

ss

datao(7:0)

irq

scko scken

mo so soen

ss7o ss6o ss5o ss4o ss3o ss2o ss1o ss0o

PINS DESCRIPTION

PIN clk rst datai(7:0) addr(1:0) cs rd we scki mi si ss datao(7:0) irq scko sckz mo so ss7o-ss0o

The DSPI is a technology independent design that can be implemented in a variety of process technologies.

The DSPI system is flexible enough to interface directly with numerous standard product peripherals from several manufacturers. The system can be configured as a master or a slave device. Data rates as high as CLK/4. Clock control logic allows a selection of clock polarity and a choice of two fundamentally different clocking protocols to accommodate most available synchronous serial peripheral devices. When the SPI is configured as a master, software selects one of eight different bit rates for the serial clock.

DSPI is fully customizable, which means it is delivered in the exact configuration to meet users’ requirements. There is no need to pay extra for not used features and wasted silicon. It includes fully automated testbench with complete set of tests allowing easy package validation at each stage of SoC design flow.

DSPI

Serial Peripheral Interface – Master/Slave ver 2.07

OVERVIEW

The DSPI is a fully configurable SPI master/slave device, which allows user to configure polarity and phase of serial clock signal SCK.

made to write data to the serial shift register while a transfer is in progress. A multiplemaster mode-fault detector automatically disables DSPI output drivers if more than one SPI devices simultaneously attempts to become bus master.

http://www.dcd.pl

Copyright 1999-2007 DCD – Digital Core Design. All Rights Reserved.

SYMBOL

clk rst

datai(7:0) addr(1:0) cs rd we

● Delivery the IP Core updates, minor and major versions changes

● Delivery the documentation updates ● Phone & email support

LICENSING

Comprehensible and clearly defined licensing methods without royalty fees make using of IP Core easy and simply.

The DSPI allows the microcontroller to communicate with serial peripheral devices. It is also capable of interprocessor communications in a multi-master system. A serial clock line (SCK) synchronizes shifting and sampling of the information on the two independent serial data lines. DSPI data are simultaneously transmitted and received.

♦ Technical documentation ◊ Installation notes ◊ HDL core specification ◊ Datasheet

♦ Synthesis scripts ♦ Example application ♦ Technical support