后端流程(初学必看)(DOC)

FTTH前后端协同“十步法”操作(试行)办法

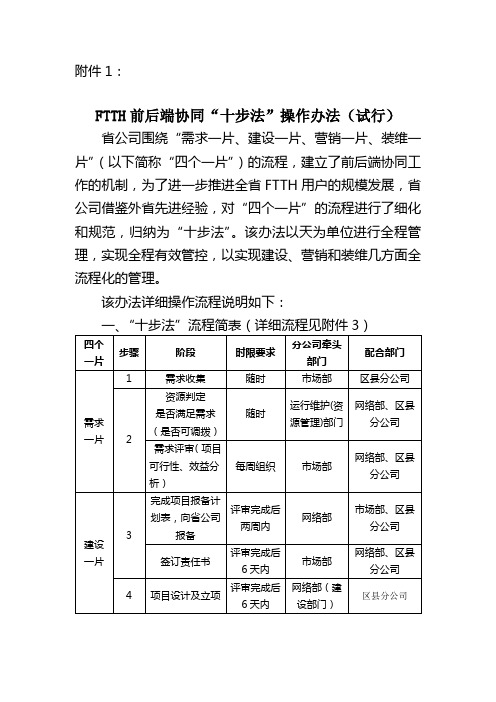

附件1:FTTH前后端协同“十步法”操作办法(试行)省公司围绕“需求一片、建设一片、营销一片、装维一片”(以下简称“四个一片”)的流程,建立了前后端协同工作的机制,为了进一步推进全省FTTH用户的规模发展,省公司借鉴外省先进经验,对“四个一片”的流程进行了细化和规范,归纳为“十步法”。

该办法以天为单位进行全程管理,实现全程有效管控,以实现建设、营销和装维几方面全流程化的管理。

该办法详细操作流程说明如下:一、“十步法”流程简表(详细流程见附件3)二、“十步法”操作说明(一)需求一片1、需求收集由区县公司根据市场及竞争情况,结合重点区域的发展要求,收集FTTH业务发展需求,分公司市场部负责每周汇总各区县公司的需求。

根据已经上报的需求情况,由分公司资源管理部门核实资源情况,对于确无资源,由市场部汇总。

区县分公司以清单方式提供小区信息、总住户数、现有电信宽带用户数、异网宽带用户数等情况。

2、需求评审经资源判定后的需求汇总后,由分公司市场部牵头组织网络部、需求单位进行联合评审。

评审以县/区公司为单元开展,综合考虑投资效益、用户价值、竞争因素,采用分等定级方法进行需求的筛选和优先顺序排定(“点亮光小区”活动收集到的需求一起纳入评审)。

3、责任书下达和评审结果报备省公司公司在评审完成后实施项目设计和立项的同时,由分公司市场部牵头完成“FTTH前后端协同工作责任书”签订,以便落实目标及责任。

责任书详见附件4。

在签订责任书的同时,由分公司网络部在评审完后两周内,按照项目报备表格式(详见附件5),将经评审后确定的建设项目报备省公司网络建设发展部和市场部。

并在之后按双周对通过评审小区的建设完成情况和用户发展情况进行更新和报备。

(二)建设一片分公司应加强对“光进铜退”资金使用的管控,做到专款专用,对违反要求的,省公司将按挪用资金额度的2倍扣减该分公司投资计划。

1、项目设计及立项在评审完成一周内,由分公司网络建设部门负责按照省公司FTTH建设指导意见完成项目勘察设计及立项工作。

前端和后端的开发流程

前端和后端的开发流程1.产品经理收集需求并进行分析。

The product manager collects and analyzes requirements.2.设计师进行界面设计和交互设计。

Designers do interface design and interaction design.3.前端工程师根据设计稿编写前端页面。

Front-end engineers write front-end pages according to the design drafts.4.前端工程师进行页面布局和样式设计。

Front-end engineers do page layout and style design.5.前端工程师进行页面逻辑与交互设计。

Front-end engineers do page logic and interaction design.6.前端工程师进行页面性能优化。

Front-end engineers optimize page performance.7.后端工程师进行服务端接口定义与设计。

Back-end engineers define and design server-side interfaces.8.后端工程师进行数据库设计与开发。

Back-end engineers do database design and development.9.后端工程师进行业务逻辑设计与开发。

Back-end engineers do business logic design and development.10.后端工程师进行服务端接口开发与调试。

Back-end engineers do server-side interface development and debugging.11.测试人员进行前后端联调测试。

Testers do front-end and back-end integration testing.12.测试人员进行性能测试与安全测试。

数字电路后端设计中的一些概念

天线效应:小尺寸的MO S 管的栅极与很长的金属连线接在一起,在刻蚀过程中 ,这根金属线有可能象一根天线一样收集带电粒子 ,升高电位,而且可以击穿 MO S 管的栅氧化层,造成器件的失效。

这种失效是不可恢复的。

不仅是金属连线 ,有时候多晶硅也可以充当天线。

Antenna Ratio(N 冷 G J 二铲包J A rea丫A rea(G K ) MO S 管的输入端开始算起,直至到达该回路最顶层金属线之下的所有金属互连线 (N i ,j ,i 为互连节点所属的金属层号,j 为金属层上的互连节点编号)的面积总和。

在这些金属互连线上将会累积电荷并导致输入端MO S 管栅氧化层出现可能被击穿的潜在危险。

而顶层金属线之下连至输出端晶体管栅极的金属线并不会被计算在内,这是因为在芯片的制造过程中其上多余的游离电荷可以通过低阻的输出端 MO S 管顺畅泻放。

同理,顶层金属线也不会对 A R 的值做出任何贡献,因其最后被刻蚀完成的同时,就标志着从输入 MO S 管到 输出MO S 管的通路正式形成,多余的电荷此时全部可以通过输出端得到泻放。

栅氧化层面积 A re a ga t e则是指各个输入端口所连接到的不同晶体管 (GK )的栅氧化层的面积总和。

以图1所 A 口聞门缸R 日込严铲Z Totallnpu tPorL-X 怕日* 工[inpuu+A 上 匕厲口 12 # inpct (2 )EM (电迁移):电迁移是指金属材料中存在大电流的情况下,金属离子在电流作用下出现宏观移动的现象,日常生活中的家用电线等金属导线由于没有良好 这里的导体面积 A r e a m e t a l 是指从图 1 M eta!3 l\ 实Pli A ri te nn a 的计门的散热能力,稍大的电流强度就会导致保险丝熔断而断路,移现象。

集成电路芯片中的金属连线则不同:它们有良好的散热环境,通常能够承受高达105A/cm2(约为普通家用电线承受极限的100倍)以上的电流强度和由此导致的大约100°C的高温。

WEB开发的流程

WEB开发的流程1.项目需求分析项目需求分析是整个WEB开发过程的起始阶段,它的目的是明确项目的需求和目标。

在这个阶段,开发团队与客户进行沟通,了解客户的需求,确定项目的范围、功能、平台和用户群体等。

2.系统设计在需求分析阶段的基础上,进行系统设计,确定项目的总体架构和技术方案。

开发团队会设计数据库结构、系统模块和各个模块之间的交互方式,并梳理出系统开发的具体任务和时间计划。

3.界面设计在系统设计的基础上,进行界面设计。

界面设计要考虑用户体验和用户界面的交互方式,包括页面布局、色彩搭配、图标设计等。

设计师会根据需求和系统定位进行界面设计,并提供给前端开发人员使用。

4.前端开发前端开发是指将设计师设计的界面进行编码实现。

前端开发人员会使用HTML、CSS和JavaScript等技术,将视觉设计转化为具体的网页。

他们需要保证页面在不同浏览器和设备上的兼容性和响应式设计。

5.后端开发后端开发是指通过编写服务器端代码来实现网站的业务逻辑和数据库的操作。

后端开发人员主要使用服务器端的编程语言和框架,如Java、Python、PHP等。

他们会根据系统设计的要求,开发相应的功能模块和接口,并与前端开发人员进行接口对接。

6.测试在开发完成后,需要进行测试来验证系统的功能和稳定性。

测试人员会根据项目需求和系统设计编写测试用例,并进行功能测试、性能测试、安全性测试等。

测试人员会报告错误和问题,开发团队需要及时修复问题并重新测试。

7.发布上线在测试通过后,将系统部署到服务器上进行发布。

这个过程包括配置服务器环境、上传代码、配置域名等。

发布后,测试人员和开发团队会进行最后一次的检查和测试,确保系统能正常运行。

8.维护系统发布上线后,需要进行后续的维护工作。

维护工作包括系统的监控、数据备份、系统安全和漏洞修复等。

同时,发现用户反馈或需求变更时,也需要及时进行维护和更新。

总之,WEB开发的流程包括项目需求分析、系统设计、界面设计、前端开发、后端开发、测试、发布上线和维护等阶段。

PICC置管流程(后端修剪式)

项目

操作方法

分值

扣分标准

操

作

前

,洗手,戴口罩

2.病人准备:了解病情及出凝血时间,评估患者局部静脉与皮肤情况,解释操作方法,取得配合,签署置管同意书。

3.物品准备:快速手消毒液,卷尺一个,无菌手套2副,PICC导管1根,PICC穿刺包1个,碘伏,75﹪酒精,0.9﹪盐水或肝素盐水,2﹪利多卡因1支,30ml注射器两副,1ml注射器1副,透明贴膜10×12cm1张,无菌输液贴1包,污物桶1个,输液接头一个。

18.擦净穿刺点血迹,将体外导管盘绕一流畅的弯曲,用胶布1固定在连接器上。覆盖10×12cm无菌透明贴膜。胶布2垫于导管下,胶带3蝶形交叉固定连接器,两侧向上黏在覆盖无菌透明贴膜上,胶带四固定在胶带3之上。

19.妥善安置病人,整理用物,向病人交代注意事项

20.X线检查确定导管尖端位置。

21.洗手,记录。

未行检查扣1分

未做到各扣1分

结

果

及

评

价

20

分

1.动作轻巧,操作熟练,穿刺准确,导管末端位置正确,无菌观念强

2.尊重关心爱护病人给予导管相关知识指导

3.用物、污物处置恰当

10

5

5

操作不熟练,流程不正确扣10分

未尊重关心爱护病人扣2.5分,未指导扣2.5分

处置不当一处扣1分

4.环境准备:房间紫外线消毒;使用隔帘,注意保护病人隐私;冬天注意保暖,环境清洁无尘。

3

5

10

2

一项未做到扣1分

评估少一项扣1分

用物缺一项扣0.5分

环境准备未作扣2分

操

作

方

法

与

程

泛微OA流程搭建操作流程(参考模板)

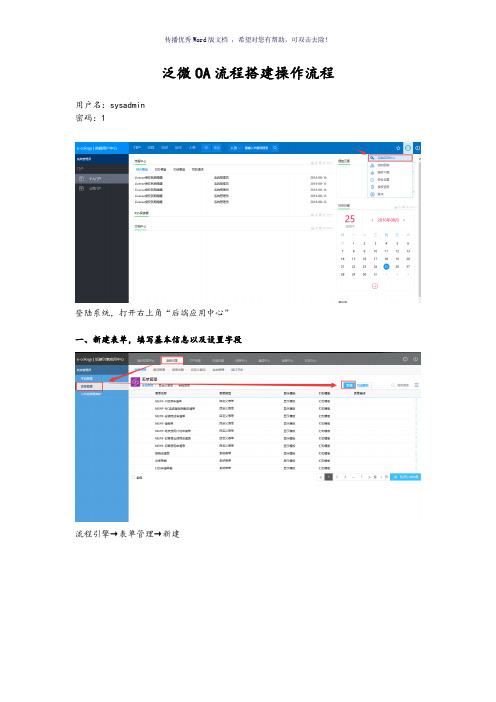

泛微OA流程搭建操作流程用户名:sysadmin密码:1登陆系统,打开右上角“后端应用中心”一、新建表单,填写基本信息以及设置字段流程引擎→表单管理→新建填写表单名称→保持并进入…“编辑字段”→“批量添加”点击“+”,按照表单字段的数量加行,每个字段占一行数据库字段名称:字段的首字母字段显示名称:中文名称字段类型:如上图所示漏了岗位,后来补上。

保存,进行下一步操作二、新建路径,绑定表单流程引擎→路径管理→路径设置→人事表单→添加填写“路径名称”,在“对应表单”里选择自定义表单,在弹出“信息确认”窗口选择“确定”。

在弹出窗口选择刚才建的表单:“NEWF-加值班登记单”在弹出“信息确认”窗口,选择“确定”提交流程后显示流程图:开启使用默认标题:开启,点击“标题设置”:按需求设置标题的显示样式:如:“《加值班登记单》{部门}{姓名}—{编号} 就是用上面的设置方法,里面只需要设置{部门} 和 {人员}其他默认就可以,右键,点击保存,进行下一步操作。

三、流转设置,节点信息设置流转设置→节点信息→空白处右键→编辑点击“+”进行加行节点名称:使用动词节点类型,必须有“创建”和“归档”,其他按要求选择,注意:“批准”是可以退回的,“提交”是不可退回的鼠标点击右键,保存,进行下一步操作。

操作组名称:创建人勾选:所有人点击加号,把内容生成一行,点击保存。

操作组名称:部门负责人通用矩阵表:通用型向上审批取值字段:部门负责人点击加号,把内容生成一行,点击保存。

操作组名称:部门分管领导通用矩阵表:通用型向上审批取值字段:部门分管领导点击加号,把内容生成一行,点击保存。

操作组名称:部门考勤员通用矩阵表:考勤员矩阵取值字段:部门考勤员点击加号,把内容生成一行,点击保存。

操作组名称:归档对象类型:勾选“创建人”勾选“创建人本人”点击加号,把内容生成一行,点击保存进行下一步操作。

表单内容,点击下面第一个按钮,如上图显示模式:选择“Html模式”点击“初始化模板”在弹出的页面上,勾上创建人这个节点在新建表单的时候,需要“显示”的和需要“可编辑”的,如上图设置注意:标题,紧急程度,一般显示,不可编辑每行显示字段数:2设置好就点击“下一步”,选择表单颜色,然后点击“完成”按钮点击“申请提交显示模板(初始化)”右键,选择“行高”,设置行高为63,用于放置新财富logo点击在标题行,点击插入→图片,在弹出的“插入图片”界面上,类型:选择“浮动”,选择图片,添加要上传的图片图片上传后,效果如上图。

工业流程基础知识点

工业流程基础知识点一、知识概述《工业流程基础知识点》①基本定义:工业流程简单说就是工业生产中为了把原料变成产品所经历的一系列步骤。

就好像做菜,从买菜(原料),到洗菜、切菜、炒菜(各个工序),最后端出一盘菜(产品),工业流程差不多也是这样的道理。

②重要程度:在工业相关学科中,这可是非常核心的部分。

没它,根本就不知道一个产品是怎么从无到有的。

就像我们要是不懂建筑的施工流程,房子可能都盖不起来。

③前置知识:得知道一些基本的化学知识(如果是化工流程的话),像元素啊、化学反应之类的;还有物理知识,比如一些基本的物理变化过程。

这就好比你要学画画,得先知道颜料怎么混合(化学知识类比)、笔怎么握得稳(物理知识类比)。

按我的经验,要是这些基础知识没掌握好,工业流程学起来就会很费劲。

④应用价值:在实际中太有用了。

比如说,想提高经济效益,可以通过优化工业流程,减少浪费、提高产量啥的。

像那些石油加工厂,不断优化流程,就能从同样多的原油里炼出更多的汽油和其他有用的东西。

二、知识体系①知识图谱:在整个工业学科里,工业流程是连接各个单元操作(像过滤、蒸馏等)、原料、产品和设备的主线。

就像人的经脉,把各个部分都串起来了。

②关联知识:和化学工程、机械工程等很多学科关联很大。

打个比方,化学工程决定了在流程里会有什么化学反应,而机械工程就保证了设备(也就是流程里干活的“家伙什儿”)是正常运转的。

③重难点分析:- 掌握难度:对于初学者有点难,因为流程往往很复杂,要考虑各种条件和设备。

- 关键点:得清楚每一步操作的目的,还有各步之间的关系,这就如同解开一团很乱的毛线球,你得找到线头(第一步操作目的),然后理清中间的连接(各步关系)。

④考点分析:- 在考试中的重要性:挺重要的,经常考。

不管是学校里的化学、物理考试,还是一些工业类的职业资格考试都会有。

- 考查方式:可能会让你写某个工业流程、分析某个流程步骤存在的问题,或者改进某个流程等。

比如给你一个钢铁炼制的简单流程,让你找出哪个步骤可以减少污染。

(完整版)IC设计流程

设计流程IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计.前端设计的主要流程:1、规格制定芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2、详细设计Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、HDL编码使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码.4、仿真验证仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格.看设计是否精确地满足了规格中的所有要求。

规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码.设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Mentor公司的Modelsim,Synopsys的VCS,还有Cadence的NC—Verilog均可以对RTL级的代码进行设计验证,该部分个人一般使用第一个—Modelsim.该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

5、逻辑综合――Design Compiler仿真验证通过,进行逻辑综合.逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist.综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。

所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。

后端开发实习报告第一周

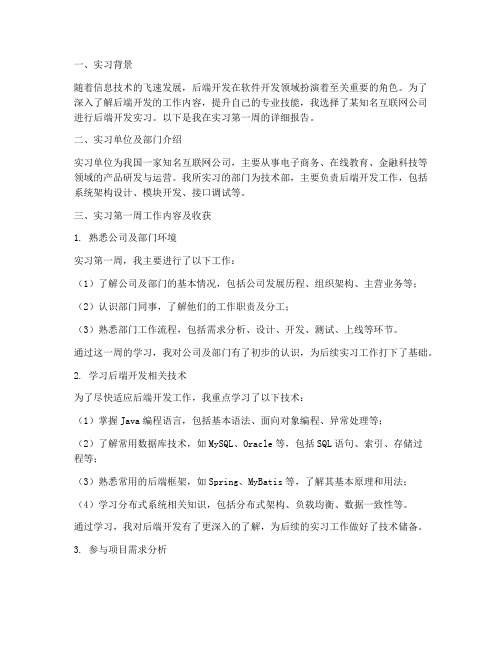

一、实习背景随着信息技术的飞速发展,后端开发在软件开发领域扮演着至关重要的角色。

为了深入了解后端开发的工作内容,提升自己的专业技能,我选择了某知名互联网公司进行后端开发实习。

以下是我在实习第一周的详细报告。

二、实习单位及部门介绍实习单位为我国一家知名互联网公司,主要从事电子商务、在线教育、金融科技等领域的产品研发与运营。

我所实习的部门为技术部,主要负责后端开发工作,包括系统架构设计、模块开发、接口调试等。

三、实习第一周工作内容及收获1. 熟悉公司及部门环境实习第一周,我主要进行了以下工作:(1)了解公司及部门的基本情况,包括公司发展历程、组织架构、主营业务等;(2)认识部门同事,了解他们的工作职责及分工;(3)熟悉部门工作流程,包括需求分析、设计、开发、测试、上线等环节。

通过这一周的学习,我对公司及部门有了初步的认识,为后续实习工作打下了基础。

2. 学习后端开发相关技术为了尽快适应后端开发工作,我重点学习了以下技术:(1)掌握Java编程语言,包括基本语法、面向对象编程、异常处理等;(2)了解常用数据库技术,如MySQL、Oracle等,包括SQL语句、索引、存储过程等;(3)熟悉常用的后端框架,如Spring、MyBatis等,了解其基本原理和用法;(4)学习分布式系统相关知识,包括分布式架构、负载均衡、数据一致性等。

通过学习,我对后端开发有了更深入的了解,为后续的实习工作做好了技术储备。

3. 参与项目需求分析在熟悉了公司及部门环境后,我开始参与项目需求分析。

本周我主要参与了以下项目:(1)项目名称:XX电商平台项目简介:该平台为一家线上购物平台,提供商品展示、购物车、订单管理等功能。

(2)项目需求分析本周我主要参与了项目需求分析环节,与产品经理、UI设计师等团队成员进行了沟通,了解项目背景、需求细节等。

通过分析,我掌握了以下需求:(1)用户注册、登录、个人信息管理等功能;(2)商品展示、分类、搜索等功能;(3)购物车、订单管理等功能;(4)支付、物流等功能。

后端项目交接文档(改)

□无□未接收

6.项目源码,关键类注释说明(源码中提供标准注释即可).

□有□已接收

□无□未接收

7.关联数据库相关配置清单(数据库地址,端口,用户名,密码),数据库备份说明.

□有□已接收

□无□未接收

8.云服务器资源配置清单(登录帐号,密钥,已安装服务器组件,安全设置,防火墙开放端口说明)

□有□已接收

□有□已接收

□无□未接收

交接项目(名称)

交接内容

交接情况

交手人

接收人

1.需求文档

□有□已接收

□无□未接收

2.后端项目业务流程文档

□有□已接收

□无□未接收

3.后端设计文档(系统架构,模块定义)

□有□已接收

□无□未接收

4.API相关接口文档及接口管理平台配置

□有□已接收

□无□未接收

5.项目运行环境配置(含仓库)文档

□有□已接收

□无□未接收

交接项目(名称)

交接内容

交接情况

交手人

接收人

1.需求文档

□有□已接收

□无□未接收

2.后端项ቤተ መጻሕፍቲ ባይዱ业务流程文档

□有□已接收

□无□未接收

3.后端设计文档(系统架构,模块定义)

□有□已接收

□无□未接收

4.API相关接口文档及接口管理平台配置

□有□已接收

□无□未接收

5.项目运行环境配置(含仓库)文档

□有□已接收

□无□未接收

6.项目源码,关键类注释说明(源码中提供标准注释即可).

□有□已接收

□无□未接收

7.关联数据库相关配置清单(数据库地址,端口,用户名,密码),数据库备份说明.

后端流程(初学必看)

基本后端流程(漂流&雪拧)----- 2010/7/3---2010/7/8本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。

此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。

此后端流程大致包括一下内容:1.逻辑综合(逻辑综合是干吗的就不用解释了把?)2.设计的形式验证(工具formality)形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL 代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格(设计周期短)的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。

另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是逻辑等价的。

3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。

(PR后也需作signoff的时序分析)4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR)5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。

6.APR后的门级功能仿真(如果需要)7.进行DRC和LVS,如果通过,则进入下一步。

常用手术体位图

常用手术体位操作流程平卧位操作流程<一>腹部手术1、安置体位前核对手术患者信息及手术部位2、患者仰卧于手术台上,戴手术帽(避免头发外露),头下垫薄软枕3、盆腔手术时骶尾部垫软垫将臀部稍抬高4、肝、胆、胰、脾手术时,术侧垫软枕,必要时将术侧手术床摇高15°5、双手自然放于身体两侧,中单固定或按需要将手臂外展固定于托手板上,双下肢伸直,双腘窝下垫软垫,约束带固定膝部6、整理用物,物归原处适应证:妇产科手术,前列腺、膀胱手术,肝、胆、胰、脾手术,胃、肠手术,头面部手术。

注意事项:1、若手臂外展不可超过90°,远端关节高于近端关节;2、手术时间过长,足跟须有保护措施。

<二>胸部手术1、安置体位前核对手术患者信息及手术部位2、患者仰卧于手术台上,戴手术帽(避免头发不外露),头下垫薄软枕3、乳腺手术时,患侧肩下垫一中长软垫。

患肢外展于托手架上或手部专用手术台上,健侧上肢自然放于身体一侧,中单固定。

4、纵行劈开胸骨行纵隔或心脏手术时,背部纵向垫一小软垫。

双手臂置于身体两侧或外展于托手板上5、双下肢伸直,双腘窝下垫一软垫,约束带固定膝部6、整理用物,物归原处(图1)适应证:前纵隔、心脏、乳腺手术。

图1注意事项:1、手臂外展不可超过90°,以免损伤臂丛神经;2、若手术时间过长,足跟部须有保护措施;3、关体腔前将体位垫取出。

<三>垂头仰卧位手术1、安置体位前核对手术患者信息及手术部位2、患者仰卧于手术台上,戴手术帽(避免头发外露),头下垫薄软枕,左手抬起患者头部,右手将肩垫置于双肩下(平肩峰)颈下垫长圆垫,保持头后仰且不悬空3、头部垫头圈或软垫,头板降低,头后仰4、放置托盘或麻醉头架于头部,距下颌上方5~6cm5、双手自然放于身体两侧,中单固定6、双腘窝部垫软垫,约束带固定双膝部7、整理用物,物归原处适应证:甲状腺、颈前路术、腭裂、扁桃腺、气管异物、食管异物等头面部及颈部手术。

数字后端流程简述

set_clock_transition:在pre_layout必须设置一个固定的transition值 (由技术库提供),目的是忽略计算clock pins的transition time,因为 时钟树还没有建立,有很大的fanout,此时计算clock pins的transition time也是很悲观的。 set_clock_skew:设置时钟的skew及delay,pre_layout和 post_layout命令选项不一样。-propagated选项让DC计算时钟树综合 之后的skew。

MinMin-Max

Min:最乐观的约束条件,使用延迟小的工艺库(如fast.db),用于 Hold Time检查分析。 Max:最悲观的约束条件,使用延迟大的工艺库(如slow.db),用于 Setup Time检查分析。 对环境属性和时序约束,同时使用Min-Max,用于指明在BEST和 WORST条件下,同时进行检查分析和逻辑优化。 set_min_library允许用户同时设置worst-case和best-case libraries, 从而在初步编译时,DC修正Hold Time violations时,验证Setup Time violations。例如: set_min_library slow.db -min_version fast.db 也可以在编译时修正Hold Time violations: set_fix_hold {all_clocks} compile -only_hold_time -incremental_mapping

汽车发动机装配线工艺流程

汽车发动机装配线工艺流程缸体底面朝下—→缸体、曲轴、凸轮轴投料、清洗、吹风、柴油机型号、标号打印—→缸体翻转180°后,打号确认—→缸体翻转后缸体底面朝上—→松瓦盖、卸瓦盖、安装上下轴瓦片、安装活塞冷却喷嘴、插入凸轮轴打入键、安装凸轮轴止推片、吊放曲轴、打入键—→打入前端销、打入前端主油道碗型塞、安装前端双头螺栓、装右端丝堵、安装主轴承盖及曲轴止推片并拧紧—→打入后端销,打入后端主油道碗型塞、装后油封座、装机油泵、装齿轮冷却喷嘴(安装增压器回油接头)—→缸孔涂油、装入活塞、装连杆盖、拧紧连杆螺栓、内装件检查—→安装柴油机前端板、安装凸轮轴齿轮、安装惰轮轴、惰轮、安装曲轴齿轮、安装前盖板(包括前盖板涂胶)—→安装机滤器总成、油底壳涂胶、安装油底壳并拧紧—→内装件确认、安装油尺套管、安装减振器、安装挺柱、柴油机型号、编号托印、记入发动机记录表—→连杆打号、分解、清洗后的连杆安装连杆瓦、活塞重量分组、活塞加热、装活塞销、装活塞环缸体翻转180°缸体上面朝上—→安装后端板、打入曲轴后端衬套、安装飞轮、安装离合器片及压盘、安装机滤座及机滤、安装发电机支架—→安装机冷器、安装水泵总成、安装真空泵总成、安装真空泵润滑油管、安装喷油泵总成—→安装喷油泵总成、安装供油角测量工具、调整供油提前角、安装喷油泵后端螺钉、安装喷油泵齿轮、安装VE泵回油接头、选择缸盖垫、安装缸盖垫—→吊装缸盖、拧紧缸盖螺栓—→安装摇臂总成、调整气门间隙、摇臂轴注油—→检测气门间隙、安装呼吸器、这、安装摇臂罩总成、安装喷油器总成、安装小回油管总成—→安装发电机总成、安装V型皮带、安装排气管、安装排气管隔热罩、安装暖风水管接头—→安装高压油管、拧紧节温器螺栓、喷油泵前罩盖涂胶、拧紧、安装进气管—→安装T/C排气丝对、安装排气管接管用丝对、安装T/C(增压器)、安装T/C回油软管、安装T/C进油管、安装T/C进水管、回水管、装真空泵管、安装排气管接管、装前侧挡板、后侧挡板、装排气支承—→装EGR阀、装进气接管及防护罩、装呼吸器、装呼吸器软管、安装EGR管装油尺、装怠速提升装置、安装油压接头、水路试漏、外观检查—→油系试漏、加注机油、外观检查发动机装配线及线上单机专用设备:清洗机、打号机、总成装配输送线、单层自由辊道、双层柔性机动滚道托盘、缸体缸盖输送车、升降机、翻转机、涂胶机、组合式螺栓拧紧机、轴承外环振动压装机、油封压装机、间隙测量机、导向拧紧装置、发动机密封性能检验机、活塞加热机、总成综合性能试验台、扭矩校准仪、气动扳手、装配线计算机控制系统、吊装式LED大屏幕显示装置、单轴气动定扭矩扳手、电动单梁悬挂起重机。

后端开发流程

后端开发流程后端开发流程后端开发是指构建和维护应用的服务器端代码,负责处理与数据库、外部服务的交互,以及实现业务逻辑。

下面将介绍常见的后端开发流程。

1. 需求分析和设计:开发前需要明确需求,并根据需求进行系统设计。

这包括确定系统的功能和模块,定义数据库结构和接口等。

2. 技术选型和环境搭建:根据项目需求,选择合适的开发语言和框架。

例如,选择Java语言和Spring框架来构建Java后端应用。

同时,搭建开发环境,包括安装IDE、配置开发服务器等。

3. 数据库设计和开发:根据需求设计数据库结构,包括表结构和关系设计。

使用SQL语言创建表、索引和约束,并编写数据库操作的存储过程或函数。

可以使用关系型数据库如MySQL或非关系数据库如MongoDB。

4. 接口开发:根据系统设计,实现与前端或其他系统交互的接口。

这包括定义接口的URL、请求方法和参数,以及编写接口的处理逻辑。

通常使用RESTful API或GraphQL来设计和实现接口。

5. 业务逻辑开发:根据需求和接口设计,实现业务逻辑。

包括处理数据的增删改查操作、编写算法和逻辑判断等。

同时,编写单元测试用例,保证代码的质量和可靠性。

6. 单元测试和集成测试:编写和运行单元测试用例,测试代码的正确性和性能。

集成测试是将不同模块或组件进行组合后的测试,确保各组件之间的交互和协作正常。

7. 部署和上线:将代码部署到生产环境或云服务器上,配置和优化服务器,确保系统正常运行。

同时,编写文档、搭建监控系统,为后续的维护和升级做准备。

8. 后期维护和优化:监控系统的运行情况,分析和处理系统中的问题和异常。

同时,进行系统性能优化,如数据库查询的优化、缓存的使用和代码的重构等。

以上是后端开发的一般流程,根据项目的不同可能会有些许差异。

在实际开发中,还需要注重代码的可读性、可维护性和安全性,以及与前端和其他团队的有效沟通和协作。

总结起来,后端开发流程包括需求分析和设计、技术选型和环境搭建、数据库设计和开发、接口开发、业务逻辑开发、单元测试和集成测试、部署和上线,以及后期维护和优化。

创建vue后端项目的流程

创建vue后端项目的流程一、前言Vue.js 是一个渐进式的JavaScript 框架,它可以用于构建单页面应用程序,也可以与其他库或现有项目结合使用。

在使用 Vue.js 开发前端应用时,我们经常需要创建后端项目来提供数据支持。

本文将介绍如何创建Vue后端项目。

二、准备工作1.安装Node.js 和 npmNode.js 是一个基于 Chrome V8 引擎的 JavaScript 运行环境,它使得 JavaScript 可以在服务器端运行。

npm 是 Node.js 的包管理器,它可以帮助我们安装和管理依赖包。

2.选择后端框架在创建 Vue 后端项目之前,我们需要选择一个适合自己的后端框架。

常见的后端框架有 Express、Koa、Hapi 等。

3.选择数据库在开发后端应用时,我们需要选择一种数据库来存储数据。

常见的数据库有 MySQL、MongoDB、PostgreSQL 等。

三、创建Vue后端项目1.使用Express框架创建项目(1)安装Express框架:```npm install express --save```(2)创建一个名为 server.js 的文件,并输入以下代码:```javascriptconst express = require('express')const app = express()app.get('/', (req, res) => {res.send('Hello World!')})app.listen(3000, () => {console.log('Server is running on port 3000.') })```(3)运行项目:```node server.js```2.使用Koa框架创建项目(1)安装Koa框架:```npm install koa --save```(2)创建一个名为 server.js 的文件,并输入以下代码:```javascriptconst Koa = require('koa')const app = new Koa()e(async ctx => {ctx.body = 'Hello World!'})app.listen(3000, () => {console.log('Server is running on port 3000.') })```(3)运行项目:```node server.js```3.使用Hapi框架创建项目(1)安装Hapi框架:```npm install hapi --save```(2)创建一个名为 server.js 的文件,并输入以下代码:```javascriptconst Hapi = require('hapi')const server = new Hapi.Server()server.connection({host: 'localhost',port: 3000})server.route({method: 'GET',path: '/',handler: function (request, reply) {return reply('Hello World!')}})server.start((err) => {if (err) {throw err;}console.log(`Server is running at: ${.uri}`);});```(3)运行项目:```node server.js```四、连接数据库在创建后端项目时,我们需要连接数据库来存储数据。

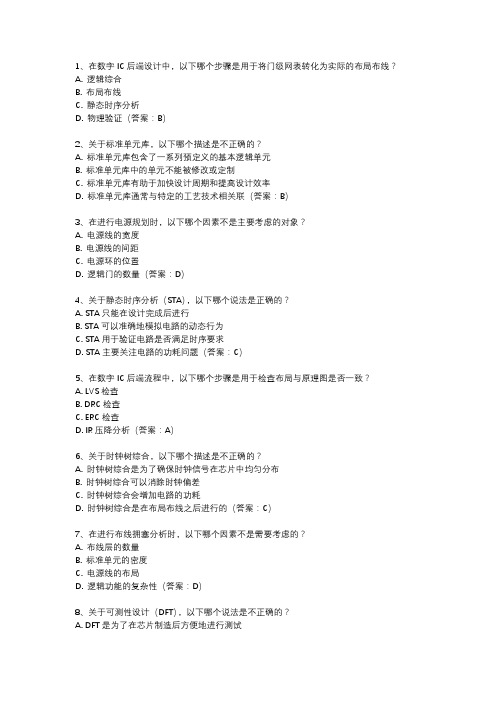

数字ic后端笔试题

1、在数字IC后端设计中,以下哪个步骤是用于将门级网表转化为实际的布局布线?A. 逻辑综合B. 布局布线C. 静态时序分析D. 物理验证(答案:B)2、关于标准单元库,以下哪个描述是不正确的?A. 标准单元库包含了一系列预定义的基本逻辑单元B. 标准单元库中的单元不能被修改或定制C. 标准单元库有助于加快设计周期和提高设计效率D. 标准单元库通常与特定的工艺技术相关联(答案:B)3、在进行电源规划时,以下哪个因素不是主要考虑的对象?A. 电源线的宽度B. 电源线的间距C. 电源环的位置D. 逻辑门的数量(答案:D)4、关于静态时序分析(STA),以下哪个说法是正确的?A. STA只能在设计完成后进行B. STA可以准确地模拟电路的动态行为C. STA用于验证电路是否满足时序要求D. STA主要关注电路的功耗问题(答案:C)5、在数字IC后端流程中,以下哪个步骤是用于检查布局与原理图是否一致?A. LVS检查B. DRC检查C. ERC检查D. IR压降分析(答案:A)6、关于时钟树综合,以下哪个描述是不正确的?A. 时钟树综合是为了确保时钟信号在芯片中均匀分布B. 时钟树综合可以消除时钟偏差C. 时钟树综合会增加电路的功耗D. 时钟树综合是在布局布线之后进行的(答案:C)7、在进行布线拥塞分析时,以下哪个因素不是需要考虑的?A. 布线层的数量B. 标准单元的密度C. 电源线的布局D. 逻辑功能的复杂性(答案:D)8、关于可测性设计(DFT),以下哪个说法是不正确的?A. DFT是为了在芯片制造后方便地进行测试B. DFT会增加一些额外的逻辑用于测试C. DFT会降低芯片的性能D. DFT可以完全替代功能测试(答案:D)。

前后端交互实习报告

一、实习背景随着互联网技术的飞速发展,前后端分离的开发模式已成为业界主流。

为了更好地了解这一模式,提升自己的实际操作能力,我于2021年7月至2021年9月期间在一家知名互联网公司进行了为期两个月的实习。

实习期间,我主要负责前后端交互的开发工作,通过实际项目操作,积累了丰富的实践经验。

二、实习内容1. 项目介绍实习期间,我参与了一个电商平台的开发项目。

该项目采用前后端分离的架构,前端使用Vue.js框架,后端使用Node.js和MongoDB。

项目主要包括商品展示、购物车、订单管理等功能模块。

2. 前后端交互(1)数据交互在项目开发过程中,前后端交互主要采用RESTful API方式进行数据交互。

前端通过发送HTTP请求,向后端获取数据;后端接收请求,处理业务逻辑,并将结果返回给前端。

(2)状态管理为了实现前后端数据同步,前端使用Vuex进行状态管理。

当后端返回数据时,前端通过Vuex将数据存储在全局状态中,以便其他组件可以访问和使用。

(3)错误处理在前后端交互过程中,可能会出现各种错误。

为了提高用户体验,前端需要对接收到的错误信息进行处理。

例如,当后端返回错误码时,前端可以根据错误码显示相应的提示信息。

3. 性能优化(1)数据缓存为了提高页面加载速度,前端对常用数据进行缓存处理。

当用户访问页面时,前端首先从缓存中获取数据,若缓存中没有数据,则向后端请求。

(2)异步加载为了提升用户体验,前端采用异步加载的方式加载图片、视频等资源。

当用户滚动页面时,前端会动态加载下一页的数据,从而避免页面加载时间过长。

4. 跨域请求在开发过程中,前端遇到跨域请求的问题。

为了解决这个问题,后端使用CORS(跨源资源共享)策略,允许前端跨域访问数据。

三、实习收获1. 技术能力提升通过实习,我掌握了前后端分离的开发模式,熟悉了Vue.js、Node.js、MongoDB等框架和技术。

同时,我对HTTP协议、RESTful API、状态管理、性能优化等知识点有了更深入的理解。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基本后端流程(漂流&雪拧)----- 2010/7/3---2010/7/8本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。

此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。

此后端流程大致包括一下内容:1.逻辑综合(逻辑综合是干吗的就不用解释了把?)2.设计的形式验证(工具formality)形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。

另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是否逻辑等价。

3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。

(PR后也需作signoff 的时序分析)4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR)5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。

6.APR后的门级功能仿真(如果需要)7.进行DRC和LVS,如果通过,则进入下一步。

8.用abstract对此8*8乘法器进行抽取,产生一个lef文件,相当于一个hard macro。

9.将此macro作为一个模块在另外一个top设计中进行调用。

10.设计一个新的ASIC,第二次设计,我们需要添加PAD,因为没有PAD,就不是一个完整的芯片,具体操作下面会说。

11.重复第4到7步1.逻辑综合1)设计的8*8verilog代码如下module mux (clk,clr,data1,data2,dataout);input clk,clr;input [7:0] data1,data2;output reg [15:0] dataout;always @(posedge clk)beginif(!clr)begindataout<=0;endelsebegindataout<=data1*data2;endendendmodule2)综合之前,我们要选取库,写好约束条件,修改dc的启动文件synopsys_dc.setup,目标库选择TSMC (此设计都是用TSMC18的库)的typical.db。

(选择max库会比较好)Dc的命令众多,但是最基本的命令差不多,此设计的约束文件命令如下:create_clock -period 10 [get_ports clk] //用于时钟的创建set_clock_latency -source -max 0.2 [get_ports clk] //外部时钟到core的clk连线延时set_clock_latency -max 0.1 [get_ports clk] //core的clk到寄存器clk端的net连线延时set_clock_uncertainty -setup 2 [get_ports clk] //时钟延时的不确定性,求setup违规时会被计算进去set_clock_uncertainty –hold 1 【all_clocks】set_input_delay -max 0.5 -clock clk [get_ports [list [remove_from_coll [all_inputs] clk] ] //输入延时,外部信号到input端的连线延时set_output_delay -max 0.5 -clock clk [all_outputs] //输出延时set_driving_cell -lib_cell INVX4 [all_inputs] //输入端的驱动强度set_load -pin_load 0.0659726 [all_outputs] //输出端的驱动力set_wire_load_model -name tsmc18_wl10 -library typical //内部net的连线模型set_wire_load_mode enclosed //定义建模连线负载相关模式set_max_area 0compilereport_timingreport_constraintchange_names -rule verilog –hierset_fix_multiple_ports_net –allwrite -format verilog -hier -output mux.sv //输出网表,自动布局布线需要write -format ddc -hier -output mux.ddc //输出ddcwrite_sdf mux.sdf //输出延时文件,静态时序分析时需要write_sdc mux.sdc //输出约束信息,自动布局布线需要3)逻辑综合启动design_vision。

Read->mux.v输入约束文件。

File->excute script->verti.con之后会产生mux.sv,mux.sdc,mux.sdf,mux.ddc等文件4)时序分析综合以后我们需要分析一下时序,看时序是否符合我们的要求,综合实际上是一个setup时间的满足过程,但是我们综合的时候,连线的负载只是库提供的(即上面的wire_load),并不是实际的延时,所以一般做完综合以后,时间余量(slack)应该为时钟的30%(经验值),以便为后面实际布局布线留下充足的延时空间。

因为如果slack太小,甚至接近于0,虽然我们看起来是没有时序违规的,但是实际布局以后,时序肯定无法满足。

使用report_timing命令,可以查看时序分析报告:****************************************Report : timing-path full-delay max-max_paths 1-sort_by groupDesign : muxVersion: D-2010.03-SP1Date : Fri Jul 2 12:29:44 2010****************************************Operating Conditions: typical Library: typical(模型库)Wire Load Model Mode: enclosedStartpoint: data2[4] (input port clocked by clk)Endpoint: dataout_reg_15_(rising edge-triggered flip-flop clocked by clk)Path Group: clkPath Type: maxDes/Clust/Port Wire Load Model Library------------------------------------------------mux tsmc18_wl10 typical (线载模型及库)Point Incr Path-------------------------------------------------------------------------- clock clk (rise edge) 0.00 0.00clock network delay (ideal) 0.00 0.00input external delay 0.50 0.50 f data2[4] (in) 0.01 0.51 f mult_14/b[4] (mux_DW_mult_uns_0) 0.00 0.51 f mult_14/U131/Y (INVX1) 0.54 1.05 r mult_14/U161/Y (NOR2X1) 0.14 1.18 f mult_14/U39/S (CMPR42X1) 0.68 1.87 f mult_14/U12/CO (ADDFX2) 0.32 2.19 f mult_14/U11/CO (ADDFX2) 0.23 2.42 f mult_14/U10/CO (ADDFX2) 0.23 2.65 f mult_14/U9/CO (ADDFX2) 0.23 2.88 f mult_14/U8/CO (ADDFX2) 0.23 3.10 f mult_14/U7/CO (ADDFX2) 0.23 3.33 f mult_14/U6/CO (ADDFX2) 0.23 3.56 f mult_14/U5/CO (ADDFX2) 0.23 3.79 f mult_14/U4/CO (ADDFX2) 0.23 4.02 f mult_14/U3/CO (ADDFX2) 0.23 4.25 f mult_14/U2/CO (ADDFX2) 0.22 4.47 f mult_14/product[15] (mux_DW_mult_uns_0) 0.00 4.47 f dataout_reg_15_/RN (DFFTRXL) 0.00 4.47 f data arrival time 4.47clock clk (rise edge) 10.00 10.00clock network delay (ideal) 0.30 10.30clock uncertainty -0.10 10.20dataout_reg_15_/CK (DFFTRXL) 0.00 10.20 r library setup time -0.19 10.01 data required time 10.01-------------------------------------------------------------------------- data required time 10.01data arrival time -4.47-------------------------------------------------------------------------- slack (MET) 5.55我们来看以上报告,dc报告的时候会显示出关键路径,即延时最大的路径,时序分析包括两段,前面一段是信号的延迟时间,即data arrival time 为4.47,下面是计算要求时间,也即相对于时钟,设计所能忍受的最大延时,由于到达寄存器clk端延时,即clock network delay,所以设计增加了0.30的余量,同样由于时钟的不确定度(可能提前也可能延后0.1),我们取最坏情况,就是时钟超前0.1,则时间余量减去0.1,最后一个是门的建立时间要求,是0.19,最后得到数据的要求时间。