数字IC芯片设计

热完整性:低功耗IC数字设计必备的技术

热完整性:低功耗IC数字设计必备的技术在本年度的设计自动化大会上,新老供给商都争相推出功率设计工具,旨在为数字IC设计师提供评估功耗的一种更好方法。

要点O泄漏的功耗随温度呈指数增长。

O在90nm工艺结点上,泄漏占总功耗的25%"45%o在65nm 工艺时,泄漏占总功耗50%~70%。

O片上温度会影响时序。

温度每增加15C,延迟会增加约IO(T15%。

O随着温度增加,EM也会呈指数增长,使产品寿命降低四倍。

O电阻与温度呈线性关系,会影响IR降。

15。

C的温度变化会使电阻值增加10%oO时钟门控与多线程CMOS加剧了片上的热量变化。

过去三年以来,芯片设计师对IC功率管理的关注已经从原先的第三位跃到了第一位,特别是对那些便携系统应用中ASIC和SoC的设计师而言,情况更是如此。

于是,在今年六月美国加州AnaheinI举行的设计自动化大会(DAC)上初次亮相了许多功率工具。

专家们称,若要真正控制晶体管泄漏(这种泄漏占系统功耗的比重越来越大),就必须先了解自己设计的热效应,以及它们对数字IC时序与可靠性的影响。

专家们声称,一旦准确计算出了芯片的发热量,就可以使自己的设计最大限度地具备正确的功耗、性能和可靠性。

如果你正采用90nm或13OnnI工艺的几何尺寸开展设计,就会明白IC功率管理是一个大问题。

有几家EDA公司开发了一些估算有效功耗的工具,有效功耗是通过正常运行而计算出的系统消耗的能量。

有些供给商也已经开发了试图说明泄漏功率的工具,这是系统处于待机模式时晶体管泄漏的功率。

泄漏在0.13mm工艺时就是一个问题,当设计进入90nm和65nm工艺时愈加严重。

专家们认为,没有准确的热分析,设计师就无法考虑泄漏问题以及IC功耗。

Apache设计方案公司总裁兼CEOAndrewYang说:“随着温度上升,泄漏会呈指数增加。

TSMC(台积电)公司推测,泄漏要消耗50%的总功率。

我们已经向用90nm硅片实现设计的客户询问过此问题,他们的答案是泄漏要消耗25%〜40%的功率。

第三章 数字IC系统的RTL级设计

.D6 (RAM3_D2), .A5 (RAM3_A1), .A6 (RAM3_A2),

module TOP ( … BIST U1 ( .D1 (RAM1_D1), .D2 (RAM1_D2), .A1 (RAM1_A1), .A2 (RAM1_A2)),

U3 ( .D1(RAM3_D1), .D2 (RAM3_D2), .A1 (RAM3_A1), .A2 (RAM3_A2),

采用 if…else 结构

module single_if ( a, b, c, d, sel ) input a, b, c, d; input[3:0] sel; output z; reg z; always @( a or b or c or d or sel ) begin z = 0;

二、同步电路的设计要求

• 寄存器的结构

• 寄存器的结构

寄存器的功能

• 建立时间与保持时间

• recovery/removal

§2 几个典型问题的处理

• • • • • 状态机设计 多时钟域的处理 时钟切换问题 时延问题 布线问题

一、状态机的设计

状态机的分类: • Mealy模型 • Moore模型

//状态寄存器,时序逻辑

always @ ( posedge clk or negedge rst_n ) if ( ! rst_n ) state <= IDLE; else state <= next;

//新状态产生,组合逻辑

Always @ ( state or go or ws ) begin next = 2’bx; case ( state ) IDLE: if (go ) next = READ; else next = IDLE; READ: next = DLY; DLY: if ( ws ) next = READ; else next = DONE; DONE: next = IDLE; endcase end

集成电路(IC)设计完整流程详解及各个阶段工d具简介

IC设计完整流程及工具IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。

前端设计的主要流程:1、规格制定芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2、详细设计Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、HDL编码使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

4、仿真验证仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。

看设计是否精确地满足了规格中的所有要求。

规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。

设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Mentor 公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL 级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。

该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

5、逻辑综合――Design Compiler仿真验证通过,进行逻辑综合。

逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。

综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。

所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。

数字IC设计笔试面试经典100题

1:什么是同步逻辑和异步逻辑?(汉王)同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系。

同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。

改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入x 有无变化,状态表中的每个状态都是稳定的。

异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。

2:同步电路和异步电路的区别:同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

3:时序设计的实质:时序设计的实质就是满足每一个触发器的建立/保持时间的要求。

4:建立时间与保持时间的概念?建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。

5:为什么触发器要满足建立时间和保持时间?因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。

这就是为什么要用两级触发器来同步异步输入信号。

这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

(比较容易理解的方式)换个方式理解:需要建立时间是因为触发器的D端像一个锁存器在接受数据,为了稳定的设置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来锁存状态,从后级门传到前级门需要时间。

一文解析IC设计工程师就业前景、发展方向(RFIC、模拟IC、数字IC)

一文解析IC设计工程师就业前景、发展方向(RFIC、模拟IC、数字IC)本文首先介绍了ic设计行业发展现状及工程师工作的内容,其次介绍了IC 设计工程师就业前景及发展方向的探究,最后阐述了如何才能成为一个优秀的ic设计工程师。

IC设计行业发展现状IC设计处于集成电路产业的龙头地位,对产业整体的发展起着带动作用。

到2010年中国半导体市场将占世界总需求量的6%,位居全球第四。

未来几年内中国芯片生产有望每年以魂2%的速度递增,这大大高于全球10%的平均增长速度。

目前,中国现有400多所高校设置了计算机系,新近又特批了51所商业化运作的软件学院。

但这些软件学院和计算机系培养的是程序员。

中国目前只有十来所大学能够培养IC设计专业的学生。

因此工C设计专业人才处于极度供不应求的状态。

可以这样说,这正是我国很大程度上没有足够的IC卡设计人才的根源。

IC设计工程师工作内容负责数字电路的规格定义、RTL代码编写、验证、综合、时序分析、可测性设计;负责进行电路设计、仿真以及总体布局和修改;制作IC芯片功能说明书;负责与版图工程师协作完成版图设计;提供技术支持。

ic设计工程师职业前景ic设计工程师不是越老前景越差,反而随着高科技的发展,越来越吃香。

集成电路是信息产业的核心技术之一,是实现把我国信息产业做大做强的战略目标的关键。

近期发布的“国家中长期科学和技术发展规划纲要”和“国民经济和社会发展第十一个五年规划纲要”,都把大力发展IC技术和产业放在突出重要的位置,因此IC设计工程师的前途光明。

全球对半导体芯片的需求量迅猛增长,中国也正加入这一供给行列中。

对于中国而言,芯片生产不仅是创利的途径,也是走入高科技经济的一条捷径。

如今,大陆80%的半导体依赖进口,但企业们正努力开发、生产能参与世界竞争的芯片。

作为这个行业的后来者,。

IC设计流程课件

综合(Synthesis)

门级验证(Gate-level Verification)

后端设计(Back-end Design)

电路参数提取(Circuit Extraction)

版图后仿真(Post-layout Simulation)

物理

生产(Manufacture) 测试(Test)

数据形式与工具

目前DC可称作ASIC业界最流行的综合工具和 实际标准

09/11/08

6

西安邮电学院ASIC中心

静态时序分析工具

CMOS集成电路版图

静态时序分析技术是一种穷尽分析方法,可以 提取整个电路的所有时序路径,且不依赖于激 励,运行速度很快,占用内存很少,适合进行 超大规模的片上系统电路的验证,可以节省多 达20%的设计时间,但是静态时序分析存在的 问题在于不了解电路的动态行为。

09/11/08

11

西安邮电学院ASIC中心

版本管理工具

CMOS集成电路版图

在芯片开发流程中,文档、代码、网表 、工具配置脚本、工艺库甚至EDA工具本 身都在不断变更,版本控制的重要性日益 凸显。

常用的版本管理工具有CVS、Subvision 等,都包括windows和linux等版本。

09/11/08

IC设计流程课件

09/11/08

1

数字IC设计的流程

CMOS集成电路版图

逻辑

流程

需求分析(Requirement)

算法设计(Algorithm Optimization)

结构设计(Architecture Exploration)

RTL设计(RTL Design)

RTL验证(RTL Verification)

数字ic设计流程与模拟IC

数字ic设计流程与模拟IC1. 首先是使用HDL语言进行电路描述,写出可综合的代码。

然后用仿真工具作前仿真,对理想状况下的功能进行验证。

这一步可以使用Vhdl或Verilog作为工作语言,EDA工具方面就我所知可以用Synopsys的VSS(for Vhdl)、VCS(for Verilog)Cadence的工具也就是著名的Verilog-XL和NC Verilog2.前仿真通过以后,可以把代码拿去综合,把语言描述转化成电路网表,并进行逻辑和时序电路的优化。

在这一步通过综合器可以引入门延时,关键要看使用了什么工艺的库这一步的输出文件可以有多种格式,常用的有EDIF格式。

综合工具Synopsys的Design Compiler,Cadence的Ambit3,综合后的输出文件,可以拿去做layout,将电路fit到可编程的片子里或者布到硅片上这要看你是做单元库的还是全定制的。

全定制的话,专门有版图工程师帮你画版图,Cadence的工具是layout editor单元库的话,下面一步就是自动布局布线,auto place & route,简称apr cadence的工具是Silicon Ensembler,Avanti的是Apollo layout出来以后就要进行extract,只知道用Avanti的Star_rcxt,然后做后仿真,如果后仿真不通过的话,只能iteration,就是回过头去改。

4,接下来就是做DRC,ERC,LVS了,如果没有什么问题的话,就tape out GDSII格式的文件,送制版厂做掩膜板,制作完毕上流水线流片,然后就看是不是work 了做DRC,ERC,LVSAvanti的是Hercules,Venus,其它公司的你们补充好了btw:后仿真之前的输出文件忘记说了,应该是带有完整的延时信息的设计文件如:*.VHO,*.sdfRTL->SIM->DC->SIM-->PT-->DC---ASTRO--->PT----DRC,LVS--->TAPE OUT1。

数字IC设计

数字IC设计数字IC设计是指采用数字电路元件和技术,在符合设定功能要求的基础上,实现指定功能的集成电路设计。

数字IC设计是集成电路设计的一个重要分支,该设计应用面广,广泛应用于通信、计算机、工业、家用电器等领域中。

本文将从数字IC设计的概念、发展历程、设计方法、常用的设计工具等方面进行探讨。

一、数字IC设计的概念数字IC设计是指使用数字电路元件及技术,在设定的功能要求的前提下,实现指定功能的集成电路的设计。

数字IC设计是由组合逻辑、时序逻辑、存储器等数字电路元件构成的。

数字IC设计的核心是实现数字电路设计的复杂性,在各种复杂的应用领域中,进行数字电路系统的快速设计和优化。

数字IC设计的关键是实现函数逻辑关系的描述和形式化,使用数字语言,对电路系统的逻辑关系进行严格的描述和方便化的实现。

数字IC设计具有复杂性、可扩展性、可靠性、精度高、功耗低等特点。

二、数字IC设计的发展历程数字IC设计发展历程从20世纪60年代开始,到今天数十年来经历了从基础到高级的一系列发展过程。

其中有一些重要的里程碑事件,大大促进了数字IC设计的发展。

早期的数字IC设计是使用硬件直接链接模拟电路实现,其设计过程比较简单,如模拟计算器。

1971年,美国Texas Instruments公司推出了世界上第一款集成电路计算器TMS0100,该计算器采用了数字IC设计技术进行实现。

在此之后,数字IC设计开始迎来了快速的发展,人们越来越依赖集成电路和数字IC设计技术带来的方便和高效性。

20世纪80年代,数字IC的设计和制造技术日趋成熟,数字IC的速度和芯片的集成度愈加高。

随着数字IC设计技术的不断提高和发展,出现了大规模集成(LSI),超大规模集成(VLSI)和超高规模集成(UHVSI)等技术,这一系列的技术标志着数字IC设计的进一步发展。

21世纪以来,数字IC设计技术与微电子技术的迅速发展,尤其是3D器件、功能扩张技术和生物微型芯片等的出现,有力地推动了数字IC设计技术向更为高级、复杂和智能方向发展,以应对日益复杂的计算和控制技术需求。

数字IC设计方法学(共52张PPT)

➢比方,RTL综合等后端处理阶段和RTL代码功能仿真阶段可以并行进行;再如, 后端设计过程中的静态时序分析和后仿真可以并行进行。 ➢多阶段之间的并行操作缩短了IC设计周期,但也给设计中数据管理提出了更 高要求,因为多个操作阶段间有数据依赖关系。 ➢设计各阶段间的反复迭代和并行操作要求数字IC设计必须有严格的数据管理机 制才能保证工程正常进行。

➢在指令装载状态下,可重构密码协处理器将密码程序中的指令按顺序装载到指令存 储器中。在指令执行状态下,可重构密码协处理器自动地、不断地从指令存储器中取 出指令、进行译码并加以执行,直至所有指令执行完毕。在空闲状态下,可重构密码 协处理器不进行指令装载操作和指令执行操作,并保持所有的运算结果存放器的值不 变。 ➢主处理器只需对指令执行使能信号ins_exe施加一个脉冲,就可以将可重构密码协处理 器设置为指令执行状态,从而启动指令自动执行过程,然后在整个过程中不再需要主处理 器的干预,这大大减少了主处理器的控制开销和可重构密码协处理器访问外部设备的开销 ,提高了加/解密的处理速度。

clk rst insnumr_en insw_en

指令装载 控制逻辑

i n s w_a d d r< 1 2 : 0 >

d a t a b u<s7 : 0 >

clk

rst

o p c o d<ex : 0 > c o n d a t<ax : 0 >

jump_id halt_id

逻辑

指令译码

ins<207:0> comp_id<4:0>

可重构密码协处理器

数字ic设计知识点

数字ic设计知识点数字 IC 设计知识点数字 IC 设计是现代电子系统设计中的重要领域之一,它涉及到数字电路设计、逻辑设计、时序设计等多个方面的知识点。

本文将为您介绍一些基本的数字 IC 设计知识点,希望对您在该领域的学习和实践有所帮助。

I. 逻辑门逻辑门是数字 IC 设计中最基本的组成单元,它能够实现布尔逻辑运算。

常见的逻辑门包括与门、或门、非门、与非门、或非门、异或门等。

逻辑门的功能可以通过真值表或逻辑表达式来描述。

II. 布尔代数布尔代数是数字 IC 设计中描述逻辑运算的基本数学工具。

它包括布尔运算、布尔函数和布尔表达式等概念。

通过使用布尔代数,可以简化逻辑电路的设计和分析过程。

III. 组合逻辑电路组合逻辑电路是由逻辑门和连线连接而成的电路。

它的输出仅取决于当前的输入状态,与过去的输入状态无关。

组合逻辑电路可以实现各种逻辑功能,如加法器、减法器、多路选择器等。

IV. 时序逻辑电路时序逻辑电路是由逻辑门、存储元件和时钟信号组成的电路。

它的输出取决于当前的输入状态以及过去的输入状态。

时序逻辑电路可以实现各种时序功能,如触发器、计数器、状态机等。

V. 数字系统数字系统是由数字 IC 设计构成的系统,它可以完成数字信号的处理和运算。

常见的数字系统包括二进制系统、八进制系统、十进制系统和十六进制系统等。

VI. IC 设计流程IC 设计流程是指从需求分析到芯片生产的全过程,它包括需求分析、系统设计、电路设计、物理设计、验证仿真和芯片生产等阶段。

严格的 IC 设计流程可以确保芯片的功能和性能符合设计要求。

VII. 数字 IC 设计工具数字 IC 设计工具是用于辅助数字 IC 设计的软件工具,它包括逻辑设计工具、布局设计工具、验证仿真工具等。

常用的数字 IC 设计工具有EDA工具、VHDL/Verilog语言和IC设计软件等。

VIII. 数字 IC 测试数字IC 测试是指对已制造的芯片进行功能验证和故障检测的过程。

数字IC设计学习路线

数字IC必读书籍本文将从简单到复杂的顺序依次列出数字IC设计需要阅读的书籍。

1、数字电路基础数字IC设计最基础的书籍了,相关书籍比较多,可以随意挑选:主要是为了弄清楚与或门电路,触发器、译码器、脉冲产生、逻辑化简等待。

读书策略: 用时短、打基础、必读认真阅读、把书中的习题都做一遍、每章节重点必须要掌握。

书籍选择: 数字电路与系统(第3版)戚金清,王兢编2、《数字集成电路--电路、系统与设计》经典书籍:畅销书、本书详细地介绍了MOS管原理、CMOS组合逻辑、时序逻辑、加法器乘法器等运算单元、存储结构、以及时序、互连、电路寄生效应,包含充分的理论分析和电路结构图。

掌握此书能为数字IC设计打下非常坚固的基础。

读书策略:非常重要、堪称数字IC设计基石、慢慢研读---基础书籍此书耗时较长,不必一口气看完,慢慢研读即可、掌握其中的理论知识、理论推导不必非常了解,能够知道公式的结论即可。

3、《Verilog数字系统设计教程(第4版)》Verilog语言学习经典书籍,教你学会使用Verilog编写电路,实现常见功能。

Verilog是IC设计必须掌握的语言、常备此书,时常查阅。

读书策略:必读、时常查阅----基础书籍第一遍可以快速阅读、知道知识点含义以及相应的位置、忘记的时候翻一翻书籍。

4、《Verilog编程艺术》本书介绍了大量verilog实现实例、包含计算单元、分频电路、状态机等,并且介绍了verilog设计的良好习惯,可以称之为初学者的Verilog规范与素材库。

读书策略:verilog进阶书籍、常备---进阶书籍对于初学者来说,此书很使用,Verilog数字系统设计教程知识介绍了verilog的设计语法与少量实例,此书能够帮助我们更扎实的掌握verilog语言、能够教会我们如何使用verilog语言设计电路。

5、《专用集成电路设计实用教程》此书介绍了集成电路设计的整个流程,其中重点介绍了综合原理、电路优化、最后还介绍了后端各流程的知识点。

数字IC的设计流程及验证方法介绍

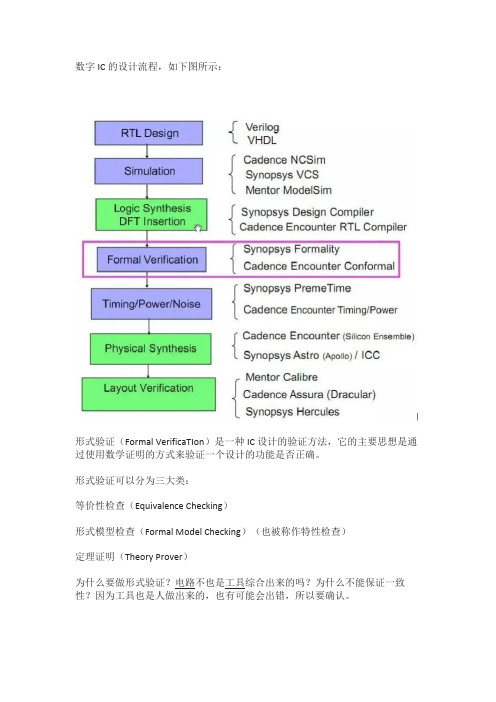

数字IC的设计流程,如下图所示:形式验证(Formal VerificaTIon)是一种IC设计的验证方法,它的主要思想是通过使用数学证明的方式来验证一个设计的功能是否正确。

形式验证可以分为三大类:等价性检查(Equivalence Checking)形式模型检查(Formal Model Checking)(也被称作特性检查)定理证明(Theory Prover)为什么要做形式验证?电路不也是工具综合出来的吗?为什么不能保证一致性?因为工具也是人做出来的,也有可能会出错,所以要确认。

我们平时做的最多的模拟仿真,就是给各种case的输入,穷尽各种组合,总是希望100%的验证到所有的情况。

但是有些情况下,你不太可能达到这一个目的。

假如有一个32位的比较器:比较产生等于、大于、大于的结果。

假设采用一个快速模拟器,每微秒运行一个向量,则用模拟器模拟完全部模拟向量需要的时间为:264 (all input patterns)X 10^-6—————————————————3600 (seconds)X 24 (hours)X 365 (days)≈584,942 years显然这是一个不切实际的验证时间。

而形式验证使用严格的数学推理来证明待测试设计的正确性,由于其静态、数学的特性,避免了对所有可能测试向量的枚举,而且能够达到100%无死角的检测。

定理证明是形式验证技术中最高大上的,它需要设计行为的形式化描述,通过严格的数学证明,比较HDL描述的设计和系统的形式化描述在所有可能输入下是否一致。

这种验证方法需要非常深厚的数学功底,而且不能完全自动化,所以应用案例较少。

当然还是有一些例子,例如HOL系统、PVS系统和ACL2系统等,并且都有成功应用案例。

Moore等人验证了AMD5K86芯片的除法算法的微码,Brock等验证了Motorola的CAP处理器,Clark等验证了SRT除法算法。

模型检验是一种检测设计是否具有所需属性的方法,如安全性、活性和公平性。

数字IC设计——整理

数字集成电路设计整理一、概念1. ASIC——Application Specific Integrated Circuit专用集成电路ASIC在批量生产时与通用集成电路(IC)相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

全定制能够比半定制的ASIC芯片运行速度更快。

2.IP——Intellectual Property知识产权3.数字后端指将前端设计产生的门级网表通过EDA设计工具进行布局布线和进行物理验证并最终产生供制造用的GDSII数据的过程。

其主要工作职责有:芯片物理结构分析、逻辑分析、建立后端设计流程、版图布局布线、版图编辑、版图物理验证、联络代工厂并提交生产数据。

作为连接设计与制造的桥梁,合格的版图设计人员既要懂得IC 设计、版图设计方面的专业知识,还要熟悉制程厂的工作流程、制程原理等相关知识。

4.Standard Cell——标准单元库5.RTL——寄存器传输级描述通过一个寄存器到另一个寄存器的逻辑变换和传输来描述设计。

逻辑值被存储在寄存器中,通过一些组合逻辑对其要求值,随后将结果存储于下一个寄存器。

RTL的功能类似于软件与硬件之间的桥梁。

是与工艺无关的网表的文本结构描述。

6.布局(Place)布线(Route)布图规划floorplan比布局更重要。

规划包括指令,macro的放置,电源线的设计power plan。

floorplan一旦确定,芯片的面积就定下来了,也与整个设计的timming和布通率有很大关系。

高级数字IC设计

同步

“同步”:两个触发器简单的组合在一起如图所 示。

如果遇到触发器的setup time和hold time,这将是cell 设计者保证输入能够正确变为输出的时间。亚稳态影 响物理系统的时间分辨率,同样也影响输出值。

在理论上,当取样操作接近被取样事件的时候,时间 分辨率是无限的渐进曲线。

MTBF(平均无故障时间)与可靠性

如果一个设计中包含同步组件,无论是否愿意它都会 出现亚稳态。亚稳态无法彻底消除,因此我们所做的 就是计算错误概率以及在时间上来描述它。

亚稳态

亚稳态:是指触发器无法在某个规定时间段内达到一个可 确认的状态。

当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也 无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期 间,触发器输出一些中间级电平,或者可能处于振荡状态,并且 这种无用的输出电平可以沿信号通道上的各个触发器级联式传播 下去。

亚稳态发生的原因 在 同 步 系 统中 , 如 果触发器 的 setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端 Q在有效时钟沿之后比较长的一段时间处于不确定的状 态,在这段时间里Q端毛刺、振荡、固定的某一电压值, 而不是等于数据输入端D的值。这段之间成为决断时间 (亚稳态到稳定稳态的时间)(resolution time)。 经过resolution time之后Q端将稳定到0或1上,但是 究竟是0还是1,这是随机的,与输入没有必然的关系。

数模混合IC设计流程

数模混合IC设计流程1.数模混合IC设计近十年来,随着深亚微米及纳米技术的发展,促使芯片设计与制造由分离IC、ASIC 向SoC转变,现在SoC芯片也由数字SoC全面转向混合SoC,成为真正意义上的系统级芯片。

如今人们可以在一块芯片上集成数亿只晶体管和多种类型的电路结构。

此时芯片的制造工艺已经超越了传统制造理论的界限,对电路的物理实现具有不可忽略的影响。

因此,片上系统所依赖的半导体物理实现方式,面临着多样化和复杂化的趋势,设计周期也越来越长。

目前越来越多的设计正向混合信号发展。

最近,IBS Corp做过的一个研究预测,到2006年,所有的集成电路设计中,有73%将为混合信号设计。

目前混合信号技术正是EDA业内最为热门的话题。

设计师在最近才开始注意到混合信号设计并严肃对待,在他们意识到这一领域成为热点之前,EDA公司已经先行多年。

EDA业内领头的三大供应商Mentor Graphics、Synopsys和Cadence在几年前即开始合并或研发模拟和混合信号工具和技术。

其中Mentor Graphics是第一个意识到这一点,并投入力量发展混合信号技术的EDA供应商。

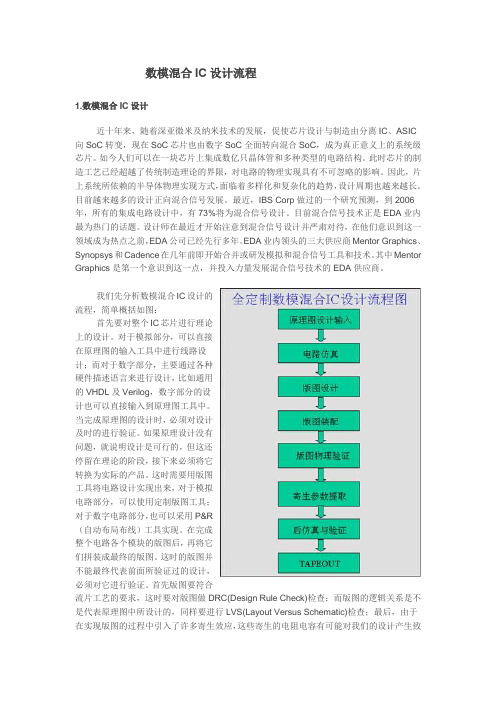

我们先分析数模混合IC设计的流程,简单概括如图:首先要对整个IC芯片进行理论上的设计。

对于模拟部分,可以直接在原理图的输入工具中进行线路设计;而对于数字部分,主要通过各种硬件描述语言来进行设计,比如通用的VHDL及Verilog,数字部分的设计也可以直接输入到原理图工具中。

当完成原理图的设计时,必须对设计及时的进行验证。

如果原理设计没有问题,就说明设计是可行的,但这还停留在理论的阶段,接下来必须将它转换为实际的产品。

这时需要用版图工具将电路设计实现出来,对于模拟电路部分,可以使用定制版图工具;对于数字电路部分,也可以采用P&R(自动布局布线)工具实现。

在完成整个电路各个模块的版图后,再将它们拼装成最终的版图。

这时的版图并不能最终代表前面所验证过的设计,必须对它进行验证。

数字IC低功耗设计综述

ACV 2 f 图WA1V功I 耗sho的rt 电 V路I示le意ak 图f A C V W

由公式(2)可f 以A看出C:V降低W跳变功耗可以通过降

低 载

器f

电

件A的

容或

工C作

者降

电V 压W和工 低WA电VI路sh的ort

作跳v频变WA率因E、子(V减来WddA小实V单现VI sth元;ho)rt器与3 v件短WA的路E负功(Vdd

结构重构是利用在电路中插入缓冲器或冗余电 路的方法来消除由于路径延迟不同而引起的glitch, 消除glitch对输出的影响,而且不改变原电路实现的 功能。不过,冗余电路本身会增加一定的功耗。

数字电路中,时钟的翻转必然会引起各时序单 元的动作,使得相同的输入值在每个时钟周期都被 重复加载进后面的寄存器中,使后面的寄存器、时 钟网络和多选器产生不必要的功耗。插入门控电路 可以将寄存器的时钟关闭,防止时钟触发寄存器, 大幅度降低功耗[7]。时钟门控[8]技术可以说是当前最 有效的低功耗技术,可以减少30% ~ 40%的功耗。时 钟门控技术可以作用于局部电路或一个模块,也可 以作用于整个电路。作用范围越大,功耗减少越显 著,但是门控时钟的插入可以引起时钟脉冲相位差 不平衡和额外的插入延迟。

采用先进的工艺,能获得更小的晶体管尺寸, 有助于减小互连线长度和开关电容,从而有助于降低 电路功耗[3]。同样地,多层金属布线可以避免使用大 范围连线,减少开关电容降低功耗。但是多层金属会 导致耦合寄生电容的增加,抵消部分降低的功耗。

过,降低电源电压会使得延迟增加、性能下降。作 为折中,可以在阈值电压不变的情况下,采取多电 源电压(Multi Supply Multi Voltage, MSMV)的方 法。即在系统的关键时序路径上,采用较高的电源 电压保证整个系统的性能,而在其它路径上,采用 低的电源电压以减少功耗。不过,电平转换电路的 增加是其主要的制约因素。

数字IC芯片设计

Formal Verification (Scan Inserted Netlist

vs CT Inserted Netlist)

Auto Routing

DRC,LVS,ECO

Formal Verification (ECO Netlist vs

CT Inserted Netlist)

述

• 综合:

•

将RTL级设计中所得的程序代码翻

译成实际电路的各种元器件以及他们

之间的连接关系,可以用一张表来表

示,称为门级网表(Netlist)。

• STA(Static Timing Analysis,静态时

序分析): 套用特定的时序模型(

Timing Model),针对特定电路分析

其是否违反设计者给定的时序限制(

30

得到最后的布线图

31

时钟树综合

时钟树综合的目的: 低skew 低clock latency

时钟树和复位树综合为什么要放在APR时再做呢?

32

DFM (Design For Manufacturing)

DFM: 可制造性设计 DFM步骤在整个布局布线流程以后开始,主要目的是通 过一些技术处理防止芯片在物理制造过程中出现问题,造 成芯片不能工作。DFM的目的在于提高良率。

Post-layout STA

Power check

Timing OK? Yes

Tape Out

DC MODELSIM MBISTARCHITECT FORMALITY

PT

Astro AstroRail FORMALITY

PT Hercules Caliber Virtuoso

5

数字IC设计

• Cadence Incisive • Synopsys VCS • Mentor Graphics Questasim

• 高级验证语言

• SystemVerilog • SystemC

• 验证方法学:

• Assertion based verification • SytemVerilog:UVM验证方法学

1. 导入netlist 2. 创建floorplan 3. 添加电源环、电源带、特殊物理单元 4. Place 5. 电源route 6. 时钟树综合 7. Route 8. Metal fill

后端设计

Innovus

• 启动方法: • 输入命令innovus

• 关闭之后有时会导致终端打字不显示,输入reset可以解决

• 大括号中的表达式不解析,可看作列表

• 过程、条件判断、循环等可以先不用

综合——设置库

• 设置库既可以在脚本里设置,也可以设置在家目录 的.synopsys_dc.setup文件

• 主要设置4个变量

• search_path 指定各个文件的搜索路径 • target_library 综合的目标库文件,通常是.db文件 • link_library 包含*(内存中的库)以及target_library和macro library • symbol_library 符号库,通常是.sdb文件,可以没有

5. 设置输入阻抗为0 set_drive

6. 设置为禁止优化网络 set_dont_touch_network

7. 设置为理想网络 set_ideal_network

• 对于pll时钟和分频时钟,只需要设置频率倍数,不需要设置上述参数 • 高级时钟控制:Clock gating • 通常把各个参数设得严格一些,以保留一些设计余量

数字ic设计流程

数字ic设计流程数字IC设计流程。

数字IC设计是一项复杂而精密的工程,它涉及到从概念设计到验证和生产的全过程。

在数字IC设计流程中,需要经过多个阶段的设计、验证和优化,以确保最终产品的性能和可靠性。

本文将介绍数字IC设计的整体流程,并对每个阶段进行详细的分析和说明。

首先,数字IC设计的第一步是概念设计。

在这个阶段,设计团队需要明确产品的功能需求和性能指标,并进行初步的架构设计和功能分解。

同时,还需要进行市场调研和竞品分析,以确保产品的竞争力和市场需求。

接下来是RTL设计阶段。

在这个阶段,设计团队需要将概念设计转化为可实现的RTL(Register Transfer Level)描述。

这个过程涉及到逻辑设计、时序分析、面积优化等工作,需要充分考虑电路的性能、功耗和面积等指标。

然后是综合与布局阶段。

在这个阶段,设计团队需要对RTL描述进行综合,生成门级网表,并进行布局布线。

这个过程需要充分考虑电路的时序和布局约束,以确保电路的性能和可靠性。

接着是验证与仿真阶段。

在这个阶段,设计团队需要对设计的功能和性能进行全面的验证和仿真。

这包括功能仿真、时序仿真、功耗仿真等多个方面,以确保设计的正确性和可靠性。

最后是物理验证和后端流程。

在这个阶段,设计团队需要进行DRC(Design Rule Check)和LVS(Layout Versus Schematic)等物理验证工作,以确保电路的版图符合工艺的制程要求。

同时,还需要进行后端流程的工艺转换和芯片生产的准备工作。

综上所述,数字IC设计流程涉及到多个阶段的设计、验证和优化。

每个阶段都需要设计团队的精心设计和严格验证,以确保最终产品的性能和可靠性。

同时,数字IC设计流程也需要充分考虑市场需求和竞争情况,以确保产品的竞争力和市场地位。

希望本文的介绍能够对数字IC设计流程有一个全面的了解,并为相关从业人员提供一定的参考和帮助。

数字ic设计方法技巧与实践

数字ic设计方法技巧与实践

本书主要介绍数字IC设计的方法、技巧和实践。

全书涵盖数字电路设计的基本知识、数字系统设计流程、数字信号处理技术、数字模拟混合信号设计、FPGA设计和验证、ASIC设计和验证等方面。

具体内容包括:数字电路基础知识、组合逻辑设计、时序逻辑设计、存储器和寄存器设计、数字信号处理技术、FPGA设计实践、ASIC设计流程、数字设计中的时序约束与时钟分配、数字系统的抗干扰设计、数字模拟混合信号设计等。

本书适合从事数字IC设计工作的从业人员、学习数字电路基础知识的大学本科生和研究生使用。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Logic Synthesis,Optimization & Scan Insertion

No No

Formal Verification (RTL vs Gates)

Pre-layout STA

Timing OK? Yes

Floorplanning & Placement,

CT Insertion

Formal Verification (Scan Inserted Netlist

vs CT Inserted Netlist)

Auto Routing

DRC,LVS,ECO

Formal Verification (ECO Netlist vs

CT Inserted Netlist)

• LVS:Layout Versus Schematic ,版图电路图一致性检查。

APR(Auto Place And Route,自动布局布线)

布局布线主要是通过EDA工具来完成的

• 芯片布图(RAM,ROM等的摆放、芯片供电网络配置、 I/O PAD摆放)

• 标准单元的布局 • 时钟树综合 • 布线 • DFM(Design For Manufacturing)

Post-layout STA

Power check

Timing OK? Yes

Tape Out

DC MODELSIM MBISTARCHITECT FORMALITY

PT

Astro AstroRail FORMALITY

PT Hercules Caliber Virtuoso

数字IC设计流程

算法模型 c/matlab code

Timing Constraint) 整个ASIC设计流程都是一个迭代的流程,在 任何一步不能满足要求,都需要重复之前步 骤,甚至重新设计RTL代码。

模拟电路设计的迭代次数甚至更多。。。

前端工具

• 仿真和验证 1. QUATURS II 2. Cadence的Incisive:就是大家最常用的nc_verilog,

Standcell library

RTL HDL vhdl/verilog

综合工具根据基本单元库的功能-时序模型,将行 为级代码翻译成具体的电路实现结构

NETLIST verilog

LAYOUT GDSII

布局布线工具根据基本单元库的时序-几何模型, 将电路单元布局布线成为实际电路版图

对功能,时序,制造参数进行检查

• 综合:

将RTL级设计中所得的程序代码翻译成 实际电路的各种元器件以及他们之间的 连接关系,可以用一张表来表示,称为 门级网表(Netlist)。

• STA(Static Timing Analysis,静态时 序分析):套用特定的时序模型( Timing Model),针对特定电路分析 其是否违反设计者给定的时序限制(

• 5、creat power ring

在power里选择power planing→add rings会弹出add ring对话框

TAPE-OUT

前端设计(RTL to Netlist)

RTL Code

风格代码检查

代码修改

功能仿真

逻辑综合 成功?

约束修改

N

综合后仿真

成功?

N

STA

成功?

N

Netlist 后端

• RTL(Register Transfer Level)设计

利用硬件描述语言,如verilog,对电路 以寄存器之间的传输为基础进行描述

nc_sim, nc_lauch,verilog-xl的集合 。 • 综合 1. Synopsys的DC 2. Cadence的RTL Compliler号称时序,面积和功耗都优

于DC,但是仍然无法取代人们耳熟能详的DC. 3. BuildGates :与DC同期推出的综合工具,但是在国内

基本上没有什么市场,偶尔有几家公司用。 4. 启动命令:bg_shell –gui&

后端设计(Netlist to Layout)

Netlist

ARP

Extrat RC N

STA 成功?

DRC 成功?

N

Layout Edit

LVS

成功?

N

后仿真

• APR:Auto Place and Route,自动 布局布线

• Extract RC:提取延时信息

• DRC:Design Rule Check,设 计规则检查。

4、布图规划floorplan

一开始有默认值,但我们需要对自动布局的结果进来手 工调整。 Floorplan→specify Floorplan 我们需要芯片具体的尺寸要求改变里面的数值。 将Ratio(H/W) 改为1 将core utilization改为0.5 将core to left /right/top/bottom 改为10

模拟?

OR

数字?

数字IC设计流程

数字IC设计流程

制定芯片的具体指标 用系统建模语言对各个模块描述 RTL设计、RTL仿真、硬件原型验证、

电路综合 版图设计、物理验证、后仿真等

具体指标

•制作工艺 •裸片面积 •封装

•速度 •功耗

•功能描述 •接口定义

前端设计与后端设计

数字前端设计(front-end) 以生成可以布局布线的网 表(Netlist)为终点。

数字后端设计( back-end ) 以生成可以可以送交 foundry进行流片的GDS2 文件为终点。 术语: tape-out—提交最终GDS2 文件做加工; Foundry—芯片代工厂,如 中芯国际。。。

Concept + Market Research Architechtural specs & RTL coding

➢ 网表文件:bin/accu_synth.v

➢ 约束文件:bin/accu.sdc

➢ 时序库: hjtc18_ff.lib hjtc18_ss.lib hjtc18_tt.lib

➢ IO约束文件:bin/accu.io

Import design

• 3、在advanced的power里添加 VDD GND

APR工具

APR

工具

Synopsys

ASTRO

Cadence

Encounter

布局布线流程

IO,电源和地的布置

指

布线

ENCOUTER布局布线设计流程

1、登录服务器,进入终端,输入:encounter ,进入soc encounter

2、调入门级网表和库