plc外文翻译

PLC毕业设计外文翻译3

学校名称外文翻译专业:班级学号:学生姓名:指导教师:二〇一一年六月学校名称本科生毕业设计原文1:Programmable logic controllers 译文1:可编程逻辑控制器原文2:Foundation of PLC译文2:PLC基础专业班级:学生姓名:指导教师:学院:2011年6月原文1:Programmable logic controllersProgrammable logic controller(PLC) is eight 10- Year on behalf new generation industry that develop the control equip, and is an automatic control, calculator with the thing that the correspondence technique combine together, and is a the spot equipments for exclusively used foring the industry production line controling. Make the PLC there is characteristics of obvious oneself on the design with the long- term and continuous that circulate because of the special of the complexity, usage environment of the control object: The dependable is high, and the adaptability is wide, and have to correspond by letter the function, and weave the the convenience, construction mold piece . Gather the the control in the modern in the system, the PLC have already become a kind of importance of basic control unit, control the realm the inside in the industry applied the foreground is very and extensive.A programmable logic controller(PLC) is a solid-state devide used to control machine motion or process operation by means of a stored program. The PLC sends output control signals and receives input signals through input/output (I/O) devices.A PLC controls outputs in response to stimuli at the inputs according to the logic prescribed by the stored program.The inputs are made up of limit switches,pushbuttons,thumbwheels, switches,pulses,analog signals,ASCII serial data,and binary or BCD data from absolute position encoders.The outputs are voltage or current levers to drive end devices such as lolenids,motor staters,relays,lights,and so on.Other output devices such include analog devices,digital BCD displays,ASCII compatible devices,servo variable-speed drives,and even computers.Programmable controllers were developed(circa in 1968) when General Motors Corp,and other automobile manufacturers were experimenting to see if there might be an alterantive to scrapping all their hardwired control panels of machine tools and other production equipment during a model changeover.This annual tradition was necessary because rewiring of the panels was more expensive than buying new oens.The automotive companies approached a number of control equipment manufacturers and asked them to develop a control system that would have a longer productive life without major rewiring,but would still be understandable to and repairable by plant personnel.The new product wa namd a“programmable controller”.The processor part of the PLC contains a central processing unit and memory.The central proce ssing unit(CPU) is the“trafficdirector”of the processor,the memory stores ing into the processor are the electrical signals from the input devices,as conditioned by the input module to voltage levels acceptable to processor logic.The processor scans the state of I/O and updates outputs based on instructions stored in the memory of the PLC.For example,the processor may be programmed so that if an input connected to a limit switch is true(1imit switch closed),then a corresponding output wired to an output module is to be energized.This output might be asolenoid for example.The processor remembers this command through its memory and compares on each scan to see if that limit is, in fact ,closed. If it is closed, the processor energizes the solenoid by turning on the output module.The output device, such as a solenoid or motor stater,is wired to an output mofule’s terminal,and itreceives its shift signal from the processor, in effect the peocessor is performing a long and complicated series of logic decisions. The PLC performs such decisions sequentially and in accordance with the stored program.similarly, analog I/O allows the processor to make decisions based on the magnitude of a signal, rather than just if is on or off.For example,the processor may be programmes toencrease or decrease the steam flow to a boiler(analog output) based on a comparison of the actual temperature in the boiler(analog input) to the desired temperature. this is often performed by utilizing the built-in PID(proportional,integral,derivative) capabilities of the processor.Proper power to the programmable controller is critical. Today’s systems are available in a wide variety of electrical configurations. Virtually all are designed for use in single-phase power systems, and most are now beginning to be offered with the optional ability to operate in a DC supply environment. AC designs are offered in either single voltage supplies, such as 115 or 230V AC; while some can be configured as either through a selection made on the power supply. Proper grounding of the power supply connection is required for a safe installation. Some programmable controller designs have individual grounding connections from rack to face- plates and other system components, so care must be taken to follow well electrical practice in system grounding during electricalinstallation. In certain applications, a 24 or 120 V DC power supply is required. This is common for installations that axe made where no AC power is available, such as remote electrical generation stations. It is also found where AC power is unreliable and where loss of control is considered an unacceptable situationEven the best of today' s well-designed and manufactured programmable controllers require occasional preventative maintenance and repair. This section looks at some of the tools provided by the manufacturer and techniques for general maintenance.Most of the medium- and large-sized programmable controller systems available today are designed to be maintained by individuals with a wide variety of skills, without the benefit of in-depth formal training of this piece of equipment. This is accomplished in the design by providing individual modules of functionality installed in a chassis serviced from the front (all module types including power supplies). Front access is critical to proper maintenance. This allows easy inspection and replacement of the suspected bad module. Module health is determined by inspecting the LED indicators normally provided on the front of each module. Typical indicators will be on or off depending on the design and individual condition of the module in question. Various CPU and I/O modules will have indicators showing I/O control communications status, memory integrity, power supply tolerance check, scan integrity, and others. On future controller designs, and even today on a few systems, it is likely that English language messages will be displayed on the controller advising the user or maintenance personnel that a particular failure has occurred and recommended actions to take.The modular design and diagnostic indicators are, of course, important, but would be quite useless without well designed documentation provided by the manufacturer for the programmable controller system in question. Proper documentation will have sections dedicated to each major subsystem including CPU, I/O, and programming device. Each should explain in depth the stop-by-stop inspection of the system. All possible combinations of failure mode should be listed, along with suggested actions for repair. This will most often involve only the substitution of a re- placement board for the suspected failed unit. The user is urged to purchase a set of spare modules for the system in question as recommended by the manufacturer. This is normally, at a minimum, a single replacement module for each CPU and programming device serviceable module, and spare I/O modules equal to 10% of the number in the system.Because a PLC is “software based”,its control logic functions can be changed byreprogramming its memory. Keyboard programming devices facilitate entry of the revised program, which can be designed to cause an existing machine or process to operate in a different sequence or to respond to different levels of, or combinations of stimuli .Hardware modifications are needed only if additional, changed, or relocated input/output devices are involved.Programmable controller memory is formatted into bits, bytes, and words of memory.A bit is a single storage element for either a zero or a one. A byte consists of eight bits, and a word (normally) consists of 16 bits, or two bytes. Some systems still use a word length of eight bits, but most have adopted a 16 bit word, even though they may use an 8 bit microprocessor.Depending on the specific design of the programmable controller, it will have a stated memory capacity. This is an indication, although not the only one, of the capability and power of the system. Medium and large controllers are normally expandable from one memory size to their maximum size. Small controllers are normally fixed in their memory size. Size of the memory capacity must be examined relative to the word size ( 8 bit or 16 bit) and utilization. While it is clear that twice the information can be stored in a 16 bit word than in an 8 bit word, it may not be immediately clear that some controllers utilize memory more efficiently than others. For example, a normally open contact and its associated reference address (e.g. Input 1), may use in 8 bit byte each for storage. Combined, they consume one 16 bit word. Some controllers may use more memory than this for these instructions or others. In a large program, these inefficiencies can build on each other to cause a poor utilization of the system memory. A careful analysis of the various programmable controller models is required to assess utilization efficiency. Normal practice calls for an additional 20% - 40% of memory size to be specified to allow for modifications and later expansion. This analysis, combined with knowledge of the application needs, will allow for an intelligent choice of programmable controller.In fine, PLC conduct and actions the spot control equipments, can dependable,accurately complete the control the operation, and can pass with upper grade work machine correspondence, constitute the distribute type the system to complete to control the industry equip. system control request, is a modern industry control the inside compare forerunner’s control project, and apply the foreground to is extensive.译文1:可编程逻辑控制器可编程逻辑控制器(PLC)是八十年代发展起来的新一代工业控制装置,是自动控制、计算机和通信技术相结合的产物,是一种专门用于工业生产过程控制的现场设备。

PLC中英文资料外文翻译

附录外文资料PLC technique discussion and future development Along with the development of the ages, the technique that is nowadays is also gradually perfect, the competition plays more more strong; the operation that list depends the artificial has already can't satisfied with the current manufacturing industry foreground, also can't guarantee the request of the higher quantity and high new the image of the technique business enterprise.The people see in produce practice, automate brought the tremendous convenience and the product quantities for people up of assurance, also eased the personnel's labor strength, reduce the establishment on the personnel. The target control of the hard realization in many complicated production lines, whole and excellent turn, the best decision etc., well-trained operation work, technical personnel or expert, governor but can judge and operate easily, can acquire the satisfied result. The research target of the artificial intelligence makes use of the calculator exactly to carry out, imitate these intelligences behavior, moderating the work through person's brain and calculators, with the mode that person's machine combine, for resolve the very complicated problem to look for the best pathWe come in sight of the control that links after the electric appliances in various situation, that is already the that time generation past, now of after use in the mold a perhaps simple equipments of grass-roots control that the electric appliances can do for the low level only;And the PLC emergence also became the epoch-making topic, adding the vivid software control through a very and stable hardware, making the automation head for the new high tide.The PLC biggest characteristics lie in: The electrical engineering teacher already no longer electric hardware up too many calculationses of cost, as long as order the importation that the button switch or the importation of the sensors order to link the PLC up can solve problem, pass to output to order the conjunction contact machine or control the start equipments of the big power after the electric appliances, but theexportation equipments direct conjunction of the small power can.PLC internal containment have the CPU of the CPU, and take to have an I/ O for expand of exterior to connect a people's address and saving machine three big pieces to constitute, CPU core is from an or many is tired to add the machine to constitute, mathematics that they have the logic operation ability, and can read the procedure save the contents of the machine to drive the homologous saving machine and I/ Os to connect after pass the calculation; The I/ O add inner part is tired the input and output system of the machine and exterior link, and deposit the related data into the procedure saving machine or data saving machine; The saving machine can deposit the data that the I/ O input in the saving machine, and in work adjusting to become tired to add the machine and I/ Os to connect, saving machine separately saving machine RAM of the procedure saving machine ROM and datas, the ROM can can do deposit of the data permanence in the saving machine, but RAM only for the CPU computes the temporary calculation usage of hour of buffer space.The PLC anti- interference is very and excellent, our root need not concern its service life and the work situation bad, these all problems have already no longer become the topic that we fail, but stay to our is a concern to come to internal resources of make use of the PLC to strengthen the control ability of the equipments for us, make our equipments more gentle.PLC language is not we imagine of edit collected materials the language or language of Cs to carry on weaving the distance, but the trapezoid diagram that the adoption is original after the electric appliances to control, make the electrical engineering teacher while weaving to write the procedure very easy comprehended the PLC language, and a lot of non- electricity professional also very quickly know and go deep into to the PLC.Is PLC one of the advantage above and only, this is also one part that the people comprehend more and easily, in a lot of equipmentses, the people have already no longer hoped to see too many control buttons, they damage not only and easily and produce the artificial error easiest, small is not a main error perhaps you can still accept; But lead even is a fatal error greatly is what we can't is tolerant of. Newtechnique always for bringing more safe and convenient operation for us, make we a lot of problems for face on sweep but light, do you understand the HMI? Says the HMI here you basically not clear what it is, also have no interest understanding, change one inside text explains it into the touch to hold or man-machine interface you knew, it combines with the PLC to our larger space.HMI the control not only only is reduced the control press button, increase the vivid of the control, more main of it is can sequence of, and at can the change data input to output the feedback with data, control in the temperature curve of imitate but also can keep the manifestation of view to come out. And can write the function help procedure through a plait to provide the help of various what lies in one's power, the one who make operate reduces the otiose error. Currently the HMI factory is also more and more, the function is also more and more strong, the price is also more and more low, the noodles of the usage are wide more and more. The HMI foreground can say that think ° to be good very.At a lot of situations, the list is is a smooth movement that can't guarantee the equipments by the control of the single machine, but pass the information exchanges of the equipments and equipments to attain the result that we want. For example fore pack and the examination of the empress work preface, we will arrive wrapping information feedback to examine the place, and examine the information of the place to also want the feedback to packing. Pass the information share thus to make both the chain connect, becoming a total body, the match of your that thus make is more close, at each other attain to reflect the result that mutually flick.The PLC correspondence has already come more more body now its value, at the PLC and correspondence between PLCs, can pass the communication of the information and the share of the datas to guarantee that of the equipments moderates mutually, the result that arrive already to repair with each other. Data conversion the adoption RS232 between PLC connect to come to the transmission data, but the RS232 pick up a people and can guarantee 10 meters only of deliver the distance, if in the distance of 1000 meters we can pass the RS485 to carry on the correspondence, the longer distance can pass the MODEL only to carry on deliver.The PLC data transmission is just to be called a form to it in a piece of and continuous address that the data of the inner part delivers the other party, we, the PLC of the other party passes to read data in the watch to carry on the operation. If the data that data in the watch is a to establish generally, that is just the general data transmission, for example today of oil price rise, I want to deliver the price of the oil price to lose the oil ally on board, that is the share of the data; But take data in the watch for an instruction procedure that controls the PLC, that had the difficulty very much, for example you have to control one pedestal robot to press the action work that you imagine, you will draw up for it the form that a procedure combine with the data sends out to pass by.The form that information transport contain single work, the half a work and the difference of a workses .The meaning of the single work also is to say both, a can send out only, but a can receive only, for example a spy he can receive the designation of the superior only, but can't give the superior reply; A work of half is also 2 and can can send out similar to accept the data, but can't send out and accept at the same time, for example when you make a phone call is to can't answer the phone, the other party also; But whole pair works is both can send out and accept the data, and can send out and accept at the same time. Be like the Internet is a typical example.The process that information transport also has synchronous and different step cent: The data line and the clock lines are synchronous when synchronous meaning lie in sending out the data, is also the data signal and the clock signals to be carry on by the CPU to send out at the same time, this needs to all want the specialized clock signal each other to carry on the transmission and connect to send, and is constrained, the characteristics of this kind of method lies in its speed very quick, but correspond work time of take up the CPU and also want to be long oppositely, at the same time the technique difficulty also very big. Its request lies in can'ting have an error margins in a datas deliver, otherwise the whole piece according to compare the occurrence mistake, this on the hardware is a bigger difficulty. Applied more and more extensive in some appropriative equipmentses, be like the appropriative medical treatment equipments, the numerical signal equipments...etc., in compare the one data deliver,its result is very good.And the different step is an application the most extensive, this receive benefit in it of technique difficulty is opposite and want to be small, at the same time not need to prepare the specialized clock signal, its characteristics to lie in, its data is partition, the long-lost send out and accept, be the CPU is too busy of time can grind to a stop sex to work, also reduced the difficulty on the hardware, the data throw to lose at the same time opposite want to be little, we can pass the examination of the data to observe whether the data that we send out has the mistake or not, be like strange accidentally the method, tired addition and eight efficacies method etc., can use to helps whether the data that we examine to send out have or not the mistake occurrence, pass the feedback to carry on the discriminator.A line of transmission of the information contain a string of and combine the cent of: The usual PLC is 8 machines, certainly also having 16 machines. We can be an at the time of sending out the data a send out to the other party, also can be 88 send out the data to the other party, an and 8 differentiationses are also the as that we say to send out the data and combine sends out the data. A speed is more and slowly, but as long as 2 or three lines can solve problem, and can use the telephone line to carry on the long range control. But combine the oscular transmission speed is very quick of, it is a string of oscular of 25600%, occupy the advantage in the short distance, the in view of the fact TTL electricity is even, being limited by the scope of one meter generally, it combine unwell used for the data transmission of the long pull, thus the cost is too expensive.Under a lot of circumstances we are total to like to adopt the string to combine the conversion chip to carry on deliver, under this kind of circumstance not need us to carry on to depositted the machine to establish too and complicatedly, but carry on the data exchanges through the data transmission instruction directly, but is not a very viable way in the correspondence, because the PLC of the other party must has been wait for your data exportation at the time of sending out the data, it can't do other works.When you are reading the book, you hear someone knock on door, you stop tostart up of affair, open the door and combine to continue with the one who knock on door a dialogue, the telephone of this time rang, you signal hint to connect a telephone, after connecting the telephone through, return overdo come together knock on door to have a conversation, after dialogue complete, you continue again to see your book, this kind of circumstance we are called the interruption to it, it has the authority, also having sex of have the initiative, the PLC had such function .Its characteristics lie in us and may meet the urgently abrupt affairs in the operation process of the equipments, we want to stop to start immediately up of work, the whereabouts manages the more important affair, this kind of circumstance is we usually meet of, PLC while carry out urgent mission, total will keep the current appearance first, for example the address of the procedure, CPU of tired add the machine data etc., be like to to stick down which the book that we see is when we open the door the page or simply make a mark, because we treat and would still need to continue immediately after book of see the behind. The CPU always does the affair that should do according to our will, but your mistake of give it an affair, it also would be same to do, this we must notice.The interruption is not only a, sometimes existing jointly with the hour several inside break, break off to have the preferred Class, they will carry out the interruption of the higher Class according to person's request. This kind of breaks off the medium interruption to also became to break off the set. The Class that certainly break off is relevant according to various resources of CPU with internal PLC, also following a heap of capacity size of also relevant fasten.The contents that break off has a lot of kinds, for example the exterior break off, correspondence in of send out and accept the interruption and settle and the clock that count break off, still have the WDT to reset the interruption etc., they enriched the CPU to respond to the category while handle various business. Speak thus perhaps you can't comprehend the internal structure and operation orders of the interruption completely also, we do a very small example to explain.Each equipments always will not forget a button, it also is at we meet the urgent circumstance use of, that is nasty to stop the button. When we meet the Human body trouble and surprised circumstances we as long as press it, the machine stops alloperations immediately, and wait for processing the over surprised empress recover the operation again.Nasty stop the internal I/ O of the internal CPU of the button conjunction PLC to connect up, be to press button an exterior to trigger signal for CPU, the CPU carries on to the I/ O to examine again, being to confirm to have the exterior to trigger the signal, CPU protection the spot breaks off procedure counts the machine turn the homologous exterior I/ O automatically in the procedure to go to also, be exterior interruption procedure processing complete, the procedure counts the machine to return the main procedure to continue to work.Have 1:00 can what to explain is we generally would nasty stop the button of exterior break off to rise to the tallest Class, thus guarantee the safety.When we are work a work piece, giving the PLC a signal, counting PLC inner part the machine add 1 to compute us for a day of workload, a count the machine and can solve problem in brief, certainly they also can keep the data under the condition of dropping the electricity, urging the data not to throw to lose, this is also what we hope earnestly.The PLC still has the function that the high class counts the machine, being us while accept some datas of high speed, the high speed that here say is the data of the in all aspects tiny second class, for example the bar code scanner is scanning the data continuously, calculating high-speed signal of the data processor DSP etc., we will adopt the high class to count the machine to help we carry on count. It at the PLC carries out the procedure once discover that the high class counts the machine to should of interruption, will let go of the work on the hand immediately. The trapezoid diagram procedure that passes by to weave the distance again explains the high class for us to carry out procedure to count machine would automatic performance to should of work, thus rise the Class that the high class counts the machine to high one Class.You heard too many this phrases perhaps:" crash", the meaning that is mostly is a workload of CPU to lead greatly, the internal resources shortage etc. the circumstance can't result in procedure circulate. The PLC also has the similar circumstance, there is a watchdog WDT in the inner part of PLC, we can establishtime that a procedure of WDT circulate, being to appear the procedure to jump to turn the mistake in the procedure movement process or the procedure is busy, movement time of the procedure exceeds WDT constitution time, the CPU turn but the WDT reset the appearance. The procedure restarts the movement, but will not carry on the breakage to the interruption.The PLC development has already entered for network ages of correspondence from the mode of the one, and together other works control the net plank and I/ O card planks to carry on the share easily. A state software can pass all se hardwares link, more animation picture of keep the view to carries on the control, and cans pass the Internet to carry on the control in the foreign land, the blast-off that is like the absolute being boat No.5 is to adopt this kind of way to make airship go up the sky.The development of the higher layer needs our continuous effort to obtain.The PLC emergence has already affected a few persons fully, we also obtained more knowledge and precepts from the top one experience of the generation, coming to the continuous development PLC technique, push it toward higher wave tide.摘自《可编程控制器技术讨论与未来发展》中文翻译可编程控制器技术讨论与未来发展随着时代的发展,当今的技术也日趋完善、竞争愈演愈烈;单靠人工的操作已不能满足于目前的制造业前景,也无法保证更高质量的要求和高新技术企业的形象.人们在生产实践中看到,自动化给人们带来了极大的便利和产品质量上的保证,同时也减轻了人员的劳动强度,减少了人员上的编制.在许多复杂的生产过程中难以实现的目标控制、整体优化、最佳决策等,熟练的操作工、技术人员或专家、管理者却能够容易判断和操作,可以获得满意的效果.人工智能的研究目标正是利用计算机来实现、模拟这些智能行为,通过人脑与计算机协调工作,以人机结合的模式,为解决十分复杂的问题寻找最佳的途径我们在各种场合看到了继电器连接的控制,那已经是时代的过去,如今的继电器只能作为低端的基层控制模块或者简单的设备中使用到;而PLC的出现也成为了划时代的主题,通过极其稳定的硬件穿插灵活的软件控制,使得自动化走向了新的高潮。

电气工程及其自动化专业_外文文献_英文文献_外文翻译_plc方面.

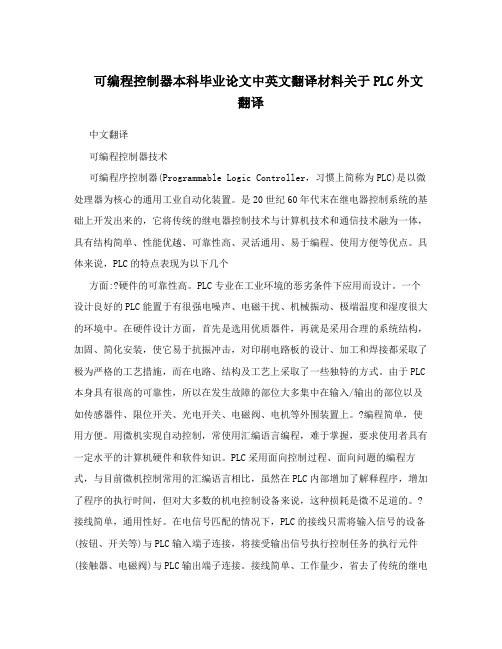

1、外文原文A: Fundamentals of Single-chip MicrocomputerTh e si ng le -c hi p m ic ro co mp ut er i s t he c ul mi na ti on of both t h e de ve lo pm en t of the dig it al com pu te r an d th e in te gr at ed c i rc ui t arg ua bl y t h e tow m os t s ig ni f ic an t i nv en ti on s o f t he 20th c e nt ur y [1].Th es e tow type s of arch it ec tu re are foun d in sin g le -ch i p m i cr oc om pu te r. Som e empl oy the spli t prog ra m/da ta me mo ry of the H a rv ar d ar ch it ect u re , sh ow n in Fig.3-5A -1, oth ers fo ll ow the p h il os op hy , wi del y ada pt ed for gen er al -p ur po se com pu te rs and m i cr op ro ce ss o r s, o f ma ki ng no log i ca l di st in ct ion be tw ee n p r og ra m and dat a me mo ry as in the Pr in ce to n arch ite c tu re , show n i n Fig.3-5A-2.In gen er al ter ms a sin gl e -chi p mic ro co mp ut er i sc h ar ac te ri zed b y t he i nc or po ra ti on of a ll t he un it s of a co mp uter i n to a sin gl e d ev i ce , as sho wn inFi g3-5A -3.Fig.3-5A-1 A Harvard typeFig.3-5A-2. A conventional Princeton computerFig3-5A-3. Principal features of a microcomputerRead only memory (ROM.R OM is usua ll y for the pe rm an ent,n o n-vo la ti le stor a ge of an app lic a ti on s pr og ra m .M an ym i cr oc om pu te rs and m are inte nd e d for high -v ol um e ap pl ic at ions a n d he nc e t h e eco n om ic al man uf act u re of th e de vic e s re qu ir es t h at t he cont en t s o f t he prog ra m me m or y be co mm it t ed perm a ne ntly d u ri ng the man ufa c tu re of ch ip s .Cl ea rl y, thi s im pl ie s a r i go ro us app ro ach to ROM cod e deve l op me nt sin ce cha ng es can not b e mad e afte r manu f a c tu re .Th is dev e lo pm en t proc ess may invo lv e e m ul at io n us in g aso ph is ti ca te d de ve lo pm en t sy ste m wit h a h a rd wa re emu la tio n cap ab il it y as w el l as the use o f po we rf ul s o ft wa re too ls.So me man uf act u re rs pro vi de add it io na l RO M opt i on s by i n cl ud in g in their ra n ge dev ic es wit h (or int en de d fo r use wit h u s er pro gr am ma ble me mo ry. Th e sim p le st of th es e is usu al ly d e vi ce whi ch can op er at e in a micro p ro ce ssor mod e by usi ng som e o f the inp ut /outp u t li ne s as an ad dr es s an d da ta b us fora c ce ss in g ex te rna l mem or y. Thi s t y pe of de vi ce can beh av ef u nc ti on al ly as th e sing le chip mi cr oc om pu te r from whi ch it is d e ri ve d al be it wit h re st ri ct ed I/O and a mod if ied ex te rn al c i rc ui t. The use of thes e d ev ic es is com mo n eve n in prod uc ti on c i rc ui ts wher e t he vo lu me does no tj us ti f y t h e d ev el o pm en t c osts o f c us to m o n -ch i p R OM [2];t he re c a n s ti ll bea s ignif i ca nt saving i n I /O and o th er c h ip s com pa re d to a conv en ti on al mi c ro pr oc es sor b a se d ci rc ui t. Mor e ex ac t re pl ace m en t fo r RO M dev i ce s ca n be o b ta in ed in th e fo rm of va ri an ts w it h 'p ig gy -b ack 'E P RO M(Er as ab le pro gr am ma bl e ROM s oc ke ts or dev ic e s with EPROM i n st ea d o f RO M 。

PLC中英文资料外文翻译

可编程控制器技术讨论与未来发展学生姓名: ******所在院系: ******所学专业: ******导师姓名: ******完成时间:******外文资料PLCtechnique discussion and future developmentWith the development of the times, today's technology is maturing, competition intensified。

rely on manual operation does not satisfy the current industry outlook, there is no guarantee of higher quality requirements and high-tech corporate image.People saw in the production practice, automation to bring great convenience and product quality assurance, but also reduce the labor intensity, reducing the staff on the establishment in many complex production process is difficult to achieve target control, the overall optimization, optimal decision-making, skilled operatives, technicians or specialists, managers can easily determine and operate it, you can get satisfactory results. artificial intelligence research is the use of computers to achieve the target, the analog These intelligent behavior, through coordination of the human brain and a computer to combine human models for solving very complex problem of finding the best way.PLC's most important feature is: electrical engineer electrical hardware no longer spend too much scheming, as long as the button switch or sensor input connected to the PLC input point will solve the problem by connecting the output point contacts or relay to control the power of the boot device, and small power output devices can be connected directly.Contained within the PLC having a central processor of the CPU, and with an external I / O port expansion I / O interface and the memory addresses of three major components, CPU core is formed by one or more accumulators, which have the logical math capabilities, and can read the contents of the program memory to drive through the calculation of the corresponding memory and I / O interface。

可编程控制器本科毕业论文中英文翻译材料关于PLC外文翻译

可编程控制器本科毕业论文中英文翻译材料关于PLC外文翻译中文翻译可编程控制器技术可编程序控制器(Programmable Logic Controller,习惯上简称为PLC)是以微处理器为核心的通用工业自动化装置。

是20世纪60年代末在继电器控制系统的基础上开发出来的,它将传统的继电器控制技术与计算机技术和通信技术融为一体,具有结构简单、性能优越、可靠性高、灵活通用、易于编程、使用方便等优点。

具体来说,PLC的特点表现为以下几个方面:?硬件的可靠性高。

PLC专业在工业环境的恶劣条件下应用而设计。

一个设计良好的PLC能置于有很强电噪声、电磁干扰、机械振动、极端温度和湿度很大的环境中。

在硬件设计方面,首先是选用优质器件,再就是采用合理的系统结构,加固、简化安装,使它易于抗振冲击,对印刷电路板的设计、加工和焊接都采取了极为严格的工艺措施,而在电路、结构及工艺上采取了一些独特的方式。

由于PLC 本身具有很高的可靠性,所以在发生故障的部位大多集中在输入/输出的部位以及如传感器件、限位开关、光电开关、电磁阀、电机等外围装置上。

?编程简单,使用方便。

用微机实现自动控制,常使用汇编语言编程,难于掌握,要求使用者具有一定水平的计算机硬件和软件知识。

PLC采用面向控制过程、面向问题的编程方式,与目前微机控制常用的汇编语言相比,虽然在PLC内部增加了解释程序,增加了程序的执行时间,但对大多数的机电控制设备来说,这种损耗是微不足道的。

?接线简单,通用性好。

在电信号匹配的情况下,PLC的接线只需将输入信号的设备(按钮、开关等)与PLC输入端子连接,将接受输出信号执行控制任务的执行元件(接触器、电磁阀)与PLC输出端子连接。

接线简单、工作量少,省去了传统的继电器控制系统的接线和拆线的麻烦。

PLC的编程逻辑提供了能随要求而改变的逻辑关系,这样生产线的自动化过程就能随意改变。

这种性能使PLC具有很高的经济效益。

用于连接现场设备的硬件接口实际上已经设计成为PLC的组成部分,模块化的自诊断接口电路能指出故障,并易于排除故障与替换故障部件,这样的软硬件设计就使现场电气人员与技术人员易于使用。

PLC的应用外文文献翻译、中英文翻译、外文翻译

Application of PLCPLC is one kind specially for the digital operation operation electronic installation which applies under the industry environment designs. It uses may the coding memory, uses for in its internal memory operation and so on actuating logic operation, sequence operation, time, counting and arithmetic operation instructions, and can through digital or the simulation-like input and the output, controls each type the machinery or the production process. PLC and the related auxiliary equipment should according to form a whole easy with the industrial control system, easy to expand its function the principle to design.”In the 1970s the last stage, the programmable controller entered the practical application development phase, the computer technology has introduced in comprehensively the programmable controller, causes its function to have the leap. The higher operating speed, the subminiature volume, the more reliable industry antijamming design, the simulation quantity operation, the PID function and the extremely high performance-to-price ratio has established it in the modern industry status. In the early-1980s, the programmable controller has obtained the widespread application in the advanced industrial nation. This time programmable controller develops the characteristic is large-scale, the high velocity, the high performance, the product seriation. This stage's another characteristic is in the world produces the programmable controller's country to increase day by day, the output rises day by day. This symbolizes that the programmable controller marched into the mature stage.The 20th century last stage, the programmable controller's development characteristic was even more adapts in the modern industry need. From the control scale, this time has developed the large-scale machinery and subminiature machine; From the control, was born various special function unit, used in the pressure, the temperature, the rotational speed, the displacement and so on all kinds of control situation; From product necessary ability, has produced each kind of man-machine contact surface unit, the correspondence unit, caused to apply the programmable controller's industrial control equipment necessary to be easier. At present, the programmable controller in domain and so on machine manufacture, petroleum chemical industry, metallurgy steel and iron, automobile, light industry applications obtained the considerable development.Our country programmable controller's introduction, applies, the development, the production to follow the reform and open policy to start. At first has used the programmable controller massively in the introduction equipment. Then expanded the PLC application unceasingly in each kind of enterprise's production equipment and the product. At present, our country have been possible to produce the middle and small scale programmable controller. East Shanghai the room electricity Limited company produces the CF series, Hangzhou engine bed electrical equipment factory production's DKK and D series, Dalian Aggregate machine-tool Research institute produces S series, the Suzhou Electronic accounting machine Factory production's YZ series and so on many kinds of products have had certain scale and have obtained the application in the manufactured products. In addition, the non-flowers of tin light company, Chinese-foreign joint ventures and so on Shanghai Township Island Company are also our country quite famous PLC Manufacturers. May anticipate that along with our country modernization process's thorough, PLC will have the broader application world in our country.Uses the manual operation in view of the YNL draw die machine electric control system, the existence operation is complex, the operation requests high, needs specially shortcomings and so on operators, has designed PLC the control system. Has given the electrical machinery main return route, the PLC periphery wiring diagram; Has established the systems operation trapezoidal chart and the instruction list; And to this system key element shaping. After the improvement control system has realized the entire system board process automation, not only raised the production efficiency, but also has saved the labor force, reduced the production cost, may obtain a greater economic efficiency.PLC的应用PLC是一种专门为在工业环境下应用而设计的数字运算操作的电子装置。

有关PLC中英文翻译资料

PLC简介可编程控制器是60年代末在美国首先出现的,当时叫可编程逻辑控制器PLC (Programmable Logic Controller),目的是用来取代继电器。

以执行逻辑判断、计时、计数等顺序控制功能。

提出PLC概念的是美国通用汽车公司。

PLC的基本设计思想是把计算机功能完善、灵活、通用等优点和继电器控制系统的简单易懂、操作方便、价格便宜等优点结合起来,控制器的硬件是标准的、通用的。

根据实际应用对象,将控制内容编成软件写入控制器的用户程序存储器内,使控制器和被控对象连接方便。

70年代中期以后,PLC已广泛地使用微处理器作为中央处理器,输入输出模块和外围电路也都采用了中、大规模甚至超大规模的集成电路,这时的PLC已不再是仅有逻辑(Logic)判断功能,还同时具有数据处理、PID调节和数据通信功能。

国际电工委员会(IEC)颁布的可编程控制器标准草案中对可编程控制器作了如下的定义:可编程控制器是一种数字运算操作的电子系统,专为在工业环境下应用而设计。

它采用了可编程序的存储器,用来在其内部存储执行逻辑运算,顺序控制、定时、计数和算术运算等操作的指令,并通过数字式和模拟式的输入和输出,控制各种类型的机械或生产过程。

可编程控制器及其有关外围设备,易于与工业控制系统联成一个整体,易于扩充其功能的设计。

可编程控制器对用户来说,是一种无触点设备,改变程序即可改变生产工艺。

目前,可编程控制器已成为工厂自动化的强有力工具,得到了广泛的普及推广应用。

可编程控制器是面向用户的专用工业控制计算机,具有许多明显的特点。

①可靠性高,抗干扰能力强;②编程直观、简单;③适应性好;④功能完善,接口功能强。

可编程逻辑控制器(PLC )的计算模块是由理查德.e.莫雷在1968年发明的,现在已广泛应用于工业中的制造系统,运输系统,化工过程控制,以及许多其他领域。

PLC 使用软连线逻辑或所谓的梯形图取代硬接线逻辑,采用编程语言和可视化的模拟硬接线逻辑设计,这样使的系统的配置时间从以前的6个月减少到了6天。

plc外文文献译文

Programmable logic controllerA programmable logic controller(PLC)is a digital computer used for automation of electromechanical processes,such as control of machinery on factory assembly lines,amusement rides,or lighting fixtures.PLC is used in many industries and machines.1.HistoryThe PLC was invented in response to the needs of the American automotive manufacturing industry.Before the PLC,control,sequencing,and safety interlock logic for manufacturing automobiles was accomplished using hundreds or thousands of relays,cam timers,and drum sequencers and dedicated closed-loop controllers. In1968GM Hydramatic issued a request for proposal for an electronic replacement for hard-wired relay systems.The first PLC,designated the084because it was Bedford Associates'eighty-fourth project,was the result.Bedford Associates started a new company dedicated to developing,manufacturing,selling,and servicing this new product:Modicon,which stood for MOdular DIgital CONtroller.The Modicon brand was sold in1977to Gould Electronics,and later acquired by German Company AEG and then by French Schneider Electric,the current owner.One of the very first084 models that was presented to Modicon by GM,when the unit was retired after nearly twenty years of uninterrupted service.Modicon used the84moniker at the end of its product range until the984made its appearance.2.DevelopmentEarly PLCs were designed to replace relay logic systems.These PLCs were programmed in"ladder logic",which strongly resembles a schematic diagram of relay logic.Other early PLCs used a form of instruction list programming,based on a stack-based logic solver.Modern PLCs can be programmed in a variety of ways,from ladder logic to more traditional programming languages such as BASIC and C.Another method is State Logic,a very high-level programming language designed to program PLCs based on state transition diagrams.3.FunctionalityThe functionality of the PLC have sequential relay control,motion control, process control,distributed control systems and networking.Regarding the practicality of these desktop computer based logic controllers,it is important to note that they have not been generally accepted in heavy industry because the desktop computersrun on less stable operating systems than do PLCs,and because the desktop computer hardware is typically not designed to the same levels of tolerance to temperature, In more recent years,small products called PLRs(programmable logic relays), are used in light industry where only a few points of I/O(i.e.a few signals coming in from the real world and a few going out)are involved,and low cost is desired. Popular names include PICO Controller,NANO PLC,and other names implying very small controllers.the PLRs are usually not modular or expandable,but their price can be two orders of magnitude less than a PLC and they still offer robust design and deterministic execution of the logic.4.PLC compared with other control systemsPLCs are well-adapted to a range of automation tasks.These are typically industrial processes in manufacturing where the cost of developing and maintaining the automation system is high relative to the total cost of the automation,and where changes to the system would be expected during its operational life.PLCs contain input and output devices compatible with industrial pilot devices and controls;little electrical design is required,and the design problem centers on expressing the desired sequence of operations.PLC applications are typically highly customized systems so the cost of a packaged PLC is low compared to the cost of a specific custom-built controller design.On the other hand,in the case of mass-produced goods,customized control systems are economic due to the lower cost of the components,which can be optimally chosen instead of a"generic"solution,and where the non-recurring engineering charges are spread over thousands or millions of units.A microcontroller-based design would be appropriate where hundreds or thousands of units will be produced and so the development cost(design of power supplies,input/output hardware and necessary testing and certification)can be spread over many sales,and where the end-user would not need to alter the control. Automotive applications are an example;millions of units are built each year,and very few end-users alter the programming of these controllers.However,some specialty vehicles such as transit busses economically use PLCs instead of custom-designed controls,because the volumes are low and the development cost would be uneconomic.Programmable controllers are widely used in motion control,positioning control and torque control.Some manufacturers produce motion control units to be integrated with PLC so that G-code(involving a CNC machine)can be used to instruct machinemovements.PLCs may include logic for single-variable feedback analog control loop,a "proportional,integral,derivative"or"PID controller".A PID loop could be used to control the temperature of a manufacturing process,for example.Historically PLCs were usually configured with only a few analog control loops;where processes required hundreds or thousands of loops,a distributed control system(DCS)would instead be used.As PLCs have become more powerful,the boundary between DCS and PLC applications has become less distinct.PLCs have similar functionality as Remote Terminal Units.An RTU,however, usually does not support control algorithms or control loops.As hardware rapidly becomes more powerful and cheaper,RTUs,PLCs and DCSs are increasingly beginning to overlap in responsibilities,and many vendors sell RTUs with PLC-like features and vice versa.The industry has standardized on the IEC61131-3functional block language for creating programs to run on RTUs and PLCs,although nearly all vendors also offer proprietary alternatives and associated development environments.5.The prospects for PLC.5.1.FeaturesThe main difference from other computers is that PLCs are armored for severe conditions(such as dust,moisture,heat,cold)and have the facility for extensive input/output(I/O)arrangements.PLCs read limit switches,analog process variables (such as temperature and pressure),and the positions of complex positioning systems. Some use machine vision.On the actuator side,PLCs operate electric motors, pneumatic or hydraulic cylinders,magnetic relays,solenoids,or analog outputs.The input/output arrangements may be built into a simple PLC,or the PLC may have external I/O modules attached to a computer network that plugs into the PLC.5.2System scaleA small PLC will have a fixed number of connections built in for inputs and outputs.Typically,expansions are available if the base model has insufficient I/O. Modular PLCs have a chassis(also called a rack)into which are placed modules with different functions.The processor and selection of I/O modules is customised for the particular application.Several racks can be administered by a single processor,and may have thousands of inputs and outputs.A special high speed serial I/O link is used so that racks can be distributed away from the processor,reducing the wiring costs for large plants.5.3User interfacePLCs may need to interact with people for the purpose of configuration,alarm reporting or everyday control.A simple system may use buttons and lights to interact with the user.Text displays are available as well as graphical touch screens.More complex systems use a programming and monitoring software installed on a computer, with the PLC connected via a communication interface.5.4CommunicationsPLCs have built in communications ports,usually9-pin RS-232,but optionally EIA-485or Ethernet.Modbus,BACnet or DF1is usually included as one of the communications protocols.Other options include various fieldbuses such as DeviceNet or Profibus.Other communications protocols that may be used are listed in the List of automation protocols.Most modern PLCs can communicate over a network to some other system,such as a computer running a SCADA(Supervisory Control And Data Acquisition)system or web browser.PLCs used in larger I/O systems may have peer-to-peer(P2P)communication between processors.This allows separate parts of a complex process to have individual control while allowing the subsystems to co-ordinate over the communication link.These communication links are also often used for HMI devices such as keypads or PC-type workstations.可编程逻辑控制器可编程逻辑控制器(PLC)或可编程序控制器是用于机电过程自动化的数字计算机,例如控制机械厂生产线、游乐设施或照明的装置。

PLC中英文资料外文翻译教学文案

P L C中英文资料外文翻译附录外文资料PLC technique discussion and future development Along with the development of the ages, the technique that is nowadays is also gradually perfect, the competition plays more more strong; the operation that list depends the artificial has already can't satisfied with the current manufacturing industry foreground, also can't guarantee the request of the higher quantity and high new the image of the technique business enterprise.The people see in produce practice, automate brought the tremendous convenience and the product quantities for people up of assurance, also eased the personnel's labor strength, reduce the establishment on the personnel. The target control of the hard realization in many complicated production lines, whole and excellent turn, the best decision etc., well-trained operation work, technical personnel or expert, governor but can judge and operate easily, can acquire the satisfied result. The research target of the artificial intelligence makes use of the calculator exactly to carry out, imitate these intelligences behavior, moderating the work through person's brain and calculators, with the mode that person's machine combine, for resolve the very complicated problem to look for the best pathWe come in sight of the control that links after the electric appliances in various situation, that is already the that time generation past, now of after use in the mold a perhaps simple equipments of grass-roots control that the electric appliances can do for the low level only;And the PLC emergence also became the epoch-making topic, adding the vivid software control through a very and stable hardware, making the automation head for the new high tide.The PLC biggest characteristics lie in: The electrical engineering teacher already no longer electric hardware up too many calculationses of cost, as long as order the importation that the button switch or the importation of the sensors order to link the PLC up can solve problem, pass to output to order the conjunction contact machine orcontrol the start equipments of the big power after the electric appliances, but the exportation equipments direct conjunction of the small power can.PLC internal containment have the CPU of the CPU, and take to have an I/ O for expand of exterior to connect a people's address and saving machine three big pieces to constitute, CPU core is from an or many is tired to add the machine to constitute, mathematics that they have the logic operation ability, and can read the procedure save the contents of the machine to drive the homologous saving machine and I/ Os to connect after pass the calculation; The I/ O add inner part is tired the input and output system of the machine and exterior link, and deposit the related data into the procedure saving machine or data saving machine; The saving machine can deposit the data that the I/ O input in the saving machine, and in work adjusting to become tired to add the machine and I/ Os to connect, saving machine separately saving machine RAM of the procedure saving machine ROM and datas, the ROM can can do deposit of the data permanence in the saving machine, but RAM only for the CPU computes the temporary calculation usage of hour of buffer space.The PLC anti- interference is very and excellent, our root need not concern its service life and the work situation bad, these all problems have already no longer become the topic that we fail, but stay to our is a concern to come to internal resources of make use of the PLC to strengthen the control ability of the equipments for us, make our equipments more gentle.PLC language is not we imagine of edit collected materials the language or language of Cs to carry on weaving the distance, but the trapezoid diagram that the adoption is original after the electric appliances to control, make the electrical engineering teacher while weaving to write the procedure very easy comprehended the PLC language, and a lot of non- electricity professional also very quickly know and go deep into to the PLC.Is PLC one of the advantage above and only, this is also one part that the people comprehend more and easily, in a lot of equipmentses, the people have already no longer hoped to see too many control buttons, they damage not only and easily and produce the artificial error easiest, small is not a main error perhaps you can stillaccept; But lead even is a fatal error greatly is what we can't is tolerant of. New technique always for bringing more safe and convenient operation for us, make we a lot of problems for face on sweep but light, do you understand the HMI? Says the HMI here you basically not clear what it is, also have no interest understanding, change one inside text explains it into the touch to hold or man-machine interface you knew, it combines with the PLC to our larger space.HMI the control not only only is reduced the control press button, increase the vivid of the control, more main of it is can sequence of, and at can the change data input to output the feedback with data, control in the temperature curve of imitate but also can keep the manifestation of view to come out. And can write the function help procedure through a plait to provide the help of various what lies in one's power, the one who make operate reduces the otiose error. Currently the HMI factory is also more and more, the function is also more and more strong, the price is also more and more low, the noodles of the usage are wide more and more. The HMI foreground can say that think ° to be good very.At a lot of situations, the list is is a smooth movement that can't guarantee the equipments by the control of the single machine, but pass the information exchanges of the equipments and equipments to attain the result that we want. For example fore pack and the examination of the empress work preface, we will arrive wrapping information feedback to examine the place, and examine the information of the place to also want the feedback to packing. Pass the information share thus to make both the chain connect, becoming a total body, the match of your that thus make is more close, at each other attain to reflect the result that mutually flick.The PLC correspondence has already come more more body now its value, at the PLC and correspondence between PLCs, can pass the communication of the information and the share of the datas to guarantee that of the equipments moderates mutually, the result that arrive already to repair with each other. Data conversion the adoption RS232 between PLC connect to come to the transmission data, but theRS232 pick up a people and can guarantee 10 meters only of deliver the distance, if inthe distance of 1000 meters we can pass the RS485 to carry on the correspondence, the longer distance can pass the MODEL only to carry on deliver.The PLC data transmission is just to be called a form to it in a piece of and continuous address that the data of the inner part delivers the other party, we, the PLC of the other party passes to read data in the watch to carry on the operation. If the data that data in the watch is a to establish generally, that is just the general data transmission, for example today of oil price rise, I want to deliver the price of the oil price to lose the oil ally on board, that is the share of the data; But take data in the watch for an instruction procedure that controls the PLC, that had the difficulty very much, for example you have to control one pedestal robot to press the action work that you imagine, you will draw up for it the form that a procedure combine with the data sends out to pass by.The form that information transport contain single work, the half a work and the difference of a workses .The meaning of the single work also is to say both, a can send out only, but a can receive only, for example a spy he can receive the designation of the superior only, but can't give the superior reply; A work of half is also 2 and can can send out similar to accept the data, but can't send out and accept at the same time, for example when you make a phone call is to can't answer the phone, the other party also; But whole pair works is both can send out and accept the data, and can send out and accept at the same time. Be like the Internet is a typical example.The process that information transport also has synchronous and different step cent: The data line and the clock lines are synchronous when synchronous meaning lie in sending out the data, is also the data signal and the clock signals to be carry on by the CPU to send out at the same time, this needs to all want the specialized clock signal each other to carry on the transmission and connect to send, and is constrained, the characteristics of this kind of method lies in its speed very quick, but correspond work time of take up the CPU and also want to be long oppositely, at the same time the technique difficulty also very big. Its request lies in can'ting have an error margins in a datas deliver, otherwise the whole piece according to compare the occurrence mistake, this on the hardware is a bigger difficulty. Applied more and more extensivein some appropriative equipmentses, be like the appropriative medical treatment equipments, the numerical signal equipments...etc., in compare the one data deliver, its result is very good.And the different step is an application the most extensive, this receive benefit in it of technique difficulty is opposite and want to be small, at the same time not need to prepare the specialized clock signal, its characteristics to lie in, its data is partition, the long-lost send out and accept, be the CPU is too busy of time can grind to a stop sex to work, also reduced the difficulty on the hardware, the data throw to lose at the same time opposite want to be little, we can pass the examination of the data to observe whether the data that we send out has the mistake or not, be like strange accidentally the method, tired addition and eight efficacies method etc., can use to helps whether the data that we examine to send out have or not the mistake occurrence, pass the feedback to carry on the discriminator.A line of transmission of the information contain a string of and combine the cent of: The usual PLC is 8 machines, certainly also having 16 machines. We can be an at the time of sending out the data a send out to the other party, also can be 88 send out the data to the other party, an and 8 differentiationses are also the as that we say to send out the data and combine sends out the data. A speed is more and slowly, but as long as 2 or three lines can solve problem, and can use the telephone line to carry on the long range control. But combine the oscular transmission speed is very quick of, it is a string of oscular of 25600%, occupy the advantage in the short distance, the in view of the fact TTL electricity is even, being limited by the scope of one meter generally, it combine unwell used for the data transmission of the long pull, thus the cost is too expensive.Under a lot of circumstances we are total to like to adopt the string to combine the conversion chip to carry on deliver, under this kind of circumstance not need us to carry on to depositted the machine to establish too and complicatedly, but carry on the data exchanges through the data transmission instruction directly, but is not a very viable way in the correspondence, because the PLC of the other party must has beenwait for your data exportation at the time of sending out the data, it can't do other works.When you are reading the book, you hear someone knock on door, you stop to start up of affair, open the door and combine to continue with the one who knock on door a dialogue, the telephone of this time rang, you signal hint to connect a telephone, after connecting the telephone through, return overdo come together knock on door to have a conversation, after dialogue complete, you continue again to see your book, this kind of circumstance we are called the interruption to it, it has the authority, also having sex of have the initiative, the PLC had such function .Its characteristics lie in us and may meet the urgently abrupt affairs in the operation process of the equipments, we want to stop to start immediately up of work, the whereabouts manages the more important affair, this kind of circumstance is we usually meet of, PLC while carry out urgent mission, total will keep the current appearance first, for example the address of the procedure, CPU of tired add the machine data etc., be like to to stick down which the book that we see is when we open the door the page or simply make a mark, because we treat and would still need to continue immediately after book of see the behind. The CPU always does the affair that should do according to our will, but your mistake of give it an affair, it also would be same to do, this we must notice.The interruption is not only a, sometimes existing jointly with the hour several inside break, break off to have the preferred Class, they will carry out the interruption of the higher Class according to person's request. This kind of breaks off the medium interruption to also became to break off the set. The Class that certainly break off is relevant according to various resources of CPU with internal PLC, also following a heap of capacity size of also relevant fasten.The contents that break off has a lot of kinds, for example the exterior break off, correspondence in of send out and accept the interruption and settle and the clock that count break off, still have the WDT to reset the interruption etc., they enriched the CPU to respond to the category while handle various business. Speak thus perhaps you can't comprehend the internal structure and operation orders of the interruption completely also, we do a very small example to explain.Each equipments always will not forget a button, it also is at we meet the urgent circumstance use of, that is nasty to stop the button. When we meet the Human body trouble and surprised circumstances we as long as press it, the machine stops all operations immediately, and wait for processing the over surprised empress recover the operation again.Nasty stop the internal I/ O of the internal CPU of the button conjunction PLC to connect up, be to press button an exterior to trigger signal for CPU, the CPU carries on to the I/ O to examine again, being to confirm to have the exterior to trigger the signal, CPU protection the spot breaks off procedure counts the machine turn the homologous exterior I/ O automatically in the procedure to go to also, be exterior interruption procedure processing complete, the procedure counts the machine to return the main procedure to continue to work.Have 1:00 can what to explain is we generally would nasty stop the button of exterior break off to rise to the tallest Class, thus guarantee the safety.When we are work a work piece, giving the PLC a signal, counting PLC inner part the machine add 1 to compute us for a day of workload, a count the machine and can solve problem in brief, certainly they also can keep the data under the condition of dropping the electricity, urging the data not to throw to lose, this is also what we hope earnestly.The PLC still has the function that the high class counts the machine, being us while accept some datas of high speed, the high speed that here say is the data of the in all aspects tiny second class, for example the bar code scanner is scanning the data continuously, calculating high-speed signal of the data processor DSP etc., we will adopt the high class to count the machine to help we carry on count. It at the PLC carries out the procedure once discover that the high class counts the machine to should of interruption, will let go of the work on the hand immediately. The trapezoid diagram procedure that passes by to weave the distance again explains the high class for us to carry out procedure to count machine would automatic performance to should of work, thus rise the Class that the high class counts the machine to high one Class.You heard too many this phrases perhaps:" crash", the meaning that is mostly is a workload of CPU to lead greatly, the internal resources shortage etc. the circumstance can't result in procedure circulate. The PLC also has the similar circumstance, there is a watchdog WDT in the inner part of PLC, we can establish time that a procedure of WDT circulate, being to appear the procedure to jump to turn the mistake in the procedure movement process or the procedure is busy, movement time of the procedure exceeds WDT constitution time, the CPU turn but the WDT reset the appearance. The procedure restarts the movement, but will not carry on the breakage to the interruption.The PLC development has already entered for network ages of correspondence from the mode of the one, and together other works control the net plank and I/ O card planks to carry on the share easily. A state software can pass all se hardwares link, more animation picture of keep the view to carries on the control, and cans pass the Internet to carry on the control in the foreign land, the blast-off that is like the absolute being boat No.5 is to adopt this kind of way to make airship go up the sky.The development of the higher layer needs our continuous effort to obtain.The PLC emergence has already affected a few persons fully, we also obtained more knowledge and precepts from the top one experience of the generation, coming to the continuous development PLC technique, push it toward higher wave tide.摘自《可编程控制器技术讨论与未来发展》中文翻译可编程控制器技术讨论与未来发展随着时代的发展,当今的技术也日趋完善、竞争愈演愈烈;单靠人工的操作已不能满足于目前的制造业前景,也无法保证更高质量的要求和高新技术企业的形象.人们在生产实践中看到,自动化给人们带来了极大的便利和产品质量上的保证,同时也减轻了人员的劳动强度,减少了人员上的编制.在许多复杂的生产过程中难以实现的目标控制、整体优化、最佳决策等,熟练的操作工、技术人员或专家、管理者却能够容易判断和操作,可以获得满意的效果.人工智能的研究目标正是利用计算机来实现、模拟这些智能行为,通过人脑与计算机协调工作,以人机结合的模式,为解决十分复杂的问题寻找最佳的途径我们在各种场合看到了继电器连接的控制,那已经是时代的过去,如今的继电器只能作为低端的基层控制模块或者简单的设备中使用到;而PLC的出现也成为了划时代的主题,通过极其稳定的硬件穿插灵活的软件控制,使得自动化走向了新的高潮。

PLC的工作原理中英文翻译

PLC的工作原理可编程控制器,英文称ProgrammableLogicController,简称PLC。

PLC是基于电子计算机,且适用于工业现场工作的电控制器。

它源于继电控制装置,但它不像继电装置那样,通过电路的物理过程实现控制,而主要靠运行存储于PLC内存中的程序,进行入出信息变换实现控制。

PLC基于电子计算机,但并不等同于普通计算机。

普遍计算机进行入出信息变换,多只考虑信息本身,信息的入出,只要人机界面好就可以了。

而PLC则还要考虑信息入出的可靠性、实时性,以及信息的使用等问题。

特别要考虑怎么适应于工业环境,如便于安装,抗干扰等问题。

当PLC投入运行后,其工作过程一般分为三个阶段,即输入采样、用户程序执行和输出刷新三个阶段。

完成上述三个阶段称作一个扫描周期。

在整个运行期间,PLC的CPU以一定的扫描速度重复执行上述三个阶段。

1.输入采样阶段在输入采样阶段,PLC以扫描方式依次地读入所有输入状态和数据,并将它们存入I/O映象区中的相应得单元内。

输入采样结束后,转入用户程序执行和输出刷新阶段。

在这两个阶段中,即使输入状态和数据发生变化,I/O映象区中的相应单元的状态和数据也不会改变。

因此,如果输入是脉冲信号,则该脉冲信号的宽度必须大于一个扫描周期,才能保证在任何情况下,该输入均能被读入。

2.用户程序执行阶段在用户程序执行阶段,PLC总是按由上而下的顺序依次地扫描用户程序(梯形图)。

在扫描每一条梯形图时,又总是先扫描梯形图左边的由各触点构成的控制线路,并按先左后右、先上后下的顺序对由触点构成的控制线路进行逻辑运算,然后根据逻辑运算的结果,刷新该逻辑线圈在系统RAM存储区中对应位的状态;或者刷新该输出线圈在I/O映象区中对应位的状态;或者确定是否要执行该梯形图所规定的特殊功能指令。

即,在用户程序执行过程中,只有输入点在I/O映象区内的状态和数据不会发生变化,而其他输出点和软设备在I/O映象区或系统RAM存储区内的状态和数据都有可能发生变化,而且排在上面的梯形图,其程序执行结果会对排在下面的凡是用到这些线圈或数据的梯形图起作用;相反,排在下面的梯形图,其被刷新的逻辑线圈的状态或数据只能到下一个扫描周期才能对排在其上面的程序起作用。

PLC基础知识简介外文文献翻译、中英文翻译、外文翻译

附录:外文资料译文PLC elementary knowledge synopsisIn the automated control domain, PLC is one kind of important control device. At present, in the world has more than 200 factories to produce more than 300 varieties PLC product, applies in the automobile (23%), the grain processing (16.4%), chemistry/drugs manufacture (14.6%), the metal/mine (11.5%), the paper pulp/papermaking (11.3%) and so on the profession. In order to make fellow beginners conveniently to understand PLC, this article to the PLC development, the basic structure, the disposition, using and so on the elementary knowledge makes a synopsis.First, PLC development courseIn the industrial production process, the massive switches quantity sequential control, it carries on the smooth movement according to the logical condition, and defers to the logical relations to carry on the chain-like protection movement the control, and massive data acquisition. In the tradition, these functions are realize through air operated or the electricity control system. In 1968 American GM (general automobile) the company proposed the substitution continues the electricity control device the request, the second year, the American numeral company developed based on the integrated circuit and the electronic technology control device, used sequenced the method to apply for the first time to the electrical control, this was the first generation of programmable foreword controller, calledProgrammable Controller (PC).After the personal computer (is called PC) to develop, in order to be convenient, also in order to reflect the programmable controller the function characteristic, the programmable foreword controller chooses a name is Programmable Logic Controller (PLC), now, still frequently was called PLC PC.The PLC definition has many kinds. The international electrician committee (IEC) to PLC the definition is: The programmable controller is one kind of digital operation operation electronic system, specially for applies under the industry environment designs. It uses the programmable foreword the memory, uses for to carry out the logic operation, the sequential control in its internal storage, fixed time, counts with operation the and so on arithmetic operation instruction, and through digital, the simulation input and the output, controls each kind of type the machinery or the production process. The programmable foreword controller and its the related equipment, all should according to easy form a whole with the industry control system, is easy to expand its function the principle design.On the century 80's to the 90's intermediate stages, are PLC develop the quickest time, the yearly rate continuously maintenance are 30-40%. In this time, PLC in the processing simulation quantity ability, the digital operation ability, the man-machine connection ability and the networking capability obtains the large scale enhancement, PLC gradually enters the process control domain, substituted in certain applications has been at the dominant position in the process control domain the DCS system.PLC has the versatility strongly, the easy to operate,the adaption surface broad, the reliability high, the antijamming ability strong, the programming is simple and so on the characteristic. PLC in the industrial automation control specially is in the sequential control status, in future which may foresee, is unable to substitute.Second, PLC constitutionFrom the structure the minute, PLC divides into the stationary type and the combined type (module type) two kinds. Stationary PLC including the CPU board, the I/O board, demonstrated the kneading board, the memory block, the power source and so on, these element groups synthesize a not dismantable whole. Module type PLC including the CPU module, the I/O module, the memory, the power source module, the ledger wall or the rack, these modules may defer to the certain rule combination disposition. Second, PLC constitution.Third, CPU constitutionCPU is the PLC core, plays nerve center's role, every time wraps PLC at least to have CPU, it function receive and storage user program and data which entrusts with according to the PLC system program, with scanning way gathering the condition or the data which sends by the scene input device, and stores the stipulation in the register, simultaneously, diagnoses the power source and in the PLC internal circuit active status and the programming process grammatical error and so on. After enters the movement, reads from the user program memory by the strip takes the instruction, the duty which stipulated according to the instruction produces the corresponding control signal again after the analysis, directs the related control circuit.CPU mainly by the logic unit, the controller, theregister and realizes the data, the control and the condition main line constitution which between them relates, the CPU unit also includes the periphery chip, the main line connection and the related electric circuit. The memory mainly uses in the stored routine and the data, is the PLC essential composition unit.Looked like in the user, nonessential multianalysis CPU internal circuit, but or should have the enough understanding to each part of work mechanism. The CPU controller controls the CPU work, reads by it takes the instruction, the interpretive order and carries out the instruction. But the work rhythm by shakes the signal control. The logic unit uses in to carry on the numeral or the logic operation, works under the controller direction. The register participation operation, coexists stores the operation the intermediate result, it also is works under the controller direction.The CPU speed and the memory capacity are the PLC important parameter, they are deciding the PLC working speed, the IO quantity and the software capacity and so on, therefore is limiting the control scale.Fourth, I/O modulePLC and the electrical return route connection, is (I/O) completes through the input output unit. The I/O module integrated the PLC I/O electric circuit, its input temporary storage device reflection input signal condition, output point reflection output latch condition. The load module transforms the electrical signal the digital signal to enter the PLC system, the output module is opposite. I/O divides into the switch quantity input (DI), switch quantity output (DO), simulation quantity input (AI), simulation quantity output (AO) and so on module.The switch quantity is refers has and closes (or 1 and 0) two kind of conditions signals, the simulation quantity is only a quantity which refers continuously changes. Commonly used I/O classifies as follows:Switch quantity: Divides equally according to the voltage water, has 220VAC, 110VAC, 24VDC, divides according to the isolation way, has the relay isolation and the transistor isolation.Simulation quantity: Divides according to the signal type, has the electric current (4-20mA,0-20mA), the voltage (0-10V,0-5V, -10-10V) and so on, divides according to the precision, has 12bit,14bit,16bit and so on.Besides above general I/O, but also has the special I/O module, like module and so on thermal resistance, thermo-element, pulse.According to the I/O points determination module specification and the quantity, the I/O module may be many may be few, but its biggest number the basic disposition ability which can manage CPU, namely biggest ledger wall or rack Key slot number limit.Fifth, power source moduleThe PLC power source uses in is the PLC various modules integrated circuit provides the work power source. At the same time, some also provides 24V for the input circuit the work power source. The mains input type includes: (What the alternating current supply (220VAC or 110VAC), the direct-current power supply is commonly used is 24VAC).Sixth, PLC system other equipment1st, programs the equipment: The programming is the PLC development application, the monitor movement, the inspection maintains the essential component, uses in toprogram, makes some hypotheses to the system, monitors the system working condition which PLC and PLC controls, but it not directly participates in the scene control movement. Small programming PLC generally has the grasping programming, at present generally (movement programming software) acts as the programming by the computer.2nd, man-machine contact surface: The simplest man-machine contact surface is the indicating lamp and the button, at present the liquid crystal screen (or touches screen) a formula writing style operator terminal application to be more and more widespread, (movement configuration software) acts as the man-machine contact surface by the computer extremely to popularize.3rd, input-output device: Uses in permanently the memory user data, like EPROM, EEPROM reading in, bar code microreader, input simulation quantity potentiometer, printer and so on.PLC基础知识简介在自动化控制领域,PLC是一种重要的控制设备。

电气工程与其自动化专业_外文文献_英文文献_外文翻译_plc方面

1、外文原文A: Fundamentals of Single-chip MicrocomputerTh e si ng le -c hi p mic ro co mput er i s t he c ul mi na ti on of both t h e de ve lo pmen t o f t he d ig it al co m pu te r an d th e i n te gr at ed c i rc ui t a rg ua bl y t h e to w mos t s ig ni f ic an t i nv en ti on s of t he 20th c e nt ur y [1].Th es e t ow ty pe s of ar ch it ec tu re a re fo un d i n s in gle -ch i p m i cr oc ompu te r. So me em pl oy t he spl i t pr og ra m/da ta memory o f th e Ha rv ar d ar ch it ect ure , sh own in Fi g.3-5A-1, o th ers fo ll ow t he ph il os op hy , wi del y a da pt ed f or ge ner al -pur po se co m pu te rs a nd m i cr op ro ce ss or s, o f maki ng n o log i ca l di st in ct ion be tw ee n pr og ra m an d d at a memory a s i n t he P r in ce to n ar ch ite c tu re , sh own i n F ig.3-5A-2.In g en er al te r ms a s in gl e -chi p m ic ro co mput er i sc h ar ac te ri zed by t he i nc or po ra ti on of a ll t he un it s of a co mputer i n to a s in gl e d ev i ce , as s ho wn in Fi g3-5A-3.Fig.3-5A-1 A Harvard typeProgrammemory DatamemoryCPU Input&Outputunitmemory CPU Input&OutputunitFig.3-5A-2. A conventional Princeton computerReset Interrupts PowerFig3-5A-3. Principal features of a microcomputerRead only memory (ROM).R OM i s us ua ll y f or th e p erm an ent, no n-vo la ti le s tor age o f an a pp lic ati on s pr og ra m .Man ym i cr oc ompu te rs an d m ar e in te nd e d f or hi gh -v ol ume a ppl ic at ions an d he nc e t he eco nomic al m an uf act ure o f th e de vic es re qu ir es t h at t he co nt en t s of t he pr og ra m mem or y b e co mm it t ed pe rm ane ntly du ri ng t he m an ufa c tu re o f ch ip s .Cl ea rl y, t hi s i mpl ie s a r i go ro us a pp ro ach to R OM c od e de ve l op ment s in ce ch ang es c an not be mad e af te r manu f ac tu re .Th is d ev elo pmen t pr oc ess ma y in vo lv e emul at io n us in g a so ph is ti ca te d d eve lo pmen t sy ste m w it h a ha rd ware e mula tio n c ap ab il it y as wel l as t he u se o f po werf ul s o ft ware t oo ls.Some m an uf act ure rs p ro vi de ad d it io na l ROM opt i on s byi n cl ud in g i n th eir r ange d ev ic es wi t h (or i nt en de d f or u se wit h)us er p ro gr ammable memory. Th e sim ple st o f th es e i s u su al lyde vi ce w hi ch c an o per at e in a mi cro pro ce ss or mod e b y u si ng s ome of t he i np ut /o utp ut li ne s as a n a ddr es s an d da ta b us f or ac ce ss in g ex te rna l m emor y. T hi s t y pe o f de vi ce ca n b eh av eExternalTimingcomponents System clock Timer/ CounterSerial I/OPrarallelI/ORAMROMCPUf u nc ti on al ly a s t he si ng le ch ip mi cr oc ompu te r fro m w hi ch it is de ri ve d al be it wi t h re st ri ct ed I/O a nd a m od if ied ex te rn alc i rc ui t. Th e u se o f th es e dev ic es i s c ommon e ve n i n pr od uc ti on c i rc ui ts wh ere t he vo lu me do es no t j us tif y t h e dev el opmen t costsof c us to m o n-ch i p ROM[2];t he re c a n s ti ll be a s ig nif i ca nt sa vingi n I/O an d o th er c hip s c ompa re d t o a co nv en ti on al mi c ro pr oc es sor ba se d ci rc ui t. Mo r e ex ac t re pl ace m en t fo r RO M dev i ce s ca n be ob ta in ed i n th e f orm o f va ri an ts wit h 'p ig gy-b ack'EPRO M(Er as ab le pr o gr ammabl e RO M )s oc ke ts o r d ev ic e s wi th EP ROM i n st ea d of ROM 。

数控专业外文翻译--PLC和组态软件