orcad原理图中常见DRC错误的取缔方法

OrCADCIS使用ICA出错的解决办法

OrCADCIS使用ICA出错的解决办法OrCAD CIS使用ICA出错的解决办法OrCAD CIS使用ICA可以在线查找众多厂商的元器件和相关的原理图,这样可以大大较少我们画原理图封装库的时间,例如NXP的LPC2131这些多引脚的封装,画起来是相当的耗时间。

有了ICA的服务就相对简单多了,只要在线输入LPC2131就可查找出来它的器件的信息,包括原理图的封装和Datasheet的链接。

ICA功能的使用方法:首先进入原理图的编辑界面,然后右击鼠标,出现“place database part”,然后会打开一个“CIS Explorer”窗口,在状态栏下面会有“Local part database”的选项卡,旁边会有“Internet Components Assistance”的选项卡,选择这个选项卡,就可以切换到ICA的功能了。

如果没有显示这个选项卡,请按照我文章中的方法注册相关的dll文件即可。

但当我在OrCAD中使用ICA的时候,弹出如下提示:“ICA Warning Dialog.Class in orpiica.dll Not Registered Internet Component”.经过搜索,找到了官方的解答,英文原文如下:其实关键的问题就是把以下这几个dll文件注册就行了:· "C:\Program Files\Common Files\Orcad\CIS\orpiica.dll"· "C:\Program Files\Common Files\Orcad\CIS\genlibcom.dll"· "C:\Program Files\Common Files\Orcad\CIS\apconctl.dll"· "C:\Program Files\Common Files\Microsoft shared\DAO\dao350.dll"只要找到这几个文件,然后右击---“Register dll”就行了。

orcad使用中常见问题

1、什么时FANOUT布线?FANOUT布线:延伸焊盘式布线。

为了保证SMD器件的贴装质量,一般遵循在SMD焊盘上不打孔的原则,因此用fanout布线,从SMD器件的焊盘向外延伸一小段布线,再放置VIA,起到在焊盘上打孔的作用。

在LAYOUT PLUS 中,用AUTO/Fanout/Board,实现fanout布线。

先要设置好FANOUT的参数。

在自动布线前要对PCB上各SMD器件先FANOUT布线。

2、现在顶层图上有四个模块,选中任一模块后,按右键选Descend Hierarchy 后可进入子图,现在子图已画好,如何在顶层中自动生成PORT?而不用自己一个一个往上加PORT?(子图中已给一些管脚放置了PORT)阶层式电路图的模块PIN脚要自己放置。

选中模块后用place pin快捷菜单。

自动应该不可能。

3、只是想把板框不带任何一层,单独输出gerber文件.该咋整?发现在layout 自带的模板中,有一些关于板框和尺寸的定义,都是在notes层。

所以你也可以在设定板框时,尝试单独将obstacle type 设定为board outline,将obstacle layer设定为 notes,当然要在layers对话框里添加上notes层,再单独输出notes层gerber文件4、层次原理图,选中,右键,Descend Hierarchy,出现错误:Unable to descend part.?建议重新设置层级、重新设置属性后就可以了5、层次原理图是什么概念呢?阶层电路就是将经常要用到的原理图(如半加器)作为一个模块,不仅可以使设计版图简洁,而且便于其他设计引用6、有关ORCAD产生DEVICE的问题用ORCAD出DEVICE文件时,它只默认原理图上所显示的元件的PIN连接来出,悬空的PIN在DEVICE里的PINCOUNT没有统计进去,而且确定不了元件PIN 的数量(由于悬空没有显示)这样的话,做封装的时候很容易做错,如果没有DATA SHEET的话。

Allegro中常见的DRC错误代码解析

Hold to Orthogonal Wire Spacing

钻孔与垂直/水平线之间的距离太近

IM

Impedance Constraint

走线的阻抗值错误

JN

T Junction Not Allowed

走线呈T形的错误

KB

RouteKeepintoBondpad

Bondpad在Keepin之外

Through ViatoThrough Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

无

Min Length Wire End Segment at 135Degree

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

HH

Hold to Hold Spacing

钻孔之间的距离太近

HW

Diagonal Wire to Hold Spacing

BBVia与Test元件脚太近

BBViato Through Pin Spacing

BBVia与Through元件脚太近

SMD Pin to Test Via Spacing

SMD Pin与Test Via太近

SMDPin toThrough Via Spacing

SMD Pin与Through Via太近

orcad原理图中常见DRC错误的取缔方法

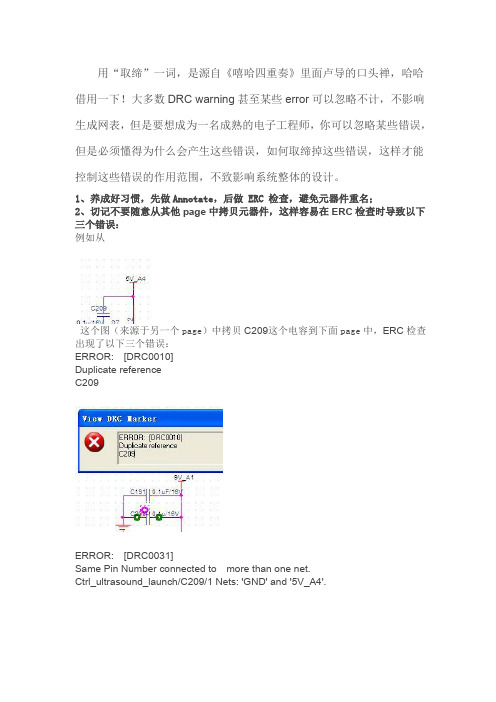

用“取缔”一词,是源自《嘻哈四重奏》里面卢导的口头禅,哈哈借用一下!大多数DRC warning甚至某些error可以忽略不计,不影响生成网表,但是要想成为一名成熟的电子工程师,你可以忽略某些错误,但是必须懂得为什么会产生这些错误,如何取缔掉这些错误,这样才能控制这些错误的作用范围,不致影响系统整体的设计。

1、养成好习惯,先做Annotate,后做 ERC 检查,避免元器件重名;2、切记不要随意从其他page中拷贝元器件,这样容易在ERC检查时导致以下三个错误:例如从这个图(来源于另一个page)中拷贝C209这个电容到下面page中,ERC检查出现了以下三个错误:ERROR: [DRC0010]Duplicate referenceC209ERROR: [DRC0031]Same Pin Number connected to more than one net.Ctrl_ultrasound_launch/C209/1 Nets: 'GND' and '5V_A4'.ERROR: [DRC0031]Same Pin Number connected to more than one net.Ctrl_ultrasound_launch/C209/2 Nets: '9V_A1' and 'GND'.解决方法:先做annotate,所有元器件重新编号,再做ERC检查,这样避免不同页面元器件重名而导致网络连接在一起,可以直接解决以上3个错误!WARNING:[DRC0003]Port has a type which is inconsistent with other ports on the net TMCL 解决方法:Net TMCL两端的端口类型冲突,修改一下type就好了!ERROR: [DRC0004]Possible pin type conflictU5,Vout Output Connected to Power解决方法:把芯片的pintype由output换成passiveWARNING:[DRC0004]Possible pin type conflict E2,1 Bidirectional Connected to Output: BENCH, C (0.40, 10.10)解决方法:These errors are produced based on the settings in the ERC matrix. If you've finished your design and you think that the connections are correct after you've checked all these errors, you can change the settings in the ERC matrix to remove them from the Design Rules Check.To change the ERC matrix:1.Select the schematic page in the Project Manager.2.Choose Design Rules Check from the Tools menu, then selectthe ERC matrix tab.3.Make changes to the matrix, then click OK. When you click OK,Design Rules Check will run with the new settings.简单来说就是修改ERC matrix,来控制ERC检查,这样就提高了容错能力,更容易通过,但前提是对自己的设计要有把握,确保正确。

对OrCAD一问题的解决

可见,元件数据有FFF3H×2=1FFE6H字节,离最大容量128K仅差1AH字节(任何一个无限 的数据都超出此值);字符数据块占有3ACGH字节;边框数据和走线数据分别有51H×8=288H、1EFB×8=F7D8H字节。

从库文件字节数我们得知最后添加的元件(是一电阻)的数据量为96H字节。这样,我们就有了解救的办法:用DEBUG将文件调入内存,计算字符数据块起始位置,用M命令(MOVE)将其后的所有文件数据向前搬移96H字节,覆盖掉最后添加的那个电阻的数据,再把寄存器BX:CX 减去96H得文件新长度,最后将文件写回磁盘。这个修改后的文件果然能被PCB程序调出,除了那个去掉的电阻外,其它内容完好无损,真可谓起死回生了!

11C2:0110 00 00 00 00 00 00 00 00-00 00 00 00 00 00 00 F3 FF……

11C2:0120 CC 3A 51 00 FB 1E 00 00-00 00 00 00 20 20 20 20 :Q……

11C2:0130 41 33 45 34 30 31 41 31-AA 02 01 00 17 0D B1 15 A3E401A1……

对OrCAD一问题的解决

殷忠军

1992-10-16

在设计过程中,为了方便,曾在板图区域外放置了许多常用的自建元件模型,如电阻、电容、二极管、跨接线等多种规格不同朝向的共八十多个。这些可以随时方便地拷贝到所需位置,但也占据了不少内存空间和文件容量。当设计按近尾声时,程序的元件缓冲区(最大分配128K)已所剩无几。由于未认识到严重性,没及时删掉那些不再使用的自建模型,终于在某次添加元件后,得到提示:“元件缓冲区已满!”同时程序发生混乱,不能正常设计了,当即放弃存盘退出,欲重新运行PCB程序删除上述那些多余元件,即发现板图工作文件和两个后备文件都已无法调出(一调便死机)。

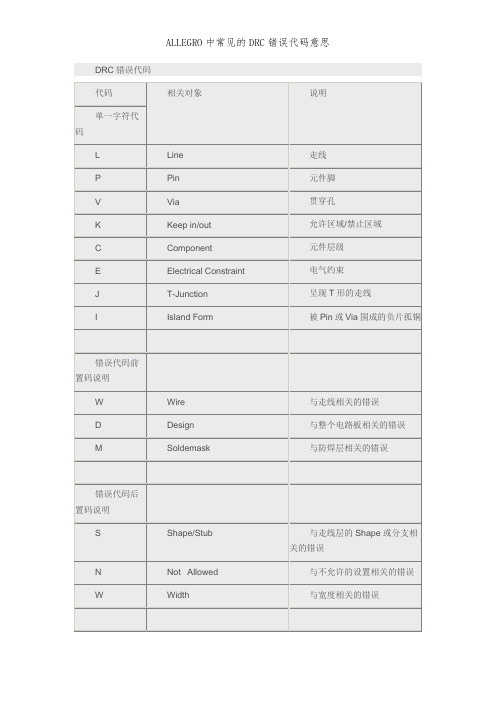

ALLEGRO中常见的DRC错误代码意思

KL

Line to RouteKeepinSpacing

走线在RouteKeepin之外

Line to RouteKeepoutSpacing

走线在RouteKeepout之内

KS

Shape to RouteKeepinSpacing

Shape在RouteKeepin之外

Test Via在ViaKeepout之内

Through Via to RouteKeepinSpacing

Through Via在RouteKeepin之外

Through Via to RouteKeepoutSpacing

Through Via在RouteKeepout之内

Through Via to ViaKeepoutSpacing

DRC错误代码

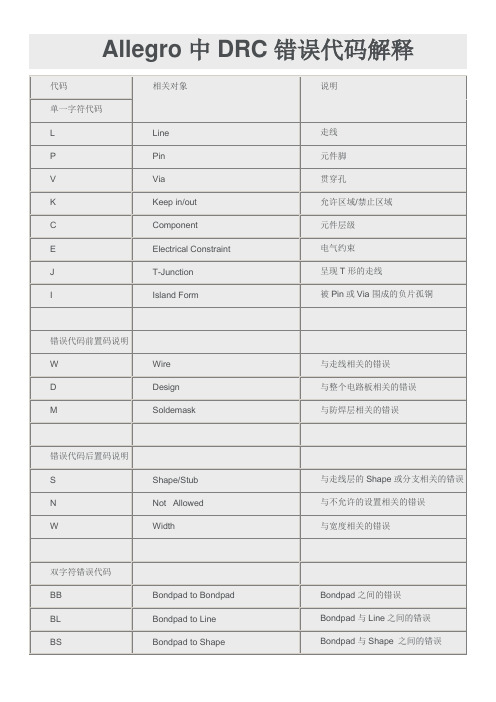

代码

相关对象

说明

单一字符代码

L

Line

走线

P

Pin

元件脚

V

Via

贯穿孔

K

Keep in/out

允许区域/禁止区域

C

Component

元件层级

E

Electrical Constraint

电气约束

J

T-Junction

呈现T形的走线

I

Island Form

被Pin或Via围成的负片孤铜

错误代码前置码说明

Through ViatoThrough Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

PADS、PCB原理图常见错误及DRC报告网络问题(精选)

PADS、PCB原理图常见错误及DRC报告网络问题(精选)第一篇:PADS、PCB原理图常见错误及DRC报告网络问题(精选)PADS/PCB/原理图常见错误及DRC报告网络问题1.原理图常见错误:(1)ERC报告管脚没有接入信号:a.创建封装时给管脚定义了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c.创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.2.PCB中常见错误:(1)网络载入时报告NODE没有找到:a.原理图中的元件使用了pcb库中没有的封装;b.原理图中的元件使用了pcb库中名称不一致的封装;c.原理图中的元件使用了pcb库中pin number不一致的封装。

如三极管:sch中pin number 为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:a.创建pcb库时没有在原点;b.多次移动和旋转了元件,pcb板界外有隐藏的字符。

选择显示所有隐藏的字符,缩小pcb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部分:表示这个网络没有连通,看报告文件,使用选择CONNECTED COPPER查找。

另外提醒朋友尽量使用WIN2000, 减少蓝屏的机会;多几次导出文件,做成新的DDB文件,减少文件尺寸和PROTEL僵死的机会。

如果作较复杂得设计,尽量不要使用自动布线。

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。

PCB布线有单面布线、双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。

orcad16.6 DRC报错问题

Duplicate Pin Name "GND" found on Package

重复引脚编号

Checking Pins and Pin Connections

ERROR: [DRC0031] Same Pin Number connected to more than one net. LED&Switch&7-Segment Disp/U17/3 Nets: '3V3' and '485_RE/DE'.

无法根治

这个#2 Warning [ALG0016] Part Name "?j#w?rm

之类的错误在于你建立元件原理图的时候你的原件Value值太长了超过32个字符,从而使系统在进行命名规范的时候溢出,而出错,很简单的,只写关键元件名,比如 A2541P10_HDR2X5-100MIL_2X5 HEADER" is renamed to "A2541P10_HDR2X5-100MIL_2X5 HEAD错误只需要

(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决

(8)

#60 Warning [ALG0016] Part Name "COM_17×2_SIP17X2_COM_17×2" is renamed to "COM_172_SIP17X2_COM_172".

Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08)

ORCAD使用中常见问题汇集及答案 (全)

ORCAD使用中常见问题汇集及答案(全)ORCAD使用中常见问题汇集及答案1、什么时FANOUT布线?FANOUT布线:延伸焊盘式布线。

为了保证SMD器件的贴装质量,一般遵循在SMD焊盘上不打孔的原则,因此用fanout布线,从SMD器件的焊盘向外延伸一小段布线,再放置VIA,起到在焊盘上打孔的作用。

在LAYOUT PLUS 中,用AUTO/Fanout/Board,实现fanout布线。

先要设置好FANOUT的参数。

在自动布线前要对PCB上各SMD器件先FANOUT布线。

2、现在顶层图上有四个模块,选中任一模块后,按右键选Descend Hierarchy后可进入子图,现在子图已画好,如何在顶层中自动生成PORT?而不用自己一个一个往上加PORT?(子图中已给一些管脚放置了PORT)阶层式电路图的模块PIN脚要自己放置。

选中模块后用place pin快捷菜单。

自动应该不可能。

3、只是想把板框不带任何一层,单独输出gerber文件.该咋整?发现在layout 自带的模板中,有一些关于板框和尺寸的定义,都是在notes层。

所以你也可以在设定板框时,尝试单独将obstacle type 设定为board outline,将obstacle layer设定为notes,当然要在layers对话框里添加上notes层,再单独输出notes层gerber文件4、层次原理图,选中,右键,Descend Hierarchy,出现错误:Unable to descend part.?建议重新设置层级、重新设置属性后就可以了5、层次原理图是什么概念呢?阶层电路就是将经常要用到的原理图(如半加器)作为一个模块,不仅可以使设计版图简洁,而且便于其他设计引用6、有关ORCAD产生DEVICE的问题用ORCAD出DEVICE文件时,它只默认原理图上所显示的元件的PIN连接来出,悬空的PIN 在DEVICE里的PINCOUNT没有统计进去,而且确定不了元件PIN 的数量(由于悬空没有显示)这样的话,做封装的时候很容易做错,如果没有DATA SHEET的话。

DRC规则检查常见错误

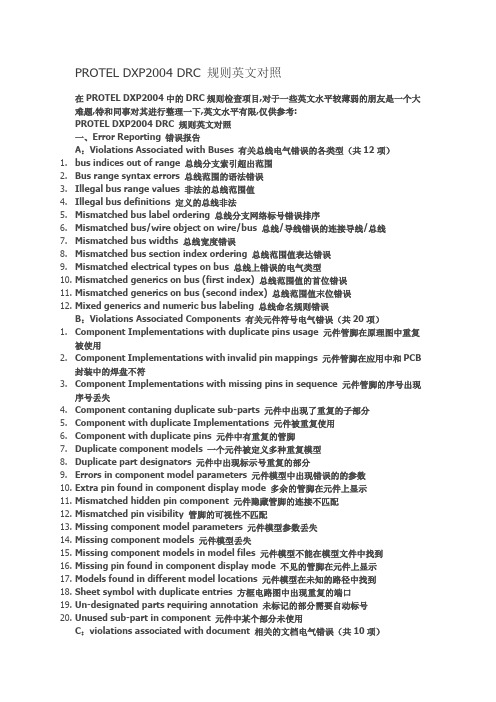

PROTEL DXP2004 DRC 规则英文对照在PROTEL DXP2004中的DRC规则检查项目,对于一些英文水平较薄弱的朋友是一个大难题,特和同事对其进行整理一下,英文水平有限,仅供参考:PROTEL DXP2004 DRC 规则英文对照一、Error Reporting 错误报告A:Violations Associated with Buses 有关总线电气错误的各类型(共12项)1.bus indices out of range 总线分支索引超出范围2.Bus range syntax errors 总线范围的语法错误3.Illegal bus range values 非法的总线范围值4.Illegal bus definitions 定义的总线非法5.Mismatched bus label ordering 总线分支网络标号错误排序6.Mismatched bus/wire object on wire/bus 总线/导线错误的连接导线/总线7.Mismatched bus widths 总线宽度错误8.Mismatched bus section index ordering 总线范围值表达错误9.Mismatched electrical types on bus 总线上错误的电气类型10.Mismatched generics on bus (first index) 总线范围值的首位错误11.Mismatched generics on bus (second index) 总线范围值末位错误12.Mixed generics and numeric bus labeling 总线命名规则错误B:Violations Associated Components 有关元件符号电气错误(共20项)ponent Implementations with duplicate pins usage 元件管脚在原理图中重复被使用ponent Implementations with invalid pin mappings 元件管脚在应用中和PCB封装中的焊盘不符ponent Implementations with missing pins in sequence 元件管脚的序号出现序号丢失ponent contaning duplicate sub-parts 元件中出现了重复的子部分ponent with duplicate Implementations 元件被重复使用ponent with duplicate pins 元件中有重复的管脚7.Duplicate component models 一个元件被定义多种重复模型8.Duplicate part designators 元件中出现标示号重复的部分9.Errors in component model parameters 元件模型中出现错误的的参数10.Extra pin found in component display mode 多余的管脚在元件上显示11.Mismatched hidden pin component 元件隐藏管脚的连接不匹配12.Mismatched pin visibility 管脚的可视性不匹配13.Missing component model parameters 元件模型参数丢失14.Missing component models 元件模型丢失15.Missing component models in model files 元件模型不能在模型文件中找到16.Missing pin found in component display mode 不见的管脚在元件上显示17.Models found in different model locations 元件模型在未知的路径中找到18.Sheet symbol with duplicate entries 方框电路图中出现重复的端口19.Un-designated parts requiring annotation 未标记的部分需要自动标号20.Unused sub-part in component 元件中某个部分未使用C:violations associated with document 相关的文档电气错误(共10项)1.conflicting constraints 约束不一致的2.duplicate sheet symbol name 层次原理图中使用了重复的方框电路图3.duplicate sheet numbers 重复的原理图图纸序号4.missing child sheet for sheet symbol 方框图没有对应的子电路图5.missing configuration target 缺少配置对象6.missing sub-project sheet for component 元件丢失子项目7.multiple configuration targets 无效的配置对象8.multiple top-level document 无效的顶层文件9.port not linked to parent sheet symbol 子原理图中的端口没有对应到总原理图上的端口10.sheet enter not linked to child sheet 方框电路图上的端口在对应子原理图中没有对应端口D:violations associated with nets 有关网络电气错误(共19项)1.adding hidden net to sheet 原理图中出现隐藏网络2.adding items from hidden net to net 在隐藏网络中添加对象到已有网络中3.auto-assigned ports to device pins 自动分配端口到设备引脚4.duplicate nets 原理图中出现重名的网络5.floating net labels 原理图中有悬空的网络标签6.global power-objects scope changes 全局的电源符号错误 parameters with no name 网络属性中缺少名称 parameters with no value 网络属性中缺少赋值s containing floating input pins 网络包括悬空的输入引脚s with multiple names 同一个网络被附加多个网络名s with no driving source 网络中没有驱动s with only one pin 网络只连接一个引脚s with possible connection problems 网络可能有连接上的错误14.signals with multiple drivers 重复的驱动信号15.sheets containing duplicate ports 原理图中包含重复的端口16.signals with load 信号无负载17.signals with drivers 信号无驱动18.unconnected objects in net 网络中的元件出现未连接对象19.unconnected wires 原理图中有没连接的导线E:Violations associated with others有关原理图的各种类型的错误(3项)1.No Error 无错误2.Object not completely within sheet boundaries 原理图中的对象超出了图纸边框3.Off-grid object原理图中的对象不在格点位置F:Violations associated with parameters 有关参数错误的各种类型1.same parameter containing different types 相同的参数出现在不同的模型中2.same parameter containing different values 相同的参数出现了不同的取值二、Comparator 规则比较A:Differences associated with components 原理图和PCB上有关的不同(共16项)1.Changed channel class name 通道类名称变化2.Changed component class name 元件类名称变化3.Changed net class name 网络类名称变化4.Changed room definitions 区域定义的变化5.Changed Rule 设计规则的变化6.Channel classes with extra members 通道类出现了多余的成员ponent classes with extra members 元件类出现了多余的成员8.Difference component 元件出现不同的描述9.Different designators 元件标示的改变10.Different library references 出现不同的元件参考库11.Different types 出现不同的标准12.Different footprints 元件封装的改变13.Extra channel classes 多余的通道类14.Extra component classes 多余的元件类15.Extra component 多余的元件16.Extra room definitions 多余的区域定义B:Differences associated with nets 原理图和PCB上有关网络不同(共6项)1.Changed net name 网络名称出现改变2.Extra net classes 出现多余的网络类3.Extra nets 出现多余的网络4.Extra pins in nets 网络中出现多余的管脚5.Extra rules 网络中出现多余的设计规则 class with Extra members 网络中出现多余的成员C:Differences associated with parameters 原理图和PCB上有关的参数不同(共3项)1.Changed parameter types 改变参数类型2.Changed parameter value 改变参数的取值3.Object with extra parameter 对象出现多余的参数【Violations Associated with Buses】栏——总线电气错误类型(1)【Bus indices out of range】:总线分支索引超出范围。

orCAD_PADS学习笔记[1]

![orCAD_PADS学习笔记[1]](https://img.taocdn.com/s3/m/678286f7aef8941ea76e0597.png)

orCAD_PADS学习笔记--林旭OrCAD篇如何在orCAD中批量修改元器件属性?1.选择项目文件(*.dsn),点击Tools\Export Properties。

2.设置参数。

Scope:Export entire design or Library(导出全部项目或库文件)。

Contents:part Properties(器件属性)。

Mode:Export Instance Properties(使用当前属性)。

3.进入存放路径,右击导出的*.exp文件,选择用Excel打开。

4.修改表中需要修改的参数,保存并选择“是”。

5.回到原理图环境下面,点击Tools\Import Properties,导入刚保存的Excel文件,完毕。

注意:修改时不能修改或删除属性文件的第一行和每一行的第一项和第二项。

orCAD如何生成BOM表?1.选择项目文件(*.dsn),点击Tools\Bill of Materials。

2.设置参数。

Scope:Export entire design or Library(导出全部项目或库文件)。

Contents:part Properties(器件属性)。

Mode:Export Instance(Properties)(使用当前属性)。

3.Line Item Definition中:(以下为我常用的)Header:项目\t属性\t封装\t数量\t元器件编号\tCombined property string:{Item}\t{Value}\t{pcb footprint}\t{Quantity}\t{Reference}\t4.选中Open in Excel。

5.点OK就可以了。

为什么orCAD中无法输出网表?1.DRC检查时问题特征为:ERROR [NET0021] Cannot get part.[FMT0024] Ref-des not found. Possible Logical/Physical annotation conflict.[FMT0018] Errors processing intermediate file.2.问题的原因是因为使用了orCAD中的Pspice器件库。

DRC错误及纠错,找不到DRC错误的Net

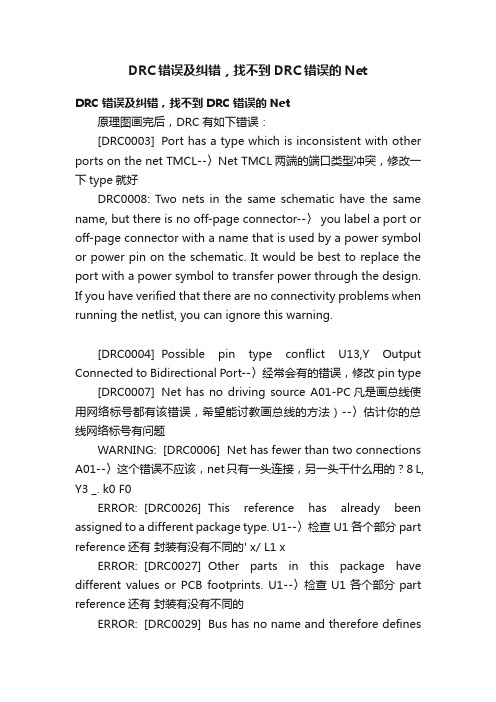

DRC错误及纠错,找不到DRC错误的NetDRC错误及纠错,找不到DRC错误的Net原理图画完后,DRC有如下错误:[DRC0003] Port has a type which is inconsistent with other ports on the net TMCL--〉Net TMCL两端的端口类型冲突,修改一下type就好DRC0008: Two nets in the same schematic have the same name, but there is no off-page connector--〉 you label a port or off-page connector with a name that is used by a power symbol or power pin on the schematic. It would be best to replace the port with a power symbol to transfer power through the design. If you have verified that there are no connectivity problems when running the netlist, you can ignore this warning.[DRC0004] Possible pin type conflict U13,Y Output Connected to Bidirectional Port--〉经常会有的错误,修改pin type [DRC0007] Net has no driving source A01-PC凡是画总线使用网络标号都有该错误,希望能讨教画总线的方法)--〉估计你的总线网络标号有问题WARNING: [DRC0006] Net has fewer than two connections A01--〉这个错误不应该,net只有一头连接,另一头干什么用的?8 L, Y3 _. k0 F0ERROR: [DRC0026] This reference has already been assigned to a different package type. U1--〉检查U1各个部分part reference还有封装有没有不同的' x/ L1 xERROR: [DRC0027] Other parts in this package have different values or PCB footprints. U1--〉检查U1各个部分part reference还有封装有没有不同的ERROR: [DRC0029] Bus has no name and therefore definesno signals. N08158--〉同样是BUS 的命名有问题,找周润景的书看一下,虽然那书不怎么样,不过Orcad讲的还算可以5如果在原理图中Ctrl+F找不到出现DRC错误的Net,或出现DRC 错误的Net的坐标超出图纸范围,则应把原理图的Page Size放大,有可能是因为当初画图时某些器件忘记删掉就直接调整图纸大小了。

orcad使用中常见问题

1、什么时FANOUT布线?FANOUT布线:延伸焊盘式布线。

为了保证SMD器件的贴装质量,一般遵循在SMD焊盘上不打孔的原则,因此用fanout布线,从SMD器件的焊盘向外延伸一小段布线,再放置VIA,起到在焊盘上打孔的作用。

在LAYOUT PLUS 中,用AUTO/Fanout/Board,实现fanout布线。

先要设置好FANOUT的参数。

在自动布线前要对PCB上各SMD器件先FANOUT布线。

2、现在顶层图上有四个模块,选中任一模块后,按右键选Descend Hierarchy 后可进入子图,现在子图已画好,如何在顶层中自动生成PORT?而不用自己一个一个往上加PORT?(子图中已给一些管脚放置了PORT)阶层式电路图的模块PIN脚要自己放置。

选中模块后用place pin快捷菜单。

自动应该不可能。

3、只是想把板框不带任何一层,单独输出gerber文件.该咋整?发现在layout 自带的模板中,有一些关于板框和尺寸的定义,都是在notes层。

所以你也可以在设定板框时,尝试单独将obstacle type 设定为board outline,将obstacle layer设定为 notes,当然要在layers对话框里添加上notes层,再单独输出notes层gerber文件4、层次原理图,选中,右键,Descend Hierarchy,出现错误:Unable to descend part.?建议重新设置层级、重新设置属性后就可以了5、层次原理图是什么概念呢?阶层电路就是将经常要用到的原理图(如半加器)作为一个模块,不仅可以使设计版图简洁,而且便于其他设计引用6、有关ORCAD产生DEVICE的问题用ORCAD出DEVICE文件时,它只默认原理图上所显示的元件的PIN连接来出,悬空的PIN在DEVICE里的PINCOUNT没有统计进去,而且确定不了元件PIN 的数量(由于悬空没有显示)这样的话,做封装的时候很容易做错,如果没有DATA SHEET的话。

ALLEGRO中常见的DRC错误代码意思

Shape to Test Via Spacing

Shape与Test Via太近

Shape to Through Via Spacing

Shape与Through Via太近

VV

BB Via to BB Via Spacing

BB Via之间太近

BB Via to Test Via Spacing

Test Pin to Test Pin Spacing

Test元件脚与ቤተ መጻሕፍቲ ባይዱest元件脚太近

Test Pin to Through Pin Spacing

Test元件脚与Through元件脚太近

Through Pin to SMD Pin Spacing

Through元件脚与SMD元件脚太近

Through Pin to Through Pin Spacing

BBVia to Via Keepout Spacing

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

DF

Differential Pair Length Tolerance

差分对走线的长度误差过长

Differential Pair Primary Max Separation

差分对走线的主要距离太大

Differential Pair Secondary Max Separation

差分对走线的次要距离太大

无

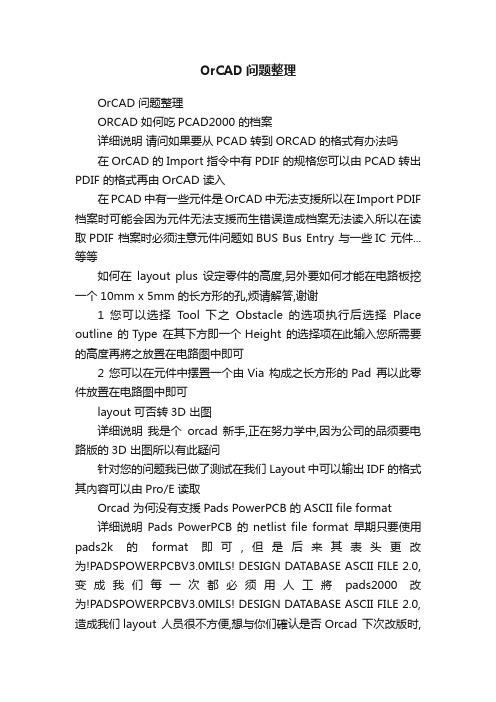

OrCAD问题整理

OrCAD问题整理OrCAD 问题整理ORCAD 如何吃PCAD2000 的档案详细说明请问如果要从PCAD 转到ORCAD 的格式有办法吗在OrCAD 的Import 指令中有PDIF 的规格您可以由PCAD 转出PDIF 的格式再由OrCAD 读入在PCAD 中有一些元件是OrCAD 中无法支援所以在Import PDIF 档案时可能会因为元件无法支援而生错误造成档案无法读入所以在读取PDIF 档案时必须注意元件问题如BUS Bus Entry 与一些IC 元件...等等如何在layout plus 设定零件的高度,另外要如何才能在电路板挖一个10mm x 5mm 的长方形的孔,烦请解答,谢谢1 您可以选择Tool 下之Obstacle 的选项执行后选择Place outline 的Type 在其下方即一个Height 的选择项在此输入您所需要的高度再將之放置在电路图中即可2 您可以在元件中摆置一个由Via 构成之长方形的Pad 再以此零件放置在电路图中即可layout 可否转3D 出图详细说明我是个orcad 新手,正在努力学中,因为公司的品须要电路版的3D 出图所以有此疑问针对您的问题我已做了测试在我们Layout 中可以输出IDF 的格式其內容可以由Pro/E 读取Orcad 为何没有支援Pads PowerPCB 的ASCII file format详细说明Pads PowerPCB 的netlist file format 早期只要使用pads2k 的format 即可,但是后来其表头更改为!PADSPOWERPCBV3.0MILS! DESIGN DATABASE ASCII FILE 2.0,变成我们每一次都必须用人工將pads2000 改为!PADSPOWERPCBV3.0MILS! DESIGN DATABASE ASCII FILE 2.0,造成我们layout 人员很不方便,想与你们確认是否Orcad 下次改版时,会加入Pads PowerPCB 专用的netlist format?对於您的问题,在原厂的下载区有符合POWERPCB 的格式,其档案为Padpwr1.zip 的压缩档,其输出的Netlist 表头为!PADSPOWERPCBV2.0MILS! DESIGN DATABASE ASCII FILE 1.0,您可以参考是否有误请问如何import verilog file to orcad由於OrCAD Capture 並没有Import Verilog 的格式,所以无法读取Verilog 的档案,必须由Verilog 输出OrCAD Capture 可以读取的格式再由OrCAD Capture 读取档案即可標题 pspice9.0 如何更改元件参数详细说明 pspice9.0 的元件从library 叫出后..选edit properties 找不到参数的设定例如叫出某个型號的FET想设定其IS , Cd ,Cs 等等..请问如何找到其参数与修改?若因为它是特定型號不能修改则可以叫出一个电晶体的model 自设参数?在Orcad 9.0 中,更改一个电晶体的元件参数的Step 如下述:Step1: 在Capture 里,叫出其符號.Step2: 选欲更改的符號后, 选在Orcad Capture Windows 里的Edit/Pspice Model 选项.Step3: Orcad Model Editor Windows 出后,您就可以更改元件参数.请问orcad 4.的线路图如何给orcad 7.读Capture 如何开启 DOS 版本的 SDT V3 / V4 及 SDT 386+ 之图档详细说明 OrCAD Capture 如何开启 DOS 版本的 SDT V3 / V4 及SDT 386+ 之图档下列两项条件必须具备你必须有 DOS 版的线路图档(.SCH)以及该图档所有使用到的零件库档案(.lib)最好零件库档是单一的专属零件库(这可以使用DOS 所提供的Libarch.exe 档对该图档去製作出来) 如果不是单一的零件库档案也是可以的只是较为麻烦你最好在该部电脑安装有 DOS 版的OrCAD SDT之程式如果没有则您必须进行下列的境设定境设定请在你的 Autoexec.bat 档內加入一行设定范例如下@ECHO OFFPROMPT $P$GPATHC:WINDOWS;C:WINDOWSCOMMAND;C:;C:DOS;C:ORCADWIN SET ORCADPROJ=C:ORCAD 加入此行设定SET TEMP=C:TEMPLH MOUSELH DOSKEY请从原来装有OrCAD SDT 程式的电脑寻找一个SDT.CFG 档(该档案一般是放在ORCADTEMPLATES 目录下如果您找不到此档案亦可从OrCAD 的网站(/doc/e37319276.html,)上去取得该档案然后使用文书编辑软体去开启该档案並將此档案修改如下{OrCAD/SDT IV Configuration File }PDRV = C:ORCADPSCH =PLIB = C:ORCAD.LIB 將 LIB 的路径设为ORCAD 之目录DD = VGA640.DRVPRD =PLD =LIB = 'MYPROJ.LIB 输入您的零件库档名有几个就加入几行LIB = DEVICE.LIBDMF =DIM =LMF =假设你的图档与零件库档名分別为MYPROJ.SCH 与MYPROJ.LIB 则请在C 磁碟建立一个ORCAD 目录並且把图档MYPROJ.SCH 与零件库档MYPROJ.LIB 复製到此目录下然后也將上述已修改好的SDT.CFG 档复到此目录下將ORCADWINCAPTURE 路径下的Capture.ini档內容修改如下范例Part Selector Configured Libraries]Number of Configured Libraries=2Library0=C:ORCADWINCAPTURELIBRARYANALOG.OLBLibrary1=C:ORCADWINCAPTURELIBRARYDEVICE.OLB[Part Selector Configured Libraries]Number of Configured Libraries=0开启进行档案转换避免程式在转换时先去抓取原来Capture 所加入选用之零件库进入OrCAD Capture 程式內然后在功能表选择Open Design在Open Design 的对话框內切换档案类型为SDT Schematic(.sch) 然后进入OrCAD 目录去开启MYPROJ.SCH 图档並將它转存为DSN 档(OrCAD Capture 档案格式)即可標题请问如何设计和建立自己的焊&详细说明在PCB 零件中的焊如何设计並建立自己的焊库.在PCB 中的焊(Pad)是一?物件所以不管是单?的Pad 与元件的Pad 皆为同一设定您在library 中选择您要??之Pad 再按下Shift 与T 键即会切换至Pad 的设定?窗下您再依据您所需要的设?来作?更即可(元件也是相同做法)標题请问PSpicead 的问题?详细说明我的问题为我每次模擬时,PSpicead 中的Display 都为"Fast",是否可以设定那里?可以每次模擬,PSpicead 中Display 为"immediate",这样模擬比较快.....在PSpiceAD window 中的Display item 里,我们利用Immediate,fast,slow 选项来决定更新PSpiceAD window 资料的速度(Immediate 最快,fast 居中)然而就模擬而言,显示资料更新的频繁,佔据程式更多的时间,而使模擬速度变慢.因此,单就模擬时间而言,我们建议您使用slow 选项若有更进一步之问题欢迎指教標题 OrCAD Capture 9.2 有关Capture Netlist 问题详细说明问题1 Capture 新版的Netlist to Allegro 功能有无更详细的说明User Guide 写的相简陋问题2 某一零件的所有Pin 都接电源就出Error这並不合理因为如CPU 一般都会分成ABCD 等部份而某部份是所有PIN 都是接POWER 和 GND这种Message 就不合理问题3 由Capture 生Netlist 且选开启进入Allegro这之间处理所花的时间远比之前用Third Party 方式超过太多(太慢) 而新版Capture 又无提供旧方式的生方式害我只能將旧版的Allegro.dll Copy 到Capture etsform 下才能用旧的方式生NetList为什新版的问题那多而且又不Friendly... Why?A1:请参考help 之netlist to allegro 其中如 assign properties in Capture for use inAllegro 即会说明例如何將VDD,VPP,VSS 绑成VCC 讯號之PROPERTIES => POWER_GROUP = VDD=VCC;VPP=VCC;VSS=VCCA2:请务必用orcad 9.2.3(allegro 14.2).即可不须同一零件中in name 须不同 orcad 9.2.2 有此限制A3:新转法的特性是除了传递NETlist 之连线关係外更能传递对零件或讯號所定之PROPERTIES如FIXED,min_line width 等宣告.会转出三个 .dat如果只要NETlist 作LAYOUT.如您所做將旧版的Allegro.dll 覆製到Capture etsform 下用create NETLIST/OTHER/Allegro 转出单一netlist. AllegroOrCAD Capture 9 23 Netlist to Allegro详细说明关於之前提过的问题同一Part 有相同PinName 会生Error如下所示(只是截取部份的错误讯息有近2 万的Errors)#7874 Error [ALG0050] Duplicate Pin Name "GND" found on Package VT8235A , U37A:main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7875 Error [ALG0050] Duplicate Pin Name "GND" found on Package VT8235A , U37A:main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7876 Error [ALG0050] Duplicate Pin Name "GND" found on Package VT8235A , U37A:main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7877 Error [ALG0050] Duplicate Pin Name "GND" found on Package VT8235A , U37A:main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7878 Error [ALG0050] Duplicate Pin Name "GND" found on Package VT8235A , U37A:main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7879 Error [ALG0050] Duplicate Pin Name "GND" found on Package VT8235A , U37A:main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7880 Error [ALG0050] Duplicate Pin Name "GND" found on Package VT8235A , U37A:main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7881 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7882 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7883 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7884 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7885 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7886 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7887 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7888 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7889 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7890 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.#7891 Error [ALG0050] Duplicate Pin Name "VCC33" found on Package VT8235A , U37A: main, 16 SOUTH BRIDGE 1 (2.40, 1.60). Please renumber one of these.这是用Cadence 14.2 內的Capture 转出的请问如何更正这些错误..... 太多了而且这种错误讯息应该是可以改成Warnning 而不应该是用Error 进而造成Create Netlist 的中断不是很合理PS: 本人对於这种Create Netlist 的方式觉得很不错只是过程中仍有一些无法理解的问题....答有Duplicate Pin Name 表示您所建的Orcad Library Part 的Pin Name 一样可能要改成不同Pin Name 才可以如加上0,1,2,3...的编號一般来说Pin name 若不同的话在建Part 时就有Warning Message 但是有些使用者就忽略这些Message, 在旧版的Capture 因为是用Third Party 方式转成Allegro Netlist 然是没有问题但在新版的Netlist to Allegto 就会出Pin Name 重覆的问题......OrCAD Capture 9 1標题 .DSN 的版本详细说明为何无法將9.1 的DSN 存为7.2 的DSN.之前都可以(用的是OrCAD Capture CLS9.1)RE在使用Capture9.1 的程式再开启电路图再执行"Save as"功能后在存档类型中即有7.2格式的选项您可以选择7.2 的格式存档即可感谢您的指教OrCAD Capture 9 02標题有问题~~详细说明 layer name 中文说明副档名Silkscreen Top 顶层文字绢印层 .SSTSilkscreen Bottom 底层文字绢印层 .SSBTop Layer 顶层零件面走线层 .TOPBottom Layer 底层銲锡面走线层 .BOTInner Layer 1,etc. 中间铜箔走线层第一层第二层等 .IN1,IN2Power Layer. 內层电源层 .PWRGround Layer. 內层接地层 .GNDSoldermask Top 顶层防銲层 .SMTSoldermask Bottom 底层防銲层 .SMBSolder Paste Top 顶层锡膏印刷钢板层 .SPTSolder Paste Bottom 底层锡膏印刷钢板层 .SPBDrill Drawing 钻孔尺寸標记层 .DRDAssembly Top 顶层资料图 .ASTAssembly Bottom 底层资料图 .ASBGlobal Layer 禁入(置)层请问上述的那些档案用.max 档转换的步骤为何??在ORCAD Layout 中,是否有副档名为 .drd 的档案如果有,该如何叫出来??谢谢!!RE转出GerberFile 步骤如下1.执行Options 下Post Process Settings 功能2.再按滑鼠右键选择Run Batch 选项即可3.与".max"同一个档案夹中即会出所有的Gerber 档案有副档名为DRD Drill Drawing 钻孔尺寸標记层 .DRD 您转出GerberFiles 即会有谢谢您的指教OrCAD Pspice 9.02標题请问一下layout 输出副档名详细说明请问一下...零件面,銲锡面,钻孔档,成型档layout 输出的副档名各是什??RE:您好:您所需要的资料如下:layer name 中文说明副档名Silkscreen Top 顶层文字绢印层 .SSTSilkscreen Bottom 底层文字绢印层 .SSBTop Layer 顶层零件面走线层 .TOPBottom Layer 底层銲锡面走线层 .BOTInner Layer 1,etc. 中间铜箔走线层第一层第二层等 .IN1,IN2Power Layer. 內层电源层 .PWRGround Layer. 內层接地层 .GNDSoldermask Top 顶层防銲层 .SMTSoldermask Bottom 底层防銲层 .SMBSolder Paste Top 顶层锡膏印刷钢板层 .SPTSolder Paste Bottom 底层锡膏印刷钢板层 .SPBDrill Drawing 钻孔尺寸標记层 .DRDAssembly Top 顶层资料图 .ASTAssembly Bottom 底层资料图 .ASBGlobal Layer 禁入(置)层OrCAD Capture CIS 9.0標题为什V:9.0 和V9.1 的Logic IC 操作方式不同详细说明 V9.0 的Logic IC 使用复合包装零件(U?A,U?B..)在置放於电路图时会自动增加Part numbering(ex:U1A 在置放后,置放下一个则编號增为U1B),但V9.1 確增加零件编號(ex:U1A 置放后,下一个编號增为U2A),请问是设定问题还是版本问题.如果要V9.1 使用V9.0 的方式可以吗??RE:关於您的问题,在这两个版本並无不同在复合式的零件里,做重覆放置的动作,其Part Numbering 都会自动递增(EX:U1A U2A......)因此您所发的问题,应该是不会发生才是.如有进一步的问题,欢迎指教......DSN 的版本详细说明请问如何看的出来DSN 的版本?!RE:您好:您可以UltraEdit 或一些可能看档案ASCII 的文书编辑软体,从ASCII 里就会有敘述那个DSN是那个版本所建立.如有进一步的问题,欢迎指教......hofc@/doc/e37319276.html,OrCAD Capture 9.0请问电路图是否可以转换成PowerPCB 的档案(.pcb 档)详细说明OrCAD Capture CIS 中的电路图是否可以转换成PowerPCB 的档案(.pcb 档)RE:如果您要由OrCAD Capture 的电路转Netlist file 到Power PCB 请再执行Create Netlist 功能后选择Other 选项的Pads2k.dll 再將.NET 更改为.ASC 即可由Power PCB 中载入Netlist至於载入方式请询问Power PCB 的代理厂商如此才会得到最正確的做法OrCAD Capture 9.0標题绘图档可否转为pdf 档详细说明绘图档可否转为pdf 档,how to doRE:您好:关於您所提出的问题,这是Acrobat Write 才有的功能,而此功能是要付费的.您可以到下面所列的网页上,穫得到更详细的说明:/doc/e37319276.html,/products/acrobat/re adstep.htmlOrCAD Capture CIS 9.0自建零件修改后如何同步使用於电路图详细说明建完零件后,用於电路图上,但如果要修改自建零件,修正完后,电路图上却无法自动更新成零件库所修正的零件,请问要如何设定才能同步更新呢或有其他的方式.Thanks.RE:您好:关於您的问题,您可以用Update Cache 的动作將电路图上的零件Update 成跟Library 一样.其做法如下:1.到Project Manager 视窗,並將Design Cache 展开2. 选该元件(会Highlight 起来)3.將滑鼠移到上Mean Bar 找Design >Update Cache 即可.OrCAD Layout 9.0標题 Gerber file merge详细说明 Sir,我想將不同的max file 放在同一个 gerber file 上 (2 种不同的pcb 放在同一个 panel, 我试过用 merge 这个命令, 但出来的结果是令一块板所有的pad size 同 drill size 都变了,我是否做错了??ThanksMingRE:一般併版的用途是用在於將相同的PCB 档案作复製使用在PCB 已製作完成要输出Gerber file 前所以您的做法用在这里不太恰在我们的操作中Pad 的资料並没有不同所以不知您出的错误为何版本 9.0问题类別 OrCAD Layout標题 How to convert format from .max to .pcb详细说明 Sir,有没有方法可由.max file (orcad layout) 转到pcb file (powerPCB) ?我试过由max 转 gerber, 再由gerber 转pcb, 但是pcb file 就不可再做更改,这只是表面...谢谢RE:您可以在进入Layout 后直接使用File 下的Export 指令在此指令中选择您所要的格式您可以选择power PCB 的前一个版本PADs 的格式再由power PCB 中匯入即可由於power PCB 不属於Cadence 的软体在此无法为您解答所以在power PCB 中如何匯入与修改请询问power PCB 的厂商感谢您的询问版本 9.0问题类別 OrCAD Layout標题请教各位前辈,如何设定盲孔和埋孔?详细说明请教各位前辈:盲孔和埋孔要在那个功能中设定?请指..感激不尽.RE:您可以进入padstacks 中將不需要的层別关闭(Pad Width 与Pad Height 修改为0)即可例如:六层版中的埋孔设定您可以进入Padstacks 中针对所需修改的Pad 关闭不使用的层別(如Top,Inner1,Inner4,Bottom)四层资料如此即成为只有Inner2 与Inner3 的埋孔了同理可以设定Inner2,Inner3,Inner4,Bottom 关闭如此即设定为半埋孔了感谢您的指教版本 13.6问题类別 Cadence Allegro Studio標题为何无法將NET 档载入详细说明请问:我在allegro 中的File>Import>Logic 输入NET 档却无法载入我该使用何种方法载入ORCAD 的档案做Layout请確认在Orcad 中是用Create Netlist/others/Allegro 来生Netlist File在Allegro 中是用File/import/logic/Third Party 模式来载入否则Netlist 只是交待零件外型及连线关係至Layout tool 中,格式对了只差两边是否对应的问题请依其错误讯息与您的支援厂商查核版本 9.1问题类別 OrCAD Capture標题请教我如何在pspice9.1 下设kp 值??详细说明上次我写的不够清楚~这次我说清楚一我不会irf150 的kp 值~题目要我用参数扫描的方式来分析nmosIRF150 的模型参数kp 值分別为20u 40u 60u 时的输入输出转换电压图可是我在capture 中找不到可以设kp 值的地方~请教教我~ 谢谢~RE:此Kp 值是在model 里,所以在Capture 中您看不到如果您想知道kp 在那里,你可以跟著下面的步骤做:Step 1:在Capture 选该元件(会有粉红色的highlight)Step 2:在令命令列找Edit>PSpice model 就可以看到此个元件的model.里头就有KP 的值(此为原来的设定)至於您要如何做kp 值的设定及模擬,你可以跟著下面的步骤做:Step 1:在模擬设定里选择DC Sweep 並做好设定.Step 2:在同一视窗的左下有Option,请勾选Secondary Sweep, 会出跟DC Sweep 一像的设定面Step 3:在Sweep Variable>Model parameterModel type >选择该零件的格式(Ex:NPN ..etc)Model name >电路图上该零件的编號(Ex:Q1 ..etc)Parameter name>设定该零件的参数名称(Ex:Kp ..etc)Step 4:在Sweep Type >Value list 设定成20u 40u 60u 即可.Step 5:做完模擬后, 选您想看的节,就可看到您要的结果.版本 9.0问题类別 OrCAD Pspice標题请问若VPWL 超过八组参数,该怎设定详细说明请问我如果需要输入一个驱动IC 波形,则需要超过十二个以上的(T,V)设定,可是PSPICE 的VPWL 只提供八组,请问该如何使用呢?谢谢RE:您好:您可以使用VPWL_ENH 这个零件代替在 "FIRSTS_NPAIR" 做(T,V)的设定即可Ex:(1m,1v)(2m,3v)....(T,V)如果您想要所设的波形有週期性,请在"Repart_value" 设定成1 即可.版本 14.1问题类別 Cadence Allegro Studio標题 power plane 走线, gerber 如何出负片详细说明 PSD14.1 是否允许在定义为负片层走线? 如何出gerber?RE:power plane 走线只要將其层面设为conduct 成一加般走线层面先走线再铺铜铺上去的铜会依设定自动避开先前所走的线到时出一张正片即可若是负片层要走线则要开一层只走內层线並將加粗后之效果製作在负片层上最后出底片时要出內层负片(plane)及正片(走线)两个erber 再合要是负片层走线不多则利用切割作出其效果不用出两张底片再合问题类別 OrCAD Layout標题 Layout 上的问题详细说明在单面板上如何做出水滴状的佈线(使用 Dip 零件 )RE:在Layout 中並无直接做出泪滴的功能您可以利用free track 在pad 左右各补一条走线,使之达到泪滴的功能版本 9.2问题类別 OrCAD Capture標题如何找到元件库中没有的SPICE MODEL详细说明想要找到MMBV609LT1 这个元件的SPICE MODEL 请问要到哪里找RE:关於您的问题,您可透过下列几种方式去找寻元件的model.可从网上去做搜寻(例如/doc/e37319276.html,)或从零件供应商取得如果都没有的话,最后您也可以用等效电路的方式来做模擬版本 orcad releace9问题类別 OrCAD Capture標题无法进入orcad,救救我吧!详细说明为什我安装了orcad 9 之后,我进入orcad 的任何一个程式都显示[2001]Unable to find a license file .correct the error and chick "Retry",orchick"cancel"to about the program.我隨便按了个键就跳开了,我有下载单机版的安装步骤但都是乱码,所以请指导一下,感激不尽!RE:软体没解密找一个解密程式將其解掉即可=问题类別 OrCAD Capture標题马上知道某个零件在layout 上外型详细说明在Capture 的Schematic 图中如果要知道某个零件在layout 上外型(pack) 我该如何作RE在Capture 中並无观看Layout footprint 的功能如您要观看Layout 的外观只有Capture CIS的程式才有此功能而其外观只有OrCAD Laout & Cadence Allegro 两种Layout 软体才可观看其Layout 外观图版本 micro sim 8.0问题类別 OrCAD Pspice標题有个相依电源的问题想请教详细说明 1.如果有一行pspice 的语法EF1 SF1 MF1 POLY(2) TF1 0 TF2 0 0.0 1.707 0.707( EF1=1.707VTF1+0.707VTF2)这是一个电压控制电压源的元件他有四个端我这四个端要如何去设定,要如何把他连接起来2.如果我想找有关多条传输线耦合,去耦合变成单跟理想传输线的问题要找哪些书??3.如果我有关这方面的问题,在网上留言不清楚可以到贵公司去请教你们的工程师吗谢谢RE1.Pspice 里面的E_poly 元件,仅有一个变数来做电压控制,无法直接转成您所描述的格式(两个变数来做电压控制),因此若要达到您的需求,则需要请您参考相关的书籍並建立两个变数控制的E_poly 元件.(您可以到/doc/e37319276.html,/technical/library/analog/analog.asp 的网站,下载相关Pspice 的说明电子档)2.关於您说的"多条传输线耦合,去耦合变成单跟理想传输线"的问题,看不出是属於那方面的问题.因此如果可以的话,烦请说明一下您设计电路的方式.至於书籍方面,很遗憾没有很的资讯可提供给您.版本 9.0问题类別 OrCAD Capture標题如何在G 元件中输入变数详细说明一般在使用G 元件(电压控制电流源)时GAIN 参数只能输入常数但是我在需要让G 元件的输出电流为输入电压的倒数也就是GAIN 参数需输入1/Vin 请问Capture 是否有提供此功能谢谢RE您可以使用"GVALUE"这个元件,在EXPR 这个参数只要设定成"1/(%IN+,%IN)",就可以达成您的要求.版本 9.1问题类別 OrCAD Layout標题如何將Capture 的档案转入Layout 的MAX 档案详细说明如何將Capture 的档案转入Layout 的MAX 档案例如在Capture 的电路图做好后要用Layout 来佈线RE您好:您必须先在Capture 中设定Layout 所需的Footprint 您Footprint 输入完成后即可输出Net list File再直接进入Layout 程式中选取File 中的NEW 指令﹔使用DEFAULT.TCH 技术档再指定您所输出的Netlist file 即可版本 9.00b问题类別 OrCAD Layout標题单层板佈线详细说明使用layout plus 作单层BOTTOM 佈线,TOP 层设为Jumper Layer Jumper Attributes 內 Jumper 1 length=100, Jumper2 length=200,Jumper3 length =300 后. 用Smartrute autoroute board 自动佈线完成后发仍有几条鼠线未完成佈置.为什没自动放置Jumper1 or 2.....??单层板佈线应如何设Jumper?? 谢谢回答!!RE您所敘述的Jumper 是Layout 的功能而非Smartroute 的功能所以在Smartroute 中是无法达到您所设定的功能您可以在Layout 中执行Autoroute 则可以出jumper版本 9.00b问题类別 OrCAD Layout標题接地/layer详细说明你好:设计脚针式双面板,壹铺铜区欲接地obstacle typecopper area, Net attachmentGND POWER, component reference designatorU1(ex.8051), pin name20.发U1 与铺铜区成一体.但autoroute board 完成后却无连结借library manager 之零件皆有POWER/GND 层(灰色).设计脚针式双面板设TOP/BOT 设routing 余设为unused但在post process 中仍有.PWR/.GND 层,是否正確??由.mnl 转来图可否先手工怖线重要线路,其余由smrtroute autoroute board 来完成?试好几次皆无效!RE您可以先执行Auto 中Refresh All 的指令此指令可以將所有物件重新整理如此即可將铜铂重新整理输出的板层取决於Post process 中是否有此资料如您不想输出.GND 与.POWER 两层请您將Post process 的.POWER 与.GND 刪除则输出的Gerber 中即不会输出此资料如您刪除后想再加入.POWER 或.GND 则在Post process 新增回来即可可以先在Layout 中绘製重要线路再於smartrote 中选择options 下之Net properties 將您佈好的走线使用unrote 则在Auto route 后此线段即可保留版本 9.0问题类別 OrCAD Layout標题如何將lay 好的线路做成连板详细说明如何將lay 好的线路做成连板RE一般製作连板大多是在CAM 的软体中处理的如您在Layout9.0 中可能无法达成连板的动作版本 9.00b问题类別 OrCAD Layout標题 pad & via详细说明你好:如何设pad 直径和solder mask expansion 的直径,就是pad 和防銲漆之间的空隙,要使零针脚吃銲锡的地方.在library manager 中找好久指令皆无法完成!(vias 同样问题!)pbc 板的螺丝固定孔如何设定?如4.5mm 直径圆周要吃銲锡空隙!试了很多指令皆不得其门而入,帮帮忙!在top layer 设一四方形铺铜区,如何设为不喷防銲区.亦是要接地和可銲区?板层设双面板,top/bottom 层为routing 其余皆设为unused.用run post processor 转gerber 档后,为何出.GND/.PWR layer? 这是否正常?以上问题是否帮帮忙! Mnay Thanks!RE您好:针对您的问题我一项一项回您1.您选择View 下Database spreadsheets 中的Padstacks 功能执行后找到相对应的Pad 资料在其中更改各层別中的Width 与Height 即可改变其直径2.您可以製作一个螺丝固定孔的Pad 资料將各Route layer 的Width 与Height 资料设定比Drldwg 与Drill 层別小即可3.您在放置铜箔后再复製一笔资料將其层別设定为SMT(顶层防焊层)SMB(底层防焊层)即可將此铜箔区域上绿漆(不可镀锡) 反之如无相同资料在SMT 与SMB 如此这个铜箔区域即可上锡4..GND 与.POWER 为层別中之內层电源层如您无此需求则將GND 与POWER 层別设定为Unused Routing 即可將GND 与POWER 关闭如您的设计有內层电源层则必须开启版本 9.1问题类別 OrCAD Capture標题 IGBT model 如何Include 至零件中详细说明您好:使用pspice 来模擬电路,元件中有IGBT 但是没有Model,我至元件供应商下载pspice 的model,但是我应如何加至library.另外有些元件无法加入pspice 的model,出undefine 的Error,在simulation 的时后,请问该如何解决.RE1.下载的这个model,若要加到Pspice 去做模擬,有三个步骤: .(1).建立一个新的元件(For Pspice).(2).並在Symbol 的属性里,加上PSpiceTemplate 的描述格式(For Pspice netlist).(3).將下载的model 加入到模擬的设定(For Pspice's model link).2.这个讯息表示,您叫取的元件並不是For Pspice (因为没有model),纯粹只是Symbol 而已版本 9.0问题类別 OrCAD Capture標题有个关於传输线问题想问大家详细说明我想用元件 T2couple 来模擬两根输线,请问T2 couple 跟T2couple X 有什不同,为什我用T2 couple 来模擬两根传输线耦合的波型模擬出来的都是错的,我的L11=L22=341nH L21=L12=58nH,C11=C22=76.6pF,c21=C12=14.6pF 电压是VPWL 传输线长度123m那参数设定值是不是L=341nH Lm=58nH C=76.6pF Cm=14.6pF LEN=123m如果我设的不错那请问我还有哪些地方有可能错ㄋ我的VpwL 在spice 语法是 VPWL(0 0 0.5us 0 0.75us 2.4 4us 2.4 4.25us 0)我在orcad 里设定的是t1=0 v1=0 t2=0.5u v2=0 t3=0.75u v3=2.4 t4=4u v4=2.4 t5=4.25u v5=0)请问我有哪些地方设错吗RE关於您的问题,分两部份来说明:1.编辑新的TitleBlock > 开启Capsym.olb 並开启TitleBlock 的library,即可编辑里头的TitleBlock(PS:请另存新的档名).2.开启一张电路图,在Menu Bar 的Option >Design Template >TitleBlock可做Orgnization Name,Document Number,Revision 等的设定.(ps:里头的Symbol >Library Name:若存在Capsym.olb,此路径不用给;若存在不同的路径,请给完整的路径(Ex: "c:lirary.olb") Title Block Name:打上要叫取TitleBlock 的名称.3.加入TitleBlocek 到图档里,有两个方式:(1).在电路图里在Manu Bar 的找Place >找TitleBlock 加入即可.(2).或是在步骤2 设定好TitleBlock 的路径和名称,在新增一个新图时,即可直接套用.版本 9.0问题类別 OrCAD Layout標题救救我详细说明如何在LAYOUT 中改銲的大小~~`不是孔径的大小~~~ 谢谢~~~可以快一回我吗~~~我很需要~~~~RE您好:请您在Database Spreadsheets 选项中执行Padstack 指令在其表单中选择所需更改的Pad 资料更改成你所需的大小即可版本 8.0问题类別 OrCAD Pspice標题请问如何把pspice 的电路图贴在word详细说明如標题请问要如何把pspice 的电路图贴在wordRE关於您的问题可直接在PSpice 的电路图上圈选(用滑鼠按住左键並拖拉您的滑鼠)您想要的部分並使用PSpice 的Copy 命令再將Word 打开直接使用Word 的Paste 的指令即可达到您要的功能版本 9.0问题类別 OrCAD Capture CIS標题请问如何编製专属电路的零件库?详细说明您好:因每个零件都有其专属的零件库档案,以至於佔用不少容量,但是如orcad4.0 有编制其专属零件库的功能(即是把各个零件库中有用到的零件另外存成一个零件库)不知orcad9.0 是否有?非常感谢您的协助RE在Orcad Capture(包含Capture CIS)里都可以做到您想要的功能在Windows 版本里的Project manager 视窗(类似像档案总管的架构去里)里有Design Cache 这个资料夹(此资料夹即是在存放有"叫取过的零件" 会在此做个列表)您可以打开这个电路图在 Menu bar 里的File>New> Library ( 此。

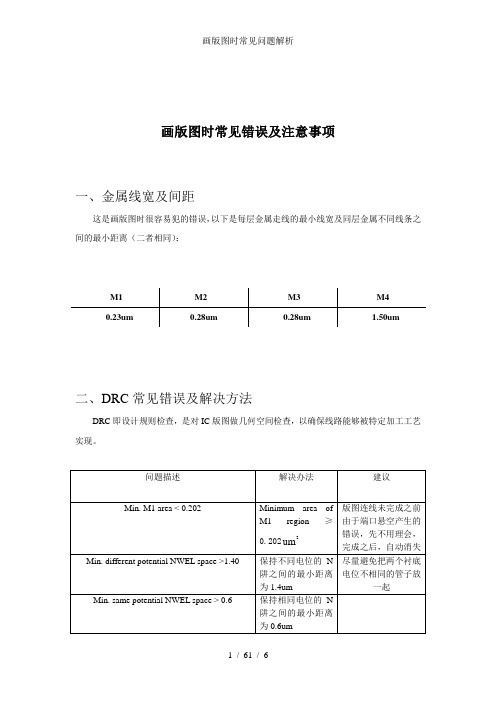

画版图时常见问题解析

画版图时常见错误及注意事项一、金属线宽及间距这是画版图时很容易犯的错误,以下是每层金属走线的最小线宽及同层金属不同线条之间的最小距离(二者相同):二、DRC常见错误及解决方法DRC即设计规则检查,是对IC版图做几何空间检查,以确保线路能够被特定加工工艺实现。

NP space >0.440 (NP:N+ S/D Implantatiaon) 保持两个N管N+注入区最小距离0.440um(对应的Layer name为NIMP层)PP space >0.440 (PP:P+ S/D Implantatiaon) 保持两个P管P+注入区最小距离0.440um(对应PIMP层)VIA3 must be 0.36 x 0.36 通孔的大小由默认值决定,不能更改VTMN.S.1 { @ Min. space between two VTM_N regions < 0.44um } 保持两个器件的VTM_N层间距>=0.44um同样是距离的问题,这是中阈值管相对其它管子多出的一层掩模层A bent PO region is not allowed in VTM_Nregion 用POL Y做连接时POL Y的宽度必须与管子的栅长相等直接用POL Y连接两个器件的栅时,首先必须保证两个器件的栅长相等!@ Any point inside NMOS source/drain space to the nearest PW STRAP in the same PW <= 30 um @ Any point inside PMOS source/drain space to the nearest NW STRAP in the same NW <= 30 um 对相应的器件打阱即可Min. enc.Of NTAP by NP<0.18 with PWLL<0.43 在通孔周围画N阱,使得N阱到扩散区的距离>=0.43um 这是在自动生成M1_NWELL contact 时产生的错误,是由于自动生成的contact 的扩散区到NWELL 的距离小于0.43um上面的错误大多是距离的问题,有时这些要求满足了,还会出现一些问题,这时就要考虑是不是器件选用的错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

orcad原理图中常见DRC错误的取缔方法用“取缔”一词,是源自《嘻哈四重奏》里面卢导的口头禅,哈哈借用一下~大多数DRC warning甚至某些error可以忽略不计,不影响生成网表,但是要想成为一名成熟的电子工程师,你可以忽略某些错误,但是必须懂得为什么会产生这些错误,如何取缔掉这些错误,这样才能控制这些错误的作用范围,不致影响系统整体的设计。

1、养成好习惯,先做Annotate,后做 ERC 检查,避免元器件重名;

2、切记不要随意从其他page中拷贝元器件,这样容易在ERC检查时导致以下三个错误:

例如从

这个图(来源于另一个page)中拷贝C209这个电容到下面page中,ERC检查出现了以下三个错误:

ERROR: [DRC0010]

Duplicate reference

C209

ERROR: [DRC0031]

Same Pin Number connected to more than one net.

Ctrl_ultrasound_launch/C209/1 Nets: 'GND' and '5V_A4'.

ERROR: [DRC0031]

Same Pin Number connected to more than one net.

Ctrl_ultrasound_launch/C209/2 Nets: '9V_A1' and 'GND'.

解决方法:先做annotate,所有元器件重新编号,再做ERC检查,这样避免不同页面元器件重名而导致网络连接在一起,可以直接解决以上3个错误~WARNING: [DRC0003]

Port has a type which is inconsistent with other ports on the net TMCL 解决方法:Net TMCL两端的端口类型冲突,修改一下type就好了~ERROR: [DRC0004]

Possible pin type conflict

U5,Vout Output Connected to Power

解决方法:把芯片的pintype由output换成passive

WARNING: [DRC0004]

Possible pin type conflict E2,1 Bidirectional Connected to Output: BENCH, C (0.40, 10.10)

解决方法:

These errors are produced based on the settings in the ERC matrix. If you've finished your design and you think that the connections are correct after you've checked all these errors, you can change the settings in the ERC matrix to remove them from the Design Rules Check.

To change the ERC matrix:

1. Select the schematic page in the Project Manager.

2. Choose Design Rules Check from the Tools menu, then select

the ERC matrix tab.

3. Make changes to the matrix, then click OK. When you click OK,

Design Rules Check will run with the new settings.

简单来说就是修改ERC matrix,来控制ERC检查,这样就提

高了容错能力,更容易通过,但前提是对自己的设计要有把握,

确保正确。

WARNING: [DRC0006]

Net has fewer than two connections A01

解决方法:网络标号只有一处,没有配对的,或者网络标号命名有差别,注意必须命名相同才表示连接。

WARNING: [DRC0006]

Net has fewer than two connections

5V_A2

解决方法:这个warning的产生在于一页原理图上电源bar只有一次连接点,这样就会报

错,通常可以忽略,或者在芯片的电源引脚旁边加一个0.1uF的 bypass 电容接地就

,,,这种设计习惯也是比较好的,只要名称相同,不同页的电源bar

就是相连的。

ERROR: [DRC0007]

Net has no driving source A01-PC

解决方法: 总线网络标号有问题,即总线的标号必须与总线名中的一致,例如总线名为:A[0..5],那么总线的分支网络标号就只能取A0、

A1、……A5中间的一部分或者全部,而不能超出或者改成其他的。

WARNING: [DRC0008]

Two nets in the same schematic have the same name, but there is no

off-page connector--〉

解决方法:you label a port or off-page connector with a name that is used by a power symbol or power pin on the schematic. It would be

best to replace the port with a power symbol to transfer power through the design. If you have verified that there are no connectivity problems when running the netlist, you can ignore this warning.

ERROR: [DRC0026]

This reference has already been assigned to a different package type.

U1

解决方法:检查U1各个部分part reference还有封装有没有不同的

ERROR: [DRC0027]

Other parts in this package have different values or PCB footprints.

U1--〉

解决方法:检查U1各个部分part reference还有封装有没有不同的

ERROR: [DRC0029]

Bus has no name and therefore defines no signals.

N9792615

解决方法:再总线上加上总线名称即可消除两端的DRC错误,总线命名必须和总线两端的的分支网络名相一致,即必须是分支网络名称的集合。

如果在原理图中Ctrl+F找不到出现DRC错误的Net,或出现DRC错误的Net的坐标超出图纸范围,则应把原理图的Page Size放大,有可能是因为当初画图时某些器件忘记删掉就直接调整图纸大小了。

确实很低级的错误

这篇东西也参考了网上很多文章和论坛里面的一些问题和解答,由于自己做得辛苦,所以就综合一下子,结合自己的理解和过程,希望初学的朋友不再对DRC检查迷茫,当然这些内容也不全,后续碰到了其他warning和error再补上来。