基于FPGA的倒计时定时器

FPGA实验 计时器和倒计时的系统设计

实验五 计时器和倒计时的系统设计一、实验目的①掌握用Verilog HDL 文本输入法设计计时电路的方法,并通过电路仿真和硬件验证,进一步了解计时器的功能和特性。

②掌握用Verilog HDL 文本输入法设计倒计时电路的方法,并通过电路仿真和硬件验证,进一步了解倒计时电路的功能和特性。

二、实验原理1. 计时器24小时计时器的电路框图如图8.1所示。

图8.1 24 小时计时器的电路框图24小时计时器由2个60进制加计数器和1个24进制加计数器构成,输入CLK 为1Hz(秒)的时钟,经过60进制加计数后产生1分钟的进位时钟信号,再经过60进制加计数后产生1小时的进位时钟信号送给24进制加计数器进行加计数,当加计数到达23: 59: 59后,再来一个秒脉冲,产生时的进位输出。

将两个60进制加计数器和一个24进制加计数器的输出送数码管显示,得到计时器的显示结果。

其中,秒脉冲由EDA 实训仪上的20MHz 晶振分频得到。

2. 侧计时器24小时倒计时器的电路框图如图8.2所示。

图8.2 24 小时倒计时器的电路框图24小时倒计时器由2个60进制减计故器和1个24进制减计数器构成,输入CLK 为1Hz(秒)的时钟,经过60进制减计数后产生1分钟的借位时钟信号,再经过60进制减计数后产生1小时的借位时钟信号送给24进制减计数器进行减计数,当减计数到达00: 00: 00后,产生时的借位输出,同时24小时倒计时器停止倒计时,并发出提醒信号。

将两个60进制减计数器和一个24进制减计数器的输出送数码管显示,得到倒计时的显示结果。

其中,秒脉冲由EDA 实训仪上的20MHz 晶振分频得到。

三、实验设备秒脉冲①EDA实训仪1台。

②计算机1台(装有QuartusⅡ软件)。

四、实验内容1. 计时器在QurtusⅡ软件中,按照实验原理中24小时计时器的电路框图,用Verilog HDL编程设计计时器电路,然后进行编辑、编译(综合)、仿真,引脚的锁定,并下载到EDA实训仪中进行验证。

基于BASYS2FPGA的0—99秒可设置倒计时器

基于BASYS2FPGA的0—99秒可设置倒计时器姓名班级学号实验⽇期 12-10 节次 9-10 教师签字成绩实验名称基于BASYS 2 FPGA 的0 — 99秒可设置倒计时器1.实验⽬的利⽤Xilinx BASYS 2开发板,实现0—99秒的可设置倒计时器。

1、实验板的⼋个开关,前四个控制⼗位,后四个控制个位,按照四位⼆进制数所对应⼗进制数输出(⼤于等于9的均视为9)。

2、四位⼋段数码管⽤于显⽰时间,第⼀位对应⼗位,第⼆位对应个位,后两位对应1秒的百分数。

3、两个按键,RESET 为复位键,按键后,倒计时从当前开关状态重新开始,PAUSE 键为暂停,按住时倒计时暂停,松开后继续。

2.总体设计⽅案或技术路线3.实验电路图Ⅰ、总体RTL SCHEMATIC:端⼝说明:CLK_IN为50MHZ时钟输⼊;PAUSE 计时暂停;RESET 计时重置;S1,S0为重置时设置的倒计时的⾼位和次⾼位的起始值;QA_OUT连接到数码管阳极;QC_OUT连接到⼋段数码管(含⼩数点)阴极;图1 RTL SCHEMATIC整体图图 2 RTL SCHEMATIC细节图Ⅱ、源程序1)主模块顶层程序top.v:module top(CLK_IN,RESET,PAUSE,S1,S0,QC_OUT,QA_OUT);input CLK_IN,RESET,PAUSE;input [3:0] S1,S0;output [7:0] QC_OUT;output [3:0] QA_OUT;wire CLK_OUT;wire CLK2_OUT;wire [3:0] Q1,Q2,Q3,Q4;wire [7:0] Q1_OUT,Q2_OUT,Q3_OUT,Q4_OUT;frediv f1(CLK_OUT,CLK2_OUT,CLK_IN);source_counter_1 c1(Q1,Q2,Q3,Q4,CLK_OUT,RESET,PAUSE,S1,S0);display d1(Q1_OUT,Q1);display2 d2(Q2_OUT,Q2);display d3(Q3_OUT,Q3);display d4(Q4_OUT,Q4);coordination o1(QC_OUT,QA_OUT,Q1_OUT,Q2_OUT,Q3_OUT,Q4_OUT,CLK2_OUT); endmodule2)分模块具体程序1、分频模块frediv.vmodule frediv(CLK_OUT,CLK2_OUT,CLK_IN);output CLK_OUT,CLK2_OUT;input CLK_IN; //50MHZ输⼊reg [18:0] cn; //19位计数器wire CLK_OUT;wire CLK2_OUT;initialbegincn=0;endalways @(posedge CLK_IN)beginif(cn==499999)begin cn<=0; endelse cn<=cn+19'd1;endassign CLK_OUT=cn[18]; //输出100HZ,作为四位数码管赋值模块时钟输⼊assign CLK2_OUT=cn[15]; //输出800HZ,作为数码管扫描频率2、对四位数码管赋值模块source_counter_1.vmodule source_counter_1(Q1,Q2,Q3,Q4,CLK,RESET,PAUSE,S1,S0);input CLK,RESET,PAUSE;input [3:0] S1,S0;output [3:0] Q1,Q2,Q3,Q4;reg [3:0] Q1,Q2,Q3,Q4;reg [3:0] N,M;always @(posedge CLK )begincase (S1)4'd0: N=4'd0;4'd1: N=4'd1;4'd2: N=4'd2;4'd3: N=4'd3;4'd4: N=4'd4;4'd5: N=4'd5;4'd6: N=4'd6;4'd7: N=4'd7;4'd8: N=4'd8;4'd9: N=4'd9;default :N=4'd9;endcasecase(S0)4'd0: M=4'd0;4'd1: M=4'd1;4'd2: M=4'd2;4'd3: M=4'd3;4'd4: M=4'd4;4'd5: M=4'd5;4'd6: M=4'd6;4'd7: M=4'd7;4'd8: M=4'd8;4'd9: M=4'd9;default :M=4'd9;endcase //⾼位和次⾼位的起始值预置if(RESET==1) begin Q1<=N;Q2<=M;Q3<=4'd0;Q4<=4'd0;end //RESET重置else if(PAUSE==1) begin Q1<=Q1;Q2<=Q2;Q3<=Q3;Q4<=Q4; end //PAUSE 暂停else if (Q4==0)begin Q4<=4'd9;if(Q3==0)begin Q3<=4'd9;if(Q2==0)begin Q2<=4'd9;if(Q1==0)begin Q1<=N;Q2<=M;Q3<=4'd0;Q4<=4'd0;endelse Q1<=Q1-4'd1;endelse Q2<=Q2-4'd1;endelse Q3<=Q3-4'd1;endelse Q4<=Q4-4'd1; //对四位数码管依次赋值,类似于递减1的计数器end3、译码显⽰模块3.1:display.vmodule display(Q_OUT,Q);input [3:0] Q;output [7:0] Q_OUT;reg [7:0] Q_OUT;always@(Q)begincase (Q)4'd0:Q_OUT<=8'b11000000; //共阳极数码管4'd1:Q_OUT<=8'b11111001;4'd2:Q_OUT<=8'b10100100;4'd3:Q_OUT<=8'b10110000;4'd4:Q_OUT<=8'b10011001;4'd5:Q_OUT<=8'b10010010;4'd6:Q_OUT<=8'b10000010;4'd7:Q_OUT<=8'b11111000;4'd8:Q_OUT<=8'b10000000;4'd9:Q_OUT<=8'b10010000;default :Q_OUT<=8'b11111111; //数码管的⼩数点DP段码不点亮endcase endEndmodule3.2:display2.vmodule display2(Q_OUT,Q);input [3:0] Q;output [7:0] Q_OUT;reg [7:0] Q_OUT;always@(Q)begincase (Q)4'd0:Q_OUT<=8'b01000000;4'd1:Q_OUT<=8'b01111001;4'd2:Q_OUT<=8'b00100100;4'd3:Q_OUT<=8'b00110000;4'd4:Q_OUT<=8'b00011001;4'd5:Q_OUT<=8'b00010010;4'd6:Q_OUT<=8'b00000010;4'd7:Q_OUT<=8'b01111000;4'd8:Q_OUT<=8'b00000000;4'd9:Q_OUT<=8'b00010000;default :Q_OUT<=8'b01111111; //数码管的⼩数点DP段码点亮,endcaseend其中,3.1和3.2的区别在于数码管的⼩数点DP段码的点亮与否,在top模块的调⽤时保证其整体上显⽰为Q1Q2.Q3Q4形式,即只有Q2通过display2来译码,其他三个通过Display来译码。

基于FPGA的定时器计数器的设计与实现

基于FPGA的定时器/计数器的设计与实现摘要本课题旨在用EDA工具与硬件描述语言设计一个基于Altera公司的FPGA 16位计数器\定时器,可对连续和非连续脉冲进行计数,并且计数器在具有计数定时功能基础上,实现简单脉宽调制功能和捕获比较功能。

本设计采用QuartusII编译开发工具使用VerilogHDL 设计语言进行设计,并采用了由上而下的设计方法对计数器进行设计,体现了VerilogHDL 在系统级设计上自上而下设计风格的优点。

本设计中采用了三总线的设计方案,使设计更加简洁与规范。

本设计所有模块与功能均在Quartus II 7.0_1.4G_Liwz版本下通过编译与仿真,实现了定时器/计数器的设计功能。

关键词:VerilogHDL硬件描述语言;QuartusII;FPGA;定时器/计数器FPGA-based timer / counter design and implementationThis topic aims to use EDA tools to design a 16 bit counter \ timer based on Altera's FPGA by hardware descripe language, which can count continuous and discontinuous pulset, and the counter with the function of capture and PWM. This design uses VerilogHDL language and top-down design method to design the counter on QuartusII compile tool, the design reflect the advantages of VerilogHDL top-down design in system-level design. The design uses a three-bus design, which make design much more specifications and concise. The design and function of all modules are compiled and simulationed on the Quartus II 7.0_1.4G_Liwz versions, and achieve the timer / counter’s features.Key words: VerilogHDL hardware description language; QuartusII; FPGA; timer / counter河北大学2011届本科生毕业论文(设计)目录引言 (1)1 计数器设计方式选择与论证 (4)1.1 计数器实现方案论证 (4)1.2 设计方式选择认证 (4)1.2.1 自下而上的设计方法 (4)1.2.2 自上而下的设计方法 (4)1.2.3 混合的设计方法 (5)2 计数器整体设计方案 (6)3 计数器/定时器各种工作方式的设计 (8)3.1 计数模块 (8)3.1.1 位加计数器模块 (8)3.1.2 位减计数器 (9)3.2 顶层模块设计 (11)4 总结 (19)谢辞........................................ 错误!未定义书签。

基于FPGA的1 100s计时器

摘要高精度计时器常用于体育竞赛及各种要求有较精确定时的技术领域。

通常,采用中规模集成电路即可实现高精度计时器的设计。

本项研究将基于新一代硬件描述语言(HDL)、采取ASIC(专用集成电路)设计方法,实现1/100s计时器的前端设计。

本计时器包括5个模块:键输入模块、时钟分频模块、开关及控制模块、时钟定时模块、显示模块,以完成1/100s计时器所界定的功能。

在键输入模块中,将产生消除抖动后的reset0(复位脉冲输出)和on_off0(启/停脉冲输出)。

时钟分频子模块。

clk_div实际上是一个用计数器进行分频的分频电路,得到用于计时的100Hz脉冲信号和消除抖动的25Hz脉冲信号。

控制子模块是根据计时器的工作状态,控制是否输出计数允许信号enable,它用于控制计数子模块的计数工作。

计时子模块是一个定时计数器,用来产生要显示的8位计时信息,当使能信号enable有效时计数器开始有效计数。

计时器显示模块的输入信号为计时模块输出的计时信息;它的输出信号是choose和segment,驱动用于计时显示的8个LED七段显示数码管。

在输出信号中,由于八进制计数器循环计数,LED七段显示数码管循环点亮来显示计时器的计时输出。

对各个功能模块进行硬件描述以后,然后采用新一代可编程逻辑器件开发软件平台Quartus II,进行逻辑功能仿真与时序验证,并在FPGA开发板上进行了综合和适配。

关键词:计数器;HDL;集成电路设计;仿真ABSTRACTA precise calculargraph is usually applied to any technical fields as athletic competition that demands accuratetiming. Usually, the design of precise calculargraph can be maded by using mediate scale integrate circuit.The study which is based on the new hardware description language and adapts the design method of ASIC will realize the advanced design of calculargraph whose accuracy will be 1/100s. This calculargraph, including keyin module, clock frequency division module, switching and controlling module, display module ,can realize the function exercised by accurate calculargraph of 1/100s .The key_in module will produce reset0 and on_off0. Clock frequency division is actually a frequency division circuit divided by a calculator. When divided 10 times 1 KHz clock signal will result in clock’s 100Hz clock pulse signal and redivided 4 times it will result in 25Hz. The controlling sub_module is used to control whether enable the calculating signal according to the calculator’s working status. The calculating sub_module is a calculating timer, used to display 8_figure calculating information when the enable signal starts calculating effectively. The input signal of calculargraph display module is the calculating information it outputs, with the output signal choose and segment, driving the eight LED 7_section display digital tube used for calculating display. When it outputs signals, the LED 7_section display digital tube will be highlighted in circles to display the calculating output because of the 8_figure display’s calculating in circles.When describing all function modules’hardwares, a programming software plat from Quartus II will be developed. Its logical function emulation and time sequence will be tested, integrated into specific device and adapted.Key words:calculargraph; HDL; integrate circuit design; imitation目录摘要 (I)ABSTRACT........................................................... I I 第一章绪论.. (1)1.1 引言 (1)1.2 基于硬件描述语言(HDL)的电路设计 (2)1.3 可编程逻辑器件的设计流程 (3)1.3.1 系统说明 (4)1.3.2 设计输入 (4)1.3.3 设计实现 (5)1.3.4 器件编程 (5)第二章计时器的硬件描述语言(VHDL)设计 (6)2.1 1/100s计时器的功能描述 (6)2.2 计时器的模块划分 (9)2.3 计时器的模块设计 (12)2.3.1 键输入模块 (13)2.3.2 时钟分频模块 (15)2.3.3 控制模块 (18)2.3.4 计时模块 (20)2.3.5 显示模块 (24)2.4 计时器的顶层设计 (31)第三章 1/100s计时器的FPGA实现 (35)3.1 设计平台和器件的选择 (35)3.2 使用ModelSim对设计进行仿真 (36)3.2.1 键输入模块的时序仿真 (36)3.2.2 时钟分频模块的时序仿真 (37)3.2.3 控制模块时序仿真 (37)3.2.4 计时模块时序仿真 (38)3.2.5 显示模块时序仿真 (38)3.2.6 顶层模块时序仿真 (39)第四章 1/100s计时器的后端实现 (40)4.1 FPGA开发板简介 (40)4.2 综合和配置 (41)结论 (44)参考文献 (45)致谢 (48)第一章绪论1.1 引言在EDA出现以前,人们一直采用传统的硬件电路设计方法来设计系统的硬件。

FPGA定时器24s倒计时

设计一个用于篮球比赛的定时器。

要求:(1)定时时间为24秒,按递减方式计时,每隔1秒,定时器减1;(2)定时器的时间用两位数码管显示;(3)设置两个外部控制开关,开关K1控制定时器的直接复位/启动计时,开关K2控制定时器的暂停/连续计时;当定时器递减计时到零(即定时时间到)时,定时器保持零不变,同时发出报警信号,报警信号用一个发光二极管指示。

(4)输入时钟脉冲的频率为1kHz。

(5)用Verilog HDL语言设计,用Modelsim软件做功能仿真,用Quartus II综合。

(6)将设计代码和仿真代码写在作业本上。

module gcount(out,sel,clock_1k,clear,pause,gcon);input clock_1k,clear,pause;output [6:0] out;output sel,gcon;reg [6:0] out;reg sel,gcon;reg [3:0] cnt_sl,cnt_sh,count;reg [9:0] fenpin;wire clock_1 = fenpin[9]; // 1Hz;always @(posedge clock_1k or negedge clear)beginif (!clear)fenpin <= 10'b0;elsefenpin <= fenpin + 1;end//cnt_slalways@(posedge clock_1 or negedge clear)//always@(posedge clock_1 or negedge clear or posedge pause)beginif(!clear)cnt_sl<=4'h4;else if (!pause)cnt_sl<=cnt_sl;else if (cnt_sh == 0 && cnt_sl == 0)cnt_sl<=4'h0;else if (cnt_sl == 0)cnt_sl<=4'h9;elsecnt_sl<=cnt_sl-1;end//cnt_shalways@(posedge clock_1 or negedge clear)//always@(posedge clock_1 or negedge clear or posedge pause) beginif(!clear)cnt_sh<=4'h2;else if (!pause)cnt_sh <= cnt_sh;else if (cnt_sh == 0 && cnt_sl == 0)cnt_sh<=4'h0;else if (cnt_sl == 0)cnt_sh<=cnt_sh-1;elsecnt_sh <= cnt_sh;end//gcon//always@(posedge clock_1 or negedge clear)always@(cnt_sh or cnt_sl)beginif (cnt_sh == 0 && cnt_sl == 0)gcon<=1;elsegcon <= 0;end//regalways@(posedge clock_1k or negedge clear)beginif(!clear)sel<=0;elsesel <= ~sel;endalways @(sel)count = (sel == 0)?cnt_sh:cnt_sl;always @(count)begincase(count)4'b0000: out=7'b011_1111;4'b0001: out=7'b000_0110;4'b0010: out=7'b101_1011;4'b0011: out=7'b100_1111;4'b0100: out=7'b110_0110;4'b0101: out=7'b110_1101;4'b0110: out=7'b111_1101;4'b0111: out=7'b000_0111;4'b1000: out=7'b111_1111;4'b1001: out=7'b110_1111;default: out=7'b000_0000;endcaseendendmodule`timescale 1ns/1ns`include"./gcount.v"module test;reg Clock_1k,Clear,Pause;wire [6:0] Out;wire Sel,Gcon;initialbeginClock_1k<=0;Clear<=1;Pause<=1;#100 Clear<=0;#100 Clear<=1;#5000 Pause<=0;#5000 Pause<=1;#5000 Clear<=0;#5000 Clear<=1;endalways #1 Clock_1k<=~Clock_1k;gcount m(.out(Out),.sel(Sel),.clock_1k(Clock_1k),.clear(Clear),.pause(Pause),.gcon(Gcon));endmodule。

24小时计时器--FPGA

课程设计任务书学生姓名:罗序森专业班级:通信gj1101______ 指导教师:胡辑伟工作单位:____信息工程学院_____ 题目: 通信工程应用技术课设——FPGA一、设计任务与要求设计一个具有系统时间设置和带闹钟功能的24小时计时器中的应用。

电子钟要求如下:(1)计时功能:4位LED数字时钟对当前时间的小时和分钟进行显示,显示的最长时间为23小时59分。

(2)设置并显示新的闹钟时间:用户先按“set”键,再用数字键“0”~“9”输入时间,然后按“alarm”键确认。

在正常计时显示状态下,用户直接按下“alarm”键,则已设置的闹钟时间显示在显示屏上。

(3)设置新的计时器时间:用户先按“set”键,再用数字键“0”-“9”输入新的时间,然后按“time”键确认。

在输入过程中;输入的数字在显示屏上从右到左依次显示。

例如,用户要设置新的时间12:00,则按顺序输入“l”,“2”,“0”,“0”键,与之对应,显示屏上依次显示的信息为:“1”,“12”;“120”,“1200”。

如果用户在输入任意几个数字后较长时间内,例如5秒,没有按任何键,则计时器恢复到正常的计时显示状态。

(4)闹钟功能:如果当前时间与设置的闹钟时间相同,则扬声器发出蜂鸣声;三.时间安排:指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (2)Abstract ................................................... 错误!未定义书签。

1 绪言 ..................................................... 错误!未定义书签。

1.1 课题的研究背景及意义................................ 错误!未定义书签。

1.2 闹钟系统的.......................................... 错误!未定义书签。

基于FPGA的计时器设计(最终)

本科毕业设计(论文)基于FPGA的计时器的设计学院自动化学院专业电子信息科学与技术年级班别2009级(1)班学号3109001158学生姓名刘健忠指导教师谭北海2013年4月基于F P G A 的计时器设计刘健忠自动化学院摘要随着电子设计自动化技术和可编程逻辑器件的出现和飞速发展,在设计周期得到大大的缩短的同时系统成本也有了大幅度的降低,显然标准逻辑器件的组装已远不能满足这方面的要求。

而Verilog HDL能提供高阶电路描述语言的方式,让复杂的电路可以通过Verilog HDL编辑器的电路合成方式,轻易而且快速的达到设计的规格。

由于Verilog HDL电路描述语言能涵盖的范围相当广,能适用于各种不同阶层的设计工程师的需要,所以Verilog HDL电路设计毫无疑问的成为硬件设计工程师的必备工具。

本系统是用Verilog编写的基于Altera DE2的电话计费器。

该设计采用了现场可编程逻辑器件FPGA设计,并基于硬件描述语言Verilog HDL在Altera公司的Quartus Ⅱ软件上实现仿真。

根据电话局反馈回来的信号,此信号是提前预设的,数码管显示通话类型、用户余额以及通话时长(包括秒数和分钟数)。

根据每种通话类型的计费价格不同,当系统所设置的余额数不够,用户将无法拨通电话,当用户余额小于指定金额时,系统发出警告信号,提醒用户。

当告警时间过长(超过1分钟)时自动切断通话信号。

当用户结束通话,系统清零。

关键词:Verilog ,FPGA,通话信号,计时器AbstractWith the rapid development of electronic design automation technology and programmable logic devices which greatly shorten the design period and reduced the cost of the system at the same time. Apparently, the assembly of standard logic devices can not meet the requirements in this regard. Verilog HDL can provide high-level circuit description language, which allows complex circuit by the Verilog HDL Editor circuit synthesis method as well by meeting the design specification appropriately. Verilog HDL circuit description language covers a very wide range,which can be applied to a variety of different sectors of the needs of design engineers, the circuit design of Verilog HDL without a doubt to become an essential tool for hardware design engineers.The system is based on Altera DE2 written by Verilog phone devices. It is used by Field Programmable Gate Array FPGA based on Verilog HDL hardware description language to design and Altera's Quartus Ⅱin software for emulation. According to the feedback of the telephone office back signal which is actually pre-designed, digital pipe display type, user balance and phone call duration (including the number of seconds or minutes). Depending on the billing price of each call type is different,when a began to balance the set is not enough, the user will not be able to dial the phone, and when the balance is less than the specified money, issuing a warning signal system, reminding to users. When the alarm time is too long (more than 1 minutes), the conversation signal will be automatically cut off . When the user end the call, the system will be reseted.Key words:Verilog ,FPGA,Calling signal,calculagraph目录1绪论 (1)1.1 课题研究的目的 (1)1.2 国内外发展现状 (1)1.3课题的主要技术路线 (2)2FPGA技术及硬件描述语言 (3)2.1 FPGA的介绍 (3)2.1.1可编程逻辑器件发展简史 (3)2.1.2可编程逻辑器件的基本结构 (3)2.1.3可编程逻辑器件分类 (4)2.1.4 Altera Cyclone Ⅱ系列器件介绍 (5)2.1.5 FPGA的开发流程 (5)2.2 FPGA设计方法 (6)2.3 利用硬件描述语言(HDL)的硬件电路设计方法 (7)2.4 Verilog HDL语言的设计流程 (8)2.5 Quartus Ⅱ概述及其设计流程 (11)2.5.1 Quartus Ⅱ概述 (11)2.5.2 Quartus Ⅱ设计流程 (12)3系统总体设计 (14)3.1 计费模块介绍 (14)3.2 预设模块介绍 (15)3.3 时钟分频模块介绍 (15)3.4 分拆模块介绍 (15)3.5 数码管显示模块介绍 (16)3.6 警告模块介绍 (17)3.7 逻辑资源使用情况 (17)4系统的操作与分析 (18)4.1系统功能介绍 (18)4.2 选择通话类型和设置余额 (20)4.3通话开始 (21)4.4通话结束 (22)结论 (23)参考文献 (24)致谢 (25)附录A (26)附录B (27)附录C (31)附录D (32)附录E (33)附录F (35)附录G (36)1绪论1.1课题研究的目的时钟计时器在现在应用场合非常的广泛,近年来,随着科学技术的进步和时代的发展,人们对时钟的功能和精度提出了越来越高的要求,各种时钟的设计也越来越重要。

基于fpga的倒计时时钟实验报告总结

基于FPGA的倒计时时钟实验报告总结一、实验目的本实验旨在通过FPGA技术,设计一个能够进行倒计时的时钟电路,并进行相应的功能验证。

二、实验内容1. 确定实验目标:设计一个基于FPGA的倒计时时钟电路,实现倒计时功能。

2. 学习FPGA设计工具:熟悉并掌握FPGA设计工具的使用方法,包括逻辑综合、时序分析等。

3. 编写时钟电路代码:利用Verilog硬件描述语言编写时钟电路的代码。

4. 进行仿真验证:对时钟电路进行仿真验证,确保设计的正确性和稳定性。

5. 下板实验验证:将设计好的时钟电路下载到FPGA开发板上,进行实际验证。

三、实验步骤与结果分析1. 设计倒计时时钟电路通过学习资料和实验指导,我们利用Verilog HDL进行倒计时时钟电路的设计,并对其功能进行初步测试。

初步测试结果表明,设计的倒计时时钟电路能够正常工作。

2. 时钟电路仿真验证我们利用FPGA设计工具对时钟电路进行了仿真验证,通过时序分析和波形仿真,确认了时钟电路的正确性和稳定性。

仿真结果显示,时钟电路能够准确地进行倒计时操作。

3. 下板实验验证将设计好的时钟电路下载到FPGA开发板上进行实际验证。

经过实际测试,我们发现倒计时时钟电路能够稳定可靠地进行倒计时操作,符合设计要求。

四、实验总结通过本次实验,我们深入学习了FPGA技朰,并成功设计并验证了基于FPGA的倒计时时钟电路。

实验中我们克服了一些困难,如时钟电路设计的复杂性和仿真验证的精确性等。

我们顺利完成了实验目标,掌握了FPGA设计工具的使用方法,提高了自己的实践能力和动手能力。

这次实验为我们今后在FPGA领域的研究打下了坚实的基础,也对我们的专业素养、工程实践能力提出了更高的要求。

五、改进建议在今后的实验中,我们可以进一步深入研究FPGA技术,探索更多的应用场景,提高我们的设计水平。

注重团队合作、创新思维,不断提升自己的综合素质和实践能力,为将来的科研工作和工程实践打下更加坚实的基础。

基于FPGA的加减计时器设计

基于FPGA的加减计时器设计作者:陈龙险来源:《电子技术与软件工程》2015年第11期摘要基于现场可编程门阵列FPGA(系Field Programmable Gate Array的缩写)的电路系统设计,是目前数字电路设计的主流方法之一。

本文阐述了基于FPGA的加减计时器设计方法,提出了系统电路的设计思路及合理方案,该设计计时器兼备秒加计时和秒减倒计时的功能。

并借助于Quartus II开发平台完成仿真设计,通过FPGA硬件实验箱进行测试,验证结果表明本文提出的设计方案正确可行。

【关键词】FPGA Quartus II EDA 计数器随着全球经济的高速发展、科学技术的不断创新,电子设计自动化EDA(系Electronic Design Automation的缩写)技术,在电子信息工程领域成为了当今世界上最先进的电子电路设计技术。

它依靠功能强大的电子计算机,在EDA工具软件平台上,对以硬件描述语言HDL (系Hardware Description Language的缩写)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、优化、仿真,直至下载到可编程逻辑器件如现场可编程门阵列FPGA或复杂的可编程逻辑器件CPLD(系Complex Programmable Logic Device的缩写)或专用集成电路ASIC(系Application Specific Integrated Circuit的缩写)芯片中,从而实现既定电子电路的功能系统设计。

因此,在电子工程应用领域,用EDA技术来完成电子系统的设计,已成为现代电子设计技术的核心。

1 设计方案本文提出的系统设计方案采用自顶向下的设计方法,从系统设计入手,在顶层对计时器整体电路系统进行功能方框图的划分和结构设计,在方框图一级进行仿真、纠错,用硬件描述语言(HDL)对高层次的系统行为进行描述并于功能一级进行验证;系统电路的设计依托于FPGA硬件平台,采用超高速集成电路硬件描述语言—VHDL(系Very High Speed Integrated Circuit Hardware Description Language的缩写),设计在Quartus II开发环境下进行;设计出的计时器计时范围为00.00--59.00秒,精度为0.01秒,具有秒加和秒减计时、清零、计时—停止—继续计时等功能,对百分之秒和秒的计数信息采用四位LED数码管进行友好界面显示。

基于FPGA的有限状态机计时器设计

基于FPGA的有限状态机计时器设计当前FPGA应用很广,可以用来设计很多自身需求的程序以达到一定的便利。

本文使用FPGA设计一个计时器,该计时器用到有限状态机的机制来实现控制,计时器可实现时分秒的精确计数,并可显示出去再液晶屏或者显示屏。

最后进行功能仿真以校验时序和控制的准确性。

标签:FPGA;计时器;控制;状态机1.前言当前FPGA的应用非常广,用它进行编程的人也越来越多。

应用FPGA进行自身所需求的产品的设计是非常合适的,用有限状态机的机制去控制计时器,让计时器可以重置、报时等。

有限状态机常常被用在自动售货机、排号机、ATM、银行业务自助机等上面。

该计时器可显示时分秒,最大计时为59时59分59秒,可以清零和每隔10分钟进行报时。

2.设计与实现该计时器由三个部分组成,这三个部分分别是控制部分、计时部分、显示和发声部分。

控制部分主要由一个有限状态机完成控制,有清零和启动/暂停等按键。

该有限状态机设置六个状态,分别是清零状态、零值状态、开始状态、计时状态、停止状态、启动状态。

该状态机两个输入分别是清零按键(re)、启停按键(star/stop),两个输出分别是计时许可(able)、计时清零(rst),其状态机图如下图1所示:其中,当清零按键re按下时,状态机进入清除状态,其计时许可控制输出信号able为低电平,计时清零输出信号rst为高电平,则进行清零,计时器就会清除当前所有计时,并从清零状态进入到零值的状态;而在零值状态下,当按下启停按键(star/stop)時,就会进入开始状态,则计时器开始计时;而在开始状态下时,当star/stop按键由0变成1时,则会进入自动计时状态,计时许可控制信号able为高电平,允许计数器计数;在计时状态下,当按下启停按键时即star/stop 按键由1变成0时,则停止计时,会进入停止状态;在停止状态下,当star/stop 按键由0变成1时,就会进入启动状态;在启动状态下,当按下启停按键时即star/stop按键由1变成0时,则又进入开始状态;当star/stop按键由0变成1时,进入计时状态,这时计数器会在原来已经计有的数字的基础上继续计时。

基于FPGA十进制计时器设计

十进制计时器设计一、实验目的:熟悉Quartus II的开发环境和开发流程,掌握Verilog文本设计流程,并使用Verilog编写一个十进制计时器,在Altera-Modelsim软件上仿真,验证十进制计时器的功能是否正确。

二、实验原理:十进制计数器的CLK为计数的信号,上升沿有效;RST为计数器复位信号;EN为时钟使能信号,当EN处于高电平时,计数器在CLK有效时开始计数;DATA为4位并行的数据输入端;DOUT为4位并行的数据输出端;Load为计数器的数据加载控制信号,当Load处于低电平时,数据输入端DATA 的数据被加载至数据输出端DOUT;Cout为计数器的进位输出。

三、实验步骤:3.1创建项目(1)新建一个文件夹存放EDA项目设计的相关文件。

本项设计的内容为十进制计数器,并且文件名不能使用中文,因此文件夹取名为CNT10,存放的路径为C:\Users\pp\Desktop\CNT10。

其次,项目的顶层文件名设置必须与编辑代码中的顶层模块名一致。

(2)将设计文件加入工程中。

单击File name栏后的控件,将与工程相关的Verilog文件加入工程;若没有编写相关Verilog文件,便单击Next进入下一步。

(3)选择目标芯片。

根据项目开发的硬件平台,选择与之相应的FPGA芯片。

首先在Device Family下拉列表中选择Cyclone系列,在引脚数目pin count中选择144,可快速筛选出符合条件得芯片型号。

(4)EDA工具设置。

此窗口中有三项选择:Design Entry/Synthesis用于选择输入的HDL类型和综合工具;Simulation用于选择仿真工具;Timing Analysis用于选择时序分析工具。

若不作选择,则默认选择Quartus II自含的EDA设计工具。

3.2 Verilog文本输入选择File->New命令,在New窗口中选择Verilog HDL File命令建立Verilog 文本,设置文件名为cnt10.v并存放在C:\Users\pp\Desktop\CNT10文件夹的根目录下。

基于FPGA的倒计时定时器

数电实验设计报告

实验名称:倒计时定时器

实验目的:

1.掌握组合逻辑与时序逻辑电路的设计方法及调试方法

2.熟练掌握常用MSI逻辑芯片的功能及使用方法

3.初步掌握Verilog HDL数字系统设计方法

4.熟悉PLD实验箱的结构和使用及Quartus II软件的基本操作

5.掌握采用Quartus II软件和实验箱设计实现逻辑电路的基本过程

设计要求:

一、倒计时定时器:

用适当的中小规模集成电路设计一个定时器,实现60s以内的定时功能,可以设置60s 以内任何时间作为倒计时的起点,将设计下载到实验箱并进行硬件功能测试。

要求:

用开关或按键进行定时设置

倒计时计数状态用两位数码管显示

计时结束时用彩灯或声响作为提

电路设计过程:

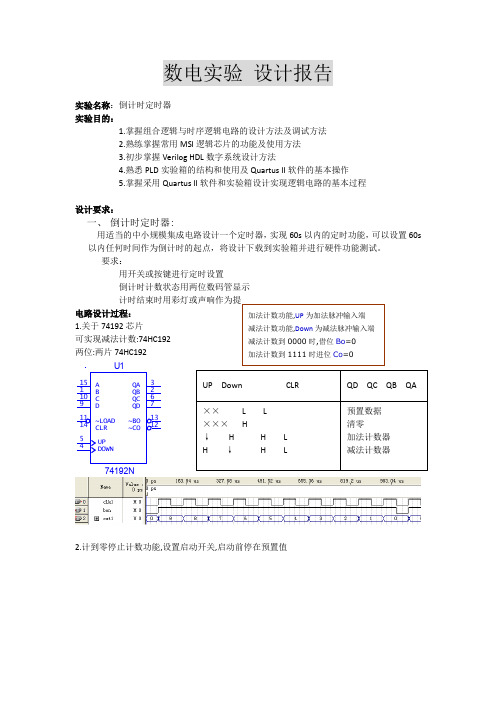

1.关于74192芯片

可实现减法计数:74HC192

两位:两片74HC192

2.计到零停止计数功能,设置启动开关,启动前停在预置值

U1

74192N

A

15

B

1

C

10

D

9

UP

5

QA3

QB2

QC6

QD7

DOWN

4

~LOAD

11~BO13

~CO12

CLR

14

加法计数功能,UP为加法脉冲输入端

减法计数功能,Down为减法脉冲输入端

减法计数到0000时,借位Bo=0

加法计数到1111时进位Co=0

模拟结果如下

3.运用两片74192级联,组成倒计时计数器,个位减到0,十位开始减法计数.

4.加入译码器完成数码管显示

设计原理图:

数码管动态扫描原理图:

分析统图:

管脚分配方案:。

基于FPGA的篮球24秒倒计时系统设计

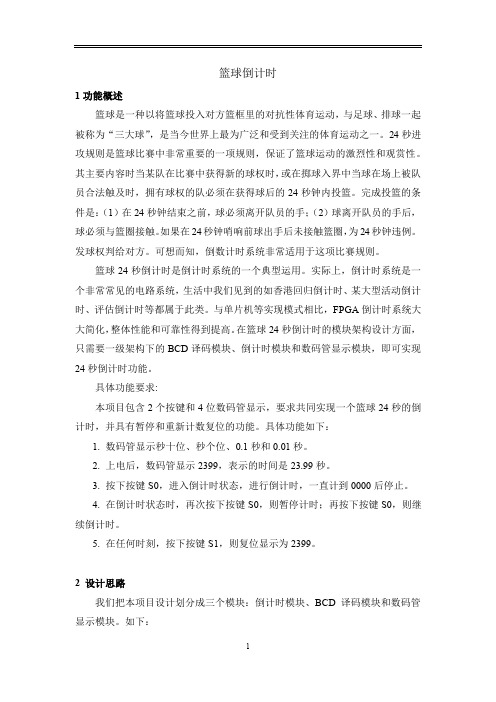

基于FPGA的篮球24秒倒计时系统设计一、功能描述 本工程包含了两个按键和4位数码管显示,共同实现一个篮球24秒倒计时、并具有暂停和重新计数复位的功能。

具体功能如下: 1. 数码管显示秒十位、秒个位、0.1秒和0.01秒。

2. 上电后,数码管显示2399,表示时间是23.99秒。

3. 按下按键1,进入倒计时状态,进行倒计时,一直计到0000后停止。

4. 在倒计时状态时,再次按下按键1,则暂停计时;再按下按键1,则继续倒计时。

5. 在任何时刻,按下按键2,则复位显示为2399。

二、平台效果图 1.Altera核心板效果图 2.Xilinx核心板效果图 三、实现过程 首先根据所需要的功能,列出工程顶层的输入输出信号列表。

我们可以把工程划分成三个模块,分别是倒计时模块、BCD译码模块和数码管显示模块。

1.倒计时模块 倒计时模块实现的是24s倒计时功能,其输出两组计数信号cnt_s和cnt_ms。

例如当时间为23.99时,cnt_s的值为23,cnt_ms的值为99;当时间为08.12时,cnt_s的值为8,cnt_ms的值为12。

模块还实现了暂停和重开始功能,按下按键1开始倒计时,再次按下则暂停,再次按下则开始,无论何时按下按键2,恢复到23.99。

本模块的信号列表如下: 2.BCD译码模块 由于倒计时模块输出的是2进制的cnt_s和cnt_ms,但数码管是个位和十位分别显示的。

例如当cnt_s值为10时,也就是8b00001010,而送给数码管的个位值为4b0000,十位值为4b0001。

这个转换过程也就是BCD译码,也就是本模块要实现的功能。

此处介绍二进制转BCD码的硬件实现,采用左移加3的算法,具体描述如下:(此处以8-bit 二进制码为例) 1、左移要转换的二进制码1位 2、左移之后,BCD码分别置于百位、十位、个位 3、如果移位后所在的BCD码列大于或等于5,则对该值加3 4、继续左移的过程直至全部移位完成 举例:将十六进制码0xFF转换成BCD码 本模块的信号列表如下: 由于秒和毫秒都要译码,所以要例化两个BCD译码模块。

基于FPGA的篮球倒计时的设计和实现 (优选.)

篮球倒计时1功能概述篮球是一种以将篮球投入对方篮框里的对抗性体育运动,与足球、排球一起被称为“三大球”,是当今世界上最为广泛和受到关注的体育运动之一。

24秒进攻规则是篮球比赛中非常重要的一项规则,保证了篮球运动的激烈性和观赏性。

其主要内容时当某队在比赛中获得新的球权时,或在掷球入界中当球在场上被队员合法触及时,拥有球权的队必须在获得球后的24秒钟内投篮。

完成投篮的条件是:(1)在24秒钟结束之前,球必须离开队员的手;(2)球离开队员的手后,球必须与篮圈接触。

如果在24秒钟哨响前球出手后未接触篮圈,为24秒钟违例。

发球权判给对方。

可想而知,倒数计时系统非常适用于这项比赛规则。

篮球24秒倒计时是倒计时系统的一个典型运用。

实际上,倒计时系统是一个非常常见的电路系统,生活中我们见到的如香港回归倒计时、某大型活动倒计时、评估倒计时等都属于此类。

与单片机等实现模式相比,FPGA倒计时系统大大简化,整体性能和可靠性得到提高。

在篮球24秒倒计时的模块架构设计方面,只需要一级架构下的BCD译码模块、倒计时模块和数码管显示模块,即可实现24秒倒计时功能。

具体功能要求:本项目包含2个按键和4位数码管显示,要求共同实现一个篮球24秒的倒计时,并具有暂停和重新计数复位的功能。

具体功能如下:1. 数码管显示秒十位、秒个位、0.1秒和0.01秒。

2. 上电后,数码管显示2399,表示的时间是23.99秒。

3. 按下按键S0,进入倒计时状态,进行倒计时,一直计到0000后停止。

4. 在倒计时状态时,再次按下按键S0,则暂停计时;再按下按键S0,则继续倒计时。

5. 在任何时刻,按下按键S1,则复位显示为2399。

2 设计思路我们把本项目设计划分成三个模块:倒计时模块、BCD译码模块和数码管显示模块。

如下:FPGA顶层模块的信号列表如下:倒计时模块——实现的是24s倒计时功能,其输出两组计数信号cnt_s和cnt_ms。

例如,当时间为23.99时,cnt_s的值为23,cnt_ms的值为99;当时间为08.12时,cnt_s的值为8,cnt_ms的值为12。

推荐-基于FPGA的倒计时系统的设计 精品

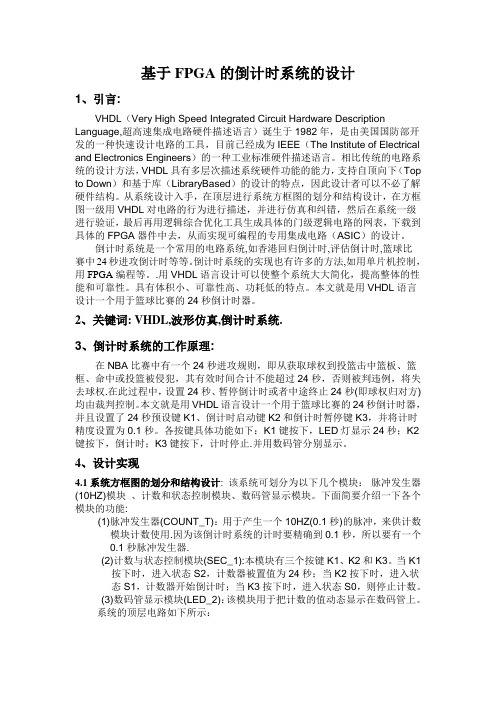

基于FPGA的倒计时系统的设计1、引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)诞生于1982年,是由美国国防部开发的一种快速设计电路的工具,目前已经成为IEEE(The Institute of Electrical and Electronics Engineers)的一种工业标准硬件描述语言。

相比传统的电路系统的设计方法,VHDL具有多层次描述系统硬件功能的能力,支持自顶向下(Top to Down)和基于库(LibraryBased)的设计的特点,因此设计者可以不必了解硬件结构。

从系统设计入手,在顶层进行系统方框图的划分和结构设计,在方框图一级用VHDL对电路的行为进行描述,并进行仿真和纠错,然后在系统一级进行验证,最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表,下载到具体的FPGA器件中去,从而实现可编程的专用集成电路(ASIC)的设计。

倒计时系统是一个常用的电路系统,如香港回归倒计时,评估倒计时,篮球比赛中24秒进攻倒计时等等。

倒计时系统的实现也有许多的方法,如用单片机控制,用FPGA编程等。

.用VHDL语言设计可以使整个系统大大简化,提高整体的性能和可靠性。

具有体积小、可靠性高、功耗低的特点。

本文就是用VHDL语言设计一个用于篮球比赛的24秒倒计时器。

2、关键词: VHDL,波形仿真,倒计时系统.3、倒计时系统的工作原理:在NBA比赛中有一个24秒进攻规则,即从获取球权到投篮击中篮板、篮框、命中或投篮被侵犯,其有效时间合计不能超过24秒,否则被判违例,将失去球权.在此过程中,设置24秒、暂停倒计时或者中途终止24秒(即球权归对方)均由裁判控制。

本文就是用VHDL语言设计一个用于篮球比赛的24秒倒计时器,并且设置了24秒预设键K1、倒计时启动键K2和倒计时暂停键K3,并将计时精度设置为0.1秒。

FPGA计时器

桂林电子科技大学职业技术学院实训报告桂林电子科技大学职业技术学院FPGA实训报告计时器学院(系):电子信息工程系专业:电子信息工程技术学号: ===========学生姓名: =======指导教师: ========桂林电子科技大学职业技术学院实训报告目录目录 (2)摘要 (3)2 课题背景 (4)2.1设计任务与要求 (4)2.2设计目的 (4)2.2.1 设计题目的概述 (5)3 总体设计方案 (5)3.1 设计思想 (5)3.2方案选择与论证 (5)4 硬件功能描述 (6)4.1动态显示模块 (6)4.2综合引脚配置 (7)5软件设计 (9)5.1软件流程图及功能介绍 (9)5.2 核心程序设计 (10)6调试 (12)7结论 (12)摘要FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

FPGA以设计灵活、速度快、功耗低的特点,在集成电路设计中得到广泛应用。

在我们的实际生活中,高精度计时器常用于体育竞赛及各种要求有较精确定时的技术领域中。

通常采用中规模集成电路即可实现高精度计时器的设计。

本次设计的计时器包括3个模块:时钟分频模块、开关及控制模块、显示模块,以完成此计时器所界定的功能。

对各个功能模块进行硬件描述以后,可以采用新一代可编程逻辑器件开发软件平台Verilog HDL,进行逻辑功能仿真与时序验证,并在FPGA开发板上进行了综合和适配。

关键词 : 计时器 FPGA Verilog HDL1 绪论在我们的实际生活中,高精度计时器常用于体育竞赛及各种要求有较精确定时的技术领域中。

通常,采用中规模集成电路即可实现高精度计时器的设计。

本项研究将基于新一代硬件描述语言(HDL)、采取ASIC(专用集成电路)设计方法,来实现秒、分计时器的前端设计。

本设计利用VHDL语言采用自顶向下的方法完成了计时器的设计,最后在FPGA开发板进行测试。

基于FPGA的高精度数码电子计时仪设计

基于FPGA的高精度数码电子计时仪设计在现代科技快速发展的时代,电子计时仪已经成为各个领域中不可或缺的一项技术。

在运动竞技、物理实验、计算机研究等领域中,我们都需要用到高精度的计时仪来提供准确的数据支持。

而这里我们要介绍的基于FPGA的高精度数码电子计时仪,正是最新的一种计时仪技术。

一、FPGA技术介绍FPGA即现场可编程门阵列,是一种可编程逻辑器件,主要由可编程逻辑模块、内部控制器、高速缓存、可编程I/O模块组成。

它的主要特点是具有现场可编程性,可以在用户现场进行逻辑和电路设计,提供了更高的灵活性和性能。

因此FPGA技术已经在各个领域中得到了广泛的应用。

二、基于FPGA的高精度数码电子计时仪设计基于FPGA的高精度数码电子计时仪是一种基于可编程技术的计时仪,它利用FPGA的现场可编程特性,将各种计时、数码信号处理等电路全部集成在一块芯片上,从而实现高速、高精度的计时功能。

其主要设计流程如下:1.系统框图设计首先需要对计时仪的各个部分进行需求分析,设计系统框图。

系统框图是整个计时仪的基础,它描述了硬件电路、软件程序、各种控制信号等之间的关系,为后续的设计提供了参考。

2.数码预处理电路设计数码电子计时仪的核心是数码电路,包括数码显示、数字信号处理等电路。

其中数码预处理电路负责数据输入、数据处理等功能。

在数字信号处理方面,数码计时电路主要有比较器、检测器、解码器等电路组成,以保证每次计时的准确性。

3.逻辑控制电路设计逻辑控制电路主要是用来控制数码计时仪的运行状态,包括计时状态、预置状态、停止状态、清零状态等。

在整个电路中,逻辑电路起到了控制和判定的重要作用。

4.FPGA电路设计FPGA电路的设计是最为重要的一步,它包含了所有的硬件和软件设计。

在FPGA的设计过程中,首先需要将设计好的数码预处理电路和逻辑控制电路进行集成,进而实现高精度的计时功能。

5.时序分析和测试验证在所有的电路设计完成后,还需要对整个系统进行时序分析和测试验证。

基于FPGA的节日时钟倒计时控制系统设计

基于FPGA的节日时钟倒计时控制系统设计

刘亦萍;刘涛;王玮;周荣荣

【期刊名称】《机电一体化》

【年(卷),期】2013()8

【摘要】该节日时钟倒计时控制系统是以FPGA芯片EP2C5Q208C8为核心器件组成的一个倒计时系统,与传统门电路相比,受到的外界干扰较小,并且擦除后FPGA 恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

整个系统利用QuartusⅡ11.0软件设计、编译、仿真,最后将程序写入FPGA黑金开发板(DB2C5),实现时钟倒计时控制与显示。

【总页数】4页(P77-80)

【关键词】Quartus;Ⅱ;11;0;EP2C5Q208C8;时钟倒计时;FPGA黑金开发板(DB2C5)

【作者】刘亦萍;刘涛;王玮;周荣荣

【作者单位】上海第二工业大学电子与电气工程学院

【正文语种】中文

【中图分类】TP334.7

【相关文献】

1.基于 FPGA的G PS同步时钟系统设计 [J], 郑恭明;沈媛媛

2.基于SoC FPGA抓包的电站控制系统时钟同步设计 [J], 刘玉升;项文蔚;王楠;王巍

3.基于FPGA控制的航天电源控制器遥测遥控系统设计 [J], 王博宇;王旭东;游小杰;李虹;郑琼林

4.基于FPGA的高精度同步时钟系统设计 [J], 谌普江;龚光华

5.基于PIC和FPGA控制多路步进电机伺服控制系统设计 [J], 申浩锋;高宁波

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数电实验设计报告

实验名称:倒计时定时器

实验目的:

1.掌握组合逻辑与时序逻辑电路的设计方法及调试方法

2.熟练掌握常用MSI逻辑芯片的功能及使用方法

3.初步掌握Verilog HDL数字系统设计方法

4.熟悉PLD实验箱的结构和使用及Quartus II软件的基本操作

5.掌握采用Quartus II软件和实验箱设计实现逻辑电路的基本过程

设计要求:

一、倒计时定时器:

用适当的中小规模集成电路设计一个定时器,实现60s以内的定时功能,可以设置60s 以内任何时间作为倒计时的起点,将设计下载到实验箱并进行硬件功能测试。

要求:

用开关或按键进行定时设置

倒计时计数状态用两位数码管显示

计时结束时用彩灯或声响作为提

电路设计过程:

1.关于74192芯片

可实现减法计数:74HC192

两位:两片74HC192

2.计到零停止计数功能,设置启动开关,启动前停在预置值

U1

74192N

A

15

B

1

C

10

D

9

UP

5

QA3

QB2

QC6

QD7

DOWN

4

~LOAD

11~BO13

~CO12

CLR

14

加法计数功能,UP为加法脉冲输入端

减法计数功能,Down为减法脉冲输入端

减法计数到0000时,借位Bo=0

加法计数到1111时进位Co=0

模拟结果如下

3.运用两片74192级联,组成倒计时计数器,个位减到0,十位开始减法计数.

4.加入译码器完成数码管显示

设计原理图:

数码管动态扫描原理图:

分析统图:

管脚分配方案:。