形式化验证工具Formalityshi实验报告

认识形式化验证

认识形式化验证 软件开发中⼀般使⽤“测试”来找bug,这种⽅法只能找到bug,不能证明程序没有bug。

形式化验证是⽤逻辑来验证程序的可靠性,就是把⼀段程序⽤逻辑的⽅法证明⼀遍,证明它能得到预期的结果,没有bug。

⼀般这类研究主要应⽤于昂贵的航天器材的操作系统、危险的医疗设备的程序之中。

因为航天器材、医疗设备牵扯到⼈的⽣命,如果操作系统出现错误,那么很危险,⼜不能⽤测试⼀遍⼀遍的测,所以⽤形式化验证来做。

⽐如美国航天局NASA就会雇佣⼤批形式化验证的专家来验证他们操作系统的正确性。

学习这个⽅向,最好有⽐较好的逻辑知识(数理逻辑、拉姆达验算),最好⽐较了解程序(⽐如操作系统的设计、编译器的设计等)。

这个⽅向是⽐较犀利的研究⽅向,但不⼤容易出论⽂,需要长时间积累才能发⼀篇好论⽂。

这个⽅向只是科研⽅向,不适合找⼯作,如果你读完硕⼠打算找⼯作⽽不做研究,这个⽅向不适合。

因为企业没⼈⽤形式化验证来验证程序。

Formal Verification(形式验证) 在计算机硬件(特别是集成电路)和软件系统的设计过程中,形式验证的含义是根据某个或某些形式规范或属性,使⽤数学的⽅法证明其正确性或⾮正确性。

形式验证是⼀个系统性的过程,将使⽤数学推理来验证设计意图(指标)在实现(RTL)中是否得以贯彻。

形式验证可以克服所有3种仿真挑战,由于形式验证能够从算法上穷尽检查所有随时间可能变化的输进值。

形式验证形式验证的出现 由于仿真对于超⼤规模设计来说太耗费时间,形式验证就出现了。

当确认设计的功能仿真是正确的以后,设计实现的每⼀个步骤的结果都可以与上个步骤的结果做形式⽐较,也就是等价检查,如果⼀致就说明设计合理,不必进⾏仿真了。

形式验证主要是进⾏逻辑形式和功能的⼀致性⽐较,是靠⼯具⾃⼰来完成,⽆需开发测试向量。

⽽且由于实现的每个步骤之间逻辑结构变化都不是很⼤,所有逻辑的形式⽐较会⾮常快。

这⽐仿真的时间要少很多。

⼀般要做形式验证的步骤有:RTL和RTL。

形式验证

在目前複雜的數位設計開發過程中,功能驗證十分重要。

雖然硬體的複雜度仍遵循摩爾定律持續成長,但是驗證的複雜性更具挑戰。

事實上,隨著硬體複雜性隨時間呈雙指數成長,驗證複雜性理論上也呈指數成長。

驗證已被公認為是設計過程中的主要瓶頸:高達70%的設計開發時間和資源花在功能驗證上。

Collett International Research認為,即使在驗證上花費如此巨大的精力和資源,功能性缺陷仍是晶片重新投片的頭號原因。

功能性驗證挑戰功能性驗證挑戰邊際情形(corner-case)的缺陷是模擬偽像,由於以模擬為基礎的驗證具有非窮盡的固有特性,因此邊際情形無法被檢測到。

事實上,不管你用多少時間模擬,也不管你的測試平台和產生器有多麼智慧,透過模擬驗證設計意圖對於最小電路以外的所有電路來說都是不完整的。

基本的模擬偽像可以被分成三類:窮盡型、可控型和可觀察型,如表1所示。

表1:模擬與形式驗證的比較。

形式驗證是一個系統性的過程,將使用數學推理來驗證設計意圖(指標)在實現(RTL)中是否得以貫徹。

形式驗證可以克服所有3種模擬挑戰(表1),因為形式驗證能夠從演算法上窮盡檢查所有隨時間可能變化的輸入值。

換句話說,沒有必要顯示如何激勵設計或製作多種條件來實現較高的可觀察性。

雖然從理論上講,模擬測試平台的輸入埠針對待驗證設計(DUV)具有較高的可控性,但測試平台對內部點的可控性一般較差。

為了使用基於模擬的方法識別設計錯誤,以下條件必須保持:* 必須產生正確的輸入激勵,以啟動(也就是感應化)設計中某個點的缺陷* 必須產生正確的輸入激勵,以便將源自缺陷的所有效果傳送到輸出埠在使用基於模擬的驗證時,需要規劃設計中需要驗證的對象:* 定義需要測試的各種輸入條件* 製作功能性覆蓋模型(確定是否做了足夠的模擬)* 搭建測試平台(檢查器,測試樁,產生器等)* 製作特定的直接測試* 成年累月的模擬現實中,工程師一直在反覆做著這些事:執行測試、除錯故障、再次模擬回歸組、觀察各種覆蓋率指標,以及調整激勵(例如操控輸入產生器)以覆蓋以前未覆蓋的設計部份。

Formily讲解_2

设置Implementation Design

• 点击Implement按钮,在Read Design Files 中点击Veril og,出现Add verilog files对话框,

• 选择netlist_w_svf目录下的verlog网表文件mR4000.gat es.v

• 选择Set Top Design,在Choose a library中选择WORK ( Design Library)

• 在Choose a design中选择顶层模块名mR4000 • 点击Set Top按钮。此时在Implementation出现绿色的

对号符。

Match

• 检查reference design 和 Implemention des

4

5 6 7

内容

形式化验证简介

形式化验证的优点

Formality同其他的工具的区别 Formality使用范围 重要概念 Formality工作流程 Formality操作方法

形式化验证简介

形式化验证方法不需要仿真向量,通过数学方法比较实现 与参考是否等价。

Reference Design

module top (…); always @ (posedge clk) . . . endmodule

• 一般调试是从cell数目最小的compare point开始 。在这里我们从第一个compare point开始。

• 选择错误点, 击鼠标右键,选择菜单中的view Lo gic Cones,出现Logic Cones View窗口。

• 在这个新窗口里显示的是reference design 和Imeplemention design的原理图,

synopsys_formality指导手册_概述说明

synopsys formality指导手册概述说明1. 引言1.1 概述在硬件设计领域,验证是一个非常重要的环节。

在设计过程中,我们需要确保设计的正确性和可靠性。

为了实现这个目标,Formality工具被广泛应用于电子设计自动化(EDA)过程中的形式验证。

Synopsys Formality是一款强大的形式验证工具,它可以帮助我们验证两个不同层次或版本的设计之间的等效性。

通过使用Formality,我们可以有效地检查逻辑门级网表和原始RTL之间是否存在功能差异或者错误。

本指导手册将介绍Formality工具的基本概念、应用场景以及使用步骤。

你将了解到如何利用Formality进行验证,并掌握其使用方法和技巧。

1.2 文章结构本文将分为以下几个部分:- 引言:对Formality进行概述并介绍文章结构。

- 正文:详细介绍Formality工具及其相关内容。

- Formality基本概念:解释Formality中涉及到的关键概念和术语。

- Formality的应用场景:探讨使用Formality解决哪些问题以及在哪些情况下选择使用该工具。

- 使用Formality进行验证的步骤:分步骤介绍如何使用Formality进行验证。

- 结论:总结本文的主要内容,并指出Formality在硬件验证中的重要性和前景。

1.3 目的本指导手册的目的是为读者提供对于Formality工具的全面理解。

通过阅读本文,读者将能够了解Formality在形式验证中的基本概念、功能和应用场景,从而能够更好地应用该工具来提高硬件设计的准确性和可靠性。

2. 正文Formality是Synopsys公司开发的一款形式验证工具,它旨在为硬件设计工程师提供一种高效且可靠的形式验证解决方案。

Formality通过比较两个逻辑设计的等效性来进行验证,确保电路实现与规范之间不存在功能差异或逻辑错误。

Formality作为一种形式验证工具,在电路设计领域中有着广泛的应用。

形式化验证方法浅析

形式化验证方法浅析随着信息技术的不断发展,软件系统已经成为现代社会和经济的基础设施之一。

软件系统的正确性和可靠性越来越受到重视,因为软件错误会带来巨大的经济损失和安全隐患。

为了提高软件系统的质量和可靠性,形式化验证方法逐渐成为了重要的研究领域。

本文将对形式化验证方法进行一定的浅析,介绍其基本概念、原理和应用。

一、形式化验证方法的基本概念形式化验证是一种基于数学逻辑的方法,通过数学语言描述待验证系统的行为规范或性质,然后利用自动化或手工化的技术对系统进行验证。

形式化验证方法主要包括模型检测、定理证明和符号执行等技术,其中模型检测和定理证明是相对常见和成熟的技术。

模型检测是一种自动化验证技术,它通过穷举系统的所有可能状态来检测系统是否满足给定的性质。

模型检测的核心就是构建系统的状态转移模型,然后利用状态空间搜索算法进行验证。

常用的状态空间搜索算法包括符号模型检测、显式状态搜索和隐式状态搜索等。

模型检测方法的优点是自动化程度高,能够发现系统中的错误和性质违反情况,但是其缺点是状态空间爆炸问题,对于大规模的系统往往难以处理。

定理证明是一种手工化验证技术,它通过数学推理和演绎来证明系统是否满足给定的性质。

定理证明的核心是将系统的行为规范或性质转化为逻辑公式,然后利用数学推理规则和定理证明工具来验证系统。

定理证明方法的优点是能够处理复杂的性质和系统,但是其缺点是依赖于人工的推理和分析,效率较低并且受到形式化规约的限制。

1. 系统建模:形式化验证的第一步是对系统进行建模,将系统的行为规范或性质形式化描述。

系统建模可以采用多种形式化语言和工具,如时序逻辑、Petri网、状态机和模型检测工具等。

建模的目的是将系统的行为抽象化和形式化,为后续的验证工作奠定基础。

2. 性质描述:形式化验证的第二步是对系统的性质进行描述,通常包括功能性要求和安全性要求。

功能性要求是描述系统的期望行为,如正确性、完备性和一致性等;安全性要求是描述系统的禁止行为,如死锁、饥饿和冲突等。

验证型实验报告格式

一、实验目的通过本次实验,验证某一理论或假设的正确性,并分析实验结果与理论或假设的符合程度。

二、实验原理简要介绍实验所依据的理论或假设,阐述实验的基本原理。

三、实验仪器与材料1. 实验仪器:- 仪器名称1:型号及规格- 仪器名称2:型号及规格- 仪器名称3:型号及规格(根据实际实验仪器填写)2. 实验材料:- 材料名称1:规格及数量- 材料名称2:规格及数量- 材料名称3:规格及数量(根据实际实验材料填写)四、实验步骤1. 准备实验仪器和材料;2. 按照实验原理,设置实验参数;3. 按照实验步骤进行操作;4. 记录实验数据;5. 对实验数据进行分析。

五、实验数据记录与分析1. 实验数据记录:| 序号 | 实验参数 | 实验结果 || ---- | -------- | -------- || 1 | 参数1 | 结果1 || 2 | 参数2 | 结果2 || 3 | 参数3 | 结果3 || ... | ... | ... |2. 实验数据分析:(1)分析实验数据与理论或假设的符合程度;(2)分析实验过程中可能存在的误差及原因;(3)总结实验结果,得出结论。

六、实验结论根据实验结果,验证理论或假设的正确性,并总结实验过程中的经验和教训。

七、实验讨论1. 分析实验结果与理论或假设的差异,探讨可能的原因;2. 对实验过程中的不足之处进行反思,提出改进措施;3. 结合实验结果,对相关理论或假设进行进一步研究。

八、实验总结1. 实验目的:验证某一理论或假设的正确性;2. 实验原理:简要介绍实验所依据的理论或假设;3. 实验仪器与材料:列举实验所需的仪器和材料;4. 实验步骤:详细描述实验操作过程;5. 实验数据记录与分析:记录实验数据,分析实验结果;6. 实验结论:验证理论或假设的正确性;7. 实验讨论:分析实验结果与理论或假设的差异,提出改进措施;8. 实验总结:总结实验过程中的经验和教训。

(注:以上为验证型实验报告格式,实际字数根据实验内容进行调整。

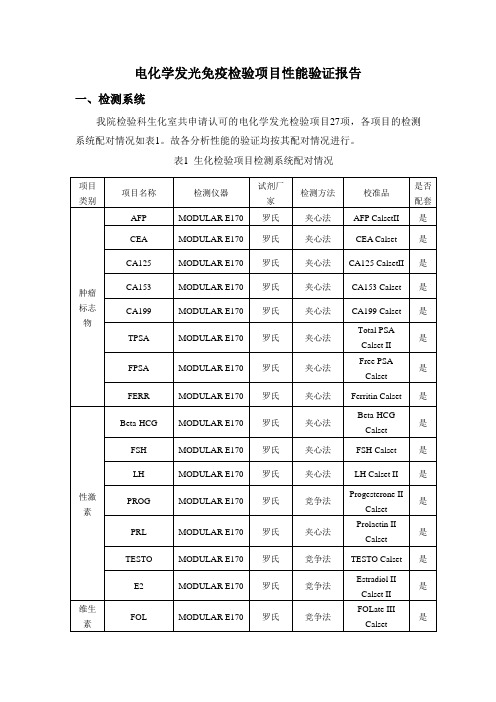

罗氏性能验证报告模板

电化学发光免疫检验项目性能验证报告一、检测系统我院检验科生化室共申请认可的电化学发光检验项目27项,各项目的检测系统配对情况如表1。

故各分析性能的验证均按其配对情况进行。

表1 生化检验项目检测系统配对情况二、范围:2.1 精密度(包括批内及日间精密度)。

2.2 准确度2.3线性范围验证:2.4 稀释度(可报告范围)2.5 生物参考区间的验证三方法1、精密度评估1.1 批内精密度;仪器:瑞士ROCHE公司MODULAR E170全自动电化学发光免疫分析仪材料:ROCHE正常肿瘤质控(批号),ROCHE病理肿瘤质控(批号);ROCHE 正常通用质控(批号),ROCHE病理通用质控(批号);ROCHE正常杂项质控(批号),ROCHE病理杂项质控(批号)。

评估步骤:在确定ROCHE MODULAR E170性能正常的情况下,重复测定20次上述各质控品,计算出各项目的均值、标准差和变异系数。

变异系数即代表精密度。

统计方法:用EXCEL来分析计算均数、标准差和变异系数。

评价方法:根据CLIA'88要求,批内精密度应≤1/4TEa,总精密度应≤1/3TEa,若CLIA'88中未做出规定,则依据中国卫生部临床检验中心室间质评要求执行或验证试剂说明书声明的精密度数据。

结论:1. 2 批间精密度;仪器:瑞士ROCHE公司MODULAR E170全自动电化学发光免疫分析仪材料:ROCHE正常肿瘤质控(批号),ROCHE病理肿瘤质控(批号);ROCHE 正常通用质控(批号),ROCHE病理通用质控(批号);ROCHE正常杂项质控(批号),ROCHE病理杂项质控(批号)。

评估步骤:在确定ROCHE MODULAR E170性能正常的情况下,在5个工作日,测定2批,每次测定2次上述质控,计算出均值,标准差和变异系数。

变异系数即代表精密度。

统计方法:用EXCEL来分析计算均数、标准差和变异系数。

评价方法:根据CLIA'88要求,批内精密度应≤1/4TEa,总精密度应≤1/3TEa,若CLIA'88中未做出规定,则依据中国卫生部临床检验中心室间质评要求执行或验证试剂说明书声明的精密度数据。

静态时序分析(PrimeTime)&形式验证(Formality)详解

摘要:本文介绍了数字集成电路设计中静态时序分析(Static Timing Analysis)和形式验证(Formal Verification)的一般方法和流程。

这两项技术提高了时序分析和验证的速度,在一定程度上缩短了数字电路设计的周期。

本文使用Synopsys 公司的PrimeTime进行静态时序分析,用Formality进行形式验证。

由于它们都是基于Tcl(Tool Command Language)的工具,本文对Tcl也作了简单的介绍。

关键词:静态时序分析形式验证 PrimeTime Formality Tcl目录第一章绪论 (1)1.1 静态时序分析1.2 时序验证技术第二章PrimeTime简介 (3)2.1 PrimeTime的特点和功能2.2 PrimeTime进行时序分析的流程2.3 静态时序分析中所使用的例子2.4 PrimeTime的用户界面第三章Tcl与pt_shell的使用 (6)3.1 Tcl中的变量3.2 命令的嵌套3.3 文本的引用3.4 PrimeTime中的对象3.4.1 对象的概念3.4.2 在PrimeTime中使用对象3.4.3 针对collection的操作3.5 属性3.6 查看命令第四章静态时序分析前的准备工作 (12)4.1 编译时序模型4.1.1 编译Stamp Model4.1.2 编译快速时序模型4.2 设置查找路径和链接路径4.3 读入设计文件4.4 链接4.5 设置操作条件和线上负载4.6 设置基本的时序约束4.6.1 对有关时钟的参数进行设置4.6.2 设置时钟-门校验4.6.3 查看对该设计所作的设置4.7 检查所设置的约束以及该设计的结构第五章静态时序分析 (18)5.1 设置端口延迟并检验时序5.2 保存以上的设置5.3 基本分析5.4 生成path timing report5.5 设置时序中的例外5.6 再次进行分析第六章 Formality简介 (22)6.1 Formality的基本特点6.2 Formality在数字设计过程中的应用6.3 Formality的功能6.4 验证流程第七章形式验证 (27)7.1 fm_shell命令7.2 一些基本概念7.2.1 Reference Design和Implementation Design7.2.2 container7.3 读入共享技术库7.4 设置Reference Design7.5 设置Implementation Design7.6 保存及恢复所作的设置7.7 验证第八章对验证失败的设计进行Debug (32)8.1 查看不匹配点的详细信息8.2 诊断程序8.3 逻辑锥8.3.1 逻辑锥的概念8.3.2 查看不匹配点的逻辑锥8.3.3 使用逻辑锥来Debug8.3.4 通过逻辑值来分析第一章 绪论我们知道,集成电路已经进入到了VLSI和ULSI的时代,电路的规模迅速上升到了几十万门以至几百万门。

应用形式化方法验证软件正确性研究

应用形式化方法验证软件正确性研究在软件工程领域,软件的正确性一直是一个重要的问题。

因为一旦软件存在错误,可能会导致安全问题、质量问题以及用户体验问题。

因此,技术人员需要采用一些方法和工具来验证软件的正确性。

本文主要介绍应用形式化方法来验证软件的正确性的研究进展。

一、形式化方法介绍形式化方法是一种基于数学逻辑的方法,用于以严格的方式描述系统的行为。

它们通常被应用于验证硬件和软件系统的正确性。

形式化方法被广泛应用于不同的领域,如计算机科学、信息科学、通信系统和人工智能等。

其中,常用的方法包括定理证明、模型检测、抽象解释和程序分析等。

二、形式化方法在软件工程中的应用软件系统通常是复杂的,并且需要满足很多不同的要求。

因此,将形式化方法应用于软件工程中,有助于在设计和实现软件系统时减少错误和风险。

以下是一些常用的形式化方法和它们在软件工程中的应用:1. 公理化语义公理化语义是一种描述计算机程序的数学方法。

在公理化语义中,程序可以用公式表示。

这种方法被广泛应用于程序的正确性验证和程序设计的证明。

2. Hoare 逻辑Hoare 逻辑是一种用于推断程序正确性的形式化方法。

在 Hoare 逻辑中,程序的正确性可以用谓词逻辑刻画。

这种方法适用于证明一个程序是否满足其规范。

3. 模型检测模型检测是一种常用的形式化方法,它用于验证关于系统行为的性质。

在模型检测中,系统的行为可以被描述为一个状态转化图。

这种方法被广泛应用于验证硬件和软件系统的正确性。

4. 程序分析程序分析是一种形式化方法,用于自动检测程序中可能存在的错误。

程序分析可以检测出程序中的潜在问题,并产生报告,以指导开发人员进行改进。

以上方法都有其独特的优缺点,需要根据具体的应用场景选择最适合的方法。

三、形式化方法的优势和挑战形式化方法的主要优势是它可以提供证明系统正确性的严格方法。

与传统的测试和调试方法相比,形式化方法可以在设计和实现过程中尽早地发现错误,并减少调试的时间和精力。

形式验证

形式验证现在做集成电路好像不提什么后仿真了。

时髦的名词是“形式验证”。

Formal Verification(形式验证),由于后仿真对于超大规模设计来说太耗费时间,形式验证就出现了。

当确认设计的功能仿真是正确的以后,设计实现的每一个步骤的结果都可以与上个步骤的结果做形式比较,也就是等价检查,如果一致就OK啦,不必进行仿真了。

FV主要是进行逻辑形式和功能的一致性比较,是靠工具自己来完成,无需开发测试向量。

而且由于实现的每个步骤之间逻辑结构变化都不是很大,所有逻辑的形式比较会非常快。

这比仿真的时间要少很多。

一般要做FV的步骤有:RTL和RTL,Synthesized Netlist和RTL,P&R后的网表和Synthesized Netlist,等等。

跨步骤的结果之间也都可以做FV,很多设计也是这样做的,虽然比较的时间会长一点,但可以节省比较的次数。

FV只保证功能正确,timing的分析是靠STA,FV不能完成timing正确性的分析,他只证明了在timing正确的前提下,功能是正确的,所以STA必须照样进行。

Q[n+1] = F( Q[n], x[n] ),此算式表示Q的下一个状态由Q当前状态以及系统输入x决定(可以广义的认为Q,x均为向量,代表所有系统状态,和所有系统输入)。

F为一个布尔函数,假定合成后次关系时就变成了另一种形式Q[n+1] = G( Q[n], x[n] )。

FV只证明了F函数和G函数相等,但是在实际电路上G( Q[n], x[n] )的计算是需要时间的,这个时间必须小于一个系统时钟周期(再加上DFF的setup时间),而且这个时间必须大于DFF的hold 时间。

如果这个不满足了那么前面的差分方程就不成立了。

假定硬件计算G( Q[n], x[n] )要花一个系统时钟多一点(小于两个系而统时钟),在DFF load新的值实际是:G( Q[n-1], x[n-1] ),有可能是G( Q[n-1], x[n] ),因为不同路径delay不同,这样更糟糕} 所以在RTL 时关系式是: F( Q[n], x[n] )。

SOC验证——用Formality做形式验证

用Formality 做形式验证1. 什么是形式验证?形式验证是一种系统化方法,用穷举的算法技术证明设计实现满足设计规范的特征。

它覆盖了输入的所有可能序列,不需要开发测试向量,检查所有的边角逻辑,提供了完整的覆盖率。

2. Formality 的验证原理找到reference design 和 implementation design 二者相对应的 compare points, 把相邻两个 compare point之间的组合逻辑电路转化为数学模型,把每一个 compare point 的输入的各种逻辑情况都遍历一遍,比较二者是否一致,即比较每一个 compare point 在输入相同的情况下所得到的值是否相同。

相邻两个 compare point之间是一些组合逻辑电路,Formality 主要就是比较这两个组合逻辑电路的功能是否一致。

compare point: a compare point can be an output port, register, latch, black box input pin, or net driven by multiple drivers.3. Formality 的验证步骤(1) load reference design and implementation design(2) match compare points(3) verify4. 一个通过验证的模块的reportReference design is 'r:/WORK/Dsss_TX'Implementation design is 'i:/WORK/Dsss_TX'Status: Checking designs...Status: Building verification models...Status: Generating datapath components ...Arch Source Instance PathNo multipliers match these criteria.Status: Qualifying datapath components ...Status: Datapath qualification complete.Status: Matching...************************ Matching Results************************ 7 Compare points matched by name199 Compare points matched by signature analysis0 Compare points matched by topology47 Matched primary inputs, black-box outputs6(0) Unmatched reference(implementation) compare points0(0) Unmatched reference(implementation) primary inputs, black-boxoutputs58(0) Unmatched reference(implementation) unread points----------------------------------------------------------------- Unmatched Objects REF IMPL ----------------------------------------------------------------- Registers 6 0 Constant 0 6 0 *****************************************************************16 Unmatched points (6 reference, 0 implementation):Ref DFF0 r:/WORK/Dsss_TX/CCK_11_MOD1/CdataI_reg[0]Ref DFF0 r:/WORK/Dsss_TX/CCK_11_MOD1/CdataQ_reg[0]Ref DFF0 r:/WORK/Dsss_TX/CCK_55_MOD1/CdataI_reg[0]Ref DFF0 r:/WORK/Dsss_TX/CCK_55_MOD1/CdataI_reg[2]Ref DFF0 r:/WORK/Dsss_TX/CCK_55_MOD1/CdataQ_reg[0]Ref DFF0 r:/WORK/Dsss_TX/CCK_55_MOD1/CdataQ_reg[2][BBNet: multiply-driven netBBox: black-boxBBPin: black-box pinBlock: hierarchical blockBlPin: hierarchical block pinCut: cut-pointDFF: non-constant DFF registerDFF0: constant 0 DFF registerDFF1: constant 1 DFF registerDFFX: constant X DFF registerLAT: non-constant latch registerLAT0: constant 0 latch registerLAT1: constant 1 latch registerLATX: constant X latch registerLATCG: clock-gating latch registerLATTR: transparent latch registerLoop: cycle break pointNet: matchable netPort: primary (top-level) portUnd: undriven signal cut-point]1Reference design is 'r:/WORK/Dsss_TX'Implementation design is 'i:/WORK/Dsss_TX'************************ Matching Results ************************ 7 Compare points matched by name199 Compare points matched by signature analysis0 Compare points matched by topology47 Matched primary inputs, black-box outputs6(0) Unmatched reference(implementation) compare points0(0) Unmatched reference(implementation) primary inputs, black-box outputs58(0) Unmatched reference(implementation) unread points-----------------------------------------------------------------Unmatched Objects REF IMPL ----------------------------------------------------------------- Registers 6 0 Constant 0 6 0 ***************************************************************** Status: Verifying...********************** Verification Results ********************* Verification SUCCEEDED----------------------Reference design: r:/WORK/Dsss_TXImplementation design: i:/WORK/Dsss_TX206 Passing compare points-----------------------------------------------------------------Matched Compare Points BBPin Loop BBNet Cut Port DFF LAT TOTAL ----------------------------------------------------------------- Passing (equivalent) 0 0 0 0 7 199 0 206 Failing (not equivalent) 0 0 0 0 0 0 0 0 *****************************************************************1No failing compare points.1可以看到有6个 unmatched reference compare points, 这6个点只在 reference design 中有,在 implementation design 中没有。

形式化验证讲义

设计良好的描述形式,满足在各层次上描述软件及相关 事物的需要:数据流图、控制流图、状态机、UML等;

开发适用的工具,支持各阶段的不同活动,支持对开发 结果的深入分析和检查:编辑器、调试器、程序分析工 具、集成程序开发环境、UML支持工具等;

形式化规格(3)

形式规格精确地描述了用户的需求、软件系统的功能 以及各种性质,其描述的是“做什么”,而不考虑 “怎么做”。

在书写规格时应该注意的一个问题是如何描述得恰如 其分,既不过多也不过少。在规格中描述过多会导致 “实现偏向”,给实现施加了不必要的限制,从而排 除了一些原本是合理的实现;描述得过少又有容纳不 合理实现的危险。

常用的开发模型:如传统的瀑布模型,较 新近的快速原型、迭代式开发模型等等

软件开发的期望

软件质量稳定,可靠性高 尽量提高开发的效率 尽量降低开发的成本

问题:现在的情况怎么样?

软件开发的实际情况

软件开发的实际情况并不乐观

项目经常延误,预算经常超支 开发的后续阶段常发现许多前期设计错误,更正

立的层次或部分,封装并提供清晰接口。如系统开发 的层次模型,模块化技术,面向对象的技术等; 研究有效的程序开发模型及支持技术,设法屏蔽软件 开发中的难点、解决共性问题。如图形用户界面技术, 客户端-服务器模型,中间件技术,Web服务模型等;

软件问题的应对(2)

研究各种构件形式,以利用已有的开发成果,提高开发 层次,降低开发代价:子程序库、类库、组件库等;

模型检验主要适用于有穷状态系统,其优点是完全自动化 并且验证速度快;并且,模型检验可用于系统部分规格, 即对于只给出了部分规格的系统,通过搜索也可以提供关 于已知部分正确性的有用信息;此外,当所检验的性质未 被满足时,将终止搜索过程并给出反例,这种信息常常反 映了系统设计中的细微失误,因而对于用户排错有极大的 帮助。

什么是形式化验证

设计正确性的验证问题是目前学术界和工业界均予以关注的重要研究课题。

在学术界,对相关课题的研究集中了世界上最优秀的数学家和计算机科学家,他们广泛分布于世界上最著名的高校、科研机构和公司;在工业界,几乎所有的世界顶尖IT公司都投入大量的人力和物力来开发它们的验证和测试工具。

而且,学术界和产业界的密切结合也是该领域的一个突出现象。

设计正确性验证的重要性我们可从以下两个事件切实感受到设计正确性验证的重要性。

1994年,奔腾处理器被发现在执行某个特定的浮点运算时出现错误,这种错误27000年才可能出现一次。

对此,Intel付出4.75亿美元的巨额代价回收有缺陷的奔腾处理器。

1996年6月4日,欧洲航天局研制的阿里亚娜五型火箭在发射后不到40秒爆炸。

事后调查发现,错误发生于当一个很大的64位浮点数转换为16位带符号整数时出现异常。

细微错误,使得十年的努力毁于一旦。

从以上事件可以看出,无论是在高危险性领域中使用的还是普通家用的数字系统,保证设计正确性都是至关重要的。

软件、硬件和协议是目前数字系统设计所包含的三种最基本的形式,任何复杂的数字系统大致都由这三个部分组成。

如果说在复杂系统设计过程中错误是难免的,那么出现事故的惟一原因就是:没有在产品使用前对其进行完备的置信(validation)工作,即确认系统已经完全实现了设计者的意图。

验证技术的方法和困难为什么验证一个系统的正确性会如此困难呢?让我们首先来了解一下主要的验证方法。

迄今的验证方法可分为模拟、仿真和形式验证三种。

模拟验证是传统的验证方法,而且目前仍然是主流的验证方法。

模拟验证是将激励信号施加于设计,进行计算并观察输出结果,并判断该结果是否与预期一致。

模拟验证的主要缺点是非完备性,即只能证明有错而不能证明无错。

因此,模拟一般适用于在验证初期发现大量和明显的设计错误,而难以胜任复杂和微妙的错误。

模拟验证还严重依赖于测试向量的选取,而合理而充分地选取测试向量,达到高覆盖率是一个十分艰巨的课题。

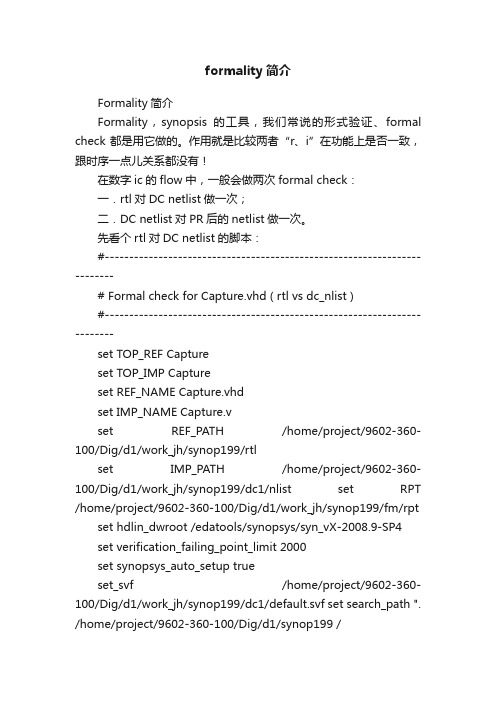

formality简介

formality简介Formality简介Formality,synopsis的工具,我们常说的形式验证、formal check 都是用它做的。

作用就是比较两者“r、i”在功能上是否一致,跟时序一点儿关系都没有!在数字ic的flow中,一般会做两次formal check:一.rtl对DC netlist做一次;二.DC netlist对PR后的netlist做一次。

先看个rtl对DC netlist的脚本:#-------------------------------------------------------------------------# Formal check for Capture.vhd ( rtl vs dc_nlist )#-------------------------------------------------------------------------set TOP_REF Captureset TOP_IMP Captureset REF_NAME Capture.vhdset IMP_NAME Capture.vset REF_PATH /home/project/9602-360-100/Dig/d1/work_jh/synop199/rtlset IMP_PATH /home/project/9602-360-100/Dig/d1/work_jh/synop199/dc1/nlist set RPT /home/project/9602-360-100/Dig/d1/work_jh/synop199/fm/rpt set hdlin_dwroot /edatools/synopsys/syn_vX-2008.9-SP4set verification_failing_point_limit 2000set synopsys_auto_setup trueset_svf /home/project/9602-360-100/Dig/d1/work_jh/synop199/dc1/default.svf set search_path ". /home/project/9602-360-100/Dig/d1/synop199 //edatools/synopsys/syn_vX-2008.9-SP4/libraries/syn"read_db {chrt35_ss_75_1pt3_SYNOPSYS2_MMSIM.db dw_foundation.sldb}read_vhdl -r $REF_PATH/$REF_NAME -l work > $RPT/read_design.rptset_top $TOP_REF > $RPT/set_top.rptreport_hdlin_mismatch > $RPT/rpt_hdlin_mismatch.rptread_verilog -i $IMP_PATH/$IMP_NAME -l work >> $RPT/read_design.rpt set_top $TOP_IMP >> $RPT/set_top.rpt #set_constant -type port r:/.../ 0#set_constant -type port i:/.../ 0match > $RPT/match.rptreport_matched_points > $RPT/matched_point.rptreport_unmatched_points > $RPT/unmatched_point.rptreport_loops -limit 0 -unfold > $RPT/loops.rptverify#以上内容可以放在一个文件里作为脚本,调用方法就是在fm_work下$ fm_shell –f ../scripts/fm_rtl2dc.tcl如果成功要看详细信息或者失败要debug的话,再输入start_gui,进入-GUI模式。

形式化验证工具Formalityshi实验报告

实验七形式化验证工具Formality

班级:XX 姓名:XX 学号:XX

1 实验目标

了解Formality工具的工作流程;

了解Formality工具的调试流程;

熟悉使用脚本进行调试,并通过图形化界面进行调试形式化验证中的不匹配点;

2 实验任务

在GUI环境下,对方使用Formality进行形式化验证的环境;

在命令行运行模式下,根据实验指导书及示例工程完成对一个简单电路的形式化验证;

3 实验环境

安装远程访问工具Xmanager/Xwin-pro的PC机:1台/生;

Linux服务器

4 实验内容

4.1 Formality工具GUI使用

按照实验指导书中的步骤,以图形方式完成对测试用例的形式化环境建立,包括参考、被测设计,库文件导入等内容。

4.2 测试用例的Formality流程

(分析第一个TCL命令的作用,并结出对应结果)

5.思考问题

(说明在进行Formality的Debug过程中的问题及解决方法)。

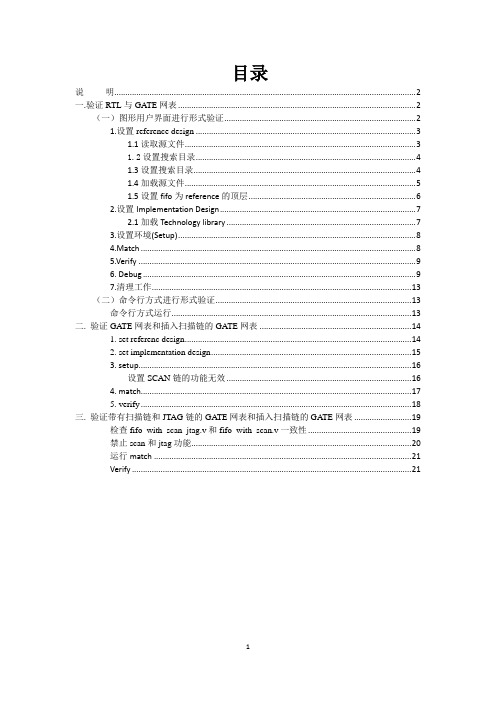

Formality使用指南

目录说明 (2)一.验证RTL与GATE网表 (2)(一)图形用户界面进行形式验证 (2)1.设置reference design (3)1.1读取源文件 (3)1.2设置搜索目录 (4)1.3设置搜索目录 (4)1.4加载源文件 (5)1.5设置fifo为reference的顶层 (6)2.设置Implementation Design (7)2.1加载Technology library (7)3.设置环境(Setup) (8)4.Match (8)5.Verify (9)6. Debug (9)7.清理工作 (13)(二)命令行方式进行形式验证 (13)命令行方式运行 (13)二. 验证GATE网表和插入扫描链的GATE网表 (14)1. set referenc design (14)2. set implementation design (15)3. setup (16)设置SCAN链的功能无效 (16)4. match (17)5. verify (18)三. 验证带有扫描链和JTAG链的GA TE网表和插入扫描链的GATE网表 (19)检查fifo_with_scan_jtag.v和fifo_with_scan.v一致性 (19)禁止scan和jtag功能 (20)运行match (21)Verify (21)说明FiFo的Tutorial目录下包含以下几个子目录:Rtl:fifo的RTL源代码;包含fifo.v, gray_counter.v, push_ctrl.v, gray2bin.v, pop_ctrl.v, rs_flop.v。

Lib:门级网表需要的技术库;包含lsi_10k.db。

Gate:综合的门级网表;包含fifo.vg 和fifo_mod.vg。

Gate_with_scan:插入扫描链的门级网表;包含fifo_with_scan.v。

Gate_with_scan_jtag:带有扫描链和JTAG链的门级网表;包含fifo_with_scan_jtag.v。

一篇很好的关于功能验证、时序验证、形式验证、时序建模的论文

FF-DX半定制/全定制混合设计流程中功能与时序验证摘要随着集成电路的规模和复杂度不断增大,验证的作用越来越重要。

要在较短的时间内保证芯片最终能正常工作,需要将各种验证方法相结合,全面充分地验证整个系统。

FF-DX是一款高性能定点DSP,为了在提升芯片性能的同时,缩短设计周期,降低开发成本,采用了半定制/全定制混合设计的方法,对RTL级代码进行优化改进,对处理器内核的执行单元采用全定制设计实现。

混合设计的复杂性,给验证工作带来了巨大的挑战。

本文针对半定制/全定制混合设计的特点,提出并实现了一套半定制/全定制混合设计流程中功能和时序验证的方法。

论文从模拟验证、等价性验证和全定制设计的功能验证三个方面对FF-DX的分支控制部件进行功能验证。

对于模拟验证中激励的产生,采用了手工生成和伪随机生成相结合的方法,并通过覆盖率评估,使设计的代码覆盖率达到98%。

对于全定制模块,采用了NC-Verilog模拟器和功能模型提取工具TranSpirit相结合的新方法,提高了验证效率。

论文还研究了运用形式验证的方法对RTL级和RTL级以及RTL级和门级网表进行等价性验证。

为了进一步保证RTL级设计和对应的全定制设计模块之间功能的等价性,设计了一个能同时考察两种设计的验证平台,以此来提高工作效率。

论文介绍了FF-DX地址计算部件的时序建模和静态时序分析方法。

在静态时序分析之后,将SDF文件中的延时信息反标到逻辑网表中,通过动态时序验证进一步保证设计的时序收敛。

论文还结合工程任务,设计实现了验证过程中使用的几种辅助工具,大大提高了验证的效率,减少了人工参与带来的失误。

运用上述验证方法对FF-DX功能部件进行验证,取得了较好的效果,缩短了验证周期,提高了验证效率。

主题词:半定制/全定制混合设计,功能验证,形式验证,时序验证,时序模型,静态时序分析,辅助工具ABSTRACTThe complexity and size of the modern VLSI has been increasing dramatically, which present a significant challenge for verification. In order to ensure proper function of the design, various methods need to be used to verify the entire system sufficiently.FF-DX, a high-performance fix-point DSP our group designed, has adopted several design methods to enhance performance, as well as cut down design cycle and lower the cost. The most featured one is what we called blended methodology which mixes semi-custom and full-custom design methods together. Nevertheless, this methodology has led to a huge challenge to verification because of the complexity it brings in. In this dissertation, based on the characteristics of the blended methodology, we propose a flow for functional and timing verification, with the novel idea of combining full-custom and semi-custom verification methods.We verify the branch control function unit in three aspects, simulation verification, equivalence verification, together with functional verification in the full-custom designs.A blended methodology is introduced to generate the testbench for functional verification, which combines both manual and pseudo-random methods, and after evaluation, the code coverage rate is 98%. We also adopt a new methodology of combining the NC-Verilog simulator with functional model extractor TranSpirit for full-custom block ,and it speed up verification efficiency. Besides, we studied equivalence verification, a formal verification methodology which is used for RTL-RTL and RTL-gate design. To guarantee the functional equivalence between RTL design and full-custom design further, we design a testbench which can verify the two designs at the same time and it can greatly improve efficiency.This paper introduces a methodology of timing modeling and STA in FF-DX core. After STA, we backanotate the delay info into the logical netlist, then the timing closure could be assured further by another dynamic timing analysis.To meet the requirement of out project, we design several tools which are used in verification. These tools greatly enhance the efficiency of verification, as well as reduce the man-made errors.We use the above methods to finish verification of the core module of FF-DX, which effectively shorten design cycle, and speed up verification efficiency.Key Words:Semi-custom/Full-custom Mixed Design, Functional Verification, Formal Verification, Timing Verification, Timing Model, Static Timing Analysis, Aiding Tool第一章绪论当今集成电路技术的高速发展以及所取得的巨大成就,使得集成电路系统的规模和复杂度日趋提高,以微处理器为代表的集成电路技术已经对整个社会产生了广泛地影响,成为信息社会的支柱产业之一。

形式检测报告

形式检测报告形式检测报告是一种评估和分析文本是否存在抄袭、篡改、造假等不当行为的工具。

这种报告可以为教育机构、出版社和企业等提供有价值的参考,以保证其所使用的文本的原创性和真实性。

本文将会介绍形式检测报告的作用和三个相关的案例。

形式检测报告的作用是帮助用户发现文本中的不当行为,例如抄袭和造假。

它可以检测出一篇文本与其他文本的相似度,并标示出两者之间的相似处。

检测结果可以提供给用户有关文本相似度的详细分析,帮助用户分析其文本是否存在不当行为。

此外,形式检测报告还可以帮助用户评估文本的可靠度和原创性,从而使用户更好地使用这些文本。

以下是三个形式检测报告的案例:1.学术作品检测学校和大学通常使用形式检测报告来检测学术作品是否存在抄袭和造假行为。

学术作品是需要严谨、高质量的,因此,在这方面要求的标准也更高。

通过形式检测报告,学校可以确保其学生的学术作品原创性,同时还可以帮助学生学会如何遵守学术道德规范。

2.出版业检测出版公司可以使用形式检测报告帮助其评估所出版的作品的原创性和可靠度。

它可以将一本书的文本与在线数据库中的其他文本进行比较,并标记出其中的相似之处。

这可以帮助出版商更好地了解所使用的文本的真实性,并确保其读者可以信任其所发布的文本。

3.企业申请检测企业在各种场合下需要写报告、提案和申请书,并经常需要使用其他来源的信息作为参考。

在这种情况下,企业可以使用形式检测报告来确保所提交的文本不会因存在抄袭行为而被拒绝。

通过形式检测工具,企业可以确保其文本的原创性和可靠性,从而提高其成功率。

总之,形式检测报告是检测文本是否存在不当行为的重要工具。

其作用是帮助用户发现文本中的不当行为、评估文本的可靠度和原创性,从而保证其可以更好地使用所提交的文本。

上述三个案例表明,形式检测报告可以为不同类型的用户提供有用的帮助,是一个非常有价值的工具。

除了上述三个案例之外,形式检测报告还可以在其他场合下使用。

例如,在科学研究中,形式检测报告可以帮助研究者评估其文献综述的原创性和准确性;在新闻出版中,形式检测报告可以检测新闻稿是否存在抄袭和篡改行为,从而确保新闻的可信度和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验七形式化验证工具Formality

班级:XX 姓名:XX 学号:XX

1 实验目标

了解Formality工具的工作流程;

了解Formality工具的调试流程;

熟悉使用脚本进行调试,并通过图形化界面进行调试形式化验证中的不匹配点;

2 实验任务

在GUI环境下,对方使用Formality进行形式化验证的环境;

在命令行运行模式下,根据实验指导书及示例工程完成对一个简单电路的形式化验证;

3 实验环境

安装远程访问工具Xmanager/Xwin-pro的PC机:1台/生;

Linux服务器

4 实验内容

4.1 Formality工具GUI使用

按照实验指导书中的步骤,以图形方式完成对测试用例的形式化环境建立,包括参考、被测设计,库文件导入等内容。

4.2 测试用例的Formality流程

(分析第一个TCL命令的作用,并结出对应结果)

5.思考问题

(说明在进行Formality的Debug过程中的问题及解决方法)。