计算机组成原理实验 总线与寄存器 PPT

合集下载

最新存储器与总线实验PPT课件

实验原理图

74LS245 通常用于数据的双向传送、缓冲和驱 动。

74LS245 通常用于数据的双向传送、缓冲和驱动。

74LS273

74LS273是8位数据/地址锁存器 74LS273是一种带清除功能的8D触发器, 1D~8D为数据输入

端,1Q~8Q为数据输出端,CLK—上升沿触发 , CLRN—低电平 清除(即当为低电平时,芯片被清除,输出全为0(低电平) ), 常用作8位地址锁存器。

实验步骤:

• 内部总线数据写入存储器 给存储器的00、01、02、03、04地址单元 中分别写入数据11、12、13、14、15,具 体操作步骤如下:

实验步骤:

数据开关 (00000000)

CBA=000

存储器RAM (00010001)

LDAR=0 /CE=0 WE=1

按STEP

三态门 CBA=001 CE=1

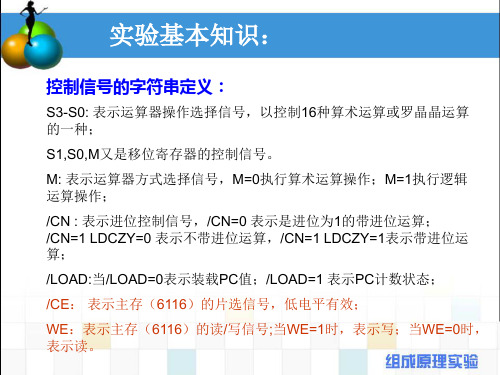

/LOAD:当/LOAD=0表示装载PC值;/LOAD=1 表示PC计数状态; /CE: 表示主存(6116)的片选信号,低电平有效; WE:表示主存(6116)的读/写信号;当WE=1时,表示写;当WE=0时, 表示读。

实验步骤:

• 完成上述连接,仔细检查无误后方可进入 本实验。

• 在闪动的“P.”状态下按动增址命令键,使 LED显示器自左向右第一位显示提示符 “H.”,表示本装置已进入手动单元实验状态。

/CE /OE /WE 方式 I/O 引 脚

H

X

X 未选中 高阻

(待用)

L

L

H

读出 Dout

L

X

L

写入

Din

数据收发器74LS245

74LS245是一种三态输出的8总线收发器。该收 发器有16个双向传送的数据端,即A1-A8,B1- B8,另有两个控制端-使能端,方向控制端DIR, 该芯片的功能见表 。

计算机组成原理实验2.1总线与寄存器

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1,#SW_BUS=0;启动仿 真,通过拨码开关送入总线BUS任意八位二进制数,赋值 74LS194的输入端D0D1D2D3。按照后页的逻辑功能表置位 74LS194的MR、S1、S0 、SL、SR端,观察并记录CLK端上升 沿和下降沿跳变时刻输出端Q0Q1Q2Q3的状态。

2) 令#SW_BUS=0,三态门74LS244导通,记录BUS总线上的数 据,与总线BIN相比较:

BUS_7 BUS_6 BUS_5 BUS_4 BUS_3 BUS_2 BUS_1 BUS_0 BUS总线

单位D触发器:74LS74 四位D触发器:74LS175

D触发器逻辑功能 表

【2】D触发器实验(一Fra bibliotek总线与寄存器 实验 电路图

三态门74LS244

拨码开关与总线缓冲器(注意观察74LS244左右电平)

【1】总线实验

实验步骤:

1) #SW_BUS = #R0_BUS= #DR_BUS= #SFT_BUS=1;启动仿真, 手动拨码开关在总线DIN上置位数据0x55。比较拨码开关 所在的总线DIN与总线BUS上的数据。

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1, #SW_BUS=0,启动 仿真,手动拨码开关输入数据到BUS总线,改变74LS74的 D端(即BUS总线的BUS_0)状态,按照后页逻辑功能表置 位74LS74的#Sd端、#Rd端,观察并记录CLK端上升沿 、 下降沿跳变时刻的Q端和#Q端状态。

的0xAA数据存入DR。观察寄存器74LS273的输出端。 6) 再令#R0_BUS=1;观察寄存器74LS374的输出端,请比较器

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1,#SW_BUS=0;启动仿 真,通过拨码开关送入总线BUS任意八位二进制数,赋值 74LS194的输入端D0D1D2D3。按照后页的逻辑功能表置位 74LS194的MR、S1、S0 、SL、SR端,观察并记录CLK端上升 沿和下降沿跳变时刻输出端Q0Q1Q2Q3的状态。

2) 令#SW_BUS=0,三态门74LS244导通,记录BUS总线上的数 据,与总线BIN相比较:

BUS_7 BUS_6 BUS_5 BUS_4 BUS_3 BUS_2 BUS_1 BUS_0 BUS总线

单位D触发器:74LS74 四位D触发器:74LS175

D触发器逻辑功能 表

【2】D触发器实验(一Fra bibliotek总线与寄存器 实验 电路图

三态门74LS244

拨码开关与总线缓冲器(注意观察74LS244左右电平)

【1】总线实验

实验步骤:

1) #SW_BUS = #R0_BUS= #DR_BUS= #SFT_BUS=1;启动仿真, 手动拨码开关在总线DIN上置位数据0x55。比较拨码开关 所在的总线DIN与总线BUS上的数据。

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1, #SW_BUS=0,启动 仿真,手动拨码开关输入数据到BUS总线,改变74LS74的 D端(即BUS总线的BUS_0)状态,按照后页逻辑功能表置 位74LS74的#Sd端、#Rd端,观察并记录CLK端上升沿 、 下降沿跳变时刻的Q端和#Q端状态。

的0xAA数据存入DR。观察寄存器74LS273的输出端。 6) 再令#R0_BUS=1;观察寄存器74LS374的输出端,请比较器

计算机组成原理第7章系统总线课件

7.1 总线概述

7.1.1 总线的基本概念

总线宽度:指一次并行传输的信息位数。 总线频率:指总线工作时每秒内能传输数据的次数。 传输率:指每秒能够传输的字节数,用MB/s表示。

传输率和总线宽度、总线频率之间的关系是: 传输率=总线宽度/8×总线频率

7.1 总线概述

7.1.2 总线的工作原理

总线是以分时的方法来为多个部件服务的,但是在任意时刻只 为某两个部件或设备所占用。当总线上的一个部件要与另一个部件 进行通信时,首先应该发出总线请求信号。在某一时刻,可能会有 多个部件同时要求使用总线,总线控制机构根据一定的判决原则, 决定首先由哪个部件使用总线。只有获得了总线控制权的部件,才 能开始传送数据。此时发送信息的总线主部件分时的将信息发往总 线,再由总线将这些信息同时发往各个接收信息的总线从部件。究 竟哪个部件接收信息,是由获得总线控制权的总线主部件给出的地 址信息经过译码之后产生的控制信号来决定。

7.1.3 总线的结构

7.1.4 总线的分类

指令系 统

吞吐量

最大存储 容量

分类

7.2 总线的控制与通信

7.2.1 总线的控制

总线在任意时刻只被某两个部件或设备所占用。当总线 上的一个部件要与另一个部件进行通信时,首先应该发出总 线请求信号。在某一时刻,可能会有多个部件同时要求使用 总线,总线控制机构根据一定的判决原则,决定首先由哪个 部件使用总线。只有获得了总线控制权的部件,才能开始传 送数据。获得总线控制权的部件被称为主部件,主部件一旦 获得总线控制权后,就立即开始向另一个部件进行一次信息 传送。负责接收信息的部件被称为从部件。

计数器的初始值还可以由程序来设置,这就可以方便地改变优先 次序,增加系统的灵活性。

7.2 总线的控制与通信

7.1.1 总线的基本概念

总线宽度:指一次并行传输的信息位数。 总线频率:指总线工作时每秒内能传输数据的次数。 传输率:指每秒能够传输的字节数,用MB/s表示。

传输率和总线宽度、总线频率之间的关系是: 传输率=总线宽度/8×总线频率

7.1 总线概述

7.1.2 总线的工作原理

总线是以分时的方法来为多个部件服务的,但是在任意时刻只 为某两个部件或设备所占用。当总线上的一个部件要与另一个部件 进行通信时,首先应该发出总线请求信号。在某一时刻,可能会有 多个部件同时要求使用总线,总线控制机构根据一定的判决原则, 决定首先由哪个部件使用总线。只有获得了总线控制权的部件,才 能开始传送数据。此时发送信息的总线主部件分时的将信息发往总 线,再由总线将这些信息同时发往各个接收信息的总线从部件。究 竟哪个部件接收信息,是由获得总线控制权的总线主部件给出的地 址信息经过译码之后产生的控制信号来决定。

7.1.3 总线的结构

7.1.4 总线的分类

指令系 统

吞吐量

最大存储 容量

分类

7.2 总线的控制与通信

7.2.1 总线的控制

总线在任意时刻只被某两个部件或设备所占用。当总线 上的一个部件要与另一个部件进行通信时,首先应该发出总 线请求信号。在某一时刻,可能会有多个部件同时要求使用 总线,总线控制机构根据一定的判决原则,决定首先由哪个 部件使用总线。只有获得了总线控制权的部件,才能开始传 送数据。获得总线控制权的部件被称为主部件,主部件一旦 获得总线控制权后,就立即开始向另一个部件进行一次信息 传送。负责接收信息的部件被称为从部件。

计数器的初始值还可以由程序来设置,这就可以方便地改变优先 次序,增加系统的灵活性。

7.2 总线的控制与通信

计算机组成原理(总线实验)

计算机组成原理实验

西工大软件学院 李易

实验前知识

• 总线的基本概念 总线是计算机系统的重要组成部分,它将各个部 件连接在一起组成计算机系统,并为部件之间信息 传送提供公共的信息通路。 • 总线的组成 总线是由传输线(地址总线、数据总线、控制总 线)、总线接口和总线仲裁部件三部分构成。 • 常用的总线 常用的总线有ISA,EISA , MCA , SCSI , VL-BUS ,PCI等 。

实验二 系统总线

• • U51 74LS245 三态门 SW-B 门控信号,低有效 U37 74LS273 地址寄存器 LDAR 地址寄存器门控信号,高有效 T3 正向脉冲时,可锁存地址 U52 6264 主存储器单元 WE 读写信号 CE 存储器片选信号,低有效 寄存器单元 R0-B R0寄存器片选信号 LDR0 保存总线上的数据 数码管显示单元LED LED-B 数码管选择信号 W/R 总线上的数据显示在数码管上

实验前知识

• 总线的两个特点: 分时与共享 分时 是指同一总线在同一时刻,只能有一个部件 占领总线发送信息,其他部件要发送信息得在该 部件发送完并释放总线后才能申请使用,但同一 时刻可以有多个部件接收信息。 共享 是指在总线上可以挂接多个部件,它们都可 以使用这一信息通路来和其他部件传输信息。

实验前知识

实验二 系统总线

• 实验步骤

(1)送数据63到寄存器R0; (2)数据20送地址寄存器; (3)然后将R0寄存器中的数送入 存储器; (4)将存储器的内容输出到LED 上显示,

实验二 系统总线

KD7-KD0 01100011 数据开关置数 SWB=0 LDR0= 开输入三态门 存入寄存器R0

送数据63到寄存器 送数据 到寄存器R0 到寄存器

西工大软件学院 李易

实验前知识

• 总线的基本概念 总线是计算机系统的重要组成部分,它将各个部 件连接在一起组成计算机系统,并为部件之间信息 传送提供公共的信息通路。 • 总线的组成 总线是由传输线(地址总线、数据总线、控制总 线)、总线接口和总线仲裁部件三部分构成。 • 常用的总线 常用的总线有ISA,EISA , MCA , SCSI , VL-BUS ,PCI等 。

实验二 系统总线

• • U51 74LS245 三态门 SW-B 门控信号,低有效 U37 74LS273 地址寄存器 LDAR 地址寄存器门控信号,高有效 T3 正向脉冲时,可锁存地址 U52 6264 主存储器单元 WE 读写信号 CE 存储器片选信号,低有效 寄存器单元 R0-B R0寄存器片选信号 LDR0 保存总线上的数据 数码管显示单元LED LED-B 数码管选择信号 W/R 总线上的数据显示在数码管上

实验前知识

• 总线的两个特点: 分时与共享 分时 是指同一总线在同一时刻,只能有一个部件 占领总线发送信息,其他部件要发送信息得在该 部件发送完并释放总线后才能申请使用,但同一 时刻可以有多个部件接收信息。 共享 是指在总线上可以挂接多个部件,它们都可 以使用这一信息通路来和其他部件传输信息。

实验前知识

实验二 系统总线

• 实验步骤

(1)送数据63到寄存器R0; (2)数据20送地址寄存器; (3)然后将R0寄存器中的数送入 存储器; (4)将存储器的内容输出到LED 上显示,

实验二 系统总线

KD7-KD0 01100011 数据开关置数 SWB=0 LDR0= 开输入三态门 存入寄存器R0

送数据63到寄存器 送数据 到寄存器R0 到寄存器

计算机组成原理课件-总线

• 保證主記憶體-處理器之間的高帶寬

– 直接和處理器連接 – 優化處理使之適應Cache塊傳送

• 輸入/輸出匯流排(行業標準)

– 通常距離較長,速度較慢 – 需要適應多種輸入/輸出設備 – 和處理器-主存匯流排通過橋連接(或通過主板匯流排)

• 主板匯流排(行業標準或專門設計)

– 主板:連接各部件器件的底盤 – 應允許處理器、主記憶體和輸入/輸出設備互連 – 應有價格優勢:所有組件連接在一條匯流排上

3. 主存發現ReadReq信號為低,將 Ack信號置低

4. 主存讀出數據後,將數據送匯流排,並將DataRdy置高

5. 外部設備發現DataRdy為高,讀數據,併發出Ack信號

6. 主存發現Ack為高,將DataRdy拉低,並釋放數據線

7. 外部設備發現DataRdy為低,拉低 Ack信號,指示傳送結束

• 匯流排事務包括兩個部分:

– 發起命令 (和地址) – 傳輸數據

• 主設備是匯流排事務的發起者:

– 發出命令(和地址)

• 從設備是匯流排事務的回應者:

– 若主設備發出的是讀命令,則將數據發送到主設備 – 否則,接收主設備發來的寫入數據

匯流排類型

• 處理器-主存匯流排 (專用)

– 傳輸距離短、速度高 – 主記憶體專用

I/O controller

Disk

Disk

Graphics output

Network

• 輸入/輸出系統設計受到多方面因素的影響(可擴展性,可恢復性等) • 性能:

— 訪問延遲 — 吞吐量 — 設備和系統的連接關係 — 層次存儲系統 — 操作系統 • 用戶和應用也各不相同

輸入/輸出系統

• 設備用於人機交互 • 匯流排定義了交互的

– 直接和處理器連接 – 優化處理使之適應Cache塊傳送

• 輸入/輸出匯流排(行業標準)

– 通常距離較長,速度較慢 – 需要適應多種輸入/輸出設備 – 和處理器-主存匯流排通過橋連接(或通過主板匯流排)

• 主板匯流排(行業標準或專門設計)

– 主板:連接各部件器件的底盤 – 應允許處理器、主記憶體和輸入/輸出設備互連 – 應有價格優勢:所有組件連接在一條匯流排上

3. 主存發現ReadReq信號為低,將 Ack信號置低

4. 主存讀出數據後,將數據送匯流排,並將DataRdy置高

5. 外部設備發現DataRdy為高,讀數據,併發出Ack信號

6. 主存發現Ack為高,將DataRdy拉低,並釋放數據線

7. 外部設備發現DataRdy為低,拉低 Ack信號,指示傳送結束

• 匯流排事務包括兩個部分:

– 發起命令 (和地址) – 傳輸數據

• 主設備是匯流排事務的發起者:

– 發出命令(和地址)

• 從設備是匯流排事務的回應者:

– 若主設備發出的是讀命令,則將數據發送到主設備 – 否則,接收主設備發來的寫入數據

匯流排類型

• 處理器-主存匯流排 (專用)

– 傳輸距離短、速度高 – 主記憶體專用

I/O controller

Disk

Disk

Graphics output

Network

• 輸入/輸出系統設計受到多方面因素的影響(可擴展性,可恢復性等) • 性能:

— 訪問延遲 — 吞吐量 — 設備和系統的連接關係 — 層次存儲系統 — 操作系統 • 用戶和應用也各不相同

輸入/輸出系統

• 設備用於人機交互 • 匯流排定義了交互的

计算机组成原理(本全PPT)

应用

用作固件存储,如BIOS、固件等。

外存储器

特点

容量大、价格低、速度慢、数据可长期保存。

分类

机械硬盘(HDD)和固态硬盘(SSD)。

外存储器

应用

作为计算机的主要存储设备。

特点

容量大、价格低、速度慢、数据可长期保存。

外存储器

分类

CD、DVD和蓝光光盘等。

应用

用于数据备份和存储。

高速缓存(Cache)

址和控制信号。

总线按照传输信号类型可以分为 数据总线、地址总线和控制总线。

总线按照连接部件可以分为内部 总线和外部总线,内部总线连接 计算机内部各部件,外部总线连

接计算机与外部设备。

主板的结构与功能

主板的结构包括

处理器插座、内存插槽、扩展插槽、硬盘接口、电源接 口等。

主板的功能包括

提供各部件之间的连接,实现数据传输和控制信号传递 ;保障系统的稳定性和可靠性;提供系统扩展能力。

I/O数据传输方式

优点

CPU可以执行其他任务,适用于高速I/O 设备。

VS

缺点

需要设置中断控制器,实现起来较为复杂 。

I/O数据传输方式

优点

CPU不直接参与数据传输,适用于大数据块 传输。

缺点

需要设置DMA控制器,成本较高。

I/O设备控制方式

要点一

优点

简单、易于实现。

要点二

缺点

CPU效率低下,适用于慢速I/O设备。

计算机组成原理(本全ppt)

• 计算机系统概述 • 中央处理器(CPU) • 存储器系统 • 输入输出系统(I/O) • 总线与主板 • 计算机系统性能评价与优化

01

计算机系统概述

计算机的发展历程

用作固件存储,如BIOS、固件等。

外存储器

特点

容量大、价格低、速度慢、数据可长期保存。

分类

机械硬盘(HDD)和固态硬盘(SSD)。

外存储器

应用

作为计算机的主要存储设备。

特点

容量大、价格低、速度慢、数据可长期保存。

外存储器

分类

CD、DVD和蓝光光盘等。

应用

用于数据备份和存储。

高速缓存(Cache)

址和控制信号。

总线按照传输信号类型可以分为 数据总线、地址总线和控制总线。

总线按照连接部件可以分为内部 总线和外部总线,内部总线连接 计算机内部各部件,外部总线连

接计算机与外部设备。

主板的结构与功能

主板的结构包括

处理器插座、内存插槽、扩展插槽、硬盘接口、电源接 口等。

主板的功能包括

提供各部件之间的连接,实现数据传输和控制信号传递 ;保障系统的稳定性和可靠性;提供系统扩展能力。

I/O数据传输方式

优点

CPU可以执行其他任务,适用于高速I/O 设备。

VS

缺点

需要设置中断控制器,实现起来较为复杂 。

I/O数据传输方式

优点

CPU不直接参与数据传输,适用于大数据块 传输。

缺点

需要设置DMA控制器,成本较高。

I/O设备控制方式

要点一

优点

简单、易于实现。

要点二

缺点

CPU效率低下,适用于慢速I/O设备。

计算机组成原理(本全ppt)

• 计算机系统概述 • 中央处理器(CPU) • 存储器系统 • 输入输出系统(I/O) • 总线与主板 • 计算机系统性能评价与优化

01

计算机系统概述

计算机的发展历程

计算机组成原理(第4版)课件第7章 总线(第4版)

33

7.4 总线标准

总线的标准制定通常有两种途径,一 种是由具有权威性的国际标准化组织制定 并推荐使用的,称为正式标准;另一种是 由某个或某几个在业界具有影响力的设备 制造商提出,而又被业内其他厂家认可并 广泛使用的标准,即所谓事实标准,这些 标准可能需要经过一段时间的使用,被厂 商提供给有关组织讨论之后才能成为正式 标准。

8

2.总线事务

通常把在总线上一对设备之间的一次信

息交换过程称为一个“总线事务”,把发出

总线事务请求的部件称为主设备,与主设备

进行信息交换的对象称为从设备。例如CPU

要求读取存储器中某单元的数据,则CPU是

主设备,而存储器是从设备。总线事务类型

通常根据它的操作性质来定义,典型的总线

事务类型有“存储器读”、“存储器写”、

34

7.4.1 系统总线标准

通常,微机的系统总线都做成多个插 槽的形式,各插槽引脚通过总线连在一起。 总线接口引脚的定义、传输速率的设定、 驱动能力的限制、信号电平的规定、时序 的安排以及信息格式的约定等,都有统一 的标准。

35

7.4.1 系统总线标准(续)

1.PC/XT总线

PC/XT总线是早期PC/XT微机所配备 的系统总线,是9位总线标准。

5

7.1 总线概述

总线是一组能为多个部件分时共享的 公共信息传送线路。共享是指总线上可以 挂接多个部件,各个部件之间相互交换的 信息都可以通过这组公共线路传送;分时 是指同一时刻总线上只能传送一个部件发 送的信息。

6

7.1 .1 总线的基本概念

总线采用分时共享技术,当总线空闲 (所有部件都以高阻状态连接在总线上) 时,如果有一个部件要与目的部件通信, 则发起通信的部件驱动总线,发出地址和 数据。其他以高阻状态连接在总线上的部 件如果收到与自己相符的地址信息后,即 接收总线上的数据。发送部件完成通信后, 将总线让出(输出变为高阻态)。

7.4 总线标准

总线的标准制定通常有两种途径,一 种是由具有权威性的国际标准化组织制定 并推荐使用的,称为正式标准;另一种是 由某个或某几个在业界具有影响力的设备 制造商提出,而又被业内其他厂家认可并 广泛使用的标准,即所谓事实标准,这些 标准可能需要经过一段时间的使用,被厂 商提供给有关组织讨论之后才能成为正式 标准。

8

2.总线事务

通常把在总线上一对设备之间的一次信

息交换过程称为一个“总线事务”,把发出

总线事务请求的部件称为主设备,与主设备

进行信息交换的对象称为从设备。例如CPU

要求读取存储器中某单元的数据,则CPU是

主设备,而存储器是从设备。总线事务类型

通常根据它的操作性质来定义,典型的总线

事务类型有“存储器读”、“存储器写”、

34

7.4.1 系统总线标准

通常,微机的系统总线都做成多个插 槽的形式,各插槽引脚通过总线连在一起。 总线接口引脚的定义、传输速率的设定、 驱动能力的限制、信号电平的规定、时序 的安排以及信息格式的约定等,都有统一 的标准。

35

7.4.1 系统总线标准(续)

1.PC/XT总线

PC/XT总线是早期PC/XT微机所配备 的系统总线,是9位总线标准。

5

7.1 总线概述

总线是一组能为多个部件分时共享的 公共信息传送线路。共享是指总线上可以 挂接多个部件,各个部件之间相互交换的 信息都可以通过这组公共线路传送;分时 是指同一时刻总线上只能传送一个部件发 送的信息。

6

7.1 .1 总线的基本概念

总线采用分时共享技术,当总线空闲 (所有部件都以高阻状态连接在总线上) 时,如果有一个部件要与目的部件通信, 则发起通信的部件驱动总线,发出地址和 数据。其他以高阻状态连接在总线上的部 件如果收到与自己相符的地址信息后,即 接收总线上的数据。发送部件完成通信后, 将总线让出(输出变为高阻态)。

存储器和总线实验..26页PPT

文 家 。汉 族 ,东 晋 浔阳 柴桑 人 (今 江西 九江 ) 。曾 做过 几 年小 官, 后辞 官 回家 ,从 此 隐居 ,田 园生 活 是陶 渊明 诗 的主 要题 材, 相 关作 品有 《饮 酒 》 、 《 归 园 田 居 》 、 《 桃花 源 记 》 、 《 五 柳先 生 传 》 、 《 归 去来 兮 辞 》 等 。

1

0

、

倚南窗以寄傲,审

容

膝

之

易

安

。

▪

26、要使整个人生都过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

存储器和总线实验..

6

、

露

凝

无

游

氛

,

天

高

风

景

澈

。

7、翩翩新 来燕,双双入我庐 ,先巢故尚在,相 将还旧居。

8

、

吁

嗟

身

后

名

,

于

我

若

浮

烟

。

9、 陶渊 明( 约 365年 —427年 ),字 元亮, (又 一说名 潜,字 渊明 )号五 柳先生 ,私 谥“靖 节”, 东晋 末期南 朝宋初 期诗 人、文 学家、 辞赋 家、散

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——达·芬奇

▪

30、意志是一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

谢谢!

26

1

0

、

倚南窗以寄傲,审

容

膝

之

易

安

。

▪

26、要使整个人生都过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

存储器和总线实验..

6

、

露

凝

无

游

氛

,

天

高

风

景

澈

。

7、翩翩新 来燕,双双入我庐 ,先巢故尚在,相 将还旧居。

8

、

吁

嗟

身

后

名

,

于

我

若

浮

烟

。

9、 陶渊 明( 约 365年 —427年 ),字 元亮, (又 一说名 潜,字 渊明 )号五 柳先生 ,私 谥“靖 节”, 东晋 末期南 朝宋初 期诗 人、文 学家、 辞赋 家、散

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——达·芬奇

▪

30、意志是一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

谢谢!

26

总线和寄存器内容74页PPT

总线和寄存器内容

11、获得的成功越大,就越令人高兴 。野心 是使人 勤奋的 原因, 节制使 人枯萎 。 12、不问收获,只问耕耘。如同种树 ,先有 根茎, 再有枝 叶,尔 后花实 ,好好 劳动, 不要想 太多, 那样只 会使人 胆孝懒 惰,因 为不实 践,甚 至不接 触社会 ,难道 你是野 人。(名 言网) 13、不怕,不悔(虽然只有四个字,但 常看常 新。 14、我在心里默默地为每一个人祝福 。我爱 自己, 我用清 洁与节 制来珍 惜我的 身体, 我用智 慧和知 识充实 我的头 脑。 15、这世上的一切都借希望而完成。 农夫不 会播下 一粒玉 米,如 果他不 曾希望 它长成 种籽; 单身汉 不会娶 妻,如 果他不 曾希望 有小孩 ;商人 或手艺 人不会 工作, 如果他 不曾希 望因此 而有收 益。-- 马钉路 德。

16、业余生活要有意义,不要越轨。——华盛顿 17、一个人即使已登上顶峰,也仍要自强不息。——罗素·贝克 18、最大的挑战和突破在于用人,而用人最大的突破在于信任人。——马云 19、自己活着,就是为了使别人过得更美好。——雷锋 20、要掌握书,莫被书掌握;要为生而读,莫为

11、获得的成功越大,就越令人高兴 。野心 是使人 勤奋的 原因, 节制使 人枯萎 。 12、不问收获,只问耕耘。如同种树 ,先有 根茎, 再有枝 叶,尔 后花实 ,好好 劳动, 不要想 太多, 那样只 会使人 胆孝懒 惰,因 为不实 践,甚 至不接 触社会 ,难道 你是野 人。(名 言网) 13、不怕,不悔(虽然只有四个字,但 常看常 新。 14、我在心里默默地为每一个人祝福 。我爱 自己, 我用清 洁与节 制来珍 惜我的 身体, 我用智 慧和知 识充实 我的头 脑。 15、这世上的一切都借希望而完成。 农夫不 会播下 一粒玉 米,如 果他不 曾希望 它长成 种籽; 单身汉 不会娶 妻,如 果他不 曾希望 有小孩 ;商人 或手艺 人不会 工作, 如果他 不曾希 望因此 而有收 益。-- 马钉路 德。

16、业余生活要有意义,不要越轨。——华盛顿 17、一个人即使已登上顶峰,也仍要自强不息。——罗素·贝克 18、最大的挑战和突破在于用人,而用人最大的突破在于信任人。——马云 19、自己活着,就是为了使别人过得更美好。——雷锋 20、要掌握书,莫被书掌握;要为生而读,莫为

计算机组成原理第1章系统总线.ppt

3.2

3.通信总线

用于 计算机系统之间 或 计算机系统 与其他系统(如控制仪表、移动通信等) 之间的通信

传输方式

串行通信总线 并行通信总线

3.3 总线特性及性能指标

一、总线物理实现

CPU 插板

主存 插板

I/O 插板

BUS

主板

二、总线特性

3.3

1. 机械特性 尺寸、形状、管脚数 及 排列顺序

2. 电气特性 3. 功能特性

6. 总线控制方式 并发、自动、仲裁、逻辑、计数

7. 其他指标

负载能力

四、总线标准

3.3

ISA

模块 标 模块

EISA

准

总 线

VESA(LV-BUS)

界

标 PCI

系统 面

系统 准 AGP

RS-232

USB

四、总线标准

3.3

总线标准 ISA EISA VESA

(VL-BUS) PCI

AGP

RS-232

3.5

数据线

总

线

控

制

BG0

部

BR0

BG1 BR1

BGn BRn

地址线

件

I/O接口0 I/O接口1 … I/O接口n

排队器

二、总线通信控制

3.5

1. 目的 解决通信双方 协调配合 问题

2. 总线传输周期

申请分配阶段 主模块申请,总线仲裁决定

寻址阶段

主模块向从模块 给出地址 和 命令

CPU

主存

I/O 设备1

I/O接口 … I/O接口

I/O 设备2

…

I/O 设备n

二、多总线结构

3.4

1. 双总线结构

计算机组成原理教学课件 第8章总线

反映了系统的规模;

线 类上型使。用的电源钟信控号制、总中线断(信c号on、troDl MbuAs控)制。信可号以、传仲送裁各信种号控等制。信号,如时

8.1.3 总 线 的 组 成 及 性 能 指 标

8.1 总线概述

2)总线的信息传送过程

(1)总线请求和仲裁过程。总线主控器接收总线请求 信号,通过仲裁过程,决定在下一个总线操作周期中进行 通信的部件;

8.1.2 总 线 的 分 类

8.1 总线概述

图8-3 三总线结构

8.1.2 总 线 的 分 类

8.1 总线概述

3)总线层次结构

(1)

(2)

局部总线

微处理器总线

(3)

系统总线

(( 4)

外部总线

8.1.2 总 线 的 分 类

8.1 总线概述

1) 总线的组成

总线实现的功能是各部件的互连

(1)

和通信。通信的信息一般有数据、地

第8章 总 线

通过这种外部扩展所形成的应用系统之间以及应用系统内部之间都需 要进行某些信息的相互传送,才能实现所期望的功能。那么,这就不可避 免的出现了应用系统之间以及应用系统内部之间的通信问题。总线即为实 现此类通信的有效方式。本章主要介绍总线的相关概念以及总线的实现方 式,即总线控制与通信。

8.1 总线概述

8.3 仲裁操作与定时

图8-12 异步总线传输读操作时序

8.3. 异 步 定 时 方 式

8.3 仲裁操作与定时

对于写操作而言,实现逻辑与写操作很相似,都是利用 请求和应答信号来促进信息的异步传输的。其实现逻辑如下 图所示,也以序号来描述其工作过程。其中,低电平表示信 息有效。

8.3. 异 步 定 时 方 式

计算机组成原理ppt课件

常见输入输出接口类型和特点比较

要点一

常见输入输出接口类型

要点二

特点比较

常见的输入输出接口类型包括PS/2接口、USB接口、HDMI 接口、DisplayPort接口、SATA接口等。

不同的输入输出接口类型具有不同的特点,如传输速度、支 持热插拔、连接方式等。例如,USB接口支持热插拔和即插 即用,而SATA接口则主要用于连接硬盘和光驱等存储设备。

定点数表示与运算方法

定点数表示方法

阐述定点数的表示方法,包括符号位、 数值位等,并介绍定点数的范围及精 度。

定点数加减运算

详细讲解定点数的加减运算方法,包 括补码加减运算等。

定点数乘除运算

介绍定点数的乘除运算方法,包括原 码乘除、补码乘除等算法。

定点数运算器的设计

阐述定点数运算器的设计原理和实现 方法,包括加法器、减法器、乘法器 和除法器等。

当中断发生时,计算机首先保存当前程序的执行状态,然后转去执行中断处理程序。中断处理程序执行完毕 后,计算机再返回原程序继续执行。这个过程需要由计算机的操作系统来管理和控制。

THANK YOU

指令系统设计原则和优化策略

有效性原则

指令系统应能有效地支持高级 语言的实现,提高程序执行效 率。

兼容性原则

新设计的指令系统应尽可能与 已有的指令系统保持兼容。

完备性原则

指令系统应满足程序设计的各 种需求,具备完备性。

规整性原则

指令系统应尽可能规整,简化 硬件实现和软件编程。

优化策略

采用流水线技术、超标量技术、 乱序执行技术等优化策略,提 高指令执行速度和效率。

高速缓冲存储器(Cache)原理及应用

Cache原理

Cache是一种高速缓冲存储器,它位于CPU和内存之间,用于存储CPU最近访问过的数 据和指令。通过Cache技术,可以提高CPU访问内存的效率和速度。

总线和寄存器内容74页PPT

xiexie! 38、我这个人走得很慢,但是我从不后退。——亚伯拉罕·林肯

39、勿问成功的秘诀为何,且尽全力做你应该做的事吧。——美华纳

40、学而不思则罔,思而不学则殆。——孔子

•

30、风俗可以造就法律,也可以废除 法律。6、自己的鞋子,自己知道紧在哪里。——西班牙

37、我们唯一不会改正的缺点是软弱。——拉罗什福科

•

26、我们像鹰一样,生来就是自由的 ,但是 为了生 存,我 们不得 不为自 己编织 一个笼 子,然 后把自 己关在 里面。 ——博 莱索

•

27、法律如果不讲道理,即使延续时 间再长 ,也还 是没有 制约力 的。— —爱·科 克

•

28、好法律是由坏风俗创造出来的。 ——马 克罗维 乌斯

•

29、在一切能够接受法律支配的人类 的状态 中,哪 里没有 法律, 那里就 没有自 由。— —洛克

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

● 为何常见的CPU都是8位、16位或32位总线?可以使用7位或 10位的总线么?计算机总线的位数是由什么决定的? 32位 CPU是否一定比8位CPU的处理能力强?

● 74LS194的SL端和SR端是提供D0D1D2D3端移入数据还是保存 D0D1D2D3端移出数据?假设要保存74LS194的D0D1D2D3端移出 的数据,该怎么修改寄存器电路?

8) 假设手动拨码开关分别打入数据0xAA和0x55到R0寄存器 (74LS374)和DR寄存器(74LS273),并且同时令 #R0_BUS=0和#DR_BUS= 0,会出现什么情况?在总线上可以 同时选择多个寄存器输出(导通输出端三态门)么?

四位双向移位寄存器 74LS194

【4】移位寄存器实验

计算机组成原理实验 总线与寄存器

(一)总线与寄存器 实验

实验目的:

● 掌握总线以及数据通路的概念及传输特性。 ● 理解锁存器、通用寄存器及移位寄存器的组成和功能。

实验内容:

● 构建一条8位总线的寄存器数据通路,将若干寄存器通过总 线连接起来。

● 通过拨码开关手动输入数据到某个寄存器;或者从一个寄 存器向另一个寄存器赋值。同时,利用移位寄存器实现数 据的置数、左移、右移等功能。

2) 手动拨码开关输入数据到BUS总线,使74LS175的D端(即 BUS总线的BUS_0)分别接高,低电平,观察并记录CLK上 升沿 、下降沿跳变时刻的Q端、#Q端状态。观察当 74LS175的S175和74LS74的异同。

大家应该也有点累了,稍作休息

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1,#SW_BUS=0;启动仿 真,通过拨码开关送入总线BUS任意八位二进制数,赋值 74LS194的输入端D0D1D2D3。按照后页的逻辑功能表置位 74LS194的MR、S1、S0 、SL、SR端,观察并记录CLK端上升 沿和下降沿跳变时刻输出端Q0Q1Q2Q3的状态。

2) 令寄存器R0(74LS374)的R0_CLK端上升沿跳变,把总线上 的数据0xAA存入R0。

3) 令#SW_BUS=1,三态门74LS244阻断,观察总线BUS的状态。 4) 令#R0_BUS=0,74LS374输出选通,观察总线BUS的状态。 5) 令寄存器DR(74LS273)的DR_CLK端上升沿跳变,把总线上

● 把原码数据0x5A和0x9A分别加载到移位寄存器74LS194,然 后两个数据都分别执行一次“左移”(即“×2”乘法操 作)。请问哪个数据会出现错误?假设把补码数据0x5A和 0x9A加载到移位寄存器74LS194中,分别执行一次“左移” (即“×2”乘法操作),请问哪些数据会出现错误?

2) 令#SW_BUS=0,三态门74LS244导通,记录BUS总线上的数 据,与总线BIN相比较:

单位D触发器:74LS74 四位D触发器:74LS175

D触发器逻辑功能 表

【2】D触发器实验

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1, #SW_BUS=0,启动 仿真,手动拨码开关输入数据到BUS总线,改变74LS74的 D端(即BUS总线的BUS_0)状态,按照后页逻辑功能表置 位74LS74的#Sd端、#Rd端,观察并记录CLK端上升沿 、 下降沿跳变时刻的Q端和#Q端状态。

2) 移位寄存器74LS194的“左移”功能可以作为把寄存器存 储的8位二进制数据做“×2”的乘法操作;其“右移”功 能则作为把寄存器存储的8位二进制数据做“÷2”的除法 操作。请问在执行上述操作的过程中,74LS194的SL端和 SR端应该连接“1”还是“0” ?

(一)总线与寄存器 实验

思考题:

的0xAA数据存入DR。观察寄存器74LS273的输出端。 6) 再令#R0_BUS=1;观察寄存器74LS374的输出端,请比较器

件74LS244、74LS273和74LS374的异同。

【3】寄存器实验

实验步骤:

7) 手动拨码开关输入新数据0x55到总线BUS(#SW_BUS= 0)。 此时,新的数据会冲掉R0寄存器保存的原有数据0xAA么? 若再令#R0_BUS=0,会出现什么情况?

大家有疑问的,可以询问和交

74LS273&374 逻辑功能表

寄存器R0:74LS374 数据缓冲寄存器DR:74LS273

【3】寄存器实验

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1; #SW_BUS=0,启动仿 真,三态门74LS244导通,手动拨码开关输入数据0xAA 到 总线,观察此时寄存器74LS374和74LS273输出端的状态。

● 比较以下器件两两之间的异同:触发器74LS74和74LS175, 寄存器74LS273和74LS374,寄存器74LS273和移位寄存器 74LS194。

(一)总线与寄存器 实验 电路图

三态门74LS244

拨码开关与总线缓冲器(注意观察74LS244左右电平)

【1】总线实验

实验步骤:

1) #SW_BUS = #R0_BUS= #DR_BUS= #SFT_BUS=1;启动仿真, 手动拨码开关在总线DIN上置位数据0x55。比较拨码开关 所在的总线DIN与总线BUS上的数据。

● 74LS194的SL端和SR端是提供D0D1D2D3端移入数据还是保存 D0D1D2D3端移出数据?假设要保存74LS194的D0D1D2D3端移出 的数据,该怎么修改寄存器电路?

8) 假设手动拨码开关分别打入数据0xAA和0x55到R0寄存器 (74LS374)和DR寄存器(74LS273),并且同时令 #R0_BUS=0和#DR_BUS= 0,会出现什么情况?在总线上可以 同时选择多个寄存器输出(导通输出端三态门)么?

四位双向移位寄存器 74LS194

【4】移位寄存器实验

计算机组成原理实验 总线与寄存器

(一)总线与寄存器 实验

实验目的:

● 掌握总线以及数据通路的概念及传输特性。 ● 理解锁存器、通用寄存器及移位寄存器的组成和功能。

实验内容:

● 构建一条8位总线的寄存器数据通路,将若干寄存器通过总 线连接起来。

● 通过拨码开关手动输入数据到某个寄存器;或者从一个寄 存器向另一个寄存器赋值。同时,利用移位寄存器实现数 据的置数、左移、右移等功能。

2) 手动拨码开关输入数据到BUS总线,使74LS175的D端(即 BUS总线的BUS_0)分别接高,低电平,观察并记录CLK上 升沿 、下降沿跳变时刻的Q端、#Q端状态。观察当 74LS175的S175和74LS74的异同。

大家应该也有点累了,稍作休息

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1,#SW_BUS=0;启动仿 真,通过拨码开关送入总线BUS任意八位二进制数,赋值 74LS194的输入端D0D1D2D3。按照后页的逻辑功能表置位 74LS194的MR、S1、S0 、SL、SR端,观察并记录CLK端上升 沿和下降沿跳变时刻输出端Q0Q1Q2Q3的状态。

2) 令寄存器R0(74LS374)的R0_CLK端上升沿跳变,把总线上 的数据0xAA存入R0。

3) 令#SW_BUS=1,三态门74LS244阻断,观察总线BUS的状态。 4) 令#R0_BUS=0,74LS374输出选通,观察总线BUS的状态。 5) 令寄存器DR(74LS273)的DR_CLK端上升沿跳变,把总线上

● 把原码数据0x5A和0x9A分别加载到移位寄存器74LS194,然 后两个数据都分别执行一次“左移”(即“×2”乘法操 作)。请问哪个数据会出现错误?假设把补码数据0x5A和 0x9A加载到移位寄存器74LS194中,分别执行一次“左移” (即“×2”乘法操作),请问哪些数据会出现错误?

2) 令#SW_BUS=0,三态门74LS244导通,记录BUS总线上的数 据,与总线BIN相比较:

单位D触发器:74LS74 四位D触发器:74LS175

D触发器逻辑功能 表

【2】D触发器实验

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1, #SW_BUS=0,启动 仿真,手动拨码开关输入数据到BUS总线,改变74LS74的 D端(即BUS总线的BUS_0)状态,按照后页逻辑功能表置 位74LS74的#Sd端、#Rd端,观察并记录CLK端上升沿 、 下降沿跳变时刻的Q端和#Q端状态。

2) 移位寄存器74LS194的“左移”功能可以作为把寄存器存 储的8位二进制数据做“×2”的乘法操作;其“右移”功 能则作为把寄存器存储的8位二进制数据做“÷2”的除法 操作。请问在执行上述操作的过程中,74LS194的SL端和 SR端应该连接“1”还是“0” ?

(一)总线与寄存器 实验

思考题:

的0xAA数据存入DR。观察寄存器74LS273的输出端。 6) 再令#R0_BUS=1;观察寄存器74LS374的输出端,请比较器

件74LS244、74LS273和74LS374的异同。

【3】寄存器实验

实验步骤:

7) 手动拨码开关输入新数据0x55到总线BUS(#SW_BUS= 0)。 此时,新的数据会冲掉R0寄存器保存的原有数据0xAA么? 若再令#R0_BUS=0,会出现什么情况?

大家有疑问的,可以询问和交

74LS273&374 逻辑功能表

寄存器R0:74LS374 数据缓冲寄存器DR:74LS273

【3】寄存器实验

实验步骤:

1) 令#R0_BUS= #DR_BUS= #SFT_BUS=1; #SW_BUS=0,启动仿 真,三态门74LS244导通,手动拨码开关输入数据0xAA 到 总线,观察此时寄存器74LS374和74LS273输出端的状态。

● 比较以下器件两两之间的异同:触发器74LS74和74LS175, 寄存器74LS273和74LS374,寄存器74LS273和移位寄存器 74LS194。

(一)总线与寄存器 实验 电路图

三态门74LS244

拨码开关与总线缓冲器(注意观察74LS244左右电平)

【1】总线实验

实验步骤:

1) #SW_BUS = #R0_BUS= #DR_BUS= #SFT_BUS=1;启动仿真, 手动拨码开关在总线DIN上置位数据0x55。比较拨码开关 所在的总线DIN与总线BUS上的数据。