SPI数据格式

spi转串口芯片

spi转串口芯片SPI(Serial Peripheral Interface)是一种全双工、同步、串行的通信协议,常被用于连接微控制器或其他数字设备与外围设备,例如传感器、存储器、显示器等。

SPI 转串口芯片(SPI to UART Bridge)是一种集成了SPI接口和串口通信功能的芯片,可以实现SPI总线与串口之间的转换。

SPI 转串口芯片通常包含如下主要特点和功能:1. SPI接口:具有主/从模式选择和多主设备共享等特性,可以与其他SPI设备进行通信。

2. 串口接口:支持标准的RS232或RS485接口,用于与计算机或其他设备进行串口通信。

3. 数据格式转换:将SPI数据格式转换为串口数据格式,实现不同协议之间的数据转换。

4. 数据缓存:内置的数据缓存,可以在SPI和串口之间进行数据存储和传输,提高数据传输效率。

5. 时钟和波特率控制:支持可编程的时钟频率和串口波特率,以适应不同的通信速度需求。

6. 错误检测和纠正:具备错误检测和纠正功能,可以检测和校正通信中的数据传输错误。

7. 多种工作模式:支持多种工作模式,例如中断模式、DMA 模式等,以适应不同的应用场景。

8. 硬件流控制:支持硬件流控制功能,可以在数据传输中实现流量的控制和管理。

9. 低功耗设计:采用低功耗设计,提供省电和节能的功能。

10. 集成电路:通常SPI转串口芯片是单芯片集成电路,体积小、功耗低、集成度高,方便使用和集成到各种应用中。

通过SPI转串口芯片,用户可以方便地实现SPI总线与串口通信的转换,扩展了SPI设备的应用范围,并与其他数字设备进行数据交换和通信。

SPI转串口芯片广泛应用于工业自动化、通信设备、消费电子、仪器仪表等领域。

SPI简介

◆ SPI 工作原理总结① 硬件上为4根线。

② 主机和从机都有一个串行移位寄存器,主机通过向它的SPI 串行寄存器写入一个字节来发起一次传输。

③ 串行移位寄存器通过MOSI 信号线将字节传送给从机,从机也将自己的串行移位寄存器中的内容通过MISO 信号线返回给主机。

这样,两个移位寄存器中的内容就被交换。

④ 外设的写操作和读操作是同步完成的。

如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机的传输。

◆ SPI 接口简介SPI:Serial Peripheral interface 的缩写,顾名思义就是串行外围设备接口。

SPI ,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,主要应用在 EEPROM ,FLASH ,实时时钟,AD 转换器,还有数字信号处理器和数字信号解码器之间。

STM32F4 的 SPI 功能很强大, SPI 时钟最高可以到 37.5Mhz ,支持 DMA 。

◆ SPI 内部结构简明图移位寄存器移位寄存器SPI 时钟发生器MISO MOSI SCLKVDDCS CS主机(Master)从机(Slave)SPI 接口一般使用4条线通信:MISO 主设备数据输入,从设备数据输出。

MOSI 主设备数据输出,从设备数据输入。

SCLK 时钟信号,由主设备产生。

CS从设备片选信号,由主设备控制。

◆SPI接口框图⏹STM32 SPI接口可配置为支持SPI协议或者支持I2S音频协议,默认是SPI模式。

可以通过软件切换到I2S方式。

27.2.1 SPI 特性● 基于三条线的全双工同步传输● 基于双线的单工同步传输,其中一条可作为双向数据线● 8 位或16 位传输帧格式选择● 主模式或从模式操作● 多主模式功能● 8 个主模式波特率预分频器(最大值为f PCLK/2)● 从模式频率(最大值为f PCLK/2)● 对于主模式和从模式都可实现更快的通信● 对于主模式和从模式都可通过硬件或软件进行NSS 管理:动态切换主/从操作● 可编程的时钟极性和相位● 可编程的数据顺序,最先移位MSB或LSB● 可触发中断的专用发送和接收标志● SPI 总线忙状态标志● SPI TI 模式● 用于确保可靠通信的硬件CRC 功能:—在发送模式下可将CRC 值作为最后一个字节发送—根据收到的最后一个字节自动进行CRC 错误校验● 可触发中断的主模式故障、上溢和CRC 错误标志● 具有DMA 功能的1字节发送和接收缓冲器:发送和接收请求时钟相位和时钟极性通过SPI_CR1 寄存器中的CPOL 和CPHA 位,可以用软件选择四种可能的时序关系。

Micro SD 卡(TF卡) spi 模式实现方法

Micro SD 卡(TF卡)spi 模式实现方法现在我们手机的内存卡多为Micro SD卡,又叫TF卡,所以Micro SD卡比SD卡常见。

自己曾经也想写写SD卡的读取程序,但又不想特地再去买个SD卡,这时想起手机内存卡不是和SD卡很像吗?在网上查了以后发现SD卡和Micro SD卡其实也就大小和引脚不一样,它们的操作其实是一样的,所以网上的SD卡读写代码其实可以直接拿来用。

关于SD卡和Micro SD卡的引脚定义和不同可见下两表:我们可以发现Micro SD卡只有8个引脚是因为比SD卡少了一个Vss。

当然你也可以买个卡套套在Micro SD卡上,这样一来大小就和SD卡一样大,这时候卡套上的9个引脚就和SD卡一样了,你可以完全当做SD卡来操作。

spi下电路的连接非常简单,接上电源线Vdd和地线Vss,再接上spi的CS,SCLK,DI(MOSI)和DO(MISO)就可以了,其他引脚可以放空。

注意SD卡的电源和操作电压都为2.7-3.6V,5V的单片机要进行电平转换或串电阻限流。

还有记得SD卡的CS,SCLKh和DI要用10~100K的电阻上拉。

我是套了卡套接的电路,因为Micro SD卡的引脚太密了,不好焊接,SD卡相对引脚好焊。

因为没有卡座,而且也没专门的PCB我就直接焊到卡套上,诶牺牲了一个卡套。

下面是我自己画的电路图:上面Micro SD卡的硬件电路就好了,下面我们讲讲Micro SD卡的软件驱动和指令集。

SD卡的命令格式如下,6字节共48位,传输时最高位(MSB)先传输:SD卡的command(命令)占6 bit,一般叫CMDx或ACMDx,比如CMD1就是1,CMD13就是13,ACMD41就是41,依此类推。

Command Argument(命令参数)占4 byte,并不是所有命令都有参数,没有参数的话该位一般就用置0。

最后一个字节由7 bit CRC校验位和1 bit停止位组成。

简述温湿度采集的数据格式

简述温湿度采集的数据格式篇一:温湿度采集是指通过传感器或仪器来测量和记录环境中的温度和湿度数据。

在温湿度采集中,数据格式是指数据的组织和表示方式。

常见的温湿度数据格式有以下几种:1. 数值格式:温湿度数据以数值的形式表示,例如温度数据以摄氏度(℃)或华氏度(℉)为单位,湿度数据以百分比表示。

例如,温度为25℃,湿度为50%。

2. 文本格式:温湿度数据以文本的形式表示,例如温度和湿度的描述和标签。

例如,'温度适宜'、'湿度过高'等。

3. 时间序列格式:温湿度数据按照时间顺序进行组织和表示。

通常,每个数据点都有一个时间戳,用于标记数据采集的时间。

例如,每隔一分钟记录一次温湿度数据。

4. 图形格式:温湿度数据以图形的形式表示,例如折线图或热力图。

图形可以更直观地展示温湿度的变化趋势和空间分布。

此外,温湿度数据还可以与其他数据进行结合,例如位置信息、设备状态等,形成更复杂的数据格式。

例如,温湿度数据与GPS数据结合,可以分析不同地点的温湿度变化;温湿度数据与设备状态数据结合,可以分析温湿度对设备性能的影响等。

温湿度采集的数据格式对于数据的存储、传输和分析都起着重要的作用。

不同的数据格式适用于不同的应用场景。

例如,在物联网中,温湿度数据通常使用时间序列格式进行存储和传输;在气象学中,温湿度数据通常使用数值格式进行分析和预测。

因此,在进行温湿度采集时,需要根据具体的应用需求选择合适的数据格式。

篇二:温湿度采集是指通过传感器等设备对环境中的温度和湿度进行监测和测量。

在温湿度采集过程中,数据通常以数字形式进行表示,具体的数据格式可根据应用和需求进行选择。

常见的温湿度数据格式包括以下几种:1. 数字温湿度数据格式:温湿度数据以数字形式表示,通常以十进制数值的形式呈现。

例如,温度可以以摄氏度或华氏度为单位,湿度可以以百分比表示。

这种格式的数据便于处理和计算,适用于大多数应用场景。

2. 二进制温湿度数据格式:温湿度数据以二进制编码的形式表示,通常使用特定的协议进行传输和解析。

SPI协议解析高速串行通信的协议标准

SPI协议解析高速串行通信的协议标准SPI(Serial Peripheral Interface)是一种高速串行通信协议,被广泛应用于各种数字设备的通信接口传输中。

本文将对SPI协议进行详细解析,介绍其协议标准,以及相关的特性和应用。

I. 介绍SPI协议是一种同步协议,常用于微控制器和外部外设之间的通信。

它通过四根信号线(时钟线、数据线、主从选择线、片选线)实现全双工通信,并且支持多主机和多从机的通信方式。

SPI协议具有高速传输、简单易用、灵活性强等特点,被广泛用于各种应用领域。

II. 协议标准SPI协议的通信规范主要包括以下几个方面:1. 时钟极性与相位SPI协议定义了两种类型的时钟极性和相位设置,分别为CPOL和CPHA。

CPOL用于控制时钟信号的极性,可以是低电平为开始(CPOL=0),或高电平为开始(CPOL=1)。

CPHA用于控制数据采样的时机,可以是时钟信号的上升沿采样(CPHA=0),或下降沿采样(CPHA=1)。

根据不同的设备要求,可以通过组合CPOL和CPHA来实现精确的时序控制。

2. 数据传输顺序SPI协议支持全双工传输,数据通信可以是单向的,也可以是双向的。

数据传输的顺序由设备的主从模式决定,主机先发送数据,然后从机进行响应。

在全双工通信中,数据可以同时双向传输,主机和从机同时发送和接收数据。

3. 主从设备选择SPI协议使用一根主从选择线(SS)来选择通信的主机或从机。

当某个从机被选中时,通过使能该从机的片选线,使其进入工作状态,其他从机则处于非工作状态。

主机可以通过控制主从选择线来选择不同的从机进行通信。

4. 数据帧格式SPI协议的数据传输是以数据帧的形式进行的。

每个数据帧由一个字节(8位)的数据组成,包括发送的数据和接收的数据。

数据帧可以是单向的,也可以是双向的。

5. 传输速率SPI协议支持各种传输速率,可以根据需要进行调整。

传输速率由时钟信号频率决定,可以通过调整时钟频率来达到不同的传输速率。

串行通信常用格式

标题:串行通信常用格式解析

一、引言

串行通信是一种常见的数据传输方式,尤其在需要长距离通信或者高带宽成本的情况下,串行通信具有很高的实用价值。

本篇文章将详细解析串行通信的常用格式,包括RS-232、RS-485、USB、I2C以及SPI等。

二、串行通信格式解析

1. RS-232:RS-232是一种广泛应用于计算机和外设之间的串行通信格式,其特点是数据传输速率较慢,但成本低,因此在一些对通信成本敏感的场合得到广泛应用。

2. RS-485:RS-485是一种改进的RS-232,它在多站点通信中表现出了更高的可靠性。

它通过采用差分信号传输,减少了噪声干扰,增强了通信的稳定性。

3. USB:USB是一种通用串行总线,支持即插即用,方便快捷。

USB通信格式支持高速和低速两种模式,适用于需要大量数据传输的场合。

4. I2C:I2C是一种简单、低成本的通信协议,主要用于芯片之间的通信。

它通过两根线(数据线)和一根地线进行通信,适用于需要少量数据传输且需要节省空间的场合。

5. SPI:SPI是一种高速、低功耗的通信协议,主要用于芯片之间的同步通信。

它通过四根线(数据线、时钟线、片选线和地址线)进行通信,适用于需要高速数据传输的场合。

三、总结

串行通信格式的选择应根据具体应用场景和需求进行。

了解并掌握各种格式的特点和适用场合,有助于我们选择最适合的通信方式,提高通信效率和稳定性。

SPI协议串行外设接口协议的特点与使用

SPI协议串行外设接口协议的特点与使用SPI(Serial Peripheral Interface)协议是一种串行外设接口协议,广泛应用于数字通信、嵌入式系统和电子设备等领域。

本文将重点介绍SPI协议的特点和使用方法。

一、SPI协议的特点SPI协议具有以下几个特点:1. 高速全双工传输:SPI协议支持全双工通信,主设备和从设备可以同时进行收发数据,提供了高效的数据传输能力。

2. 多设备串联:SPI协议支持多个从设备与一个主设备之间的串联连接。

每个从设备都有一个片选信号,主设备通过控制片选信号来选择与之通信的从设备,从而支持与多个从设备的通信。

3. 硬件实现简单:SPI协议的实现只需要少量的硬件资源,常用的器件如微控制器、存储器、传感器等晶片都具备SPI接口,这使得SPI 协议应用非常广泛。

4. 高灵活性的传输模式:SPI协议支持多种传输模式,可以通过调整时钟极性(CPOL)和时钟相位(CPHA)来配置传输模式。

这使得SPI协议可以适应不同的连接设备和通信要求。

5. 简单可靠的通信协议:SPI协议的通信方式相对简单,在时序控制方面具有可靠性和稳定性,能够保证数据的可靠传输。

二、SPI协议的使用方法在使用SPI协议时,需要注意以下几个步骤:1. 确定SPI主从模式:在SPI通信中,需要确定主设备和从设备的角色。

主设备负责发起通信,并控制片选信号选择与之通信的从设备;从设备则根据主设备的指令响应数据。

2. 配置时钟频率和传输模式:根据从设备的要求或通信距离,可以设置合适的时钟频率和传输模式。

时钟频率决定了SPI通信的速度,而传输模式则决定了数据采样和发送的时机。

3. 设置数据格式:SPI协议支持多种数据格式,包括位数、数据字节序等。

根据具体设备的要求,设置合适的数据格式以确保正确的数据传输。

4. 控制片选信号:SPI协议通过片选信号来选择与之通信的从设备。

在通信过程中,主设备通过控制片选信号来选择某个从设备进行通信,其他从设备则保持不选中状态。

视频名词解释

MIPS MIPS是世界上很流行的一种RISC处理器。

MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

它最早是在80年代初期由斯坦福(Stanford)大学Hennessy 教授领导的研究小组研制出来的。

MIPS公司的R系列就是在此基础上开发的RISC工业产品的微处理器。

这些系列产品为很多计算机公司采用构成各种工作站和计算机系统。

CEF自定义固件扩展功能工具Custom Firmware ExtenderTS DVD节目中的MPEG2格式,是MPEG2-PS,全称是Program Stream,TS的全称则是Transport Stream。

MPEG2-PS主要应用于存储的具有固定时长的节目,如DVD电影,而MPEG-TS则主要应用于实时传送的节目,比如实时广播的电视节目。

这两种格式的主要区别是什么呢?你将DVD上的VOB文件的前面一截剪掉(或者干脆就是数据损坏),那么就会导致整个文件无法解码,而电视节目是你任何时候打开电视机都能解码(收看)的,所以,MPEG2-TS格式的特点就是要求从视频流的任一片段开始都是可以独立解码的。

AVI英文全称为Audio Video Interleaved,即音频视频交错格式。

是将语音和影像同步组合在一起的文件格式。

它对视频文件采用了一种有损压缩方式,但压缩比较高,因此尽管面面质量不是太好,但其应用范围仍然非常广泛。

AVI支持256色和RLE压缩。

AVI信息主要应用在多媒体光盘上,用来保存电视、电影等各种影像信息。

ASI异步串行接口SMPTE—时间码概念SMPTE(The Society of Motion Picture and Television Engineers)。

它是目前在影音工业中得到广泛应用的一个时间码概念。

单片机中的SPI通信协议详解与应用案例

单片机中的SPI通信协议详解与应用案例SPI(Serial Peripheral Interface)是一种全双工、同步的串行通信协议,广泛应用于单片机与外围设备之间的通信。

本文将详细介绍SPI 通信协议的工作原理、通信格式以及在单片机应用中的实际案例。

### 一、SPI通信协议的工作原理SPI通信协议通常由一个主设备(Master)和一个或多个从设备(Slave)组成。

主设备负责发起通信并控制通信的时序,从设备则根据主设备的指令进行响应。

SPI通信使用四根线进行连接,包括时钟线(SCLK)、主设备输出从设备输入线(MOSI)、主设备输入从设备输出线(MISO)以及片选线(SS)。

在SPI通信中,通信双方通过时钟线同步数据传输,主设备在时钟信号的上升沿或下降沿触发数据传输,而从设备在时钟信号的相反沿进行数据接收。

此外,通过片选线可以选择与主设备进行通信的特定从设备,避免多个从设备同时响应。

### 二、SPI通信协议的通信格式在SPI通信中,数据传输的格式包括数据位数、传输顺序和时钟极性等方面的参数。

常见的SPI通信格式包括数据位宽(1~16位)、传输顺序(MSB first或LSB first)以及时钟极性(空闲时钟高电平或低电平)等。

数据传输过程中,主设备通过时钟线向从设备发送时钟信号,并同时通过MOSI线发送数据,从设备则通过MISO线接收并响应数据。

SPI通信中一般采用全双工通信方式,即主设备和从设备可以同时发送和接收数据。

### 三、SPI通信协议的应用案例SPI通信协议在单片机应用中具有广泛的应用场景,例如与外部存储器、传感器、显示屏等外围设备进行通信。

下面以单片机与外部存储器的通信为例,介绍SPI通信协议的应用过程。

1. 初始化SPI通信:配置主设备和从设备的通信参数,包括时钟频率、传输格式等,以确保通信双方能够正常进行数据传输。

2. 选中从设备:通过片选线选择要与主设备通信的具体从设备,避免多个从设备同时响应导致通信错误。

SPI总线从机接口实时模拟的实现

SPI总线从机接口实时模拟的实现SPI(Serial Peripheral Interface)总线是一种用于串行通信的同步接口协议,常用于嵌入式系统中的外围设备之间的通信。

SPI总线由一个主设备和一个或多个从设备组成,主设备通过时钟信号控制数据的传输。

在实时模拟SPI总线从机接口时,我们需要实现以下几个关键的功能:1.时钟信号生成:SPI总线的通信是通过时钟信号来同步的,因此我们需要在从机接口中生成正确的时钟信号。

可以通过使用定时器或者外部时钟信号源,按照SPI总线的时序要求生成时钟信号。

2.数据收发:SPI总线的通信是全双工的,即可以同时收发数据。

从机接收主机发送的数据,同时向主机发送响应的数据。

我们需要实现数据的收发功能,可以通过串口或者并口方式将数据从主机传输到从机,同时将从机的响应数据传输回主机。

3.数据帧格式解析:SPI总线中的数据是按照一定格式进行传输的,我们需要在从机接口中解析数据帧的格式。

数据帧通常包括数据位、校验位、起始位和停止位等信息。

在接收数据时,需要正确解析数据帧的格式,提取出有效的数据,并进行校验。

4.状态监测:在实时模拟从机接口时,需要监测SPI总线状态的变化。

包括时钟信号的变化、数据收发的状态和错误状态等。

在监测到状态的变化时,应及时进行相应的操作,例如更新数据、发送响应等。

5.错误处理:在SPI总线通信中,可能会出现各种错误,如数据传输错误、时钟信号失效等。

我们需要在从机接口中实现错误的检测和处理机制,以保证数据的可靠传输。

实时模拟SPI总线从机接口的实现,需要根据具体的硬件平台和所使用的编程语言进行相应的开发。

通常可以借助现有的软件库或者开发工具来简化开发过程,如使用Arduino等开发板、C语言或Python等编程语言。

总之,实时模拟SPI总线从机接口的实现需要考虑时钟信号生成、数据收发、数据帧格式解析、状态监测和错误处理等关键功能。

通过合理的设计和开发,可以实现SPI总线从机接口在软件上的模拟,以满足相应的通信需求。

ASI、SPI、SDI以及区别

异步串行接口(ASI) 、串行数字接口(S DI)、同步并行接口(SPI)两种完全不同的接口都简称为S PI,一种是"Serial P eriphe ral Interfa ce",意为串行外围接口,另一种是“Synchro nous Paralle l Interfa ce”,意为同步并行接口。

本文的SPI指后者。

SDI标准由S MPTE进行定义,广泛应用在广播和视频产品中。

SDI标准描述了怎样通过视频同轴电缆在剪辑设备之间传送未压缩的串行数字视频数据。

有两种SDI标准:SD-SDI和HD-SDI,它们基于不同的数据速率。

这两种标准的基本电气规范相同,主要不同点是,H D-SDI有较高的数据速率,1.485 Gbps,而SD-SDI数据速率在143 Mbps到540 Mbps之间,270 Mbps是最流行的速率。

SDI是Ser ial Digital Interfa ce 的缩写,也就是串行数字接口,它是SMPTE 259M中定义的串行数字接口,该接口采用10比特传输与非归零反向(NRZI)编码。

在传送ITU-R BT.601(A部分)4:2:2级别信号时,其时钟还率为270 Mb/s,这就是如今大名鼎鼎的SDI,后来,SDI 逐渐成为数字设备的标准配置,在此基础上终于实现了演播室、主控、播控系统的数字化;SDI是信道码流,这种码流是没有经过编码压缩的基带信号,码率较大,占用较大的传输带宽;随着高清晰度电视技术加速发展,采用串行数字接口传输高清信号已在行业内达成共识,为此,SMPTE在292M标准中定义了时钟频率达1. 5 Gb/s级别的串行数字接口HD-SDI,时钟频率提升到1.485 Gb/s;高速接口芯片技术的进步使3Gb/s级别的串行接口成为可能,SMPTE 424M也给出了类似的3Gb/s级别接口的定义。

SPI通信方式

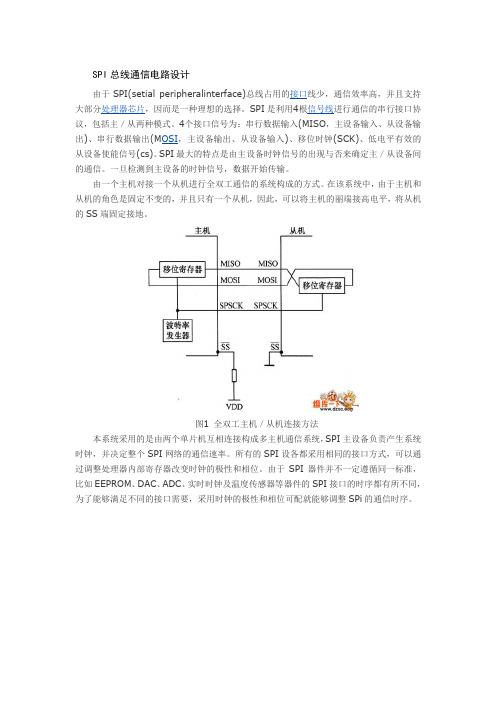

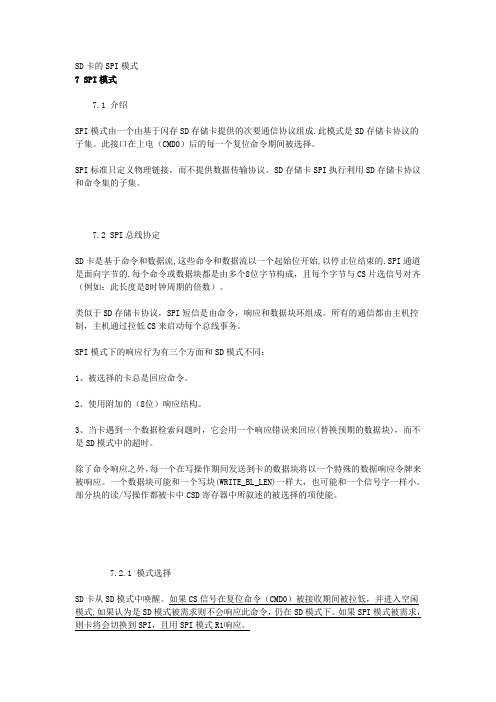

SPI总线通信电路设计由于SPI(setial peripheralinterface)总线占用的接口线少,通信效率高,并且支持大部分处理器芯片,因而是一种理想的选择。

SPI是利用4根信号线进行通信的串行接口协议,包括主/从两种模式。

4个接口信号为:串行数据输入(MISO,主设备输入、从设备输出)、串行数据输出(M OSI,主设备输出、从设备输入)、移位时钟(SCK)、低电平有效的从设备使能信号(cs)。

SPI最大的特点是由主设备时钟信号的出现与否来确定主/从设备间的通信。

一旦检测到主设备的时钟信号,数据开始传输。

由一个主机对接一个从机进行全双工通信的系统构成的方式。

在该系统中,由于主机和从机的角色是固定不变的,并且只有一个从机,因此,可以将主机的丽端接高电平,将从机的SS端固定接地。

图1 全双工主机/从机连接方法本系统采用的是由两个单片机互相连接构成多主机通信系统,SPI主设备负责产生系统时钟,并决定整个SPI网络的通信速率。

所有的SPI设各都采用相同的接口方式,可以通过调整处理器内部寄存器改变时钟的极性和相位。

由于SPI器件并不一定遵循同一标准,比如EEPROM、DAC、ADC、实时时钟及温度传感器等器件的SPI接口的时序都有所不同,为了能够满足不同的接口需要,采用时钟的极性和相位可配就能够调整SPi的通信时序。

SPI设各传输数据过程中总是先发送或接收高字节数据,每个时钟周期接收器或收发器左移1位数据。

对于小于16位的数据在发送之前必须左对齐,如果接收的数据小于16位则采用软件将无效的数据位屏蔽,当主机发送一个连续的数据流时,有些外设能够进行多字节传输。

多数具有SPI接口的存储芯片就以这种方式工作。

在这种传输方式下,从机的片选端必须在整个传输过程中保持低电平。

此时,一次传输可能会涉及到成千上万字节的信息,而不必在每个字节的数据发送的前后都去检测其起始位和结束位,这正是同步传输方式优于异步传输方式的原因所在。

W5100学习之应用资料

6.等待接收完成 7.如果所有数据都传输完成,配置/SS 为高电平

读/写内部寄存器或存储器的过程如下: 1.先将要读写的地址写入到 IDM_AR0 或 IDM_AR1 寄存器当中。 2.再从 IDM_DR 寄存器中读或写。 如果要对某个地址顺序地读写,则可以将模式寄存器 MR 的 AI 置 1,然 后执行一次述第 1 项后,在读写 IDM_DR,IDM_AR 的值将自动加 1。这 样,只需要连续对 IDM_DR 写,数据就可以连续地读出或写入。 SPI 总线接口 串行接口模式只需要 4 个引脚进行数据通信。这 4 个引脚的定义分别为: SCLK、/SS、MOSI、MISO。W5100 的 SPI_EN 引脚选择 SPI 操作。 1 设备操作 主控制器(SPI 的主设备)发出一系列指令控制 W5100 的运行。SPI 主设 备通过四个信号线与 W5100 通信:从设备选择(/SS)、料

应用资料 W5100 有三种方式与 MCU 接口:直接总线接口、间接总线接口和 SPI 总 线接口。 直接总线接口模式 直接总线接口模式采用 15 位地址线和 8 位数据线,另加 /CS,/RD,/WR,/INT 等信号线。 间接地址接口模式 间接总线接口采用 2 位地址线,8 位数据线,另加/CS,/RD,/WR 及/INT 等信号线。[14:2]没用到的地址线经过电阻接地。 间接总线接口模式相关寄存器说明如下:

l *MISO(主输入从输出):输入 2.配置/SS 为高电平 配置 SPI 主设备的寄存器 l *SPI 使能位在 SPCR 寄存器(SPI 控制寄存器) l *主/从设备选择位在 SPCR 寄存器 l *SPI 模式选择在 SPCR 寄存器 l *SPI 数据速率在 SPCR 寄存器和 SPSR 寄存器(SPI 状态寄存器) 4.向 SPDR 寄存器(SPI 数据寄存器)写入要传输的数据 5.配置/SS 为低电平

SPI总线完全解读

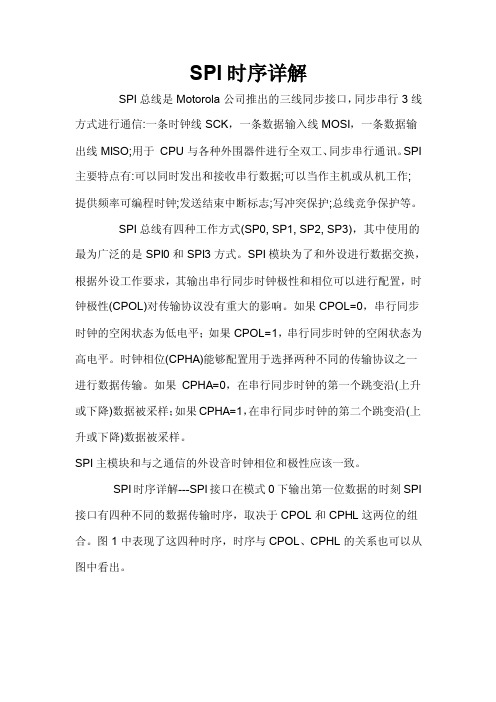

SPI时序详解SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI 主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0, SP1, SP2, SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI时序详解---SPI接口在模式0下输出第一位数据的时刻SPI 接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。

图1中表现了这四种时序,时序与CPOL、CPHL的关系也可以从图中看出。

图1CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL=1时,空闲电平为高电平。

CPHA是用来决定采样时刻的,CPHA=0,在每个周期的第一个时钟沿采样,CPHA =1,在每个周期的第二个时钟沿采样。

由于我使用的器件工作在模式0这种时序(CPOL=0,CPHA=0),所以将图1简化为图2,只关注模式0的时序。

图2我们来关注SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿,第一个时钟沿),在时钟的后沿输出数据(下降沿,第二个时钟沿)。

SPI

6-SPE

5-SPTIE 4-MSTR 3-CPOL 2-CPHA

1-SSOE

0-LSBFE

时钟模式

时钟模式

SS的用法

对于Slave模式,SS管脚一定作为片选输入用; 对于Master模式,SS管脚是否被SPI控制,取决于MODFEN,当该位为“1”表示SS被 SPI使用,但其功能由SSOE决定,SSOE为“1”时,SS作为片选输出;SSOE为“0”时 SS作为总线冲突指示输入。 总线冲突检测功能: 当管脚 SS 作为总线冲突指示用时(此时MSTR = 1, MODFEN = 1且SSOE = 0).当一个 主器件的SS管脚变为低时,意味着还有其它Master器件试图将该主器件作为Slave来 控制,此时产生总线冲突事件, 标志位MODF被置“1”(读SPIS然后写SPIC1清除该 位),且被控制器件将更改模式为Slave(MSTR位被清除),用户程序必须保证总线 冲突解除才能重新恢复器件为主模式。

4-MODF

•

SPI Data Register (SPID)

寄存器

1、读接收缓冲,写发送缓冲; 2、主模式下,写SPID启动一次数据传输; 3、只有在SPTEF为1时才写SPID; 4、在SPRF为“1”时,随时可以读取SPID,但一定要在下一次数据传输完成之前进行; 5、在SPRF为1之前读SPID,可能导致当前数据传输出错;

•图8-2 图

SPI串行总线典型时序

单片机管脚模拟SPI接口的方法 以便深入理解SPI时序

1) 用一般I/O口线模拟SPI操作 • 对于没有SPI接口的单片机来说,可使用软件来模 拟SPI的操作,包括串行时钟、数据输入和输出。 • 对于不同的串行接口外围芯片,它们的时钟时序 是不同的。 • 对于在SCK的上升沿输入(接收)数据和在下降沿 输出(发送)数据的器件(slave)

RSSPI铁路信号安全通信协议

RSSPI铁路信号安全通信协议RSSPI是铁路信号系统中使用的一种安全通信协议,它为铁路运输提供了可靠的信号传输和数据通信功能。

本文将介绍RSSPI协议的原理、特点以及在铁路信号系统中的应用。

一、RSSPI协议的原理1. 数据格式RSSPI协议采用二进制格式传输数据,具有高效的数据压缩和传输能力。

数据包由头部和数据体组成,头部包含了数据包的标识和长度信息,数据体则是具体的信号数据。

2. 数据加密为了确保通信的安全性,RSSPI协议使用了数据加密技术。

在传输过程中,数据经过加密算法处理,只有合法的接收方才能解密并获取数据内容,避免数据被非法篡改或窃取。

3. 可靠性传输RSSPI协议通过使用数据校验码和确认应答方式,实现了可靠的数据传输。

发送方在发送数据包时,会附加校验码,接收方通过比对校验码来验证数据的完整性。

如果数据包损坏或丢失,接收方会要求发送方重新发送,以确保数据的正确传递。

二、RSSPI协议的特点1. 实时性铁路信号系统对数据的实时传输要求非常高,RSSPI协议通过采用高速传输通道和优化的数据处理算法,确保数据可以实时准确地传输到目标设备。

2. 可扩展性RSSPI协议设计灵活,具有良好的可扩展性。

它支持多种数据类型的传输,可以适应不同类型的信号设备和通信系统,便于系统的升级和添加新功能。

3. 安全性铁路信号传输系统对数据的安全性要求很高,RSSPI协议通过加密技术和校验码验证等手段,保证数据传输过程中的安全性,防止数据被非法访问和篡改。

三、RSSPI协议在铁路信号系统中的应用1. 信号灯控制RSSPI协议可以用于控制铁路信号灯的状态。

通过发送特定的数据包,可以实现信号灯的变色和闪烁等操作,确保列车安全行驶。

2. 路口监控铁路信号系统需要监控路口的实时情况以保证列车通行安全。

RSSPI协议可以传输路口监控设备的数据,例如道口状态、车辆数量等,为信号系统提供准确的路况信息。

3. 列车位置报告铁路运输需要及时了解列车的位置信息,以协调列车的运行。

SD卡的SPI模式

SD卡的SPI模式7 SPI模式7.1 介绍SPI模式由一个由基于闪存SD存储卡提供的次要通信协议组成.此模式是SD存储卡协议的子集。

此接口在上电(CMD0)后的每一个复位命令期间被选择。

SPI标准只定义物理链接,而不提供数据传输协议。

SD存储卡SPI执行利用SD存储卡协议和命令集的子集。

7.2 SPI总线协定SD卡是基于命令和数据流,这些命令和数据流以一个起始位开始,以停止位结束的.SPI通道是面向字节的.每个命令或数据块都是由多个8位字节构成,且每个字节与CS片选信号对齐(例如:此长度是8时钟周期的倍数)。

类似于SD存储卡协议,SPI短信是由命令,响应和数据块环组成。

所有的通信都由主机控制,主机通过拉低CS来启动每个总线事务。

SPI模式下的响应行为有三个方面和SD模式不同:1、被选择的卡总是回应命令。

2、使用附加的(8位)响应结构。

3、当卡遇到一个数据检索问题时,它会用一个响应错误来回应(替换预期的数据块),而不是SD模式中的超时。

除了命令响应之外,每一个在写操作期间发送到卡的数据块将以一个特殊的数据响应令牌来被响应。

一个数据块可能和一个写块(WRITE_BL_LEN)一样大,也可能和一个信号字一样小。

部分块的读/写操作都被卡中CSD寄存器中所叙述的被选择的项使能。

7.2.1 模式选择SD卡从SD模式中唤醒。

如果CS信号在复位命令(CMD0)被接收期间被拉低,并进入空闲模式,如果认为是SD模式被需求则不会响应此命令,仍在SD模式下。

如果SPI模式被需求,则卡将会切换到SPI,且用SPI模式R1响应。

唯一返回SD模式的方法是进入上电周期。

在SPI模式下,SD存储卡协议状态机不被遵守。

所有的在SPI模式下被支持的SD存储卡命令总是可用的。

7.2.2 总线传输保护每个在总线上传输的SD存储卡令牌被CRC位保护。

在SPI模式下,SD存储卡提供一个非保护模式。

此模式使系统用可靠的数据链接来建立,以排除(否定)硬件或软件需要执行CRC 生成和校验功能。

SPI通信方式

SPI总线通信电路设计由于SPI(setial peripheralinterface)总线占用的接口线少,通信效率高,并且支持大部分处理器芯片,因而是一种理想的选择。

SPI是利用4根信号线进行通信的串行接口协议,包括主/从两种模式。

4个接口信号为:串行数据输入(MISO,主设备输入、从设备输出)、串行数据输出(M OSI,主设备输出、从设备输入)、移位时钟(SCK)、低电平有效的从设备使能信号(cs)。

SPI最大的特点是由主设备时钟信号的出现与否来确定主/从设备间的通信。

一旦检测到主设备的时钟信号,数据开始传输。

由一个主机对接一个从机进行全双工通信的系统构成的方式。

在该系统中,由于主机和从机的角色是固定不变的,并且只有一个从机,因此,可以将主机的丽端接高电平,将从机的SS端固定接地。

图1 全双工主机/从机连接方法本系统采用的是由两个单片机互相连接构成多主机通信系统,SPI主设备负责产生系统时钟,并决定整个SPI网络的通信速率。

所有的SPI设各都采用相同的接口方式,可以通过调整处理器内部寄存器改变时钟的极性和相位。

由于SPI器件并不一定遵循同一标准,比如EEPROM、DAC、ADC、实时时钟及温度传感器等器件的SPI接口的时序都有所不同,为了能够满足不同的接口需要,采用时钟的极性和相位可配就能够调整SPi的通信时序。

SPI设各传输数据过程中总是先发送或接收高字节数据,每个时钟周期接收器或收发器左移1位数据。

对于小于16位的数据在发送之前必须左对齐,如果接收的数据小于16位则采用软件将无效的数据位屏蔽,当主机发送一个连续的数据流时,有些外设能够进行多字节传输。

多数具有SPI接口的存储芯片就以这种方式工作。

在这种传输方式下,从机的片选端必须在整个传输过程中保持低电平。

此时,一次传输可能会涉及到成千上万字节的信息,而不必在每个字节的数据发送的前后都去检测其起始位和结束位,这正是同步传输方式优于异步传输方式的原因所在。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

497Jz4755 Multimedia Application Processor Programming Manual, Revision 1.0Copyright® 2005-2007 Ingenic Semiconductor Co., Ltd. All rights reserved.23.5 Data FormatsFour signals are used to transfer data between the processor and external peripheral. The SSI supports three formats: Motorola SPI, Texas Instruments SSP , and National Microwire. Although they have the same basic structure the three formats have significant differences, as described below.SSI_CE_/SSI_CE2_ varies for each protocol as follows:• For SPI and Microwire formats, SSI_CE_/SSI_CE2_ functions as a chip select to enable the external device (target of the transfer), and is held active-low during the data transfer. • For SSP format, this signal is pulsed high for one serial bit-clock period at the start of each frame.SSI_CLK varies for each protocol as follows: For Microwire, both transmit and receive data sources switch data on the falling edge of SSI_CLK, and sample incoming data on the rising edge.For SSP , transmit and receive data sources switch data on the rising edge of SSI_CLK, and sample incoming data on the falling edge.For SPI, the user has the choice of which edge of SSI_CLK to use for switching outgoing data, and for sampling incoming data. In addition, the user can move the phase of SSI_CLK, shifting its active state one-half period earlier or later at the start and end of a frame.While SSP and SPI are full-duplex protocols, Microwire uses a half-duplex master-slave messaging protocol. At the start of a frame, a 1 or 2-byte control message is transmitted from the controller to the peripheral. The peripheral does not send any data. The peripheral interprets the message and, if it is a READ request, responds with requested data, one clock after the last bit of the requesting message.The serial clock (SSI_CLK) only toggles during an active frame. At other times it is held in an inactive or idle state, as defined by its specified protocol.23.5.1 Motorola’s SPI Format Details 23.5.1.1 General Single Transfer FormatsThe figures below show the timing of general single transfer format.498Jz4755 Multimedia Application Processor Programming Manual, Revision 1.0Copyright® 2005-2007 Ingenic Semiconductor Co., Ltd. All rights reserved.Figure 23-1 SPI Single Character Transfer Format (PHA = 0)Figure 23-2 SPI Single Character Transfer Format (PHA = 1)For SSICR1.PHA = 0, when SSICR1.TFVCK = B’00, hardware ensures the first clock edge appears one SSI_CLK period after SSI_CE_ / SSI_CE2_ goes valid; when SSICR1.TCKFI = B’00, hardware ensures the SSI_CE_ / SSI_CE2_ negated half SSI_CLK period after last clock change edge; when SSICR1.TFVCK ≠ B’00 or SSICR1.TCKFI ≠ B’00, 1/2/3 more clock cycles are inserted.For SSICR1.PHA = 1, when SSICR1.TFVCK = B’00, hardware ensures the first clock edge appears half SSI_CLK period after SSI_CE_ / SSI_CE2_ goes valid; when SSICR1.TCKFI = B’00, hardware ensures the SSI_CE_ / SSI_CE2_ negated one SSI_CLK period after last clock change edge; when SSICR1.TFVCK ≠ B’00 or SSICR1.TCKFI ≠ B’00, 1/2/3 more clock cycles are inserted. SSI_DT SSI_GPCSSI_GPC(SSICR1.FRMHLn= 0) SSI_DT499Jz4755 Multimedia Application Processor Programming Manual, Revision 1.0Copyright® 2005-2007 Ingenic Semiconductor Co., Ltd. All rights reserved.Data is sampled from SSI_DR at every rising edge (when PHA = 0, POL = 0 or PHA = 1, POL = 1) or at every falling edge (when PHA = 0, POL = 1 or PHA = 1, POL = 0). According to SPI protocol, input data on SSI_DR should be stable at every sample clock edge.Drive data onto SSI_DT at every rising edge (when PHA = 0, POL = 1 or PHA = 1, POL = 0) or at every falling edge (when PHA = 0, POL = 0 or PHA = 1, POL = 1).23.5.1.2 Back-to-Back Transfer FormatsFigure 23-3 SPI Back-to-Back Transfer FormatFor Motorola’s SPI format transfers those continuous characters are exchanged during SSI_CE_ / SSI_CE2_ being valid, the timing is illustrated in the figure (SSICR1.LFST = 0).Back-to-back transfer is performed as transmit-only/full-duplex operation when transmit-FIFO is not empty before the completion of the last character’s transfer or performed as receive-only operation.500Jz4755 Multimedia Application Processor Programming Manual, Revision 1.0Copyright® 2005-2007 Ingenic Semiconductor Co., Ltd. All rights reserved. 23.5.1.3 Frame Interval Mode Transfer FormatWhen in interval mode (SSIITR. IVLTM ≠ ‘0’), SSI always wait for an interval time (SSIITR.IVLTM), transfer fixed number of characters (SSIICR), then repeats the operation.When SSICR0.RFINE = 1, if transmit-FIFO is still empty after the interval time, receive-only transfer will occur.During interval-wait time, SSI stops SSI_CLK, and when SSICR1.ITFRM = 0 it negates the SSI_CE_ / SSI_CE2_, when SSICR1.ITFRM = 1 it keeps asserting the SSI_CE_ / SSI_CE2_.For transfers finished with transmit-FIFO empty, if the SSI transmit-FIFO is empty before fixed number of characters being loaded to transfer (SSICR1.UNFIN must be 1), then the SSI will set SSISR.UNDR = 1; if enabled, it’ll send out a SSI underrun interrupt. At the same time, SSI will hold the SSI_CE_ / SSI_CE2_ and SSI_CLK signals at current status and wait for the transmit-FIFO filling. The SSI will continue transfer after transmit-FIFO being filled. The SSI always stops after completion of fixed number of characters’ transfer (SSICR1.UNFIN must be 0) with transmit-FIFO empty.For transfers finished by SSICR0.RFINC being valid set, the SSI will stop after finished current character transfer and needn’t wait for a whole completion of fixed number of characters’ transfer.Two Interval transfer mode are illustrated in the following figures. In these timing diagram, SSICR1.PHA = 0, SSICR1.POL = 0 and SSIICR = 0.Figure 23-4 SPI Frame Interval Mode Transfer Format (ITFRM = 0, LFST = 0)0)501Jz4755 Multimedia Application Processor Programming Manual, Revision 1.0Copyright® 2005-2007 Ingenic Semiconductor Co., Ltd. All rights reserved.Figure 23-5 SPI Frame Interval Mode Transfer Format (ITFRM = 1, LFST = 1)23.5.2 TI’s SSP Format DetailsIn this format, each transfer begins with SSI_CE_ pulsed high for one SSI_CLK period. Then both master and slave drive data at SSI_CLK’s rising edge and sample data at the falling edge. Data are transferred with MSB first or LSB first. At the end of the transfer, SSI_DT retains the value of the last bit sent through the next idle period.Figure 23-6 TI’s SSP Single Transfer FormatFigure 23-7 TI’s SSP Back-to-back Transfer Format23.5.3 National Microwire Format DetailsIt supports format 1 and format 2. If format 1 is selected, both master and slave drive data at SSI_CLK falling edge and sample data at the rising edge. If format 2 is selected, master drive and sample data at SSI_CLK falling edge, slave drive and sample data at SSI_CLK rising edge. SSI_CLK goes high midway through the command’s most significant bit (or LSB) and continues to toggle at the bit rate. One bit clock (format 1) or half one bit clock (format 2) period after the last command bit, the external slave must return the serial data requested, with most significant bit first (or LSB first) on SSI_DR. SSI_CE_ / SSI_CE2 deasserts high half clock (SSI_CLK) period (and 1/2/3 additional clock periods) later. Format 1 support back-to-back transfer, the start and end of back-to-back transfers are similar to those of a single transfer. However, SSI_CE_ / SSI_CE2 remains asserted throughout the transfer. The end of a character data on SSI_DR is immediately followed by the start of the next command byte on SSI_DT.Figure 23-8 National Microwire Format 1 Single Transfer503Jz4755 Multimedia Application Processor Programming Manual, Revision 1.0Copyright® 2005-2007 Ingenic Semiconductor Co., Ltd. All rights reserved.Figure 23-9 National Microwire Format 1 Back-to-back TransferFigure 23-10 National Microwire Format 2 Read TimingFigure 23-11 National Microwire Format 2 Write Timing23.6 Interrupt Operation。