MSP430F4XX中文技术手册

MSP430中文数据手册

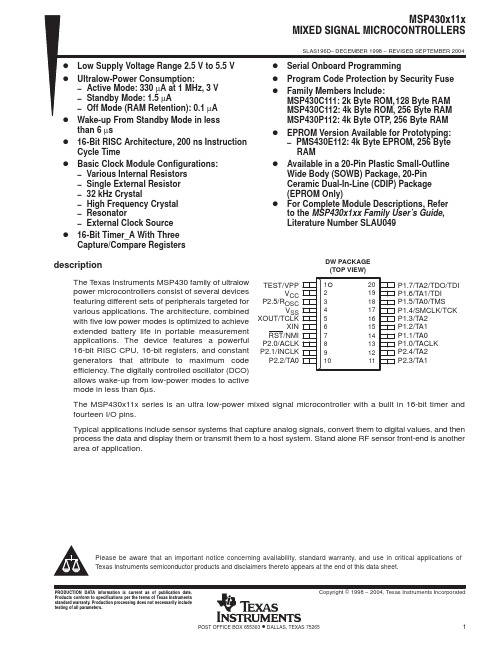

MSP430混合信号微控制器数据手册产品特性●低电压范围:2.5V~5.5V 超低功耗●超低功耗——活动模式:330μA at 1MHz, 3V——待机模式:0.8μA——掉电模式(RAM数据保持):0.1μA ●从待机模式唤醒响应时间不超过6μs ●16位精简指令系统,指令周期200ns ●基本时钟模块配置基本时钟模块配置——多种内部电阻——多种内部电阻——单个外部电阻——单个外部电阻——32kHz晶振晶振——高频晶体——高频晶体——谐振器——谐振器——外部时钟源——外部时钟源●带有三个捕获/比较寄存器的16位定时器(Timer_A)串行在线可编程●串行在线可编程●采用保险熔丝的程序代码保护措施采用保险熔丝的程序代码保护措施该系列产品包括●该系列产品包括——MSP430C111:2K字节ROM,128字节RAM ——MSP430C112:4K字节ROM,256字节RAM ——MSP430P112:4K字节OTP,256字节RAM 原型●EPROM原型——PMS430E112:4KB EPROM, 256B RAM ●20引脚塑料小外形宽体(SOWB)封装,20引脚陶瓷双列直插式(CDIP)封装(仅EPROM)●如需完整的模块说明,请查阅MSP430x1xx系列用户指南(文献编号:SLAU049 产品说明TI公司的MSP43O系列超低功耗微控制器由一些基本功能模块按照不同的应用目标组合而成。

在便携式测量应用中,这种优化的体系结构结合五种低功耗模式可以达到延长电池寿命的目的。

以达到延长电池寿命的目的。

MSP430MSP430系列的CPU 采用16位精简指令系统,集成有16位寄存器和常数发生器,发挥了最高的代码效率。

它采用数字控制振荡器(DCO DCO)),使得从低功耗模式到唤醒模式的转换时间小于6μs.MSP430x11x 系列是一种超低功耗的混合信号微控制器,系列是一种超低功耗的混合信号微控制器,它拥有一个内置的它拥有一个内置的16位计数器和14个I/0引脚。

MSP430F2XX中文手册(加了标签) 10.通用串口

MSP430F2系列16位超低功耗单片机模块原理第10章通用串口界面Universal Serial Interface 版本: 1.5日期: 2007.5.原文: TI MSP430x2xxfamily.pdf翻译: 陈安都湖南长沙-中南大学编辑: DC 微控技术论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

Page 1 of 15通用串行接口模块(USI)提供与硬件模块的SPI和I2C串行通信。

本章讨论这两种模式。

USI模块包含在MSP420X20XX系列中。

主题10.1 USI的介绍10.2 USI的使用10.3 USI的寄存器10.1 USI的介绍USI模块提供支持同步串行通信的基本功能。

一般地,一个8、16位移位寄存器能用来输出数据流,少许的几条指令就可以执行串行通信。

另外,USI包含的内置硬件可以模拟SPI和I2C通信。

USI模块还包括中断,可以进一步减少串行通信的通用程序并且保持MSP430的低功耗特性。

USI模块的特性包括:支持三线SPI模式支持I2C模式可变的数据长度在LPM4方式下不需要内部时钟MSB或LSB指令可选在I2C模式下能控制SCL打开、停止监测在主机模式下的仲裁丢失监测可编程的时钟发生器可选择的钟极性和相位控制Page 2 of 15表10-1展示了SPI模式下的USI模块Page 3 of 15表10-2展示了I2C模式下的USI模块10.2 USI的操作USI模块主要由移位寄存器和位计数器组成,通过逻辑控制来支持SPI和I2C 通信。

USI的移位寄存器为USISR,通过软件直接控制数据的移入和移出。

位计数器计算采样位的数目以及在USICNTX位写零时设置USI中断标志位Page 4 of 15USIIFG。

MPS430手册

T EXAS I NSTRUMENTSMPS430系列混合信号微控制器结构及模块用户指南目录1MSP430系列1.1特性与功能1.2系统关键性能1.3MSP430系列的各型号2结构概述2.1CPU2.2代码存储器2.3数据存储器(RAM)2.4运行控制2.5外围模块2.6振荡器、倍频器和时钟发生器3系统复位、中断和运行模式3.1系统复位和初始化3.2中断系统结构3.3中断处理3.3.1SFR中的中断控制位3.3.2外部中断3.4运行模式3.5低功耗模式3.5.1 低功耗模式0与模式1,LPM0和LPM1 3.5.2 低功耗模式2与模式3,LPM2和LPM3 3.5.3 低功耗模式4,LPM43.6 低功耗应用要点4 存储器组织4.1 存储器中的数据4.2 片内ROM组织4.2.1 ROM表的处理4.2.2 计算分支跳转和子程序调用4.3 RAM与外围模块组织4.3.1 RAM4.3.2 外围模块—地址定位4.3.3 外围模块--SFR5 16位CPU5.1 CPU寄存器5.1.1 程序计数器PC5.1.2 系统堆栈指针SP5.1.3 状态寄存器SR5.1.4 常数发生寄存器CG1与CG25.2 寻址模式5.2.1 寄存器模式5.2.2 变址模式5.2.3 符号模式5.2.4 绝对模式5.2.5 间接模式5.2.6 间接增量模式5.2.7 立即模式5.2.8 指令的时钟周期与长度5.3 指令组概述5.3.1 双操作数指令5.3.2 单操作数指令5.3.3 条件跳转5.3.4 模拟指令的短格式5.3.5 其它指令5.4 指令分布6 硬件乘法器6.1 硬件乘法器的操作6.2 硬件乘法器的寄存器6.3 硬件乘法器的SFR位6.4 硬件乘法器的软件限制6.4.1 硬件乘法器软件限制--寻址模式6.4.2 硬件乘法器软件限制--中断程序7 振荡器与系统时钟发生器7.1 晶体振荡器7.2 处理机时钟发生器7.3 系统时钟运行模式7.4 系统时钟控制寄存器7.4.1 模块寄存器7.4.2 与系统时钟发生器相关的SFR位7.5 DCO典型特性8 数字I/O配置8.1 通用端口P08.1.1 P0控制寄存器8.1.2 P0原理图8.1.3 P0中断控制功能8.2 通用端口P1、P28.2.1 P1、P2控制寄存器8.2.2 P1、P2原理图8.2.3 P1、P2中断控制功能8.3 通用端口P3、P48.3.1 P3、P4控制寄存器8.3.2 P3、P4原理图8.4 LCD端口8.5 LCD端口--定时器/端口比较器9 通用定时器/端口模块9.1 定时器/端口模块操作9.1.1 定时器/端口计数器TPCNT1,8位操作9.1.2 定时器/端口计数器TPCNT2,8位操作9.1.3 定时器/端口计数器,16位操作9.2 定时器/端口寄存器9.3 定时器/端口SFR位9.4 定时器/端口在A/D中的应用9.4.1 R/D转换原理9.4.2 分辨率高于8位的转换10 定时器10.1 Basic Timer110.1.1 BasicTimer1寄存器10.1.2 SFR位10.1.3 BasicTimer1操作10.1.4 BasicTimer1操作:LCD时钟信号f LCD 10.2 8位间隔(Interval)定时器/计数器10.2.1 8位定时器/计数器的操作10.2.2 8位定时器/计数器的寄存器10.2.3 与8位定时器/计数器有关的SFR 10.2.4 8位定时器/计数器在UART中的应用10.3 看门狗定时器10.3.1 看门狗定时器寄存器10.3.2 看门狗定时器中断控制功能10.3.3 看门狗定时器操作10.4 8位PWM定时器10.4.1 操作10.4.2 PWM寄存器11 Timer_A11.1 Timer_A的操作11.1.1 定时器操作11.1.2 捕获模式11.1.3 比较器模式11.1.4 输出单元11.2 Timer_A的寄存器11.2.1 Timer_A控制寄存器TACTL11.2.2 捕获/比较控制寄存器CCTL11.2.3 Timer_A中断向量寄存器11.3 Timer_A的应用11.3.1 Timer_A增计数模式应用11.3.2 Timer_A连续模式应用11.3.3 Timer_A增/减计数模式应用11.3.4 Timer_A软件捕获应用11.3.5 Timer_A处理异步串行通信协议11.4 Timer_A的特殊情况11.4.1 CCR0用作周期寄存器11.4.2 定时器寄存器的启/停11.4.3 输出单元Unit012 USART外围接口,UART模式12.1 异步操作12.1.1 异步帧格式12.1.2 异步通信的波特率发生器12.1.3 异步通信格式12.1.4 线路空闲多处理机模式12.1.5 地址位格式12.2 中断与控制功能12.2.1 USART接收允许12.2.2 USART发送允许12.2.3 USART接收中断操作12.2.4 USART发送中断操作12.3 控制与状态寄存器12.3.1 USART控制寄存器UCTL12.3.2 发送控制寄存器UTCTL12.3.3 接收控制寄存器URCTL12.3.4 波特率选择和调制控制寄存器12.3.5 USART接收数据缓存URXBUF12.3.6 USART发送数据缓存UTXBUF12.4 UART模式,低功耗模式应用特性12.4.1 由UART帧启动接收操作12.4.2 UART模式波特率与时钟频率12.4.3 节约MSP430资源的多处理机模式12.5 波特率的计算13 USART外围接口,SPI模式13.1 USART的同步操作13.1.1 SPI模式中的主模式,MM=1、SYNC=1 13.1.2 SPI模式中的从模式,MM=0、SYNC=1 13.2 中断与控制功能13.2.1 USART接收允许13.2.2 USART发送允许13.2.3 USART接收中断操作13.2.4 USART发送中断操作13.3 控制与状态寄存器13.3.1 USART控制寄存器13.3.2 发送控制寄存器UTCTL13.3.3 接收控制寄存器URCTL13.3.4 波特率选择和调制控制寄存器13.3.5 USART接收数据缓存URXBUF 13.3.6 USART发送数据缓存UTXBUF14 液晶显示驱动14.1 LCD驱动基本原理14.2 LCD控制器/驱动器14.2.1 LCD控制器/驱动器功能14.2.2 LCD控制及模式寄存器14.2.3 LCD显示存储器14.2.4 LCD操作软件例程14.3 LCD端口功能14.4 LCD与端口模式混合应用实例15 A/D转换器15.1 概述15.2 A/D转换操作15.2.1 A/D转换15.2.2 A/D中断15.2.3 A/D量程15.2.4 A/D电流源15.2.5 A/D输入端与多路切换15.2.6 A/D接地与降噪15.2.7 A/D输入与输出引脚15.3 A/D控制寄存器16 其它模块16.1 晶体振荡器16.2 上电电路16.3 晶振缓冲输出附录A 外围模块分布附录B 指令组说明附录C EPROM编程本书用途及表述约定MSP430用户指南以方便工程师及程序员使用的方式提供软件和硬件资料,以帮助开发应用MSP430系列的产品。

MSP430F42X0混合信号微控制器

特性

低电源电压范围:1.8V-3.6V

超低功耗:活动模式:250 A@1MHz,2.2V

待机模式:1.1 A

关闭模式(RAM保持):0.1 A

五种省电模式

6 s内从待机模式唤醒

16位RISC体系,125ns指令周期

16位带内部参考的∑-△模数转换器

12位数模转换器

带3个捕获/比较寄存器的16位定时器Timer_A

节电(Brownout)检测器

引导加载程序(BSL)

串行在线编程,无需外部编程电压

安全熔丝可编程代码保护

集成56段带对比度控制LCD驱动器

MSP430x42x0系列器件包括: - MSP430F4250: 16KB ROM,256B RAM 256B Flash Memory

P1.2/TA1/A4- 26 I/O 通用数字I/O/Timer_A,捕获:CCI1A,比较:Out1输出/模拟输入A4-

P1.1/TA0/MCLK 27 I/O 通用数字I/O/Timer_A,捕获:CCI0B/MCLK输出

P1.0/TA0

28 I/O

通用数字I/O/ Timer_A,捕获:CCI0A 输入/比较:Out0输出/BSL

生器,其余的寄存器可用作通用寄存器.

外设利用一个数据,地址和控制总线连接到CPU,并能容易的利用所有处理指令操作.

PC/R0

SP/R1

SR/CG1/R2

CG2/R3

R4

R5

●

●

R14

R15

程序计数器

堆栈指针

状态寄存器

常数发生器

MSP430单片机基础实验手册

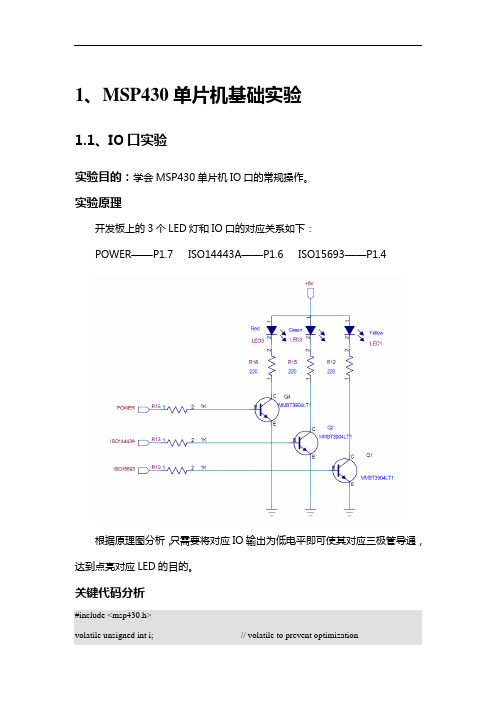

1、MSP430单片机基础实验1.1、IO口实验实验目的:学会MSP430单片机IO口的常规操作。

实验原理开发板上的3个LED灯和IO口的对应关系如下:POWER——P1.7 ISO14443A——P1.6 ISO15693——P1.4根据原理图分析,只需要将对应IO输出为低电平即可使其对应三极管导通,达到点亮对应LED的目的。

关键代码分析#include <msp430.h>volatile unsigned int i; // volatile to prevent optimizationint main(void){WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timerP1DIR |= 0x80; // Set P1.7 to output directionfor (;;){P1OUT ^= 0x80; // Toggle P1.7 using exclusive-ORi = 50000; // Delaydo (i--);while (i != 0);}}对应工程详见:\感知RF2实验光盘2013\RFID技术实验\1-MSP430单片机基础实验\io实验结果POWER对应的LED灯闪烁。

作业1、对其他连个灯进行对应操作;2、流水灯显示编程控制。

1.2、定时器实验实验目的:学会MSP430单片机定时器常规配置及中断操作。

实验原理采用定时器TA溢出中断对LED灯进行取反操作。

关键代码分析#include <msp430.h>int main(void){WDTCTL = WDTPW + WDTHOLD; // Stop WDTP1DIR |= 0x80; // P1.0 outputTACCTL0 = CCIE; // TACCR0 interrupt enabledTACCR0 = 50000;TACTL = TASSEL_2 + MC_2; // SMCLK, contmode__bis_SR_register(LPM0_bits + GIE); // Enter LPM0 w/ interrupt}// Timer A0 interrupt service routine#pragma vector=TIMERA0_VECTOR__interrupt void Timer_A (void){P1OUT ^= 0x80; // Toggle P1.7TACCR0 += 50000; // Add Offset to TACCR0}对应工程详见\感知RF2实验光盘2013\RFID技术实验\1-MSP430单片机基础实验\timer实验结果LED灯快速闪烁,改变TACCR0值,闪烁时间间隔改变。

MSP430F2XX中文手册(加了标签) 12.SPI 串行同步通讯模式

Page 4 of 14

MSP430 F2 系列超低功耗单片机模块原理 第 12 章 串行同步通讯模式 SPI

微控设计网

图12-2 通用串行通信接口主机和从机

图12-2说明了USCI在3线和4线模式下作为主机时的配置。当数据被送到传输数据缓冲器 UCxTXBUF时,USCI开始数据传送。当TX移位寄存器空了后,UCxTXBUF缓冲区的数据被传送到其 中, 在UCxSIMO上传送数据, 起始位是最高位还是最低位, 决定于UCMSB标志位的设置。 而UCxSOMI 上的数据在反向跳边沿下移入接收移位寄存器。当字符接收到之后,接收数据从RX移位寄存器 送入接收数据缓冲器UCxRXBUF,并且置位接收中断标志UCxRXIFG,表示接收/发送操作完成。 发送中断标志位UCxTXIFG被置位后,表明数据已从UCxTXBUF缓冲区进入TX移位寄存器, UCxTXBUF寄存器已经为发送新数据做好准备,但并不意味着传送和接收的完成。 为了在主机模式下接收USCI数据,数据必须事先写入UCxTXBUF,因为接收和发送操作不是 马上进行的。 4线SPI主机模式 在4线主机模式中,UCxSTE用来防止与其它主机相冲突并象表12-1描述的那样控制主机。当 UCxSTE处于主机不活动状态时: UCxSIMO 和 UCxCLK设置为输入,不再驱动总线。 出错位UCFE置位,表明在通讯的完整性上,使用者未按照规则操作。 内部状态被复位时,移位操作取消。 如果数据写入UCxTXBUF而主机通过UCxSTE位保持非工作状态, UCxSTE转换为主机工作状态, 数据立即被发送。如果一个正在工作的发送过程,因UCxSTE转换为主机不运行状态而取消时, 当UCxSTE转向主机运行状态时数据需要被重新写入UCxTXBUF。 UCxSTE输入信号不能应用3线主机 模式。 12.3.4 从机模式

MSP430F1XXX系列中文数据手册

QFN Pad

NA

建议将QFN 的封装衬垫接 VSS

TDO/TDI是用JTAG指令来区分的.

公司地址:杭州市登云路 639 号电子市场四楼 C 区 电话:0571-88800000(50 线) 传真:0571-89908080

- 5-

利尔达科技有限公司

销售热线:0571-89908088

89908091

确保代码安全

-待机模式:0.7 uA

·欠压检测电路

-掉电模式(RAM 数据保持):0.1uA

·MSP430X11X2 系列包括

·五种省电模式

MSP430F1122:4KB+256B FLASH 存储器

·从待机到唤醒不超过 6us

256B RAM

·16 位精简指令集架构,指令周期 125us

MSP430F1132:8KB+256B FLASH 存储器

输入;比较方式:OUT0输出/BSL发送端

P1.2/TA1

通用数字I/O口/定时器A捕获方式:CCI1A

23

23

I/O 输入;比较方式:OUT1输出

P1.3/TA2

24

24

I/O 通用数字I/O口/定时器A捕获方式:CCI2A

输入;比较方式:OUT2输出

P1.4/SMCLK/TCK

通用数字I/O口/SMCLK时钟信号输出/在芯

·基本的时钟模块

256B RAM

-DCO 时钟发生器集成多个可选电阻

封装:28 脚 SOWB 封装,28 脚 TSSOP 和 32 脚 QFN

-DCO 时钟发生器可接外部电阻

封装

-外部 32kHz 晶振

·MSP430X12X2 系列包括

MSP430指导书

目录目录 (I)实验一I/O端口控制实验 (1)实验二乘法器实验 (2)实验三PWM脉冲实验 (3)实验四LED数码显示实验 (4)实验五LCD段码屏显示实验 (6)实验六定时器实验 (8)实验七比较器实验 (10)实验八内部看门狗实验 (13)实验九电子时钟实验 (15)实验十独立键盘实验 (16)实验十一阵列键盘实验 (17)实验十二时钟模块FLL+操作实验 (18)实验十三 12位AD转换实验 (19)实验十四外部FLASH扩展实验 (20)实验十五I2C AT24C02实验 (22)实验十六 128×64点阵液晶显示实验(选配) (24)实验十七 RS-232通信实验 (25)IMSP430核心板的供电方式MSP430核心板有2种供电方式:1.由USB取提供,同时J0短路冒打在右边,J1短路冒打在左边,J6短路冒打在上方。

2.由外部5V的直流电源提供,把内正外负的5V电源插入JT9座,同时J0短路冒打在左边,J1短路冒打在右边,J6短路冒打在上方。

(注:5V电源用户选配)3.出厂程序为电子时钟程序,上电后自动运行电子时钟,数码管和段码LCD同时显示!II实验一 I/O端口控制实验一、实验目的1.掌握MSP430449一般IO口的应用2.掌握端口寄存器的组成和使用二、实验说明MSP430F1XX系列单片机最多有6个I/O口:P1~P6,每个端口有8个管脚。

每个管脚可以单独设置成输入或者输出方向,并且每个管脚都可以进行单独的读或者写。

P1口和P2口具有中断功能,P1口和P2口的每个管脚都可以单独设置成中断,并且可以设置成上升沿或者下降沿触发中断。

P1口的所有管脚共用一个中断向量,同样P2口的所有管脚也共用一个中断向量。

MSP430F1XX系列单片机的I/O口主要有以下特征:每个I/O口可以独立编程设置。

输入输出可以任意结合使用。

P1口和P2口的中断功能可以单独设置。

有独立的输入输出寄存器。

MSP430初学者教程(最详细)

如何学习学习就是迎接挑战、解决困难的过程,没有挑战,就没有人生的乐趣。

下面以系列为例,解释一下学习的过程。

(1)获取资料购买有关书籍,并到杭州利尔达公司网站和TI网站获取资料,例如,在网上可以找到FET 使用指导、F1xx系列、F4xx系列的使用说明和具体芯片的数据说明,可以找到FET的、实验板、知识等大量的实际应用参考电路,当然有些资料是英文的,看懂英文资料是个挑战,学会4、6级英语就是为看资料的。

英语难学,但是看资料容易,只要下决心,看完一本资料,就可以看懂所有的相关资料。

(2)购买FET和实验电路板如果经济条件不错,可以直接购买。

(3)自制FET和实验电路板自制仿真器FET,首先要到网上找到FET,然后就可以使用画电路板软件画电路图和电路板图,这又是个挑战。

FET电常简单,但要把它制作出来还是需要下一番工夫的,找一本有关书,然后练习画,画完后,就学习认识,再购买元件,这时就可以画电路板图了,一旦画好,将形成的PCB文件交给公司,10天后,就可以得到电路板,焊上元件和电缆,等实验电路板做好后,就可以与实验电路板一起调试了。

自制实验电路板,需要单片机芯片内部工作原理的知识、封装知识,清楚的知道每一个的功能,还需要、按钮、、三端、、散热器、、普通电容、电阻、等元件的知识,对于初学者,可以做一个只有3个、8个按钮、8个的简单实验板,这样的实验板,虽然简单,但足可以帮助初学者入门单片机。

自制实验电路板与自制FET一样,首先画电路图,然后买元件,再画电路板。

由于系列芯片是扁平封装,焊接起来有一定难度,这好象是个挑战,但实际上很简单,方法如下:首先在焊盘上涂上,在未干的情况下,将芯片放在焊盘上,注意芯片第一的位置,并使与焊盘对齐,将擦干净的(不能有任何)接触引脚,引脚只要一热,焊盘上的就自动将引脚焊住了,千万注意上不能有,焊接时最好配备一个。

焊接电路板时,每一个元件都要核对参数,可以用万用表测量的元件一定要测量。

MSP430F2XX中文手册(加了标签) 5.Flash块控制器

Page 1 of 18MSP430F2系列16位超低功耗单片机模块原理第5章 Flash 块控制器版本: 1.3日期: 2007.6.原文: TI MSP430x2xxfamily.pdf翻译: 余川编辑: DC 微控技术论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

第五章 Flash 存储控制器本章介绍了MSP430x2xx 系列单片机Flash 存储控制器的操作。

5.1 Flash 存储器的介绍Page 2 of 18 5.2 Flash 存储器的分段结构5.3 Flash 存储器的操作5.4 Flash 存储器的控制寄存器5.1 Flash 存储器的介绍MSP430 的F lash 存储器是可位/字节/字寻址和编程的存储器。

该模块由一个集成控制器来控制编程和擦除的操作。

控制器包括三个寄存器,一个时序发生器及一个提供编程/擦除电压的电压发生器。

MSP430 的F lash 存储器的特点有:● 产生内部编程电压● 可位/字节/字编程● 超低功耗操作● 支持段擦除和多段模块擦除F lash 存储器和控制器的结构框图如图5−1所示。

注意:F lash 写入和擦除操作期间的最小电压值V CC 应为2.2V 。

如果在操作期间V CC 低于2.2V ,写入或擦除的结果将是不确定的。

图5−1 F lash 存储器框图Page 3 of 185.2 Flash 存储器的分段结构MSP430 F lash 存储器分成多个段。

可对其进行单个位/字节/字的写入,但是最小的擦除单位是段。

F lash 存储器分为主存储器和信息存储器两部分,在操作上两者没有什么区别,程序代码和数据可以存储于任意部分。

两部分的区别在于段的大小和物理地址。

信息存储器有四个64字节的段,主存储器有两个或更多的512字节的段。

[计算机软件及应用]15MSP430中文用户指南

![[计算机软件及应用]15MSP430中文用户指南](https://img.taocdn.com/s3/m/b69a5036443610661ed9ad51f01dc281e53a5681.png)

T EXAS I NSTRUMENTSMSP430系列混合信号微控制器结构及模块用户指南目录1MSP430系列1.1特性与功能1.2系统关键性能1.3MSP430系列的各型号2结构概述2.1CPU2.2代码存储器2.3数据存储器(RAM)2.4运行控制2.5外围模块2.6振荡器、倍频器和时钟发生器3系统复位、中断和运行模式3.1系统复位和初始化3.2中断系统结构3.3中断处理3.3.1SFR中的中断控制位3.3.2外部中断3.4运行模式3.5低功耗模式3.5.1 低功耗模式0与模式1,LPM0和LPM1 3.5.2 低功耗模式2与模式3,LPM2和LPM3 3.5.3 低功耗模式4,LPM43.6 低功耗应用要点4 存储器组织4.1 存储器中的数据4.2 片内ROM组织4.2.1 ROM表的处理4.2.2 计算分支跳转和子程序调用4.3 RAM与外围模块组织4.3.1 RAM4.3.2 外围模块—地址定位4.3.3 外围模块--SFR5 16位CPU5.1 CPU寄存器5.1.1 程序计数器PC5.1.2 系统堆栈指针SP5.1.3 状态寄存器SR5.1.4 常数发生寄存器CG1与CG25.2 寻址模式5.2.1 寄存器模式5.2.2 变址模式5.2.3 符号模式5.2.4 绝对模式5.2.5 间接模式5.2.6 间接增量模式5.2.7 立即模式5.2.8 指令的时钟周期与长度5.3 指令组概述5.3.1 双操作数指令5.3.2 单操作数指令5.3.3 条件跳转5.3.4 模拟指令的短格式5.3.5 其它指令5.4 指令分布6 硬件乘法器6.1 硬件乘法器的操作6.2 硬件乘法器的寄存器6.3 硬件乘法器的SFR位6.4 硬件乘法器的软件限制6.4.1 硬件乘法器软件限制--寻址模式 6.4.2 硬件乘法器软件限制--中断程序7 振荡器与系统时钟发生器7.1 晶体振荡器7.2 处理机时钟发生器7.3 系统时钟运行模式7.4 系统时钟控制寄存器7.4.1 模块寄存器7.4.2 与系统时钟发生器相关的SFR位 7.5 DCO典型特性8 数字I/O配置8.1 通用端口P08.1.1 P0控制寄存器8.1.2 P0原理图8.1.3 P0中断控制功能8.2 通用端口P1、P28.2.1 P1、P2控制寄存器8.2.2 P1、P2原理图8.2.3 P1、P2中断控制功能8.3 通用端口P3、P48.3.1 P3、P4控制寄存器8.3.2 P3、P4原理图8.4 LCD端口8.5 LCD端口--定时器/端口比较器9 通用定时器/端口模块9.1 定时器/端口模块操作9.1.1 定时器/端口计数器TPCNT1,8位操作 9.1.2 定时器/端口计数器TPCNT2,8位操作 9.1.3 定时器/端口计数器,16位操作9.2 定时器/端口寄存器9.3 定时器/端口SFR位9.4 定时器/端口在A/D中的应用9.4.1 R/D转换原理9.4.2 分辨率高于8位的转换10 定时器10.1 Basic Timer110.1.1 BasicTimer1寄存器10.1.2 SFR位10.1.3 BasicTimer1操作10.1.4 BasicTimer1操作:LCD时钟信号f LCD 10.2 8位间隔(Interval)定时器/计数器 10.2.1 8位定时器/计数器的操作10.2.2 8位定时器/计数器的寄存器10.2.3 与8位定时器/计数器有关的SFR 10.2.4 8位定时器/计数器在UART中的应用 10.3 看门狗定时器10.3.1 看门狗定时器寄存器10.3.2 看门狗定时器中断控制功能10.3.3 看门狗定时器操作10.4 8位PWM定时器10.4.1 操作10.4.2 PWM寄存器11 Timer_A11.1 Timer_A的操作11.1.1 定时器操作11.1.2 捕获模式11.1.3 比较器模式11.1.4 输出单元11.2 Timer_A的寄存器11.2.1 Timer_A控制寄存器TACTL11.2.2 捕获/比较控制寄存器CCTL11.2.3 Timer_A中断向量寄存器11.3 Timer_A的应用11.3.1 Timer_A增计数模式应用11.3.2 Timer_A连续模式应用11.3.3 Timer_A增/减计数模式应用11.3.4 Timer_A软件捕获应用11.3.5 Timer_A处理异步串行通信协议 11.4 Timer_A的特殊情况11.4.1 CCR0用作周期寄存器11.4.2 定时器寄存器的启/停11.4.3 输出单元Unit012 USART外围接口,UART模式12.1 异步操作12.1.1 异步帧格式12.1.2 异步通信的波特率发生器12.1.3 异步通信格式12.1.4 线路空闲多处理机模式12.1.5 地址位格式12.2 中断与控制功能12.2.1 USART接收允许12.2.2 USART发送允许12.2.3 USART接收中断操作12.2.4 USART发送中断操作12.3 控制与状态寄存器12.3.1 USART控制寄存器UCTL12.3.2 发送控制寄存器UTCTL12.3.3 接收控制寄存器URCTL12.3.4 波特率选择和调制控制寄存器12.3.5 USART接收数据缓存URXBUF12.3.6 USART发送数据缓存UTXBUF12.4 UART模式,低功耗模式应用特性 12.4.1 由UART帧启动接收操作12.4.2 UART模式波特率与时钟频率12.4.3 节约MSP430资源的多处理机模式 12.5 波特率的计算13 USART外围接口,SPI模式13.1 USART的同步操作13.1.1 SPI模式中的主模式,MM=1、SYNC=1 13.1.2 SPI模式中的从模式,MM=0、SYNC=1 13.2 中断与控制功能13.2.1 USART接收允许13.2.2 USART发送允许13.2.3 USART接收中断操作13.2.4 USART发送中断操作13.3 控制与状态寄存器13.3.1 USART控制寄存器13.3.2 发送控制寄存器UTCTL13.3.3 接收控制寄存器URCTL13.3.4 波特率选择和调制控制寄存器 13.3.5 USART接收数据缓存URXBUF 13.3.6 USART发送数据缓存UTXBUF14 液晶显示驱动14.1 LCD驱动基本原理14.2 LCD控制器/驱动器14.2.1 LCD控制器/驱动器功能14.2.2 LCD控制及模式寄存器14.2.3 LCD显示存储器14.2.4 LCD操作软件例程14.3 LCD端口功能14.4 LCD与端口模式混合应用实例15 A/D转换器15.1 概述15.2 A/D转换操作15.2.1 A/D转换15.2.2 A/D中断15.2.3 A/D量程15.2.4 A/D电流源15.2.5 A/D输入端与多路切换15.2.6 A/D接地与降噪15.2.7 A/D输入与输出引脚15.3 A/D控制寄存器16 其它模块16.1 晶体振荡器16.2 上电电路16.3 晶振缓冲输出附录A 外围模块分布附录B 指令组说明附录C EPROM编程本书用途及表述约定MSP430用户指南以方便工程师及程序员使用的方式提供软件和硬件资料,以帮助开发应用MSP430系列的产品。

msp430f系列中文资料

超低功耗微控制器MSP430F40xi n de s i g n x31xLCD92x32xLCD84ADC14x33xLCD120Timer_A USART MPY8-bit T/Cx11x1Comp_AX12x USARTi n de s i g n F13xTimer_B ADC12USART Comp_AF14xTimer_B ADC122 USART MPY Comp_ANewNewF41xi n de s i g n F42xi n de s i g n F44xi n de s i g nUltra -low power design withM S P430August 00 / 11FLASH 型的时钟系统(F13x,F14x)2 个晶振, 1 个DCO, 适应不同频率需要采样/转换控制可编程参考源选择片内温度传感器Ultra -low power design withM S P430August 00 / 34F11x 应用实例)Floating Point Package)Starter Kit MSP-STK430X320TI 软件包仿真器评估板TI 软件库C-编译器编程器)TI Programming AdapterAugust 00 / 37New电源的高效率y电池缩减/ 电池寿命延长y电源电路简化/ 可远程供电硬件简化y外部元件极少y集成实时钟y集成LCD 驱动电路y集成ADC加速产品开发y用Flash 或OTP 型可快速制作样机y用Flash 型可作现场更新y容易学习和设计程序y代码效率高廉价的微控制器MSP430和开发工具FET/sc/docs/products/micro/msp430E-mail: lierda@ (wzptt)/sc/docs/products/micro/msp430E-mail: lierda@ (wzptt)。

MSP430中文资料

MSP430X1X1 系列产品中,其中 XT1 时钟源引脚接法有如 3 种应用。F13、14 的 XT1 相 同。需要注意的是,LFXT1 只有工作在高频模式下才需要外接电容。 对以引脚较少的 MSPX1XX 系列产品中有着不同时基模块,具体如下:

MSP430X11X1:LFXT1CLK , DCO

MSP430F12X: LFXT1CLK , DCO

MSP430F13X/14X/15X/16X:LFXT1CLK , DCO , XT2CLK

MSP430F4XX: LFXT1CLK , DCO , XT2CLK , FLL+

时钟发生器的原理说明: 问题的提出:1、高频、以便能对系统硬件请求和事件作出快速响应

微控设计网

微控设计网 中国 MSP430 单片机专业网站 MSP430F 常用模块应用原理

微控设计网 版主 DC 策划 原创于:2006-3-7

最后更新:2008-5-31 V8.2

微控设计网为你准备的 MSP430F 单片机入门必修课

XT5V 此位设置为 0。

Resl1.0,Resl1.1,Resl1.2 三位控制某个内部电阻以决定标称频率。

Resl=0,选择最低的标称频率。 …….. Resl=7,选择最高的标称频率。

BCSCTL2 基本时钟系统控制寄存器 2

7

6

54ຫໍສະໝຸດ SELM.1 SELM.0 DIVM.1 DIVM.0

mps430手册

msp430芯片选型中文手册指南F1XX系列Vcc1.8V-3.6V型号MSP430F1101A参数说明1KBflash,128BRam;slopeA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),比较器_A;20DW、PW封装型号MSP430F1111A参数说明2KBflash,128BRam;slopeA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),比较器_A;20DW、PW封装型号MSP430F1121A参数说明4KBflash,256BRam;slopeA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),比较器_A;20DW、PW封装型号MSP430F1122参数说明4KBflash,256BRam;5通道10bitA/D;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器),温度传感器;20DW、PW封型号MSP430F1132参数说明8KBflash,256BRam;5通道10bitAD;14个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);温度传感器;20DW、PW封型号MSP430F122参数说明4KBflash,256BRam;slopeA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口,比较器A;28DW、PW封装型号MSP430F123参数说明8KBflash,256BRam;slopeA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口,比较器A;28DW、PW封装型号MSP430F1222参数说明4KBflash,256BRam;8通道10bitA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口;温度传感器;28DW、PW封装型号MSP430F1232参数说明8KBflash,256BRam;8通道10bitA/D;22个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口;温度传感器;28DW、PW封装型号MSP430F133参数说明8KBflash,256BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;比较器_A;温度传感器;64PM封装型号MSP430F135参数说明16KBflash,512BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;比较器_A;温度传感器;64PM封装型号MSP430F147参数说明32KBflash,1024BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1471参数说明32KBflash,1024BRam;slopeA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;64PM封装型号MSP430F148参数说明48KBflash,2048BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1481参数说明48KBflash,2048BRam;slopeA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;64PM封装型号MSP430F149参数说明60KBflash,2048BRam;8通道12bitA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1491参数说明60kflash,2048BRam;slopeA/D;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;64PM封装型号MSP430F155参数说明16KBflash,512BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;I2C;比较器_A;温度传感器;64PM封装型号MSP430F156参数说明24KBflash,512BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;I2C;比较器_A;温度传感器;64PM封装型号MSP430F157参数说明32KBflash,1024BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;I2C;比较器_A;温度传感器;64PM封装型号MSP430F167参数说明32KBflash,1024BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F168参数说明48KBflash,2048BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F169参数说明60KBflash,2048BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1610参数说明32KBflash,5120BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1611参数说明48KBflash,10240BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B (7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装型号MSP430F1612参数说明55kBflash,5120BRam;8通道12bitA/D;双12bitD/A;DMA;48个I/O口;16位WDT;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;I2C;MPY;比较器_A;温度传感器;64PM封装F21X1系列Vcc1.8V-3.6V型号MSP430F2101参数说明1KBflash,128BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装型号MSP430F2111参数说明2KBflash,128BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装型号MSP430F2121参数说明4KBflash,256BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装型号MSP430F2131参数说明8KBflash,256BRam;slopeA/D;16个I/O口;15/16位WDT;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;BrownoutProtection;20DW、PW、DGV封装F4XX系列Vcc1.8V-3.6VWithLCD驱动型号MSP430F412参数说明4KBflash,256BRam;slopeA/D;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;64PM封装型号MSP430F413参数说明8KBflash,256BRam;slopeA/D;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);比较器_A;64PM封装型号MSP430F415参数说明16kBflash,512BRam;slopeA/D;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM 封装型号MSP430F417参数说明32kBflash,1024BRam;slopeA/D;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM 封装型号MSP430FE423参数说明8KBflash,256BRam;SD16A/D;Emeter计量模块;14个I/O口;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口;温度传感器;64PM封装型号MSP430FE425参数说明16KBflash,512BRam;SD16A/D;Emeter计量模块;14个I/O口;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口;温度传感器;64PM封装型号MSP430FE427参数说明32KBflash,1KBRam;SD16A/D;Emeter计量模块;14个I/O口;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个USART接口;比较器_A;温度传感器;64PM封装型号MSP430F4250参数说明16KBflash,256BRam;32个I/O口;56段LCD;SD16位ADC (具有内部参考电压);12位DAC,1个16位Timer_A(3个捕获/比较寄存器);温度传感器模块;电源检测功能;48DL封装型号MSP430F4260参数说明24KBflash,256BRam;32个I/O口;56段LCD;SD16位ADC (具有内部参考电压);12位DAC,1个16位Timer_A(3个捕获/比较寄存器);温度传感器模块;电源检测功能;48DL封装型号MSP430F4270参数说明32KBflash,256BRam;32个I/O口;56段LCD;SD16位ADC (具有内部参考电压);12位DAC,1个16位Timer_A(3个捕获/比较寄存器);温度传感器模块;电源检测功能;48DL封装型号MSP430FG437参数说明32KBflash,1024BRam;12通道12bitA/D;双12bitD/A;48个I/O口;DMA;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;温度传感器;80PN 封装型号MSP430FG438参数说明48KBflash,2048BRam;12通道12bitA/D;双12bitD/A;48个I/O口;DMA;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;温度传感器;80PN 封装型号MSP430FG439参数说明60KBflash,2048BRam;12通道12bitA/D;双12bitD/A;48个I/O口;DMA;128段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(3个捕获/比较寄存器);1个USART接口;温度传感器;80PN 封装型号MSP430FW423参数说明8KBflash,256BRam;slopeA/D;流量测量ScanIF模块;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM封装型号MSP430FW425参数说明16KBflash,512BRam;slopeA/D;流量测量ScanIF模块;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM封装型号MSP430FW427参数说明32KBflash,1024BRam;slopeA/D;流量测量ScanIF模块;48个I/O口;96段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3或5个捕获/比较寄存器);比较器_A;64PM封装型号MSP430F435参数说明16KBFlash,512BRam;8通道12bitA/D;48个I/O口;128/160段LCD;16位WDT;8bit基本定时器;16位Timer_A(3个捕获/比较寄存器)_A;16位Timer_B(3个捕获/比较寄存器)_B;1个USART接口;比较器_A;温度传感器;80PN/100PZ封装型号MSP430F436参数说明24KBFlash,1024KRam;8通道12bitA/D;48个I/O口;128/160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器)_B;1个USART接口;比较器_A;温度传感器;80PN/100PZ封装型号MSP430F437参数说明32KBFlash,1024KRam;8通道12bitA/D;48个I/O口;128/160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器)_A;1个16位Timer_B(3个捕获/比较寄存器)_B;1个USART接口;比较器_A;温度传感器;80PN/100PZ封装型号MSP430F447参数说明32KBFlash,1024KRam;8通道12bitA/D;48个I/O口;160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;100PZ 封装型号MSP430F448参数说明48KBflash,2048BRam;8通道12bitA/D;48个I/O口;160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;100PZ 封装型号MSP430F449参数说明60KBflash,2048BRam;8通道12bitA/D;48个I/O口;160段LCD;16位WDT;8bit基本定时器;1个16位Timer_A(3个捕获/比较寄存器);1个16位Timer_B(7个捕获/比较寄存器);2个USART接口;MPY;比较器_A;温度传感器;100PZ 封装型号TSS721AD参数说明M-BUS总线型号TRF6901PT参数说明无线射频率收发芯片。

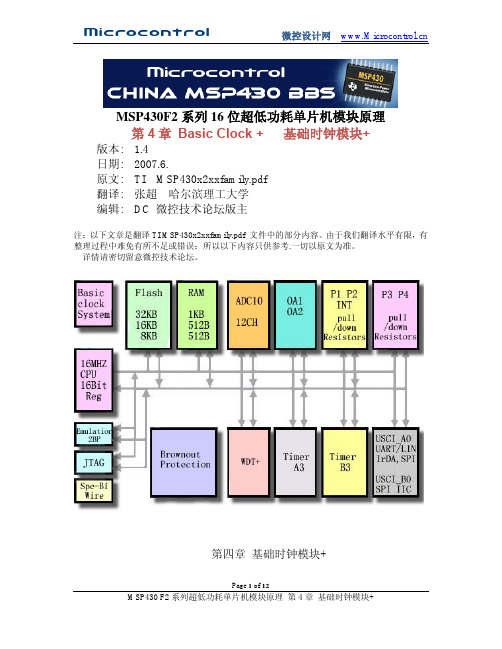

MSP430F2XX中文手册(加了标签) 4.基础时钟模块+

Page 1 of 12MSP430F2系列16位超低功耗单片机模块原理第4章 Basic Clock + 基础时钟模块+版本: 1.4日期: 2007.6.原文: TI MSP430x2xxfamily.pdf翻译: 张超 哈尔滨理工大学编辑: DC 微控技术论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

第四章 基础时钟模块+4.1基础时钟模块+介绍基础时钟模块+支持低系统消耗和超低功耗。

采用三种片内时钟信号,用户可以选择合适的性能和低功耗。

基础时钟模块只需接一个外部电阻、一个或两个外部晶体、或者用振荡器,通过软件控制。

基础时钟模块+有4个时钟源:LFXT1CLK:由低频时钟晶体或外接32768Hz时钟源产生的低频/高频振荡器或由标准晶体、振荡器,或外部400KH z~16M Hz的外部时钟源提供。

XT2CLK:可供选择的高频振荡器,由标准晶体、振荡器,或外部400KH z~16M Hz的外部时钟源提供。

DCOCLK:片内可数字控制的振荡器。

VLOCLK:片内超低功耗、12KH z的低频振荡器。

基础时钟模块可提供的三种时钟信号:ACLK:辅助时钟。

ACLK由软件选择来自LFXT1CLK和VLOCLK之一的时钟信号。

ACLK 经1,2,4,8分频后得到。

ACLK可由软件选作各个外围模块。

MCLK:主时钟。

MCLK由软件选择来自LFXT1CLK,VLOCLK,XT2CLK(如果片内提供),DCOCLK之一的时钟信号。

MCLK由1,2,4,8分频得到。

MCLK用于CPU和系统。

SMCLK:子系统时钟。

SMCLK由软件选择来自LFXT1CLK,VLOCLK,XT2CLK(片内提供),DCOCLK之一的时钟信号。

SMCLK由1,2,4,8分频得到。

MSP430F4XX中文技术手册

– MSP430F412: 4KB + 256B Flash Memory,256B RAM;

– MSP430F413: 8KB + 256B Flash Memory,256B RAM;

MSP430单片机数据手册—英

IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2004, Texas Instruments Incorporated。

MSP430F2XX中文手册(加了标签) 1..MSP430体系结构

MSP430F2系列16位超低功耗单片机模块原理第1章MSP430体系结构版本: 1.3日期: 2007.4.原文: TI MSP430x2xxfamily.pdf翻译: 袁德纯编辑: DC 微控论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

Page 1 of 7第一章 MSP430的体系结构本章主要描述了MSP430的体系结构本章内容目录1.1MSP430的体系结构1.2可编程时钟系统1.3嵌入式仿真环境1.4地址空间1.5MSP430X2XX系列的提高1.1MSP430的体系结构将MSP430内部的16位精简指令集的CPU通过冯.诺依曼结构的地址总线和数据总线连接到外围设备和可编程时钟系统。

由于有一个先进的CPU配合具有标准组件存储印象的模拟和数字的外围设备,使得MSP430可用于处理混合信号。

MSP430x2xx系列的主要特性如下:◆超低功耗延长了电池的使用寿命●保持RAM 0.1uA●实时时钟模式 0.8uA●MIPS运行 250uA◆理想精确的模拟信号测量●门控比较定时器测量电阻类元件◆16位的精简指令集的CPU全新应用●更大的寄存器空间消除了运行空间的瓶颈●紧凑的核结构设计减少了功耗、降低了成本●使得高水平的编程更优化●27条核心指令和7种寻址方式●强大的矢量中断能力◆系统内的可编程FLASH使改变代码、在线升级和数据载入更灵活1.2 可编程时钟系统时钟系统是为电池供电系统而特别设计的。

只需要一个32KHZ的晶振就可以直接驱动一个低频的辅助时钟(ACLK)。

ACLK可工作于实时时钟模式,并具能够自我唤醒。

内部集成了一个DCO使主时钟(MCLK)可以被CPU和其他的高速外围设备所使用。

由于有了DCO,使得一个窄脉冲在少于2US 的时间内就可以将MSP430唤醒CPU工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MSP430F4XX 中文技术手册

47

46 I/O 通用数字I/O/比较器A 输入脚 45 I/O 通用数字I/O/定时器_A. 捕获方式: CCI2A 输入, 比较方式: Out2 输出 44 I/O 通用数字I/O/定时器_A. 捕获方式: CCI1A 输入, 比较方式: Out1 输出 35 I/O 通用数字I/O/定时器_A. 捕获方式: CCI2A 输入, 比较方式: Out2 输出

44

P2.2/S23

35

P2.3/S22

34

P2.4/S21

33

P2.5/S20

32

P2.6/CAOUT/S19 31

P2.7/S18

30

P3.0/S17

29

P3.1/S16

28

P3.2/S15

27

P3.3/S14

26

P3.4/S13

25

P3.5/S12

24

I/O 描述

模拟正电源端,向电压检测电路, brownout, 晶体震荡电路, 锁频环电路, 比较器A,端口1,以及液晶分压电阻网络供电,上电不必早于DVCC. 内部连接于 DVSS 数字正电源端,提供所有部件电源(由 AVCC 供电的除外) 数字地,所有部件的接地(通过AVCC/AVSS. 供电的除外)

2/41

MSP430F4XX 中文技术手册

MSP430X415、MSP430X417引脚定义:

MSP430x412、MSP430x413功能模块图如下:

3/41

MSP430F4XX 中文技术手册

MSP430x415、MSP430x417功能模块图如下:

MSP430x412、MSP430x413引脚功能

– MSP430F412: 4KB + 256B Flash Memory,256B RAM;

– MSP430F413: 8KB + 256B Flash Memory,256B RAM;

– MSP430F415: 16KB + 256B Flash Memory,512B RAM;

– MSP430F417: 32KB + 256B Flash Memory,1KB RAM;

5/41

P1.7/CA1

P2.0/TA0.2

P2.1/TA1.1

P2.2/TA1.2/S23

P2.3/TA1.3/S22

P2.4/TA1.4/S21

P2.5/TA1CLK/S20 P2.6/CAOUT/S19 P2.7/S18

P3.0/S17

P3.1/S16

P3.2/S15

P3.3/S14

P3.4/S13

空脚 I/O 通用数字I/O/定时器_A. 捕获方式:CCI0A 输入, 比较方式: Out0 输出 I/O 通用数字I/O/定时器_A. 捕获方式:CCI0B 输入/MCLK 输出, 注意:在这

个引脚上,TA0 只能输入, I/O 捕获方式: CCI1A 输入, 比较方式:Out1 输出 I/O 通用数字l I/O /SVS: SVS 比较器的输出端 I/O 通用数字 I/O,CC10A 输入,OUT0 输出 I/O 通用数字 I/O / 定时器A 输入时钟/ ACLK 输出 I/O 通用数字I/O/比较器A 输入脚

引脚名称编号

AVCC

64

AVSS 62

DVCC 1

DVSS 63

NC 7,10,11

P1.0/TA0

53

P1.1/TA0/MCLK

52

P1.2/TA1

51

P1.3/SVSOut 50

P1.4

49

P1.5/TACLK/ ACLK 48

P1.6/CA0

47

P1.7/CA1

46

P2.0/TA2

45

P2.1

典型应用: 捕获传感器的模拟信号转换为数据加以处理后发送到主机。其中芯片中的比较器和定时器是工业仪表、

计数装置和手持式仪表等产品设计中的理想选择。

1/41

可选型号

MSP430F4XX 中文技术手册

封装形式PLASTIC 64-PIN

TA

QFP (PM)

-40℃—85℃

MSP430C412IPM MSP430C413IPM MSP430F412IPM MSP430F413IPM MSP430F415IPM MSP430F417IPM

51 50 49 48

I/O 描述

模拟正电源端,向电压检测电路, brownout, 晶体震荡电路, 锁频环电路, 比较器A,端口1,以及液晶分压电阻网络供电,上电不必早于DVCC. 内部连接于 DVSS

数字正电源端,提供所有部件电源(由 AVCC 供电的除外) 数字地,所有部件的接地(通过AVCC/AVSS. 供电的除外) 内部连接于 DVSS

40

I LCD 模拟电平第四极输入脚(最低电平V5)

41

I/O 通用数字I/O/ LCD 模拟电平第三极输入脚(最低电平V3 或V4)

42

I/O 通用数字I/O/ LCD 模拟电平第二极输入脚(最低电平V2)

43

I/O 通用数字I/O/ LCD 模拟电平第一极输入脚(最低电平V1)

59

I/O 通用数字I/O 脚

封装形式PLASTIC 64-PIN QFN (RTD)

MSP430C412IRTD§ MSP430C413I RTD§ MSP430F412I RTD MSP430F413I RTD MSP430F415I RTD§ MSP430F417I RTD§

MSP430X412、MSP430X413引脚定义:

4/41

P3.6/S11 P3.7/S10 P4.0/S9 P4.1/S8 P4.2/S7 P4.3/S6 P4.4/S5 P4.5/S4 P4.6/S3 P4.7/S2 P5.0/S1 P5.1/S0 COM0 P5.2/COM1 P5.3/COM2 P5.4/COM3 R03 P5.5/R13 P5.6/R23 P5.7/R33 P6.0 P6.1 P6.2 P6.3 P6.4 P6.5 P6.6D 段1 输出脚 (见注1)

12

I/O 通用数字I/O/LCD 段0 输出脚 (见注1)

36

O LCD 公共输出端COM0.

37

I/O 通用数字I/O/ LCD 公共输出端COM1

38

I/O 通用数字I/O/ LCD 公共输出端COM2

39

I/O 通用数字I/O/ LCD 公共输出端COM3

MSP430X417引脚功能

引脚名称编号

AVCC

AVSS1 DVCC DVSS AVSS2 NC P1.0/TA0.0

64

62 1 63

10 7, 11

53

P1.1/TA0.0/MCLK

52

P1.2/TA0.1 P1.3/SVSOut P1.4/TA1.0 P1.5/TA0CLK/ ACLK P1.6/CA0

空脚 I/O 通用数字I/O/定时器_A. 捕获方式:CCI0A 输入, 比较方式: Out0 输出 I/O 通用数字I/O/定时器_A. 捕获方式:CCI0B 输入/MCLK 输出, 注意:在这

个引脚上,TA0 只能输入, I/O 捕获方式: CCI1A 输入, 比较方式:Out1 输出 I/O 通用数字l I/O /SVS: SVS 比较器的输出端 I/O 通用数字 I/O I/O 通用数字 I/O / 定时器A 输入时钟/ ACLK 输出 I/O 通用数字I/O/比较器A 输入脚 I/O 通用数字I/O/比较器A 输入脚 I/O 通用数字I/O/定时器_A. 捕获方式: CCI2A 输入, 比较方式: Out2 输出 I/O 通用数字 I/O I/O 通用数字I/O/LCD 段23 输出脚 (见注1) I/O 通用数字I/O/LCD 段22 输出脚 (见注1) I/O 通用数字I/O/LCD 段21 输出脚 (见注1) I/O 通用数字I/O/LCD 段20 输出脚 (见注1) I/O 通用数字I/O/比较器A 输出/LCD 段19 输出脚 (见注1) I/O 通用数字I/O/LCD 段18 输出脚 (见注1) I/O 通用数字I/O/LCD 段17 输出脚 (见注1) I/O 通用数字I/O/LCD 段16 输出脚 (见注1) I/O 通用数字I/O/LCD 段15 输出脚 (见注1) I/O 通用数字I/O/LCD 段14 输出脚 (见注1) I/O 通用数字I/O/LCD 段13 输出脚 (见注1) I/O 通用数字I/O/LCD 段12 输出脚 (见注1)

19

I/O 通用数字I/O/LCD 段7 出脚 (见注1)

18

I/O 通用数字I/O/LCD 段6 出脚 (见注1)

17

/O 通用数字I/O/LCD 段5 出脚 (见注1)

16

I/O 通用数字I/O/LCD 段4 出脚 (见注1)

15

I/O 通用数字I/O/LCD 段3 输出脚 (见注1)

14

I/O 通用数字I/O/LCD 段2 输出脚 (见注1)

60

I/O 通用数字I/O 脚

61

I/O 通用数字I/O 脚

2

I/O 通用数字I/O 脚

3

I/O 通用数字I/O 脚

4

I/O 通用数字I/O 脚

5

I/O 通用数字I/O 脚

6

I/O 通用数字I/O 脚

58

I 复位输入脚或非屏蔽终端输入端

57

I 测试时钟. TCK 是芯片编程和测试的时钟输入脚

55

I 测试数据输入. TDI 用作数据输入. 芯片的保护熔丝与TDI 相连.

MSP430F4XX 中文技术手册

MSP430X41X混合信号微控制器

● 低电压范围:1.8 V . . . 3.6 V ● 超低功耗: