(Multisim数电仿真)计数、译码和显示电路Word版

译码显示电路以及Multisim仿真

译码显示电路以及Multisim仿真编写:樊伟敏一、显示器件数码显示器作为一种最常见的显示器件,它的应用领域非常广泛。

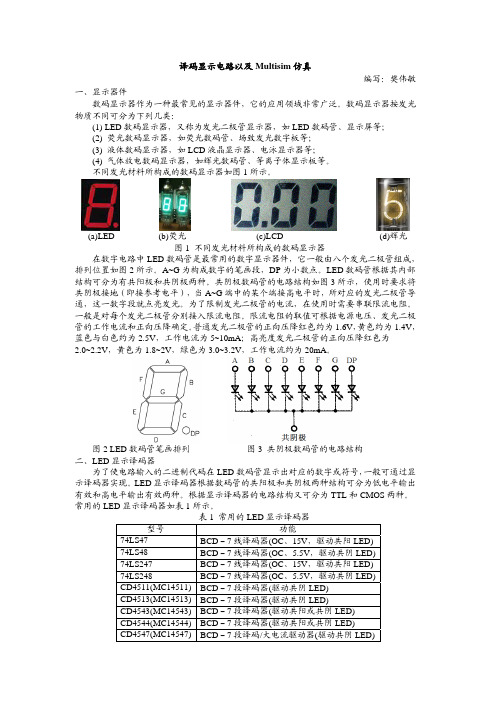

数码显示器按发光物质不同可分为下列几类:(1) LED数码显示器,又称为发光二极管显示器,如LED数码管、显示屏等;(2) 荧光数码显示器,如荧光数码管、场致发光数字板等;(3) 液体数码显示器,如LCD液晶显示器、电泳显示器等;(4) 气体放电数码显示器,如辉光数码管、等离子体显示板等。

不同发光材料所构成的数码显示器如图1所示。

(a)LED (b)荧光(c)LCD (d)辉光图1 不同发光材料所构成的数码显示器在数字电路中LED数码管是最常用的数字显示器件,它一般由八个发光二极管组成,排列位置如图2所示。

A~G为构成数字的笔画段,DP为小数点。

LED数码管根据其内部结构可分为有共阳极和共阴极两种。

共阴极数码管的电路结构如图3所示,使用时要求将共阴极接地(即接参考电平),当A~G端中的某个端接高电平时,所对应的发光二极管导通,这一数字段就点亮发光。

为了限制发光二极管的电流,在使用时需要串联限流电阻。

一般是对每个发光二极管分别接入限流电阻。

限流电阻的取值可根据电源电压、发光二极管的工作电流和正向压降确定。

普通发光二极管的正向压降红色约为1.6V,黄色约为1.4V,蓝色与白色约为2.5V,工作电流为5~10mA;高亮度发光二极管的正向压降红色为2.0~2.2V,黄色为1.8~2V,绿色为3.0~3.2V,工作电流约为20mA。

图2 LED数码管笔画排列图3 共阴极数码管的电路结构二、LED显示译码器为了使电路输入的二进制代码在LED数码管显示出对应的数字或符号,一般可通过显示译码器实现。

LED显示译码器根据数码管的共阳极和共阴极两种结构可分为低电平输出有效和高电平输出有效两种。

根据显示译码器的电路结构又可分为TTL和CMOS两种。

常用的LED显示译码器如表1所示。

表1 常用的LED显示译码器型号功能74LS47 BCD-7线译码器(OC、15V,驱动共阳LED)74LS48 BCD-7线译码器(OC、5.5V,驱动共阴LED)74LS247 BCD-7线译码器(OC、15V,驱动共阳LED)74LS248 BCD-7线译码器(OC、5.5V,驱动共阴LED)CD4511(MC14511) BCD-7段译码器(驱动共阴LED)CD4513(MC14513) BCD-7段译码器(驱动共阴LED)CD4543(MC14543) BCD-7段译码器(驱动共阳或共阴LED)CD4544(MC14544) BCD-7段译码器(驱动共阳或共阴LED)CD4547(MC14547) BCD-7段译码/大电流驱动器(驱动共阴LED)三、译码显示电路应用LED译码显示电路的Multisim仿真实例,请注意以下仿真采用的是Multisim Power Pro Edition Version 10.1.1(10.1.372)版本。

multisim仿真教程计数器译码器数码管驱动显示电路

将对话框中Node name改成与数码管相对应 的符号A。其他与逻辑分析仪的输入端的连 线都以此法行之,点击仿真开关或按F5键进 行仿真,计数器的输出和数码管的波形时序 关系则立即直观的被显示在“Logic Analyzer—XLA1”的面板窗口中。见图 12.7.2。

图12.7.3 Node对话框

由输出端QB和QD经逻辑组合电路接至计数器 (LOAD)端,构建计数进位阻塞电路。在设 计时可根据需要,由相应的输出端构建组合 逻辑电路,从而实现不同进制的计数器。

图12.7.1 计数器、译码器、数码管驱动显示电路

从虚ห้องสมุดไป่ตู้仪器中取逻辑分析仪XLA1,其上有1~F 共16个输入端,1~4端分别于计数器的四个数 据输出端QA~QD相连,第5~11端 分别与数码 管的七段A~G相连,第12端接CLK脉冲输入端。 用鼠标双击逻辑分析仪,将出现逻辑分析仪面 板窗口如图12.7.2所示。

图12.7.2 时钟脉冲、输入、输出波形时序关系图

改变逻辑分析仪Clock区(Clock/Div)的个 数,从“1”调到“32”。在图12.7.2的左侧 显示的号码为原理图的节点号码,其并不能表 示出计数器输出端和数码管的段位字母,显示 不用鼠标左键双击与逻辑分析仪“1”号输入端 连接的图线,出现如图12.7.3所示对话框。直 观,所以要对原理图进行编辑。

CAD实验六计数器,译码器和数码管显示电路

实验报告书前言•实验名称计数器、译码器和数码管显示电路•实验目的•熟悉NI Multisim 10软件的使用方法。

•学习用计数器、译码器和数码管显示电路。

•掌握计数器、数码管的使用方法。

•虚拟实验仪器及器材计数器、译码器、数码管、逻辑分析仪•实验步骤•打开Multisim10.0,依次打开菜单栏中place\component.•单击Group选框选择Sources,选择POWER_SOURCES在右边选框选择VCC,放置在制作面板。

同样路径依次放置DGND, GROUND。

选择SIGNAL_VOLTAGE_SOURCES右边选框选择CLOCK_VOLTAGE.•选择Group选框Basic.选择SWITCH\SPDT.单击OK.选择RESISTOR\1.0K .在制作面板复制7个(共8个)。

•选择Group选框All groups\74HC_6V\74HC10D_6V\OK. 选择74LS\74LS00D和74LS191D 和74LS47D.依次放置在制作面板。

也可以在Component下的选框中输入元件名字搜索。

•选择Group选框Indicators\HEX_DISPLAY\SEVEN_SGE_COM_A\OK.•在工具栏中选择Logic analyzer.(逻辑分析仪)•六步做完后显示如图:(元件可旋转,水平或垂直镜像选择合适的位置)•摆放好位置后连线。

把光标放在元器件端口出现黑色十四图标单击开始连线。

如图:•更改元件属性,双击元件Label\RefDes和Value.只更改需要更改的。

Logic analyzer(逻辑分析仪)显示如图:•当开关S1置于“2”时,数码管显示范围0到9,当开关S1置于“3”时,数码管显示范围0到6.导线“4”断开,数码管显示为0.•当删除R1-R7时,数码管能显示,•思考题:若数码管换成SEVEN_SEG_COM_K.电路如何改造才能正常显示?答:若数码管换成SEVEN_SEG_COM_K,数码管将显示不正常。

计数、译码和显示电路

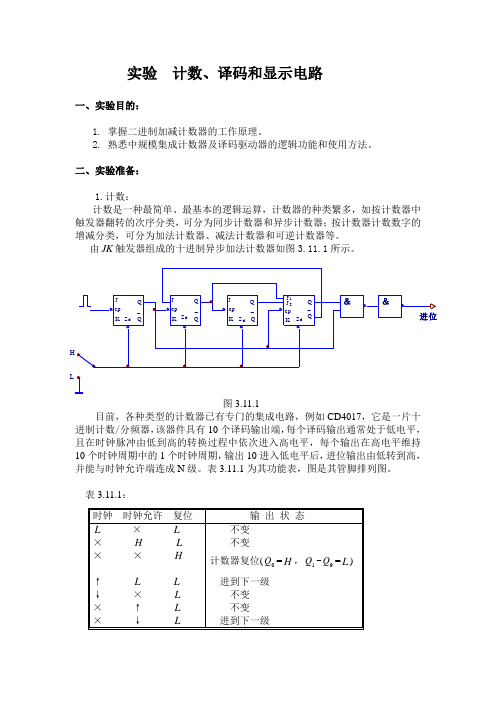

实验计数、译码和显示电路一、实验目的:1. 掌握二进制加减计数器的工作原理。

2. 熟悉中规模集成计数器及译码驱动器的逻辑功能和使用方法。

二、实验准备:1.计数:计数是一种最简单、最基本的逻辑运算,计数器的种类繁多,如按计数器中图3.11.2另外一种可预计的十进制加减可逆计数器CD4510,用途也非常广,其引脚排列如图3.11.3所示,其中,E P 为预计计数使能端,in C 为进位输入端,1P ~4P 为预计的输入端,out C 为进位输出端,U /D 为加减控制端,R 为复位端,CD4510输入、输出间的逻辑功能如表所示。

表3.11.2:。

2. 译码与显示:十进制计数器的输出经译码后驱动数码管,可以显示0~9十个数字,CD4511是BCD~7段译码驱动集成电路,其引脚排列如图3.11.4所示。

LT 为试灯输入,BI 为消隐输入,LE 为锁定允许输入,A 、B 、C 、D 为BCD 码输入,a~g 为七段译码。

CD4511的逻辑功能如表所示。

LED 数码管是常用的数字显示器,分共阴和共阳两种,BS112201是共阴的磷化镓数码管,其外形和内部结构如图3.11.5所示。

图3.11.5三、计算机仿真实验内容:1. 计数10的电路:(1).单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“CMOS”按钮,从弹出的对话框“Family”栏中选“CMOS_10V”,再在“Component”栏中选取4093BD和4017BD各一只,如图3.11.6所示,将它们放置在电子平台上。

图3.11.6(2).单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“Source”按钮,从弹出的对话框“Family”栏中选“POWER_SOURCES”,再在“Component”栏中选取“VDD”和地线,将它们调出放置在电子平台上。

(3). 双击“VDD”图标,将弹出如图3.11.7所示对话框,将“V oltage”栏改成“10”V,再点击下方“确定”按钮退出。

Multisim 数字电路仿真实验(计数器)

Multisim 数字电路仿真实验1.实验目的用Multisim 的仿真软件对数字电路进行仿真研究。

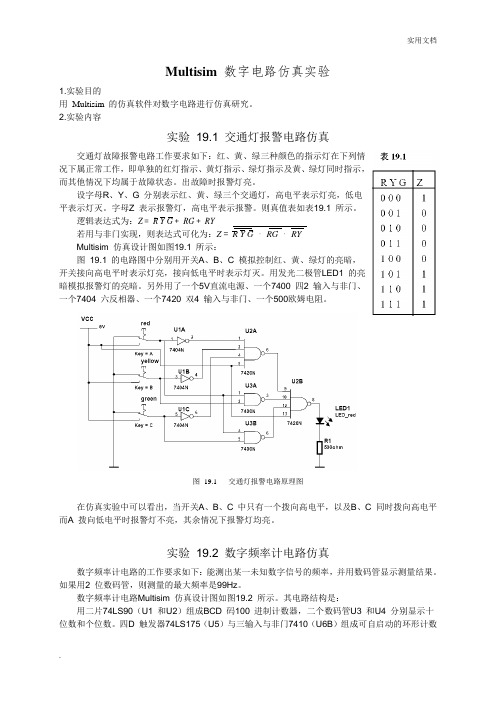

2.实验内容实验19.1 交通灯报警电路仿真交通灯故障报警电路工作要求如下:红、黄、绿三种颜色的指示灯在下列情况下属正常工作,即单独的红灯指示、黄灯指示、绿灯指示及黄、绿灯同时指示,而其他情况下均属于故障状态。

出故障时报警灯亮。

设字母R、Y、G 分别表示红、黄、绿三个交通灯,高电平表示灯亮,低电平表示灯灭。

字母Z 表示报警灯,高电平表示报警。

则真值表如表19.1 所示。

逻辑表达式为:Z = R Y G + RG + RY若用与非门实现,则表达式可化为:Z = R Y G ⋅RG ⋅RYMultisim 仿真设计图如图19.1 所示:图19.1 的电路图中分别用开关A、B、C 模拟控制红、黄、绿灯的亮暗,开关接向高电平时表示灯亮,接向低电平时表示灯灭。

用发光二极管LED1 的亮暗模拟报警灯的亮暗。

另外用了一个5V直流电源、一个7400 四2 输入与非门、一个7404 六反相器、一个7420 双4 输入与非门、一个500欧姆电阻。

图19.1 交通灯报警电路原理图在仿真实验中可以看出,当开关A、B、C 中只有一个拨向高电平,以及B、C 同时拨向高电平而A 拨向低电平时报警灯不亮,其余情况下报警灯均亮。

实验19.2 数字频率计电路仿真数字频率计电路的工作要求如下:能测出某一未知数字信号的频率,并用数码管显示测量结果。

如果用2 位数码管,则测量的最大频率是99Hz。

数字频率计电路Multisim 仿真设计图如图19.2 所示。

其电路结构是:用二片74LS90(U1 和U2)组成BCD 码100 进制计数器,二个数码管U3 和U4 分别显示十位数和个位数。

四D 触发器74LS175(U5)与三输入与非门7410(U6B)组成可自启动的环形计数器,产生闸门控制信号和计数器清0 信号。

信号发生器XFG1 产生频率为1Hz、占空比为50%的连续脉冲信号,信号发生器XFG2 产生频率为1-99Hz(人为设置)、占空比为50%的连续脉冲信号作为被测脉冲。

(完整word版)multisim 电路仿真 课程设计

4.1 仿真设计1、用网孔法和节点法求解电路。

如图4.1-1所示电路:3Ω(a)用网孔电流法计算电压u的理论值。

(b)利用multisim进行电路仿真,用虚拟仪表验证计算结果。

(c)用节点电位法计算电流i的理论值。

(d)用虚拟仪表验证计算结果。

解:电路图:(a)i1=2 解得 i1=25i2-31-i3=2 i2=1i3=-3 i3=-3 u=2 v(b)如图所示:(c)列出方程4/3 U1- U2=2 解得 U1=3 v U2=2 v2A1Ω_+_+u1Ω2V-3A图4.1-1i2U 1- U 2=2 i=1 A结果:计算结果与电路仿真结果一致。

结论分析:理论值与仿真软件的结果一致。

2、叠加定理和齐次定理的验证。

如图4.1-2所示电路:(a)使用叠加定理求解电压u 的理论值;(b)利用multisim 进行电路仿真,验证叠加定理。

(c)如果电路中的电压源扩大为原来的3倍,电流源扩大为原来的2倍,使用齐次定理,计算此时的电压u ;(d)利用multisim 对(c )进行电路仿真,验证齐次定理。

电路图:(a ) I 1=27 I 2-2 I 1- I 3=03 I 3- I 2-2 I 4=0 解得 U 1=7(V ) I 4=-3 U 1U 1=2(I 1- I 2)如图所示电压源单独作用时根据网孔法列方程得:3 I 1-2 I 2- I 3=4 I 2=-3 U 27 I 3 - I 1=0 解得 U 2=9(V ) U 2=4-2 I 3所以 U= U 1+ U 2=16(V ) (b )如图所示。

2Ω 1Ω 2Ω 4Ω 2A 3u + 4V - + u-图4.1-2(c)根据齐次定理,U=2U1+3U2=14+27=41 v(d)结果:理论值与仿真电路计算的值一样。

结论分析:齐次定理和叠加定理成立。

三、替代定理的验证。

(a)求R上的电压u和电流I的理论值;(b)利用multisim进行电路仿真,分别用相应的电压源u和电流源I替代电阻R,分别测量替代前后支路1的电流i1和支路的电压u2,验证替代定理。

电子电工实验报告8译码与显示电路

电工电子实验报告译码与显示电路一、实验目的1.掌握二进制译码器、二-十进制译码器和显示译码器的逻辑功能及各种应用。

2.熟悉十进制数字显示电路的构成方法。

3.了解动态扫描显示方式的电路工作原理及优点。

二、主要仪器设备及软件硬件:74LS139二四译码器,导线,四选一数据选择器,CD4511,电工电子综合实验箱,笔记本电脑软件:NI Multisim 14三、实验原理(或设计过程)1.译码器及其应用译码器一般都具有n个输入和m个输出的组合逻辑电路。

译码器按用途大致可以分为二类:二进制译码器和二-十进制译码器。

(1)二进制译码器二进制译码器是把n位二进制变换为具有2^n个不同状态的组合逻辑电路,常用的中规模集成译码器有2-4线、3-8线和4-16线3类。

①2-4译码器74LS139具有两个独立的2-4线译码器的中规模集成器件,其逻辑符号如图所示。

BA输入端,为二进制变量。

G非为使能端,G非为1时各项工作停止,为0时开始工作。

功能表如图②3-8译码器74LS138是3-8线译码器,其逻辑符号如图。

当G1=0或G2=G2A非+G2B 非=1时,译码器不工作;只有当G1=”1”,G2=”0”时才正常工作。

功能表如图:(2)二进制译码器的应用可以用使能端扩展、树状扩展来实现功能扩展;可以控制组件的工作时机;实现逻辑函数;实现数据分配器;实现脉冲分配器。

2.显示译码、数码管及其应用(1)显示译码管和数码管BCD七段译码器为了用数码管显示十进制数字,首先要将二-十进制代码送至显示译码器,再由译码器的输出去驱动数码管。

CD4511是七段译码器,A-D为输出BCD码输入端,a-g为译码器输出端,输出高电平有效。

LT非为测试输入端,BI非为消隐控制端。

功能表如下(2)显示译码管数码管及其应用1)静态显示电路每一组BCD都有一套独立的显示电路显示2)动态显示电路一片译码器带4个数码管的译码显示电路。

当BA=00时,选择器把A3A2A1A0送入1号数码管,当BA=01,10,11时,分别送B3B2B1B0,C3C2C1C0,D3D2D1D0到2、3、4号数码管。

multisim仿真教程译码器电路

以3线-8线译码器74LS138为例进行分析, 其逻辑功能如表8.3.1所示,表中 A2 、A1 、A0 为 地址输入端,Y7~ Y0为译码输出端,G1(S1)、 G2A (S2)、G2B(S3 )为使能端。当G1(S1)=1, G2A(S2 )+G2AB(S3)=0时,器件使能,地址码所 指定的输出端有信号(为0)输出,其它所有输出 端均无信号(全为1)输出。当G1(S1)=0, G2A ( )+G2B( )=

第7页/共21页

输出就是G2A(S2)端数据信息的原码。若数据信 息是时钟脉冲,则数据分配器便成为时钟脉冲分 配器。括号中的符号是实际芯片中的符号。

第8页/共21页

根据输入地址的不同组合译出唯一地址,故可 用作地址译码器。接成多路分配器,可将一个信号 源的数据信息传输到不同的地点。

二进制译码器还能方便地实现逻辑函数,如 图8.3.2所示,实现的逻辑函数是:

Z= ABC ABC ABC+ABC

第9页/共21页

图8.3.1 作数据分配器 图8.3.2 实现逻辑函数

第10页/共21页

利用使能端能方便地将两个 3/8译码器组合 成一个4/16译码器,如图8.3.3所示。

第11页/共21页

图8.3.3 用两个 3/8译码器组合成一个4/16译码器电路

表8.3.2 74145逻辑功能

第17页/共21页

图8.3.5 译码器驱动指示灯电路

第18页/共21页

电路中字信号输入操作:双击字信号图标, 出现如图8.3.6对话框。字信号参数设置方法请 参照1,5节中的1.5.7(字信号发生器)小节。

Edit: 栏为正在编辑的那条字信号的地址 Current: 栏为正在输出的那条字信号的地 址。

multisim仿真教程译码器电路

输出就是G2A(S 2 )端数据信息的原码。若数据信 息是时钟脉冲,则数据分配器便成为时钟脉冲分 配器。括号中的符号是实际芯片中的符号。

2020/5/5

根据输入地址的不同组合译出唯一地址,故可 用作地址译码器。接成多路分配器,可将一个信号 源的数据信息传输到不同的地点。

二进制译码器还能方便地实现逻辑函数,如 图8.3.2所示,实现的逻辑函数是:

2020/5/5

8.3.1变量译码器 变量译码器的特点:对应于输入的每一位二 进制码,译码器只有确定的一条输出线有信号输 出。这类译码芯片有2线—4线译码器74LSl39,3 线—8线译码器74LSl38、74LS137、74LS237、 74LS238、74LS538,4线-16线译码器MC74154、 MC74159、4514、4515等。

2020/5/5

Initar 和Final栏分别表示输出字信号的起始 地址和终止地址,设置后,字信号从起始地址 开始逐条输出。

本例设置起始地址是0000,终止地址是 0009。字信号的输出方式分为Step(单步)

用鼠标单击一次Step按钮,字信号输出一 条。这种方式可用于对电路进行单步调试,便 于观察电路变化状态。

Z= ABCABCABC+ABC

2020/5/5

图8.3.1 作数据分配器 图8.3.2 实现逻辑函数

2020/5/5

利用使能端能方便地将两个 3/8译码器组合 成一个4/16译码器,如图8.3.3所示。

2020/5/5

图8.3.3 用两个 3/8译码器组合成一个4/16译码器电路

2020/5/5

2020/5/5

X时,或 G1(S1)=X,G2A(S 2)+G2B(S 3 )=1 时,译码器被禁止,所有输出同时为1。括号中的 符号为实际芯片中的符号。

multisim仿真教程译码器电路

X时,或 G1(S1)=X,G2A(S 2)+G2B(S 3 )=1 时,译码器被禁止,所有输出同时为1。括号中的 符号为实际芯片中的符号。

2020/5/13

表8.3.1 74LS138逻辑功能表

2020/5/13

二进制译码器实际上也是负脉冲输出的脉冲分 配器。若利用使能端中的一个输入端输入数据信息, 器件就成为一个数据分配器(又称多路分配器),如 图8.3.1所示。若在G1(S1)输入端输入数据信息, G2A( S 2 )=G2B(S 3 )=0,地址码所对应的输出是 G1(S1)数据信息的反码;若从G2A(S 2)端输入数据信 息,令G1(S1)=1、 G2B( S 3 )=0,地址码所对应的

表8.3.2 74145逻辑功能

2020/5/13

2020/5/13

图8.3.5 译码器驱动指示灯电路

电路中字信号输入操作:双击字信号图标, 出现如图8.3.6对话框。字信号参数设置方法请 参照1,5节中的1.5.7(字信号发生器)小节。

Edit: 栏为正在编辑的那条字信号的地址 Current: 栏为正在输出的那条字信号的地 址。

2020/5/13

8.3.4 译码器驱动指示灯电路 74145是BCD码到十进制数译码器,其逻辑 功能见表8.3.2,其中×为随意态。74145为集电 极开路输出型的电路.其吸收大电流的能力较强 且输出管具有高的击穿电压。用74145选择驱动 指示灯和继电器的电路如图8.3.5所示。

2020/5/13

2020/5/13

2020/5/13

图8.3.4 74LS45的逻辑符号

8.3.3 显示译码器 用来驱动荧光数码管、发光二极管等显示器件 的译码器称为显示译码器。它可将数符或字符的各 种编码转换成字型码显示出来。这类集成芯片有: BCD-七段译码器7445、7446、7447、7448、7449、 74246、74247、74LS247、74LS248、74LS249、 4558,十进制数—七段译码器4026,BCD码—十进 制译码器/驱动器74LSl45等。

multisim仿真教程译码器电路

8.3.2 码制变换译码器

码制变换译码器可以把一种码制变换成另一 个码制。常用的集成芯片有4线-10线译码器 74LS42、7443、74441、C1M028、74141、74145 等。74LS45的逻辑电路及符号如图8.3.4所示。其4 条输入线为8421BCD码,输出的10根线为对应的 十进制状态.其输出为低电平有效。

第15页/共21页

8.3.4 译码器驱动指示灯电路

74145是BCD码到十进制数译码器,其逻辑 功能见表8.3.2,其中×为随意态。74145为集电极 开路输出型的电路.其吸收大电流的能力较强且 输出管具有高的击穿电压。用74145选择驱动指 示灯和继电器的电路如图8.3.5所示。

第16页/共21页

译码器可分为通用译码器和显示译码器两大 类。前者又分为变量译码器和代码变换译码器。 变量译码器(又称二进制译码器),用以表示输 入变量的状态,如2线-4线、3线-8线和4线- 16线译码器。

若有n个输入变量,则有 个不同的组合状 态,就有 个输出端供其使用。而每一个输出所 代表的函数对应于n个输入变量的最小项。

第19页/共21页

Initar 和Final栏分别表示输出字信号的起始 地址和终止地址,设置后,字信号从起始地址 开始逐条输出。

本例设置起始地址是0000,终止地址是 0009。字信号的输出方式分为Step(单步)

用鼠标单击一次Step按钮,字信号输出一 条。这种方式可用于对电路进行单步调试,便 于观察电路变化状态。

第3页/共21页

以3线-8线译码器74LS138为例进行分析, 其逻辑功能如表8.3.1所示,表中 A2 、A1 、A0 为 地址输入端,Y7~ Y0为译码输出端,G1(S1)、 G2A (S2)、G2B(S3 )为使能端。当G1(S1)=1, G2A(S2 )+G2AB(S3)=0时,器件使能,地址码所 指定的输出端有信号(为0)输出,其它所有输出 端均无信号(全为1)输出。当G1(S1)=0, G2A ( )+G2B( )=

基于Multisim的计数、译码与显示电路

基于Multisim的计数、译码与显示电路汪明珠;毛德梅;李泽彬;朱雪梅【摘要】介绍了利用译码驱动器74LS47(或74LS48)、十进制可逆计数器74LS192集成芯片,配合数码管、电源、开关、字信号发生器、逻辑分析仪等器件,设计实现了计数、译码与显示电路,并用Multisim虚拟仿真软件对电路进行了仿真与分析.在虚拟仿真后,再搭建硬件电路进行实物实验,通过虚实结合,优势互补,全面提高实践技能与创新能力.%This paper describes the use of decoding driver 74LS47 (or 74LS48), decimal reversible counter integrated chip 74LS192, with digital tube, power supply, switch, word generator, logic analyzer and other devices, with all the devices this counting, decoding and display circuit have been designed, and the use of Multisim virtual simulation and analysis have been made on the circuit simulation software. After the virtual simulation, build the hardware circuit to carry out the physical experiment. Through the combination of virtual and real experiment, we can complement each other's advantages and comprehensively improve the practical skills and innovative ability.【期刊名称】《皖西学院学报》【年(卷),期】2018(034)002【总页数】6页(P105-110)【关键词】Multisim;计数器;译码器;显示电路【作者】汪明珠;毛德梅;李泽彬;朱雪梅【作者单位】皖西学院皖创机器人创客实验室,安徽六安 237012;皖西学院皖创机器人创客实验室,安徽六安 237012;皖西学院皖创机器人创客实验室,安徽六安237012;皖西学院皖创机器人创客实验室,安徽六安 237012【正文语种】中文【中图分类】TP273Multisim是美国国家仪器NI(National Instruments)有限公司推出的功能强大的虚拟仿真软件,它可以广泛地应用于模拟电路、数字电路、电工电路、射频电路等诸多领域[1]。

multisim 仿真教程 译码器电路

Initar 和Final栏分别表示输出字信号的起始

地址和终止地址,设置后,字信号从起始地址 开始逐条输出。 本例设置起始地址是0000,终止地址是 0009。字信号的输出方式分为Step(单步) 用鼠标单击一次Step按钮,字信号输出一 条。这种方式可用于对电路进行单步调试,便 于观察电路变化状态。

8.3 译码器电路

译码是编码的逆过程,把二进制码还原成给定 的信息符号(数符、字符或运算符等)。能完成译码 功能的电路叫译码器。译码器输入二进制数码的位 数n与输出端数m之间的关系为m≤ 。若m= 称

为全译码。m<

称为非全译码。

译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相

器件就成为一个数据分配器(又称多路分配器),如

图8.3.1所示。若在G1(S1)输入端输入数据信息, G2A( S2 )=G2B( S3 )=0,地址码所对应的输出是 G1(S1)数据信息的反码;若从G2A( S2)端输入数据信 息,令G1(S1)=1、 G2B( S3 )=0,地址码所对应的

输出就是G2A(S2 )端数据信息的原码。若数据信 息是时钟脉冲,则数据分配器便成为时钟脉冲分

等。74LS45的逻辑电路及符号如图8.3.4所示。其4 条输入线为8421BCD码,输出的10根线为对应的 十进制状态.其输出为低电平有效。

图8.3.4 74LS45的逻辑符号

8.3.3 显示译码器

用来驱动荧光数码管、发光二极管等显示器件

的译码器称为显示译码器。它可将数符或字符的各

种编码转换成字型码显示出来。这类集成芯片有:

图8.3.2 实现逻辑函数

利用使能端能方便地将两个 3/8译码器组合 成一个4/16译码器,如图8.3.3所示。

(Multisim数电仿真)计数、译码和显示电路Word版

实验3.11 计数、译码和显示电路一、实验目的:1. 掌握二进制加减计数器的工作原理。

2. 熟悉中规模集成计数器及译码驱动器的逻辑功能和使用方法。

二、实验准备:1.计数:计数是一种最简单、最基本的逻辑运算,计数器的种类繁多,如按计数器中图图3.11.2另外一种可预计的十进制加减可逆计数器CD4510,用途也非常广,其引脚排列如图3.11.3所示,其中,E P 为预计计数使能端,in C 为进位输入端,1P ~4P 为预计的输入端,out C 为进位输出端,U /D为加减控制端,R 为复位端,CD4510输入、输出间的逻辑功能如表3.11.2所示。

表3.11.2:。

2. 译码与显示:十进制计数器的输出经译码后驱动数码管,可以显示0~9十个数字,CD4511是BCD~7段译码驱动集成电路,其引脚排列如图3.11.4所示。

LT为试灯输入,BI为消隐输入,LE为锁定允许输入,A、B、C、D为BCD码输入,a~g为七段译码。

CD4511的逻辑功能如表3.11.3所示。

LED数码管是常用的数字显示器,分共阴和共阳两种,BS112201是共阴的磷化镓数码管,其外形和内部结构如图3.11.5所示。

图3.11.4图3.11.511101111三、计算机仿真实验内容:1. 计数10的电路:(1). 单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“CMOS”按钮,从弹出的对话框“Family”栏中选“CMOS_10V”,再在“Component”栏中选取4093BD和4017BD各一只,如图3.11.6所示,将它们放置在电子平台上。

图3.11.6(2). 单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“Source”按钮,从弹出的对话框“Family”栏中选“POWER_SOURCES”,再在“Component”栏中选取“VDD”和地线,将它们调出放置在电子平台上。

(3). 双击“VDD”图标,将弹出如图3.11.7所示对话框,将“Voltage”栏改成“10”V,再点击下方“确定”按钮退出。

用Multisim仿真键号识别与显示电路设计

信息与电气工程学院电子电路仿真设计项目设计说明书(2011/2012学年第二学期)题目:键号识别与显示电路设计 __专业班级:通信10-3学生姓名:聂保玲学号:100310308指导教师:马永强陈湘国贾东立刘会军设计周数:2周设计成绩:2012年7月3日1. 项目目的1. 学习数字电路综合应用。

2. 学习简单数字系统设计方法。

3. 学习使用Multisim软件进行电路仿真2. 项目设计过程2.1 设计思路先使用8-3线优先编码器,将信号输入并编码,然后将输出信号输入七段显示译码器。

再将译码器连接到七段显示数码管,实现信号的显示。

2.2 器件的选择及其功能2.2.1 器件名称型号编码器HD74LS148P×1 译码器HD74LS48P×1 共阴极七段显示数码管×1 非门电路74HC04N×4 150欧电阻×7 集成开关×1(含八个开关)导线若干2.2.2 实物图及相应功能图2.2.2.1 HD74LS148P表2.2.2.1编码器HD74LS148图2.2.2.2 HD74LS48P表2.2.2.2译码器HD74LS48P2.3 Multisim 仿真 2.3.1 设计方案74HC148N 输入端低电平有效,于是方案一编码器前开关闭合接地时,输入低电平。

74HC147N 输入端低电平有效,于是在5V 电压输入前各个输入端都加一个非门电路,从而保证开关闭合时输入低电平。

编码器输出端低电平有效,而74LS48D 和CD4511BD 输入端高电平有效,因此在两者之间加上非门电路,以保证一致。

两个译码器均为输出高电平有效,驱动共阴极数码管,因此选择共阴极数码管。

为防止电流过大,加电阻限流。

最初设计方案图如图一和图二:图2.2.2.3非门图一2.2.2.4数码管由于所需元器件限制,没有编码器74LS147N 和单刀双掷开关,于是改进方案如图三:图二图三2.3.2 运行结果开关从上到下分别控制0、1、2、3、4、5、6、7,列举其中几个例子:当闭合开关1时,数码管显示1,如下图:当闭合开关4时,数码管显示4,如下图:当闭合开关7时,数码管显示7,如下图:由于74HC148N是优先编码器,所以当开关7闭合的情况下,在闭合其他开关仍然显示7,即数码管只显示优先级较高的数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验3.11 计数、译码和显示电路

一、实验目的:

1. 掌握二进制加减计数器的工作原理。

2. 熟悉中规模集成计数器及译码驱动器的逻辑功能和使用方法。

二、实验准备:

1.计数:

计数是一种最简单、最基本的逻辑运算,计数器的种类繁多,如按计数器中

图

图3.11.2

另外一种可预计的十进制加减可逆计数器CD4510,用途也非常广,其引脚排列如图3.11.3所示,其中,E P 为预计计数使能端,in C 为进位输入端,

1P ~4P 为预计的输入端,out C 为进位输出端,U /D

为加减控制端,R 为复位端,CD4510输入、输出间

的逻辑功能如表3.11.2所示。

表3.11.2:。

2. 译码与显示:

十进制计数器的输出经译码后驱动数码管,可以

显示0~9十个数字,CD4511是BCD~7段译码驱动集

成电路,其引脚排列如图

3.11.4所示。

LT为试灯输入,BI为消隐输入,LE为锁定允许输入,A、

B、C、D为BCD码输入,a~g为七段译码。

CD4511的逻辑功能如表3.11.3所示。

LED数码管是常用的数字显示器,分共阴和共阳两种,BS112201是共阴的磷化镓数码管,其外形和内部结构如图3.11.5所示。

图3.11.4

图3.11.5

1110

1111

三、计算机仿真实验内容:

1. 计数10的电路:

(1). 单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“CMOS”按钮,从弹出的对话框“Family”栏中选“CMOS_10V”,再在“Component”栏中选取4093BD和4017BD各一只,如图3.11.6所示,将它们放置在电子平台上。

图3.11.6

(2). 单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“Source”按钮,从弹出的对话框“Family”栏中选“POWER_SOURCES”,再在“Component”栏中选取“VDD”和地线,将它们调出放置在电子平台上。

(3). 双击“VDD”图标,将弹出如图3.11.7所示对话框,将“Voltage”栏改成“10”V,再点击下方“确定”按钮退出。

图3.11.7

(4).

单击电

子仿真

软件

Multisi

m7基本

界面左

侧真实

元件工

具条

“DIODE

”按钮,

从弹出

的对话

框

“Family ”栏中选“LED ”,再在“Component ” 栏中选取“LED_red ”红色发光二极管共10只,如图3.11.8所示。

将它们调出放置在电子平台上;其它元件调法不再赘述,将所有元件调齐并连成仿真电路如图3.11.9所示。

图3.11.8

图3.11.9

(5). 先将1J 置低电平,再打开仿真开关,然后再将1J 置高电平,观察发光二极管发光情况,并能解释电路工作原理。

2. 一位计数、译码和显示电路:

(1). 单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“CMOS ”按钮,从弹出的对话框“Family ”栏中选“CMOS_5V ”,再在“Component ” 栏中选取4510BD 和4511BD 各一只,如图3.11.10所示,将它们放置在电子平台上。

图3.11.10

(2). 单击电子仿真软件Multisim7基本界面左侧左列真实元件工具条“Indicator”按钮,如图 3.11.10所示,从弹出的对话框“Family”栏中选“HEX_DISPLAY”,再在“Component”栏中选取“SEVEN_SEG_COM_K”,如图3.11.11所示,再点击对话框右上角

“OK”按钮,将共阴数码管调出放置在电子平台上。

其它元件调法不再赘述。

图3.11.10

图3.11.11

(3). 将所有元件调齐并连成仿真电路如图3.11.12所示。

图3.11.12

(4). 打开仿真开关,将1J 置低电平,2J 置高电平,每次将3J 从低电平改变成高电平,观察数码管变化情况;再将2J 置低电平,重复上述实验,并能解释之。

四、实验室操作实验内容:

1. 计数10的电路:

图3.11.13是用两片数字集成电路CD4093和CD4017组成计数10的电路,其中CD4093为含有施密特触发器的四2输入与非门。

在 THD-1型(或Dais-2B 型)数电实验箱上按图3.11.13接好电路,开关1

K 由低电平扳向高电平,观察计数电路输出端发光二极管的变化情况,并解释之。

2. 验证译码和显示功能:

在THD-1型(或Dais-2B型)数电实验箱左上方选一片CD4011和数码管电路,将其下方的D、C、B、A (或8、4、2、1)四个孔分别接到4个钮子开关上,根据表3.11.3中,D、C、B、A的编码,逐行验证译码和数码管的显示情况,是否和理论上相符?

3.一位计数、译码和显示电路:

(1). 参阅计数集成电路CD4510的管脚排列图3.11.3(或图3.11.15)和译码驱动集成电路CD4511的管脚排列图3.11.4(或图3.11.15)及共阴数码管脚排列

图3.11.14

(2). 打开实验箱电源开关,先将CD4510的R端置“1”(复位),数码管应显示“0”,再将R端置“0”。

(3). 将CD4510的D

U/端置“1”,CP端与实验台单次脉冲输出孔相连,每按一次脉冲按钮,观察数码管的变化。

(4). 将CD4510的D

U/端置“0”,CP端与实验台单次脉冲输出孔相连,每按一次脉冲按钮,观察数码管的变化,解释上述现象。

*3.设计一个两位计数、译码和显示电路:

(1). 利用THD-1型(或Dais-2B型)数字电路实验箱左上方的译码显示电路,即CD4511与数码管已经接好,只要求用两片CD4510设计好计数电路,画出完整电路图。

(2). 根据设计好的电路图在THD-1型(或Dais-2B型)数字电路实验箱上接好实验电路。

(3). 将CP端接实验台上连续脉冲(脉冲频率选1Hz)输出孔,实现自动加或减计数、译码和显示。

五、实验报告要求:

总结整理实验结果,解释计数、译码及显示过程。

六、实验设备及材料:

1. 仿真计算机及Multisim7软件。

2. THD-1型(或Dais-2B型)数字电路实验台。

3. MF-10型万用表。

4. 电子元件:集成电路:CD4017一片、CD4093一片、CD4510两片、

CD4511一片;

共阴7段数码管1个;

100 欧姆、5.1k、10k电阻各一个;

47uF电容一个。

5. 附:集成电路管脚图。