如何读懂时序图

怎么看时序图--nand flash的读操作详解

这篇文章不是介绍nand flash的物理结构和关于nand flash的一些基本知识的。

你需要至少了解你手上的nand flash的物理结构和一些诸如读写命令操作的大概印象,你至少也需要看过s3c2440中关于nand flash控制寄存器的说明。

由于本人也没有专门学过这方面的知识,下面的介绍也是经验之谈。

这里我用的K9F2G08-SCB0 这款nand flash 来介绍时序图的阅读。

不同的芯片操作时序可能不同,读的命令也会有一些差别。

当然其实有时候像nand flash这种s3c2440内部集成了他的控制器的外设。

具体到读写操作的细节时序(比如CLE/ALE的建立时间,写脉冲的宽度。

数据的建立和保持时间等),不明白前期也没有多大的问题。

因为s3c2440内部的nand flash控制器做了大部分的工作,你需要做的基本就是设置几个时间参数而已。

然后nand flash会自动进行这些细节操作。

当然如果处理器上没有集成nand flash的控制器那么久必须要自己来写时序操作了。

所以了解最底层的时序操作总是好的但是上层一点的,比如读写操作的步骤时序(比如读操作,你要片选使能,然后发命令,然后发地址,需要的话还需发一个命令,然后需要等待操作完成,然后再读书数据)。

是必须要明白的。

这都不明白的话,怎么进行器件的操作呢也就是说s3c2440 可以说在你设置很少的几个时间参数后,将每一个步骤中细微的操作都替你做好了。

(比如写命令,你只要写个命令到相应寄存器中,cpu内部就会协各个引脚发出适应的信号来实现写命令的操作)。

而我们所需要做的就是把这些写命令,写地址,等待操作完成。

等步骤组合起来。

从而完成一个读操作就像上面说的,虽然我们不会需要去编写每个步骤中的最细微的时序。

但是了解下。

会让你对每个操作步骤的底层细节更加明了先来看一个命令锁存的时序。

也就是上面说的读nand flash操作中不是有一个写命令步骤吗。

程序员必备画图技能之——时序图

程序员必备画图技能之——时序图什么是时序图时序图(Sequence Diagram),⼜名序列图、循序图,是⼀种UML交互图。

它通过描述对象之间发送消息的时间顺序显⽰多个对象之间的动态协作。

使⽤场景时序图的使⽤场景⾮常⼴泛,⼏乎各⾏各业都可以使⽤。

当然,作为⼀个软件⼯作者,我这边主要列举和软件开发有关的场景。

1. 梳理业务流程⼀般的软件开发都是为了⽀撑某个具体的业务。

有时候业务的流程会⽐较复杂,涉及到多种⾓⾊,这时就可以使⽤时序图来梳理这个业务逻辑。

这样会使业务看起来⾮常清晰,代码写起来也是⽔到渠成的事情了。

2. 梳理开源软件作为⼀个合格的程序员,阅读源代码的能⼒⼀定要过关。

⼀般成熟框架的源代码调⽤深度都⽐较深,类之间的调⽤关系也⽐较复杂。

我喜欢⽤时序图来梳理框架中这些对象之间的关系。

⽐如再看Tomcat 启动流程的过程中,我就时序图梳理了各个组件之间的关系,看起来层次⾮常清楚,也便于记忆。

时序图的⾓⾊我们在画时序图时会涉及下⾯7种元素:⾓⾊(Actor)对象(Object)⽣命线(LifeLine)控制焦点(Activation)消息(Message)⾃关联消息组合⽚段。

其中前6种是⽐较常⽤和重要的元素,最后的组合⽚段元素不是很常⽤,但是⽐较复杂。

我们先介绍前6种元素,再单独介绍组合⽚段元素。

1. ⾓⾊(Actor)系统⾓⾊,可以是⼈或者其他系统和⼦系统。

以⼀个⼩⼈图标表⽰。

2. 对象(Object)对象位于时序图的顶部,以⼀个矩形表⽰。

对象的命名⽅式⼀般有三种:对象名和类名。

例如:华为⼿机:⼿机、loginServiceObject:LoginService;只显⽰类名,不显⽰对象,即为⼀个匿名类。

例如::⼿机、:LoginSservice。

只显⽰对象名,不显⽰类名。

例如:华为⼿机:、loginServiceObject:。

3. ⽣命线(LifeLine)时序图中每个对象和底部中⼼都有⼀条垂直的虚线,这就是对象的⽣命线(对象的时间线)。

nand flash时序图详解

怎么看时序图--nand flash的读操作详解 2013-11-16 10:25:36分类:嵌入式这篇文章不是介绍 nand flash的物理结构和关于nand flash的一些基本知识的。

你需要至少了解你手上的 nand flash的物理结构和一些诸如读写命令操作的大概印象,你至少也需要看过 s3c2440中关于nand flash控制寄存器的说明。

由于本人也没有专门学过这方面的知识,下面的介绍也是经验之谈。

这里我用的 K9F2G08-SCB0 这款nand flash 来介绍时序图的阅读。

不同的芯片操作时序可能不同,读的命令也会有一些差别。

当然其实有时候像nand flash这种 s3c2440内部集成了他的控制器的外设。

具体到读写操作的细节时序(比如 CLE/ALE的建立时间,写脉冲的宽度。

数据的建立和保持时间等),不明白前期也没有多大的问题。

因为s3c2440内部的nand flash控制器做了大部分的工作,你需要做的基本就是设置几个时间参数而已。

然后nand flash会自动进行这些细节操作。

当然如果处理器上没有集成 nand flash的控制器那么久必须要自己来写时序操作了。

所以了解最底层的时序操作总是好的但是上层一点的,比如读写操作的步骤时序(比如读操作,你要片选使能,然后发命令,然后发地址,需要的话还需发一个命令,然后需要等待操作完成,然后再读书数据)。

是必须要明白的。

这都不明白的话,怎么进行器件的操作呢也就是说 s3c2440 可以说在你设置很少的几个时间参数后,将每一个步骤中细微的操作都替你做好了。

(比如写命令,你只要写个命令到相应寄存器中,cpu内部就会协各个引脚发出适应的信号来实现写命令的操作)。

而我们所需要做的就是把这些写命令,写地址,等待操作完成。

等步骤组合起来。

从而完成一个读操作就像上面说的,虽然我们不会需要去编写每个步骤中的最细微的时序。

但是了解下。

会让你对每个操作步骤的底层细节更加明了先来看一个命令锁存的时序。

第十章时序图(顺序图)

交换机

远程交换机

访客

b {c-b<10} c

{b-a<1}

路径 e 铃响 拿起话筒 铃响停止信号

打电话的时序图

铃响停止

第十章 时序图

零售业务时序图

第十章 时序图

三、时序图中对象的创建与撤消 在时序图中,还可以描述一个对象通过发送 一条消息来创建另一个对象。

NewCustomer(Data) :Customer Windows Customer(Data) :Customer

第十章 时序图

饮料销售机的时序图

:Customer :Front 1: accept(cash,selection)

一般顺序图

:Register

:Dispenser

2: getCustomerInput(cash,selection) 3: [cash>price] checkForChange(cash,price) 4: [no change]returnCash(cash) 5: <<transaction over>>[no change] displayPrompt("Use Correct Change") 6: checkAvailability(selection) 7: [sold out]displayPrompt("Sold Out") 8: <<transaction ove>>[sold out] return(cash) 9: updateReserve(cash,price) 10: [cash>price]receiveChange(cash,price) 11: releaseSoda(selection) 12: <<transaction over>>[selection available] receiveSoda(selection)

时序图读写总结

时序图读写总结

一直不是很明白时序图的读写操作,上网搜了很久都找不到一份很好的资料,我故自己知道一点后就来记录一些,经常更新自己对时序图的理解吧,上网搜的时候很多人说时序图比较简单不知道是不是这样的。

因为csdn上传图片比较麻烦就不上传了,总结一下吧。

1. 时序图都是共用一个时钟信号,注意时钟信号在上下图中的对应。

2. 时序图中有叉或者上升下降的如果是数据线的话表示数据有变化。

菱形封闭的一段表示有效数据。

3. 数据需要一段时间稳定,一般在数据变化后,时钟的上升沿或者下降沿读入数据或者写入数据。

扩展阅读:如何看懂时序图?。

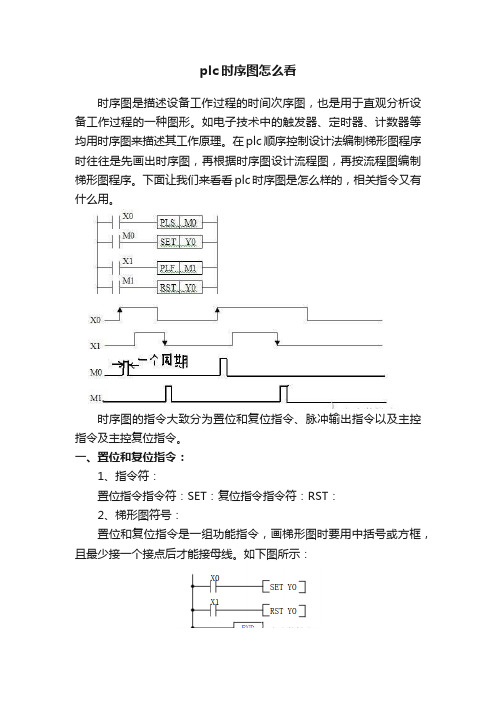

plc时序图怎么看

plc时序图怎么看时序图是描述设备工作过程的时间次序图,也是用于直观分析设备工作过程的一种图形。

如电子技术中的触发器、定时器、计数器等均用时序图来描述其工作原理。

在plc顺序控制设计法编制梯形图程序时往往是先画出时序图,再根据时序图设计流程图,再按流程图编制梯形图程序。

下面让我们来看看plc时序图是怎么样的,相关指令又有什么用。

时序图的指令大致分为置位和复位指令、脉冲输出指令以及主控指令及主控复位指令。

一、置位和复位指令:1、指令符:置位指令指令符:SET:复位指令指令符:RST:2、梯形图符号:置位和复位指令是一组功能指令,画梯形图时要用中括号或方框,且最少接一个接点后才能接母线。

如下图所示:3、指令功能:SET指令的功能:当SET指令工作的前提条件X0发生正跳变(即X0由OFF变为ON)时,SET指令使它操作的继电器Y0置位为“1”(状态变为ON)并保持。

RST指令的功能:当RST指令工作的前提条件X1发生正跳变(即X0由ON变为OFF)时,RST指令使它操作的继电器Y0复位为“0”(状态变为OFF)并保持。

SET指令的操作目标元件为Y、M、S。

而RST指令的操作元件为Y、M、S、D、V、Z、T、C。

对同一编程元件,如例中Y0等,SET、RST指令可以多次使用,且不限制使用顺序,以最后执行者有效。

RST指令可以对定时器、计数器、数据寄存器、变址寄存器的内容清零,还可用来复位积算定时器T246~T255和计数器。

二、脉冲输出指令:1、指令符:上升沿脉冲输出指令指令符:PLS;下降沿脉冲输出指令指令符:PLF2、梯形图符号:脉冲输出指令是一组功能指令,画梯形图时要用中括号或方框,且最少接一个接点后才能接母线。

如下图所示:3、指令功能:PLS指令的功能是:当X0发生正跳变时,PLS指令使指定的继电器M0产生一个扫描周期的脉冲输出。

PLF指令的功能是:当X1发生负跳变时,PLF指令使指定的继电器M1产生一个扫描周期的脉冲输出。

时序图详解

除了提供一个图形化边框之外,用于图中的框架元件也有描述交互的重要的功能, 例如序列图。

在序列图上一个序列接收和发送消息(又称交互),能通过连接消息和框架元件边界,建立模型(如图2 所见到)。

这将会在后面“超越基础”的段落中被更详细地介绍。

UML 的生命线命名标准按照如下格式:除了仅仅显示序列图上的消息调用外,图4 中的图还包括返回消息。

这些返回消息是可选择的;一个返回消息画作一个带开放箭头的虚线,向后指向来源的生命线,在这条虚线上面,你放置操作的返回值。

在图 4 中,当getSecurityClearance 方法被调用时,secSystem组合碎片(变体方案,选择项,和循环)然而,在大多数的序列图中,UML 1.x“in-line”约束不足以处理一个建模序列的必需逻辑。

这个功能缺失是UML 1.x 的一个问题。

UML 2 已经通过去掉“in-line”约束,增加一个叫做组合碎片的符号元件,解决了这一个问题。

一个组合碎片用来把一套消息组合在一起,在一个序列图中显示条件分支。

UML 2 规范指明了组合碎片的11 种交互类型。

十一种中的三种将会在“基础”段落中介绍,另外两种类型将会在“超越基础”中介绍,而那剩余的六种我将会留在另一篇文章中介绍。

(嗨,这是一篇文章而不是一本书。

我希望你在一天中看完这部分!)变体变体用来指明在两个或更多的消息序列之间的、互斥的选择。

3 变体支持经典的“if then else”逻辑的建模(举例来说,如果我买三个,然后我得到我购买的20% 折扣;否则我得到我购买的10% 折扣)。

就如你将会在图8 中注意到的,一个变体的组合碎片元件使用框架来画。

单词“alt”放置在框架的namebox里。

然后较大的长方形分为UML 2 所称的操作元。

4 操作元被虚线分开。

每个操作元有一个约束进行测试,而这个约束被放置在生命线顶端的操作元的左上部。

5 如果操作元的约束等于“true”,然后那个操作元是要执行的操作元。

如何看懂时序图

如何看懂时序图This model paper was revised by the Standardization Office on December 10, 2020时序图,LCD1602前面总算走完了对AVR MEGA16这块单片机的一些基本的应用方式了,这时候大家对AVR的一些内部资源比如定时器,ADC,最主要的IO口的使用方式应该有了一个虽比较粗浅但是却比较形象的认识了。

这节我们来看使用单片机的另外一大主题,就是用单片机来实现芯片控制。

在前面的数码管显示一文中,就已经涉及到了用单片机来控制芯片为我们工作,CEPARK AVR开发板,为了达到增强驱动能力和节省IO口的作用,运用了移位寄存器74HC595来驱动两个四位八段数码管,是一个十分有创意的设计。

但是前面的内容重心还是集中于对AVR的IO口的控制,所以,我们从这节开始要正式逐渐深入的接触各种芯片了。

先做个引子。

单片机是一种微控制器,本身内部集成了数种资源比如CPU、内存、内部和外部总线系统,目前大部分还会具有外存。

他的主要任务是利用各种资源实现电平控制,可以以此控制与它相连的下级系统,广泛用于工业自动控制领域。

我们就从这句话出发,首先单片机是用来做控制用的,而且利用的是本身的内部资源。

但是,它的功能再强大,资源再丰富也总有一个上限,总有枯竭的一天。

所以我们常常利用单片机外接芯片来弥补或者增强单片机的功能来完成我们所需功能的电路。

比如程序存储器不足,可以外接外部存储器,比如单片机内部中断级不足,可以外接中断控制器等等。

大家可以从这个角度来理解芯片控制的意义罢。

今天我们用AVR单片机来实现对LCD1602液晶显示芯片的控制。

首先从这个名字讲起,LCD:英文全称为Liquid Crystal Display,即为液态晶体显示,也就是我们常说的液晶显示了。

(平时老说LCDLCD,可能大家也都不怎么注意过这个全称吧,呵呵,当增加词汇量了)1602则是表示这个液晶一共能显示2行数据,每一行显示16个字符。

时序逻辑电路的分析方法

时序逻辑电路的分析方法1.时序图分析时序图是描述时序逻辑电路中不同信号随时间变化的图形表示。

时序图分析方法是通过绘制输入输出信号随时间变化的波形图,来观察信号之间的时序关系。

时序图分析的步骤如下:1)根据电路的逻辑功能,确定所需的时钟信号和输入信号。

2)根据电路的逻辑关系,建立出波形图的坐标系,确定时间轴和信号轴。

3)按照时钟信号的不同变化情况(上升沿、下降沿),在波形图中绘制相应的路径。

4)观察各个信号之间的时序关系,分析电路的逻辑功能和输出结果。

时序图分析方法的优点是直观、简单,可以清楚地显示信号的时序关系。

但它对于复杂的电路设计来说,图形绘制和分析过程相对繁琐,需要一定的经验和技巧。

2.状态表分析状态表分析方法是通过定义不同输入信号下的状态转移关系,来描述时序逻辑电路的行为。

状态表可以用表格的形式表示,其中包含了输入信号、当前状态、下一个状态和输出信号等信息。

状态表分析的步骤如下:1)根据电路的逻辑功能和输入信号,列出电路的状态转移关系。

2)构建状态表,定义不同输入信号下的状态转移关系和输出信号。

3)根据状态表,逐步推导出电路的状态转移路径和输出结果。

状态表分析方法的优点是逻辑严谨、结构清晰,适用于对于复杂的状态转移关系进行分析和设计。

但它对于大规模的电路设计来说,状态表会非常庞大,而且容易出现错误,需要仔细的计算和推导。

3.状态图分析状态图分析方法是通过绘制状态转移图,来描述时序逻辑电路中状态之间的转移关系。

状态图是由状态、输入信号、输出信号和状态转移路径等构成。

状态图分析的步骤如下:1)根据电路的逻辑功能和输入信号,确定电路的状态和状态转移关系。

2)构建状态图,按照状态的转移路径和输入信号绘制状态图。

3)根据状态图,分析电路的逻辑功能和输出结果。

状态图分析方法的优点是直观、清晰,可以清楚地描述状态之间的转移关系。

它可以帮助设计者对于电路的状态转移关系进行分析和调试。

但状态图也会随着电路规模的增大而变得复杂,需要仔细分析和理解。

第四课时:时序图

对象

时序图中对象的符号和对象图中对象所 用的符号一样。

将对象置于时序图的顶部意味着在交互 开始的时候对象就已经存在了,如果对 象的位置不在顶部,那么表示对象是在 交互的过程中被创建的。

对象框中对象名语法

语法

O O:C

:C

描述

一个名字为O的对象

一个名字为O的对象,它是类C的 一个实例

类C的一个匿名对象

对象在创建消息发生之后才能存在,对 象的生命线也是在创建消息之后才存在 的。

对象的创建和撤销

创建对象的两种表示方法

对象的创建和撤销

如果要撤销一个对象,只要在其生命线 终止点放置一个“X”符号即可,该点通 常是对删除或取消消息的回应。

实例-图书管理系统时序图

1. 系统管理员添加书籍的时序图 2. 图书管理员处理借书的时序图(不包

饮料销售机一般时序图

UML中通过if来表示保护条件。把进入一条路 径而不是其他路径所需要的条件放入到方括号 中。如图中[sold out]只有选购的饮料销售完的 情况下时一个对象才会发送给另一个对象的消 息。在这条消息前面加上[sold out]。

在使用一般顺序图时,按照一种场景的消息序 列完整的走下去,直到得出结论,事务完成, 并保留的信息和其他场景相关。我们可以在每 个场景的最终消息前面加上《transaction over 》。

控制消息种类: 条件控制消息; 重复控制消息。

时序图比较适合于规模较小时的可视化图解,如 果对象很多,交互又很频繁,时序图将变得很复 杂。

对于返回标记,只有在使用了这种返回标志能使 图的意义更清楚时才使用。

时序图

时序图示例

时序图

时序图的组成

时序图包含了4个元素: ① 对象(Object) ② 生命线(Lifeline) ③ 消息(Message) ④ 激活(Activation)

教你如何看懂单片机时序图

教你如何看懂单片机时序图操作时序永远使用是任何一片IC芯片的最主要的内容。

一个芯片的所有使用细节都会在它的官方器件手册上包含。

所以使用一个器件事情,要充分做好的第一件事就是要把它的器件手册上有用的内容提取,掌握。

介于中国目前的芯片设计能力有限,所以大部分的器件都是外国几个IC巨头比如TI、AT、MAXIM这些公司生产的,器件资料自然也是英文的多,所以,英文的基础要在阅读这些数据手册时得到提高哦。

即便有中文翻译版本,还是建议看英文原版,看不懂时不妨再参考中文版,这样比较利于提高。

我们首先来看1602的引脚定义,1602的引脚是很整齐的SIP单列直插封装,所以器件手册只给出了引脚的功能数据表:我们只需要关注以下几个管脚:3脚:VL,液晶显示偏压信号,用于调整LCD1602的显示对比度,一般会外接电位器用以调整偏压信号,注意此脚电压为0时可以得到最强的对比度。

4脚:RS,数据/命令选择端,当此脚为高电平时,可以对1602进行数据字节的传输操作,而此脚为低电平时,则是进行命令字节的传输操作。

命令字节,即是用来对LCD1602的一些工作方式作设置的字节;数据字节,即使用以在1602上显示的字节。

值得一提的是,LCD1602的数据是8位的。

5脚:R/W,读写选择端。

当此脚为高电平可对LCD1602进行读数据操作,反之进行写数据操作。

笔者认为,此脚其实用处不大,直接接地永久置为低电平也不会影响其正常工作。

但是尚未经过复杂系统验证,保留此意见。

6脚:E,使能信号,其实是LCD1602的数据控制时钟信号,利用该信号的上升沿实现对LCD1602的数据传输。

7~14脚:8位并行数据口,使得对LCD1602的数据读写大为方便。

现在来看LCD1602的操作时序:在此,我们可以先不读出它的数据的状态或者数据本身。

所以只需要看两个写时序:① 当我们要写指令字,设置LCD1602的工作方式时:需要把RS 置为低电平,RW置为低电平,然后将数据送到数据口D0~D7,最后E引脚一个高脉冲将数据写入。

第10章 时序图

❖ 矩形本身被称为对象的激活期或控制期,对象就 是在激活期顶端被激活的。

❖ 激活期说明对象正在执行某个动作。当动作完成 后,伴随着一个消息箭头离开对象的生命线,此 时对象的一个激活期也宣告结束。

4.消息

❖ 在任何一个软件系统中,对象都不是孤立存在的, 它们之间通过消息进行通信。

10.4 时序图建模实例

❖ 图书管理系统时序图建模 1.添加借阅者 ❖ 添加借阅者的过程为:系统管理员选择菜单项“添

加借阅者”,弹出AddBorrowerDialog对话框。系 统管理员可以在该对话框中输入借阅者的信息并提 交,随后系统对管理员所提交的借阅者信息进行验 证,查看输入的借阅证号是否已经存在于系统中, 若不存在,则为借阅者创建一个账户,并存储借阅 者信息。

❖ 当消息被处理完后,可以回送一个简单消 息,或者是隐含的返回。

异步消息 (Asynchronous Message)

❖ 异步消息表示发送消息的对象不用等待回 应的返回消息,即可开始另一个活动。

❖ 异步消息在某种程度上规定了发送方和接 收方的责任,即发送方只负责将消息发送 到接收方,至于接收方如何响应,发送方 则不需要知道。对接收方来说,在接收到 消息后它既可以对消息进行处理,也可以 什么都不做。

: Administrator

:ManageWindow :DeleteBorrowerDialog

10.2 时序图元素及表示法

❖ 时序图的这4种图形元素:

① 对象(object) ② 生命线(lifeline) ③ 激活(activation) ④ 消息(message)

1. 对象

❖ 时序图中的对象在概念上和它在对象图中 的定义是一致的,其图形表示也相同。

教你3步画好时序图,轻松掌握产品经理都在学的流程分析利器

产品经理简称PM,是指在公司中针对某一项或是某一类的产品进行规划和管理的人员,主要负责产品的研发、制造、营销、渠道等工作。

产品经理是很难定义的一个角色,如果非要一句话定义,那么产品经理是为终端用户服务,负责产品整个生命周期的人。

产品经理需要考虑目标用户特征、竞争产品、产品是否符合公司的业务模式等等诸多因素。

近年来互联网产品经理火热,一起看下为大家精选的互联网产品经理学习文章。

上次介绍了活动图,这次UML 中,另一种流程分析利器——时序图。

以前每次要分析流程,我都会用活动图。

直到有一次,我面对一个业务流程,画活动图,画来画去,总觉得哪里不对,但又表达不出来,感觉如鲠在喉。

后来,我想起时序图,用时序图把流程梳理了一遍,豁然开朗。

原来,用不同的视图去描述同一个流程,能让我们看到自己未曾发现的问题。

就像看足球比赛,在多个不同位置的摄像镜头下,能看到球员更全面的表现。

此后,我用时序图甚至比活动图还多。

那么,它有啥特别之处,居然能替代活动图来分析流程?我们一起来看看。

01 解读时序图时序图,也叫序列图、顺序图,是UML 中常用的动态视图,用于描述多个对象参与实现业务目标时,彼此之间按时间顺序进行交互的过程。

时序图,用来表达对象或角色之间交互的信息传递和时间顺序,特别方便。

每次梳理流程,跟开发沟通,我都会借助它来描述。

绘制时序图,将一个个对象和其交互动作列出来,可以直观反映出,每个对象对其他对象、或其自身做的交互动作,让我们看到业务内部的运作、系统之间的互动,从而搞清楚业务规则、系统逻辑。

在《火球:UML 大战需求分析》一书中,作者总结特别好:“任何复杂的交互,都可以分解为自己与自己、自己与别人、别人与别人的多个简单交互”。

时序图正体现了这种逻辑,所以,它表达交互逻辑时,非常清晰简单。

客户用ATM 取款的时序图作为产品经理,如果我们能掌握这一利器,用来分析业务、定义需求,与开发沟通,定能大大提高效率。

时序图常见的应用场景,是在支付领域。

什么是PLC时序图

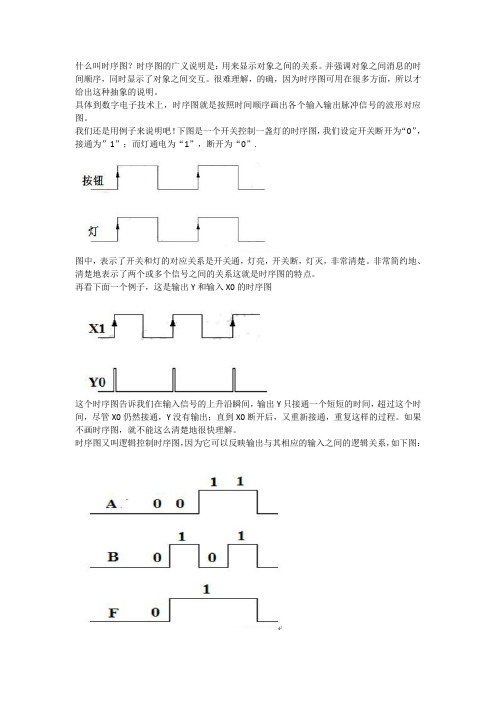

什么叫时序图?时序图的广义说明是:用来显示对象之间的关系。

并强调对象之间消息的时间顺序,同时显示了对象之间交互。

很难理解,的确,因为时序图可用在很多方面,所以才给出这种抽象的说明。

具体到数字电子技术上,时序图就是按照时间顺序画出各个输入输出脉冲信号的波形对应图。

我们还是用例子来说明吧!下图是一个开关控制一盏灯的时序图,我们设定开关断开为“0”,接通为”1”;而灯通电为“1”,断开为“0”.图中,表示了开关和灯的对应关系是开关通,灯亮,开关断,灯灭,非常清楚。

非常简约地、清楚地表示了两个或多个信号之间的关系这就是时序图的特点。

再看下面一个例子,这是输出Y和输入X0的时序图这个时序图告诉我们在输入信号的上升沿瞬间,输出Y只接通一个短短的时间,超过这个时间,尽管X0仍然接通,Y没有输出;直到X0断开后,又重新接通,重复这样的过程。

如果不画时序图,就不能这么清楚地很快理解。

时序图又叫逻辑控制时序图,因为它可以反映输出与其相应的输入之间的逻辑关系,如下图:图中,A,B是F的输入,也就是说,F和A,B之间存在着一定的逻辑关系。

那么如何从时序图中找出它们之间的逻辑关系呢?我们只有按照从上到下,从左到右的顺序关注每一个输入的上升沿和下降沿,写出相应的输入和输出逻辑关系,就会得到一张真值表,通过真值表就可分析得到其相应的逻辑关系。

通过上面所讲的方法,我们就可以写出A、B和F的真值表,如下表所示:比较一下我们在第一章中所学到的逻辑电路知识,马上可以判断这是一个“或”逻辑关系,即F=A+B。

有了逻辑代数式,就可以设计出完成上述功能的电路;有了逻辑代数式,就可以设计出在PLC中能完成上述功能的梯形图程序。

当然,上面是一个最基本的逻辑关系时序图,如果是复杂逻辑关系时序图,同样,也可以先画出输入和输出之间的真值表,再利用逻辑代数的理论进行化简,得到最简的逻辑代数表达式。

从而进一步设计出满足逻辑关系的电路图和梯形图程序。

进一步的知识大家参看相关的书籍和资料。

个教程教你解读器件时序图

3个教程教你解读:器件时序图

1、如何读单片机的时序图,国外的一个培训文档,讲解得很精细,有兴趣有朋友好好读读。

2、MCU如何根据LCD的时序来写底层驱动

3、另外一个教程(整理自国内论坛)

具体内容如下:

时序时序,就是按照一定的时间顺序给出信号

就能得到你想要的数据,或者把你要写的数据写进芯片;

举个KM62256(三星的一种存储器)读数据的例子:

先给地址,地址保持的最短时间是:trc;

再给CS片选;片选滞后地址的最短时间可以算出来;

再给OE(读信号);同样滞后的最短时间也可以算出来;

数据线上本来是高阻态;

这时,滞后OE一段时间之后,数据输出,直到数据有效输出并保持一段时间;然后OE变高;

然后CS变高;

然后改变地址;

这时数据仍然保持一段时间有效;然后无效;然后高阻;

你找一个KM62256(三星的一种存储器)看懂了,其它的芯片也都差不多了;时间参数参考下图:。

时序图-协作图-详解

动态图概念 : 从静态图中抽取瞬间值的变化描述系统随时间变化的行为, 动态图包括交互图活动图状态图, 这篇博客研究交互图包括时序图和协作图;-- 时序图 : 显示对象之间的关系, 强调对象之间消息的时间顺序, 显示对象之间的交互;-- 协作图 : 描述对象之间的交互关系;一.时序图 (Sequence Diagram)1.时序图的概念时序图定义 : 描述了对象之间传递消息的时间顺序, 用来表示用例中的行为顺序, 是强调消息时间顺序的交互图;时序图描述的事物: 时序图描述系统中类和类之间的交互, 将这些交互建模成消息交换, 时序图描述了类以及类之间的交换以完成的期望行为的消息, 时序图中每条消息都代表了类的一个操作或者引起状态机改变的触发事件;时序图表示 : 参与交互的对象在时序图顶端水平排列, 每个对象的底端绘制了一条垂直虚线, 对象A像对象B发送消息, 用一条带箭头的实线表示, 该实线起始于对象A底部的虚线, 终止于对象B底部的虚线; 实线箭头水平放置, 越靠近顶端越早被发送.时序图轨迹 : 时序图提供了随时间推移的, 清晰的可视化的轨迹;2. 时序图组成时序图组成 : 时序图包括四个元素对象(Object), 生命线(Lifeline), 激活(Activation), 消息(Message);(1) 对象(Object)对象: 时序图中的对象在交互中扮演的角色就是对象;对象的符号 : 时序图中的对象与对象图中的表示方法一样, 使用矩形将对象名称包含起来, 并且对象名称下有下划线;对象创建时机 : 对象可以在交互开始的时候创建, 也可以在交互过程中进行创建;-- 处于顶部 : 如果对象的位置在时序图顶部, 说明在交互开始的时候对象就已经存在了;-- 不在顶部: 如果对象的位置不在顶部, 那么对象在交互过程中创建的;(2)生命线(Lifeline)(3)生命线 : 生命线是一条垂直的虚线, 这条虚线表示对象的存在, 在时序图中, 每个对象的底部都有生命线;生命线作用 : 生命线是一个时间线, 从时序图顶部一直到底部都存在, 其长度取决于交互的时间;对象的生命线 : 对象与生命线结合在一起就是对象的生命线, 这个概念包含对象图标以及对象下面的生命线图标如上图;(3) 激活(Activation)激活(Activation): 代表时序图中对象执行一项操作的时期, 激活期可以理解为语义中 {} 中的内容, 表示该对象被占用以完成某个任务;去激活(Deactivation) : 指对象处于空闲状态, 在等待消息激活这个对象;激活的表示 : 当对象处于激活时期, 生命线可以拓宽为矩形, 这个矩形条成为激活条;激活去激活的时机 :-- 激活 : 对象激活是在激活条的顶部激活;-- 去激活 : 激活条的底部去激活, 通常发生在一个消息离开对象生命线;(4) 消息消息概念 : 定义交互和协作中交换信息的类, 对对象之间的通信内容建模;消息动作 :--动作种类: 消息允许在实体间传递信息 (传递参数), 允许实体请求其它服务, 对象之间通过发送和接收消息进行通信;--产生结果: 消息可以触发操作, 唤起信号, 或使目标对象创建或销毁;消息的异步和同步通信 :-- 异步通信 : 消息是信号的时候, 发送信号之后, 等待对方触发相应方法, 这是明确的命名的对象间的异步通信;-- 同步通信 : 直接调用对象的方法, 执行方法返回结果, 这种具有返回控制机制的操作是同步通信;时序图和协作图中消息的区别 : 时序图中的消息强调顺序, 协作图中的消息强调交换消息的对象间的关系;消息类型 :-- : 两个对象间绘制消息;-- : 两个对象之间的过程调用;-- : 两个对象之间的异步消息;-- : 过程调用中返回的消息;-- : 绘制反身消息;3. 时序图示例示例简介 :-- 使用场景: 汽车租赁公司;-- 使用的对象 : Customer (客户), Worker (工作人员), Order (请求), Record (记录), Car (汽车);-- 工作流程 : ①客户向工人提出租车要求, ②工人检查请求, ③客户付款, ④工人填写记录, ⑤工人取车;时序图 :4. 对象的创建和撤销对象位置:-- 顶部 : 时序图中对象的默认位置是在时序图顶部, 这表明对象在交互开始之间就已经存在;-- 中间 : 如果对象在时序图中间部分, 说明对象时在交互过程中创建的;交互过程中创建对象的方法 :--消息指向对象 : 消息是构造方法, 箭头指向对象所代表的的矩形;-- 消息指向激活条 : 消息是构造方法, 箭头指向对象下面的激活条;撤销对象 : 如果想要在时序图中撤销一个对象, 因为如果同时有几个对象, 如果不进行特殊操作其生命周期将会一样长; -- 效果图 : 下图中将 Customer 和 Order 对象撤消了, 因为它们基本没有参与后期的交互;5. 时序图建模技术时序图使用时机 : 对动态行为建模, 强调时间展开信息的次序的时候, 使用时序图;时序图管理策略 :-- 单一控制流 : 一个单独的时序图只能显示一个控制流;-- 多个时序图 : 完整的控制流很复杂, 可以绘制多个时序图, 一个主干时序图, 多个分支时序图, 使用包对这些时序图进行管理;时序图建模策略 :-- 设置交互语境 : 交互所在的环境, 包括哪些对象, 属于什么系统, 子系统, 相关的操作类用例等;-- 对象排列顺序 : 根据对象重要性, 从左到右排列在时序图中;-- 对象生命线 : 对象通常存在于交互的整个过程, 也可以在交互过程中被创建和撤销;-- 消息排列 : 引发交互信息之后, 消息按照时间顺序从上向下画出, 先发出的消息在后发出的消息上面;-- 激活期设置 : 可以将实际操作发生的时间点消息明确的显示出来;-- 时间空间约束: 每个消息都可以附加合适的时间和空间约束;-- 前置后置条件: 每条消息可以附加前置或后置条件;6. Rational Rose 时序图操作(1) 创建时序图新建时序图 : 在视图浏览器中右键点击Logical View (逻辑视图), 选择New(新建) -> Sequence Diagram(时序图);(2) 添加对象添加对象 : 时序图中有两种对象, 一种是参与者Actor, 一种是普通的对象;-- 参与者对象 : 在类图中创建一个对象, 将其 Stereotype 修改为 Actor, 就变成了参与者, 然后在视图浏览器中将这个元素拖到时序图中即可;-- 普通对象 : 直接在时序图中点击按钮, 在界面中创建对象; -- 两种对象效果 :设置对象属性 : 双击对象, 在弹出的 General 对话框中修改对象属性;-- Name: 对象名称, 不输入也可以;-- Document : 描述对象的文档;设置对象持续性 :-- 持续 (Persistent) : 对象保存在数据库或其它形式的永久存储体中;-- 静态 (Static) : 对象保存在内存中知道程序终止;-- 临时 (Transient) : 短时间内保存在内存中;(3) 添加消息消息作用 : 消息用两个对象生命线之间的箭头表示, 一个对象可以通过消息请求另一个对象执行某个操作;增加消息 :-- 发送消息 : 将从发送消息对象的生命线拖到接收消息对象的生命线上;-- 显示取消编号和激活条 : 菜单栏 Tools -> Options -> Diagram 选项卡, Sequence numbering 是消消息编号 , Focus of control 显示激活条;二. 协作图 (Collaboration Diagram)1. 协作图概念协作图: 协作图是一种类图, 包含类元角色和关联角色,不仅仅是类元和关联;-- 强调 : 强调参与交互的各个对象的结构信息和组织;协作图建模对象 : 对有交互的对象和这些对象之间的关系建模, 不参与交互的对象及它们的关系忽略;协作图内容: 协作图中表现了类操作中用到的参数, 布局变量, 操作中的永久链;对象图扩展 : 协作图可以看做对象图的扩展, 该图展示了对象之间的关联, 显示出了对象间的消息传递;2. 协作图内容(1) 对象(Object)对象 : 代表协作图交互中的主体, 和时序图中对象的概念类似;协作图和时序图中对象区别 : 协作图中对象无法创建和撤销, 因此对象在协作图的位置没有限制;(2) 链(Link)链的表示 : 链的符号和对象图中链所用的符号是一样的, 用来连接两个类角色的实线;-- : 创建对象之间的通信路径;-- : 显示对象可以调用自己的属性;-- : 在两个对象之间或一个对象本身增加消息;-- : 在两个对象之间或一个对象本身从反方向增加消息;-- : 显示两个对象之间的信息流;-- : 在反方向显示两个对象之间的信息流;路径构造性 : 对象之间的连接可以由链末尾附加的路径构造型表示;-- 添加方式 : 双击链, 选择 visibility属性即可;(3) 消息 (Message)消息概念 : 对象间通过链接发送的就是消息;--消息传递方向 : 对象之间的箭头表明对象间交换的消息流, 一个对象发出消息, 链指向的对象接收消息, 链用于实现消息传输;-- 消息标识 : 消息流标有消息的序列号和对象间发送的消息名称;-- 消息结果 : 每条消息否会触发接收对象的一系列操作;消息序号 : 协作图与时序图中的消息类型是一样的, 为了表明消息顺序, 需要为消息添加序号;3. 协作图示例示例简介 : 汽车租赁流程;-- 涉及到的对象 : Customer (客户), Order (订单), Worker (工人), Record (记录), Car (汽车);-- 流程简介 : 客户写好订单, 工人核对订单, 核对后订单存在, 允许客户取车, 工人填写记录, 并将车取出;4. 协作图建模策略协作图使用场景 : 对系统动态行为建模, 按组织对控制流建模使用协作图;协作图管理策略 :-- 单个协作图: 单个协作图只能显示一个控制流;--多个协作图 : 描述复杂系统的时候, 需要许多协作图共同描述, 一些图是主干协作图, 还有许多分支路径的控制流的协作图, 使用包管理这些协作图;协作图的建模策略 :-- 设置语境 : 设置协作图所在的环境 , 如系统, 子系统, 类, 操作, 用例或用例脚本;-- 对象顶点 : 识别对象在协作图中扮演的角色, 协作图中, 对象是图的顶点;-- 变化修改 : 每个对象最初都会设置初始值, 如果期间对象发生了变化, 修改的方式是 : 协作图中放置一个复制对象, 更新复制对象, 同过后造型 become copy 连接二者;-- 确定链接顺序 : 先确定关联链接,哪些对象相互链接; 在确定消息链接, 路径构造型等表示对象间如何连接;-- 消息顺序 : 从引起交互的消息开始编号, 将编号信息和描述信息附到链接上, 描述了对象之间的传递次序;-- 时间空间约束 : 可以为每个消息附加时间和空间上的约束;-- 前置后置条件 : 可以为每个消息附加前置和后置条件;5. Rational Rose 绘制协作图(1) 创建协作图创建流程 : 视图浏览器 -> Logical View (逻辑视图) -> New (新建) -> Collaboration Diagram (协作图);(2) 添加对象协作图中添加对象 : 与时序图基本类似;-- 添加参与者对象 : 在类图中创建好类, 然后将类型设置为Actor, 然后在视图浏览器中将Actor拖到协作图中;-- 添加普通对象 : 直接点击工具栏中的图标设置即可;(3) 添加消息添加对象间消息 : 在两个对象之间添加消息;-- 建立通信路径 : 使用连接两个对象, 建立两个对象间的通信路径;-- 添加消息 : 使用或在通信路径上添加消息;-- 设置消息名称 : 双击消息箭头, 可以在弹出的对话框中修改消息名称;添加反身消息 : 选择点击对象, 就会出现指向对象本身的路径, 选择点击这个指向本身的路径, 可以为该对象添加消息;(4) 添加数据流数据流概念 : 数据流是一个对象向另一个对象发送消息返回的消息;-- 使用场景 : 没必要在每个消息上都加上数据流, 只要在中药消息上附加数据流即可;数据流添加方法 : 选择或按钮, 单击要返回的数据消息, 数据流箭头就会被添加到这个消息上;.6. 时序图与协作图转换各自侧重点 : 时序图和协作图是等价的, 可以任意转换, 而不丢失信息;--时序图: 描述交互过程中的时间顺序, 没有明确表达对象间关系;--协作图: 描述了对象间的关系, 但是时间顺序必须从消息的序号中获取;转换示例 :-- 场景介绍 : 学生毕业管理;-- 对象介绍 : 教务人员, 学位评价, 成绩管理, 奖惩管理, 信息打印;-- 控制流介绍 : ①教务人员输入学号进入学位评价模块, ②学位评价模块会向成绩管理模块查询成绩, ③向奖惩管理模块查询奖惩记录, ④学位评价模块会将结果打印到信息打印模块, ⑤信息打印模块将结果返回给教务人员;时序图:协作图 :7. 时序图和协作图对比时序图和协作图共同点 : 都是有消息和类角色组成;-- 规定责任 : 时序图和协作图都规定了消息发送对象和消息接收对象的责任, 每个接收对象都有消息对应的接口, 这个接口方法由消息发送对象触发;-- 支持消息 : 时序图和协作图都支持消息;-- 衡量工具 : 时序图和协作图可以作为衡量系统耦合性的工具, 耦合性就是系统中模型之间的依赖性, 两个模型之间的依赖关系通过查看两个模型之间的消息数量和类型就可以看出, 消息交互少的耦合性高;时序图和协作不同点 :-- 对象创建撤销侧重点 : 时序图侧重描述对象的创建和撤销, 新创建的对象放在对象生命线上对应的时间点, 撤销的对象在结束的地方放一个 X 表示该对象不能再继续使用;协作图中创建撤销的概念不存在, 对象时始终存在的, 只能通过消息描述或约束来说明对象的创建和撤销;-- 链接侧重点 : 时序图中的链没有表示出来, 可以随意绘制消息, 有些逻辑交互可能不会发生; 协作图的消息是映射在链上的, 消息和链平行放置, 如果想要通过消息查看对象之间的关联使用协作图最好;-- 激活和去激活 : 时序图表现有激活和去激活, 协作图上没有时间概念的描述, 无法清晰地表示对象的激活和去激活;三. 实例 - 图书管理系统1. 管理员为图书添加类别控制流说明 :-- 涉及到的对象 : Admin (管理员), BookInfoWindow (图书信息窗口), Tittle (图书类别), Item (图书条目);-- 流程 : 管理员查询图书信息窗口, 查看有没有相应的图书类别, 如果有插入该图书条目;时序图 :\协作图 :2. 管理员删除图书控制流说明 :-- 涉及到的对象 : Admin (管理员), BookInfoWindow (图书信息窗口), Tittle (图书类别), Item(图书条目);-- 控制流程 : 管理员登陆图书信息窗口删除图书, 查表图书类别是否存在, 查找图书是否存在, 如果都返回true, 删除图书条目;时序图 :协作图 :3. 管理员借书时序图控制流说明 :-- 参与的对象 : Admin (管理员), BookInfoWindow (图书信息窗口), Tittle (图书类别), Borrower (借阅者), Loan (借书记录), item (图书条目);-- 流程 : 管理员登陆图书信息窗口, 查询图书类别是否存在, 查询图书条目是否存在, 查询借阅者是否存在, 创建借书记录;时序图 :协作图 :21。

如何看懂时序图

时序图,LCD1602前面总算走完了对AVR MEGA16这块单片机的一些基本的应用方式了,这时候大家对AVR的一些内部资源比如定时器,ADC,最主要的IO口的使用方式应该有了一个虽比较粗浅但是却比较形象的认识了。

这节我们来看使用单片机的另外一大主题,就是用单片机来实现芯片控制。

在前面的数码管显示一文中,就已经涉及到了用单片机来控制芯片为我们工作,CEPARK AVR开发板,为了达到增强驱动能力和节省IO口的作用,运用了移位寄存器74HC595来驱动两个四位八段数码管,是一个十分有创意的设计。

但是前面的内容重心还是集中于对AVR的IO口的控制,所以,我们从这节开始要正式逐渐深入的接触各种芯片了。

先做个引子。

单片机是一种微控制器,本身内部集成了数种资源比如CPU、内存、内部和外部总线系统,目前大部分还会具有外存。

他的主要任务是利用各种资源实现电平控制,可以以此控制与它相连的下级系统,广泛用于工业自动控制领域。

我们就从这句话出发,首先单片机是用来做控制用的,而且利用的是本身的内部资源。

但是,它的功能再强大,资源再丰富也总有一个上限,总有枯竭的一天。

所以我们常常利用单片机外接芯片来弥补或者增强单片机的功能来完成我们所需功能的电路。

比如程序存储器不足,可以外接外部存储器,比如单片机内部中断级不足,可以外接中断控制器等等。

大家可以从这个角度来理解芯片控制的意义罢。

今天我们用AVR单片机来实现对LCD1602液晶显示芯片的控制。

首先从这个名字讲起,LCD:英文全称为Liquid Crystal Display,即为液态晶体显示,也就是我们常说的液晶显示了。

(平时老说LCDLCD,可能大家也都不怎么注意过这个全称吧,呵呵,当增加词汇量了)1602则是表示这个液晶一共能显示2行数据,每一行显示16个字符。

这个就是LCD1602的全部来由。

液晶显示的使用有多广泛我就不多说了,LCD1602好像10元左右就可以拿到了的,不算贵。

如何读懂时序图

/itangcleCPE/EE 421MicrocomputersWEEK #10Interpreting the Timing Diagram如何读懂时序图The 68000 Read Cycle2 Alan Clements3 Actual behavior of a D flip - f lopTiming Diagram of a Simple Flip - F lopIdealized form of the timing diagramData hold timeData setup time Max time for output to become valid after clock4 An alternative form of the timing diagramGeneral form of the timing diagramA memory access begins in clockstate S0 and ends in state S76The most important parameterof the clock is the duration of a cycle, t C YC.8Address Timing地址时序•We are interested in when the 68000 generates a new address for use in the current memory access我们感兴趣的是当6800芯片能够生成一个新的地址供当前的内存访问•The next slide shows the relationship between the new address and the state of the 68000 ’s clock下面展示的是新的地址跟6800芯片时钟的关系Alan Clements1: S0在没有初始化的时候,地址总线总是包涵新的地址。

LCD1602液晶显示屏幕时序图分析

LCD1602液晶显示屏幕时序图分析

这段时间里回头看看所学的单片机知识,发现一个很严重的问题看不懂时序图!研究了一上午说说自己的结果,欢迎各位拍砖和指点!

图7.2.2是1602液晶写的时序,时序图从上到下看、从左到右看。

先说说时序图的规则:

高低电平上面的线是高电平,下面的线是低电平,如果高低交叉可能会产生高电平或低电平。

电平的走向看到低电平和高电平交叉产生电平的变化,

看到红圈花的部分,竖线那里有条横线,代表着这个选用的是高电平。

还有一种情况

这种情况是高低电平一起变化,看图中横线标出了电平的变化。

现在我们了解完了规则,现在分析时序图

原图我进行了标号。

时序图从上往下看,从左往右看

1 rs 为高电平 rw 为低电平

2 载入数据db

3 始能e由低电平变为高电平

4和5 始能e由高电平转化为低电平最后数据写完。

这个就是我的理解,如果有错误或不对的地方欢迎指正。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/itangcle

CPE/EE 421

Microcomputers

WEEK #10

Interpreting the Timing Diagram

如何读懂时序图

The 68000 Read Cycle

2 Alan Clements

3 Actual behavior of a D flip - f lop

Timing Diagram of a Simple Flip - F lop

Idealized form of the timing diagram

Data hold time

Data setup time Max time for output to become valid after clock

4 An alternative form of the timing diagram

General form of the timing diagram

A memory access begins in clock

state S0 and ends in state S7

6

The most important parameter

of the clock is the duration of a cycle, t C YC.

8

Address Timing

地址时序

•We are interested in when the 68000 generates a new address for use in the current memory access

我们感兴趣的是当6800芯片能够生成一个新的地址供当前的内存访问

•The next slide shows the relationship between the new address and the state of the 68000 ’s clock

下面展示的是新的地址跟6800芯片时钟的

关系

Alan Clements

1: S0在没有初始化的时候,地址总线总是包涵新的地址。

2: S1这个状态说明一个新的地址可以供内存访问

Alan Clements

Address Timing

地址时序

• Let’s look at the sequence of events that govern the timing of the address bus 让我们看看事件发生的顺序,管理时间的地址总线 • The “old” address is removed in state S0 旧的地址已经从S0中移除

• The address bus is floated for a short time, and the CPU puts out a new address in state S1

地址要先存在一小段时间后,CPU 才能把心的地址状态写入S1中12

The old address is removed in clock state S0 and the address bus floated

t C LA V

The designer is interested in the point at which the address first becomes valid. This point is t C LA V seconds after the falling edge of S0.

Address and Address Strobe

地址跟地址选通

•We are interested in the relationship between the time at which the address is valid and the time at which the address strobe, AS*, is asserted

我们感兴趣的事在地址总线能够访问时,地址选通是否有效。

•When AS* is active-low it indicates that the

上图说明:1:当地址有效的时候把AS 低电平信号.

当地址要改变前,要把AS变成高电We now look at the timing of the clock, the address, and the address strobe

从上面的时序图可以看出到,时钟脉冲,地址信号,片选脉冲;3者的关系。

16

AS* goes low in clock state S2

The Data Strobes 数据选通•The 68000 has two data strobes LDS* and UDS*. These select the lower byte or the upper byte of a word during a memory access

6800芯片有两个数据选通信号LDS(低)和UDS(高).内存通过选择LDS和UDS来访问数据。

•To keep things simple, we will use a single data strobe, DS* 为了让事情看起来简单,我们只要选通DS就可以了。

(DS的高8位是UDS低8位是LDS)

•The timing of DS* in a read cycle is the same as the address strobe, AS*

DS的读数据跟AS读地址的时序是一样的。

Alan Clements 19

Alan Clements

The data strobe, is asserted

at the same time as AS*

in a read cycle

During a read cycle the memory provides 20

Alan Clements

Alan Clements 21

Analyzing the Timing Diagram

分析时序图

• We are going to redraw the timing diagram to remove clutter

让我们从头到脚分析这个时序图让头脑不那么乱

• We aren’t interested in the signal paths

themselves, only in the relationship between the signals 我们不能单单从一条信号线来分析了,我们得从整体上来分析。

据选通)和数据在读周期

Alan Clements

Alan Clements

在地址开始有效的时候,内存就可以访问数据了。

在地址可访问,内存可以接收数据的时间是t acc 秒。

Alan Clements

Calculating the Access Time

计算访问时间

• We need to calculate the memory’s access time 我们必须计算内存的访问时间

• By knowing the access time, we can use the appropriate memory component 通过了解访问时间,我们可以适当使用内存

• Equally, if we select a given memory component, we can calculate whether its access time is adequate for a particular system 同样,如果我们选择一个特定内存组件,我们可以计算出它的访问时间是否足够用来在一个特定的系统

Alan Clements 27

28

Alan Clements

在t DICL 后,数据必须有效。

Alan Clements

我们知道在地址和数据可以访问的时候之间的时间是t acc 秒

Alan Clements

地址数据在t CLA V 后能被访问

Alan Clements

在地址有效,从S0到S6结束,数据就别俘获了。

Alan Clements

Alan Clements 33

34

Timing Example

•68000 clock 8 MHz t CYC = 125 ns •68000 CPU t CLA V = 70 ns

•68000 CPU t DICL = 15 ns

•What is the minimum t acc?

•3 t CYC = t CLA V + t acc + t DICL

•375 = 70 + t acc + 15

•t acc = 290 ns

Alan Clements 35。