二进制数到BCD码的转换

二进制转换成十进制BCD码(加3移位法)

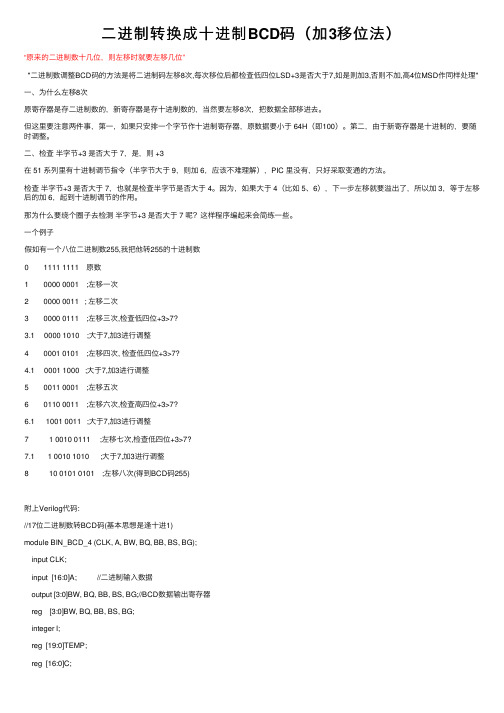

⼆进制转换成⼗进制BCD码(加3移位法)“原来的⼆进制数⼗⼏位,则左移时就要左移⼏位”"⼆进制数调整BCD码的⽅法是将⼆进制码左移8次,每次移位后都检查低四位LSD+3是否⼤于7,如是则加3,否则不加,⾼4位MSD作同样处理"⼀、为什么左移8次原寄存器是存⼆进制数的,新寄存器是存⼗进制数的,当然要左移8次,把数据全部移进去。

但这⾥要注意两件事,第⼀,如果只安排⼀个字节作⼗进制寄存器,原数据要⼩于 64H(即100)。

第⼆,由于新寄存器是⼗进制的,要随时调整。

⼆、检查半字节+3 是否⼤于 7,是,则 +3在 51 系列⾥有⼗进制调节指令(半字节⼤于 9,则加 6,应该不难理解),PIC ⾥没有,只好采取变通的⽅法。

检查半字节+3 是否⼤于 7,也就是检查半字节是否⼤于 4。

因为,如果⼤于 4(⽐如 5、6),下⼀步左移就要溢出了,所以加 3,等于左移后的加 6,起到⼗进制调节的作⽤。

那为什么要绕个圈⼦去检测半字节+3 是否⼤于 7 呢?这样程序编起来会简练⼀些。

⼀个例⼦假如有⼀个⼋位⼆进制数255,我把他转255的⼗进制数0 1111 1111 原数1 0000 0001 ;左移⼀次2 0000 0011 ; 左移⼆次3 0000 0111 ;左移三次,检查低四位+3>7?3.1 0000 1010 ;⼤于7,加3进⾏调整4 0001 0101 ;左移四次, 检查低四位+3>7?4.1 0001 1000 ;⼤于7,加3进⾏调整5 0011 0001 ;左移五次6 0110 0011 ;左移六次,检查⾼四位+3>7?6.1 1001 0011 ;⼤于7,加3进⾏调整7 1 0010 0111 ;左移七次,检查低四位+3>7?7.1 1 0010 1010 ;⼤于7,加3进⾏调整8 10 0101 0101 ;左移⼋次(得到BCD码255)附上Verilog代码://17位⼆进制数转BCD码(基本思想是逢⼗进1)module BIN_BCD_4 (CLK, A, BW, BQ, BB, BS, BG);input CLK;input [16:0]A; //⼆进制输⼊数据output [3:0]BW, BQ, BB, BS, BG;//BCD数据输出寄存器reg [3:0]BW, BQ, BB, BS, BG;integer I;reg [19:0]TEMP;reg [16:0]C;always @ (posedge CLK)beginC=A;TEMP=0;for (I=1; I<17; I=I+1)begin{TEMP, C}={TEMP[18:0], C, 1'b0};//左移⼀位 if (TEMP[3:0]>4'b0100)beginTEMP[3:0]=TEMP[3:0]+3; // >4则加3endif (TEMP[7:4]>4'b0100)beginTEMP[7:4]=TEMP[7:4]+3;endif (TEMP[11:8]>4'b0100)beginTEMP[11:8]=TEMP[11:8]+3;endif (TEMP[15:12]>4'b0100)beginTEMP[15:12]=TEMP[15:12]+3;endif (TEMP[19:16]>4'b0100)beginTEMP[19:16]=TEMP[19:16]+3;end{BW, BQ, BB, BS, BG}={TEMP[18:0], A[0]}; endendendmodule。

二进制与BCD码转换资料

16位二进制数转换成BCD码的的快速算法-51单片机2010-02-18 00:43在做而论道上篇博文中,回答了一个16位二进制数转换成BCD码的问题,给出了一个网上广泛流传的经典转换程序。

程序可见:/%D7%F6%B6%F8%C2%DB%B5%C0/blog/item/6154551f93ba561440341732. html中的HEX2BCD子程序。

.说它经典,不仅是因为它已经流传已久,重要的是它的编程思路十分清晰,十分易于延伸推广。

做而论道曾经利用它的思路,很容易的编写出了48位二进制数变换成16位BCD码的程序。

但是这个程序有个明显的缺点,就是执行时间太长,转换16位二进制数,就必须循环16遍,转换48位二进制数,就必须循环48遍。

上述的HEX2BCD子程序,虽然长度仅仅为26字节,执行时间却要用331个机器周期。

.单片机系统多半是用于各种类型的控制场合,很多时候都是需要“争分夺秒”的,在低功耗系统设计中,也必须考虑因为运算时间长而增加系统耗电量的问题。

为了提高整机运行的速度,在多年前,做而论道就另外编写了一个转换程序,程序的长度为81字节,执行时间是81个机器周期,(这两个数字怎么这么巧!)执行时间仅仅是经典程序的1/4!.近来,在网上发现了一个链接:/news/Article/uc/uc8051/200803/4751.html,也对这个经典转换程序进行了改进,话是说了不少,只是没有实质性的东西。

这篇文章提到的程序,一直也没有找到,也难辩真假。

这篇文章好像是选自某个著名杂志,但是在术语的使用上,有着明显的漏洞,不像是专业人员的手笔。

比如说文中提到的:“使用51条指令代码,但执行这段程序却要耗费312个指令周期”,就是败笔。

51条指令代码,真不知道说的是什么,指令周期是因各种机型和指令而异的,也不能表示确切的时间。

.下面说说做而论道的编程思路。

;-----------------------------------------------------------------------;已知16位二进制整数n以b15~b0表示,取值范围为0~65535。

二进制,十进制,十六进制,ASCII,BCD码的转换,单片机

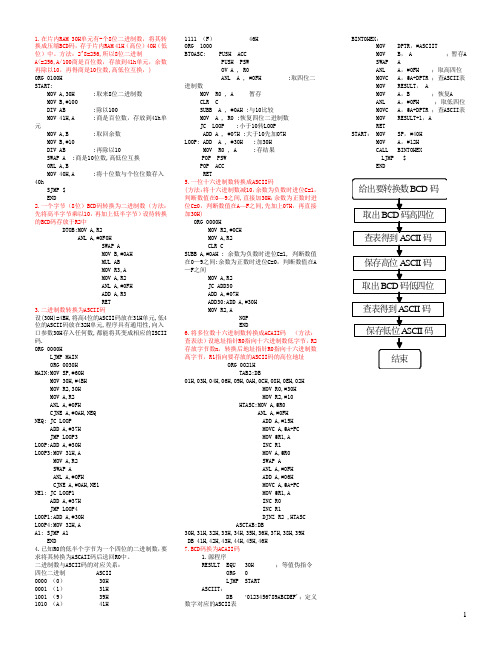

1.在片内RAM 30H单元有-个8位二进制数,将其转换成压缩BCD码,存于片内RAM 41H(高位)40H(低位)中。

方法:2^8=256,所以8位二进制A<=256,A/100商是百位数,存放到41h单元,余数再除以10,再得商是10位数,高低位互换,) ORG 0100HSTART:MOV A,30H ;取来8位二进制数MOV B,#100DIV AB ;除以100MOV 41H,A ;商是百位数,存放到41h单元MOV A,B ;取回余数MOV B,#10DIV AB ;再除以10SWAP A ;商是10位数,高低位互换ORL A,BMOV 40H,A ;将十位数与个位位数存入40hSJMP $END2.一个字节(8位)BCD码转换为二进制数(方法:先将高半字节乘以10,再加上低半字节)设待转换的BCD码存放于R2中DTOB:MOV A,R2ANL A,#0F0HSWAP AMOV B,#0AHMUL ABMOV R3,AMOV A,R2ANL A,#0FHADD A,R3RET3.二进制数转换为ASCII码设(30H)=4BH,将高4位的ASCII码放在31H单元,低4位的ASCII码放在32H单元,程序具有通用性,向入口参数30H存入任何数,都能将其变成相应的ISCII 码.ORG 0000HLJMP MAINORG 0030HMAIN:MOV SP,#60HMOV 30H,#4BHMOV R2,30HMOV A,R2ANL A,#0FHCJNE A,#0AH,NEQNEQ: JC LOOPADD A,#37HJMP LOOP3LOOP:ADD A,#30HLOOP3:MOV 31H,AMOV A,R2SWAP AANL A,#0FHCJNE A,#0AH,NE1NE1: JC LOOP1ADD A,#37HJMP LOOP4LOOP1:ADD A,#30HLOOP4:MOV 32H,AA1: SJMP A1END4.已知R0的低半个字节为一个四位的二进制数,要求将其转换为ASCAII码后送回R0中。

16位二进制转换为BCD码的C51汇编程序

SWAP A

ANL 36H,#0F0H

MOV A,36H

SWAP A

MOV 30H,A

RET

XIANSHI:MOV DPTR,#TAB

DE: MOV R6,#0FFH

DJNZ R6,$

DJNZ R7,DE

RET

TAB:DB 3FH,05H,5BH,4FH,65H,6EH,7EH,07H,7FH,6FH

DB 0BFH,85H,0DBH,0CFH,0E5H,0EEH,0FEH,87H,0FFH,0EFH

UBCD: MOV A,34H

CJNE A,#00H,WUWEI

MOV R1,#35H

MOV R0,#36H

MOV A,#00H

XCHD A,@R0

AJMP RETURN

JIA: CLR C

MOV A,36H

ADDC A,#56H

DA A

MOV 36H,A

MOV A,35H

16位二进制转BCD码的程序算法及51汇编实现:

n=b15~b0

n=[b15~b8]*256+[b7~b0]

=[b15~b12]*4096+[b11~b0]

,高四位[b15~b12]取值范围为0~15,代表了4096的个数

n=[b15~b12]*4000+{[b15~b12]*(100-4)+[b11~b0]}

[b6~b0]中减去2*y

就有:

n=n=4*x(千位)+(x+y)(百位)+3*y(十位)+[b6~b0]-2*y

由此,就可以明确由高9位[b15~b7]变换出来十进制的各个位的数值,可能大于9,到最后整理一下即可。

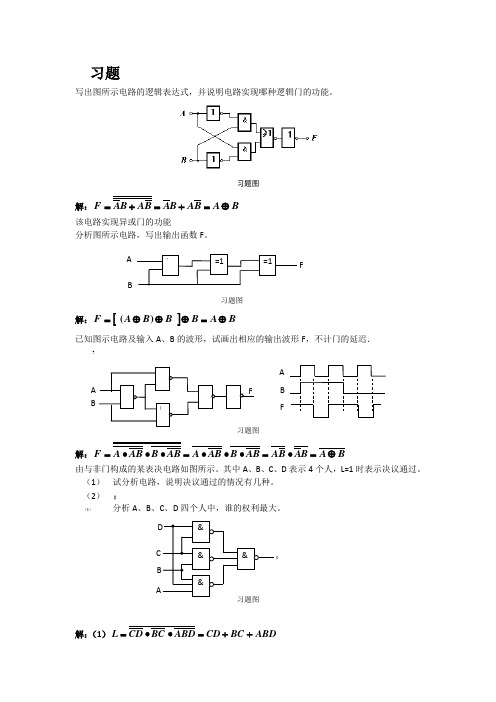

第4章_组合逻辑电路习题解答

习题写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能分析图所示电路,写出输出函数F 。

习题图 解:[]B A B BB A F ⊕=⊕⊕⊕=)(已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.?解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 【 (3) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题图解:(1)ABD BC CD ABD BC CD L ++=••=C & && & D $ L B A " =1=1 =1FFA B[FB A(2)(3)根据真值表可知,四个人当中C 的权利最大。

分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

&习题图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)(3)当S 1S 0=00和S 1S 0=11时,该电路实现两输入或门,当S 1S 0=01时,该电路实现两输入或非门,当S 1S 0=10时,该电路实现两输入与非门。

(2)1¥电路逻辑功能为:“判输入ABC 是否相同”电路。

已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题图:解:(1)根据波形图得到真值表:,(2)由真值表得到逻辑表达式为C AB BC A C B A F ++=、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

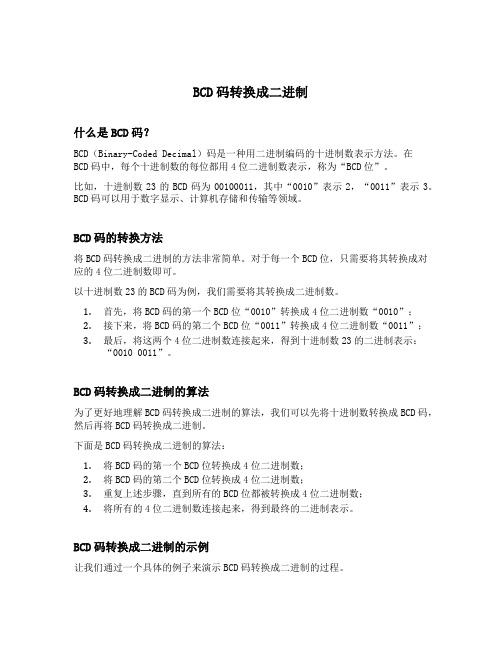

bcd码转换成二进制

BCD码转换成二进制什么是BCD码?BCD(Binary-Coded Decimal)码是一种用二进制编码的十进制数表示方法。

在BCD码中,每个十进制数的每位都用4位二进制数表示,称为“BCD位”。

比如,十进制数23的BCD码为00100011,其中“0010”表示2,“0011”表示3。

BCD码可以用于数字显示、计算机存储和传输等领域。

BCD码的转换方法将BCD码转换成二进制的方法非常简单。

对于每一个BCD位,只需要将其转换成对应的4位二进制数即可。

以十进制数23的BCD码为例,我们需要将其转换成二进制数。

1.首先,将BCD码的第一个BCD位“0010”转换成4位二进制数“0010”;2.接下来,将BCD码的第二个BCD位“0011”转换成4位二进制数“0011”;3.最后,将这两个4位二进制数连接起来,得到十进制数23的二进制表示:“0010 0011”。

BCD码转换成二进制的算法为了更好地理解BCD码转换成二进制的算法,我们可以先将十进制数转换成BCD码,然后再将BCD码转换成二进制。

下面是BCD码转换成二进制的算法:1.将BCD码的第一个BCD位转换成4位二进制数;2.将BCD码的第二个BCD位转换成4位二进制数;3.重复上述步骤,直到所有的BCD位都被转换成4位二进制数;4.将所有的4位二进制数连接起来,得到最终的二进制表示。

BCD码转换成二进制的示例让我们通过一个具体的例子来演示BCD码转换成二进制的过程。

假设我们要将十进制数27转换成BCD码,然后再将BCD码转换成二进制。

1.将十进制数27转换成BCD码,得到BCD码的表示为“0010 0111”;2.将BCD码的第一个BCD位“0010”转换成4位二进制数“0010”;3.将BCD码的第二个BCD位“0111”转换成4位二进制数“0111”;4.将这两个4位二进制数连接起来,得到最终的二进制表示:“0010 0111”。

总结BCD码是一种用二进制编码的十进制数表示方法。

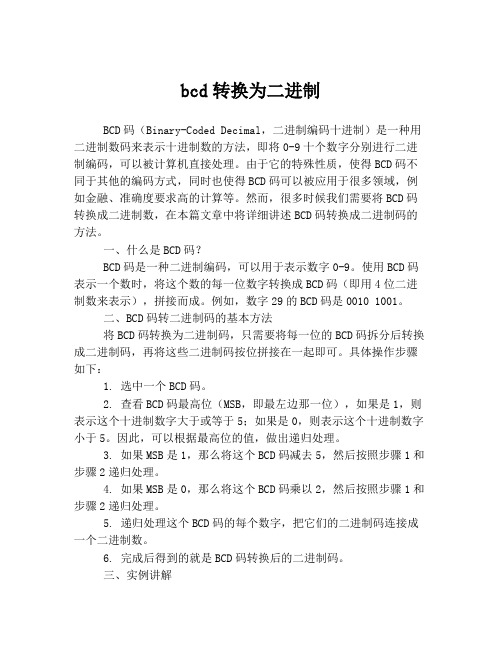

bcd转换为二进制

bcd转换为二进制BCD码(Binary-Coded Decimal,二进制编码十进制)是一种用二进制数码来表示十进制数的方法,即将0-9十个数字分别进行二进制编码,可以被计算机直接处理。

由于它的特殊性质,使得BCD码不同于其他的编码方式,同时也使得BCD码可以被应用于很多领域,例如金融、准确度要求高的计算等。

然而,很多时候我们需要将BCD码转换成二进制数,在本篇文章中将详细讲述BCD码转换成二进制码的方法。

一、什么是BCD码?BCD码是一种二进制编码,可以用于表示数字0-9。

使用BCD码表示一个数时,将这个数的每一位数字转换成BCD码(即用4位二进制数来表示),拼接而成。

例如,数字29的BCD码是0010 1001。

二、BCD码转二进制码的基本方法将BCD码转换为二进制码,只需要将每一位的BCD码拆分后转换成二进制码,再将这些二进制码按位拼接在一起即可。

具体操作步骤如下:1. 选中一个BCD码。

2. 查看BCD码最高位(MSB,即最左边那一位),如果是1,则表示这个十进制数字大于或等于5;如果是0,则表示这个十进制数字小于5。

因此,可以根据最高位的值,做出递归处理。

3. 如果MSB是1,那么将这个BCD码减去5,然后按照步骤1和步骤2递归处理。

4. 如果MSB是0,那么将这个BCD码乘以2,然后按照步骤1和步骤2递归处理。

5. 递归处理这个BCD码的每个数字,把它们的二进制码连接成一个二进制数。

6. 完成后得到的就是BCD码转换后的二进制码。

三、实例讲解以BCD码1001(即数字9的BCD码)为例,通过上述步骤,将其转换为二进制码的过程如下:1. 选中BCD码1001。

2. 最高位为1,表示这个十进制数字大于等于5。

3. 1001 - 0101 = 0100。

减去5,得到4,然后对这个数字应用上述步骤。

4. 选中BCD码0100。

5. 最高位为0,表示这个十进制数字小于5。

6. 0100 * 2 = 1000。

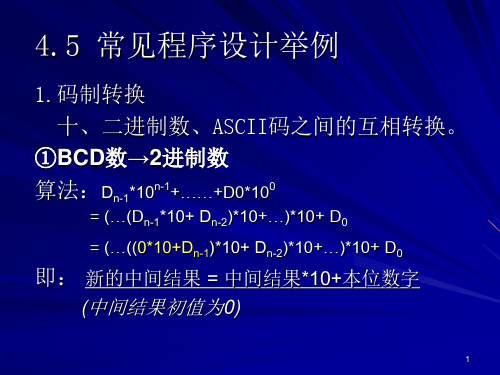

码制转换十二进制数ASCII码之间的互相转换BCD

MOV SS,AX

MOV SP,TOP

LEA BX,STRING ;取变量偏址

PUSH BX

;将偏址压栈

PUSH NUM

;将变量压栈

堆栈

AF 25 02 00

0060H 0062H 0064H

26

CALL BINHEX

;(SP)=005EH

CS:0113 LEA DX,STRING ;(DX)=0002H

;若(CL)=0,转NEXT2 ;取字符 ;转换成BCD码 ;加到中间结果上

10

MOV MUL INC JMP NEXT2: MOV AND ADD CMP JNZ NEG NEXT3: MOV RET

DX,10 DX BX SHORT LP1 DL,[BX] DL,0FH AX,DX CH,’-’ NEXT3 AX [DI],AX

(AX)+1000(AX) DL存至缓冲区 令(DL)=0

求100的个数,结构同上

A

(AX)-10

Y

<0?

N

(DL)+1

(AX)+10(AX) 存DL 存AL

返回DOS

15

汇编程序如下:

DATA SEGMENT BNUM DB 270FH DNUM DB 4 DUP(?) ;存放BCD码的缓冲区 DATA ENDS CODE SEGMENT

STR1

0A

02

32

36

0D …

STR2

0A

02

33 33

0D …

NUM

1A

00

21

00

SUM

3B

00

OVER

‘O’

…

…

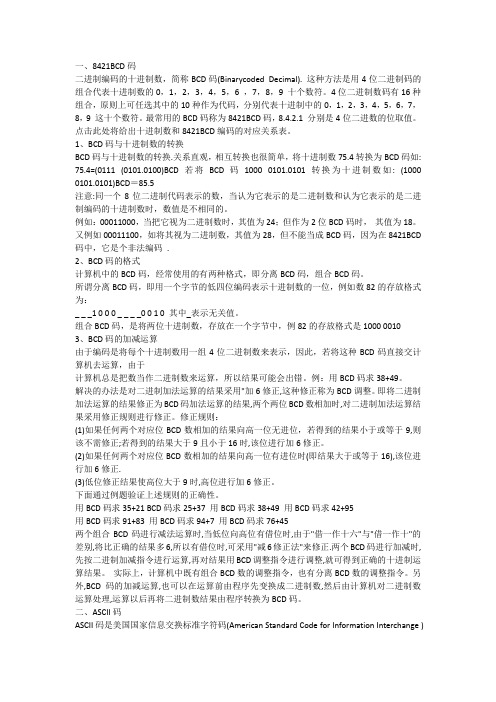

8421BCD码、ASCII码、二进制码

一、8421BCD码二进制编码的十进制数,简称BCD码(Binarycoded Decimal). 这种方法是用4位二进制码的组合代表十进制数的0,1,2,3,4,5,6 ,7,8,9 十个数符。

4位二进制数码有16种组合,原则上可任选其中的10种作为代码,分别代表十进制中的0,1,2,3,4,5,6,7,8,9 这十个数符。

最常用的BCD码称为8421BCD码,8.4.2.1 分别是4位二进数的位取值。

点击此处将给出十进制数和8421BCD编码的对应关系表。

1、BCD码与十进制数的转换BCD码与十进制数的转换.关系直观,相互转换也很简单,将十进制数75.4转换为BCD码如: 75.4=(0111 (0101.0100)BCD 若将BCD码1000 0101.0101转换为十进制数如: (1000 0101.0101)BCD=85.5注意:同一个8位二进制代码表示的数,当认为它表示的是二进制数和认为它表示的是二进制编码的十进制数时,数值是不相同的。

例如:00011000,当把它视为二进制数时,其值为24;但作为2位BCD码时,其值为18。

又例如00011100,如将其视为二进制数,其值为28,但不能当成BCD码,因为在8421BCD 码中,它是个非法编码.2、BCD码的格式计算机中的BCD码,经常使用的有两种格式,即分离BCD码,组合BCD码。

所谓分离BCD码,即用一个字节的低四位编码表示十进制数的一位,例如数82的存放格式为:_ _ _1 0 0 0 _ _ _ _0 0 1 0 其中_表示无关值。

组合BCD码,是将两位十进制数,存放在一个字节中,例82的存放格式是1000 00103、BCD码的加减运算由于编码是将每个十进制数用一组4位二进制数来表示,因此,若将这种BCD码直接交计算机去运算,由于计算机总是把数当作二进制数来运算,所以结果可能会出错。

例:用BCD码求38+49。

解决的办法是对二进制加法运算的结果采用"加6修正,这种修正称为BCD调整。

八位二进制码转化为BCD码及余三码、BCD码转化余三码

河南科技大学课程设计说明书课程名称 EDA技术题目八位二进制转化为BCD码及余三码、BCD码转化为余三码学院车辆与动力工程学院班级学生姓名指导教师日期2012年7月14号八位二进制码转化为BCD码及余三码、BCD码转化余三码摘要八位二进制数转化为BCD码和余三码的转换在计算机语言中起到了非常重要的作用,通过这次的课程设计让我们更好地掌握二进制数转化为BCD 码和余三码。

二进制转化为余三码不能直接转化,只能通过BCD码为中介进而转化成余三码。

余三码(余3码)是由8421BCD码加上0011形成的一种无权码,由于它的每个字符编码比相应的8421BCD码多3,故称为余三码。

BCD码的一种。

余三码是一种对9的自补代码,因而可给运算带来方便。

其次,在将两个余三码表示的十进制数相加时,能正确产生进位信号,但对“和”必须修正。

修正的方法是:如果有进位,则结果加3;如果无进位,则结果减3。

如,(526)10进制=(0101 0010 0110)8421BCD码=(1000 0101 1001)余3码EDA技术打破了软件和硬件间的壁垒,使计算机的软件技术与硬件实现、设计效率与产品性能合二为一,它代表了电子设计技术和应用技术的发展方向。

VHDL主要用于描述数字系统的接口,结构和功能,它的语法简单易懂,移植性好。

本设计采用VHDL,Altera公司的Quartus II软件仿真,来实现八位二进制到BCD和BCD到余三码的转换。

由于八位二进制的最大范围是0~255,而八位BCD码的范围是0~99,故在转换时输入信号只能取99以内的数。

关键词:八位二进制、BCD码、余三码、VHDL目录第一章绪论 (1)§1.1 课程设计题目 (1)§1.2 设计目的 (2)§1.3 课程设计要求 (2)第二章EDA、VHDL简介 (3)§2.1 EDA简介 (3)§2.2 VHDL简介 (3)第三章设计过程 (5)§3.1设计规划 (5)§3.2各个模块设计及原理图 (5)§3.2.1八位二进制码转化为八位BCD码 (5)§3.2.2八位BCD码转化为八位余三码 (6)§3.2.3八位二进制码转化为8位余三码 (7)第四章系统仿真 (9)§4.1八位二进制码转化为八位BCD码仿真及分析 (9)§4.2八位BCD码转化为八位余三码仿真及分析 (9)§4.3八位二进制码转化为八位余三码仿真及分析 (10)第五章总结 (11)参考文献 (12)第一章绪论随着计算机科学与技术突飞猛进地发展,用数字电路进行信号处理的优势也更加突出,自20世纪70年代开始,这种用数字电路处理模拟信号的所谓“数字化”浪潮已经席卷了电子技术几乎所有的应用领域EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

二进制转化bcd

二进制码转BCD码在单片机里面,如:显示个温度值,这时,要取一个数的个位、十位、百位,可以用/和 %(求商和求余)来解决。

但是,在FPGA里面用求商和求余将会非常消耗资源,这样就必须用到二进制转BCD码了,这里介绍一种简单的加3移位算法。

注:B代表二进制,D代表十进制,0x代表十六进制,BCD为BCD 码,下同。

1、加3移位法以二进制数(0000_101 Xn)B=(10+Xn)D为例,串行输入三位后,(0101)B=5(D)左移一位后:(0000_101Xn)B=(10+Xn)D如果(0000_101Xn)B直接输出显示为:当Xn=0时,0000_1010=0x0A。

此为错误的BCD码。

采用加3移位法,修正移位结果:串行输入三位后,结果大于4(0101)B=5(D)加3:(0101)B+(0011)B=(1000)B --十进制表示:5+3=8 再左移一位后:(1000Xn)B=(0001_000Xn)BCD对应十进制显示:1 Xn每四位BCD码对应一位十进制数,即:(10+Xn)D,转换成功注:Xn为下一位串行输入的二进制数。

2、设计思路这里一共需要四个模块:计数器、移位器、加法器、寄存器输出。

分别设计好之后,用状态机控制它们,就完成了。

3、仿真结果注:图中clk为时钟,en为高电平使能,rst为高电平复位,data_in为输入的12位二进制码,以十进制的形式显示在时序图;qout为输出的16位BCD码,以十六进制的形式显示在时序图,17个时钟上升沿可完成转换任务。

4、综合结果5、难点分析要搞懂这个加3移位算法,必须要按照8位二进制(11101011)转BCD过程图,自己手动推导一下,才容易理解。

此算法的难点在于,需要把输入的二进制数,按照每四个bit来划分为一个单元(所以输入的二进制数,位宽必须是4的倍数),然后,每个单元都要同时判断是否大于4,大于就要加3,否则不加.理解了这个算法之后,那么BCD转二进制就非常容易了,减3移位即可,减3可以用补码来解决。

bcd码的转换

bcd码也叫8421码就是将十进制的数以8421的形式展开成二进制,大家知道十进制是0~9十个数组成,着十个数每个数都有自己的8421码:0=00001=00012=00103=00114=01005=01016=01107=01118=10009=1001举个例子:321的8421码就是3 2 10011 0010 0001二进制编码的十进制数,简称BCD码(Binarycoded Decimal). 这种方法是用4位二进制码的组合代表十进制数的0,1,2,3,4,5,6 ,7,8,9 十个数符。

4位二进制数码有16种组合,原则上可任选其中的10种作为代码,分别代表十进制中的0,1,2,3,4,5,6,7,8,9 这十个数符。

最常用的BCD码称为8421BCD 码,8.4.2.1 分别是4位二进数的位取值。

右图为十进制数和8421BCD编码的对应关系表:1、BCD码与十进制数的转换BCD码与十进制数的转换.关系直观,相互转换也很简单,将十进制数75.4转换为BCD码如:75.4=(0111 (0101.0100)BCD 若将BCD码1000 0101.0101转换为十进制数如: (1000 0101.0101)BCD=85.5注意:同一个8位二进制代码表示的数,当认为它表示的是二进制数和认为它表示的是二进制编码的十进制数时,数值是不相同的。

例如:00011000,当把它视为二进制数时,其值为24;但作为2位BCD码时,其值为18。

又例如00011100,如将其视为二进制数,其值为28,但不能当成BCD码,因为在8421BCD码中,它是个非法编码.2、BCD码的格式计算机中的BCD码,经常使用的有两种格式,即分离BCD码,组合BCD 码。

所谓分离BCD码,即用一个字节的低四位编码表示十进制数的一位,例如数82的存放格式为:_ _ _1 0 0 0 _ _ _ _0 0 1 0 其中_表示无关值。

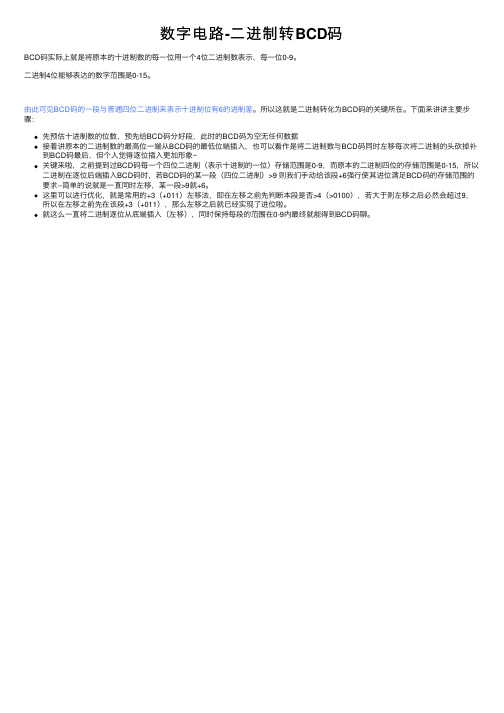

数字电路-二进制转BCD码

数字电路-⼆进制转BCD码

BCD码实际上就是将原本的⼗进制数的每⼀位⽤⼀个4位⼆进制数表⽰,每⼀位0-9。

⼆进制4位能够表达的数字范围是0-15。

由此可见BCD码的⼀段与普通四位⼆进制来表⽰⼗进制位有6的进制差。

所以这就是⼆进制转化为BCD码的关键所在。

下⾯来讲讲主要步骤:

先预估⼗进制数的位数,预先给BCD码分好段,此时的BCD码为空⽆任何数据

接着讲原本的⼆进制数的最⾼位⼀端从BCD码的最低位端插⼊,也可以看作是将⼆进制数与BCD码同时左移每次将⼆进制的头砍掉补到BCD码最后,但个⼈觉得逐位插⼊更加形象~

关键来啦,之前提到过BCD码每⼀个四位⼆进制(表⽰⼗进制的⼀位)存储范围是0-9,⽽原本的⼆进制四位的存储范围是0-15,所以⼆进制在逐位后端插⼊BCD码时,若BCD码的某⼀段(四位⼆进制)>9 则我们⼿动给该段+6强⾏使其进位满⾜BCD码的存储范围的要求--简单的说就是⼀直同时左移,某⼀段>9就+6。

这⾥可以进⾏优化,就是常⽤的+3(+011)左移法,即在左移之前先判断本段是否>4(>0100),若⼤于则左移之后必然会超过9,所以在左移之前先在该段+3(+011),那么左移之后就已经实现了进位啦。

就这么⼀直将⼆进制逐位从底端插⼊(左移),同时保持每段的范围在0-9内最终就能得到BCD码聊。

八位二进制——BCD码转换器

实验报告:8位二进制-BCD码转换器姓名:学号:指导教师:一.实验目的了解二进制-BCD码转换器实现原理,掌握移位加3算法,熟悉Verilog编程中模块复用模式。

二.实验任务1.掌握用移位加三算法实现二进制-BCD码转换器的设计;2.设计Verilog实验程序;3.生成比特流文件,将文件下载到开发板中进行硬件验证。

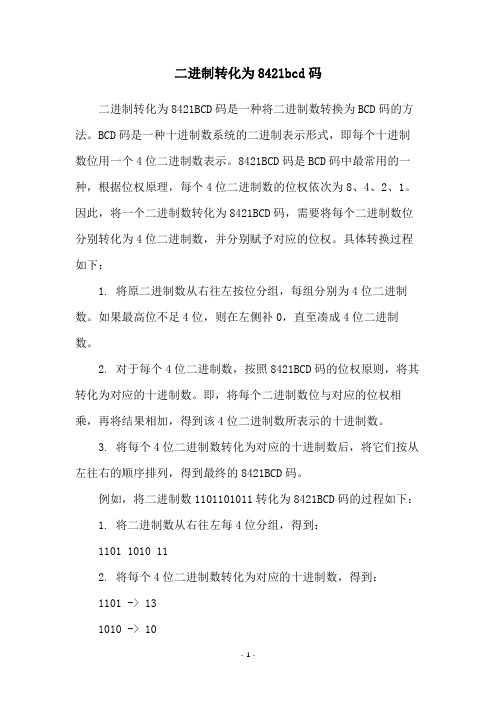

三.实验设备1.计算机(安装Xilinx ISE 10.1软件平台);2.NEXYS2 FPGA开发板一套(带USB-MIniUSB下载线)四.实验原理设计任意数目输入的二进制-BCD码转换器的方法就是采用移位加三算法(Shift and Add 3 Algorithm)。

此方法包含以下4个步骤:1)把二进制左移1位;2)如果共移了8位,那么BCD数就在百位、十位和个位列;3)如果在BCD列中,任何一个二进制数是5或者比5更大,那么就在BCD列的数值加上3;4)回到步骤1)。

其工作过程如图1所示:图1. 一个8位的二进制数转换成BCD码的步骤五.实验内容在Xilinx ISE 10.1上完成8位二进制-BCD码转换器设计,输入设计文件,仿真后,生成二进制码流文件下载到FPGA开发板上进行验证;1)依照实验1的方式,在Xilinx ISE 10.1中新建一个工程example02;2)在工程管理区任意位置单击鼠标右键,在弹出的快捷菜单中选择“New Source”命令,弹出新建源代码对话框,这里我们选择“Verilog Module”类型,输入Verilog文件名“binbcd8.v”,完整代码如下:module binbcd8(input [7:0] b,output reg [9:0] p);reg [17:0] z;integer i;always @(*)beginfor (i=0;i<=17;i=i+1)z[i]=0;z[10:3]=b;repeat(5) //重复5次beginif (z[11:8]>4)z[11:8]=z[11:8]+3;if (z[15:12]>4)z[15:12]=z[15:12]+3;z[17:1]=z[16:0];endp=z[17:8];endendmodule3)设计相应的7段显示管程序,将相应的十进制数在开发板的显示管上显示出来。

bcd码的转换

bcd码的转换bcd码也叫8421码就是将⼗进制的数以8421的形式展开成⼆进制,⼤家知道⼗进制是0~9⼗个数组成,着⼗个数每个数都有⾃⼰的8421码:0=00001=00012=00103=00114=01005=01016=01107=01118=10009=1001举个例⼦:321的8421码就是3 2 10011 0010 0001⼆进制编码的⼗进制数,简称BCD码(Binarycoded Decimal). 这种⽅法是⽤4位⼆进制码的组合代表⼗进制数的0,1,2,3,4,5,6 ,7,8,9 ⼗个数符。

4位⼆进制数码有16种组合,原则上可任选其中的10种作为代码,分别代表⼗进制中的0,1,2,3,4,5,6,7,8,9 这⼗个数符。

最常⽤的BCD码称为8421BCD 码,8.4.2.1 分别是4位⼆进数的位取值。

右图为⼗进制数和8421BCD编码的对应关系表:1、BCD码与⼗进制数的转换BCD码与⼗进制数的转换.关系直观,相互转换也很简单,将⼗进制数75.4转换为BCD码如:75.4=(0111 (0101.0100)BCD 若将BCD码1000 0101.0101转换为⼗进制数如: (1000 0101.0101)BCD=85.5注意:同⼀个8位⼆进制代码表⽰的数,当认为它表⽰的是⼆进制数和认为它表⽰的是⼆进制编码的⼗进制数时,数值是不相同的。

例如:00011000,当把它视为⼆进制数时,其值为24;但作为2位BCD码时,其值为18。

⼜例如00011100,如将其视为⼆进制数,其值为28,但不能当成BCD码,因为在8421BCD码中,它是个⾮法编码.2、BCD码的格式计算机中的BCD码,经常使⽤的有两种格式,即分离BCD码,组合BCD 码。

所谓分离BCD码,即⽤⼀个字节的低四位编码表⽰⼗进制数的⼀位,例如数82的存放格式为:_ _ _1 0 0 0 _ _ _ _0 0 1 0 其中_表⽰⽆关值。

二进制转BCD码

⼆进制转BCD码应⽤:⽤fpga实现对数码管显⽰,以前通常的⽅法是进⾏整除和取余进⾏运算,但是fpga并不擅长乘法除法运算,所以可以⽤BCD码来转换。

BCD码:通俗的可以理解为⽤四位⼆进制数表⽰⼀位⼗进制数字。

例如,256就可以⽤bcd码表⽰为:0010_1001_0110因此在数码管显⽰中,也就是把256各位分出来,就可以⽤bcd码来表⽰,下⾯说⼀种⼆进制转换bcd码的⽅法。

加3移位法:bcd码中只有0~9⼗进制数,但是在四位⼆进制中是16进制进1,因此在移位过程中要对⼆进制进⾏判断,当在移位之后的状态Qn+1⼤于9,要对Qn加6才可以。

例如1000移位⼤于9加6为0001_0110,对应bcd码中的16。

我们也可以在移位之前进⾏判断,如果移位之前的Qn数据⼤于4,说明Qn+1会溢出,所以可以+3再进⾏移位,例如1000⼤于4,加3为1011然后再进⾏移位0001_0110,16和刚才结果是⼀样的。

简单的说,判断的⽬的是防⽌下⼀次移位,发⽣数据溢出的情况思路:代码可以总结为三个部分:移位,加⼆进制数,判断(最后⼀次不需要判断)例如15 --- 1111(1)移位 0000_0000 加 0000_0001 判断 0000_0001(2)移位 0000_0010 加 0000_0011 判断 0000_0011(3)移位 0000_0110 加 0000_0111 判断 0000_1010(4)移位 0001_0100 加 0001_0101/*********************************功能:实现对6位⼗进制数以内的bcd码转换time: 2017/4/29vision:1.0*********************************/`define data_in_num 19`define data_bcd_num 23module pro_bcd(clk,rst_n,data_in,data_bcd);input clk;input rst_n;input [`data_in_num :0] data_in;output [`data_bcd_num:0] data_bcd;reg [`data_bcd_num:0] data_bcd_r;reg [1:0] state;reg [5:0] shift_cnt;always @(posedge clk or negedge rst_n)if(!rst_n)begindata_bcd_r <= 0;state <= 0;shift_cnt <= 0;endelsecase(state)2'd0:beginshift_cnt <= 0;data_bcd_r <= 0;state <= state + 1;end2'd1:begin //移位if(shift_cnt < `data_in_num + 1)begindata_bcd_r <= data_bcd_r<<1;shift_cnt <= shift_cnt + 1;state <= state + 1;endelsestate <= 0;end2'd2:begin //相加data_bcd_r <= data_bcd_r + data_in[`data_in_num + 1 - shift_cnt];state <= state + 1;end2'd3:begin //判断if(data_bcd_r[3:0] > 4 ) //1data_bcd_r <= data_bcd_r + 3;if(data_bcd_r[7:4]>4) //2data_bcd_r[7:4] <= data_bcd_r[7:4] + 3;if(data_bcd_r[11:8]>4) //3data_bcd_r[11:8] <= data_bcd_r[11:8] + 3;if(data_bcd_r[15:12]>4) //4data_bcd_r[15:12] <= data_bcd_r[15:12] + 3;if(data_bcd_r[19:16]>4) //5data_bcd_r[19:16] <= data_bcd_r[19:16] + 3;if(data_bcd_r[`data_bcd_num:20]>4) //6data_bcd_r[`data_bcd_num:20] <= data_bcd_r[`data_bcd_num:20] + 3;state <= 1;enddefault:state <= 0;endcaseassign data_bcd = (state == 3)&&(shift_cnt == `data_in_num + 1) ? data_bcd_r : data_bcd; endmodule。

bcd码计数器基本原理

bcd码计数器基本原理BCD(Binary Coded Decimal)码计数器是一种常用的数字电路器件,主要用于数字系统的计数和计数控制。

本文将详细介绍BCD码计数器的基本原理和设计方法。

一、基本原理BCD码计数器通常由二进制计数器、解码器和编码器组成。

二进制计数器用于实现基本的加减计数功能,解码器将二进制计数器的输出解码为BCD码,编码器再将BCD码编码为二进制数。

BCD码是一种将十进制数用四位二进制数表示的方法,其中每一位上的数字都用一位二进制数表示,这种编码方式使得数字的表示更加直观和方便。

在BCD码计数器中,解码器的作用是将二进制计数器的输出解码为四位二进制数,用于实现四位十进制数的计数。

解码器的设计需要根据具体的应用需求进行选择,常用的解码器有单输入触发器和双输入触发器等。

在实现BCD码计数器时,还需要注意计数器的进位问题。

由于BCD码表示方式采用的是二进制数,当高位数字与低位数字相加时,可能会出现进位的情况。

因此,在设计计数器时需要考虑到进位问题,以确保计数器的正确性和稳定性。

二、设计方法BCD码计数器的设计方法主要包括计数器的位数、进制选择、解码器和编码器的选择等。

根据具体的应用需求,可以选择不同的计数器位数和进制,例如1位、4位、8位等十进制计数器,也可以选择二进制或BCD码等其他进制计数器。

解码器和编码器的选择需要根据具体的解码和编码方式进行选择。

常用的解码器和编码器有移位寄存器、触发器和编码器等。

在设计过程中,需要注意解码器和编码器的逻辑关系和时序问题,以确保解码和编码的正确性和稳定性。

三、应用场景BCD码计数器广泛应用于各种数字系统中,例如时钟、计时器、频率计等。

通过BCD码计数器可以实现四位十进制数的计数和计时功能,为数字系统的控制和测量提供准确的数据支持。

此外,BCD码计数器还可以用于数字通信、自动化控制等领域。

四、总结本文介绍了BCD码计数器的基本原理和设计方法,包括二进制计数器、解码器和编码器的选择等。

java bcd码的算法

java bcd码的算法Java BCD码的算法BCD码是二进制编码的十进制表示形式,即Binary-Coded Decimal的简称。

在计算机中,常用BCD码来表示数字,可以在计算和显示数字时提供高精度和可读性。

本文将介绍Java中BCD码的算法。

1. BCD码的原理BCD码使用4位二进制数来表示一个十进制数的每一位。

例如,数字5的BCD码是0101,数字9的BCD码是1001。

BCD码的优点是可以直接与十进制数进行转换和计算,而无需进行复杂的位运算。

2. Java中BCD码的转换在Java中,可以使用整数类型(如int)来表示BCD码。

将一个十进制数转换为BCD码的算法如下:- 将十进制数的每一位拆分出来,得到个位、十位、百位等数字。

- 将每一位数字转换为对应的BCD码,例如将数字5转换为0101。

- 将每一位的BCD码按位拼接起来,得到最终的BCD码。

例如,将数字259转换为BCD码的过程如下:- 个位数字为9,对应的BCD码为1001。

- 十位数字为5,对应的BCD码为0101。

- 百位数字为2,对应的BCD码为0010。

- 将个位、十位和百位的BCD码按位拼接起来,得到最终的BCD 码为0010 0101 1001。

3. Java中BCD码的计算在Java中,可以使用BCD码进行数字的加减乘除运算。

例如,将两个BCD码相加的算法如下:- 从最低位开始,将两个BCD码对应的每一位相加,得到一个新的BCD码的每一位和进位。

- 将新的BCD码的每一位和进位拼接起来,得到最终的和。

例如,将BCD码0010 0101 1001和BCD码0011 0110 0010相加的过程如下:- 个位相加得到和为11,进位为1。

- 十位相加得到和为11,进位为1。

- 百位相加得到和为10,进位为1。

- 将个位、十位和百位的和和进位拼接起来,得到最终的和为1101 1101 0111。

4. Java中BCD码的显示在Java中,可以将BCD码转换为十进制数进行显示。

二进制转化为8421bcd码

二进制转化为8421bcd码

二进制转化为8421BCD码是一种将二进制数转换为BCD码的方法。

BCD码是一种十进制数系统的二进制表示形式,即每个十进制数位用一个4位二进制数表示。

8421BCD码是BCD码中最常用的一种,根据位权原理,每个4位二进制数的位权依次为8、4、2、1。

因此,将一个二进制数转化为8421BCD码,需要将每个二进制数位分别转化为4位二进制数,并分别赋予对应的位权。

具体转换过程如下:

1. 将原二进制数从右往左按位分组,每组分别为4位二进制数。

如果最高位不足4位,则在左侧补0,直至凑成4位二进制数。

2. 对于每个4位二进制数,按照8421BCD码的位权原则,将其转化为对应的十进制数。

即,将每个二进制数位与对应的位权相乘,再将结果相加,得到该4位二进制数所表示的十进制数。

3. 将每个4位二进制数转化为对应的十进制数后,将它们按从左往右的顺序排列,得到最终的8421BCD码。

例如,将二进制数1101101011转化为8421BCD码的过程如下: 1. 将二进制数从右往左每4位分组,得到:

1101 1010 11

2. 将每个4位二进制数转化为对应的十进制数,得到:

1101 -> 13

1010 -> 10

0011 -> 3

3. 将每个十进制数按从左往右的顺序排列,得到最终的8421BCD码:

13 10 3

因此,1101101011的8421BCD码为13103。

bcd码转化为二进制数 c语言

bcd码转化为二进制数 c语言

【原创实用版】

目录

1.BCD 码的概念和表示方法

2.C 语言中 BCD 码转换为二进制数的方法

3.实例演示

正文

一、BCD 码的概念和表示方法

BCD 码,即二 - 十进制编码,是一种将十进制数转换为二进制数的编码方式。

在数字电子设备中,为了减少所需存储空间以及简化电路设计,常常采用 BCD 码来表示数字。

BCD 码中,每一位数字用 4 位二进制数来表示,因此,它的每一位二进制数都有 2^4=16 种可能的取值。

二、C 语言中 BCD 码转换为二进制数的方法

在 C 语言中,我们可以通过以下步骤将 BCD 码转换为二进制数:

1.定义一个数组,用于存储需要转换的 BCD 码的每一位数字。

2.遍历数组,将每一位数字转换为 4 位二进制数,并存储到一个新的数组中。

3.将新数组中的 4 位二进制数合并为一个 8 位二进制数,并存储到一个结果变量中。

4.遍历完数组后,结果变量中将包含转换后的二进制数。

第1页共1页。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

得分教师签名批改日期课程编号1801770001

深圳大学实验报告课程名称:微机原理及应用

实验名称:二进制数到BCD码的转换

学院:物理科学与技术学院

指导教师:

报告人:组号:

学号实验地点K302

实验时间:2014 年10 月22 日

提交时间:2014.11.12

一、实验要求:

将AX中的一个二进制数(对应的十进制数范围是0-65535),转换成压缩性BCD码表示的十进制,并从屏幕输出转换结果。

要求用减法实现,并比较与除法方法进行运行速度比较。

二、实验目的:

(1)进一步熟练掌握8086汇编语言编译调试工具和环境的操作;

(2)掌握完整8086汇编的程序设计编写方法;

(3)掌握简单的数值码制转换方法;

(4)掌握键盘输出的DOS功能调用方法。

三、实验说明:

计算机中的数值有各种表达方式,这是计算机的基础。

掌握各种数制、码制之间的转换是一种基本功;利用DOS功能调用实现在屏幕上显示字符或数字的方法是本课程的基本要求之一。

四、除法方法:

1、算法说明:三位数先除以100,得到的商就是百分位的结果;将之前一次的余数除以10,得到的商就是十分位的结果;剩下来的余数就是个位的结果。

2、程序流程图:

图1 除法程序流程图

3、程序:

DATA SEGMENT ; 数据段

RESULT_1 DB 1

RESULT_2 DB 1

RESULT_3 DB 1

DATA ENDS

STACK SEGMENT STACK ; 堆栈段

STA DB 64 DUP(0)

STACK_TOP DB 0

STACK ENDS

CODE SEGMENT ; 代码段

ASSUME CS:CODE , DS:DATA , ES:DATA , SS:STACK

START:

; 程序开头必须要有的五条指令

MOV AX, DATA

MOV DS, AX ; 设置数据段

MOV AX, STACK

MOV SS, AX ; 设置堆栈段

LEA SP, STACK_TOP ; 设置栈顶指针

;---------------------------------------

; 程序的中间部分

MOV AX, 467

MOV CL, 100

DIV CL

MOV RESULT_1, AL ; 除以 100, 得百位数

MOV AL, AH

MOV AH, 0

MOV CL, 10

DIV CL

MOV RESULT_2, AL ; 余数除以 10, 得十位数

MOV RESULT_3, AH ; 余数为个位数

;------------------------------------------ ; 程序结束必须要有的两条指令

MOV AX, 4C00H ;

INT 21H ;

;------------------------------------------ CODE ENDS

END START ; 最后一行要按回车键

五、减法方法

1、算法说明:三位数先循环减100,直到不够减了,做减法的次数就是百分位的结果;将不够减之前一次的余数恢复,再循环减去10,直到不够减了,做减法的次数就是十分位的结果;最后恢复的正余数就是个位的结果。

2、程序流程图

开始

把二进制数送到AX

计数器CL,标志位清零

AX减去100,差放到AX

N

是否借位CL加1给CL

Y

AL加100,恢复不够减时余数

从CL存储百位数

计数器CL,标志位清零

AX减去10,差放到AX

N

是否借位CL加1给CL

Y

AL加10,恢复不够减时余数

从CL存储十位数

从AL存储个位数

结束

3、程序:

DATA SEGMENT ; 数据段

RESULT_1 DB 1

RESULT_2 DB 1

RESULT_3 DB 1

DATA ENDS

STACK SEGMENT STACK ; 堆栈段

STA DB 64 DUP(0)

STACK_TOP DB 0

STACK ENDS

CODE SEGMENT ; 代码段

ASSUME CS:CODE , DS:DATA , ES:DATA , SS:STACK START:

; 程序开头必须要有的五条指令

MOV AX, DATA

MOV DS, AX ; 设置数据段

MOV AX, STACK

MOV SS, AX ; 设置堆栈段

LEA SP, STACK_TOP ; 设置栈顶指针

;---------------------------------------

; 程序的中间部分

MOV AX,467

MOV CL, 0; 计数器清零

CLC ;

NEXT1: SUB AX, 100; 减100

JC OVER1; 有借位说明不够减

INC CL ; 否则够减,计数器加1

JMP NEXT1; 无条件跳转

OVER1: ADD AL,100; 最后恢复不够减时AL的余数

MOV RESULT_1,CL

MOV CL, 0; 计数器清零

CLC ;

NEXT2: SUB AL, 10; 减10

JC OVER2; 有借位说明不够减

INC CL ; 否则够减,计数器加1

JMP NEXT2; 无条件跳转

OVER2: ADD AL,10; 最后恢复不够减时AL的余数

MOV RESULT_2,CL

MOV RESULT_3,AL

;------------------------------------------ ; 程序结束必须要有的两条指令

MOV AX, 4C00H ;

INT 21H ;

;------------------------------------------ CODE ENDS

END START ; 最后一行要按回车键

六.实验及报告要求:

1、简要说明算法,并画出正确的程序流程图;

算法说明:三位数先循环减100,直到不够减了,做减法的次数就是百分位的结果;将

不够减之前一次的余数恢复,再循环减去10,直到不够减了,做减法的次数就是十分位的

结果;最后恢复的正余数就是个位的结果。

程序流程图如图2

2、给出完整正确的源程序代码,要求给每一句伪指令或指令加上注释;

源程序代码、伪指令或指令注释如4.3和5.3所示。

3、分别在DOS和Windows下编译、连接源程序生成可执行文件并调试,比较两个环境下

生成的机器码的长度、寄存器内容、计算结果的异同。

3.1、除法:

3.1.1、DOS环境下:

机器码:

寄存器:

结果:

3.1.2、WINDOWS环境下:

机器码:

寄存器:结果:

3.2、减法:

3.2.1、DOS环境下

机器码:

寄存器:

结果:

3.2.2、WINDOS环境下

机器码:

寄存器:结果:

从以上结果可以看出:分别在DOS和Windows下编译、连接源程序生成可执行文件并调试,生成的机器码的长度、寄存器内容、计算结果是相同的。

4、如何观察转换过程中标志寄存器中各标志位的结果?如何观察转换结果的变化?试改变

被转换数值,对结果与编制为的变化加以说明和解释。

可以通过单步执行(single step),观察标志位的变化

5、写出完整的实验报告,特别是“实验结果”与“实验总结体会”部分,是评分的主要依据。

6、实验总结中要求结合实验中的经验、教训或体会对汇编语言格式、调试方法和微机原理学习方法作出总结。

七、总结与体会:

在这次实验中,对使用除法和减法两种方式实现二进制到BCD码的转换的比较,可以看出分别在DOS环境和WINDOWS环境下两种方法的机器码长度、寄存器内容和计算结果是相同的;通过本次实验,可以看出:用寄存器AX除以一个数之后,商放在AL,余数放在AH中,用寄存器AX减去一个数之后,差值放在AX中。

通过对比源代码和机器码及多次尝试,使用WIN7操作系统时,不管是DOS下还是WINDOWS下的emu8086,数中不含a、b、c、d、e、f,可以不用加数制符号,默认为十进制数。

当数中含有a、b、c、d、e、f时,必须在数后面加上十六进制的符号h/H,为十六进制数,否则编译不能通过,即有错误。

八、思考题:

如何让你的程序自适应地处理高位为‘0’时不输出或输出空格呢?

分配一个标志,在该标志不为零时,输出值是零就不输出或输出空格,标志为零时无论何值都要输出。

如果是从高位开始输出,那么只要先置标志,在输出一个非零数字或者当做到个位数的时候,把这个标志清零。