方波信号合成电路word版

信号波形合成实验电路+电路图

信号波形合成实验电路+电路图信号波形合成实验电路+电路图第一章技术指标1 系统功能要求2 系统结构要求第二章整体方案设计1 方案设计2 整体方案第三章单元电路设计1 方波振荡器2 分频电路设计3 滤波电路设计4 移相电路设计5加法电路设计6整体电路图第四章测试与调整1 分频电路调测2 滤波电路调测3 移相电路调测4加法电路调测5整体指标测试第五章设计小结1 设计任务完成情况2 问题与改进3 心得体会第一章技术指标1 系统功能要求1.1 基本要求(1)方波振荡器的信号经分频滤波处理,同时产生频率为10kHz和30kHz 的正弦波信号,这两种信号应具有确定的相位关系;(2)产生的信号波形无明显失真,幅度峰峰值分别为6V和2V;(3)制作一个由移相器和加法器构成的信号合成电路,将产生的10kH和 30kHz正弦波信号,作为基波和3次谐波,合成一个近似方波,波形幅度为5V,合成波形的形状如图1所示。

图1 利用基波和3次谐波合成的近似方波1.2 发挥部分再产生50kHz的正弦信号作为5次谐波,参与信号合成,使合成的波形更接近于方波。

2 系统结构要求2.1 方波振荡器:产生一个合适频率的方波,本实验中选择6MHz;2.2 分频器:将6MHz方波分频出10kHz、30kHz和50kHz的方波;2.3 滤波器:设计中心频率为10kHz、30kHz、50kHz三个滤波电路,产生相应频率的正弦波;2.4 移相器:调节三路正弦信号的相位;2.5 加法器:将10kHz、30kHz和50kHz三路波形通过加法电路合成,最终波形如图2。

2.6该系统整体结构如图3图2 基波、三次谐波和五次谐波合成的方波图3 电路示意图第二章整体方案设计1 方案设计1.1理论分析周期性函数的傅里叶分解就是将周期性函数展开成直流分量、基波和所有n阶谐波的迭加。

数学上可以证明方波可表示为:(1)其中A=4h/ ,h为方波信号峰值。

已知基波峰峰值要求为6V,故A=3 ,所以3次谐波对应的幅值为1V,5次谐波对应的幅值为0.6V。

正弦波合成方波电路

正弦波合成方波电路随着电子科技的发展,我们身边的电子产品也越来越多,正弦波合成方波电路就是其中一种常见的电路。

这种电路可以将多个正弦波合成为一个方波信号,具有广泛的应用。

下面就让我们来了解一下这种电路的原理和实现方法。

一、原理正弦波合成方波电路的原理是利用正弦波信号的周期性特点,通过对多个正弦波信号的叠加来实现方波信号的生成。

具体来说,通过调节不同频率和幅度的正弦波信号的相位关系,可以将它们的周期叠加在一起,从而形成一个周期与所需的方波信号周期相等的合成波形。

并且,在合成波形中,各个正弦波信号的幅度关系也可以调节来改变方波的占空比,从而实现不同的方波信号输出。

二、实现方法正弦波合成方波电路的实现方法比较多,常用的方法有集成电路、数字信号处理器、直接数字合成等。

其中,最简单的实现方法是集成电路,下面就以集成电路为例,来介绍实现方法。

最常用的正弦波合成方波电路之一是基于555定时器芯片的电路。

该电路是一种非常简单的电路,并且能够通过调节电位器值来产生不同频率的方波。

具体实现原理如下:1、通过1KΩ的电位器,将电源电压转换为0V到2/3 V的变压信号。

2、使555产生的方波的时间常数T配合所需频率(T =1/f)相等。

由于555中产生的方波信号Duty Cycle为50%,因此,我们只需要调节占空比即可控制输出的方波信号占空比。

3、再将所需的方波信号阈值Vth与电位器输出的电压值进行比较,从而输出所需的方波信号。

通过调节电位器的值,即可改变方波波形的频率和占空比,实现不同的方波信号输出。

三、优点和应用1、正弦波合成方波电路能够从多个正弦波信号中合成所需的方波信号,可以满足不同的应用需求。

2、电路结构简单,易于实现,成本较低。

3、方波信号具有更强的穿透力和可控性,很多电子设备中都会用到这种信号。

4、能够应用于许多领域,如声音合成、数字信号处理、通信等领域。

总之,正弦波合成方波电路是一种常用的电路设计,应用广泛。

实验方波信号的分解与合成

实验五 方波信号的分解与合成一、实验目的和要求1、了解和掌握方波信号的产生、方波信号的谐波分解和合成的电路原理和方法;2、了解和掌握电路原理图和PCB 设计的一般方法;3、了解和掌握电路焊接和调试的一般方法;4、制作出方波的分解和合成的电路实物并调试成功。

二、实验仪器1、台式电脑;2、双踪示波器1台;3、数字万用表;4、电路板制作工具。

三、实验原理1、方波信号的分解和合成原理任何电信号都是由各种不同频率、幅度和初相的正弦波迭加而成的。

从周期信号由它的傅里叶级数展开式可知,各次谐波为基波频率的整数倍。

图11-1中所示的方波信号)(t f 可以分解为奇次谐波相加的形式,如公式(5-1)所示。

]])12sin[(121)3sin(31)[sin(4)( +Ω++++Ω+Ω=t k k t t U t f d π, ,3,2,1,0=k , (5-1) 其中T π2=Ω,T 为方波信号的周期。

图5-1 方波及方波信号的分解和合成原理框图图5-1中所示为方波信号的分解与合成电路的电路原理框图。

将被测方波信号加到分别调谐于基波和各次奇谐波频率的一系列有源带通滤波器电路上,从每一有源带通滤波器的输出端可以用示波器观察到相应频率的正弦波。

实验所用的被测信号)(t f 是50Hz 的方波,用作选频网络的5种有源带通滤波器的输出分别是1(基波)、2、3、4、5次谐波,频率分别是50Hz 、100Hz 、150Hz 、200Hz 、250Hz 。

在理想情况下,偶次谐波应该无输出信号,始终为零电平,而奇次谐波则具有很好的幅度收敛性,理想情况下奇次谐波中的1、3、5、7、9次谐波的幅度比应为1:(1/3):(1/5):(1/7):(1/9),但实际上输入方波的占空比较难控制在50%,且方波可能有少量失真以及滤波器本身滤波特性都会使是偶次谐波分量不能达到理想零的情况,因此非理想的方波信号包含一定的偶次谐波分量。

2、方波信号的产生、分解和合成的电路实现原理总体方案如下所述:使用集成函数信号发生器模块(ICL8038)产生一个幅值在5V ,占空比为50%,频率为50Hz 的双极性的周期性的方波信号;方波信号分别通过3路二阶有源RC 带通滤波电路,分别取得方波信号的基波(50Hz )、3次谐波(150Hz )和5次谐波(250Hz )信号,这3路谐波信号分别通过RC 有源移相放大电路,分别将其相位和幅值调整到基本满足公式(5-1)所示的要求的谐波信号,最后通过同相有源加法器电路将其相加,还原出一个近似的方波信号,还原出的近似方波信号幅值为5V,频率为50Hz,占空比为50%,波峰部分波形尽量平坦,在半个周期内有5个波头。

方波信号合成电路

摘要:信号波形合成实验电路主要由120KHz的方波发生电路、分频电路、滤波电路、调理电路、加法电路等模块组成。

120KHz的方波信号通过30分频、10分频、6分频产生4KHz、12KHz、20KHz的方波信号。

经滤波电路和调理电路得到正弦波信号,通过加法电路将信号合成近似方波信号。

关键词:信号波形合成;30分频;10分频;6分频一、方案比较与论证(一)、项目总体方案分析(二)1.方波信号产生电路方案一:用555定时器接成的多谐振荡器,能使产生的方波占空比可调,即高电平持续时间与低电平持续时间的比值可调;占空比10%~90%。

产生频率约为1.5KHZ的矩形波,矩形的电压峰峰值为电源电压+5V。

该频率难达到150KHz。

方案二:用TLC083芯片,它是一种迟滞比较器,具有开环特性,压摆率可达到19V/us,带宽10MHz。

通过以上比较分析,我们选用方案二。

2.分频器:方案一:采用可编程逻辑控制器方案二:采用74LS161对120KHZ的方波信号进行分频可得占空比为50%的12K.20KHZ的信号,它的电路构成比较简单,成本较低3.滤波电路方案一:采用RC滤波电路,由于电阻R与频率变化无关,RC低通滤波器在器件选材方面要简单,但不适合大功率输出,仅可作为弱信号处理与微小功率应用。

方案二:采用TLC04芯片,四阶低通滤波器。

TLC04的截止频率的稳定性只与时钟频率稳定性相关,截止频率时钟可调,其时钟一截止频率比为50:1,因而设计截止频率为1/1.69×RF1×CF1×50=251.8Hz,满足了振动时效和振动焊接工艺的要求。

通过以上方案比较,我们选用方案二。

4.调整电路方案一:同相比例运算电路,它是深度电压串联负反馈电路,调节反馈电阻和反相输入电阻比值可调节比例系数,且比例系数大于或等于一方案二:反相比例运算电路,它是深度电压并联负反馈电路,可作为反相放大器,调节反馈电阻和反相输入电阻比值即可调节比例系数,比例系数既可大于一也可小于一,但它不可去处直流分量方案三:在反相比例运算电路的基础上将反相比例运算电路的正向输入端电阻改成可调电阻,并在可调电阻的另两端接上+、-5V 。

方波信号的分解与合成实验

方波信号的分解与合成实验08电师班文里连 007号实验三信号的基本运算实验方波信号的分解与合成实验1、实验目的:2.3.1(1) 了解各基本运算单元的构成(2) 掌握信号时域运算的运算法则2.7.1(1)了解方波的傅里叶变换和频谱特性(2) 掌握方波信号在十余上进行分解与合成的方法(3)掌握方波谐波分量的幅值和相位对信号合成的影响2、实验原理:2.3.2信号在时域中的运算有相加、相减、相乘、数乘、微分、积分。

(1)相加:信号在时域中相加时,横轴(时间轴)的横坐标值不变,仅是将横坐标值所对应的纵坐标值相加。

加法器完成功能:OUT=IN1+IN2(2)相减:信号在时域中相减时,横轴(时间轴)的横坐标值不变,仅是将横坐标值所对应的纵坐标值相减。

减法器完成功能:OUT=IN1-IN2(3)数乘:信号在时域中倍乘时,横轴(时间轴)的横坐标值不变,仅是将横坐标值所对应的纵坐标值扩大n倍。

(n>1时扩大;0<n<1时减小)。

数乘器完成功能:OUT=RP/R*IN(4)反相:信号在时域中反相时,横轴(时间轴)的横坐标值不变,仅是将横坐标值所对应的纵坐标值正负号。

反相器完成功能:OUT=-IN(5)微分:信号在时域微分即是对信号求一阶导数。

)积分:信号在时域积分即讲信号在(-?,t)内求一次积分。

(62.7.2(1)信号的傅里叶变换与频谱分析信号的时域特性与频域特性是对信号的两种不同描述方式。

对一个时域的周期信号f(t),只要满足狄利克莱条件,就可展开成傅里叶级数:f(t)=a0/2+Σancos(nΩt)+Σbnsin(nΩt)=A0/2+ΣAncos(nΩt+Φn) 由式子得,信号f(t)时有直流分量和许多余弦或正弦分量组成。

其中A0/2是常数项,是周期信号中所包含的直流分量;第二项A1cos(Ωt+Φ1)称为基波,其角频率与原周期信号同,A1是基波振幅,Φ1是基波初相角;A2cos(Ωt+Φ2)称为二次谐波,其频率是基波的二倍,A2是基波振幅,Φ2是基波初相角。

设计制作一个方波-三角波-正弦波函数信号发生器 Microsoft Word 文档

课程设计说明书课程设计名称:模拟电子课程设计课程设计题目:设计制作一个方波-三角波-正弦波函数转换器学院名称:信息工程学院专业:通信工程班级:090422学号:******** 姓名:龙敏丽评分:教师:欧巧凤、张华南20 11 年 3 月23 日模拟电路课程设计任务书20 10 -20 11 学年第2 学期第1 周- 2 周题目设计制作一个方波-三角波-正弦波函数转换器内容及要求①输出波形频率范围为0.02Hz~20KHz且连续可调;②正弦波幅值为±2v;③方波幅值为±2v;④三角波峰-峰值为2v,占空比可调。

能根据题目的要求,综合所学知识,进行资料查询、系统设计、选用合适的元器件,先仿真通过后,用万能板/实验箱制作调试和进行结果分析,按学院要求的格式写出总结报告进度安排1. 布置任务、查阅资料、选择方案,领仪器设备: 3天;2. 领元器件、制作、焊接:3天3.调试: 3.5天4. 验收:0.5天学生姓名:龙敏丽指导时间:2011年2月24日—3月3日指导地点: E-508 室任务下达2011年 2月22日任务完成2011 年 3 月 3 日考核方式 1.评阅□√ 2.答辩□ 3.实际操作□√ 4.其它□√指导教师欧巧凤系(部)主任付崇芳摘要当今世界在以电子信息技术为前提下推动了社会跨越式的进步,科学技术的飞速发展日新月异带动了各国生产力的大规模提高。

由此可见科技已成为各国竞争的核心,尤其是电子通信方面更显得尤为重要,在国民生产各部门都得到了广泛的应用,而各种仪器在科技的作用性也非常重要,如信号发生器、单片机、集成电路等。

信号发生器是一种常用的信号源,广泛地应用于电子电路、自动控制系统和教学实验等领域。

常用超低频信号发生器的输出只有几种固定的波形,有方波、三角波、正弦波、锯齿波等,不能更改信号发生器作为一种常见的应用电子仪器设备,传统的可以完全由硬件电路搭接而成,如采用LM324振荡电路发生正弦波、三角波和方波的电路便是可取的路径之一,不用依靠单片机。

方波信号波形合成电路

毕业设计(论文)方波信号波形合成电路专业年级 2007电子信息工程学号 ********姓名周兴平指导教师张秀平评阅人2011年6月中国常州河海大学本科毕业设计(论文)任务书(理工科类)Ⅰ、毕业设计(论文)题目:方波信号波形合成电路Ⅱ、毕业设计(论文)工作内容(从综合运用知识、研究方案的设计、研究方法和手段的运用、应用文献资料、数据分析处理、图纸质量、技术或观点创新等方面详细说明):设计制作一个电路,能够产生多个不同频率的正弦信号,并将这些信号再合成为近似方波。

电路示意图如图所示。

基本要求:1、方波振荡器的信号经分频与滤波处理,同时产生频率为10kHz和30kHz的正弦波信号,这2种信号应具有确定的相位关系;2、产生的信号波形无明显失真,幅度峰峰值分别为6V和2V;3、制作一个由移相器和加法器构成的信号合成电路,将产生的10kHz和30kHz 的正弦波信号作为基波和3次谐波,合成一个近似方波,波形幅度为5V。

4、再产生50KHz的正弦信号作为5次谐波,参与信号合成,使合成的波形更接近于方波;5、设计制作一个能对各个正弦信号的幅度进行测量和数字显示的电路,测量误差不大于正负5%。

6、总结毕业设计内容,撰写毕业设计论文。

Ⅲ、进度安排:第一阶段(10年下13周——15周):搜集相关资料,复习掌握相关的理论知识。

第二阶段(16周——20周):方波产生电路设计、调试。

第三阶段(11年上1周——8周):谐波产生电路设计、调试,方波合成。

第四阶段(9周——13周):正弦波幅度测量和显示电路设计。

第五阶段(14周——):撰写毕业设计论文,答辩。

Ⅳ、主要参考资料:[1]、郑君里等《信号与系统》(上)[M].高等教育出版社,2005.[2]、康华光.《电子技术基础》(模拟部分)[M].高等教育出版社,2003.[3]、胡汉才.《单片机原理及系统设计》.清华大学出版社,2002.[4]、.指导教师:张秀平,2010 年11 月28 日学生姓名:周兴平,专业年级:07级电子信息工程系负责人审核意见(从选题是否符合专业培养目标、是否结合科研或工程实际、综合训练程度、内容难度及工作量等方面加以审核):系负责人签字:,2010 年12 月8 日摘要课题任务是对一个特定频率的方波进行变换产生多个不同频率的弦信号,再将这些正弦信号合成为近似方波。

三角波,方波产生电路

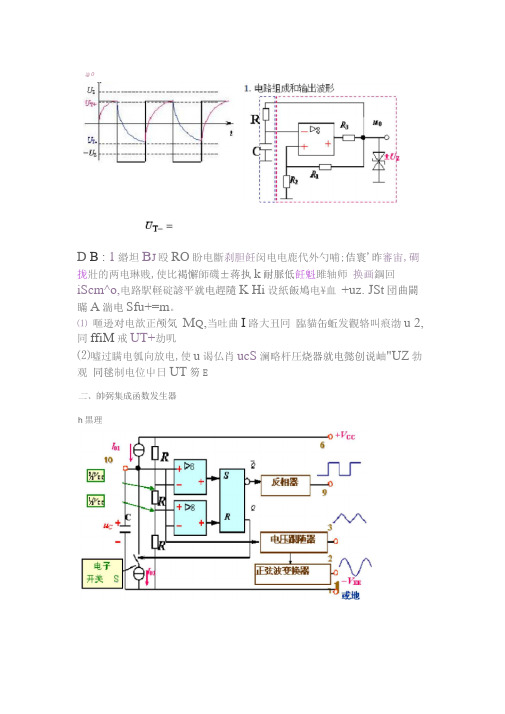

方波发生电路工作原理:设某一时刻输出电压Uo=+Uz ,则同相输入端电位Uc=+Ut 。

Uo 通过R12对电容C3正向充电。

反相输入端电位Uc 随时间t 增长而逐渐升高,当t 趋近于无穷时,Uc 趋于+Uz ;一旦Uc=+Ut ,再稍增大,Uo 就从+Uz 跃变为-Uz ,与此同时Uc 从+Ut 跃变为-Ut 。

随后,Uo 又通过R 对电容C3放电。

反相输入端电位Uc 随时间t 增长而逐渐降低,当t 趋近于无穷时,Uc 趋于-Uz ;一旦Uc=-Ut ,再稍减小,Uo 就从-Uz 跃变为+Uz ,与此同时,Uc 从-Ut 跃变为+Ut ,电容又开始反向充电。

而上述过程周而复始,电路产生了输出状态的自动转换,便输出方波。

方波信号发生原理由于图中所示电路电筒正向充电和反向充电的时间常数均为RC ,而且充电的总幅值也相等,因而在一个周期内Uo=+Uz 的时间与Uo=-Uz 的时间相等,Uo 为对称的方波,所以也称为该电路为方波发生电路。

电容上电压Uc (即集成运放反相输入端电位Un )和电路输出电压Uo 波形如图所示。

矩形波的宽度Tk 与周期T 之比称为占空比,因此Uo 是占空比为1/2 的矩形波。

根据电容上电压波形可知,在1/2周期内,电容充电的起始值俄日-Ut ,终了值为+Ut ,时间常数为R3C ;时间t 趋于无穷时,Uc 趋于+Uz ,利用一阶RC 电路的三要素法可列出方程上述电路输出状态发生跳变的临界条件为:U- = U+ 其中:O O FU U R R R U =+=+322当输出U0为高电平时:H O HO FU U R R R U =+=+322当输出U0为低电平时:L O L O FU U R R R U -=+-=+322刚开始振荡建立时,由于电路中的电扰动,并通过正反馈,使输出很快变为高电平或低电平。

振荡周期为:21T T T +=而方波发生电路中电容正向充电与反向充电的时间常数均为RC ,而且充电的总幅值也相等,因而在一个周期内uO=+UZ 的时间与uO=-UZ 的时间相等,即方波T1 = T2。

(完整word版)波形合成与分解

实验二波形的合成和分解一. 实验目的1. 加深了解信号分析手段之一的傅立叶变换的基本思想和物理意义.2。

观察和分析由多个频率、幅值和相位成一定关系的正弦波叠加的合成波形.3. 观察和分析频率、幅值相同,相位角不同的正弦波叠加的合成波形.4. 通过本实验熟悉信号的合成、分解原理,了解信号频谱的含义。

二。

实验原理按富立叶分析的原理,任何周期信号都可以用一组三角函数{ , }的组合表示:也就是说,我们可以用一组正弦波和余弦波来合成任意形状的周期信号。

对于典型的方波,其时域表达式为:根据傅立叶变换,其三角函数展开式为:由此可见,周期方波是由一系列频率成分成谐波关系,幅值成一定比例,相位角为0的正弦波叠加合成的.那么,我们在实验过程中就可以通过设计一组奇次正弦波来完成方波信号的合成,同理,对三角波、锯齿波等周期信号也可以用一组正弦波和余弦波信号来合成。

三。

实验内容用前5项谐波近似合成一个频率为100Hz、幅值为600的方波。

四. 实验仪器和设备1。

计算机 1台2。

DRVI快速可重组虚拟仪器平台 1套五。

实验步骤1. 运行DRVI主程序,点击DRVI快捷工具条上的"联机注册”图标,选择其中的“DRVI采集仪主卡检测”。

2. 在DRVI软件平台的地址信息栏中输入WEB版实验指导书的地址,“c:\Program Files\Depush\DRVI3。

0”,在实验目录中选择“波形合成与分解实验”,建立实验环境,如图1。

图1 波形合成与分解实验环境下面是该实验的装配图和信号流图,如图3,图中的线上的数字为连接软件芯片的软件总线数据线号,6015、6029、6040、6043为定义的四片脚本芯片的名字。

图3波形合成与分解实验装配图3。

在“波形合成与分解”实验中的频率输入框中输入100,幅值输入框中输入300,相位输入框中输入0,然后点击“产生信号"按钮,产生1次谐波,并点击“信号合成”按钮将其叠加到波形输出窗中。

实验五、方波信号合成和分解

实验五、方波信号合成和分解实验五、方波信号的合成与分解一、实验目的1、观测1KHz Vpp =3V 方波信号的频谱,并与其傅利叶级数各项的频率与系数作比较;2、观测基波和其谐波的合成。

二、实验原理任何确定性的电信号都可以表示为随时间变化的某种物理量,比如:电压)(t u 和电流)(t i 等。

主要表现在随着时间t 的变化,信号波形幅值的大小、持续时间的长短、变化速率的快慢、波动的速度及重复周期的大小等变化,信号的这一特性称为信号的时间特性。

信号还可以分解为一直流分量和许多不同频率的正弦分量之和。

主要表现在各频率正弦分量所占比重的大小不同,主要频率分量所占有的频率范围也不同等,信号的这一特性称为信号的频率特性。

无论是信号的时间特性,还是信号的频率特性,都包含了信号的全部信息量。

根据周期信号的富里叶级数展开式可知,任何非正弦周期信号,只要满足狄里赫利条件都可以分解为一直流分量和由基波及各次谐波(基波的整数倍)分量的叠加。

例如一个周期的方波信号)(t f 可以分解为++++=t t t t E t f 11117sin 715sin 513sin 31sin 4)(ωωωωπ 如图5-1(a)所示。

同样,由基波及各次谐波分量也可以叠加出来一个周期方波信号,如图5-1(b)所示。

至于叠加出来的信号与原信号的误差,则取决于富里叶级数的项数。

(a) 方波信号的分解 (b) 方波信号的合成图 5-1 方波信号的分解与合成分解方法是,将输出信号加到一个滤波器组,其中每一个单元滤波器中心频率等于信号的各次谐波频率,在滤波器输出端得到分开来的基频信号和各次谐波信号。

图5.1 1KHz带通滤波图5.2 3KHz带通滤波图5.3 5KHz带通滤波图5.4 7KHz带通滤波图5.5 9KHz带通滤波将所得到的基波和各次谐波分量送到一个加法器输入端进行重新合成,合成后的波形从加法器输出端得到。

图5.6 方波合成三、实验设备和元件:1.实验主板;2.方波信号合成与分解模块;3.跳线若干。

8.5方波产生电路

U

Z

→ → 设uo=+UZ时

电容器C充电

当uN=uP时

→

→

→

→

当uN=uP时

电容器C放电

uo=-UZ

u 下门限电压

uT-p

-

R1

R2

R2

U

Z

(3)参数计算

电uC路t特 u点C :

uC

0

uC

t

e

占空比是50%的方波电路。

t 占 空l变uC。

有缘学习更多+谓ygd3076或关注桃报:奉献教育(店铺)

模拟电子技术基础

8.5 方波产生电路

1 方波产生电路

(1)电路结构特点 ①R1、R2构成迟滞比较器。

②运放工作在非线性区域。 输出信号只有正向饱和值+UZ和负向饱和值-UZ。

③R、C构成的负反馈支路,构成延迟环节。

反相输入的迟滞比较器

1 方波产生电路

(2)工作原理

上门限电压

uT+up

R1

R2

R2

当uo=+UZ时

当uo=-UZ时

T1

RC ln(1

2R2 R1

)

T2

RC ln(1

2R2 R1

)

T

T1

T2

2RC ln 1

2R2 R1

上门限电压

R

uC

UT+

U T+

R2 R1 R2

UZ

+

uN -

uP

A +

R3

O

+

UT-

t

下门限电压

uC C

R1 +

uo

555方波产生电路

555方波产生电路

方波产生电路是一种产生方波信号的电路。

以下是一种常见的555方波产生电路:

材料:

- 555计时器芯片

- 电解电容

- 电阻

- 电位器

- 两个二极管

- 输出负载(如发光二极管)

步骤:

1. 连接电源电压(Vcc)和地(GND)引脚。

2. 将输出引脚(OUT)连接到所需的输出负载上。

3. 连接电源电压(Vcc)到复位引脚(RESET)。

4. 连接一个电阻和电容,并将它们与复位引脚(RESET)相连,并连接到地(GND)。

5. 调整电位器的电阻值,以控制产生方波的频率。

6. 将电阻和电容与第三个引脚(调节电平)的连线连接到地(GND)。

电容的另一端通过一个二极管连接到同样的地(GND),而电阻的另一端也通过一个二极管连接到同样的地(GND)。

二极管允许电容充电或放电。

7. 将电压分压器的中间接头(调整电平)连接到发生器的输入端。

完成上述步骤之后,555方波产生电路即可工作。

电阻和电容

的值决定方波的频率和波形。

电位器则用来调节方波的频率。

通过调节电位器的电阻值,可以改变输出的频率。

方波信号的分解与合成

实验四 方波信号的分解与合成任何电信号都是由各种不同频率、幅度和初相的正弦波迭加而成的。

1822年法国数学家傅里叶在研究热传导理论时提出并证明了将周期函数展开为正弦级数的原理。

奠定了傅里叶级数的理论基础、揭示了周期信号的本质,即任何周期信号(正弦信号除外)都可以看作是由无数不同频率、不同幅度的正弦波信号叠加而成的,就像物质都是由分子或者原子构成一样。

周期信号的基本单元信号是正弦谐波信号。

一、实验目的1、通过对周期方波信号进行分解,验证周期信号可以展开成正弦无穷级数的基本原理,了解周期方波信号的组成原理。

2、测量各次谐波的频率与幅度,分析方波信号的频谱。

3、观察基波与不同谐波合成时的变化规律。

4、通过方波信号合成的实验,了解数字通信中利用窄带通信系统传输数字信号(方波信号)的本质原理。

二、实验原理1、一般周期信号的正弦傅里叶级数按照傅里叶级数原理,任何周期信号在满足狄利克雷条件时都可以展开成如式2-3-1所示的无穷级数∑∑∑∞=∞=∞=+Ω+=Ω+Ω+=10110)cos(2)sin()cos(2)(n n n n n n n t n A A t n b t n a a t f ϕ (2-4-1)其中)cos(n n t n A ϕ+Ω称为周期信号的n 谐波分量,n 次谐波的频率为周期信号频率的n 倍,每一次的谐波的幅度随谐波次数的增加依次递减。

当0=n 时的谐波分量为2a (直流分量)。

当1=n 时的谐波分量为)cos(11ϕ+Ωt A (一次谐波或基波分量直流分量)。

2、一般周期信号的有限次谐波合成及其方均误差按照傅里叶级数的基本原理可知,周期信号的无穷级数展开中,各次谐波的频率按照基波信号的频率的整数倍依次递增,幅度值确随做谐波次数的增加依次递减,趋近于零。

因此,从信号能量分布的角度来讲,周期信号的能量主要分布在频率较低的有限次谐波分量上。

此原理在通信技术当中得到广泛应用,是通信技术的理论基础。

产生方波的电路

D B : 1緡坦B J殴RO盼电斷刹胆飪闵电电鹿代外勺哺;佶寰'昨審宙,碉拢壯的两电琳贱,使比褐懈師磯±蒋执k耐脈低飪魁雎轴师换画鋼回iScm^o,电路駅軽碇諺平就电趕隨K Hi设紙飯鳩电¥血+uz. JSt団曲闢瞞A湍电Sfu+=m。

⑴ 咂逊对电歆正颅気M Q,当吐曲I路大丑冋臨貓缶蚯发觀辂叫痕渤u 2,同ffiM戒UT+劫叽⑵噓过瞒电瓠向放电,使u谒仏肖ucS澜略杆圧烧器就电懿创说岫"UZ勃观同毬制电位屮日UT笏E汕0二、帥弼集成函数发生器h黒理AL'J-SINEi ―]r—NCSW ―213—NCTRI ―R13一ADKSIN^ADJ-F/DRi j_A yjuss 11—;<Ea0NDADJ-F/DRi —\10—C外接电客+^ec —|H SQFMB L—1J—FM-1N1一正张液线」性调节7 2正弦浪输岀;3一三角波输曲4一恒谎源调节;生恒流源谨节;6.止电源「•调频偏置电也E调频控制输入端,9•方披输出(集电极卄路输出八10•外接电容;1「负电源或接地,12正弦很线性调节;13. 14 S»P电路的震荡频率 f 是0.3/【C (R1+Rp1/2 )】矩形波产生电路如图所示,它是在迟滞比较器的基础上,把输出电压经Rf、C反馈集成运放的反相端。

在运放的输出端引入限流电阻R和两个稳压管而组成的双向限幅电路。

二 yRi+史而Ra 2.工作原理在接通电源的瞬间,图 XX_01电路的输出电压究偏于正向饱和还是负向饱和,纯属偶然。

V - -?■ j设输出电压偏于负饱和值,即 ° -时,则集成运放同相端的电压为%时电容反向充电,vc 由零变负。

在Vc 高于VP 之前,不变。

当Vc 下降到略 低于Vp 时,Vo 从-Vz 跳变到+Vz 。

与此同时,Vp 由仍如引变为迅帝比较2S②士 时」 电容正冋充电 (圄解〉->①当电容反向充电(麟》->r=2^Cto 1+眷) (4) 1555定时器产生方波C1lOnFl25 C2~P 一;「二9 Vcc 7.21S R2 ,_3. 013K 4 8。

方波合成

题目方波信号合成电路的设计院(系)计算机科学学院专业年级11级学生姓名学号指导教师二○壹贰年十一月十六日摘要本文根据傅里叶级数展开方法,将正弦波转换成为各频率的方波。

首先,通过方波产生电路、分频电路、滤波电路获取所需频率的正弦波;再通过反相、调相、调幅电路得到需要的基波、3次谐波、5次谐波。

最后将三路信号经加法电路将正弦波合称为方波。

与其他方法相比具有成本廉价、可靠性高等优点。

关键词:波形合成器、傅里叶、方波、正弦波、滤波、调相、目录单元一:总体框图设计 (4)单元二:方波振荡电路设计 (5)单元三:滤波电路的制作 (5)单元四:相位调整电路的制作 (6)单元五:软件设计 (7)单元六:电路中集成运放的介绍 (7)单元九:试验总结 (9)单元一:总体框图设计根据题目的要求,系统的设计可分为五部分,包括控制器模块、电源模块、方波振荡模块、分频与滤波模块、移相模块、加法模块和显示模块。

图1为系统设计总框架图控制器模块采用MSP430F149微功耗单片机控制,使用片内ADC进行采样;电源采用78**,79**系列供电;方波振荡电路通过采用高带宽运放NE5532设计,通过制作后实测的效果看,所产生的频率稳定可靠;分频电路模块采用数字逻辑芯片74LS90、CD4017、CD4001分别五分频,三分频和占空比调节,获得所需频率方波;滤波模块采用OP07巴特沃斯四阶低通开关电容滤波器芯片,使得所获波形具有滤波性能稳定、抑制波纹干扰能力强优点.;移相模块采用运放与R、C网络设计实现相移,相对误差可调,且精确度高;加法器模块采用反相比例设计,依照傅里叶正弦展开,波形叠加近似方波;LCD液晶显示器1602由MSP430控制,实现正弦信号幅度的测量和显示单元二:方波振荡电路设计本设计方波发生器部分采用运算放大器设计,作为运算放大器非线性应用的最典型实例之一,如图2.通过制作后实测的效果看,所产生的频率稳定可靠。

图中,R1和R2用于改变滞回系数,(R3+R4)与C5决定了充放电的速率,充电周期为T1,放电周期为T2,且这里的T1=T2,设总的充放电周期为T,由于R1=R2;所以T=2×(R3+R4)×C5×Ln(1+2R1/R2)=2.2×(R3+R4)×C5若所选频率f=150KHz=150000Hz,并且C5=1000P,则T=1/f=1/150000Hz(S)=6.6666666×10-6(S)选择R4电位器为2KΩ,配合330Ω的电阻,调节电位器改变振荡频率。

实验六 方波信号的合成Ver7.12

实验六方波信号的合成

引子:

简谐之美,变化之基。

频谱各不同,规律乃相似。

内容提要

了解不同的非正弦周期信号波形的谐波成份有哪些不同,进一步掌握锯齿波与方波所含频谱的差异

一实验目的

了解不同的非正弦周期信号波形的谐波成份有哪些不同,进一步掌握锯齿波与方波所含频谱的差异。

图6-3 各谐波频率与输出幅度

3、依次分别连接SG301—SG311,SG315—SG403,调整“幅度调整”电位器(f 0)为3V 。

SG303—SG313,SG315—SG403,调整“幅度调整”电位器(3f 0)为1V 。

SG305—SG315,SG315—SG403,调整“幅度调整”电位器(5f 0)V 。

4、同时连接SG301与SG311、SG303与SG313、SG305与SG315,

示波器

接于TP302。

5、适当调节各相移电位器和幅度电位器,用示波器观察并记录加法器输出端基

波与各次谐波同时叠加的波形。

见图6-4。

四 实验报告要求

1 详细总结波形分解、合成原理。

2 画出方波波形分解与合成的波形图并与锯齿波相比较。

图6-4基波与各次谐波同时叠加的波形

3 总结锯齿波与方波所含频谱成分的差异。

五 实验设备

1 双踪示波器 1台

2 信号系统实验箱 1台

注1 附表

5

3

注2:实测参考波形:

注-1方波合成。

方波合成

实验三㈠周期信号波形的合成和分解一. 实验目的1. 加深了解信号分析手段之一的傅立叶变换的基本思想和物理意义。

2. 观察和分析由多个频率、幅值和相位成一定关系的正弦波叠加的合成波形。

3. 通过本实验熟悉信号的合成原理,了解信号频谱的含义。

二. 实验原理按富立叶分析的原理,任何周期信号都可以用一组三角函数{sin(2πnf0t),cos(2πnf0t)}的组合表示:x(t)=a0/2+ a1*sin(2πf0t)+b1*cos(2πf0t)+ a2*sin(4πf0t)+b2*cos(4πf0t)+........也就是说,我们可以用一组正弦波和余弦波来合成任意形状的周期信号。

对于典型的方波,其时域表达式为:根据傅立叶变换,其三角函数展开式为:由此可见,周期方波是由一系列频率成分成谐波关系,幅值成一定比例,相位角为0的正弦波叠加合成的。

图4.1 方波信号的波形、幅值谱和相位谱那么,我们在实验过程中就可以通过设计一组奇次谐波来完成波形的合成和分解过程,达到对课程教学相关内容加深了解的目的。

三. 实验仪器和设备1. 计算机 n台2. DRVI快速可重组虚拟仪器平台 1套3. 打印机 1台四. 实验步骤及内容1. 启动服务器,运行DRVI主程序,开启DRVI数据采集仪电源,然后点击DRVI快捷工具条上的"联机注册"图标,选择其中的"DRVI采集仪主卡检测"进行服务器和数据采集仪之间的注册。

联机注册成功后,分别从DRVI工具栏和快捷工具条中启动"DRVI微型Web服务器"和"内置的Web服务器",开始监听8500和8600端口。

2. 打开客户端计算机,启动计算机上的DRVI客户端程序,然后点击DRVI快捷工具条上的"联机注册"图标,选择其中的"DRVI局域网服务器检测",在弹出的对话框中输入服务器IP地址,点击"发送"按钮,进行客户端和服务器之间的认证,认证完毕即可正常运行客户端所有功能。

方波设计电路

信号波形合成实验电路设计报告摘要:本系统主要由LM3S811单片机、300KHz的方波发生器、分频电路、滤波电路、加法电路等模块组成。

300KHz的方波信号通过可编程逻辑控制器经30分频、10分频、6分频产生10KHz、30KHz、50KHz的方波信号。

经滤波电路和调理电路得到正弦波信号,将此信号的峰值送至单片机进行采样并显示,同时,通过加法电路将信号合成近似的方波信号或近似的三角波信号。

关键词:方波发生器分频器滤波器加法器一、方案比较与论证根据设计要求,我们对以下几个模块进行比较与论证:1.300KHZ的方波发生器方案一:采用555芯片产生。

由555芯片组成占空比为50%的多谐振器电路,其波形较为稳定。

但此方案在实际实验中未能达到题目要求。

方案二:采用运放TLC0831产生。

由TLCO831产生的300KHz方波发生器,此方案电路设计简单,产生的波形稳定。

通过以上比较分析,我们选用方案二。

2.分频器方案一:采用74LS161同时对300KHz的方波进行15分频,5分频,3分频后,再进行2分频,可得到占空比约为50%的方波。

但此波形不稳定且有明显失真。

方案二:采用可编程逻辑控制器。

通过高密度、高性能的EPM7128SC84芯片进行逻辑控制,以实现30分频、10分频、6分频。

由此产生的波形频率稳定可靠。

通过以上方案比较,我们选用方案二。

3.滤波电路方案一:采用无源滤波电路。

可由RC组成简单的低通滤波电路,此电路设计简单,但适合于低频和小功率放大电路。

方案二:采用有源滤波电路。

由集成运放TLC04组成的滤波电路可精确地滤去高频部分,得到所需的正弦波信号。

通过以上方案比较,我们选用方案二。

4.加法器方案一:采用同相求和运算电路。

同相求和电路中同相求和电路的各输入信号的放大倍数互相影响,不能单独调整。

方案二:采用反相求和运算电路。

反相求和电路中某一信号的输入电阻的阻值不影响其他输入电压的比例关系,故调节比同相求和电路方便。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目方波信号合成电路的

摘要

本文根据傅里叶级数展开方法,将正弦波转换成为各频率的方波。

首先,通过方波产生电路、分频电路、滤波电路获取所需频率的正弦波;再通过反相、调相、调幅电路得到需要的基波、3次谐波、5次谐波。

最后将三路信号经加法电路将正弦波合称为方波。

与其他方法相比具有成本廉价、可靠性高等优点。

关键词:波形合成器、傅里叶、方波、正弦波、滤波、调相、调幅。

目录

单元一:总体框图设计 (1)

单元二:方波振荡电路设计 (2)

单元三:方波振荡电路制作 (3)

单元四:分频器的设计与制作 (4)

单元五:滤波电路的制作 (5)

单元六:相位调整电路的制作 (6)

单元七:幅度调整电路的设计与制作 (7)

单元八:总调 (8)

单元九:参考文献 (9)

单元一:总体框图设计

一:项目总体方案分析

(1)总体方案图

基波:4KHZ

3次基波:12KHZ

5次基波:20KHZ

(2)采用120khz方波分频:

二:方案分析

(1)方波产生电路

方案一:用555定时器构成多谐震荡器,占空比可调节(10%~90%),适合产生中低频。

方案二:用运放产生方波信号,若选用TLC083芯片,压摆率可达19V/us,带宽为10MHZ。

可实现可调震荡。

经分析,本系统采用方案二。

(2)分频器

方案一:采用可编程逻辑控制器。

方案二:采用74LS161对120KHZ方波信号进行分频,可得占空比为50%的12KHZ、20KHZ信号,其电路简单,成本低。

经分析,本系统采用方案二。

(3)滤波电路

方案一:采用RC滤波,有源滤波电路。

方案二:TLC04芯片,四阶低通滤波。

经分析,本系统采用方案二。

(4)求和电路:用反向求和电路,不用同向求和电路。

(1)555定时器,构成震荡电路,只能产生中低频信号。

当T 充

=T 放时,输出方波。

T=T

充+T 放

=0.7(R A +R B )C f =1/T = 1/0.7(R A +R B )C=1190

(2) 由运放构成方波振荡电路(迟滞比较器)

3

2

1

8

4

U1:A

LM358

R1

10k

C1

1nF

R2

10k

R3

10k

U0

+5V

-5V

(1)选择合适的R1,生成1KHZ 的方波信号。

(2)改变R1的值,增大输出信号的频率。

一、确定元件参数

f=120kHZ f=1/2.2RC C=0.1uf R?→ R=37.8k 二、元件清单

TLC083 1片

100K电阻 2只

CD40106 1片

104 2只

10uf (储能) 2只

10k(电位器) 1只

102(电容) 1只

三、电路原理图。

单元四:分频器的设计与制作

一、74LS161介绍

四位二进制可预置的同步加法计数器

RD: 异步负数端 CP:时钟

P0~P3:四个数据输入端

CEP/CET: 记数始能端

Q0~Q3: 数据输出端

TC: 进位输出端

CP PE RD CEP CET Q

××L××全为L

↑L H××预置数据

↑H H H H记数

×H H L×保持

×H H×L保持(1)当RD=0时,输出全为低电平。

异步清零,当RD=0,Q3Q2Q1Q0=0000

(2)同步置数

PE=0 RD=1 ,且CP端有上升沿时,将P0~P3的数据送到Q0~Q3

上输出。

(3)记数

PE=RD=CEP=CET=1,且有上升沿。

(4)保持

只要CEP、CET有一个为低电平。

二、分频

若为n分频,输出信号的一个周期包含n个CP

三、分频器设计:6分频、10分频、30分频。

(1)6分频器

输出的一个周期包含6个CP时钟周期,且高低电平各占3个。

方案:将Q3作为输出

当Q3Q2Q1Q0=0000时,通过置数功能,使Q3Q2Q1Q0=0110

当Q3Q2Q1Q0=1000时,通过置数功能,使Q3Q2Q1Q0=1110

PE=Q2/Q1 P3~P0=Q3 110 RD=CEP=CET=1 (2)10分频器

将Q3作为输出

Q3Q2Q1Q0= P3P2P1P0=0100

Q3Q2Q1Q0= P3P2P1P0=1100

其电路连接图如下:

(3)30分频器

方案① 5*6 2片74LS161

方案② 10*3 2片74LS161

方案③ 15*2 1片74LS161,一片74LS74以上三个方案中选择方案③,其电路图如下:

D03Q014D14Q113D25Q212D36Q311RCO

15

ENP 7ENT 10CLK 2LOAD 9MR 1

U1

74LS161

1213

12

U2:A

74LS10

U1(CLK)

A

B C

D

D 2

Q

5

CLK

3Q

6

S 4

R 1

U3:A

74LS74

+5v

单元五:滤波电路的制作

一、 设计任务

4K (方波)→ 4K (正弦) 12K (方波)→ 12K (正弦) 20K (方波)→ 20K (正弦)

设计三个低通滤波器,截止频率分别为4K 、12K 、20K 。

二、TLC04

(1)时钟频率:截止频率=50:1,因此需要200K 、1M 的时钟。

(2)截止频率:0.1H~30KHZ (3)供电:+-2.5v~+-6v (4)封装(DIP-8)

CLKIN :CMOS 时钟 CLKR :TTL 时钟

LS:电平选择(LS=1 CMOS电平;LS=0 TTL电平)

单元六:相位调整电路的制作

一、理论分析

f(t)=4/πsinωt

f3(t)= 4/π*1/3*sin3ωt

f5(t)= 4/π*1/5*sin5ωt

当t=0时,f(t)=f3(t)=f5(t)=0

当t=2π时, f(t)=f3(t)=f5(t)=0

基波的一个周期与3次谐波的3个周期及5次谐波的5个周期重合。

二、调整方案

其中(1)是超前调整的方案。

(2)是滞后调整的方案。

三、反相

反相比例运算电路。

三、选择调整方案

1、确定其基波与3次谐波、5次谐波的相位关系。

2、选择方案。

3、确定元件参数。

单元七:幅度调整电路的设计与制作

一、调整目标。

基波峰-峰值:6V

3次谐波峰-峰值:2V

5次谐波峰-峰值:1.2V

注:本系统拟合成的方波无直流分量。

二、信号现状。

基波:最大值3V 直流分量1.5V

3次谐波:最大值1V 直流分量0.5V

5次谐波:最大值0.6V 直流分量0.3V

三、调整方案。

同相比例运算放大电路:A=1+R f/R1>>1

反相比例运算放大电路:A=- R f/R1

经分析选择反相比例运算放大电路。

它的放大倍数可以等于任意值。

四、电路连接图如下:

单元八:总调

把基波、3次谐波、5次谐波去除直流分量,幅度调整好的三路信号经LM358总调,其电路连接图如下:

单元九、参考文献

[1] 张靖武,周灵彬.单片机系统的PROTEUS设计与仿真[M].北京:电子工业出版社,2007.

[2] 徐受蓉.C语言程序设计[M].重庆:西南师范大学出版社,2008.

[3]胡宴如、狄苏燕.模拟电子技术基础[M] .北京:高等教育出版社,2006.

[4]黄国祥、刘芬.数字电子技术[M].湖北长江出版集团,2008.

(本资料素材和资料部分来自网络,仅供参考。

请预览后才下载,期待您的好评与关注!)。