片内逻辑分析仪工具——ChipScopePro

eda+试题3

一单项选择题(每题1分,共15分)1、在一个verilogHDL描述的模块中,若有多个always块,则这些always块应按照怎样的顺序执行?(B)A 顺行B 并行C 顺行或并行D 串行2、IP核在EDA技术的应用和开发中具有十分重要的地位,此处的IP指的是(A)A 知识产权B 互联网协议C 网络地址D 连接目的的地址3、下面器件中属于易失性器件的是(D)A 熔丝(Fuse)或反熔丝开关B EEPROMC 闪速存储器(Flash Memory)D 基于SRAM工艺的FPGA4、FPGA是基于哪种结构的可编程逻辑器件(A)A LUT结构B 乘积项结构C PLD结构D OTM结构5、CPLD是基于哪种结构的可编程逻辑器件(B)A LUT结构B 乘积项结构C PLD结构D OTM结构6、Xilinx公司开发的在线片内逻辑分析工具是(A)A ChipScope ProB LogiBLOXC FloorplannerD imPACT r7、Xilinx公司推出的嵌入式开发套件是(A)A EDKB XPSC SDKD GNU8、FPGA Advantage是哪家公司推出的FPGA全流程设计工具(B)A XilinxB Mentor GraphicsC AldecD Synplicity9、关于FPGA,下面说法错的是(B)A FPGA在使用时,除了逻辑设计外,还要进行延时设计B FPGA实现同一功能可以有不同的方案,但其延时都是一样的C FPGA相比较于CPLD而言,逻辑单元小,连线关系复杂D FPGA相比较于CPLD而言,更适合进行大规模的逻辑电路设计10、关于系统仿真,下面描述正确的是(A)A 通过系统仿真,可以得知所设计系统在功能,延时等方面是否满足设计要求,并为系统的修改,优化提供依据B 时序仿真是对综合后的网表进行的仿真,只验证设计模块的基本逻辑功能C 功能仿真需要利用FPGA芯片布局布线后的信息D ModelSim不支持VHDL和VerilogHDL的混合仿真11、关于ISE Foundation提供的内嵌的综合工具,下面说法错误的是(D)A Xilinx公司提供的综合工具是XSTB 在综合前,可以打开综合属性设置对话框,设置与综合的全局目标和整体策略相关的参数C 该综合器在综合后,可以提供综合报告,综合产生的寄存器传输级模块符号和模块内部逻辑结构等信息D 该综合工具实现了将设计映射到器件结构上,进行布局布线,达到在选定器件上实现设计的目的12、关于设计输入,下面描述错误的是(D)A 设计输入是设计者将所设计的系统或电路以EDA开发软件要求的某种形式表示出来,并送入计算机的过程B 可以采用原理图、HDL、IP核、状态转移图等方式向EDA开发软件输入设计者的设计意图C 可以采用层次化设计方法,分模块、分层次地进行设计描述D 是将系统设计得到的程序化数据,按一定的格式输入,装入一个或多个PLD 的编程存储单元,定义内部模块的逻辑功能以及它们的相互连接关系13、综合是EDA设计流程的关键步骤,下面对综合的描述中错误的是(B)A 综合就是将描述电路的高级语言转化成低级的,可与FPGA/CPLD的基本结构相映射的网表文件B 综合是存软件的转化过程,与器件硬件结构无关C 综合科理解为,将软件描述与硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的D 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束14、以基本方式单独使用Modelsim进行仿真的步骤是(A)A 建立仿真库-编译源代码-启动仿真器-执行仿真B 启动仿真器-建立仿真库-编译源代码-执行仿真C 建立工程-编译并导入测试文件-添加源文件-执行仿真D 建立工程-添加源文件-编译并导入测试文件-执行仿真15、关于JTAG边界扫描测试,下面说法错误的是(D)A JTAG规范可以用于芯片的测试与配置B JTAG接口由4个必需的信号,以及1个可选信号构成C JTAG在芯片I/O端上增加移位寄存器,并将这些寄存器连接起来,配合时钟复位,测试方式选择以及扫描输入和输出端口,形成边界扫描通道D JTAG边界扫描测试需要物理探针配合捕捉数据二、名词解释(每题2分,共6分)16、PLD 可编程逻辑器件17、FPGA 现场可编程门阵列18、CPLD 复杂可编程逻辑器件三、判断改错题(每题4分,共16分)19、自顶向下设计思路是首先确定可用的元器件,然后根据这些器件进行逻辑设计,完成各模块设计后进行连接,在形成系统,最后经调剂,测量看整个系统是否达到规定的性能指标。

ChipAnalyzer教程

– 点击 工具-> 选项…在编辑页设置实例的前缀

27

定义模拟器件

• 点击 查看->显示模拟器件工具条… • 定义 NMOS/PMOS/NMOS4/PMOS4

– G、 D 和 S端口会被自动放置 – NMOS/PMOS 的W、 L、 bn和M参数需要手工设置 – NMOS4/PMOS4 的W、 L和M参数需要手工设置,还需要给它们添加B端口

• 1. 定义全部的区域或模块

• 2. 定义全部的标注工作

– 各个区域或模块单元的类型与它们自己工作区中的单元类型不同 – 有相同单元种类的区域或模块应该共用一个单元工作区 – 各个区域或模块都应该有一个相应的网表工作区,它们的单元标注是从各自的单元工作区中发送或者合并而

来的 – 需要有一个顶层网表工作区

12

常用操作

• 移动屏幕

– Page Up/Page Down/Home/End – Ctrl+Page Up/Ctrl+Page Down/Ctrl+Home/Ctrl+End – 方向键

• 关闭当前窗口 “ Alt+X” • 取消当前编辑状态 “ Esc ” • 保存当前窗口图像位置 “ Ctrl+J ” • 加载保存的窗口图像位置 “ Shift+J ” • 同时显示多层图像窗口 “ Alt+4 ”

A

ZN

A2

P_INV_18_8 B1 A1

B2 A2

I15 Z

P_AOI22_38_18

VDD

M1 VDD! 2.5u/0.35u A2

M3 VDD! 3.0u/0.35u A1

ZN

M0

M2

GND!

Xilinx官方的6个EDK实验6

试验6系统验证及调试:介绍这个试验通过XMD和ChipScope 对系统进行可观测的软件和硬件调试。

目标完成试验后,我们希望达到以下目标:•向系统中加入ChipScope片内逻辑分析仪•系统调试打开工程Step 1在D:\Lab\下创建lab6mb文件夹。

可以根据上面的实验建立工程,也可直接把lab6mb的内容直接拷贝至此目录。

编译器优化选项设置Step 2这个部分测试编译器优化水平的不同性能。

在这之前,我们要移除定时器中断服务程序用一个延时循环来代替它。

n使用Project → Software Platform Settings …打开软件平台设置GUIo点击Processor, Driver Parameters and Interrupt Handlers栏p删除Current Value的值timer_int_handler。

使其为空。

点击<OK>q从D:\Lab\lab_sources\lab6_sources路径复制system_delay.c到当前工程D:\Lab\labmb6\coder从工程MyProj移除system_timer.c并加入新的文件system_delay.cs双击MyProj标题选择Optimization Tab如图所示,设置编译器优先等级到No Optimization,点击<OK>。

图 6-1. 编译选项设置w选择Download那么这些源文件将重新编译并下载到板上去。

LED将连续0.1秒显示计数器。

w设置编译器优化等级,并再次下载到工程当中去。

注意显示速度取决于编译器的优化等级片内逻辑分析仪Step 3点击Project → Add/Edit Cores … (dialog),加入ChipScope 片内逻辑分析仪的。

配制以下端口。

如图6-2所示。

sys_clk_smb_halt (MicroBlaze)dbg_stop (MicroBlaze)图6-2 芯片域内核连接n 点击Project → Add Cores (dialog)o 在Peripherals 栏 加入chipscope_icon 与chipscope_opb_iba 参数p 在Bus connection 栏,连接chipscope_opb_iba 作为一个BA (总线分析器)器件到OPB 总线。

ChipScope Pro详细教程(Xilinx在线逻辑分析仪)

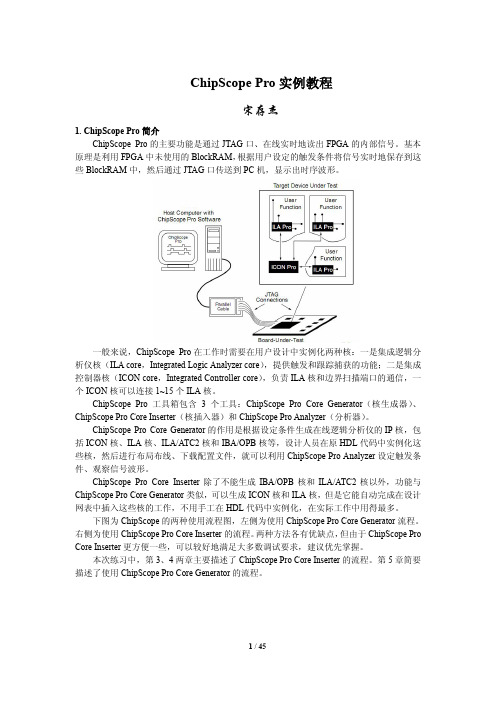

ChipScope Pro实例教程宋存杰1. ChipScope Pro简介ChipScope Pro的主要功能是通过JTAG口、在线实时地读出FPGA的内部信号。

基本原理是利用FPGA中未使用的BlockRAM,根据用户设定的触发条件将信号实时地保存到这些BlockRAM中,然后通过JTAG口传送到PC机,显示出时序波形。

一般来说,ChipScope Pro在工作时需要在用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrated Logic Analyzer core),提供触发和跟踪捕获的功能;二是集成控制器核(ICON core,Integrated Controller core),负责ILA核和边界扫描端口的通信,一个ICON核可以连接1~15个ILA核。

ChipScope Pro工具箱包含3个工具:ChipScope Pro Core Generator(核生成器)、ChipScope Pro Core Inserter(核插入器)和ChipScope Pro Analyzer(分析器)。

ChipScope Pro Core Generator的作用是根据设定条件生成在线逻辑分析仪的IP核,包括ICON核、ILA核、ILA/ATC2核和IBA/OPB核等,设计人员在原HDL代码中实例化这些核,然后进行布局布线、下载配置文件,就可以利用ChipScope Pro Analyzer设定触发条件、观察信号波形。

ChipScope Pro Core Inserter除了不能生成IBA/OPB核和ILA/ATC2核以外,功能与ChipScope Pro Core Generator类似,可以生成ICON核和ILA核,但是它能自动完成在设计网表中插入这些核的工作,不用手工在HDL代码中实例化,在实际工作中用得最多。

下图为ChipScope的两种使用流程图,左侧为使用ChipScope Pro Core Generator流程。

FPGA开发流程及的设计工具

09.03.2021

第2章

14

辅助设计工具

⊿ iMPACT iMPACT配置器可以完成配置文件的分割组合,配置文

件格式的转换,实现将配置文件下载到FPGA或相应的存 储器等功能。它的主要功能是下载、回读与校验配置数据, 调试配置过程中出现的问题。

⊿ 功耗仿真器(XPower) 功耗仿真器(XPower)是估计设计功耗的工具,帮助

09.03.2021

第2章

16

IP核输入 ⊿IP核生成器提供了大量的成熟、高效IP核为用户所用。lP

核生成器可生成的IP核功能繁多,从简单的基本设计模块 到复杂的处理器等一应俱全。配合Xilinx网站的IP中心使 用,能大幅度减轻工程师的工作量,提高设计质量。 ⊿Core Generator可生成的IP核大致分为10大功能模块: 基本模块、通信与网络模块、数字信号处理模块、数学功 能模块、存储器模块、微处理器、控制器与外设模块、标 准与协议设计模块、语音处理模块、标准总线模块、视频 与图像处理模块等。这些功能涵盖了从基本设计单元到复 杂功能样机的众多成熟设计。而且每次ISE的升级补丁中 都会有IP核的升级,另外用户可以通过Xilinx的IP中心查 询更多的IP信息。 ⊿如果用户设计只是针对 FPGA应用的,使用IP核能避免重 复设计,缩短工程时间,提高工作效率。这些IP核是根据 Xilinx的FPGA器件特点和结构而设计,直接用Xilinx FPGA底层硬件原语描述,充分发挥了FPGA的功能,其实 现结果在面积和速度上都令人满意。

PCB系统设计人员设计电源系统功率。 ⊿ 在线逻辑分析仪(Chip Scope Pro)

在线逻辑分析仪(Chip Scope Pro)是Xilinx与Agilent 合作开发的FPGA在线片内信号分析工具,它的主要功能 是通过JTAG口,在线实时地读出FPGA的内部信号。

ChipScope使用说明

ChipScope使用说明目录1.建立工程...................................................................................................... 错误!未定义书签。

2.插入及配置核 (3)2.1运行Synthesize (3)2.2新建cdc文件 (3)2.3 ILA核的配置 (4)3. Implement and generate programming file (7)4.利用Analyzer观察信号波形...................................................................... 错误!未定义书签。

4.1连接器件........................................................................................... 错误!未定义书签。

4.2下载配置fpga (9)4.3载入信号端口名 (10)4.4设置触发信号 (10)4.5运行并观察信号波形 (11)补充 (12)1.建立工程ChipScope是配合Xilinx Ise使用的片内逻辑分析工具,使用的第一步是建立ise工程文件,详细步骤可参考ise使用说明。

如果已有建好的ise工程,可跳过此步骤,打开已有工程即可。

建立工程时注意正确添加.v源文件和.ucf管脚配置文件。

2.插入及配置核这里介绍的是ICON核和ILA核的使用方法。

ILA核提供触发和跟踪功能,根据用户设置的触发条件捕获数据;然后在ICON的控制下,通过边界扫描口将数据上传到PC;最后在Analyzer中显示出信号波形。

2.1运行Ise的Synthesize单击选中sources栏中的顶层源文件,右键点击processs栏中的Synthesize,点击Run,进行代码综合。

chipscope入门

Reference Imformation

• 1. /

• 2.Chipscope Pro XILINX Shenzhen • 3. Spartan-3E user Guide.pdf

Problem

• 作为一个初学者,该设计方案的前后仿真虽然功能都是正确的, 但是会想到如果在加入芯片延时信息之后如果影响了功能,该 设计改如何修改,是应该重新设计,还是应该在原有的基础上 进行修改,如果是工程很大,重新设计可能性很小,那如何修 改才能使工程完成预期的功能? • 如果对该简化的方案进行一个全面的调试,该如何完成数据的 输入? • 并行数据转换为串行输出的关键是采用移位输出,assign语句与 always块是并行的,但觉得在运行的过程中判断always块在先, 这是为什么? • 在FPGA设计初期是否该考虑到设计所占资源的问题,比如说乘 法器采用移相相加乘法器,查找表乘法器,加法器树乘法器, 混合乘法器,该如何把握?

(一般我们选择使用这种方法)

ChipScope使用的核

• ChipScope经常使用的核有:ICON,ILA,VIO; ICON:集成控制核,负责ILA和JTAG的通信, 一个可以最多控制15个ILA或VIO; ILA:集成逻辑分析核,主要提供触发和捕获 功能;(相当于示波器) VIO:虚拟输入、输出核;(注意IN,OUT代码 的例化)

WHY? Use chipScope

使用ChipScope的要求?

ChipScope的组件?

ChipScope组件功能简介

ChipScope工作模式

How ?Use ChipScope

Different of two ways!

1.使用方法 Inserter: /article/10-03/94536_2s.html Generator:这种方法比较常使用,后面会结合实例讲解 2.优缺点 Inserter:操作步骤复杂繁琐,但不需要修改设计代码; Generator:操作简单,但需要在HDL中例化CORE。

实验4 PowerPC 处理器系统验证与调试

实验4 PowerPC 处理器系统验证与调试信息14 李兰鑫 2110502077一、实验目的通过实验1、学会如何添加ChipScope到一个系统里2、学会使用ChipScope和SDK debugger进行调试3、初步掌握系统调试的方法4、熟悉向系统中加入ChipScope 片内逻辑分析仪的方法和交叉调试方法二、实验内容本实验将完成调试处理器系统的过程,其中包括编写中断服务程序来访问OPB定时器等。

XPS和ChipScope将用于观测系统的硬件和软件。

1、安装Chipscope Core。

通过IP Catalog 添加Chipscope cores并进行相应的配置设计。

建立触发机制,当某一个值出现在OPBaddress、OPB data、OPB control bus上时触发。

2、SDK和Chipscope操作。

打开一个SDK工程,用XMD建立面向目标的连接。

在成功生成设计之后,使用SDK debugger和ChipScope Pro工具观察其运行过程。

3、HW/SW 交互调试。

在触发/波形窗口设置相应参数,运行软件调试器,等待触发条件。

三、实验结果实验结果如下图所示:实验中首先安装Chipscope Core,随后用SDK和ChipScope进行调试,在设置了触发/波形窗口中的各项参数之后,便可观察到如图的波形结果。

四、结果分析在EDK 中,ChipScope硬件调试模块可以作为IP模块被添加,同时,ChipScope分析仪可与SDK调试器共同提供一个调试环境。

该环境下,允许软件与硬件之间使用一个共享的JTAG接口进行交叉触发与调试。

五、心得体会通过本次实验,我进一步熟悉了XPS的使用方法,进一步掌握了IP添加和配置的方法,并熟练使用SDK进行软件调试。

同时,本次实验还接触到Chipscope调试软件,初步学习了其中的一些配置和操作。

完成了实验指导书的内容。

我了解到Chipscope是一个逻辑分析仪,主要用于在上板测试过程中采集并观察芯片内部信号,以便于调试。

xilinx软件介绍

ISE Design Suite涉及了FPGA设计的各个应用方面,包括逻辑开发、数字信号处理系统以及嵌入式系统开发等,本次设计应用了多个开发工具,在这里进行简要介绍。

1)ISE Foundation:开发集成工具

2)ChipScope Pro:在线逻辑分析仪工具

3)PlanAhead:用于布局和布线等设计分析工具

ISE Foundation软件是xilinx公司推出的FPGA/CPLD集成开发环境,不仅包括逻辑设计所需的一切,还具有简便易用的内置式工具和向导,使得I/O分配、功耗分析、时序驱动设计收敛、HDL仿真等关键步骤变得容易二直观。

ChipScope Pro软件

Xilinx公司推出了在线逻辑分析仪,通过软件方式为用户提供稳定和方便的解决方案。

该在线逻辑分析仪不仅具有逻辑分析仪的功能,而且成本低廉、操作简单,因此具有很高的实用价值。

ChipScope Pro既可以独立使用,也可以在ISE集成环境中使用,非常灵活,为用户提供方便和稳定的逻辑分析解决方案,支持Spartan和Virtex全系列FPGA芯片。

ChipScope Pro将逻辑分析器、总线分析器和虚拟I/O小型软件核直接插入到用户的设计当中,可以直接查看任何内部信号和节点,包括嵌入式硬或软处理器。

PlanAhead软件

PlanAhead工具简化了综合与布局布线之间的设计步骤,能够将大型设计划分为较小的、更易于管理的模块,并集中精力优化各个模块。

此外,还提供了一个直观的环境,为用户设计提供原理图、平面布局规划或器件图,可快速确定和改进设计的层次,以便获得更好的结果和更有效地使用资源,从而获得最佳的性能和利用率,极大地提升了整个设计的性能和质量。

基于基于FPGA平台的电信传输系统实验三

本次课程安排•ISE开发工具使用•Modelsim仿真工具使用•硬件描述语言ISE软件简介•Xilinx 作为当今世界上最大的FPGA/CPLD 生产商之一,长期以来一直推功者FPGA/C PLD技术的发展. 其开发的软件也不断升级换代,由早期的Foundation系列逐步发展到目前的ISE14.x系列。

•I S E 是集成综合环境的缩写,它是Xilinx FPGA/CPLD 的综合性集成设计平台,集成了设计、输入、仿真、逻辑综合、布局布线与实现、时序分析、芯片下载与配置、功率分析等几乎所有设计流程所需工具。

ISE的主要特点•优良的集成环境–I S E 是一个集成环境,可以完成整个FPGA/C P LD 开发过程.•简洁流畅的界面风格–I S E 界面风格简洁流畅,易学易用,秉承了可视化编程技本. 界面根据设计流程而组织,整个设计过程只需按照界面组织结构依次单击相应的按钮或选择相应的选项即可。

•丰富的在线帮助信息•强大的设计辅助功能ISE软件的安装第三方软件的接口设置ISE软件的启动ISE软件的设计流程•设置工作环境•新建工程•添加设计源文件•写测试激励文件•功能仿真(前仿)•综合•综合后仿真•设计用户约束文件•实现ISE软件的设计流程•布局布线后仿真(后仿)•下载•在线调试•烧写ISE软件的设计流程新建工程新建工程顶层模块类型说明新建工程设置工程属性新建工程新建工程属性说明为工程新建资源新建资源对话框为工程新建资源新建资源类型说明更改工程属性编译工程代码编译后的出错提示新建测试激励文件新建测试激励波形文件片上逻辑分析仪(Chipscope Pro)使用Chipscope应用框图Chipscope Pro 设计流程Chipscope Pro Core Inserter简介新建Chipscope Pro Core Inserter资源对话框Chipscope Pro Core Inserter简介Chipscope Pro Core Inserter用户界面Chipscope Pro Core Inserter简介Select Intergrated Logic Analyzer Option 对话框Chipscope Pro Core Inserter简介触发条件判断单元的类型Chipscope Pro Core Inserter简介Capture Parameters选项卡设置Chipscope Pro Core Inserter简介网线连接对话框Chipscope Pro Analyzer简介在ISE中直接启动Chipscope Pro AnalyzerChipscope Pro Analyzer简介配置FPGAChipscope Pro Analyzer简介完成配置后用户界面Chipscope Pro Analyzer简介Match设置对话框Chipscope Pro Analyzer简介Trig设置对话框观测波形Chipscope Pro波形观测波形组合总线数据观测波形总线数据生成结果Modelsim仿真工具简介•Modelsim是硬件描述语言的仿真工具,该软件可以对设计的VHDL、Verilog或者是混合语言的程序进行仿真。

Xilinx_ISE使用教程

Next

--主要功能

ISE的主要功能包括设计输入、综合、仿真、实现和 下载,涵盖了可编程逻辑器件开发的全过程,从功能上 讲,完成CPLD/FPGA的设计流程无需借助任何第三方 EDA软件。下面简要说明各功能的作用: 1、设计输入:ISE提供的设计输入工具包括用于 HDL代码输入和查看报告的ISE文本编辑器(The ISE Text Editor),用于原理图编辑的工具ECS(The Engineering Capture System),用于生成IP Core的Core Generator,用于状态机设计的StateCAD以及用于约束文 件编辑的Constraint Editor等。

Xilinx公司ISE10.1软件介绍

--ISE设计流程

规划 和预算 创建代码/ 原理图 HDL RTL 仿真

实现

翻译 映射 布局和布线 得到时序收敛 功能仿真 综合以创建网表

时序仿真

产生.1软件介绍

--ISE主界面

Xilinx公司ISE10.1软件介绍

Xilinx公司软件平台介绍

--DSP_Tools软件

Xilinx公司推出了简化FPGA数字处理系统的集成开 发工具DSP Tools,快速、简易地将DSP系统的抽象算法 转化成可综合的、可靠的硬件系统,为DSP设计者扫清 了编程的障碍。DSP Tools主要包括System Genetator和 AccelDSP两部分,前者和Mathworks公司的Simulink实现 无缝链接,后者主要针对c/.m语言。

--创建一个新工程

新建文件 的类型, 不同的类 型有着不 同的功能 和意义。

该文 件的 实体 名

Xilinx公司ISE10.1软件设计流程介绍

ise里用chipscope

Chipscope的使用本来论文都差不多了,但是老师说缺少实验数据,没有办法,自己再加班加点补吧。

好在自己恰好有ChipScope的盘,于是赶快安装上,临阵磨枪,突击看了一晚上,有了一点点概念,这次记一下,下次就不用绞尽脑汁了。

还要感谢King帮忙查找资料。

逻辑分析仪的产生有两种方法:Core Generator(核产生器)和Core Inserter(核插入器),第一种方法产生内核,将这些内核例化后添加到原设计文件,最后综合,实现,下载。

第二种方法不需要修改原文件,它是将生成的内核添加到综合后的网表文件中,所以我们采用第二种方方法。

Core Inserter 的流程为:1)的RTL 综合成Netlist;2)调用Core Inserter 插入逻辑分析仪;3)布置和布局;4)产生bit 文件下载验证。

1. 首先用ISE对所设计的文件进行综合,然后再添加新建文件,选择ChipScope Definition 文件,选择完毕之后,添加到ISE工程。

2.对core Inserter进行配置,选择器件族,其它的默认即可,接下来是选择数据位宽,捕捉对比,进行信号连线等配置,可以根据自己的情况详细设置。

需要注意的是综合的设置需要保存Keep Hierarchy,防止优化过度。

3.按照以前运行ISE的步骤即可,知道最后下载到FPGA开发板,在ISE的最后会有ChipS cope Pro Analyze,然后点击,就运行逻辑分析仪。

然后点击JTAG连接方式,我的是用U SB的,然后选择[Device] configure 进行器件配置。

在window菜单下面可以选择触发设置窗口等选项,然后运行就可以观察你想要的波形了。

搭建Xilinx开发环境(3)…… 使用ChipScope进行调试Xilinx的ChipScope工具就相当于Altera的SignalTap II,能够捕捉FPGA内部的信号,方便了调试过程。

ChipScope培训

看我们的DEMO演示!

ChipScope增强功能

• IBA (Integrated Bus Analyzer):用来Debug

IBM coreconnect总线 • ATC(Agilent Trace Core):Agilent为Xilinx FPGA开发的支持片外采样数据存储的设 备。

缩略语解释

Chipscope Pro Core Inserter 流程

• Step1 : 综合的时候要保留设计层次

– XST 缺省设置是将设计打平以取得好的综合 效果 – Synplifcity 缺省设置是保留设计层次

• Step2: 在ISE 中做Translate的时候需要设置

”Preserve Hierarchy on Sub module” . 缺省情 况下为不设置.

Xilinx Shenzhen

什么是 ChipScope Pro?

ChipScopePro 是基于Xilinx FPGA的内嵌的逻辑分析 仪。它只需要一个JTAG口就可以访问到FPGA 内部的所有信号。极大的方便了Xilinx FPGA的 现场调试。

为什么要用 ChipScope?

•验证FPGA内部/外部的功能 •探测不容易看到的信号 •避免购买昂贵的“逻辑分析仪”

从windows 开始菜单单独启动

• Step4: 设置输入网表和输出网表,输出目录,

器件类型

– 一般情况下只需将输入网表设置为工程目录 下translate后的输出网表即可,工具会自动设置 缺省的输出目录和输出网表文件名

Chipscope Pro Core Inserter 流程

Chipscope Pro Core Inserter 流程

• 启动Chipscope Pro Analyzer

第四部分2:FPGA配置及片内调试技术

第四部分:FPGA设计基础(2)北京理工大学雷达技术研究所陈禾FPGA配置及片内调试技术{边界扫描原理{FPGA配置的基本方式{高级配置环境{基于嵌入式处理器的配置技术{基于Internet的可重构逻辑实现{ChipScope Pro片内调试系统边界扫描原理{IEEE Standard 1149.1 -Test Access Port and Boundary-Scan Architecturez JTAG是JOINT TEST ACTION GROUP组织最初提出的,最终由IEEE批准并且标准化的。

IEEE 1149.1一般也俗称JTAG调试标准。

z在JTAG调试标准当中,边界扫描(Boundary-Scan)是一个很重要的概念。

边界扫描技术的基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。

因为这些移位寄存器单元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

边界扫描原理{当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片和外围的输入输出隔离开来。

通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。

{对于芯片的输入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该管脚中去。

{对于芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”(capture)该管脚上的输出信号。

边界扫描原理{在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的。

{芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。

{一般的芯片都会提供几条独立的边界扫描链,用来实现完整的测试功能。

边界扫描链可以串行的输入和输出,通过相应的时钟信号和控制信号,就可以方便的观察和控制处在调试状态下的芯片。

利用边界扫描链可以实现对芯片的输入输出进行观察和控制。

Chipscope 简明教程

Chipscope 简明教程stevechou@一、操作环境本教程假定用户已有安装好仿真、综合、ISE和相应的Chipscope,教程使用的环境如下:仿真:Modelsim 5.8综合:Synplify pro 7.5.1布局:ISE 6.2分析:Chipscope 6.2二、RTL设计及其仿真RTL 源代码参见rtl/lfsr.v,testbench 参见rtl/lfsr_tb.v,其仿真波形如下:三、逻辑分析仪产生逻辑分析仪的产生有两种方法:Core Generator(核产生器)和Core Inserter(核插入器),Core Inserter 的流程为:1)的RTL 综合成Netlist;2)调用Core Inserter 插入逻辑分析仪;3)布置和布局;4)产生bit 文件下载验证。

而Core Generator 的流程为:1)调用Core Generator 产生逻辑分析仪的Netlist;2)修改用户的RTL,插入逻辑分析代码;3)布置和布局;4)产生bit 文件下载验证。

因为使用Core Inserter 需要在网表中搜索信号,相对修改RTL 来说比较麻烦,并且每次修改RTL 后需要重新插入逻辑分析仪,故本教程以Core Generator 流程为例,这样每次修改RTL 后,只需要重新综合、布置和布局即可。

1)从“开始”-->“程序”-->“ChipScope Pro 6.2”--> “ChipScope Pro Core Generator”2)选择ICON,即集成控制器产生3)选择输出目录和设备家族4)选择语言和综合工具5)点击“Generate Core”产生集成控制器6)点击“Start Over”,回到主菜单,选择“ILA”,即产生集成逻辑分析仪7)选择输出目录、设备家族和采样时钟边缘8)在Trigger Width 框填入触发宽度329)选择“Data Same AsTrigger”,即数据端口和触发端口相同;从Data Depth下拉框选择采样深度,“Number of Block RAMs”处将同时显示需要的Block RAM 块数,对于Sparten II 200 来说,共有14 块Block RAM,注意不要超过限制10)选择语言和综合工具11)点击“Generate Core”产生集成逻辑分析仪Chipscope 将在相应目录产生以下主要文件:icon.edn 集成控制器的网表icon.ncf 集成控制器的网表约束文件icon_synplicity_example.v 集成控制器的嵌入例子代码ila.edn 集成逻辑分析仪的网表ila.ncf 集成逻辑分析仪的网表约束文件ila_synplicity_example.v 集成逻辑分析仪的嵌入例子代码用户需要依照例子代码修改RTL 代码,以下示出最后的结果,请特别注意红色部分://-----------------------------------------------------------------//// ICON core wire declarations////-----------------------------------------------------------------wire [35:0] control0;//-----------------------------------------------------------------//// ICON core instance////-----------------------------------------------------------------icon i_icon(.control0(control0));//-----------------------------------------------------------------//// ILA Core wire declarations////-----------------------------------------------------------------wire [31:0] trig0;//-----------------------------------------------------------------//// ILA core instance////-----------------------------------------------------------------ila i_ila(.control(control0), //控制器接口.clk(clk), //采集的时钟.trig0(trig0));assign trig0 = q; //需要采集的信号列表四、综合代码将文件icon_synplicity_example.v、ila_synplicity_example.v和lfsr.v添加到工程中综合:五、 布置、布局和下载电路将icon.edn 、icon.ncf 、ila.edn 和ila.ncf 拷贝到综合器生成 edf 的目录。

chipscope使用方法

chipscope的学习与使用(1) chipscope有三个主要的功能:1、ChipScope Core Inserter配置ICON核配置ILA核触发参数、捕获参数、网线连接2、ChipScope Pro Analyzer初始化边界扫描链,选择芯片型号配置芯片(JTAG CLOCK)设置触发条件观察信号波形3、ChipScope Pro Generator生成ICON核生成ILA核通过功能1生成了一个CDC文件,在这个CDC文件中需要配置一下触发参数的个数、深度以及连接。

最后工程需要重新run一下。

功能1通过后,可以双击Analyze Design Using ChipScope来启动分析仪,通过分析仪可以查看CDC 文件中配置的连线的波形。

功能3是一个集成功能,它把功能1和功能2集成为一个功能。

功能3需要打开ChipScope Pro Generator软件,在这个软件中新建一个工程,配置芯片型号以及合适的语言(V erilog HDL),配置ICON核和ILA核。

之后在工程中加入这两个文件:xxx_icon.xco和xxx_ila.xco文件在工程.v文件中加入ICON核和ILA核的调用,这时不需要把cdc文件,而且CDC文件需要从工程中移除。

下面是一个小的例子(调用ICON核和ILA核):wire [w_icon-1 : 0] con;wire [w_trig-1 : 0] p_data;xxx_icon u_icon(.CONTROL0(con));xxx_ila u_ila(.CLK(clk),.CONTROL(con),.TRIG0(p_data));最后再打开分析仪就可以来查看波形了,如果需要有时候可以再次加载CDC 文件。

以下是具体的操作说明:ChipScope Pro Generator打开方式:(见图《软件打开》)开始->程序->Xilinx ISE Suite 12.4->ISE Design Tools->CORE Generator打开这个软件后,新建一个工程。

Xilinx网站资源导读(绝对有用)

Topics:1. Xilinx软件介绍2. 软件版本和软件更新3. 软件教程哪里找4. 硬件资料5. 参考设计6. 问题解决7.总结1.Xilinx软件介绍用Xilinx的软件做FPGA开发,主要涉及到得软件是Xilinx自家的ISE, EDK, ChipScope Pro, System Generator, PlanAhead 和第三方的ModelSim和Synplify。

ISE是主要的逻辑设计软件,其他软件的具体实现功能都依附于ISE。

ISE有Foundation版和WebPack版。

WebPack版免费,Foundation版收费。

两者的区别是支持的器件不同。

功能是相同的。

WebPack版支持的功能可以看这里:/ise/products/webpack_config.htm。

Foundation当然支持所有功能,功能列表可以在这里找到:/ise/logic_design_prod/foundation.htm。

说这些的目的是,如果开发所使用的器件是WebPack版支持的,那么就从网上下载免费版就好了,不用费劲心机地找Fondation版却用不到他支持的功能。

ChipScope Pro 是片内的逻辑分析仪。

可以让用户方便地抓取片内信号进行debug。

ChipScope支持的Trig方式非常多样,用熟悉了以后几乎是想要观察什么内部信号都可以观察到,即使他有BRAM深度的限制。

/chipscopePlanAhead工具自从ISE7时代被开发出来并发展了这么多年之后,已经成为了提高设计效率和提高产品性能的有力工具。

它可以帮我们在布局布线之前做好管脚定位和DRC检查、规划区域约束、查看综合网表,并且可以跑多次实现,找出最佳的布局并分析时序。

/planaheadEDK - Embedded Development Kit,顾名思义就是用来做嵌入式系统的。

它提供对PowerPC 硬核和MicroBlaze软核的支持,免费提供一些常用的硬件IP Core,比如各种Memory Controller、各种外设如IIC, SPI, GPIO,并集成了GNU工具链,使之成为软硬件设计一体化的设计工具。

赛灵思官网资源导读

赛灵思官网资源导读俗话说“授之鱼不如授之以渔”,看到这边有人要资料有人送资料的,其实论坛不更应该是一个交流的空间么?那就让找资料更有效率一点,让大家花更多时间来交流吧。

言归正传,写这篇文章主要想介绍Xilinx各种资料的找法、分类方法和什么问题该看哪些资料。

限于经验,难免有错漏,希望大家指出错误并继续补充。

一、软件Xilinx的软件主要是ISE, EDK, ChipScope Pro, System Generator, PlanAhead, ModelSim,如果要算上AccelDSP也凑合,不过相信国内没多少人用。

ISE是主要的逻辑设计软件,其他软件的具体实现功能都依附于ISE。

ISE有Foundation版和WebPack版。

WebPack版免费,Foundation版收费。

两者的区别是支持的器件不同。

功能是相同的。

WebPack版支持的功能可以看/blog/link2url.php?link=http%3A%2F%%2Fise%2Fpro ducts%2Fwebpack_config.htm。

Foundation的话当然全支持拉,要看的话在这里/blog/link2url.php?link=http%3A%2F%%2Fise%2Flogi c_design_prod%2Ffoundation.htm。

说这些的目的就是,如果你的器件WebPack支持,就直接到网上下载WebPack吧,没有版权之类的后顾之忧;如果不行,Verycd上找些东西还是挺方便的。

ModelSim MX有免费的starter version,可以和ISE WebPack一起下载,安装以后在开始里面点licens_e request就可以申请starter的使用权了。

另外,可以VHDL和Verilog各申请一个,那么就可以仿真两种语言了,不过不支持mix language。

/blog/link2url.php?link=http%3A%2F%%2Fise%2Fverifica tion%2Fmxe_details.html不过那一页说的ModelSim XE的use case不准的,XE,PE,SE的差别还是仔细看这里吧。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第11章片内逻辑分析仪工具——ChipScope Pro11.1 ChipScope Pro工具介绍在FPGA调试阶段,传统的信号分析手段要求在设计时保留一定数量的FPGA管脚作为测试管脚,这种方法灵活性差,对PCB布线也有一定的影响。

当今先进的FPGA器件所具有的规模、速度和板级要求使得利用传统逻辑分析方法来调试采用FPGA器件进行的设计几乎是不可能的。

Xilinx公司推出的片内逻辑分析仪ChipScope Pro能够通过JTAG口,实时地读出FPGA的所有内部信号,而只需要片内的少量BlockRAM和逻辑资源,使得逻辑分析灵活方便。

ChipScope Pro是与ISE配套使用的,其版本经过了ChipScope 4.1i,ChipScope 4.2i,ChipScope Pro 5.1i,ChipScope Pro 5.2i和ChipScope Pro 6.1i的升级过程,ChipScope Pro 6.1i是与ISE 6.1配套使用的最新版本。

ChipScope Pro软件由3个工具组成:(1) ChipScope Pro内核生成器:为综合控制器(ICON)内核、CoreConnect™ OPB的总线分析内核(IBA/OPB)、逻辑分析(ILA)内核及安捷伦跟踪内核(ILA/ATC)提供网表和实例化的模板;(2) ChipScope Pro内核插入器:自动地为用户已经综合完的设计中插入ICON、ILA和ILA/ATC的内核;(3) ChipScope Pro分析仪:提供器件的配置、触发的设定和ILA、IBA/OPB及ILA/ATC核的踪迹显示功能。

各种内核实现了信号的触发和捕获,而ICON内核专门用于与边界扫描(Boundary Scan)管脚的通信。

使用ChipScope Pro工具的设计可以容易地同任何标准的FPGA设计流程结合起来,其中要用到标准的HDL综合工具和Xilinx ISE的实现工具,设计流程如图11.1所示。

ChipScope Pro图11.1 使用ChipScope Pro的设计流程用户可以使用ChipScope Pro 内核生成器生成的例示代码插入HDL源程序中,从而将ICON、ILA等内核插入到设计中(图11.1左);当然,也可以使用ChipScope Pro内核插入器将ICON、ILA等内核直接插入到已经综合完成的设计网表中(图11.1右)。

然后,利用Xilinx ISE 5.1i的综合工具进行综合布线,生成配置文件。

下一步,用户就可以通过ChipScope Pro分析仪软件将配置数据流下载到待测的器件中,进行分析测试。

11.2 ChipScope Pro Core Generator的使用11.2.1 ChipScope Pro Core Generator概述ChipScope Pro Core Generator可以用来生成如下内核:集成的控制内核(ICON)集成的逻辑分析仪内核(ILA)附带安捷伦跟踪内核的集成逻辑分析仪(ILA/ATC)用于片上外围总线内核分析的总线分析仪作为一个整体,我们称之为ChipScope Pro内核。

一旦生成了ChipScope Pro内核,就可以利用实例化的模板将它们作为元件插入到VHDL或Verilog设计中。

当完成例化元件的连接并综合后,就可以用Xilinx ISE软件将设计实现。

11.2.2 ICON内核的生成Core Generator允许用户在VHDL和Verilog设计中定义和生成一个所需要的ICON内核,来控制一个或多个ILA、ILA/ATC和IBA/OPB捕获内核。

当然可以根据需要定制控制端口的数量,以及用于JTAG连接的边界扫描元件。

当Core Generator确认了用户定义的参数都有效后,就会生成一个EDIF 网表文件(*.edn),一个网表约束文件(*.ncf)和用于合成的VHDL和Verilog例子代码。

这样,在常规的FPGA设计流程中就可以调用生成的ICON元件(Component),将其加入自己的设计。

打开Core Generator的第一个窗口如图11.2所示,可供选择要产生的内核。

选择ICON(Integrated Controller)并点击【Next】进入下一步。

图11.2 Core Generator内核类型选择窗口ICON内核的常规参数设置第二个窗口用来对ICON内核进行常规的参数设置,如图11.3所示。

图11.3 ICON内核常规参数设置窗口选择文件存放路径在【Output Netlist】一项选择生成ICON的EDIF文件(icon.edn)存放的路径。

默认的路径为Core Generator的安装路径,可以更改为FPGA设计路径。

选择目标器件类别根据设计所用的FPGA器件在【Device Fiamily】下进行相应选择,按此类别生成的ICON内核只能用于该系列的器件。

选择控制端口的数量一个ICON内核可以同时与多达15个ILA、ILA/ATC或IBA/OPB捕捉内核单元进行通信。

然而,一个单独的捕捉内核单元与其它任何单元都无法共享控制端口。

因此,ICON内核同样需要多达15个不同的控制端口来处理这种需求。

可以在【Number of Control Ports】的下拉列表中选择控制端口的数量。

禁止边界扫描组件在Virtex-II系列器件中,边界扫描的基本组件(BSCAN_VIRTEX2或BSCAN_VIRTEX)用来完成与JTAG边界扫描逻辑的通信。

边界扫描组件扩展了FPGA器件JTAG测试存取口(TAP)的接口,因此可以在FPGA内部建立最多两个扫描链。

ChipScope Pro Analyzer通过边界扫描组件提供的两个内部扫描链(USER1或USER2)中的一个实现与ChipScope Pro内核的通信。

由于ChipScope Pro内核并不需要使用边界扫描组件的全部两个内部扫描链,因此在用户的设计中可能将边界扫描组件与其他的组件共享,主要有以下两种共享方式:将边界扫描组件例化到ICON内核内部,并将未使用的边界扫描链信号作为ICON内核接口的端口信号。

将边界扫描组件例化到设计中的其他任何部分,并把USER1或USER2之一的扫描链信号对应到ICON内核接口的相应端口信号。

默认情况下边界扫描组件被例化到ICON内,可以选中【Disable Boundary Scan Component Instance】前的复选框来禁止边界扫描组件的例化。

选择边界扫描链ChipScope Pro Analyzer可以使用USER1或USER2边界扫描链之一与ChipScope Pro内核进行通信。

如果在上一选项中未禁止边界扫描链,就可以在【Boundary Scan Chain】选择其中之一。

禁止插入JTAG Clock BUFG如果未禁止边界扫描链,就允许在JTAG时钟信号上不插入BUFG元件。

如果在JTAG时钟信号上不插入BUFG元件,设计工具在实现时就可以用普通的资源为JTAG时钟布线,否则就会用到全局时钟资源。

缺省情况下JTAG时钟采用一个全局时钟资源(BUFG)布线。

使能未用到的边界扫描端口边界扫描本身有两副端口:USER1和USER2。

这两个端口提供了Virtex-II系列器件的边界扫描TAP 控制器的接口。

由于ICON内核只用其中的一个端口进行通信,另外一个未用到的就可以被设计中的其他单元使用。

如果选择【Enable Unused Boundary Scan Ports】,就提供了对未用到的USER1或USER2的访问。

设置例化模板参数选择了ICON内核的参数之后,就可以建立一个HDL例化模板。

点击【Next】就可以看到生成例化代码的选项(如图11.4所示),选择使用的综合工具和语言。

图11.4 示例代码生成参数的选择支持的综合工具有以下几种:Exemplar LeonardoSpectrumSynopsys FPGA CompilerSynopsys FPGA Compiler IISynopsys FPGA ExpressSynplicity SynplifyXST(Xilinx Synthesis Technology)前面设置的设计属性和参数就会根据不同的综合工具嵌入到HDL例化模板中。

选中【Generate Example File】前的复选框,就会生成ICON内核的示例文件。

生成ICON内核设置了前面各项参数之后,点击【Generate Core】就生成了EDIF网表、NCF约束文件和可用的例子代码。

这时会弹出一个消息窗口如图11.5所示,显示各步的信息。

用户可以返回重新设置参数,或者点击【Start Over】来产生新的内核,若要退出则直接单击窗口右上角的“关闭”按钮。

图11.5 完成ICON内核的生成使用ICON内核把生成的ICON核的HDL例子用到设计中,在将ICON内核的端口信号连接到其他信号上时应遵守以下原则:ICON的一组控制信号只能连接到一个ILA,ILA/ATC或IBA/OPB内核的控制端口不要将未用到的ICON核的控制端口悬空,否则设计工具实现时会报错。

因此,生成的ICON 内核的控制端口数应与ILA等内核的控制端口数一致11.2.3 ILA内核的生成使用ChipScope Pro Core Generator可以生成用户需要的ILA捕捉内核,以加入到HDL设计中。

可以定制触发端口的数量、宽度及其性能,也可以定制ILA核所存储的采样数据的最大数量,以及采样数据的宽度(可以大于触发端口的宽度,但必需包括触发信号)。

与生成ICON时一样,在图11.2中的单选框中选择ILA(Integrated Logic Analyzer),然后点击【Next】进入下一步。

常规参数设置与生成ICON的图11.3类似,包括存储路径,器件类别等。

ILA内核的触发参数设置设置完ILA核的常规参数后,进入触发参数设置窗口如图11.6所示。

图11.6 ILA内核的触发参数设置选择触发端口的数量每个ILA内核可以设置最多四个触发端口。

选择了触发端口的数量后,每个触发端口的参数选项就会列出来,TRIG0~3表示相应的触发端口。

触发端口的参数包括触发宽度、连接到触发端口的匹配单元(Match Unit)的数目,以及这些匹配单元的类型。

设置触发端口的宽度每个触发端口是由一组信号构成的总线。

组成一个触发端口的位数称为触发宽度。

每个触发端口的宽度可以在【Trigger Width】域分别设置,宽度范围为1到256。

设置触发匹配单元的数目匹配单元是连接到触发端口的一个比较器,用来检测这个触发端口的事件。

一个或多个匹配单元的结果组合在一起构成一个触发事件,用以控制数据的捕捉。