交通灯控制系统的设计

交通灯控制系统设计

交通灯控制系统设计1. 引言交通灯控制系统是城市交通管理的重要组成部分,通过控制交通灯的信号灯来指示车辆和行人通行状态,提高道路交通的安全性和效率。

本文将介绍一个交通灯控制系统的设计方案,包括系统的硬件组成、工作流程和功能实现。

2. 系统硬件设计2.1 控制器交通灯控制系统的核心是控制器,它负责接收输入信号,控制信号灯的状态,并输出相应的控制信号。

控制器通常由微控制器或可编程逻辑控制器(PLC)构成,具备较强的处理能力和控制灵活性。

2.2 信号灯信号灯是交通灯控制系统的输出设备,用于指示车辆和行人的通行状态。

典型的信号灯由红、黄、绿三个灯组成,红色表示停止、黄色表示准备、绿色表示通行。

2.3 传感器传感器用于获取与交通流量相关的信息,为交通灯控制系统提供输入数据。

常用的传感器包括车辆检测器、行人检测器和环境光传感器。

车辆检测器可以通过感应车辆的存在来调整交通灯的信号灯时间,行人检测器用于检测行人的存在并延长绿灯时间,环境光传感器可以根据光线强度自动调整信号灯的亮度。

2.4 通信设备交通灯控制系统通常需要与其他设备进行通信,例如与中心交通管理系统进行数据交换、与红绿灯时序控制器进行通信等。

为此,通信设备如无线模块、以太网接口等是必需的。

3. 系统工作流程交通灯控制系统的工作流程可分为以下几个步骤:1.接收输入信号:通过传感器获取交通流量、车辆和行人的信息。

2.状态判断:根据输入信号判断当前的交通状况,如车辆是否排队、行人是否需要过马路等。

3.灯光控制:根据判断结果,控制信号灯的状态。

例如,如果没有车辆和行人需要通行,则可以使所有信号灯都为红灯;如果有车辆排队等待通行,则根据交通流量调整绿灯的时间。

4.数据更新:根据交通灯状态的变化,更新相关的数据,如交通流量统计、时序控制参数等。

5.状态监测:监测信号灯的运行状态,定期检查硬件设备,如传感器和控制器的正常工作。

4. 功能实现交通灯控制系统主要具备以下功能:•信号灯的时序控制:根据交通流量和行人需求,动态调整信号灯的时序,以保证交通的流畅和安全。

智能交通灯控制系统的设计与实现

智能交通灯控制系统的设计与实现随着城市化进程的加速,城市道路交通越来越拥堵,交通管理成为城市发展的一个重要组成部分。

传统的交通信号灯只具备固定时序控制交通流量的功能,但随着技术的进步和智能化应用的出现,要求交通信号灯具备实时性、自适应性和智能化,因此,智能交通信号灯控制系统应运而生。

本文将从软硬件系统方面,详细介绍智能交通灯控制系统的设计与实现。

一、硬件设计智能交通灯控制系统的硬件部分由四个部分组成:单片机系统、交通灯控制器、传感器及联网模块。

1. 单片机系统单片机是智能交通灯控制系统的核心,该系统选用了8位单片机,主要实现红绿灯状态的自适应和切换。

在设计时,需要根据具体情况选择型号和板子,选择时需要考虑其开发环境、风险和稳定性等因素。

2. 交通灯控制器交通灯控制器是智能交通灯控制系统中的另一个重要部分,主要实现交通信号的灯光控制。

在控制器的设计时,需要考虑网络连接、通信、数据传输等多方面因素,确保系统的稳定性和可靠性。

3. 传感器传感器主要负责采集道路交通信息,包括车辆数量、速度、方向和道路状态等,从而让智能交通灯控制系统更好地运作。

传感器有多种类型,包括磁感应传感器、摄像头、光电传感器等,需要根据实际需求选择。

4. 联网模块联网模块主要负责智能交通灯控制系统的联网和数据传输,包括存储和处理车流数据、上传和下载数据等。

在设计时,需要考虑网络连接的稳定性、数据安全等因素,确保智能交通灯控制系统的连续性和可靠性。

二、软件设计智能交通灯控制系统的软件部分主要由两部分组成:嵌入式系统和上位机系统。

1. 嵌入式系统嵌入式系统是智能交通灯控制系统的主体,主要设计车流量检测、信号灯状态切换等程序。

为了保证系统的自适应性和实时性,需要采用实时操作系统,如FreeRTOS等。

在软件设计阶段,需要注意设计合理的算法和模型,确保系统的准确性和稳定性。

2. 上位机系统上位机系统主要实现智能交通灯控制系统的监控和管理,包括车流量监控、灯光状态监控、信号灯切换和日志记录等。

信号交通灯控制系统设计

信号交通灯控制系统设计1.系统简介信号交通灯控制系统设计旨在通过自动调节交通灯的控制策略,使得交通流量能够得到优化和平衡,并提高道路的通行效率。

该系统采用了一种基于传感器和通信技术的智能控制方法,能够根据实时交通状况自动调整信号灯的时序,使得交通能够更加顺畅。

2.系统原理该系统通过部署在道路上的传感器来获取实时的交通流量、车辆速度和车辆密度等信息。

这些传感器可以采用多种技术,比如地磁感应器、红外线传感器或摄像头等。

传感器采集到的数据将通过通信技术传输到信号控制中心,信号控制中心将根据收集到的数据来决定信号灯的显示时序。

3.系统功能3.1实时监测与数据采集:传感器能够实时监测道路上的交通状况,比如车辆流量、速度和密度等。

这些数据将被采集并传输到信号控制中心,作为交通灯时序调整的依据。

3.2智能信号灯控制:信号控制中心通过运算分析传感器采集到的数据,确定各个路口的交通情况,并相应地调整信号灯的时序。

比如,在高峰时段,信号控制中心可以将绿灯的时长适当延长,以增加道路的通行能力。

3.3优化交通流量:通过智能信号灯控制,系统能够根据实时交通状况进行灵活调整,优化交通流量的分配。

当其中一路口的交通流量过大时,系统可以将绿灯的时长相应延长,以避免交通拥堵。

3.4提高交通安全:该系统能够根据实时交通情况,自动识别道路上的交通事故或危险情况,并及时作出相应调整。

比如,当系统检测到其中一路段有车辆发生碰撞时,它可以及时调整信号灯的时序,保证其他车辆的安全通行。

4.系统优势4.1提高道路通行效率:通过智能信号灯控制,系统能够根据实时交通状况进行灵活调整,提高道路的通行能力和效率。

4.2降低交通拥堵和排放:该系统能够根据实时交通情况进行灵活调整,避免交通拥堵,减少排放量,降低环境污染。

4.3提升交通安全性:系统能够实时监测交通状况,并及时作出相应调整,减少交通事故的发生。

4.4节约能源消耗:系统通过灵活调整信号灯的时序,减少车辆的停等时间,降低燃油消耗和能源浪费。

交通灯控制系统毕业设计论文

交通灯控制系统毕业设计论文一、引言随着城市交通流量的日益增加,交通拥堵问题日益突出。

传统的交通灯控制方式已经不能有效地满足实际需求。

因此,设计一个智能化的交通灯控制系统成为了刻不容缓的任务。

二、设计目标本课题的目标是设计一个基于智能算法的交通灯控制系统,通过实时监测道路交通情况,合理分配交通信号时间,从而提高道路通行效率和交通安全性。

三、系统架构本交通灯控制系统包含以下几个模块:交通流量检测模块、信号控制模块、数据处理模块、用户界面模块等。

其中,交通流量检测模块通过摄像头、雷达等设备实时监测道路上的车辆情况;信号控制模块根据交通流量检测模块提供的数据,采用智能算法进行信号灯调度;数据处理模块负责对采集到的交通数据进行分析和处理;用户界面模块为用户提供交互操作界面,方便用户对系统进行配置和监控。

四、智能算法本设计采用基于遗传算法的交通灯控制方法。

遗传算法是一种模拟自然界的优化演化过程的计算方法,通过染色体编码和进化运算,能够在空间中找到最优解。

本设计将交通灯的时间分配看作一个优化问题,通过遗传算法进行优化求解,找到最优的信号灯控制方案。

五、设计流程1.数据采集:使用摄像头等设备实时采集道路上的交通数据。

2.数据预处理:对采集到的数据进行噪声去除、数据归一化等处理,以便进行后续的算法运算。

3.遗传算法初始化:根据系统要求和交通流量情况,初始化遗传算法的染色体编码、种群数量、交叉概率、变异概率等参数。

4.适应度评估:根据交通数据和设定的交通灯控制方案,评估每个个体的适应度,即信号灯控制方案的效果好坏。

5.选择、交叉和变异:根据适应度评估结果,选择适应度高的个体作为父代,通过交叉和变异操作生成新的个体。

6.迭代优化:重复进行适应度评估、选择、交叉和变异的操作,直到达到预设的停止条件。

7.生成最优解:经过多次迭代优化后,得到最优的交通灯控制方案。

六、结论通过本设计,成功地实现了一个基于智能算法的交通灯控制系统。

智能交通灯控制系统的设计与实现

智能交通灯控制系统的设计与实现一、引言随着城市交通的不断拥堵,智能交通灯控制系统的设计与实现成为改善交通流量、减少交通事故的关键。

本文将对智能交通灯控制系统的设计原理和实际应用进行深入探讨。

二、智能交通灯控制系统的设计原理智能交通灯控制系统的设计原理主要包括实时数据收集、交通流量分析和信号灯控制决策三个方面。

2.1 实时数据收集智能交通灯控制系统通过传感器、摄像头等设备实时采集车辆和行人的信息,包括车辆数量、车速、行人密度等。

这些数据可以通过无线通信技术传输到中央服务器进行处理。

2.2 交通流量分析在中央服务器上,通过对实时数据进行分析处理,可以得到不同道路的交通流量情况。

交通流量分析可以包括车辆流量、行人流量、车速和拥堵程度等指标,为后续的信号灯控制提供依据。

2.3 信号灯控制决策基于交通流量分析结果,智能交通灯控制系统可以根据交通状况智能地决定信号灯的开启和关闭时间。

优化的信号灯控制策略可以使车辆和行人的通行效率达到最大化。

三、智能交通灯控制系统的实现智能交通灯控制系统的实现需要使用计算机技术、通信技术和物联网技术等多种技术手段。

3.1 计算机技术的应用智能交通灯控制系统中的中央服务器需要配置高性能的计算机系统,以支持实时数据的处理和交通流量分析。

同时,通过计算机系统可以实现信号灯控制策略的优化算法。

3.2 通信技术的应用智能交通灯控制系统需要使用通信技术实现各个交通灯和中央服务器之间的数据传输。

传统的有线通信和无线通信技术都可以应用于智能交通灯控制系统中,以实现数据的实时传输。

3.3 物联网技术的应用智能交通灯控制系统可以通过物联网技术实现与交通工具和行人之间的连接。

车辆和行人可以通过智能终端设备向交通灯发送信号,交通灯可以实时地根据这些信号做出相应的决策。

四、智能交通灯控制系统的实际应用智能交通灯控制系统已经在一些城市得到了广泛的应用。

4.1 交通拥堵减少智能交通灯控制系统根据实时的交通流量情况,可以合理地分配交通信号灯的开启和关闭时间,从而避免了交通拥堵现象的发生,提高了道路的通行效率。

交通灯PLC控制系统设计

交通灯PLC控制系统设计交通灯是城市交通管理的重要组成部分,交通灯控制系统的设计对于保障交通安全和优化交通流量起着关键作用。

PLC(可编程逻辑控制器)技术在交通灯控制系统中得到了广泛应用,本文将从系统设计的整体框架、PLC程序设计、硬件选型以及系统特点等方面来详细介绍。

交通灯PLC控制系统设计的整体框架主要包括信号采集模块、信号处理模块、控制模块和执行模块四部分。

信号采集模块主要负责将交通流量、行人流量等信息转化为电信号输入给PLC控制器;信号处理模块对采集到的信号进行处理,如检测交通流量的高低以及行人通过的情况;控制模块根据信号处理结果,生成控制信号输出给执行模块;执行模块实现交通灯的控制,通过电路和执行器实现交通灯的开关。

PLC程序设计是交通灯PLC控制系统设计的核心部分,主要包括输入端口设置、控制逻辑设计、输出端口设置和通信设置等。

在输入端口设置中,确定采集到的数据类型和数据源,如交通流量和行人流量分别通过传感器采集。

控制逻辑设计是根据交通灯的状态和信号控制规则确定交通灯的控制方式,比如根据交通流量高低切换交通灯的状态。

输出端口设置是将确定好的控制信号输出到对应的执行模块,如输出信号控制交通灯的红绿灯状态。

通信设置是实现与其他相关系统的联动,如与监控系统的数据交互。

硬件选型是交通灯PLC控制系统设计的重要环节,主要包括PLC控制器、传感器、执行器和电源等。

PLC控制器应该具有高性能、稳定可靠的特点,能够满足交通灯控制系统的需求。

传感器的选型应基于交通流量和行人流量的检测需求,常用的有光电传感器、气压感应器等。

执行器的选型应根据交通灯的类型确定,如LED灯管、数码管等。

电源的选型应满足交通灯控制系统的供电需求,选用稳定可靠的电源。

交通灯PLC控制系统设计具有以下特点:灵活性高、可靠性强、实时性好。

PLC控制器的可编程性使得交通灯的控制逻辑可以根据实际需求进行灵活调整,满足不同时间段的交通流量要求。

PLC的智能交通灯控制系统设计..

PLC的智能交通灯控制系统设计--智能交通灯控制系统设计文档1-引言1-1 目的和范围本文档旨在设计一套基于PLC的智能交通灯控制系统,用于实现交通流畅和安全管理。

1-2 定义●PLC:可编程逻辑控制器(Programmable Logic Controller),是一种可编程数字运算控制器。

●智能交通灯:根据实时交通信息和需求,自动调整交通灯的信号显示。

●交通流畅:指通过合理的交通信号控制,减少交通拥堵和延误,提高交通效率。

●安全管理:通过合理的交通信号控制,确保道路交通的安全性和可靠性。

2-系统架构设计2-1 系统组成部分●PLC控制器●交通灯信号灯●交通检测传感器●人行横道信号灯●数据通信模块2-2 系统工作原理智能交通灯控制系统通过交通检测传感器获取实时交通信息,根据预设的控制算法,向信号灯发送指令来调整信号显示。

同时,通过数据通信模块与其他交通管理设备进行通信,实现跨路口协调控制。

3-系统硬件设计3-1 PLC控制器选型选择适宜的PLC控制器,满足系统的输入输出要求和性能需求。

3-2 交通灯信号灯设计根据道路交通需求和交通管理规范,设计合适的交通灯信号灯,包括信号显示颜色和亮度。

3-3 交通检测传感器选型选择适宜的交通检测传感器,可根据车辆和行人的实时情况,提供准确的交通流量数据。

3-4 人行横道信号灯设计根据行人需求和交通管理规范,设计合适的人行横道信号灯,保证行人安全过马路。

3-5 数据通信模块选型选择适宜的数据通信模块,实现系统与其他交通管理设备的数据交互和远程控制。

4-系统软件设计4-1 PLC编程使用PLC编程软件进行控制算法的编写,实现交通灯信号的动态调整。

4-2 信号灯控制算法设计设计合理的控制算法,根据实时交通信息和需求,动态调整交通灯信号显示。

4-3 数据通信协议设计设计系统与其他交通管理设备之间的数据通信协议,实现数据交互和远程控制。

5-系统测试与验证5-1 硬件测试对系统硬件进行功能测试,确保各部件正常工作。

面向物联网的智能交通灯控制系统设计

面向物联网的智能交通灯控制系统设计智能交通灯控制系统设计——为物联网时代的交通提供智慧解决方案概述随着物联网技术的快速发展,交通领域也迎来了巨大的变革。

传统的交通管理方式逐渐无法适应日益增长的交通流量和复杂的交通环境。

智能交通灯控制系统设计应运而生,致力于提供高效、安全、智慧的交通管理方案。

1. 引言智能交通灯控制系统是一种基于物联网技术的交通管理系统,通过数据采集、分析和处理,实现交通信号灯的智能控制。

本文将围绕智能交通灯控制系统的设计展开,讨论其意义、功能以及设计方案等内容。

2. 智能交通灯控制系统的意义智能交通灯控制系统在促进交通流畅、减少交通事故、提高交通效率等方面具有重要意义。

首先,通过实时数据采集和分析,系统可以根据交通流量合理调整交通信号灯的绿灯时间,提高道路吞吐量,缓解交通拥堵。

其次,系统可以实现智能化交通信号灯的配时调度,根据道路状况和交通需求进行实时调整,减少司机的等待时间,提高交通效率。

另外,系统还可以监测和控制交通信号设备的运行状态,及时发现故障并进行维护,保障道路交通的正常运行。

此外,智能交通灯控制系统的设计还可以帮助自治区交通管理部门进行交通流量预测和道路规划,优化交通布局。

3. 智能交通灯控制系统的功能智能交通灯控制系统具备多项实用功能,主要包括实时数据采集、交通信号配时、交通流量控制、交通事故预警和故障检测与维护等方面。

实时数据采集:通过各类传感器、监控摄像头等设备,系统可以实时采集道路交通流量、车辆类型、速度、方向等数据,并进行实时上传和处理。

交通信号配时:系统根据实时数据分析和预设算法,自动优化交通信号灯的配时方案,合理分配不同方向的绿灯时间,满足不同道路状况下的交通需求。

交通流量控制:通过智能识别和分析,系统可以根据交通流量的变化进行动态调整,提高道路的通行能力,减少交通拥堵。

交通事故预警:系统可以通过摄像头和传感器实时监测道路上的交通状况,识别可能发生的交通事故风险,并及时预警,减少交通事故发生的概率。

PLC的智能交通灯控制系统设计

PLC的智能交通灯控制系统设计智能交通灯控制系统设计是一种基于PLC技术的智能化交通管理系统,通过对交通信号灯控制进行智能化优化,实现交通流量的合理分配和交通管控的智能化管理,在提高道路通行效率的同时确保交通安全。

本文将介绍智能交通灯控制系统的设计理念、系统架构、功能模块、硬件设备和软件编程等方面。

一、设计理念智能交通灯控制系统的设计理念是通过PLC技术实现对交通信号灯的智能控制,根据车辆流量和道路情况实时调整信号灯的变化,合理分配绿灯时间,优化交通信号配时方案,提高道路通行效率和交通安全性。

系统应具有智能化、自适应性和实时响应性,能够有效应对不同交通情况,提供个性化的交通管控解决方案。

二、系统架构智能交通灯控制系统的架构主要包括传感器模块、PLC控制器、交通信号灯、通信模块和监控终端等部分。

传感器模块用于感知道路上的车辆流量和行驶方向等信息,将数据传输给PLC控制器;PLC控制器根据传感器数据实时调整信号灯控制策略;交通信号灯根据PLC控制器的指令变化显示不同颜色信号;通信模块用于系统与监控终端之间的数据通信,监控终端用于监控系统运行状态和实时操作。

三、功能模块智能交通灯控制系统的功能模块包括车辆检测模块、信号灯控制模块、通信模块和监控模块等。

车辆检测模块通过车辆检测器实时感知道路上的车辆流量和行驶方向等信息;信号灯控制模块根据车辆检测模块的数据智能调整信号灯配时,实现绿灯优先和拥堵车辆识别等功能;通信模块提供系统与监控终端之间的数据传输通道,实现数据交换和远程监控;监控模块实时监测系统运行状态和信号灯显示情况,可对系统进行远程操作和管理。

四、硬件设备智能交通灯控制系统的硬件设备主要包括传感器、PLC控制器、交通信号灯、通信模块和监控终端等部分。

传感器用于感知车辆流量和行驶方向等信息;PLC控制器用于处理传感器数据,实现信号灯的智能控制;交通信号灯显示不同颜色信号,指示不同车辆通行状态;通信模块提供系统与监控终端之间的数据传输通道;监控终端用于监控系统运行状态和实时操作。

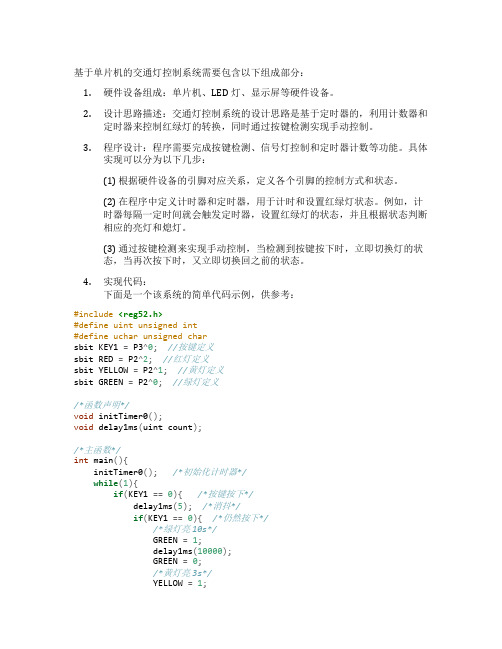

基于单片机的交通灯控制系统设计与实现

基于单片机的交通灯控制系统需要包含以下组成部分:1.硬件设备组成:单片机、LED 灯、显示屏等硬件设备。

2.设计思路描述:交通灯控制系统的设计思路是基于定时器的,利用计数器和定时器来控制红绿灯的转换,同时通过按键检测实现手动控制。

3.程序设计:程序需要完成按键检测、信号灯控制和定时器计数等功能。

具体实现可以分为以下几步:(1) 根据硬件设备的引脚对应关系,定义各个引脚的控制方式和状态。

(2) 在程序中定义计时器和定时器,用于计时和设置红绿灯状态。

例如,计时器每隔一定时间就会触发定时器,设置红绿灯的状态,并且根据状态判断相应的亮灯和熄灯。

(3) 通过按键检测来实现手动控制,当检测到按键按下时,立即切换灯的状态,当再次按下时,又立即切换回之前的状态。

4.实现代码:下面是一个该系统的简单代码示例,供参考:#include <reg52.h>#define uint unsigned int#define uchar unsigned charsbit KEY1 = P3^0;//按键定义sbit RED = P2^2;//红灯定义sbit YELLOW = P2^1;//黄灯定义sbit GREEN = P2^0;//绿灯定义/*函数声明*/void initTimer0();void delay1ms(uint count);/*主函数*/int main(){initTimer0();/*初始化计时器*/while(1){if(KEY1 ==0){/*按键按下*/delay1ms(5);/*消抖*/if(KEY1 ==0){/*仍然按下*//*绿灯亮10s*/GREEN =1;delay1ms(10000);GREEN =0;/*黄灯亮3s*/YELLOW =1;delay1ms(3000);YELLOW =0;/*红灯亮7s*/RED =1;delay1ms(7000);RED =0;/*黄灯亮2s*/YELLOW =1;delay1ms(2000);YELLOW =0;}}}return0;}/*函数定义*/void initTimer0(){TMOD &=0xF0;TMOD |=0x01;TH0 =0xFC;TL0 =0x18;EA =1;ET0 =1;TR0 =1;}/*1ms延时函数*/void delay1ms(uint count){uint i,j;for(i=0;i<count;i++){for(j=0;j<125;j++){}}}/*计时器中断函数*/void timer0() interrupt 1{TH0 =0xFC;TL0 =0x18;}以上是一个简单的基于单片机的交通灯控制系统设计与实现示例。

智能交通灯控制系统设计

智能交通灯控制系统设计

1. 介绍

智能交通灯控制系统是一种基于现代技术的交通管理系统,旨在提高交通效率、减少交通拥堵和事故发生率。

本文将探讨智能交通灯控制系统的设计原理、功能模块和实现方法。

2. 设计原理

智能交通灯控制系统的设计原理主要包括以下几个方面: - 传感器检测:通过各类传感器实时监测路口车辆和行人情况,获取交通流量信息。

- 数据处理:将传感器采集到的数据经过处理分析,确定交通信号灯的相位和时长。

- 控制策略:根据不同情况制定合理的交通信号灯控制策略,优化交通流动。

3. 功能模块

智能交通灯控制系统通常包括以下几个功能模块: - 传感器模块:负责采集交通流量数据,如车辆和行人信息。

- 数据处理模块:对传

感器采集的数据进行处理和分析,生成交通控制方案。

- 控制模块:

实现交通信号灯的控制,根据控制策略调整信号灯状态。

- 通信模块:与其他交通设备或中心平台进行通信,实现数据共享和协调控制。

4. 实现方法

实现智能交通灯控制系统主要有以下几种方法: - 基于传统控制

算法:采用定时控制、车辆感应等方式设计交通灯控制系统。

- 基于

人工智能:利用深度学习等技术处理大量数据,实现智能化交通灯控制。

- 基于物联网技术:通过物联网技术实现交通信号灯与其他设备

的连接和信息共享,提高交通系统的整体效率。

5. 结论

智能交通灯控制系统的设计可以有效优化交通信号灯的控制策略,提高交通效率和安全性。

结合现代技术的发展,智能交通灯控制系统

将在未来得到更广泛的应用和发展。

交通灯PLC控制系统设计

交通灯PLC控制系统设计摘要:本文介绍了交通灯PLC控制系统的设计。

交通灯是城市交通管理中的重要设备,它能有效协调交通流量,提高道路通行效率和安全性。

本文以PLC控制系统为基础,设计了一个简单的交通灯控制系统,包括信号灯的控制逻辑、PLC程序的编写和硬件连接等。

关键词:交通灯;PLC控制系统;信号灯;程序编写1.引言交通拥堵一直是城市发展中的一个重要问题。

为了有效管理交通流量,提高道路通行效率和安全性,交通灯被广泛应用于路口和人行横道等交通场所。

交通灯通过控制不同车辆和行人的通行时间来协调交通流量,确保道路交通的顺畅。

传统的交通灯控制方式多采用电路控制或计时器控制,这种方式存在控制逻辑复杂、维护困难等问题。

而PLC控制系统采用可编程控制器(PLC)作为控制核心,具有功能强大、操作灵活、易于扩展等优点,逐渐成为现代交通灯控制的主流方式。

本文将介绍一个基于PLC控制系统的交通灯控制系统。

首先介绍交通灯的基本原理和工作方式,然后详细设计PLC程序和硬件连接,最后进行系统测试和验证。

2.交通灯工作原理交通灯主要由红灯、黄灯和绿灯组成。

不同颜色的灯泡代表不同的信号状态,用来指示不同类型车辆和行人的通行情况。

当绿灯亮起时,表示允许车辆通行;当红灯亮起时,表示禁止车辆通行;当黄灯亮起时,表示信号即将变换,要求车辆减速停车。

通过不同颜色的灯泡的组合和闪烁,可以实现不同的交通信号。

交通灯的控制逻辑一般采用有限状态机(FSM)来描述,包括不同状态之间的转换条件和动作执行。

常见的状态包括绿灯状态、红灯状态、黄灯状态等。

3.PLC程序设计在设计交通灯控制系统的PLC程序时,需要将交通灯的控制逻辑转化为PLC指令,以实现信号灯的控制。

下面以一个简单的路口为例,介绍PLC程序的编写。

首先定义输入和输出变量,如IN1表示车辆检测器信号,OUT1表示绿灯输出信号,OUT2表示红灯输出信号,OUT3表示黄灯输出信号。

然后编写控制逻辑,包括输入信号的检测和输出信号的控制。

智能交通灯PLC控制系统的设计

智能交通灯PLC控制系统的设计一、本文概述随着城市化的快速发展,交通拥堵和交通事故的问题日益严重,智能交通系统因此应运而生。

作为智能交通系统的重要组成部分,智能交通灯控制系统在提高道路通行效率、保障交通安全方面发挥着至关重要的作用。

本文将对基于PLC(可编程逻辑控制器)的智能交通灯控制系统设计进行深入探讨,旨在通过技术创新提高交通管理效率,优化城市交通环境。

本文将首先介绍智能交通灯PLC控制系统的基本概念和原理,阐述其相较于传统交通灯控制系统的优势。

接着,将详细论述系统的设计过程,包括硬件选型、软件编程、系统架构搭建等关键环节。

还将探讨该系统的实际应用效果,分析其对交通流量、交通安全等方面的影响。

通过本文的研究,期望能够为智能交通灯PLC控制系统的设计提供有益的参考和借鉴,推动城市交通管理向更加智能化、高效化的方向发展。

也希望本文的研究能够为相关领域的技术创新和应用提供有益的启示和思路。

二、PLC基础知识介绍可编程逻辑控制器(Programmable Logic Controller,简称PLC)是一种专为工业环境设计的数字运算电子系统,用于实现逻辑控制、顺序控制、定时、计数和算术运算等操作的指令,并通过数字或模拟的输入/输出控制各种类型的机械设备或生产过程。

自20世纪60年代诞生以来,PLC以其高可靠性、强大的功能、灵活的配置和易于编程的特点,在工业控制领域得到了广泛应用。

PLC的基本结构主要包括中央处理器(CPU)、存储器、输入/输出(I/O)接口、电源以及通信接口等部分。

其中,CPU是PLC的核心,负责执行用户程序、处理数据、控制I/O接口等任务;存储器用于存储系统程序、用户程序及工作数据;I/O接口用于与外部的输入/输出设备连接,实现与外部世界的交互;电源为PLC提供稳定的工作电压;通信接口则用于PLC与其他设备或系统的数据交换和通信。

PLC的编程语言主要有梯形图(Ladder Diagram)、指令表(Instruction List)、功能块图(Function Block Diagram)等,这些语言直观、易学,方便工程师进行编程和调试。

交通灯控制系统设计-实验报告

交通灯控制系统设计-实验报告

实验目的:设计一个交通灯控制系统,实现对交通灯的自动控制。

实验材料:

1. Arduino UNO开发板

2. 红绿黄LED灯各1个

3. 杜邦线若干

实验原理:

交通灯系统的控制主要是通过控制LED灯的亮灭来实现。

红

色LED灯表示停止,绿色LED灯表示通行,黄色LED灯表

示警示。

通过控制不同LED灯的亮灭状态,可以模拟交通灯

的不同信号。

实验步骤:

1. 将红色LED灯连接到Arduino开发板的数字输出引脚13,

绿色LED灯连接到数字输出引脚12,黄色LED灯连接到数

字输出引脚11。

2. 在Arduino开发环境中编写控制交通灯的程序。

3. 将Arduino开发板与计算机连接,将程序上传到Arduino开

发板中。

4. 接通Arduino开发板的电源,观察交通灯的亮灭状态。

实验结果:

根据程序编写的逻辑,交通灯会按照规定的时间间隔进行变换,实现红绿灯的循环。

实验总结:

通过本次实验,我们设计并实现了一个简单的交通灯控制系统。

掌握了Arduino编程和控制LED灯的方法,加深了对控制系

统的理解。

通过实验,我们发现了交通灯控制系统的重要性和意义,为今后的交通控制提供了一种可行的解决方案。

智能交通灯管理系统的设计和实现

智能交通灯管理系统的设计和实现随着人们生活水平的提高,城市内的机动车数量以及人员流量越来越大,为了保障交通的安全与便捷,智能交通灯管理系统应运而生。

一、设计目的智能交通灯管理系统旨在提供全面的交通管控方案,包括车辆与行人流量的监测、智能绿灯时间的调配及异常情况处理。

其设计目的主要包括以下方面:1.提高交通流量的效率,缓解交通拥堵问题;2.提升交通安全水平,降低交通事故发生率;3.智能化管理,让公共交通更便捷、更经济。

二、设计要点交通灯控制系统是智能交通灯管理系统中最为重要的组成部分之一,其设计要点如下:1.车辆或行人流量监测传感器的安装,以物联网技术进行相互连接;2.建立基于流量检测的交通管理模型,实现对路口互动信息的监测及分析;3.对路口交通信息进行分析,实时计算绿灯时间,并根据交通流量实时调配绿灯时间,以实现绿灯变换更加科学合理;4.针对复杂路口,对智能交通灯控制系统进行优化升级,提高交通流量效率。

三、实现方法智能交通灯管理系统的实现方法大致可以分为以下几个步骤:1.使用传感器捕捉路口的行人和车辆数据,将数据传输到后端系统数据处理系统;2.在后端数据处理系统中,使用大数据分析技术对传感器收集数据进行分析;3.在数据分析阶段,系统会根据路口流量状况设计最优的路口信号时间表;4.通过这样的优化,绿灯时间将会更加合适,不仅缓解了路口拥堵,还提高了交通生产力;5.系统持续进行数据的分析和优化,以逐步优化路口信号的性能和效率。

四、优点及前景智能交通灯管理系统相对于传统的交通灯控制系统,具有以下优点:1.更加科学合理,绿灯时间更加准确、合理而且比较符合实际;2.实时监测路口的交通流量、车辆与行人,及时采取最适宜的灯光变换方案;3.减少路口拥堵情况,提升了交通流量效率,缩短了人们等待的时间。

随着智能技术的迅速发展,智能交通灯管理系统在未来有着广阔的前景和市场。

未来智能交通灯管理系统将会成为人们日常交通中不可或缺的一部分,并成为城市智能化建设的基石之一。

交通灯控制系统的设计

1.3 系统设计

框图设计

基于AT89C51单片机的交通信号控制系统由电源电路、单片 机主控电路、按键控制电路、时钟电路、复位电路和数码管

显示电路几部分组成,框图所示。

系统原理

单片机设计交通灯控制系统,可用单片机直接控制 信号灯的状态变化,指挥交通的具体通行。当然,接 入 LED数码管就可以显示倒计时,以提醒行使者, 更具人性化。

Hale Waihona Puke 晶振电路复位电路系统刚上电时,单片机内部的程序还没有开始执行,需要一 段准备时间,也就是复位时间。一个稳定的单片机系统必须设 计复位电路。当程序跑飞或死机时,也需要进行系统复位。复 位电路有很多种,有上电复位,手动复位等。

按键电路

本设计设置了有 4个 键: (1)、S1 键设置按键。 (2)、S2键为增加时间按 键。 (3)、 S3 键为减少时间按 键。 (4)、S4键为模式切换按键。

(4) 通过单片机的P3.0位来控制系统是工作或设 置初值,当为0就对系统进行初始化,为1系统就 开始工作。

元件清单

软件设计

总体流程图

1.6 系统仿真及调试

基于AT89 C51单片机的交通信号灯控制系统仿真过程参考附 录C。交通信号与控制状态仿真结果。

单片机系统的硬件调试和软件调试是不能分开的,许多硬件 错误是在软件调试过程中被发现和纠正的。但通常是先排除 明显的硬件故障以后,再和软件结合起来调试以进一步排除 故障。可见硬件的调试是基础,如果硬件调试不通过,软件 设计则无从谈起。

基于物联网技术的智能交通灯控制系统设计

基于物联网技术的智能交通灯控制系统设计在当今社会,智能交通系统正在成为城市交通管理的重要组成部分。

随着人口的不断增长和车辆数量的剧增,传统的交通信号灯已无法满足日益增长的交通需求。

因此,基于物联网技术的智能交通灯控制系统的设计变得至关重要。

一、设计目标智能交通灯控制系统的设计目标是提高交通流畅性,减少交通事故,并提高交通效率。

该系统旨在通过智能化的信号控制,根据实际道路状况来分配交通信号,以实现路口交通的有效管理。

二、系统架构智能交通灯控制系统包括传感器节点、通信模块、控制中心和交通信号灯组成。

1. 传感器节点:传感器节点用于实时监测交通流量、车辆速度和道路状况等变量。

通过使用车辆检测器、红外线传感器、摄像头等技术,传感器节点可以获取精确的交通数据,为系统提供决策依据。

2. 通信模块:通信模块负责将传感器节点收集到的数据传输给控制中心。

采用无线通信技术,如Wi-Fi、蓝牙或LoRa 等,可以实现节点之间的远程通信,并确保传输的即时性和可靠性。

3. 控制中心:控制中心是智能交通灯控制系统的核心部分,负责数据处理和信号控制策略的制定。

通过收集和分析传感器节点的数据,控制中心可以根据交通流量、车辆速度等信息,智能地调整交通信号灯的时序和时长。

4. 交通信号灯:交通信号灯作为系统的输出设备,根据控制中心的指令进行灯光切换。

准确的信号控制可以提高交通效率,缓解交通拥堵,降低事故风险。

三、系统工作流程智能交通灯控制系统的工作流程如下:1. 传感器节点实时监测道路上的交通流量、车辆速度和道路状况等数据,并通过通信模块将数据传输到控制中心。

2. 控制中心接收并分析传感器节点的数据,根据交通流量、车辆速度等情况,制定合理的信号控制策略。

3. 控制中心将信号控制指令发送给交通信号灯,控制灯光的切换。

4. 交通信号灯根据控制中心的指令改变灯光状态,实现智能化的信号控制。

四、设计考虑因素在智能交通灯控制系统的设计过程中,需要考虑以下因素:1. 交通流量:通过传感器节点的数据采集,系统需要实时监测和分析交通流量,在高峰期合理调整信号时序,以提高交通效率。

单片机控制的交通灯控制系统设计

单片机控制的交通灯控制系统设计交通灯控制系统是现代城市交通管理的重要组成部分,通过对交通流量的调控,保障道路的交通安全和通行效率。

本文将介绍一个基于单片机的交通灯控制系统的设计。

首先,我们需要确定该交通灯控制系统的基本功能和设计要求。

在设计过程中,我们考虑以下几点:1.确定交通灯的工作模式:根据不同的交通流量,交通灯可以设置为定时模式或感应模式。

2.支持不同交通流量的调节:根据交通流量的变化,交通灯系统需要能够自动调整红绿灯的时间间隔。

3.考虑交通信号的同步问题:为了确保交通流畅,不同路口的交通灯信号需要同步。

4.灯光状态显示:系统需要实时显示交通灯的状态,方便交通参与者了解当前交通情况。

基于以上基本要求,我们可以进行以下设计:1.硬件方案:a.单片机选择:选择适合的单片机作为核心控制器。

一般选择性能较强的ARM单片机,如STM32系列。

b.光电传感器:用于检测车辆和行人的存在,以实现感应模式。

通过光电传感器的输出信号,控制交通灯灯组的切换。

c.信号灯:根据交通需要,设置红、黄、绿三色信号灯。

d.显示屏:用于显示交通灯的状态,实时反馈给交通参与者。

e.供电和保护电路:为系统提供稳定的电源和电路保护。

2.软件方案:a.初始化设置:根据实际道路布局和交通流量情况,设定交通灯的初始调节参数。

b.交通信号控制:根据交通流量和光电传感器的反馈信息,控制交通灯灯组的切换,并实现不同模式的调节。

c.信号同步:通过与其他交通灯系统的交互,实现不同路口的交通信号同步,避免交通拥堵和事故发生。

d.状态显示:通过显示屏实时显示交通灯的状态,方便行人和驾驶员了解道路交通情况。

在完成硬件和软件的设计后,需要进行系统的测试和优化。

通过不断的测试和实验,对交通灯控制系统的参数进行调整和优化,以达到最佳的交通通行效率。

本文提出了一个基于单片机的交通灯控制系统的设计方案,通过硬件和软件的协同工作,能够根据交通流量的变化,自动调节交通灯的时间间隔,实现交通信号的同步,并通过显示屏实时显示交通灯的状态。

交通灯控制系统设计报告

交通灯控制系统设计报告一、引言二、设计目标1.提高交通状况:通过合理的信号配时和交通流量控制,缓解交通堵塞,减少交通拥堵现象。

2.保障交通安全:确保行人和车辆能够按规定时间通行,减少交通事故的发生。

3.提高道路利用率:根据道路情况和交通流量,合理调整信号配时,提高道路通行效率。

三、设计原理1.信号配时根据不同时段的交通流量需求,采用动态信号配时方案,实现信号随交通流量变化而变化。

2.检测系统通过传感器等设备对交通流量、车辆行驶速度等进行检测,实时获取交通状况。

3.系统控制根据检测到的交通状况和预设的预案,对交通灯进行实时控制,优化信号配时。

四、设计方案1.信号配时方案根据平峰期、高峰期和低峰期的交通流量,采取不同的信号配时策略。

低峰期信号配时较短,高峰期信号配时较长,平峰期则根据实时交通流量进行动态调整。

2.检测系统设计搭建检测系统,采用传感器等设备对交通流量、行驶速度进行实时监测,将数据传输给控制系统,为信号配时提供依据。

3.控制系统设计设计控制系统,将检测到的数据进行分析和处理,根据预设的算法和策略,实现实时调整交通灯的信号配时。

五、实施计划1.设计和搭建检测系统,选择合适的传感器和设备,进行安装和调试。

预计完成时间为一个月。

2.设计和开发控制系统,包括信号配时算法和策略,并进行功能测试和调整。

预计完成时间为两个月。

3.将检测系统和控制系统进行整合,并进行联调测试和性能优化。

预计完成时间为一个月。

4.在交叉口或拥堵较为严重的路段进行试运行,并根据实际情况调整信号配时参数。

预计试运行时间为一个月。

5.完成系统的正式发布,并进行长期监测和调优,根据实时交通状况和用户反馈进行优化和改进。

六、总结通过本次交通灯控制系统的设计和实施,能够有效改善城市交通状况,提高道路利用率和交通安全性。

本设计方案将根据实际情况进行实施,确保系统的高效可靠运行,并根据实时数据进行调整和优化。

希望本报告能够为交通管理部门提供有价值的参考,并为城市交通发展做出贡献。

交通灯控制系统的设计

添加标题

交通灯控制系统由红、 黄、绿三种颜色的信 号灯组成,用于指示 车辆和行人的行驶状

态。

添加标题

交通灯控制系统的基 本工作原理是通过控 制信号灯的亮灭顺序 和时间间隔,来调节 交通流量,保障交通

安全和顺畅。

添加标题

红灯表示停止,黄灯 表示准备停车,绿灯 表示通行。在每个信 号周期中,每个方向 的信号灯按照预定的 时间间隔交替亮灭。

电源模块:为 整个交通灯控 制系统提供稳 定的电源,保 证系统的正常

运行。

信号采集模块: 采集交通路口 的车流量、人 流量等信息, 为系统提供决

策依据。

控制器模块: 根据采集到的 信号,控制交 通灯的亮灭时 间,实现交通 路口的智能化

管理。

显示模块:实 时显示交通路 口的车流、人 流等信息,方 便驾驶员和行 人了解交通情

况。

交通灯控制系统的软件设计

信号采集与处理算法

数据处理:对采集到的数据 进行处理,包括去噪、滤波 等操作

信号采集:实时监测交通流 量、车速等数据

算法实现:采用合适的算法 实现信号控制,如模糊控制、

神经网络等

优化与调试:对算法进行优 化和调试,提高控制精度和

稳定性

交通灯控制策略

定时控制:根据预 设的时间间隔控制 交通灯的亮灭

优化手段:算法改进、代码 优化、系统架构调整等

交通灯控制系统的应用与实现

实际应用场景与需求分析

城市交通路口:控制交通 流量,保障交通安全

高速公路:调节车流速度, 减少交通事故

铁路平交道口:确保铁路 与道路交通的安全转换

校园安全:规范车辆和行 人通行,保障师生安全

系统实现方案与技术路线

实现方案:采用嵌入式系统技术,将交通灯控制系统集成在嵌入式设备中, 实现智能化控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《微型计算机技术》课程设计报告题目交通灯控制系统的设计作者xx班级xx学号xx指导教师xx2005 年6月20日《微型计算机技术》课程设计报告题目交通灯控制系统的设计作者xx班级xx学号xx指导教师xx2005 年6月20日目录第一部分:微机硬件结构组成及原理知识---------------------------------------------------- 2第二部分:微型计算机应用的系统设计------------------------------------------------------- 5一、要求-------------------------------------------------------------------------------- 5二、目的--------------------------------------------------------------------- 5三、内容设计与步骤------------------------------------------------------ 5四、设计结果与分析------------------------------------------------------ 10五、设计体会--------------------------------------------------------------- 10六、感谢--------------------------------------------------------------------- 10第一部分微机硬件结构组成及原理知识一、处理器、微型计算机和微型计算机系统的关系:微处理器是指由一片大规模集成电路组成的中央处理器。

微型计算机是指以微处理器为基础,配以内存储器以及输入输出接口电路和相应的辅助电路而构成的裸机。

微型计算机系统是指由微型计算机配有相应的外围设备(如打印机、显示器、磁盘机、磁带机等)及其它专用电路、面板、电源、机架以及足够的软件而构成的系统。

三者之间的关系如下:运算器微处理器控制器寄存器组微型计算机内存储器输入/输出接口微型计算机系统输入/输出设备及外存储器系统软件应用软件电源、面板和机架等二、8086到PentiumIII的发展历程中微处理器发展的特点:1、8086微处理器包括两个独立功能部件:总线接口部件(BIU)、执行部件(EX)。

2、80286微处理器包括四个功能部件:地址部件(AU)、指令部件(IU)、执行部件(EU)、总线部件(BU)。

3、80386微处理器包括六大部件:总线接口部件(BIU)、指令预取部件(IPU)、指令预译码部件(IDU)、执行部件(EU)、分段部件(SU)、分页部件(PU)。

4、80486 微处理器采用了CASH 技术,包括八大部件:总线接口部件(BIU)、指令预取部件(IPU)、指令预译码部件(IDU)、执行部件(EU)、控制部件(CU)、存储管理部件(MMU)、超高速缓冲存储器(CASH)、高性能浮点处理部件(FPU)。

5、Pentium增加了超标量流水线、独立的指令和数据CASH 、重新设计了浮点部件、分支预测技术。

6、PII的特点是增加了三维图象和多媒体方面的可视化。

7、PIII增加了如指掌0条浮点多媒体指令和8个128位单精度寄存器,适用于移动PC。

三、CPU与存储器的接口技术及三种译码方式的优点:1、CPU的带负载能力通常CPU的总线负载能力为一个TTL器件或20个MOS器件,当总线上挂接的器件超过上述规定时,应考虑总线的驱动能力问题。

2、CPU时序与存储器芯片存取速度的配合问题CPU在存储器读写周期中读写时间要大于所选择的存储器芯片规定的时间,需要设计一个插入等待TW周期电路,使之CPU时序能与存储器存取速度相匹配。

3、地址线的连接存储器的容量与地址线的条数有关,由于片存储器芯片的容量是有限的,因此,需要组成一个大容量的存储模块,通常需要几片或几十片存储芯片三种译码方式:①全译码:输出有效状态对应唯一的高位地址. 特点:无地址重叠,接线多;②部分译码:输出有高位地址没有参加译码. 特点:有地址重叠;③线选译码:输出有更多高位地址没有参加译码.特点:地址重叠最严重。

四、CPU通过三总线(地址总线、数据总线、控制总线)与外设进行的三种信息(数据信息、状态信息、控制信息)的交换:数据信息、状态信息、控制信息通常以数据形式通过CPU的数据总线(微机总线)同CPU进行传送的,这些信息分别存放在外设接口的不同类型的寄存器(端口)中.CPU同外设之间的信息传送实质上是对数据口,状态口,控制口进行读,写操作。

五、I/O接口电路的电路单元组成:I/O接口电路应具有以下电路单元:输入/输出数据锁存器和缓冲器,控制命令和状态寄存器,地址译码器,读写控制逻辑,中断控制逻辑。

六、8255A工作于方式0与方式1的区别:方式0:基本的输入/输出方式,三个端口都可以由程序规定为输入/输出方式,但不能既为输入有为输出,也没有固定的联络信号;各端口在输出方式下有锁存功能,输入不能。

方式1:选通输入/输出方式,A,B口作为输入或输出口都有锁存功能。

七、8255A在工作方式1输入时的过程:(A口)当外设准备好数据,在送出数据的同时,送出一个选通信号STB.8255A 的A口数据锁存器在STB下降沿将数据锁存.8255A向外设送出高电平的IBF,表示锁存数据已完成,暂时不要再送数据.如果INTE==1,这时就会使INTR变成高电平输出,向CPU发出中断请求,而RD结束时的上升沿则使IBF复位到零.外设在检测到IBF为零后,可以开始输入下一个字节。

八、8255A在工作方式1输出时的过程:当OBF低电平有效时,CPU已将数据输出到制定的端口,ACK低电平有效时,外设接受数据,INTR端口向CPU发出中断请求,请求CPU再输出后面的数据。

第二部分微型计算机应用的系统设计题目:交通灯控制系统设计一、要求设计一个十字路口的交通灯控制系统。

南北东西四个方向:南北口绿灯亮,东西红灯亮,南北方向通车,时间为20秒;南北口绿灯灭,黄灯开始闪烁5秒,红灯亮,东西口红灯灭,绿灯亮,东西口方向通车,时间为20秒;东西口绿灯灭,黄灯闪烁5秒,红灯亮,南北口红灯灭,黄灯开始闪烁5秒,绿灯亮,南北口通车,以此类推循环运行,按任意键停止。

若有紧急情况,四个路口红灯全亮,紧急车通过时间为本10秒。

二、目的应用、掌握接口芯片与中断技术的硬件电路组成及中断处理程序等软件的编制方法。

三、内容设计与步骤用实验箱上的发光二级管模拟十字路口交通灯信号。

用可编程并行接口芯片8255A来实现该设计。

8255A的B口和C口控制12个LED发光二极管的亮、灭(“0”亮,“1”灭)。

(1) 8255A介绍Intel 8255A是一种通过的可编程序并行I/O接口芯片,又称为“可编程外设接口芯片”,是为Intel 8080/8085系列微处理器设计的,也可用于其他系列的微机系统。

可由程序来改变其功能,通用性强,使用灵活。

通过8255A,CPU可直接同外设相连,是应用最广的并行I/O接口芯片。

8255A的内部结构由四部分组成,数据总线缓冲器,三个8位端口PA、PB和PC,A组和B组的控制电路,读/写控制逻辑。

(2) 并行接口硬件连线如图所示(见下页)图1. 并行接口连线图(3)三个端口均工作于方式0,处于输出状态(4)8255A A口地址为218H,B口地址为219H,C口为21AH,控制端口地址为21BH(5)程序代码DATA SEGMENTPB DB ?MESS DB …Enter any key can exit to DOS!‟,0DH,0AH,‟$‟DATA ENDSSTACK SEGMENTSTA DWTOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS: CODE, DS:DATA, SS:STACK START : MOV AX, DATAMOV DS, AXMOV ES, AXMOV AH, 09HMOV DX,OFFSET MESSINT 21HMOV DX,21BHMOV AL,82HOUT DX,ALMOV DX,219HIN AL,DXMOV PB,ALMOV DX,21BHMOV AL,80HOUT DX,ALMOV DX,219HMOV AL,PBOR AL,0F0HOUT DX,AL 黄灯亮MOV DX,21AHMOV AL,0F0H 红灯亮OUT DX,ALCALL DELAY10PRT0:MOV AL,10100101B 南北方向绿灯亮MOV DX,21AHOUT DX,ALCALL DELAY10CALL DELAY10OR AL,0F0H 南北方向绿灯灭OUT DX,ALMOV CX,000AHPRT1:MOV DX,219HMOV AL,PBAND AL,10101111B 南北方向黄灯亮OUT DX,ALCALL DELAY1OR AL,01010000BOUT DX,AL 南北方向黄灯灭CALL DELAY1LOOP PRT1MOV DX,21AHMOV AL,0F0HOUT DX,ALCALL DELAY1MOV AL,01011010BOUT DX,AL 东西方向绿灯亮,南北方向红灯亮CALL DELAY10CALL DELAY10OR AL,0F0HOUT DX,ALMOV CX,0008HPRT2: MOV DX,219HMOV AL,PBAND AL,01011111BOUT DX,AL 东西方向黄灯亮CALL DLAY1OR AL,10100000BOUT DX,ALCALL DELAY1LOOP PAT2MOV DX,21AHMOV AL,0F0HOUT DX,ALCALL DELAY1MOV AH,06HMOV DL,0FFHINT 21HJNZ PRT3JMP PRT0PRT3:MOV AX,4C00HINT 21HDELAY1 PROC NEARPUSH CXMOV CX,8000HCCC:LOOP CCCPOP CXRETDELAY1 ENDPDELAY10 PROC NEARPUSH AXPUSH CXMOV CX,0030HPRT4:CALL DELAY1LOOP PRT4POP CXPOP AXRETDELAY10 ENDP CODE ENDS END START5、流程图四、设计结果与分析用8255A设计的结果实现了交通信号灯的控制以及特殊情况的信号处理。

具体实现为:南北东西四个方向。